(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3586268号

(P3586268)

(45) 発行日 平成16年11月10日(2004.11.10)

(24) 登録日 平成16年8月13日(2004.8.13)

(51) Int.C1.<sup>7</sup>

F 1

|             |             |   |

|-------------|-------------|---|

| HO1L 21/318 | HO1L 21/318 | M |

| HO1L 21/316 | HO1L 21/316 | X |

| HO1L 21/76  | HO1L 21/76  | L |

| HO1L 21/768 | HO1L 21/90  | M |

請求項の数 12 (全 10 頁)

|           |                              |

|-----------|------------------------------|

| (21) 出願番号 | 特願2002-200266 (P2002-200266) |

| (22) 出願日  | 平成14年7月9日 (2002.7.9)         |

| (65) 公開番号 | 特開2004-47565 (P2004-47565A)  |

| (43) 公開日  | 平成16年2月12日 (2004.2.12)       |

| 審査請求日     | 平成15年2月27日 (2003.2.27)       |

|           |                                       |

|-----------|---------------------------------------|

| (73) 特許権者 | 000003078<br>株式会社東芝<br>東京都港区芝浦一丁目1番1号 |

| (74) 代理人  | 100075812<br>弁理士 吉武 賢次                |

| (74) 代理人  | 100088889<br>弁理士 橋谷 英俊                |

| (74) 代理人  | 100082991<br>弁理士 佐藤 泰和                |

| (74) 代理人  | 100096921<br>弁理士 吉元 弘                 |

| (74) 代理人  | 100103263<br>弁理士 川崎 康                 |

最終頁に続く

(54) 【発明の名称】半導体装置及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項1】

半導体基板上に形成され、密度が $2.2\text{ g/cm}^3$ 以下であるシリコン窒化膜と、前記シリコン窒化膜上に、TEOS及び $\text{O}_3$ を含む雰囲気中で成膜されたシリコン酸化膜と、

を備えることを特徴とする半導体装置。

## 【請求項2】

半導体基板上に形成されたゲート電極と、前記ゲート電極を覆うように形成され、密度が $2.2\text{ g/cm}^3$ 以下であるシリコン窒化膜と、

前記シリコン窒化膜上に、TEOS及び $\text{O}_3$ を含む雰囲気中で成膜されたシリコン酸化膜と、

を備えることを特徴とする半導体装置。

## 【請求項3】

半導体基板の表面部分に形成された溝の内部表面を覆うように形成され、密度が $2.2\text{ g/cm}^3$ 以下であるシリコン窒化膜と、

前記シリコン窒化膜で覆われた前記溝の内部を埋め込むように、TEOS及び $\text{O}_3$ を含む雰囲気中で成膜されたシリコン酸化膜と、

を備えることを特徴とする半導体装置。

## 【請求項4】

10

20

前記シリコン窒化膜は、窒素／シリコン比が1.2以下であることを特徴とする請求項1乃至3のいずれかに記載の半導体装置。

【請求項5】

前記シリコン窒化膜は、膜中に含まれる塩素濃度が1.0E21~1.0E22 atoms/cm<sup>3</sup>であることを特徴とする請求項1乃至4のいずれかに記載の半導体装置。

【請求項6】

前記シリコン窒化膜は、膜表面から深さ1~3nmに渡って、酸素濃度が1.0E21 atoms/cm<sup>3</sup>以上であることを特徴とする請求項1乃至5のいずれかに記載の半導体装置。

【請求項7】

半導体基板上に、密度が2.2g/cm<sup>3</sup>以下であるシリコン窒化膜を形成する工程と、成膜温度が500以下、成膜圧力が200~760Torr、TEOS及びO<sub>3</sub>を含みO<sub>3</sub>の濃度が5wt%以上の雰囲気において、前記シリコン窒化膜上にシリコン酸化膜を形成する工程と、

を備えることを特徴とする半導体装置の製造方法。

【請求項8】

半導体基板上にゲート電極を形成する工程と、

前記ゲート電極を覆うように、密度が2.2g/cm<sup>3</sup>以下であるシリコン窒化膜を形成する工程と、

成膜温度が500以下、成膜圧力が200~760Torr、TEOS及びO<sub>3</sub>を含みO<sub>3</sub>の濃度が5wt%以上の雰囲気において、前記シリコン窒化膜上にシリコン酸化膜を形成する工程と、

を備えることを特徴とする半導体装置の製造方法。

【請求項9】

半導体基板の表面部分に溝を形成する工程と、

前記溝の内部表面を覆うように、密度が2.2g/cm<sup>3</sup>以下であるシリコン窒化膜を形成する工程と、

成膜温度が500以下、成膜圧力が200~760Torr、TEOS及びO<sub>3</sub>を含みO<sub>3</sub>の濃度が5wt%以上の雰囲気において、前記シリコン窒化膜で覆われた前記溝の内部を埋め込むようにシリコン酸化膜を形成する工程と、

を備えることを特徴とする半導体装置の製造方法。

【請求項10】

前記シリコン窒化膜を形成する工程では、Si<sub>n</sub>C<sub>1(2n+2-x)Hx</sub>(nは2以上の整数、xは0以上2n+1以下の整数)を原料とし、減圧CVD法を用いて前記シリコン窒化膜を形成することを特徴とする請求項7乃至9のいずれかに記載の半導体装置の製造方法。

【請求項11】

前記シリコン窒化膜を形成する工程では、成膜温度を350~600に設定することにより、前記シリコン窒化膜の密度を2.2g/cm<sup>3</sup>以下にすることを特徴とする請求項7乃至10のいずれかに記載の半導体装置の製造方法。

【請求項12】

前記シリコン窒化膜を形成する工程では、成膜温度を350~600に設定することにより、窒素／シリコン比を1.2以下にすることを特徴とする請求項7乃至11のいずれかに記載の半導体装置の製造方法。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は半導体装置及びその製造方法に係わり、例えばゲート電極上に層間絶縁膜を形成する場合、あるいはSTI(Shallow Trench Isolation)における溝の内部を絶縁膜で埋め込む場合等に好適なものに関する。

10

20

30

40

50

**【0002】****【従来の技術】**

ゲート電極を形成した後に、層間絶縁膜としてシリコン酸化( $\text{SiO}_2$ )膜を形成したり、STI形成時における溝の内部にシリコン酸化膜を埋め込むことが行われている。

**【0003】**

成膜温度が500℃以下で、 $\text{O}_3$  / TEOSの雰囲気中でシリコン酸化膜を成膜すると、リフロー工程無しにフロー性、即ち自己平坦性を示すような膜形状になり、優れた埋め込み特性を得ることができる。

**【0004】**

しかしこの場合の成膜反応は、下地膜の表面に対して大変敏感で依存性を有する場合がある。特に、シリコン窒化( $\text{SiN}$ )膜の表面上にシリコン酸化膜を形成する場合には、しばしば異常成長を起こし、ポーラスな膜を形成することがある。このような現象を、一般に下地依存性と称している。

10

**【0005】**

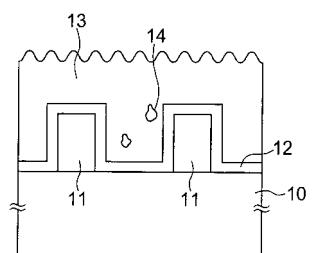

図11に、下地依存性が存在する状況でシリコン酸化膜を形成したときの断面の状態を示す。

**【0006】**

半導体基板10の表面上に電極材を堆積してパターニングを行い、ゲート電極11を形成する。ゲート電極11及び半導体基板10を覆うようにシリコン窒化膜12を形成した後、シリコン窒化膜12を覆うように、成膜温度が500℃以下、 $\text{O}_3$  / TEOS雰囲気中で層間絶縁膜としてのシリコン酸化膜13を形成する。シリコン酸化膜13に下地依存性があることにより、 $\text{O}_3$  / TEOSプロセス特有のフロー性が失われ、埋め込み特性が極端に劣化してシリコン酸化膜13中にボイド14が発生する。

20

**【0007】**

ここで、 $\text{O}_3$ 濃度が低い雰囲気中で成膜を行うと下地依存性が発生しないことが知られている。そこで従来は、成膜の初期段階において低濃度 $\text{O}_3$ ガスを用いて成膜し、その後高濃度 $\text{O}_3$ ガスで成膜するという2段階で成膜を行う手法がしばしば用いられていた。

**【0008】**

しかしこの手法により成膜する場合は、下地依存性を低減させるために、第1層目のシリコン酸化膜の膜厚が100nm以上必要となる。

30

**【0009】**

さらに、低 $\text{O}_3$ 濃度で成膜される第1層目のシリコン酸化膜は埋め込み特性が悪い。近年の微細化されたパターンでは、第1層目のシリコン酸化膜で溝の内部が埋まってしまうため、このような2段階で成膜する手法を用いることは困難となっている。

**【0010】**

また、プラズマ照射を行ってシリコン窒化膜の表面を改質することによっても、下地依存性を消失することができる。しかし、プラズマ照射のための装置が新たに必要となりコストが増加し、またプラズマダメージによりトランジスタ特性が劣化するという懸念もあり、この手法を用いることにも問題があった。

**【0011】**

40

**【発明が解決しようとする課題】**

上述のように、従来はゲート電極間やSTI等を埋め込むためシリコン酸化膜を形成する際に、下地依存性により埋め込み特性が劣化する問題があった。

**【0012】**

本発明は上記事情に鑑み、プラズマ照射のような新たな工程を追加したり、プラズマダメージによりトランジスタ特性を劣化させることなく、シリコン酸化膜を形成する際に下地依存性を解消し、良好な埋め込み特性を得ることが可能な半導体装置及びその製造方法を提供することを目的とする。

**【0013】****【課題を解決するための手段】**

50

本発明の半導体装置は、半導体基板上に形成され、密度が $2.2\text{ g/cm}^3$ 以下であるシリコン窒化膜と、前記シリコン窒化膜上に、TEOS及び $\text{O}_3$ を含む雰囲気中で成膜されたシリコン酸化膜とを備えることを特徴とする。

【0014】

また本発明の半導体装置は、半導体基板上に形成されたゲート電極と、前記ゲート電極を覆うように形成され、密度が $2.2\text{ g/cm}^3$ 以下であるシリコン窒化膜と、前記シリコン窒化膜上に、TEOS及び $\text{O}_3$ を含む雰囲気中で成膜されたシリコン酸化膜とを備えることを特徴とする。

【0015】

あるいは本発明の半導体装置は、半導体基板の表面部分に形成された溝の内部表面を覆うように形成され、密度が $2.2\text{ g/cm}^3$ 以下であるシリコン窒化膜と、前記シリコン窒化膜で覆われた前記溝の内部を埋め込むように、TEOS及び $\text{O}_3$ を含む雰囲気中で成膜されたシリコン酸化膜とを備えることを特徴とする。 10

【0016】

前記シリコン窒化膜は、窒素/シリコン比が1.2以下であってよく、また膜中に含まれる塩素濃度が $1.0\text{ E }21 \sim 1.0\text{ E }22\text{ atoms/cm}^3$ であってもよく、さらには膜表面から深さ $1 \sim 3\text{ nm}$ に渡って、酸素濃度が $1.0\text{ E }21\text{ atoms/cm}^3$ 以上であってもよい。

【0017】

本発明の半導体装置の製造方法は、半導体基板上に、密度が $2.2\text{ g/cm}^3$ 以下であるシリコン窒化膜を形成する工程と、成膜温度が500以下、成膜圧力が $200 \sim 760\text{ Torr}$ 、TEOS及び $\text{O}_3$ を含み $\text{O}_3$ の濃度が5wt%以上の雰囲気において、前記シリコン窒化膜上にシリコン酸化膜を形成する工程とを備えることを特徴とする。 20

【0018】

また本発明の半導体装置の製造方法は、半導体基板上にゲート電極を形成する工程と、前記ゲート電極を覆うように、密度が $2.2\text{ g/cm}^3$ 以下であるシリコン窒化膜を形成する工程と、成膜温度が500以下、成膜圧力が $200 \sim 760\text{ Torr}$ 、TEOS及び $\text{O}_3$ を含み $\text{O}_3$ の濃度が5wt%以上の雰囲気において、前記シリコン窒化膜上にシリコン酸化膜を形成する工程とを備えることを特徴とする。

【0019】

あるいは本発明の半導体装置の製造方法は、半導体基板の表面部分に溝を形成する工程と、前記溝の内部表面を覆うように、密度が $2.2\text{ g/cm}^3$ 以下であるシリコン窒化膜を形成する工程と、成膜温度が500以下、成膜圧力が $200 \sim 760\text{ Torr}$ 、TEOS及び $\text{O}_3$ を含み $\text{O}_3$ の濃度が5wt%以上の雰囲気において、前記シリコン窒化膜で覆われた前記溝の内部を埋め込むようにシリコン酸化膜を形成する工程とを備えることを特徴とする。 30

【0020】

前記シリコン窒化膜を形成する工程では、 $\text{Si}_n\text{C}_1(2n+2-x)\text{H}_x$ (nは2以上の整数、xは0以上 $2n+1$ 以下の整数)を原料とし、減圧CVD法を用いて前記シリコン窒化膜を形成することもできる。 40

【0021】

あるいは前記シリコン窒化膜を形成する工程では、成膜温度を $350 \sim 600$ に設定することにより、前記シリコン窒化膜の密度を $2.2\text{ g/cm}^3$ 以下にすることもできる。

【0022】

あるいはまた、前記シリコン窒化膜を形成する工程では、成膜温度を $350 \sim 600$ に設定することにより、窒素/シリコン比を1.2以下にしてもよい。

【0023】

【発明の実施の形態】

上述したように、従来はシリコン酸化膜を形成する際の下地依存性が問題となっていた。これに対し発明者は、下地となるシリコン窒化膜の膜密度が小さい場合には依存性が軽減

されることを確認するに至った。膜密度が小さいシリコン窒化膜上に、フロー性が得られる成膜条件として、500以下成膜温度でO<sub>3</sub> / TEOS 雰囲気中においてシリコン酸化膜を形成することにより、下地依存性が低く埋め込み性能に優れたシリコン酸化膜を形成することができる。

【0024】

以下、上記考察に基づいて成した本発明の実施の形態について図面を参照して説明する。

【0025】

(1) 第1の実施の形態

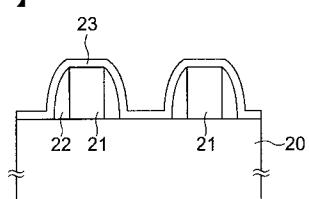

本発明の第1の実施の形態について、図1を用いて説明する。本実施の形態は、ゲート電極上に層間絶縁膜としてシリコン酸化膜を形成する場合に関する。10

【0026】

半導体基板20の表面上に電極材を堆積してパターニングを行い、ゲート電極21を形成する。ゲート電極21及び半導体基板20を覆うようにシリコン窒化膜22を堆積し、エッチバックを行って電極21の側面にのみ残存させてスペーサ22を形成する。

【0027】

さらに、ゲート電極21、スペーサ22及び半導体基板20を覆うように、シリコン窒化膜23を形成する。このシリコン窒化膜23の形成は、HCDガス、即ちSi<sub>n</sub>C<sub>1(2n+2-x)Hx</sub>(nは2以上の整数、xは0以上2n+1以下の整数)、及びアンモニア(NH<sub>3</sub>)を原料とし、成膜温度を350~600、好ましくは例えば450として減圧CVD法を用いて行う。このような低温で成膜することにより、シリコン窒化膜を2.2g/cm<sup>3</sup>以下の低密度とすることができます。20

【0028】

また、この場合のシリコン窒化膜23の窒素/シリコン比は、1.2以下となる。シリコン窒化膜23の膜中に含まれる塩素濃度は、HCDガスを用いた場合はこのガスに含まれる塩素が原因となり、1.0E21~1.0E22atoms/cm<sup>3</sup>となる。さらに、このシリコン窒化膜23は、膜密度が低く表面が酸化され易い状態にあるため、膜表面から深さ1~3nmに渡って、酸素濃度が1.0E21atoms/cm<sup>3</sup>以上となる。

【0029】

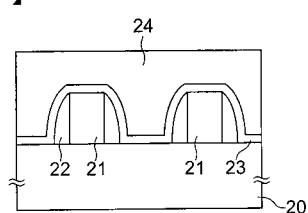

得られた低密度のシリコン窒化膜23を覆うように、フロー性が得られる成膜条件として成膜温度が500以下、好ましくは例えば400~480、成膜圧力が200~760Torr、O<sub>3</sub>濃度が5wt%以上、O<sub>3</sub> / TEOS雰囲気中で、図2に示されたように層間絶縁膜としてシリコン酸化膜24を堆積する。30

【0030】

シリコン窒化膜23を低密度に形成したことで、シリコン酸化膜24の下地依存性が消滅する。これにより、O<sub>3</sub> / TEOSプロセス特有のフロー性が失われず、埋め込み性能が劣化せず、シリコン酸化膜24中のボイドの発生が防止される。

【0031】

(2) 第2の実施の形態

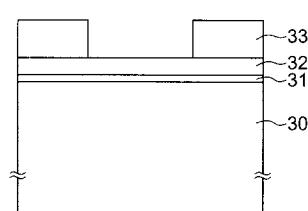

本発明の第2の実施の形態について、図3~図7を用いて説明する。本実施の形態は、STI工程において形成された溝の内部を埋め込むためにシリコン酸化膜を形成する場合に関する。40

【0032】

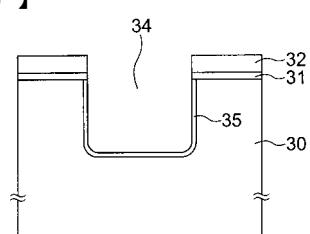

図3に示されたように、半導体基板30の表面上に熱酸化法を用いてシリコン酸化膜31を形成し、シリコン酸化膜31上にCVD法によりシリコン窒化膜32を形成する。シリコン窒化膜32上に、溝を形成する部分が除去されたレジスト膜33を形成する。

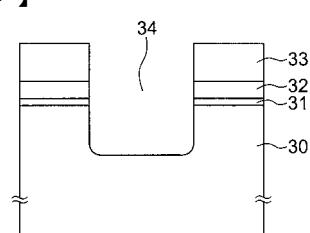

【0033】

図4に示されたように、レジスト膜33をマスクとして異方性エッチングを行い、半導体基板30の表面部分に溝34を形成する。レジスト膜33を除去する。

【0034】

図5に示されたように、溝34の内面に露出した基板表面上に、熱酸化法を用いてシリコン酸化膜34を形成する。

【0035】

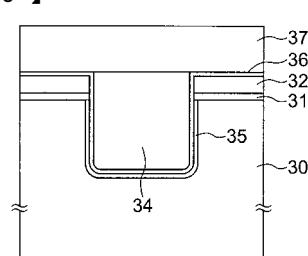

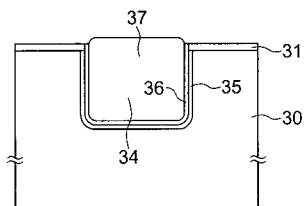

図6に示されたように、溝34の内部表面を含めて全体を覆うように、シリコン窒化膜36を $2.2\text{ g/cm}^3$ 以下の低密度で形成する。この場合の成膜条件は、上記第1の実施の形態と同様である。

【0036】

このシリコン窒化膜36の表面上に、上記第1の実施の形態と同様の成膜条件で、シリコン酸化膜37をSTIの埋め込み材として堆積する。この後、図7に示されたように、CMP(Chemical Mechanical Polishing)、及び密度を高めるためのアニール処理を行う。さらに、ホット磷酸を用いてシリコン窒化32、36を除去し、STIを得る。

【0037】

熱酸化法により形成したシリコン酸化膜上に直接 $\text{O}_3/\text{TEOS}$ によるシリコン酸化膜を形成すると、下地依存性が大きく現れる。本実施の形態では、熱酸化法によるシリコン酸化膜35の表面上に直接 $\text{O}_3/\text{TEOS}$ 雰囲気中でシリコン酸化膜37を成膜せず、バッファ層として膜密度が低いシリコン窒化膜36を形成することで、 $\text{O}_3/\text{TEOS}$ 雰囲気中でシリコン酸化膜37を下地依存性が消失する。これにより、 $\text{O}_3/\text{TEOS}$ プロセス特有のフロー性が現れ、埋め込み特性が向上しボイドを発生させることなく溝34を埋め込むことができる。

【0038】

ここで、シリコン窒化膜36が溝34の内部に残るが、絶縁膜であるためデバイス特性に影響は与えない。

【0039】

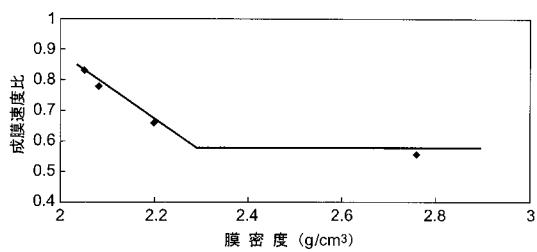

下地依存性を議論する際、しばしば成膜速度比(=シリコン窒化膜上でのシリコン酸化膜の成長速度/シリコン基板上でのシリコン酸化膜の成長速度)が指標として使用される。下地依存性が存在する場合には、シリコン窒化膜上でのシリコン酸化膜の膜成長速度が小さくなるため、成膜速度比が小さくなる。

【0040】

図8に、成膜速度比がシリコン窒化膜の膜密度に依存する特性を示す。このグラフより、シリコン窒化膜の膜密度が小さいほど成膜速度比が大きくなっている。下地依存性が軽減されることがわかる。また、その成膜速度比の変化は、シリコン窒化膜の膜密度が $2.2\text{ g/cm}^3$ を境に大きくなっている。よって、上記実施の形態では、シリコン窒化膜の膜密度を $2.2\text{ g/cm}^3$ 以下としている。

【0041】

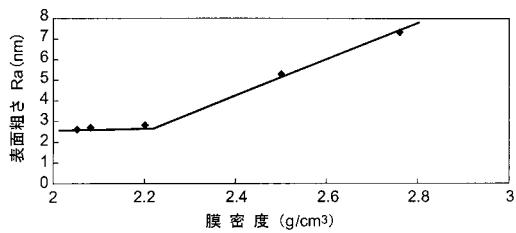

次に、 $\text{O}_3/\text{TEOS}$ 雰囲気中でシリコン酸化膜の表面粗さが下地のシリコン窒化膜の膜密度に依存する特性を図9に示す。

【0042】

このグラフから明らかなように、シリコン窒化膜の膜密度が $2.2\text{ g/cm}^3$ 下を超えると、下地依存性が発生してシリコン酸化膜が異常成長し、シリコン酸化膜の表面の粗さが大きくなる。このシリコン酸化膜の表面粗さの変化も、上述した成膜速度比と同様に、シリコン窒化膜の膜密度が $2.2\text{ g/cm}^3$ 以下の領域から改善していることが分かる。

【0043】

膜密度が $2.2\text{ g/cm}^3$ 以下のシリコン窒化膜は、膜質が悪く、ポーラスな膜になっている。このため、膜表面が酸化され易く、膜表面から深さ $1\sim3\text{ nm}$ の範囲に渡って、酸素が約 $1.0\text{ E }21$ の濃度で含まれている。このような膜密度の低いポーラスなシリコン窒化膜には、中間生成物の吸着サイトが多く存在することで下地依存性が軽減されると考えられる。

【0044】

またこのようなシリコン窒化膜は、上述したように低温で成膜することで得られるが、そ

10

20

30

40

50

の際に膜中に塩素を多く含み、膜中濃度が  $1.0 \times 10^{-21} \sim 1.0 \times 10^{-22}$  atoms/cm<sup>3</sup> の範囲で存在する。

【0045】

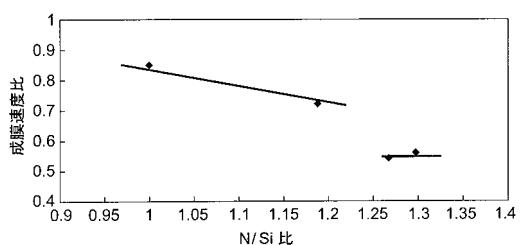

シリコン窒化膜のN/Si組成比と成膜速度比との関係を図9に示す。このグラフから、シリコンが過剰なほど成膜速度比が大きく、下地依存性が小さくなっていることがわかる。膜表面の過剰なシリコンは、大気中の酸素によってポーラスな酸化膜を形成し、中間生成物の吸着サイトを多く生成し下地依存性が軽減されると考えられる。このグラフに示されたように、成膜速度比はN/Si比が1.2以下の領域で大きくなっていること、この領域においてシリコン窒化膜の表面にポーラスな酸化膜が形成されると考えられる。

【0046】

このようなポーラスなシリコン窒化膜を下地に使用することで、埋め込み性に優れたO<sub>3</sub>/TEOSによるシリコン酸化膜を形成することができる。

【0047】

上述した実施の形態は一例であり、本発明を限定するものではない。例えば、上述した実施の形態では、低温においてシリコン窒化膜の成膜が可能なようにHCDガスを用いている。しかしこれに限らず、低温での成膜が可能なように例えばBTBASガス等、他のガスを用いてもよい。

【0048】

【発明の効果】

以上説明したように、本発明の半導体装置及びその製造方法によれば、膜密度が低いシリコン窒化膜上に、O<sub>3</sub>/TEOS雰囲気中でシリコン酸化膜を500以下の温度で成膜することにより、下地依存性が消失し優れた埋め込み特性を得ることができる。

【図面の簡単な説明】

【図1】本発明の第1の実施の形態による半導体装置の縦断面及びその製造方法における一工程を示した縦断面図。

【図2】同第1の実施の形態による半導体装置の縦断面及びその製造方法における一工程を示した縦断面図。

【図3】本発明の第2の実施の形態による半導体装置の縦断面及びその製造方法における一工程を示した縦断面図。

【図4】同第2の実施の形態による半導体装置の縦断面及びその製造方法における一工程を示した縦断面図。

【図5】同第2の実施の形態による半導体装置の縦断面及びその製造方法における一工程を示した縦断面図。

【図6】同第2の実施の形態による半導体装置の縦断面及びその製造方法における一工程を示した縦断面図。

【図7】同第2の実施の形態による半導体装置の縦断面及びその製造方法における一工程を示した縦断面図。

【図8】シリコン酸化膜の成膜速度比が、下地のシリコン窒化膜の密度に依存する特性を示したグラフ。

【図9】シリコン酸化膜の表面粗さが、下地のシリコン窒化膜の密度に依存する特性を示したグラフ。

【図10】シリコン酸化膜の成膜速度比が、下地のシリコン窒化膜のN/Si組成比に依存する特性を示したグラフ。

【図11】従来の半導体装置の縦断面及びその製造方法における一工程を示した縦断面図。

【符号の説明】

20、30 半導体基板

21 ゲート電極

22 シリコン窒化膜によるスペーサ

23、36 シリコン窒化膜(低密度)

10

20

30

40

50

- 2 4、3 7 シリコン酸化膜 (O<sub>3</sub> / TEOS 膜)

3 1、3 5 シリコン酸化膜 (熱酸化膜)

3 2 シリコン窒化膜

3 3 レジスト膜

3 4 溝

【図 1】

【図 2】

【図 3】

【図 4】

【図 5】

【図 6】

【図7】

【図8】

【図9】

【図10】

【図11】

---

フロントページの続き

(72)発明者 桧 山 晋

神奈川県横浜市磯子区新杉田町8番地 株式会社東芝 横浜事業所内

(72)発明者 赤 堀 浩 史

神奈川県横浜市磯子区新杉田町8番地 株式会社東芝 横浜事業所内

(72)発明者 斎 田 繁 彦

神奈川県横浜市磯子区新杉田町8番地 株式会社東芝 横浜事業所内

(72)発明者 山 本 明 人

神奈川県横浜市磯子区新杉田町8番地 株式会社東芝 横浜事業所内

審査官 和瀬田 芳正

(56)参考文献 特開2001-168092(JP,A)

特開平5-259297(JP,A)

特開平7-94505(JP,A)

特開2001-102441(JP,A)

(58)調査した分野(Int.Cl.<sup>7</sup>, DB名)

H01L 21/316 - 21/318

H01L 21/76

H01L 21/768