(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6794635号

(P6794635)

(45) 発行日 令和2年12月2日(2020.12.2)

(24) 登録日 令和2年11月16日(2020.11.16)

|              |              |

|--------------|--------------|

| (51) Int.Cl. | F 1          |

| B 41 J 2/045 | (2006.01)    |

| B 41 J 2/14  | (2006.01)    |

| H 03 F 3/217 | (2006.01)    |

|              | B 41 J 2/045 |

|              | B 41 J 2/14  |

|              | H 03 F 3/217 |

請求項の数 9 (全 44 頁)

(21) 出願番号 特願2016-34988 (P2016-34988)

(22) 出願日 平成28年2月26日 (2016.2.26)

(65) 公開番号 特開2017-149065 (P2017-149065A)

(43) 公開日 平成29年8月31日 (2017.8.31)

審査請求日 平成31年1月10日 (2019.1.10)

(73) 特許権者 000002369

セイコーエプソン株式会社

東京都新宿区新宿四丁目1番6号

(74) 代理人 100125689

弁理士 大林 章

(74) 代理人 100128598

弁理士 高田 聖一

(74) 代理人 100121108

弁理士 高橋 太朗

(72) 発明者 阿部 彰

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

審査官 石附 直弥

最終頁に続く

(54) 【発明の名称】 駆動回路、駆動回路の制御方法および液体吐出装置

## (57) 【特許請求の範囲】

## 【請求項 1】

容量性負荷を駆動する駆動信号の電圧と前記駆動信号の元となる元駆動信号の電圧とに基づいた差電圧を増幅して出力する差動増幅器と、

ハイサイドトランジスターおよびローサイドトランジスターを含み、前記駆動信号を出力端から出力する増幅部と、

を備え、

前記駆動信号は、

単位時間当たりで第1電圧以上で電圧が変化する第1期間と、

前記単位時間当たりで第1電圧よりも低く電圧が変化する、または、変化しない第2期間と、

を含み、

前記第1期間では、前記ハイサイドトランジスターと前記ローサイドトランジスターとの一方がスイッチング動作する期間を含み、

前記第2期間では、前記ハイサイドトランジスターと前記ローサイドトランジスターとの一方がリニア動作する期間を含む、

ことを特徴とする駆動回路。

## 【請求項 2】

前記駆動信号は、台形波形であり、

前記第1期間は、前記駆動信号の電圧が変化する期間であり、

10

20

前記第2期間は、前記駆動信号の電圧が一定である期間であることを特徴とする請求項1に記載の駆動回路。

**【請求項3】**

前記駆動信号は、傾きに連続性を有する波形であり、

前記第1期間は、前記駆動信号の電圧変化が相対的に大きい期間であり、

前記第2期間は、前記駆動信号の電圧変化が相対的に小さい期間である、

ことを特徴とする請求項1に記載の駆動回路。

**【請求項4】**

前記第1期間のうち、

前記駆動信号の電圧が上昇する場合では、前記ハイサイドトランジスターがスイッチング動作し、前記ローサイドトランジスターがオフし、10

前記駆動信号の電圧が低下する場合では、前記ローサイドトランジスターがスイッチング動作し、前記ハイサイドトランジスターがオフする、

ことを特徴とする請求項1乃至3のいずれかに記載の駆動回路。

**【請求項5】**

前記第2期間のうち、

前記駆動信号が所定の閾値以上の電圧の場合では、前記ハイサイドトランジスターがリニア動作し、前記ローサイドトランジスターがオフし、20

前記駆動信号が前記閾値よりも低い電圧の場合では、前記ローサイドトランジスターがリニア動作し、前記ハイサイドトランジスターがオフする、

ことを特徴とする請求項1乃至4のいずれかに記載の駆動回路。

**【請求項6】**

前記閾値は、

前記駆動信号の電圧の最高値よりも低く、

前記駆動信号の電圧の最低値よりも高い、

ことを特徴とする請求項5に記載の駆動回路。

**【請求項7】**

前記ハイサイドトランジスターまたは前記ローサイドトランジスターのいずれかを選択し、当該選択したトランジスターのゲート端子に前記差電圧を印加し、非選択としたトランジスターのゲート端子に当該非選択としたトランジスターをオフにさせる信号を供給するセレクターをさらに備える30

ことを特徴とする請求項1乃至6のいずれかに記載の駆動回路。

**【請求項8】**

容量性負荷を駆動する駆動信号の電圧と前記駆動信号の元となる元駆動信号の電圧とに基づいた差電圧を増幅して出力する差動増幅器と、

ハイサイドトランジスターおよびローサイドトランジスターを含み、前記駆動信号を出力端から出力する増幅部と、

を備え、容量性負荷を駆動する駆動回路の制御方法であって、

前記駆動信号は、

単位時間当たりで第1電圧以上で電圧が変化する第1期間と、40

前記単位時間当たりで第1電圧よりも低く電圧が変化する、または、変化しない第2期間と、

を含み、

前記差動増幅器は、

前記第1期間の少なくとも一部期間において、前記ハイサイドトランジスターと前記ローサイドトランジスターとの一方をスイッチング動作させ、

前記第2期間の少なくとも一部期間において、前記ハイサイドトランジスターと前記ローサイドトランジスターとの一方をリニア動作させる、

ことを特徴とする駆動回路の制御方法。

**【請求項9】**

駆動信号の印加により変位する圧電素子を含み、当該圧電素子の変位により液体を吐出する吐出部と、

前記駆動信号の電圧と前記駆動信号の元となる元駆動信号の電圧とに基づいた差電圧を増幅して出力する差動増幅器と、

ハイサイドトランジスターおよびローサイドトランジスターを含み、前記駆動信号を出力端から出力する増幅部と、

を備え、

前記駆動信号は、

単位時間当たりで第1電圧以上で電圧が変化する第1期間と、

前記単位時間当たりで第1電圧よりも低く電圧が変化する、または、変化しない第2期間と、10

を含み、

前記第1期間では、前記ハイサイドトランジスターと前記ローサイドトランジスターとの一方がスイッチング動作する期間を含み、

前記第2期間では、前記ハイサイドトランジスターと前記ローサイドトランジスターとの一方がリニア動作する期間を含む、

ことを特徴とする液体吐出装置。

#### 【発明の詳細な説明】

##### 【技術分野】

20

##### 【0001】

本発明は、駆動回路、駆動回路の制御方法および液体吐出装置に関する。

##### 【背景技術】

##### 【0002】

インクを吐出して画像や文書を印刷するインクジェットプリンターには、圧電素子（例えばピエゾ素子）を用いたものが知られている。圧電素子は、ヘッドユニットにおいて複数のノズルのそれぞれに対応して設けられ、それぞれが駆動信号にしたがって駆動されることにより、ノズルから所定のタイミングで所定量のインク（液体）を吐出させて、ドットを形成させる。圧電素子は、電気的にみればコンデンサーのような容量性負荷であるので、各ノズルの圧電素子を動作させるためには十分な電流を供給する必要がある。30

##### 【0003】

このため、駆動信号の元となる元駆動信号を増幅回路で増幅し、駆動信号としてヘッドユニットに供給して、圧電素子を駆動する構成となっている。増幅回路としては、元駆動信号をA B級などで電流増幅する方式（リニア増幅、特許文献1参照）が挙げられる。ただし、リニア増幅では消費電力が大きく、エネルギー効率が悪いので、近年では、D級増幅についても提案されている（特許文献2参照）。D級増幅は、端的にいえば、元駆動信号をパルス幅変調やパルス密度変調するとともに、当該変調信号にしたがって電源電圧間ににおいて直列に挿入されたハイサイドトランジスターおよびローサイドトランジスターをスイッチングし、このスイッチングによる出力信号をローパスフィルターで濾波することで、元駆動信号を増幅する、というものである。40

##### 【先行技術文献】

##### 【特許文献】

##### 【0004】

【特許文献1】特開2009-190287号公報

【特許文献2】特開2010-114711号公報

##### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0005】

しかしながら、D級増幅方式では、リニア増幅方式と比較してエネルギー効率が高いものの、ローパスフィルターで消費される電力が無視できないので、消費電力を改善する点50

において改良の余地がある。

そこで、本発明のいくつかの態様の目的の一つは、消費電力を改善した駆動回路、駆動回路の制御方法および液体吐出装置を提供することにある。

【課題を解決するための手段】

【0006】

上記目的の一つを達成するために、本発明の一態様に係る駆動回路は、容量性負荷を駆動する駆動信号と前記駆動信号の元となる元駆動信号とに基づいて制御信号を生成する制御信号生成部と、前記制御信号に基づいて制御されるハイサイドトランジスターおよびローサイドトランジスターを含み、前記駆動信号を出力端から出力する増幅部と、を備え、容量性負荷を駆動する駆動回路であって、前記駆動信号は、単位時間当たりで第1電圧以上で電圧が変化する第1期間と、前記単位時間当たりで第1電圧よりも低く電圧が変化する、または、変化しない第2期間と、を含み、前記第1期間では、前記ハイサイドトランジスターと前記ローサイドトランジスターとの一方がスイッチング動作する期間を含み、前記第2期間では、前記ハイサイドトランジスターと前記ローサイドトランジスターとの一方がリニア動作する期間を含む、ことを特徴とする。

上記一態様に係る駆動回路によれば、D級増幅方式と比較して、ローパスフィルターが不要であるので、当該ローパスフィルターにおいて消費される電力を無視することができ、その分、低消費電力化が図られる。また、D級増幅方式のように、スイッチング動作だけであると、駆動信号の波形精度が低下しやすいが、上記一態様によれば、第2期間でのリニア動作によって波形精度の向上が図られる。

【0007】

上記一態様に係る駆動回路において、前記駆動信号は、台形波形であり、前記第1期間は、前記駆動信号の電圧が変化する期間であり、前記第2期間は、前記駆動信号の電圧が一定である期間である構成としても良い。この構成によれば、例えば圧電素子の駆動に適切な台形波形を、リニア動作により精度良く再現することができる。

また、上記一態様に係る駆動回路において、前記駆動信号は、傾きに連続性を有する波形であり、前記第1期間は、前記駆動信号の電圧変化が相対的に大きい期間であり、前記第2期間は、前記駆動信号の電圧変化が相対的に小さき期間である構成としても良い。この構成によれば、傾きに連続性を有する波形については、例えば正弦波の極小・極大値付近のように、電圧変化が相対的に小さい期間では、リニア動作により精度良く再現することができる。

【0008】

上記一態様に係る駆動回路において、前記第1期間のうち、前記駆動信号の電圧が上昇する場合には、前記ハイサイドトランジスターがスイッチング動作し、前記ローサイドトランジスターがオフし、前記駆動信号の電圧が低下する場合には、前記ローサイドトランジスターがスイッチング動作し、前記ハイサイドトランジスターがオフする構成としても良い。

また、上記一態様に係る駆動回路において、前記第2期間のうち、前記駆動信号が所定の閾値以上の電圧の場合では、前記ハイサイドトランジスターがリニア動作し、前記ローサイドトランジスターがオフし、前記駆動信号が前記閾値よりも低い電圧の場合では、前記ローサイドトランジスターがリニア動作し、前記ハイサイドトランジスターがオフする構成としても良い。

この構成において、前記閾値は、前記駆動信号の電圧の最高値よりも低く、前記駆動信号の電圧の最低値よりも高くしても良い。

【0009】

なお、本発明は、圧電素子のような容量性負荷を駆動する駆動回路に限られず、種々の態様で実現することが可能であり、例えば駆動回路の制御方法や、当該駆動回路を含む液体吐出装置、さらには、当該液体吐出装置におけるヘッドユニットなどとしても概念することが可能である。

また、ここでいう液体吐出装置とは、液体を吐出するものであれば良く、これには後述

10

20

30

40

50

する印刷装置のほかに、立体造形装置（いわゆる 3D プリンター）、捺染装置なども含まれる。

【図面の簡単な説明】

【0010】

【図 1】印刷装置（その 1）の概略構成を示す図である。

【図 2 A】ヘッドユニットにおけるノズルの配列等を示す図である。

【図 2 B】ヘッドユニットにおけるノズルの配列等を示す図である。

【図 3】ヘッドユニットにおける要部構成を示す断面図である。

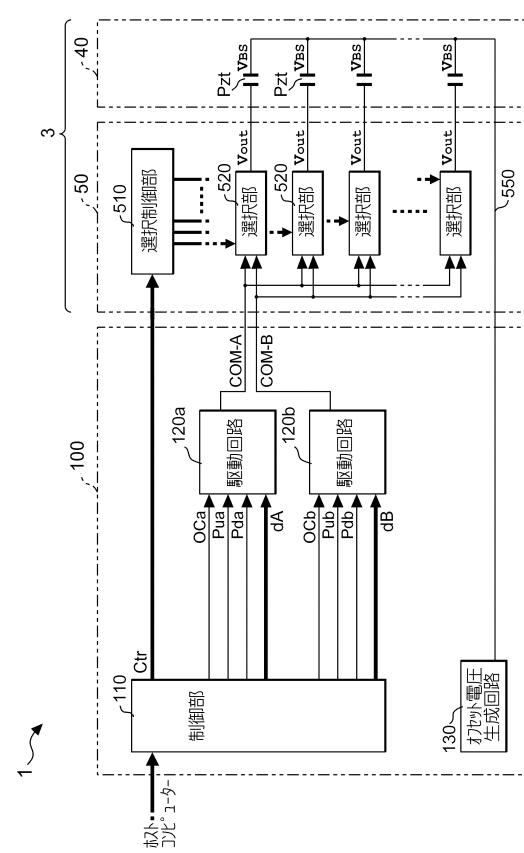

【図 4】印刷装置（その 1）の電気的な構成を示すブロック図である。

【図 5】駆動信号の波形等を説明するための図である。

【図 6】選択制御部の構成を示す図である。

【図 7】デコーダーのデコード内容を示す図である。

【図 8】選択部の構成を示す図である。

【図 9】選択部から圧電素子に供給される駆動信号を示す図である。

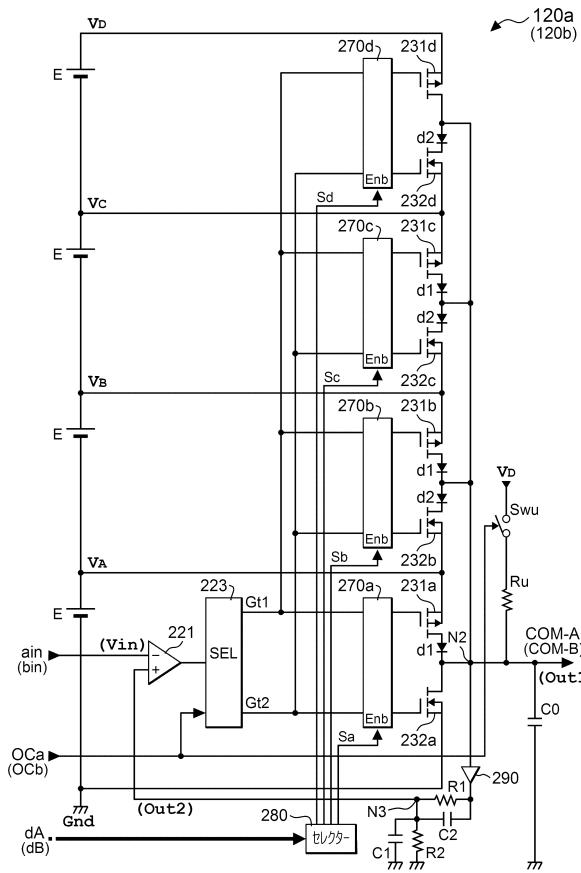

【図 10】印刷装置（その 1）に適用される駆動回路（その 1）の構成を示す図である。

【図 11】駆動回路（その 1）の動作を説明するための図である。

【図 12 A】駆動回路（その 2）を示す図である。

【図 12 B】駆動回路（その 3）を示す図である。

【図 13】印刷装置（その 2）の電気的な構成を示すブロック図である。

【図 14 A】印刷装置（その 2）に適用される駆動回路（その 4）を示す図である。

【図 14 B】印刷装置（その 2）に適用される駆動回路（その 5）を示す図である。

【図 15】駆動回路（その 4）の電圧範囲を示す図である。

【図 16】駆動回路（その 4）の動作を説明するための図である。

【図 17】印刷装置（その 3）の電気的な構成を示すブロック図である。

【図 18】印刷装置（その 3）に適用される駆動回路（その 6）を示す図である。

【図 19】印刷装置（その 3）に適用される駆動回路（その 7）を示す図である。

【図 20】駆動回路（その 7）における単位回路を示す図である。

【図 21】印刷装置（その 4）の電気的な構成を示すブロック図である。

【図 22】印刷装置（その 4）に適用される駆動回路（その 8）を示す図である。

【図 23】印刷装置（その 4）に適用される駆動回路（その 9）を示す図である。

【図 24】駆動回路（その 9）における単位回路を示す図である。

【図 25】印刷装置（その 3）に適用される駆動回路（その 10）を示す図である。

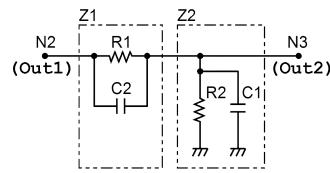

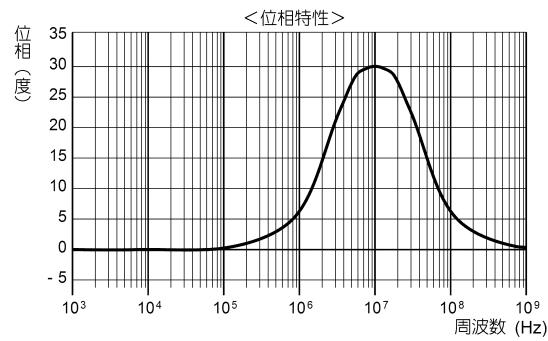

【図 26】駆動回路（その 10）における微積回路のゲイン特性を示す図である。

【図 27】駆動回路（その 10）における微積回路の位相特性を示す図である。

【図 28】駆動回路（その 10）における微積回路を示す図である。

【図 29】印刷装置（その 3）に適用される駆動回路（その 11）を示す図である。

【図 30】印刷装置（その 5）の電気的な構成を示すブロック図である。

【図 31】印刷装置（その 5）に適用される駆動回路（その 12）を示す図である。

【図 32】駆動回路（その 13）を示す図である。

【発明を実施するための形態】

【0011】

以下、図面を参照して本発明を実施するための形態について、印刷装置を例にとって説明する。

【0012】

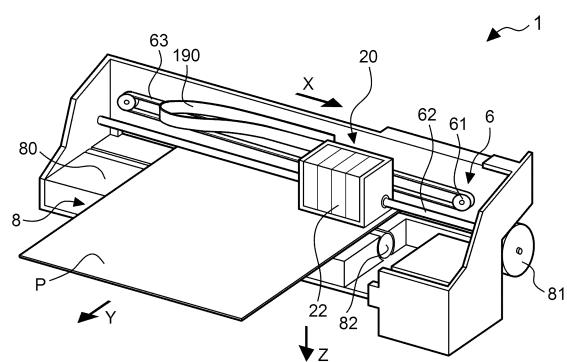

図 1 は、印刷装置（その 1）の概略構成を示す斜視図である。

この図に示される印刷装置（その 1）は、液体の一例であるインクを吐出することによって、紙などの媒体 P にインクドット群を形成し、これにより、画像（文字、図形等を含む）を印刷する液体吐出装置の一種である。

なお、印刷装置については、便宜的に符号を 1 で統一するが、後述するように、いくつかの態様が存在するので、区別するために印刷装置（その 1）、印刷装置（その 2）とい

10

20

30

40

50

うように符号の代わりに括弧書を付与する場合がある。

【0013】

図1に示されるように、印刷装置1は、キャリッジ20を、主走査方向(X方向)に移動(往復動)させる移動機構6を備える。

移動機構6は、キャリッジ20を移動させるキャリッジモーター61と、両端が固定されたキャリッジガイド軸62と、キャリッジガイド軸62とほぼ平行に延在し、キャリッジモーター61により駆動されるタイミングベルト63と、を有している。

キャリッジ20は、キャリッジガイド軸62に往復動自在に支持されるとともに、タイミングベルト63の一部に固定されている。そのため、キャリッジモーター61によりタイミングベルト63を正逆走行させると、キャリッジ20がキャリッジガイド軸62に案内されて往復動する。

【0014】

キャリッジ20には、印刷ヘッド22が搭載されている。この印刷ヘッド22は、媒体Pと対向する部分に、インクを個別にZ方向に吐出する複数のノズルを有する。なお、印刷ヘッド22は、カラー印刷のために、概略的に4個のブロックに分かれている。個々のブロックは、ブラック(Bk)、シアン(C)、マゼンタ(M)、イエロー(Y)のインクをそれぞれ吐出する。

なお、キャリッジ20には、フレキシブルフラットケーブル190を介してメイン基板(この図では省略)から駆動信号を含む各種の制御信号等が供給される構成となっている。

【0015】

印刷装置1は、媒体Pを、プラテン80上で搬送させる搬送機構8を備える。搬送機構8は、駆動源である搬送モーター81と、搬送モーター81により回転し、媒体Pを副走査方向(Y方向)に搬送する搬送ローラー82と、を備える。

【0016】

このような構成において、キャリッジ20の主走査に合わせて印刷ヘッド22のノズルから印刷データに応じてインクを吐出せるとともに、媒体Pを搬送機構8によって搬送する動作を繰り返すことで、媒体Pの表面に画像が形成される。

なお、本実施形態において主走査は、キャリッジ20を移動させることで実行されるが、媒体Pを移動させることで実行しても良く、キャリッジ20と媒体Pとの双方を移動させても良い。要は、媒体Pとキャリッジ20(印刷ヘッド22)とが相対的に移動する構成であれば良い。

【0017】

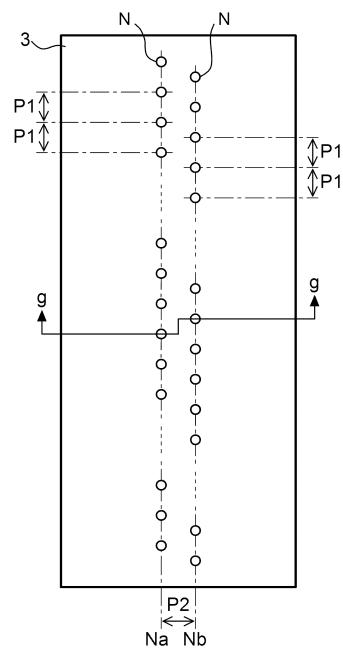

図2Aは、印刷ヘッド22におけるインクの吐出面を媒体Pからみた場合の構成を示す図である。この図に示されるように、印刷ヘッド22は、4個のヘッドユニット3を有する。4個のヘッドユニット3の各々は、それぞれブラック(Bk)、シアン(C)、マゼンタ(M)、イエロー(Y)に対応し、主走査方向であるX方向に沿って配列する。

【0018】

図2Bは、1個のヘッドユニット3におけるノズルの配列を示す図である。

この図に示されるように、1個のヘッドユニット3では、複数のノズルNが2列で配列する。ここで、説明の便宜上、この2列をそれぞれノズル列Na、Nbとする。

【0019】

ノズル列Na、Nbでは、それぞれ複数のノズルNが、副走査方向であるY方向に沿ってピッチP1で配列する。また、ノズル列Na、Nb同士は、X方向にピッチP2だけ離間する。ノズル列Naに属するノズルNとノズル列Nbに属するノズルNとは、Y方向に、ピッチP1の半分だけシフトした関係となっている。

このようにノズルNを、ノズル列Na、Nbの2列で、Y方向にピッチP1の半分だけシフトして配置することにより、Y方向の解像度を、1列の場合と比較して実質的に倍に高めることができる。

なお、1個のヘッドユニット3におけるノズルNの個数を便宜的にm(mは2以上の整

10

20

30

40

50

数)とする。

【0020】

ヘッドユニット3は、特に図示しないが、アクチュエーター基板に可撓性の回路基板が接続されるとともに、当該可撓性の回路基板に駆動ICが実装された構成である。そこで次に、アクチュエーター基板の構造について説明する。

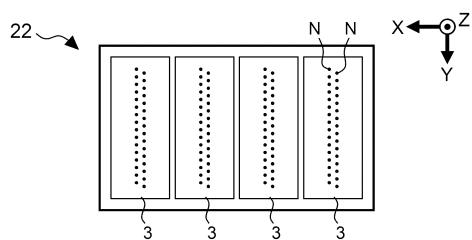

【0021】

図3は、アクチュエーター基板の構造を示す断面図である。詳細には図2Bにおけるg-g線で破断した場合の断面を示す図である。

図3に示されるように、アクチュエーター基板40は、流路基板42のうち、Z方向の負側の面上に圧力室基板44と振動板46とが設けられる一方、Z方向の正側の面上にノズル板41が設置された構造である。

アクチュエーター基板40の各要素は、概略的にはY方向に長尺な略平板状の部材であり、例えば接着剤等により互いに固定される。また、流路基板42および圧力室基板44は、例えばシリコンの単結晶基板で形成される。

【0022】

ノズルNは、ノズル板41に形成される。ノズル列Naに属するノズルに対応する構造と、ノズル列Nbに属するノズルに対応する構造とは、Y方向にピッチP1の半分だけシフトした関係にあるが、それ以外では、略対称に形成されるので、以下においてはノズル列Naに着目してアクチュエーター基板40の構造を説明することにする。

【0023】

流路基板42は、インクの流路を形成する平板材であり、開口部422と供給流路424と連通流路426とが形成される。供給流路424および連通流路426は、ノズル毎に形成され、開口部422は、複数のノズルにわたって連続するように形成されるとともに、対応する色のインクが供給される構造となっている。この開口部422は、液体貯留室Srとして機能し、当該液体貯留室Srの底面は、例えばノズル板41によって構成される。具体的には、流路基板42における開口部422と各供給流路424と連通流路426とを閉塞するように流路基板42の底面に固定される。

【0024】

圧力室基板44のうち流路基板42とは反対側の表面に振動板46が設置される。振動板46は、弹性的に振動可能な平板状の部材であり、例えば酸化シリコン等の弹性材料で形成された弹性膜と、酸化ジルコニア等の絶縁材料で形成された絶縁膜との積層で構成される。振動板46と流路基板42とは、圧力室基板44の各開口部422の内側で互いに間隔をあけて対向する。各開口部422の内側で流路基板42と振動板46とに挟まれた空間は、インクに圧力を付与するキャビティ442として機能する。各キャビティ442は、流路基板42の連通流路426を介してノズルNに連通する。

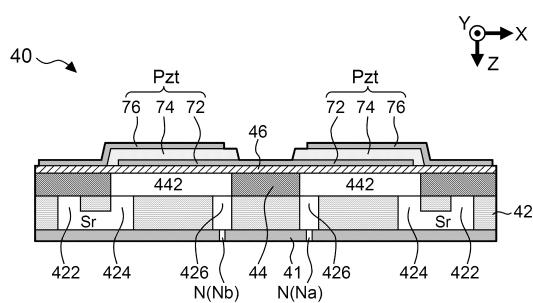

振動板46のうち圧力室基板44とは反対側の表面には、ノズルN(キャビティ442)毎に圧電素子Pztが形成される。

【0025】

圧電素子Pztは、振動板46の面上に形成された複数の圧電素子Pztにわたって共通の駆動電極72と、当該駆動電極72の面上に形成された圧電体74と、当該圧電体74の面上に圧電素子Pzt毎に形成された個別の駆動電極76とを包含する。このような構成において、駆動電極72、76によって圧電体74を挟んで対向する領域が圧電素子Pztとして機能する。

【0026】

圧電体74は、例えば加熱処理(焼成)を含む工程で形成される。具体的には、複数の駆動電極72が形成された振動板46の表面に塗布された圧電材料を、焼成炉内での加熱処理により焼成してから圧電素子Pzt毎に成形(例えばプラズマを利用したミーリング)することで圧電体74が形成される。

【0027】

なお、ノズル列Nbに対応する圧電素子Pztも同様に、駆動電極72と、圧電体74と

10

20

30

40

50

、駆動電極 7 6 とを包含した構成である。

また、この例では、圧電体 7 4 に対し、共通の駆動電極 7 2 を下層とし、個別の駆動電極 7 6 を上層としたが、逆に駆動電極 7 2 を上層とし、駆動電極 7 6 を下層とする構成としても良い。

なお、アクチュエーター基板 4 0 については、駆動 I C を直接実装した構成でも良い。

#### 【0028】

後述するように、圧電素子 Pzt の一端である駆動電極 7 6 には、吐出すべきインク量に応じた駆動信号の電圧 Vout が個別に印加される一方、圧電素子 Pzt の他端である駆動電極 7 2 には、電圧 VBS の保持信号が共通に印加される。

このため、圧電素子 Pzt は、駆動電極 7 2 、 7 6 に印加された電圧に応じて、上または下方向に変位する。詳細には、駆動電極 7 6 を介して印加される駆動信号の電圧 Vout が低くなると、圧電素子 Pzt における中央部分が両端部分に対して上方向に撓む一方、当該電圧 Vout が高くなると、下方向に撓む構成となっている。

ここで、上方向に撓めば、キャビティ 4 4 2 の内部容積が拡大（圧力が減少）するので、インクが液体貯留室 S r から引き込まれる一方、下方向に撓めば、キャビティ 4 4 2 の内部容積が縮小（圧力が増加）するので、縮小の程度によっては、インク滴がノズル N から吐出される。このように、圧電素子 Pzt に適切な駆動信号が印加されると、当該圧電素子 Pzt の変位によって、インクがノズル N から吐出される。このため、少なくとも圧電素子 Pzt 、キャビティ 4 4 2 、ノズル N によってインクを吐出する吐出部が構成されることになる。

#### 【0029】

次に、印刷装置 1 の電気的な構成について説明する。

#### 【0030】

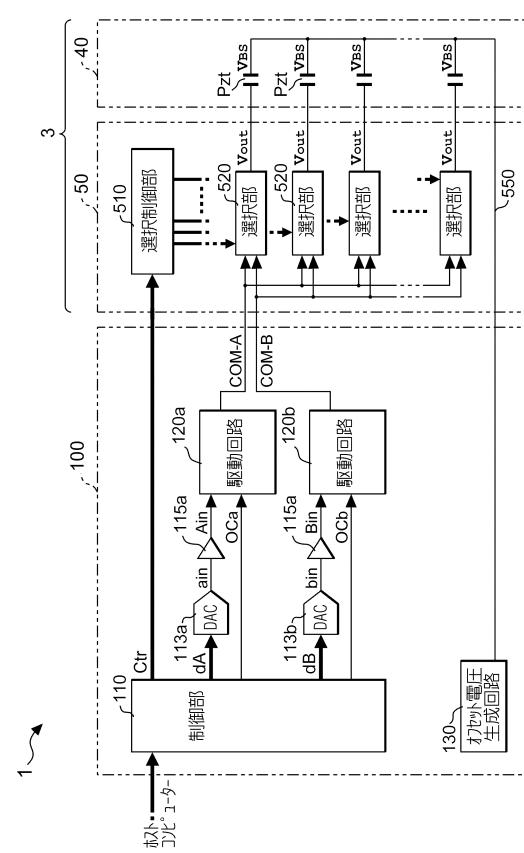

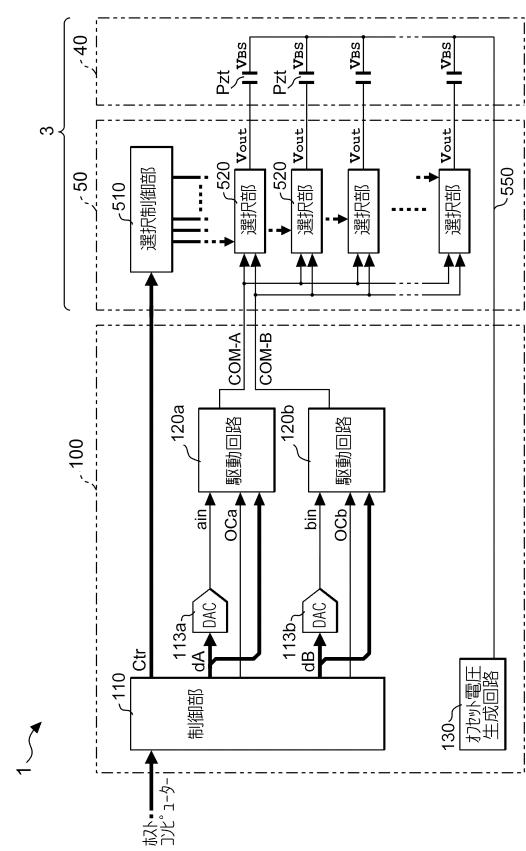

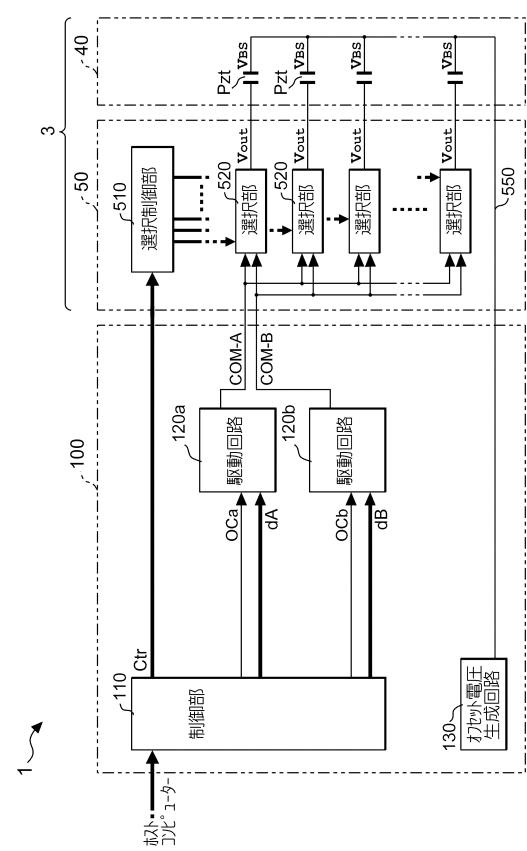

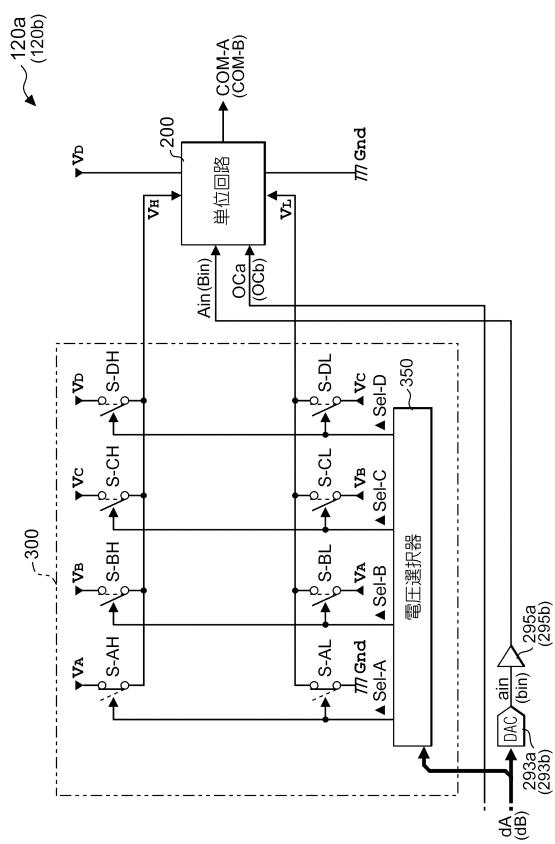

図 4 は、印刷装置 1 の電気的な構成を示すブロック図である。

この図に示されるように、印刷装置 1 は、メイン基板 1 0 0 にヘッドユニット 3 が接続された構成となっている。ヘッドユニット 3 は、アクチュエーター基板 4 0 と、駆動 I C 5 0 とに大別される。

メイン基板 1 0 0 は、駆動 I C 5 0 に、制御信号 Ctr や、駆動信号 COM - A 、 COM - B を供給し、アクチュエーター基板 4 0 に、電圧 VBS （オフセット電圧）の保持信号を、配線 5 5 0 を介して供給する。

なお、印刷装置 1 では、4 個のヘッドユニット 3 が設けられ、メイン基板 1 0 0 が、4 個のヘッドユニット 3 をそれぞれ独立に制御する。4 個のヘッドユニット 3 では、吐出すインクの色以外において異なることがないので、以下においては便宜的に1 個のヘッドユニット 3 について代表して説明することにする。

#### 【0031】

図 4 に示されるように、メイン基板 1 0 0 は、制御部 1 1 0 、 D / A 変換器（ D A C 、 Digital Analog Converter ） 1 1 3 a 、 1 1 3 b 、電圧増幅器 1 1 5 a 、 1 1 5 b 、駆動回路 1 2 0 a 、 1 2 0 b 、および、オフセット電圧生成回路 1 3 0 を含む。

このうち、制御部 1 1 0 は、 C P U や、 R A M 、 R O M などを有する一種のマイクロコンピューターであり、印刷対象となる画像データがホストコンピューター等から供給されたときに、所定のプログラムを実行して各部を制御するための各種の制御信号等を出力する。

#### 【0032】

具体的には、制御部 1 1 0 は、第 1 に、 D A C 1 1 3 a および駆動回路 1 2 0 a にデジタルのデータ d A を繰り返して供給し、 D A C 1 1 3 b および駆動回路 1 2 0 b にデジタルのデータ d B を同じく繰り返して供給する。ここで、データ d A は、ヘッドユニット 3 に供給する駆動信号 COM - A の波形を規定し、データ d B は、駆動信号 COM - B の波形を規定する。

#### 【0033】

D A C 1 1 3 a は、デジタルのデータ d A をアナログの信号 a in に変換する。電圧増幅

10

20

30

40

50

器 115a は、信号 a in の電圧を例えば 10 倍に増幅し、信号 A in として駆動回路 120a に供給する。同様に、D A C 113b は、デジタルのデータ d B をアナログの信号 b in に変換し、電圧増幅器 115b は、信号 b in の電圧を例えば 10 倍に増幅し、信号 B in として駆動回路 120b に供給する。

【0034】

駆動回路 120a は、詳細については後述するが、信号 A in を、容量性負荷である圧電素子 Pzt に対し、駆動能力を高めて（低インピーダンスに変換して）駆動信号 C O M - A として出力する。同様に、駆動回路 120b は、信号 B in を、駆動能力を高めて駆動信号 C O M - B として出力する。

なお、駆動信号 C O M - A、C O M - B（アナログ変換後の信号 a in、b in、インピーダンス変換前の信号 A in、B in）については、それぞれ後述するように台形波形である。

【0035】

D A C 113a（113b）により変換された信号 a in（b in）は例えば電圧 0 ~ 4 V 程度で比較的小さく振幅するのに対し、駆動信号 C O M - A（C O M - B）の電圧は 0 ~ 40 V 程度で比較的大きく振幅する。このため、D A C 113a（113b）により変換された信号 a in（b in）の電圧を電圧増幅器 115a（115b）が増幅し、当該電圧増幅した信号 A in（B in）を、駆動回路 120a（120b）がインピーダンス変換する構成となっている。

【0036】

第 2 に、制御部 110 は、移動機構 6 および搬送機構 8 に対する制御に同期して、ヘッドユニット 3 に各種の制御信号 C tr を供給する。なお、ヘッドユニット 3 に供給される制御信号 C tr には、ノズル N から吐出させるインクの量を規定する印刷データ（吐出制御信号）、当該印刷データの転送に用いるクロック信号、印刷周期等を規定するタイミング信号等が含まれる。

なお、制御部 110 は、移動機構 6 および搬送機構 8 を制御するが、このような構成については既知であるので省略する。

【0037】

メイン基板 100 におけるオフセット電圧生成回路 130 は、電圧 V<sub>B\_S</sub> の保持信号を生成して、配線 550 を介してアクチュエーター基板 40 における複数の圧電素子 Pzt の他端にわたって共通に印加する。電圧 V<sub>B\_S</sub> の保持信号は、複数の圧電素子 Pzt の他端を、それぞれ一定の状態に保つためのものである。

【0038】

一方、ヘッドユニット 3 において、駆動 I C 50 は、選択制御部 510 と、圧電素子 Pzt に一対一に対応した選択部 520 と、を有する。このうち、選択制御部 510 は、選択部 520 の各々における選択をそれぞれ制御する。詳細には、選択制御部 510 は、制御部 110 からクロック信号に同期して供給される印刷データを、ヘッドユニット 3 のノズル（圧電素子 Pzt）の数個分、一旦蓄積するとともに、各選択部 520 に対し、印刷データにしたがって駆動信号 C O M - A、C O M - B の選択を、タイミング信号で規定される印刷周期の開始タイミングで指示する。

各選択部 520 は、選択制御部 510 による指示にしたがって、駆動信号 C O M - A、C O M - B のいずれかを選択し（または、いずれも選択せずに）、電圧 V<sub>out</sub> の駆動信号として、対応する圧電素子 Pzt の一端に印加する。

アクチュエーター基板 40 には、上述したようにノズル N 毎に圧電素子 Pzt が 1 個ずつ設けられる。圧電素子 Pzt の各々における他端は共通接続されて、当該他端には配線 550 を介してオフセット電圧生成回路 130 による電圧 V<sub>B\_S</sub> が印加される。

【0039】

本実施形態において、1 つのドットについては、1 つのノズル N からインクを最多で 2 回吐出させることで、大ドット、中ドット、小ドットおよび非記録の 4 階調を表現させる。この 4 階調を表現するために、本実施形態では、2 種類の駆動信号 C O M - A、C O M - B を用意するとともに、各々の 1 周期にそれぞれ前半パターンと後半パターンとを持た

10

20

30

40

50

せている。そして、1周期のうち、前半・後半において駆動信号COM-A、COM-Bを、表現すべき階調に応じた選択して（または選択しないで）、圧電素子Pztに供給する構成となっている。

そこで先に、駆動信号COM-A、COM-Bについて説明し、この後、駆動信号COM-A、COM-Bを選択するための選択制御部510および選択部520の詳細な構成について説明する。

#### 【0040】

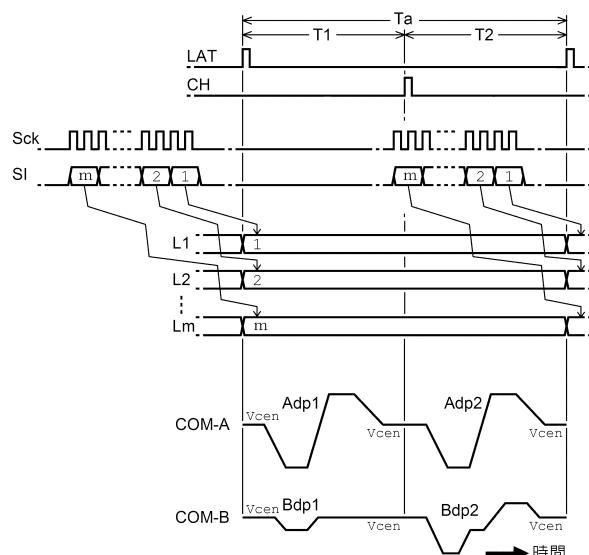

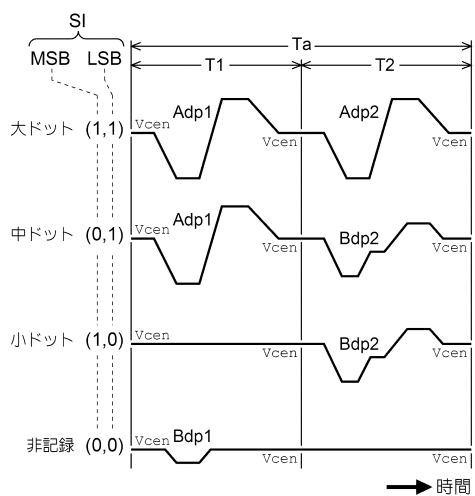

図5は、駆動信号COM-A、COM-Bの波形等を示す図である。

図に示されるように、駆動信号COM-Aは、印刷周期Taのうち、制御信号LATが出力されて（立ち上がって）から制御信号CHが出力されるまでの期間T1に配置された台形波形Adp1と、印刷周期Taのうち、制御信号CHが出力されてから次の制御信号LATが出力されるまでの期間T2に配置された台形波形Adp2とを繰り返す波形となっている。

#### 【0041】

本実施形態において台形波形Adp1、Adp2とは、互いにほぼ同一の波形であり、仮にそれぞれが圧電素子Pztの一端である駆動電極76に供給されたとしたならば、当該圧電素子Pztに対応するノズルNから所定量、具体的には中程度の量のインクをそれぞれ吐出させる波形である。

#### 【0042】

駆動信号COM-Bは、期間T1に配置された台形波形Bdp1と、期間T2に配置された台形波形Bdp2とを繰り返す波形となっている。本実施形態において台形波形Bdp1、Bdp2とは、互いに異なる波形である。このうち、台形波形Bdp1は、ノズルN付近のインクを微振動させてインクの粘度の増大を防止するための波形である。このため、仮に台形波形Bdp1が圧電素子Pztの一端に供給されたとしても、当該圧電素子Pztに対応するノズルNからインク滴が吐出されない。また、台形波形Bdp2は、台形波形Adp1(Adp2)とは異なる波形となっている。仮に台形波形Bdp2が圧電素子Pztの一端に供給されたとしたならば、当該圧電素子Pztに対応するノズルNから上記所定量よりも少ない量のインクを吐出させる波形である。

#### 【0043】

台形波形Adp1、Adp2、Bdp1、Bdp2の開始タイミングでの電圧と、終了タイミングでの電圧とは、いずれも電圧Vcenで共通である。すなわち、台形波形Adp1、Adp2、Bdp1、Bdp2は、それぞれ電圧Vcenで開始し、電圧Vcenで終了する波形となっている。

#### 【0044】

なお、駆動回路120a(120b)は、本例では信号Ain(Bin)をインピーダンス変換するものであるから、入力である信号Ain(Bin)の波形は、多少の誤差を伴うものの、駆動信号COM-A(COM-B)の波形そのままである。一方で、信号Ain(Bin)は、信号ain(bin)の電圧を10倍に増幅したものであるから、信号ain(bin)の波形は、信号Ain(Bin)の電圧を1/10倍とした関係にある。信号ain(bin)は、データdA(dB)をアナログ変換したものであるので、駆動信号COM-A(COM-B)の電圧波形は、制御部110によって規定されることになる。

#### 【0045】

制御部110は、駆動信号COM-Aの台形波形に対して、次のような論理レベルとなる信号OCA(選択信号)を駆動回路120aに出力する。詳細には、制御部110は、信号OCAを、駆動信号COM-A(信号ain)の電圧を低下させる期間と駆動信号COM-Aを閾値Vthよりも低い電圧で一定にさせる期間とにわたってHレベルとし、それ以外の駆動信号COM-Aの電圧を上昇させる期間と駆動信号COM-Aを閾値Vth以上の電圧で一定にさせる期間とにわたってLレベルとする。

本例では、駆動信号COM-A(信号ain)の電圧の最高値をmaxとし、最低値をminとしたときに、便宜的にmax > Vth > Vcen > minとして説明する。なお、max > Vcen >

10

20

30

40

50

$V_{th} > min$  としても良い。

【0046】

同様に、制御部 110 は、駆動信号 COM-B の台形波形に対して、次のような論理レベルとなる信号 OCB を駆動回路 120b に出力する。詳細には、制御部 110 は、信号 OCB を、駆動信号 COM-B (信号 Bin) の電圧を低下させる期間と、駆動信号 COM-B を閾値電圧  $V_{th}$  よりも低い電圧で一定にさせる期間とにわたって H レベルとし、それ以外の駆動信号 COM-B の電圧を上昇させる期間と駆動信号 COM-B を閾値電圧  $V_{th}$  以上の電圧で一定にさせる期間とにわたって L レベルとする。

【0047】

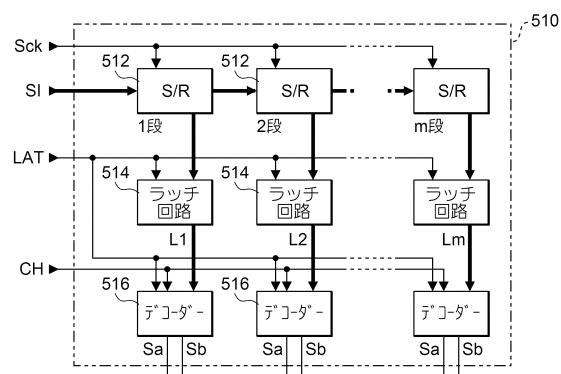

図 6 は、図 4 における選択制御部 510 の構成を示す図である。

10

この図に示されるように、選択制御部 510 には、クロック信号 Sck、印刷データ SI、制御信号 LAT、CH が供給される。選択制御部 510 では、シフトレジスタ (S/R) 512 とラッチ回路 514 とデコーダー 516 との組が、圧電素子 Pzt (ノズル N) のそれぞれに対応して設けられている。

【0048】

印刷データ SI は、印刷周期  $T_a$  にわたって、着目しているヘッドユニット 3 において、すべてのノズル N によって形成すべきドットを規定するデータである。本実施形態では、非記録、小ドット、中ドットおよび大ドットの 4 階調を表現するために、ノズル 1 個分の印刷データは、上位ビット (MSB) および下位ビット (LSB) の 2 ビットで構成される。

20

印刷データ SI は、クロック信号 Sck に同期してノズル N (圧電素子 Pzt) 毎に、媒体 P の搬送に合わせて供給される。当該印刷データ SI を、ノズル N に対して 2 ビット分、一旦保持するための構成がシフトレジスタ 512 である。

詳細には、m 個の圧電素子 Pzt (ノズル) の各々に対応した計 m 段のシフトレジスタ 512 が継続接続されるとともに、図において左端に位置する 1 段のシフトレジスタ 512 に供給された印刷データ SI が、クロック信号 Sck にしたがって順次後段 (下流側) に転送される構成となっている。

なお、図では、シフトレジスタ 512 を区別するために、印刷データ SI が供給される上流側から順番に 1 段、2 段、...、m 段と表記している。

【0049】

30

ラッチ回路 514 は、シフトレジスタ 512 で保持された印刷データ SI を制御信号 LAT の立ち上がりでラッチする。

デコーダー 516 は、ラッチ回路 514 によってラッチされた 2 ビットの印刷データ SI をデコードして、制御信号 LAT と制御信号 CH とで規定される期間  $T_1$ 、 $T_2$  ごとに、選択信号 Sa、Sb を出力して、選択部 520 での選択を規定する。

【0050】

図 7 は、デコーダー 516 におけるデコード内容を示す図である。

この図において、ラッチされた 2 ビットの印刷データ SI については (MSB、LSB) と表記している。デコーダー 516 は、例えばラッチされた印刷データ SI が (0, 1) であれば、選択信号 Sa、Sb の論理レベルを、期間  $T_1$  ではそれぞれ H、L レベルで、期間  $T_2$  ではそれぞれ L、H レベルで、出力するということを意味している。

40

なお、選択信号 Sa、Sb の論理レベルについては、クロック信号 Sck、印刷データ SI、制御信号 LAT、CH の論理レベルよりも、レベルシフター (図示省略) によって、高振幅論理にレベルシフトされる。

【0051】

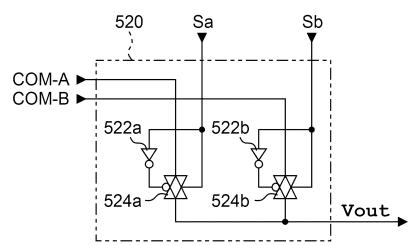

図 8 は、図 4 における選択部 520 の構成を示す図である。

この図に示されるように、選択部 520 は、インバーター (NOT 回路) 522a、522b と、トランスファーゲート 524a、524b とを有する。

デコーダー 516 からの選択信号 Sa は、トランスファーゲート 524a において丸印が付されていない正制御端に供給される一方で、インバーター 522a によって論理反転

50

されて、トランസファーゲート 524aにおいて丸印が付された負制御端に供給される。同様に、選択信号 Sb は、トランസファーゲート 524b の正制御端に供給される一方で、インバーター 522b によって論理反転されて、トランസファーゲート 524b の負制御端に供給される。

トランസファーゲート 524a の入力端には、駆動信号 COM-A が供給され、トランസファーゲート 524b の入力端には、駆動信号 COM-B が供給される。トランസファーゲート 524a、524b の出力端同士は、共通接続されるとともに、対応する圧電素子 Pzt の一端に接続される。

トランസファーゲート 524a は、選択信号 Sa が H レベルであれば、入力端および出力端の間を導通（オン）させ、選択信号 Sa が L レベルであれば、入力端と出力端との間を非導通（オフ）させる。トランsusファーゲート 524b についても同様に選択信号 Sb に応じて、入力端および出力端の間をオンオフさせる。

10

#### 【0052】

図 5 に示されるように、印刷データ SI は、ノズル毎に、クロック信号 Sck に同期して供給されて、ノズルに対応するシフトレジスタ 512 において順次転送される。そして、クロック信号 Sck の供給が停止すると、シフトレジスタ 512 のそれぞれには、各ノズルに対応した印刷データ SI が保持された状態になる。

ここで、制御信号 LAT が立ち上がると、ラッチ回路 514 のそれぞれは、シフトレジスタ 512 に保持された印刷データ SI を一齊にラッチする。図 5 において、L1、L2、…、Lm 内の数字は、1 段、2 段、…、m 段のシフトレジスタ 512 に対応するラッチ回路 514 によってラッチされた印刷データ SI を示している。

20

#### 【0053】

デコーダー 516 は、ラッチされた印刷データ SI で規定されるドットのサイズに応じて、期間 T1、T2 のそれれにおいて、選択信号 Sa、Sb の論理レベルを図 7 に示されるような内容で出力する。

すなわち、第 1 に、デコーダー 516 は、当該印刷データ SI が (1, 1) であって、大ドットのサイズを規定する場合、選択信号 Sa、Sb を、期間 T1 において H、L レベルとし、期間 T2 においても H、L レベルとする。第 2 に、デコーダー 516 は、当該印刷データ SI が (0, 1) であって、中ドットのサイズを規定する場合、選択信号 Sa、Sb を、期間 T1 において H、L レベルとし、期間 T2 において L、H レベルとする。第 3 に、デコーダー 516 は、当該印刷データ SI が (1, 0) であって、小ドットのサイズを規定する場合、選択信号 Sa、Sb を、期間 T1 において L、L レベルとし、期間 T2 において L、H レベルとする。第 4 に、デコーダー 516 は、当該印刷データ SI が (0, 0) であって、非記録を規定する場合、選択信号 Sa、Sb を、期間 T1 において L、H レベルとし、期間 T2 において L、L レベルとする。

30

#### 【0054】

図 9 は、印刷データ SI に応じて選択されて、圧電素子 Pzt の一端に供給される駆動信号の電圧波形を示す図である。

印刷データ SI が (1, 1) であるとき、選択信号 Sa、Sb は、期間 T1 において H、L レベルとなるので、トランsusファーゲート 524a がオンし、トランsusファーゲート 524b がオフする。このため、期間 T1 において駆動信号 COM-A の台形波形 Adp1 が選択される。選択信号 Sa、Sb は期間 T2 においても H、L レベルとなるので、選択部 520 は、駆動信号 COM-A の台形波形 Adp2 を選択する。

40

このように期間 T1 において台形波形 Adp1 が選択され、期間 T2 において台形波形 Adp2 が選択されて、駆動信号として圧電素子 Pzt の一端に供給されると、当該圧電素子 Pzt に対応したノズル N から、中程度の量のインクが 2 回にわけて吐出される。このため、媒体 P にはそれぞれのインクが着弾し合体して、結果的に、印刷データ SI で規定される通りの大ドットが形成されることになる。

#### 【0055】

印刷データ SI が (0, 1) であるとき、選択信号 Sa、Sb は、期間 T1 において H

50

、Lレベルとなるので、トランスマルチゲート524aがオンし、トランスマルチゲート524bはオフする。このため、期間T1において駆動信号COM-Aの台形波形Adp1が選択される。次に、選択信号Sa、Sbは期間T2においてL、Hレベルとなるので、駆動信号COM-Bの台形波形Bdp2が選択される。

したがって、ノズルから、中程度および小程度の量のインクが2回にわけて吐出される。このため、媒体Pには、それぞれのインクが着弾して合体して、結果的に、印刷データSIで規定された通りの中ドットが形成されることになる。

#### 【0056】

印刷データSIが(1、0)であるとき、選択信号Sa、Sbは、期間T1においてともにLレベルとなるので、トランスマルチゲート524a、524bがオフする。このため、期間T1において台形波形Adp1、Bdp1のいずれも選択されない。トランスマルチゲート524a、524bがともにオフする場合、当該トランスマルチゲート524a、524bの出力端同士の接続点から圧電素子Pztの一端までの経路は、電気的にどの部分にも接続されないハイ・インピーダンス状態になる。ただし、圧電素子Pztの両端では、自己が有する容量性によって、トランスマルチゲートがオフする直前の電圧(Vcen-V<sub>BS</sub>)が保持される。

次に、選択信号Sa、Sbは期間T2においてL、Hレベルとなるので、駆動信号COM-Bの台形波形Bdp2が選択される。このため、ノズルNから、期間T2においてのみ小程度の量のインクが吐出されるので、媒体Pには、印刷データSIで規定された通りの小ドットが形成されることになる。

#### 【0057】

印刷データSIが(0、0)であるとき、選択信号Sa、Sbは、期間T1においてL、Hレベルとなるので、トランスマルチゲート524aがオフし、トランスマルチゲート524bがオンする。このため、期間T1において駆動信号COM-Bの台形波形Bdp1が選択される。次に、選択信号Sa、Sbは期間T2においてともにLレベルとなるので、台形波形Adp2、Bdp2のいずれも選択されない。

このため、期間T1においてノズルN付近のインクが微振動するのみであり、インクは吐出されないので、結果的に、ドットが形成されない、すなわち、印刷データSIで規定された通りの非記録になる。

#### 【0058】

このように、選択部520は、選択制御部510による指示にしたがって駆動信号COM-A、COM-Bを選択し(または選択しない)、圧電素子Pztの一端に印加する。このため、各圧電素子Pztは、印刷データSIで規定されるドットのサイズに応じて駆動されることになる。

なお、図5に示した駆動信号COM-A、COM-Bはあくまでも一例である。実際には、媒体Pの性質や搬送速度などに応じて、予め用意された様々な波形の組み合わせが用いられる。

また、ここでは、圧電素子Pztが、電圧の低下に伴って上方向に撓む例で説明したが、駆動電極72、76に印加する電圧を逆転させると、圧電素子Pztは、電圧の低下に伴って下方向に撓むことになる。このため、圧電素子Pztが、電圧の低下に伴って下方向に撓む構成では、図に例示した駆動信号COM-A、COM-Bが、電圧Vcenを基準に反転した波形となる。

#### 【0059】

次に、メイン基板100における駆動回路120a、120bについて説明する。

なお、駆動回路の符号については、駆動信号COM-Aを出力する側を120aで、駆動信号COM-Bを出力する側を120bで、それぞれ統一するが、後述するように、いくつかの態様が存在するので、印刷装置と同様に、区別するために、駆動回路(その1)、駆動回路(その2)というように符号の代わりに括弧書を付与する場合がある。

#### 【0060】

そこでまず、駆動回路(その1)について、駆動信号COM-Aを出力する側の駆動回

10

20

30

40

50

路 1 2 0 a を例にとって説明する。

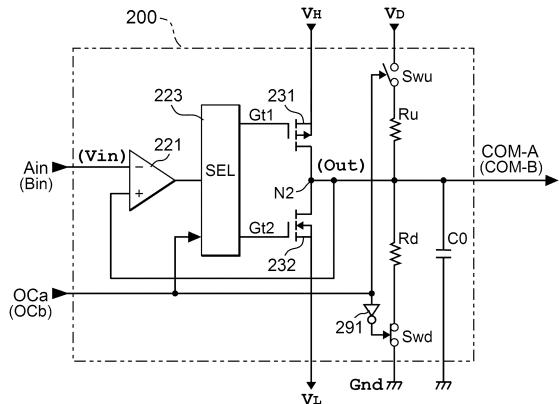

【 0 0 6 1 】

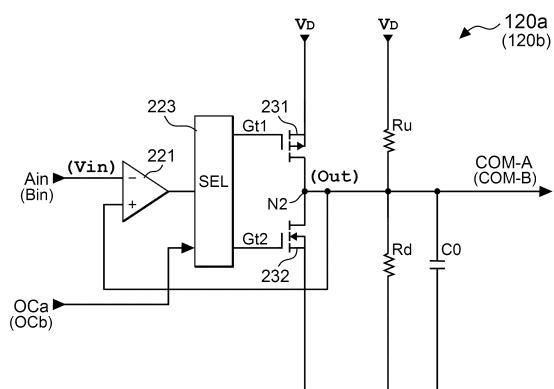

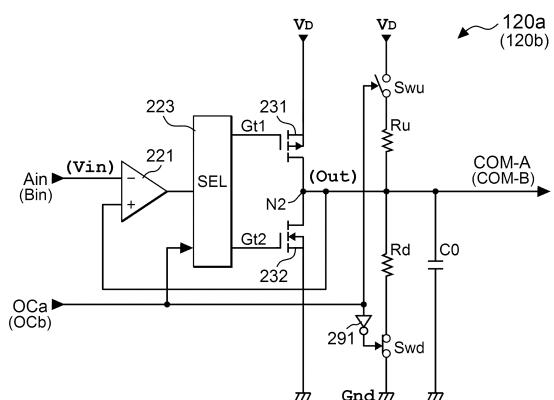

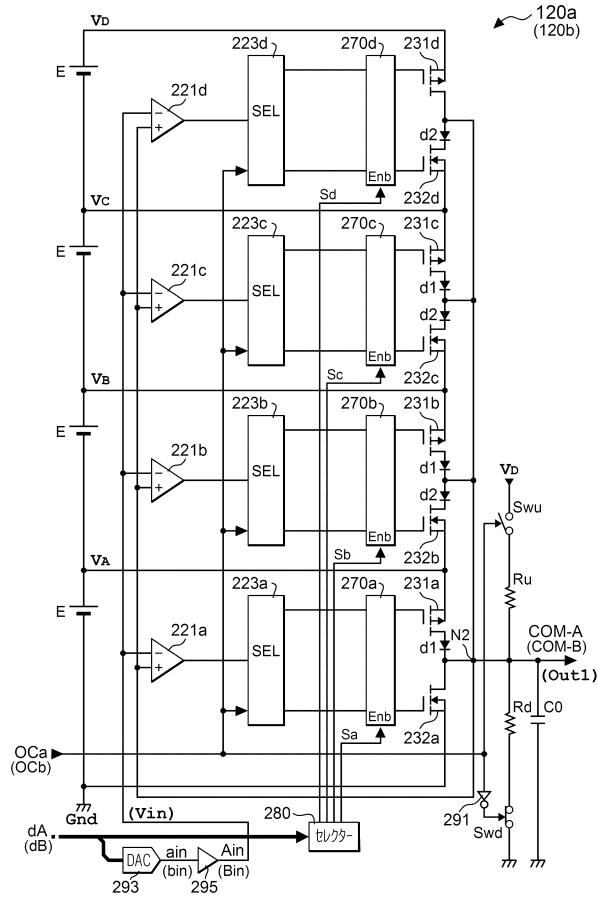

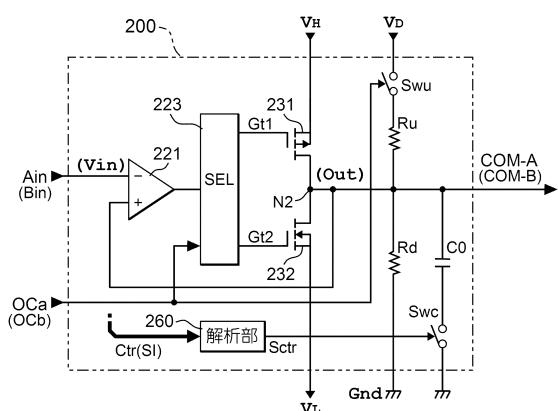

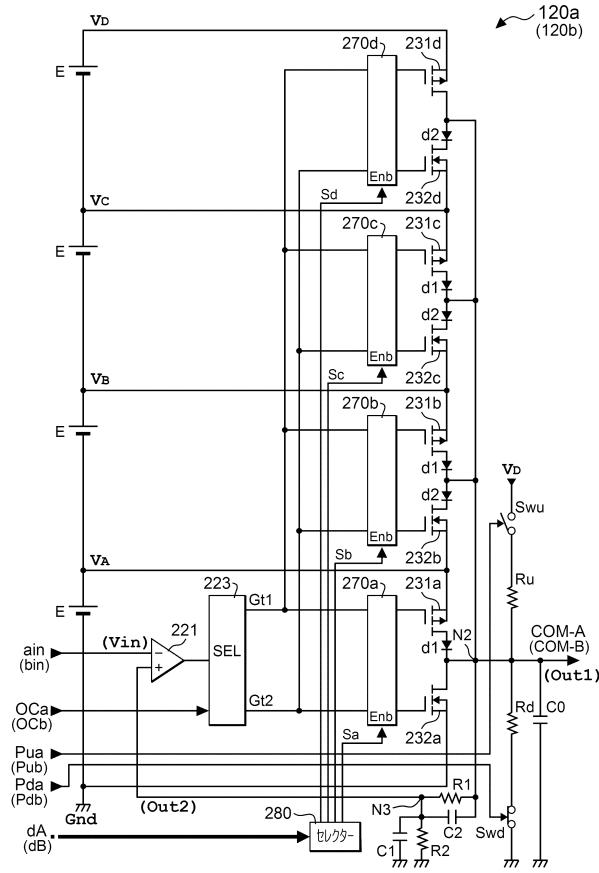

図 1 0 は、駆動回路 ( その 1 ) を示す図である。この図に示されるように、駆動回路 1 2 0 a は、差動増幅器 2 2 1 と、セレクター 2 2 3 と、トランジスター対と、抵抗素子 R u 、 R d と、コンデンサー C 0 とを含む。

【 0 0 6 2 】

差動増幅器 2 2 1 にあっては、負入力端 ( - ) に信号 A in が供給される一方、正入力端 ( + ) には出力である駆動信号 C O M - A が帰還されている。このため、差動増幅器 2 2 1 は、正入力端 ( + ) の電圧から負入力端 ( - ) の電圧を減算した差電圧、つまり、出力である駆動信号 C O M - A の電圧 Out から、入力である大振幅の信号 A in ( 元駆動信号 ) の電圧 V in を減算した差電圧を増幅して出力することになる。

【 0 0 6 3 】

ただし、差動増幅器 2 2 1 は、特に図示しないが例えば電源の高位側を電圧 V D とし、低位側をグランド G nd としている。このため、出力電圧は、グランド G nd から電圧 V D までの範囲となる。

なお、差動増幅器 2 2 1 の出力信号は、後述するスイッチング動作のための信号として用いられる場合もあれば、リニア動作のための信号として用いられる場合もある。スイッチング動作のための信号として用いられる場合、H レベルは電圧 V D であり、L レベルは電圧ゼロのグランド G nd である。

また、差動増幅器 2 2 1 による出力信号は、結局のところ、後述するようにトランジスター 2 3 1 、 2 3 2 のスイッチング動作およびリニア動作を制御するので、トランジスターの制御信号と言うことができる。また、後述するように、駆動信号を降圧して帰還する一方、元駆動信号を電圧増幅して駆動信号として出力する場合もあるので、駆動信号に基づく信号が差動増幅器 2 2 1 に帰還される、と言っても良い。

【 0 0 6 4 】

セレクター ( 選択部 ) 2 2 3 は、信号 O C a が L レベルであれば、信号 G t1 として差動増幅器 2 2 1 の出力信号を選択し、トランジスター 2 3 1 のゲート端子に供給するとともに、信号 G t2 として L レベルを選択し、トランジスター 2 3 2 のゲート端子に供給する。一方、セレクター 2 2 3 は、信号 O C a が H レベルであれば、信号 G t1 として H レベルを選択し、トランジスター 2 3 1 のゲート端子に供給するとともに、信号 G t2 として差動増幅器 2 2 1 の出力信号を選択し、トランジスター 2 3 2 のゲート端子に供給する。

換言すれば、セレクター 2 2 3 は、信号 O C a が L レベルであれば、トランジスター 2 3 1 を選択して、差動増幅器 2 2 1 の出力信号である差信号を当該トランジスター 2 3 1 のゲート端子に供給し、信号 O C a が H レベルであれば、トランジスター 2 3 2 を選択して、上記差信号を当該トランジスター 2 3 2 のゲート端子に供給する一方、選択しなかったトランジスターのゲート端子には、後述するように当該トランジスターをオフにさせる信号を供給する構成となっている。

【 0 0 6 5 】

トランジスター対は、トランジスター 2 3 1 、 2 3 2 によって構成される。このうち、高位側のトランジスター 2 3 1 ( ハイサイドトランジスター ) は、例えば P チャネル型の電界効果トランジスターであり、ソース端子には電源の高位側電圧 V D が印加されている。低位側のトランジスター 2 3 2 ( ローサイドトランジスター ) は、例えば N チャネル型の電界効果トランジスターであり、ソース端子が電源の低位側となるグランド G nd に接地されている。

トランジスター 2 3 1 、 2 3 2 のドレイン端子同士は、互いに接続されて、駆動回路 1 2 0 a の出力端であるノード N 2 となっている。すなわち、ノード N 2 から駆動信号 C O M - A が出力される構成となっている。

なお、駆動回路 1 2 0 a の出力であるノード N 2 の電圧を Out と表記し、入力である信号 A in の電圧を V in と表記する。

【 0 0 6 6 】

10

20

30

40

50

ノードN 2は、差動増幅器221の正入力端(+)に接続されるとともに、抵抗素子R<sub>u</sub>(第1抵抗素子)を介して電圧V<sub>D</sub>にプルアップされる一方で、抵抗素子R<sub>d</sub>(第2抵抗素子)を介してグランドにプルダウンされている。また、コンデンサーC0(出力コンデンサー)は、異常発振の防止等のために設けられ、一端がノードN 2に接続され、他端が一定電位の、例えばグランドGndに接地されている。

#### 【0067】

なお、差動増幅器221、セレクター223は、トランジスター231、232の制御信号を生成して出力することになるので、両者を制御信号生成部として概念することができる。また、トランジスター231、232、抵抗素子R<sub>u</sub>、R<sub>d</sub>を1つのブロックとして考えてみた場合に、上記制御信号に基づいて駆動信号がノードN 2から出力されることになるので、当該ブロックを増幅部として概念することができる。10

#### 【0068】

ここでは、駆動信号COM-Aを出力する駆動回路120aについて説明したが、駆動信号COM-Bを出力する駆動回路120bの構成については、駆動回路120aと同一であって、入出力信号だけが異なる。すなわち、駆動回路120bは、図10の括弧書きで示されるように、差動増幅器221の負入力端(-)に信号Binが供給され、セレクター223に信号OCbが供給される一方、ノードN 2から駆動信号COM-Bが出力されることになる。

#### 【0069】

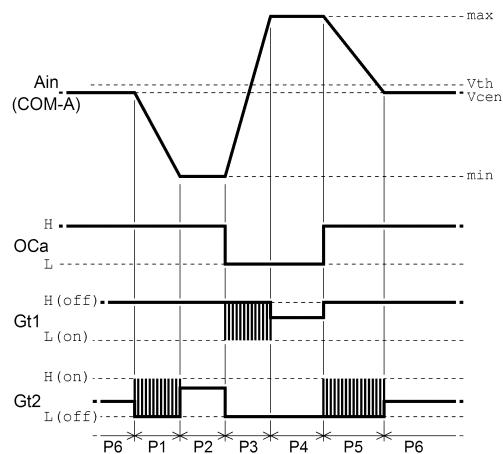

次に、駆動回路120a、120bの動作について、駆動信号COM-Aを出力する駆動回路120aを例にとって説明する。20

#### 【0070】

図11は、駆動回路120aの動作を説明するための図である。

この図において、信号Ainは、駆動信号COM-Aのインピーダンス変換前の信号であるので、当該駆動信号COM-Aとほぼ同波形である。また、上述したように、駆動信号COM-Aは、印刷周期Taにおいて2つの同じ台形波形Adp1、Adp2が繰り返された波形であるので、信号Ainも同様な繰り返し波形である。

#### 【0071】

なお、図11は、このような繰り返し波形のうち、1つの台形波形を示している。また、この図において、期間P1は、信号Ainの電圧Vinが電圧Vcenから最低値minまで低下する期間であり、当該期間P1に続く期間P2は、電圧Vinが最低値minで一定となる期間であり、当該期間P2に続く期間P3は、電圧Vinが最低値minから最高値maxまで上昇する期間であり、当該期間P3に続く期間P4は、電圧Vinが最高値maxで一定となる期間であり、当該期間P4に続く期間P5は、電圧Vinが最高値maxから電圧Vcenまで低下する期間である。30

図11における電圧波形のそれぞれについて、説明の便宜上、電圧を示す縦スケールは必ずしも揃っていない。

#### 【0072】

まず、期間P1は、駆動信号COM-A(Ain)の電圧低下期間である。このため、期間P1では、信号OCaがHレベルであるので、セレクター223は、信号Gt1としてHレベルを選択し、信号Gt2として差動増幅器221の出力信号を選択する。40

期間P1では、信号Gt1がHレベルであるので、Pチャネル型のトランジスター231はオフする。

一方、当該期間P1では、まず信号Ainの電圧VinがノードN 2の電圧Outよりも先んじて低下する。逆にいえば、電圧Outは、電圧Vin以上となる。このため、信号Gt2として選択される差動増幅器221の出力信号の電圧は、両者の差電圧に応じて高くなり、ほぼHレベルに振れる。信号Gt2がHレベルになると、トランジスター232がオンするので、電圧Outが低下する。なお、電圧Outは、コンデンサーC0や容量性を有する圧電素子Pztなどにより、実際には、一気にグランドGndに低下することはなく、緩慢に低下する。50

電圧 Out が電圧 Vin よりも低くなると、信号 Gt2 が L レベルになり、トランジスター 232 がオフするが、電圧 Vin が低下しているので、再び電圧 Out が電圧 Vin 以上となる。このため、信号 Gt2 が H レベルとなって、トランジスター 232 が再びオンすることになる。

期間 P1 では、信号 Gt2 が H、L レベルで交互に切り替えられ、これにより、トランジスター 232 は、オンオフを繰り返す動作、すなわちスイッチング動作をすることになる。このスイッチング動作により、電圧 Out を電圧 Vin の低下に追従させる制御が実行されることになる。

#### 【0073】

次に、期間 P2 は、駆動信号 COM-A (Ain) が閾値電圧 Vth よりも低い電圧の最低値 min で一定となる期間である。このため、期間 P2 では、期間 P1 から引き続いて信号 OCa が H レベルであるので、セレクター 223 は、信号 Gt1 として H レベルを選択し、信号 Gt2 として差動増幅器 221 の出力信号を選択する。 10

前の期間 P1 では、電圧 Out が電圧 Vin に追従するように制御されるが、その制御内容は、上述したようにトランジスター 232 のスイッチング動作である。このため、期間 P2 の開始直後、すなわち電圧 Vin が最低値 min で一定に転じた直後では、電圧 Out が、電圧 Vin に一致していない場合がある。

#### 【0074】

この場合において、電圧 Out が電圧 Vin に対して高ければ、信号 Gt2 の電圧、すなわち差動増幅器 221 の出力電圧も高くなるので、トランジスター 232 のソース・ドレイン間の抵抗が小さくなり、ノード N2 の電圧 Out を低下させるように働く。一方、電圧 Out が電圧 Vin に対して低ければ、信号 Gt2 の電圧も低くなるので、トランジスター 232 のソース・ドレイン間の抵抗が大きくなり、電圧 Out を上昇させる方向に働く。 20

したがって、期間 P2 において、電圧 Out は、当該電圧 Out を低下させる方向と上昇させる方向とが均衡する地点、すなわち、電圧 Vin (最低値 min) に一致する地点で一定になる。このとき、トランジスター 232 は線形 (リニア) 動作となり、信号 Gt2 は、トランジスター 232 におけるソース・ドレイン間の抵抗、および、抵抗素子 Ru、Rd で定まる電圧 Out が電圧 Vin となるような電圧で一定となる。

なお、図 11 では、期間 P1 から期間 P2 にかけての信号 Gt2 の電圧変化については簡略化して、直ちに一定となった状態を示している。 30

#### 【0075】

期間 P3 は、駆動信号 COM-A (Ain) の電圧上昇期間である。このため、期間 P3 では、信号 OCa が L レベルになるので、セレクター 223 は、信号 Gt1 として差動増幅器 221 の出力信号を選択し、信号 Gt2 として L レベルを選択する。

期間 P3 では、信号 Gt2 が L レベルであるので、N チャネル型のトランジスター 232 はオフする。

一方、当該期間 P3 では、まず電圧 Vin が電圧 Out よりも先んじて上昇する。逆にいえば、電圧 Out は、電圧 Vin よりも低くなる。このため、信号 Gt1 として選択される差動増幅器 221 の出力信号の電圧は、両者の差電圧に応じて低くなり、ほぼ L レベルに振れる。信号 Gt1 が L レベルになると、トランジスター 231 がオンするので、電圧 Out が上昇する。なお、電圧 Out は、コンデンサー C0 や容量性を有する圧電素子 Pzt などにより、実際には、一気に電圧 VD に上昇することではなく、緩慢に上昇する。 40

電圧 Out が電圧 Vin 以上になると、信号 Gt2 が H レベルになり、トランジスター 231 がオフする。トランジスター 231 がオフすると、電圧 Out の上昇は停止するが、電圧 Vin が上昇しているので、再び電圧 Out が電圧 Vin よりも低くなる。このため、信号 Gt1 が L レベルとなって、トランジスター 231 が再びオンすることになる。

期間 P3 では、信号 Gt1 が H、L レベルで交互に切り替えられ、これにより、トランジスター 231 は、スイッチング動作をすることになる。このスイッチング動作により、電圧 Out を電圧 Vin の上昇に追従させる制御が実行されることになる。

#### 【0076】

10

20

30

40

50

期間 P 4 は、駆動信号 C O M - A ( A in ) が閾値電圧  $V_{th}$  以上の電圧で一定となる期間である。このため、期間 P 2 では、期間 P 3 から引き続いて信号 O C a が L レベルであるので、セレクター 2 2 3 は、信号 G t1 として差動増幅器 2 2 1 の出力信号を選択し、信号 G t2 として L レベルを選択する。

前の期間 P 3 では、電圧 Out が電圧 V in に追従するように制御されるが、その制御内容は、上述したようにトランジスター 2 3 1 によるスイッチング動作であるので、期間 P 4 において電圧 V in が最高値 max で一定に転じた直後では、電圧 Out が、信号 A in の電圧 V in に一致していない場合がある。

#### 【 0 0 7 7 】

この場合において、電圧 Out が電圧 V in に対して高ければ、信号 G t1 の電圧、すなわち差動増幅器 2 2 1 の出力電圧も高くなるので、トランジスター 2 3 1 のソース・ドレイン間の抵抗が大きくなり、ノード N 2 の電圧 Out を低下させるように働く。一方、電圧 Out が電圧 V in に対して低ければ、信号 G t1 の電圧も低くなるので、トランジスター 2 3 1 のソース・ドレイン間の抵抗が小さくなり、電圧 Out を上昇させる方向に働く。

したがって、期間 P 4 において、電圧 Out は、当該電圧 Out を低下させる方向と上昇させる方向とが均衡する地点、すなわち、電圧 V in ( 最高値 max ) に一致する地点で一定になる。このとき、トランジスター 2 3 2 はリニア動作となり、信号 G t2 は、トランジスター 2 3 2 におけるソース・ドレイン間の抵抗、および、抵抗素子  $R_u$ 、 $R_d$  で定まる電圧 Out が電圧 V in ( 最高値 max ) となるような電圧で一定となる。

なお、図 1 1 では、期間 P 3 から期間 P 4 にかけての信号 G t2 の電圧変化については簡略化して、直ちに一定となった状態を示している。

#### 【 0 0 7 8 】

期間 P 5 は、駆動信号 C O M - A ( A in ) の電圧低下期間である。このため、期間 P 5 は、期間 P 1 と同様な動作となる。すなわち、信号 G t2 が H、L レベルで交互に切り替えられ、これによりトランジスター 2 3 2 がスイッチング動作となり、ノード N 2 の電圧 Out を電圧 V in の電圧低下に追従させる制御が実行される。なお、期間 P 5 は、期間 P 4 との関係でいえば、信号 O C a が H レベルに切り替わるので、セレクター 2 2 3 は、信号 G t1 として H レベルを選択し、信号 G t2 として差動増幅器 2 2 1 の出力信号を選択する。

#### 【 0 0 7 9 】

期間 P 5 の後の期間 P 6 は、駆動信号 C O M - A ( A in ) が閾値電圧  $V_{th}$  よりも低い電圧  $V_{cen}$  で一定となる期間である。このため、期間 P 6 では、期間 P 5 から引き続いて信号 O C a が H レベルであるので、セレクター 2 2 3 は、信号 G t1 として H レベルを選択し、信号 G t2 として差動増幅器 2 2 1 の出力信号を選択する。

期間 P 5 では、電圧 Out を信号 A in の電圧 V in に追従させる制御が実行されるが、期間 P 6 において電圧 V in が電圧  $V_{cen}$  で一定に転じた直後では、電圧 Out が、信号 A in の電圧 V in に一致していない場合があるが、期間 P 2 に転じた直後と同様に、電圧 Out は、電圧 V in (  $V_{cen}$  ) に一致する地点で一定になる。このとき、トランジスター 2 3 2 はリニア動作となり、信号 G t2 は、トランジスター 2 3 2 におけるソース・ドレイン間の抵抗、および、抵抗素子  $R_u$ 、 $R_d$  で定まる電圧 Out が電圧 V in (  $V_{cen}$  ) となるような電圧で一定となる。

なお、図 1 1 では、期間 P 5 から期間 P 6 にかけての信号 G t2 の電圧変化については簡略化して、直ちにバランスした状態を示している。

#### 【 0 0 8 0 】

図 1 0 に示した駆動回路 1 2 0 a によれば、期間 P 1 ~ P 6 毎に、次のような動作によつて駆動信号 C O M - A の電圧 Out を、信号 A in の電圧 V in に追従させる制御が実行される。

すなわち、電圧 V in が低下する期間 P 1、P 5 ではトランジスター 2 3 2 のスイッチング動作により、電圧 V in が閾値  $V_{th}$  よりも低い値で一定となる期間 P 2、P 6 では、トランジスター 2 3 2 のリニア動作により、電圧 V in が上昇する期間 P 3 ではトランジスター 2 3 1 のスイッチング動作により、電圧 V in が閾値  $V_{th}$  以上の値で一定となる期間 P 4 で

10

20

30

40

50

は、トランジスター 231 のリニア動作により、それぞれ電圧  $V_{out}$  を電圧  $V_{in}$  に追従させる制御が実行される。

#### 【0081】

このような駆動回路 120a によれば、常時スイッチングする D 級增幅と比較して、電圧  $V_{in}$  が一定である期間 P2、P4、P6 では、トランジスター 231、232 がスイッチング動作をしない。また、D 級增幅では、スイッチング信号を復調する LPF (Low Pass Filter)、特にコイルのようなインダクターが必要となるが、駆動回路 120a では、そのような LPF は不要である。このため、駆動回路 120a によれば、D 級增幅と比較して、スイッチング動作や LPF で消費される電力を抑えることができるほか、回路の簡略化、小型化を図ることができる。

10

#### 【0082】

なお、駆動回路（その1）において、駆動信号 COM-A の電圧  $V_{out}$ （信号 A in の電圧  $V_{in}$ ）が上昇する期間 P3 では、トランジスター 231 がスイッチング動作し、電圧  $V_{out}$  が低下する期間 P1、P5 では、トランジスター 232 がスイッチング動作すると説明したが、接続される圧電素子  $P_{zt}$  の個数が多い場合、トランジスターのオン抵抗と負荷容量で決まる時定数の関係で、リニア動作する場合もあり得る。

また、駆動回路（その1）において、電圧  $V_{out}$  が閾値  $V_{th}$  以上の電圧で一定となる期間 P4 では、トランジスター 231 がリニア動作し、電圧  $V_{out}$  が閾値  $V_{th}$  よりも低い電圧で一定となる期間 P2、P6 では、トランジスター 232 がリニア動作すると説明したが、同様な理由により、スイッチング動作する場合もあり得る。

20

#### 【0083】

駆動信号 COM-A (COM-B) については台形波形に限らず、正弦波などのように傾きに連続性を有する波形であっても良い。このような波形を出力させる場合、駆動回路（その1）では、駆動信号 COM-A の電圧  $V_{out}$ （信号 A in の電圧  $V_{in}$ ）の変化が相対的に大きい場合、具体的には、単位時間当たりにおいて所定電圧以上で電圧が変化する期間（第1期間）でトランジスター 231、232 の一方がスイッチング動作する一方で、電圧  $V_{out}$  の変化が相対的に小さい場合、具体的には、単位時間当たりにおいて所定電圧よりも低い電圧で変化する、または、変化しない一定の期間（第2期間）でトランジスター 231、232 の一方がリニア動作することになる。

#### 【0084】

30

また、駆動回路（その1）において抵抗素子  $R_u$  のプルアップ先は、駆動信号 COM-A の最高電圧以上の電圧であれば良いので、この例では、電圧  $V_D$  の給電線としている。また、抵抗素子  $R_d$  のプルダウン先は、駆動信号 COM-A の最低電圧以下の電圧であれば良いので、この例では、グランド Gnd としている。

#### 【0085】

ここでは、駆動信号 COM-A を出力する駆動回路 120a を例にとって説明したが、駆動信号 COM-B を出力する駆動回路 120b についても同様な動作となる。駆動信号 COM-B の波形については図5で説明した通りであり、信号 OCb については上述した通りであるので、波形についての図示を省略する。なお、駆動回路 120b についても、信号 B in の電圧に追従するような電圧  $V_{out}$  の駆動信号 COM-B を出力することになる。

40

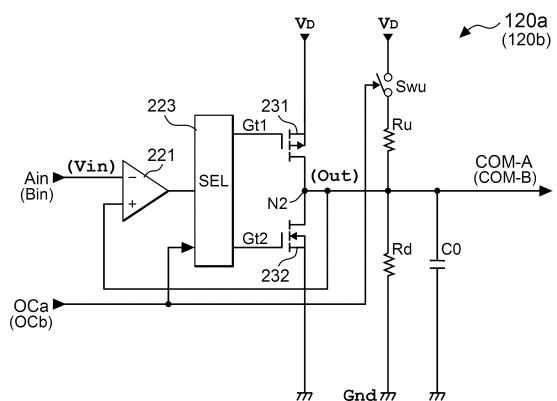

#### 【0086】

ところで、図10に示した構成では、抵抗素子  $R_u$ 、 $R_d$  が電源の電圧  $V_D$  およびグランド Gnd の間で電気的に直列に接続されるので、貫通電流が常時流れ、消費電力の点で改善の余地がある。そこで次に、この点を改善した別構成に係る駆動回路（その2）について説明する。

#### 【0087】

図12Aは、駆動回路（その2）の構成を示す図である。この図に示される駆動回路（その2）が、図10に示した駆動回路（その1）と相違する点は、スイッチ  $S_{wu}$  を有する点である。スイッチ  $S_{wu}$ （第1スイッチ）は、抵抗素子  $R_u$  とともに、電源電圧の高

50

位側電圧  $V_D$  の給電線とノード N 2との間ににおいて電気的に直列に接続され、信号 O c a が H レベルであればオンし、L レベルであればオフする。このため、スイッチ S w u は、セレクター 2 2 3 により信号 G t1 として差動増幅器 2 2 1 の出力信号が選択される場合、すなわち期間 P 1、P 2、P 5、P 6 でオンする。一方で、スイッチ S w u は、信号 G t2 として差動増幅器 2 2 1 の出力信号が選択される場合、すなわち期間 P 3、P 4 でオフする。このため、駆動回路（その 2）によれば、図 1 0 に示される駆動回路（その 1）と比較して、貫通電流により消費される電力を抑えることができる。

#### 【 0 0 8 8 】

なお、駆動回路（その 2）においては、プルアップ用の抵抗素子 R u の側にスイッチ S w u を設けたが、プルダウン用の抵抗素子 R d の側にも別のスイッチを設けても良い。 10

#### 【 0 0 8 9 】

図 1 2 B は、抵抗素子 R d の側にスイッチ S w d を有する駆動回路（その 3）を示す図である。この図において、NOT 回路 2 9 1 は、信号 O C a の論理レベルを反転して、スイッチ S w d のオンオフを制御する。スイッチ S w d（第 2 スイッチ）は、NOT 回路 2 9 1 の出力信号が H レベルであればオンし、L レベルであればオフする。

このため、スイッチ S w u、S w d が互いに排他的にオンオフするので、電源の高位側電圧  $V_D$  からグランド Gnd に向かって、抵抗素子 R u、R d を介して貫通電流が流れない。このため、駆動回路（その 3）は、駆動回路（その 2）と比較して、さらに低消費電力化を図ることができる。 20

#### 【 0 0 9 0 】

後述するように、スイッチ S w u については、期間 P 1、P 5 においてもオフさせ、スイッチ S w d については、期間 P 3 においてもオフさせる構成としても良いが、信号 O C a とは独立した信号が必要となり、制御部 1 1 0 等の複雑化を招く。逆にいえば、駆動回路（その 2、その 3）では、制御部 1 1 0 を、駆動回路（その 1）と同じものを用いながら、消費電力を抑えることができる。 20

#### 【 0 0 9 1 】

ここで、ノード N 2 のプルアップおよびプルダウンの役割について検討する。

プルアップが特に必要となる場合とは、信号 A in（駆動信号 C O M - A）が閾値  $V_{th}$  よりも低い電圧で一定となる期間 P 2、P 6、すなわちトランジスター 2 3 2 をリニア動作させる場合である。この場合、高位側のトランジスター 2 3 1 がオフであるので、低位側のトランジスター 2 3 2 によってノード N 2 の電圧 Out を信号 A in に追従させるためには、ノード N 2 を高位側にプルアップする必要がある。 30

一方、プルダウンが特に必要となる場合とは、信号 A in（駆動信号 C O M - A）が閾値  $V_{th}$  以上の電圧で一定となる期間 P 4、すなわちトランジスター 2 3 1 をリニア動作させる場合である。この場合、ローサイドのトランジスター 2 3 2 がオフであるので、ハイサイドのトランジスター 2 3 1 によってノード N 2 の電圧 Out を電圧 A in に追従させるために、ノード N 2 を低位側にプルダウンする必要がある。

#### 【 0 0 9 2 】

なお、信号 O C a ( O C b ) については、制御部 1 1 0 が出力するのではなく、データ d A ( d B ) を次のように解析することで、別の回路が生成することが可能である。 40

例えば、データ d A ( d B ) についての、時間的に隣り合う離散値（データ）同士を比較し、当該離散値同士が同じであれば、電圧一定区間であるし、当該一定区間における離散値を判別することで、一定区間の電圧が閾値  $V_{th}$  以上であるか否かを判別することができる。また、当該離散値同士のうち、時間的に後の離散値が前の離散値よりも電圧変換したときに高くなっているれば、電圧上昇区間であるし、時間的に後の離散値が前の離散値よりも電圧変換したときに低くなっているれば、電圧低下区間である。

データ d A ( d B ) ではなく、アナログ変換後の信号を同様に解析しても良い。

#### 【 0 0 9 3 】

さて、駆動回路（その 1、その 2、その 3）では、駆動信号 C O M - A ( C O M - B ) の振幅に合わせて一対のトランジスター 2 3 1、2 3 2 が電源電圧 ( $V_D$  - Gnd) で動作 50

する。上述したように駆動信号 COM - A の電圧は最大で 40 ボルト程度であるので、セレクター 223 および差動増幅器 221 に対して高耐圧が要求される。その理由は、トランジスター 231 のゲート端子に信号 Gt1 を供給するとともに、トランジスター 232 のゲート端子に信号 Gt2 を供給する必要があるからである。

そこで次に、この点を改善した別構成に係る駆動回路（その 4）について説明する。

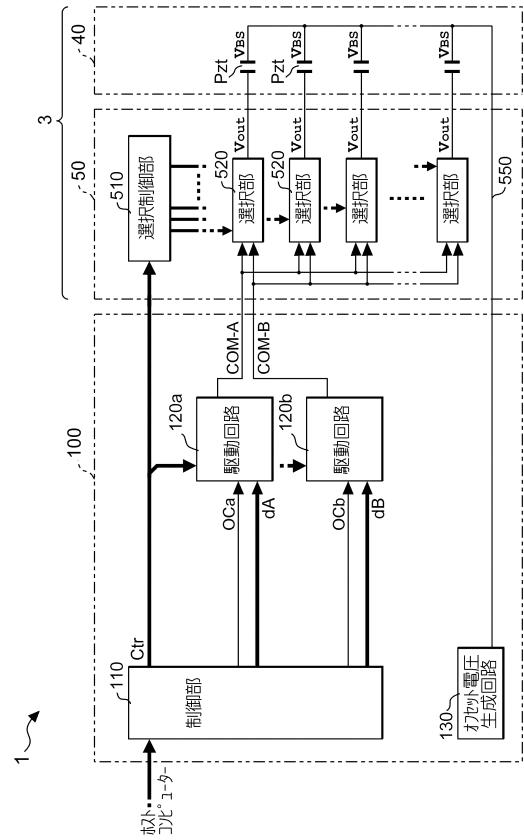

#### 【0094】

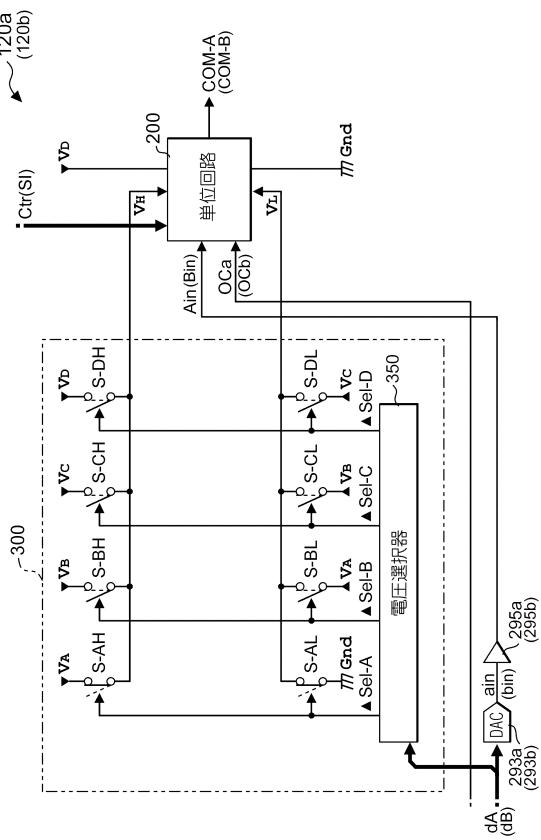

図 13 は、駆動回路（その 4）を含む印刷装置（その 2）の電気的な構成を示すプロック図である。この図に示される印刷装置（その 2）が、図 4 に示した印刷装置（その 1）と相違する点は、第 1 に、電圧増幅器 115a、115b を有さない点である。このため、DAC 113a の出力である小振幅の信号 ain が駆動回路 120a に供給されるとともに、DAC 113b の出力である小振幅の信号 bin が駆動回路 120b に供給される。また、相違点としては、第 2 に、データ dA が駆動回路 120a に、データ dB が駆動回路 120b に、それぞれ供給される点である。

#### 【0095】

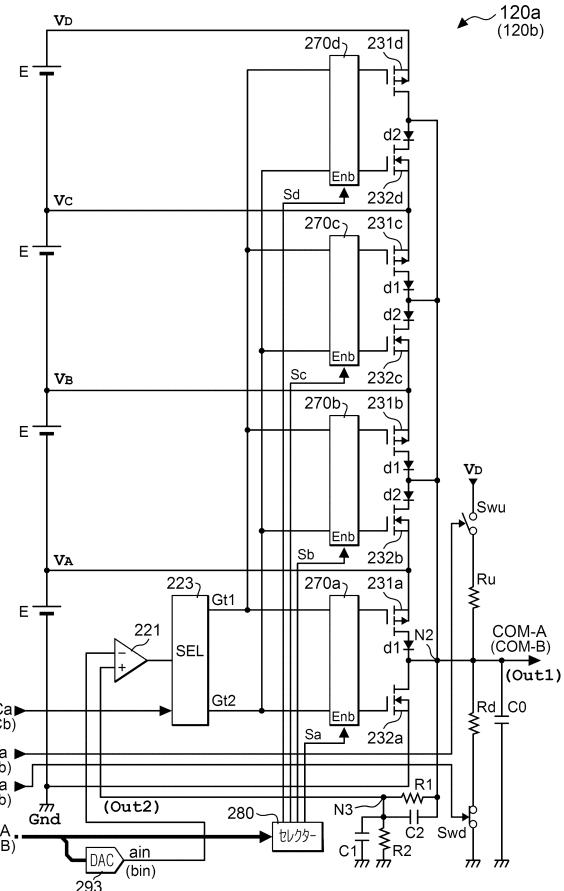

図 14A は、駆動回路（その 4）の構成を示す図である。

この図に示されるように、駆動回路 120a は、4 つの基準電源 E と、差動増幅器 221 およびセレクター 223 に加えて、ゲートセレクター 270a、270b、270c、270d と、セレクター 280 と、4 つのトランジスター対と、抵抗素子 R1、R2 と、スイッチ SWU と、コンデンサー C0 とを含む。

#### 【0096】

駆動回路（その 4）では、電圧 E を出力する基準電源の 4 段直列接続によって電圧 E、2E、3E、4E がそれぞれ電圧 VA、VB、VC、VD として出力される。

#### 【0097】

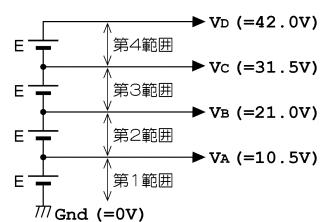

図 15 は、電圧 VA、VB、VC、VD について説明するための図である。

この図に示されるように、電圧 E を例えば 10.5V としたとき、電圧 VA、VB、VC、VD の各々は、それぞれ 10.5V、21.0V、31.5V、42.0V である。本実施形態では、電圧 VA、VB、VC、VD で次のような電圧範囲が規定される。すなわち、電圧ゼロのグランド Gnd 以上電圧 VA 未満の範囲が第 1 範囲として規定され、電圧 VA 以上電圧 VB 未満の範囲が第 2 範囲として規定され、電圧 VB 以上電圧 VC 未満の範囲が第 3 範囲として規定され、電圧 VC 以上電圧 VD 未満の範囲が第 4 範囲として規定される。

#### 【0098】

図 14A の説明に戻すと、差動増幅器 221 の負入力端（-）には小振幅の信号 ain が供給される一方、正入力端（+）にはノード N3 の電圧 Out2 が印加されている。このため、差動増幅器 221 は、電圧 Out2 から、入力である信号 ain の電圧 Vin を減算した差電圧を増幅して出力することになる。

なお、駆動回路（その 4）における差動増幅器 221 は、駆動回路（その 1）とは異なり、電源の高位側を電圧 VA としている。このため、差動増幅器 221 の出力電圧は、グランド Gnd から電圧 VA までの範囲となる。

#### 【0099】

セレクター 280 は、制御部 110（図 13 参照）から供給されるデータ dA (dB) から、信号 ain (bin) の電圧 Vin の範囲を判別して、当該判別の結果に応じて、それぞれ次のように選択信号 Sa、Sb、Sc、Sd を出力する。

詳細には、セレクター 280 は、データ dA (dB) で規定される電圧 Vin が 0V 以上 1.05V 未満であると判別した場合、すなわち、電圧 Vin を 10 倍で増幅したときの電圧が上記第 1 範囲に含まれる場合、選択信号 Sa のみを H レベルとし、他の選択信号 Sb、Sc、Sd を L レベルとする。また、セレクター 280 は、データ dA (dB) で規定される電圧 Vin が 1.05V 以上 2.10V 未満であると判別した場合、すなわち、電圧 Vin を 10 倍で増幅したときの電圧が上記第 2 範囲に含まれる場合、選択信号 Sb のみを H レベルとし、他の選択信号 Sa、Sc、Sd を L レベルとする。同様に、セレクター 2

10

20

30

40

50

80は、データdA(dB)で規定される電圧Vinが2.10V以上3.15V未満であると判別した場合、すなわち、電圧Vinを10倍で増幅したときの電圧が上記第3範囲に含まれる場合、選択信号S<sub>c</sub>のみをHレベルとし、他の選択信号S<sub>a</sub>、S<sub>b</sub>、S<sub>d</sub>をLレベルとし、当該電圧Vinが3.15V以上4.20V未満であると判別した場合、すなわち、電圧Vinを10倍で増幅したときの電圧が上記第4範囲に含まれる場合、選択信号S<sub>d</sub>のみをHレベルとし、他の選択信号S<sub>a</sub>、S<sub>b</sub>、S<sub>c</sub>をLレベルとする。

#### 【0100】

ここで説明の便宜上、4つのトランジスター対について説明する。

この例において、4つのトランジスター対は、トランジスター231a、232aのペア、トランジスター231b、232bのペア、トランジスター231c、232cのペア、および、トランジスター231d、232dのペアによって構成される。10

各トランジスター対のうち、ハイサイドのトランジスター231a、231b、231c、231dは、例えばPチャネル型の電界効果トランジスターであり、ローサイドのトランジスター232a、232b、232c、232dは、例えばNチャネル型の電界効果トランジスターである。

#### 【0101】

トランジスター231aについては、ソース端子に電圧V<sub>A</sub>が印加され、ドレイン端子がノードN2に接続される。トランジスター232aについては、ソース端子がグランドGndに接地され、ドレイン端子がノードN2に共通に接続される。

同様に、トランジスター231b(231c、231d)については、ソース端子に電圧V<sub>B</sub>(V<sub>C</sub>、V<sub>D</sub>)が印加され、ドレイン端子がノードN2に接続される。トランジスター232b(232c、232d)については、ソース端子に電圧V<sub>A</sub>(V<sub>B</sub>、V<sub>C</sub>)が印加され、ドレイン端子がノードN2に共通に接続される。20

#### 【0102】

なお、例えばトランジスター231aを第1ハイサイドトランジスターとし、トランジスター232aを第1ローサイドトランジスターとして、トランジスター231a、232aが第1トランジスター対とした場合、トランジスター231bが第2ハイサイドトランジスターとなり、トランジスター232bが第2ローサイドトランジスターとして、トランジスター231b、232bが第2トランジスター対となる。

#### 【0103】

詳細については後述するが、トランジスター231a、232aは、ゲートセレクター270aがイネーブルされたときに、電圧V<sub>A</sub>とグランドGndとを電源電圧として駆動信号を出力し、トランジスター231b、232bは、ゲートセレクター270bがイネーブルされたときに、電圧V<sub>B</sub>と電圧V<sub>A</sub>とを電源電圧として駆動信号を出力する。同様に、トランジスター231c、232cは、ゲートセレクター270cがイネーブルされたときに、電圧V<sub>C</sub>と電圧V<sub>B</sub>とを電源電圧として駆動信号を出力し、トランジスター231d、232dは、ゲートセレクター270dがイネーブルされたときに、電圧V<sub>D</sub>と電圧V<sub>C</sub>とを電源電圧として駆動信号を出力する構成となっている。30

この構成では、トランジスター231a、232aの電源電圧、トランジスター231b、232bの電源電圧、トランジスター231c、232cの電源電圧、および、トランジスター231d、232dの電源電圧は、それぞれ10.5Vとなる。40

#### 【0104】

ゲートセレクター270aは、入力端E<sub>nb</sub>に供給された選択信号S<sub>a</sub>がHレベルになつてイネーブルされたときに、セレクター223から出力される信号G<sub>t1</sub>、G<sub>t2</sub>をそれぞれレベルシフトして、トランジスター231a、232aのゲート端子に供給する。詳細には、ゲートセレクター270aは、イネーブルされたときに、信号G<sub>t1</sub>の最低電圧から最高電圧までの範囲を、グランドGndから電圧V<sub>A</sub>までの第1範囲にレベルシフトして、トランジスター231aのゲート端子に供給し、信号G<sub>t2</sub>の最低電圧から最高電圧までの範囲を、上記第1範囲にレベルシフトして、トランジスター232aのゲート端子に供給する。50

なお、ゲートセレクター 270a に限っていえば、信号 Gt1、Gt2 の最低電圧から最高電圧までの範囲は第 1 範囲に一致しているので、イネーブルされたときに、信号 Gt1、Gt2 をそのままトランジスター 231a、232a のゲート端子に供給する。

【0105】

ゲートセレクター 270b は、イネーブルされたときに、信号 Gt1 の最低電圧から最高電圧までの範囲を、電圧  $V_A$  から電圧  $V_B$  までの第 2 範囲にレベルシフトして、トランジスター 231b のゲート端子に供給し、信号 Gt2 の最低電圧から最高電圧までの範囲を、上記第 2 範囲にレベルシフトして、トランジスター 232b のゲート端子に供給する。すなわち、ゲートセレクター 270b に限っていえば、イネーブルされたときに、信号 Gt1、Gt2 に 10.5V を上乗せして、トランジスター 231b、232b のゲート端子に供給する。

10

【0106】

同様に、ゲートセレクター 270c は、イネーブルされたときに、信号 Gt1 の最低電圧から最高電圧までの範囲を、電圧  $V_B$  から電圧  $V_C$  までの第 3 範囲にレベルシフトして、トランジスター 231c のゲート端子に供給し、信号 Gt2 の最低電圧から最高電圧までの範囲を、上記第 3 範囲にレベルシフトして、トランジスター 232c のゲート端子に供給する。すなわち、ゲートセレクター 270c に限っていえば、イネーブルされたときに、信号 Gt1、Gt2 に 21.0V を上乗せして、トランジスター 231c、232c のゲート端子に供給する。

20

ゲートセレクター 270d についても同様に、イネーブルされたときに、信号 Gt1 の最低電圧から最高電圧までの範囲を、電圧  $V_C$  から電圧  $V_D$  までの第 4 範囲にレベルシフトして、トランジスター 231d のゲート端子に供給し、信号 Gt2 の最低電圧から最高電圧までの範囲を、上記第 4 範囲にレベルシフトして、トランジスター 232d のゲート端子に供給する。すなわち、ゲートセレクター 270d に限っていえば、イネーブルされたときに、信号 Gt1、Gt2 に 31.5V を上乗せして、トランジスター 231d、232d のゲート端子に供給する。

【0107】

なお、ゲートセレクター 270a、270b、270c、270d は、それぞれの入力端  $E_{nb}$  に供給された選択信号が L レベルになってディセーブルされたとき、それぞれに対応する 2 つのトランジスターをそれぞれオフとさせる信号を出力する。すなわち、ゲートセレクター 270a、270b、270c、270d は、ディセーブルにされると、信号 Gt1 を強制的に H レベルに変換し、信号 Gt2 を強制的に L レベルに変換する。

30

ここでいう H、L レベルは、ゲートセレクター 270a、270b、270c、270d のそれぞれにおける電源電圧の高位側電圧、低位側電圧である。例えば、ゲートセレクター 270b は、電圧  $V_B$  と電圧  $V_A$  とを電源電圧とするので、高位側の電圧  $V_B$  が H レベルであり、低位側の電圧  $V_A$  が L レベルである。

【0108】

ノード N2 は、抵抗素子 R1 を介して差動増幅器 221 の正入力端 (+) に帰還される。この例では、便宜的に、差動増幅器 221 の正入力端 (+) をノード N3 と表記する一方、当該ノード N3 の電圧を Out2 と表記している。

40

ノード N3 は、抵抗素子 R2 を介してグランド Gnd に接地される。このため、ノード N3 の電圧 Out2 は、電圧 Out の電圧を、抵抗素子 R1、R2 の抵抗値で規定される比、すなわち、 $R2 / (R1 + R2)$  で分圧した電圧となる。本実施形態において、降圧比は、1 / 10 に設定される。換言すれば、電圧 Out2 は、電圧 Out の 1 / 10 という関係にある。

【0109】

また、図 14A の駆動回路（その 4）では、図 12A に示した駆動回路（その 2）と同様に、スイッチ Swu と抵抗素子 Ru とが電源電圧の高位側電圧  $V_D$  の給電線とノード N2 との間ににおいて電気的に直列に接続されている。一方で、ノード N2 のプルダウンは、図 14A に示される駆動回路（その 4）では、ノード N2 の電圧 Out を降圧して差動増幅

50

器 2 2 1 に帰還する抵抗素子 R 1、R 2 が担っている。逆にいえば、駆動回路（その 4）における抵抗素子 R 1、R 2 は、ノード N 2 をプルダウンする機能と、電圧 Out を降圧して差動増幅器 2 2 1 に帰還する機能との双方を担っている。

#### 【 0 1 1 0 】

ダイオード d 1、d 2 は逆流防止用である。ダイオード d 1 の順方向は、トランジスター 2 3 1 a、2 3 1 b、2 3 1 c のドレイン端子からノード N 2 に向かう方向であり、ダイオード d 2 の順方向は、ノード N 2 からトランジスター 2 3 1 b、2 3 1 c、2 3 1 d のドレイン端子に向かう方向である。

なお、ノード N 2 の電圧 Out は電圧  $V_D$  よりも高くならないので、逆流を考慮する必要がない。このため、トランジスター 2 3 1 d に対してダイオード d 1 は設けられていない。同様にノード N 2 の電圧 Out は電圧ゼロのグランド Gnd よりも低くなないので、トランジスター 2 3 2 a に対してダイオード d 2 は設けられていない。

#### 【 0 1 1 1 】

次に、駆動回路（その 4）の動作を、駆動信号 COM - A を出力する場合を例にとって説明する。

#### 【 0 1 1 2 】

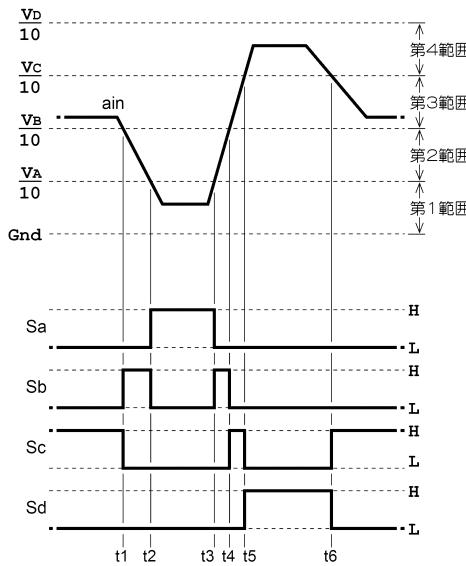

図 16 は、駆動回路（その 4）の動作を説明するための図である。この図に示されるように、また上述したように信号 a in は、駆動信号 COM - A の相似形であるが、D A C 1 1 3 a によりアナログ変換した直後の小振幅の信号であって、駆動信号 COM - A の電圧の 1 / 1 0 の関係にある。

このため、電圧  $V_A$ 、 $V_B$ 、 $V_C$ 、 $V_D$  で規定される第 1 範囲から第 4 範囲までを、信号 a in の電圧範囲に換算する場合、電圧  $V_A / 1 0$ 、 $V_B / 1 0$ 、 $V_C / 1 0$ 、 $V_D / 1 0$  で規定される。詳細には、信号 a in については、0 V 以上電圧  $V_A / 1 0$  (= 1 . 0 5 V) 未満の範囲が第 1 範囲に相当し、電圧  $V_A / 1 0$  以上電圧  $V_B / 1 0$  (= 2 . 1 0 V) 未満の範囲が第 2 範囲に相当し、電圧  $V_B / 1 0$  以上電圧  $V_C / 1 0$  (= 3 . 1 5 V) 未満の範囲が第 3 範囲に相当し、電圧  $V_C / 1 0$  以上電圧  $V_D / 1 0$  (= 4 . 2 0 V) 未満の範囲が第 4 範囲に相当する。

#### 【 0 1 1 3 】

まず、セレクター 2 8 0 は、電圧  $V_{in}$  がタイミング t 1 よりも前において第 3 範囲であるとデータ d A から判別した場合、選択信号 S c のみを H レベルとし、他の選択信号 S a、S b、S d を L レベルとするので、ゲートセレクター 2 7 0 c がイネーブルされ、他のゲートセレクター 2 7 0 a、2 7 0 b、2 7 0 d がディセーブルされる。したがって、この場合、トランジスター 2 3 1 c、2 3 2 c が、電源電圧として電圧  $V_C$ 、 $V_B$  を用いて駆動信号 COM - A を出力することになる。

#### 【 0 1 1 4 】

次に、電圧  $V_{in}$  がタイミング t 1 からタイミング t 2 までの期間にわたって第 2 範囲となつたとき、セレクター 2 8 0 は、選択信号 S b のみを H レベルとし、他の選択信号 S a、S c、S d を L レベルとするので、ゲートセレクター 2 7 0 b がイネーブルされ、他のゲートセレクター 2 7 0 a、2 7 0 c、2 7 0 d がディセーブルされる。したがって、この場合、トランジスター 2 3 1 b、2 3 2 b が電源電圧として電圧  $V_B$ 、 $V_A$  を用いて駆動信号 COM - A を出力することになる。

電圧  $V_{in}$  がタイミング t 2 からタイミング t 3 までの期間にわたって第 1 範囲となつたとき、セレクター 2 8 0 は、選択信号 S a のみを H レベルとし、この結果、ゲートセレクター 2 7 0 a のみがイネーブルされるので、トランジスター 2 3 1 a、2 3 2 a が電源電圧として電圧  $V_A$ 、グランド Gnd を用いて駆動信号 COM - A を出力することになる。

#### 【 0 1 1 5 】

以降については簡単に説明すると、タイミング t 3 からタイミング t 4 までの期間では、ゲートセレクター 2 7 0 b のみがイネーブルされるので、トランジスター 2 3 1 b、2 3 2 b が電源電圧として電圧  $V_B$ 、 $V_A$  を用い、タイミング t 4 からタイミング t 5 までの期間では、ゲートセレクター 2 7 0 c のみがイネーブルされるので、トランジスター 2

10

20

30

40

50

31c、232cが電源電圧として電圧V<sub>C</sub>、V<sub>B</sub>を用い、タイミングt5からタイミングt6までの期間では、ゲートセレクター270dのみがイネーブルされるので、トランジスター231d、232dが電源電圧として電圧V<sub>D</sub>、V<sub>C</sub>を用い、タイミングt6からは、ゲートセレクター270cのみがイネーブルされるので、トランジスター231c、232cが電源電圧として電圧V<sub>C</sub>、V<sub>B</sub>を用いて、それぞれ駆動信号COM-Aを出力することになる。

#### 【0116】

一方、ノードN3の電圧Out2は、電圧Outの1/10なので、差電圧を求めるにあたって両者のスケールが揃えられている。

#### 【0117】

駆動回路(その4)では、信号ainの電圧Vinに応じてゲートセレクター270a、270b、270c、270dのいずれかがイネーブルされるとともに、イネーブルされたいずれか1つのゲートセレクターに対応するトランジスター対によって、電圧Outを1/10に降圧した電圧Out2が電圧Vinに追従するような動作、逆にいえば、電圧Vinに対して電圧Outが10倍となるように動作が実行される。

#### 【0118】

例えば、電圧Out2が電圧Vinに追従するような動作は、電圧Vinが第1範囲に相当する場合であれば、ゲートセレクター270aがイネーブルされるので、トランジスター231a、232aによって実行される。同様に、電圧Out2が電圧Vinに追従するような動作は、電圧Vinが第2範囲に相当する場合であれば、ゲートセレクター270bがイネーブルされるので、トランジスター231b、232bによって、電圧Vinが第3範囲に相当する場合であれば、ゲートセレクター270cがイネーブルされるので、トランジスター231c、232cによって、電圧Vinが第4範囲に相当する場合であれば、ゲートセレクター270dがイネーブルされるので、トランジスター231d、232dによって、それぞれ実行される。

#### 【0119】

信号ainの電圧Vinについては、第1範囲から第4範囲までにおいて隣り合う領域を跨ぐ(移行)場合がある。例えば図16でいえば、電圧Vinは、タイミングt1において第3範囲から第2範囲へと移行する。電圧Vinが第3範囲であれば、ゲートセレクター270cがイネーブルされるので、トランジスター231c、232cによって、当該電圧Vinに対して電圧Outが10倍となるように制御される。タイミングt1において電圧Vinが第3範囲から第2範囲に移行したとき、ゲートセレクター270cがディセーブルになり、ゲートセレクター270bがイネーブルされるので、トランジスター231b、232bによって、電圧Out2が電圧Vinに追従するように制御される。

ここでは、電圧Vinが第3範囲から第2範囲へと移行する場合を例にとって説明したが、他の場合でも同様であり、例えば第2範囲から第1範囲への移行であれば、ゲートセレクター270bがディセーブルになり、ゲートセレクター270aがイネーブルされるので、トランジスター231a、232aによって、引き続き電圧Out2が電圧Vinに追従するように制御される。

#### 【0120】

駆動回路(その4)にはトランジスター対が4組存在するが、動作しているトランジスター対は、常に1組であり、他のトランジスター対はオフしているので、低消費電力化を図ることができる。また、駆動回路(その4)によれば、差動増幅器221およびセレクター223については、電源としては比較的低い電圧(V<sub>A</sub>-Gnd)で動作するので、素子サイズの肥大化などを抑制することができる。

#### 【0121】

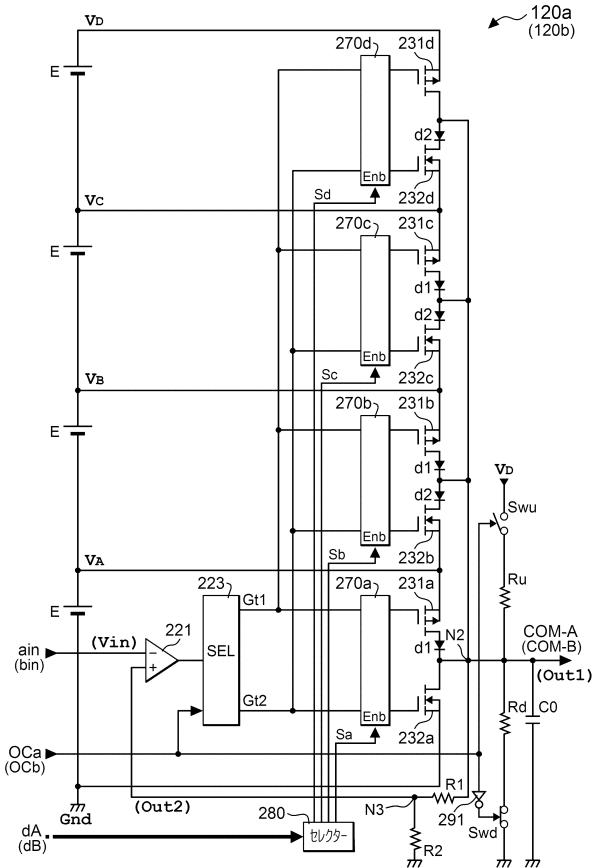

図14Bは、駆動回路(その5)を示す図である。この駆動回路(その5)は、駆動回路(その3)と同様に、プルアップを無効化するスイッチSwuに加えて、プルダウンを無効化するスイッチSwdを設けた構成である。駆動回路(その5)によれば、貫通電流が流れないので、駆動回路(その4)と比較して、さらに低消費電力化を図ることができる。

10

20

30

40

50

る。

【0122】

図14Aの駆動回路(その4)や図14Bの駆動回路(その5)における差動増幅器221およびセレクター223について、比較的高い電圧で動作することが許容されるのであれば、次のような駆動回路(その6)でも良い。

【0123】

図17は、駆動回路(その6)を含む印刷装置(その3)の電気的な構成を示すプロック図である。この図に示される印刷装置(その3)が図13に示した印刷装置(その2)と相違する点は、DAC113a、113bを有さない点である。ただし、次に説明するように、DACおよび電圧増幅器に相当する回路が駆動回路120a(120b)の側に設けられている。

10

【0124】

図18は、駆動回路(その6)の構成を示す図である。この図に示される駆動回路(その6)が図14Bに示した駆動回路(その5)と相違する主な点は、第1に、駆動信号COM-Aを出力する駆動回路120aでいえば、データdAをアナログで小振幅の信号ainに変換するDAC293aと、信号ainの電圧を例えれば10倍に増幅して大振幅の信号Ainとして出力する電圧増幅器295aとを備える点と、第2に、トランジスター対のそれぞれに対応して差動増幅器とセレクターとのセットが設けられる点と、第3に、抵抗素子R1、R2を有しない点である。

20

【0125】

第1の点について説明すると、上述したように、DAC293aは図4におけるDAC113aに相当し、電圧増幅器295aは図4における電圧増幅器115aに相当する。

このため、DAC113aは、デジタルのデータdAをアナログで小振幅の信号ainに変換し、電圧増幅器295aは、当該信号ainの電圧を例えれば10倍に増幅して、大振幅の信号Ainとして出力する。

30

【0126】

第2の点について説明すると、トランジスター231a、232aの対に対応して差動増幅器221aおよびセレクター223aが設けられ、トランジスター231b、232bの対に対応して差動増幅器221bおよびセレクター223bが設けられ、トランジスター231c、232cの対に対応して差動増幅器221cおよびセレクター223cが設けられ、トランジスター231d、232dの対に対応して差動増幅器221dおよびセレクター223dが設けられている。

【0127】

差動増幅器221a、221b、221c、222dは、図10における差動増幅器221と同様であり、電源の高位側を電圧V<sub>D</sub>とし、低位側をグランドGndとして、出力である駆動信号COM-Aの電圧Outから、入力である大振幅の信号Ainの電圧Vinを減算した差電圧を増幅して出力する。

駆動回路(その6)では、ノードN2の電圧Outを降圧して帰還する必要がないので、図14Aで示される駆動回路(その4)の抵抗素子R1、R2が廃止されている。ただし、ノードN2をプルダウンするために、抵抗素子RdがスイッチSwとともに設けられている。

40

【0128】

セレクター223a、223b、223c、223dは、図10におけるセレクター223と同様に、信号OCaがLレベルであれば、差動増幅器の出力信号を選択して、ハイサイドトランジスター側に出力するとともに、ローサイドトランジスターをオフにする信号を、当該ローサイドトランジスター側に出力する一方、信号OCaがHレベルであれば、差動増幅器の出力信号を選択して、ローサイドトランジスター側に出力するとともに、ハイサイドトランジスターをオフにする信号を、当該ハイサイドトランジスター側に出力する。

【0129】

50

なお、駆動回路（その6）におけるゲートセレクター270a、270b、270c、270dは、駆動回路（その4、その5）と比較してレベルシフトする機能を有さず、単にイネーブルされたときに、対応するトランジスターのゲート端子の各々に、対応するセレクターの出力信号をそれぞれ供給する一方、ディセーブルされたときに、対応するトランジスターのゲート端子の各々に、当該トランジスターのそれぞれをオフする信号をそれぞれ供給する。

#### 【0130】

また、駆動回路（その6）には、駆動回路（その5）と同様に、NOT回路291、スイッチSwdが設けられている。スイッチSwdは、抵抗素子Rdとともに、ノードN2とグランドGndとの間において電気的に直列に接続され、信号OcaをNOT回路291により論理反転した信号がHレベルであればオンし、Lレベルであればオフする。このため、スイッチSwu、Swdは、互いに排他的にオンオフする。

#### 【0131】

駆動回路（その6）によれば、電圧Outが、電圧Ainの電圧に追従するように制御される。この制御に際して、駆動回路（その6）では、駆動回路（その4、その5）と同様に、トランジスター対が4組存在するが、動作しているトランジスター対は、常に1組であり、他のトランジスター対はオフしているので、低消費電力化を図ることができる。

また、駆動回路（その6）によれば、スイッチSwu、Swdが互いに排他的にオンオフするので、電源の高位側電圧VDおよびグランドGndの間において抵抗素子R1、R2を介して貫通電流が流れないので、さらなる低消費電力化を図ることができる。

#### 【0132】

駆動回路（その4、その5、その6）において、セレクター280は、アナログ変換前のデータdA(dB)によって電圧Vinが第1範囲から第4範囲までのいずれかに含まれるかを判別する構成としたが、多少精度や遅延が発生するものの、アナログ変換後の信号ain(bin)で判別しても良い。

このため、トランジスター対を元駆動信号に基づく信号に応じて選択する、といった場合の当該信号には、データdA(dB)の場合もあるし、当該データdA(dB)をアナログ変換した信号ain(bin)の場合もあるし、データdA(dB)と信号ain(bin)とを重み付けした信号の場合もある。

なお、4つのトランジスター対については、元駆動信号に基づく信号に応じてセレクター280によって選択されるとともに、選択されたトランジスター対から駆動信号COM-Aが出力される一方、非選択としたトランジスター対がゲートセレクターによってオフにさせられるので、セレクター280およびゲートセレクター270a、270b、270c、270dをトランジスター対切替部として概念することができる。

#### 【0133】

駆動回路（その4、その5、その6）において、トランジスター対のセット数をそれぞれ「4」としたが、「2」以上であれば良い。セット数が多くなるにつれて、各基準電源Eの電圧を低く抑えることができる。

また、駆動回路（その4、その5、その6）において、電圧VA、VB、VC、VDについて、電圧Eを出力する基準電源の4段直列接続（図15参照）によって出力する構成としたので、各電圧セットにおける高位側電圧と低位側電圧との差を電圧E（=10.5V）で揃えたが、不揃いとした構成でも良い。

電圧範囲については、第1範囲から第4範囲までのうち、隣り合う範囲については一部重複させても良い。

なお、セレクター280がアナログ変換後の信号ain(bin)で判別しても良い点や、トランジスター対のセット数が「2」以上であれば良い点等については、後述する駆動回路（その10、その11、その12）でも同様に適用可能である。

#### 【0134】

さて、駆動回路（その4、その5、その6）では、4組のトランジスター対のうち、データdA(dB)等に応じていずれかを選択する構成としたが、次の駆動回路（その7、

10

20

30

40

50

その 8 ) のように、1組のトランジスター対で電源電圧をデータ d A ( d B ) 等に応じて切り替える構成も可能である。

【 0 1 3 5 】

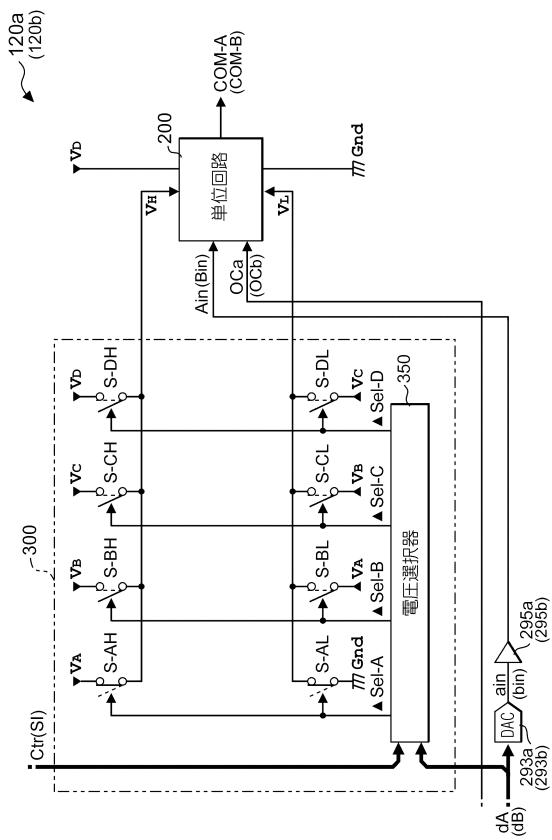

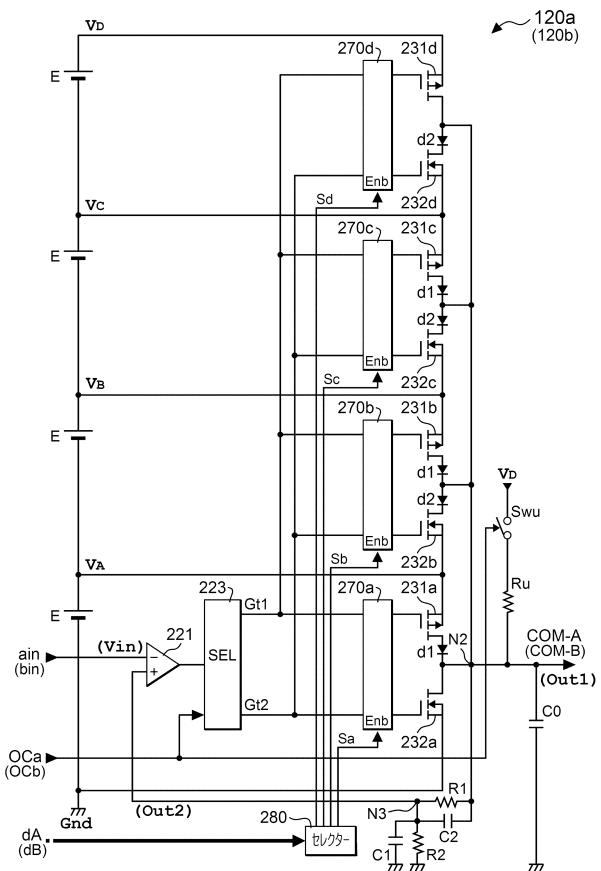

なお、駆動回路 ( その 7 ) を含む印刷装置の電気的な構成を示すブロック図については、図 17 の印刷装置 ( その 3 ) と同様である。すなわち、制御部 110 から、データ d A および信号 O C a が駆動回路 120 a に供給されるとともに、データ d B および信号 O C b が駆動回路 120 b に供給される構成となっている。

【 0 1 3 6 】

図 19 は、駆動回路 ( その 7 ) の構成を示す図である。この図に示されるように、駆動信号 C O M - A を出力する駆動回路 ( その 7 ) は、単位回路 200 、 D A C 293 a 、電圧増幅器 295 a および電圧切替器 300 を含む。

10

このうち、 D A C 293 a は、デジタルのデータ d A をアナログで小振幅の信号 a in に変換し、電圧増幅器 295 a は、当該信号 a in の電圧を例えば 10 倍に増幅して大振幅の信号 A in として出力する。

【 0 1 3 7 】

電圧切替器 ( 電源電圧切替部 ) 300 は、データ d A に応じて、電圧セット ( V A 、 G nd ) 、 ( V B 、 V A ) 、 ( V C 、 V B ) または ( V D 、 V C ) のいずれかを選択し、当該選択した電圧セットを単位回路 200 の電源電圧 ( V H 、 V L ) として給電するものである。

詳細には、電圧切替器 300 は、電圧選択器 350 と、スイッチ S - A H 、 S - A L の組と、スイッチ S - B H 、 S - B L の組と、スイッチ S - C H 、 S - C L の組と、スイッチ S - D H 、 S - D L の組と、を含み、電圧選択器 350 がデータ d A に応じて選択信号 Sel - A 、 Sel - B 、 Sel - C 、 Sel - D を次のように出力する。

20

【 0 1 3 8 】

すなわち、電圧選択器 350 は、データ d A をアナログ変換して電圧増幅した信号 A in の電圧が第 1 範囲になる場合、選択信号 Sel - A を H レベルとし、選択信号 Sel - B 、 Sel - C 、 Sel - D を L レベルとし、信号 A in の電圧が第 2 範囲になる場合、選択信号 Sel - B を H レベルとし、選択信号 Sel - A 、 Sel - C 、 Sel - D を L レベルとし、信号 A in の電圧が第 3 範囲になる場合、選択信号 Sel - C を H レベルとし、選択信号 Sel - A 、 Sel - B 、 Sel - D を L レベルとし、信号 A in の電圧が第 4 範囲になる場合、選択信号 Sel - D を H レベルとし、選択信号 Sel - A 、 Sel - B 、 Sel - C を L レベルとする。

30

【 0 1 3 9 】

スイッチ S - A H 、 S - A L は、選択信号 Sel - A が H レベルのときにオンするものであり、スイッチ S - A H の一端には電圧 V A が印加され、スイッチ S - A L の一端は電圧ゼロのグランド G nd に接続されている。スイッチ S - B H 、 S - B L は、選択信号 Sel - B が H レベルのときにオンするものであり、スイッチ S - B H の一端には電圧 V B が印加され、スイッチ S - B L の一端には電圧 V A が印加されている。スイッチ S - C H 、 S - C L は、選択信号 Sel - C が H レベルのときにオンするものであり、スイッチ S - C H の一端には電圧 V C が印加され、スイッチ S - B L の一端には電圧 V B が印加されている。スイッチ S - D H 、 S - D L は、選択信号 Sel - D が H レベルのときにオンするものであり、スイッチ S - D H の一端には電圧 V D が印加され、スイッチ S - B L の一端には電圧 V C が印加されている。

40

【 0 1 4 0 】

スイッチ S - A H 、 S - B H 、 S - C H 、 S - D H の他端は、共通接続されるとともに、これらのスイッチのいずれかのオンによって選択された電圧が単位回路 200 に電源の高位側電圧 V H として給電される。同様にスイッチ S - A L 、 S - B L 、 S - C L 、 S - D L の他端は、共通接続されるとともに、これらのスイッチのいずれかのオンによって選択された電圧が単位回路 200 に電源の低位側電圧 V L として給電される。

【 0 1 4 1 】

したがって、単位回路 200 の電源電圧 ( V H 、 V L ) は、信号 A in の電圧に応じて次

50

のようになる。すなわち、電源電圧 ( $V_H$ 、 $V_L$ ) は、信号  $A_{in}$  の電圧が第 1 範囲の場合に電圧セット ( $V_A$ 、 $Gnd$ ) となり、第 2 範囲の場合に電圧セット ( $V_B$ 、 $V_A$ ) となり、第 3 範囲の場合に電圧セット ( $V_C$ 、 $V_B$ ) となり、第 4 範囲の場合に電圧セット ( $V_D$ 、 $V_C$ ) となる。

【0142】

図 20 は、駆動回路 (その 7) における単位回路 200 の構成を示す図である。この図に示される単位回路 200 は、図 12B に示される駆動回路 (その 3) とほぼ同様であり、相違点は、トランジスター 231 のソース端子に、高位側電圧  $V_H$  が印加されるとともに、トランジスター 232 のソース端子に、低位側電圧  $V_L$  が印加される点である。

すなわち、トランジスター対の電源電圧が相違するだけであり、ノード N2 の電圧  $Out$  を、トランジスター 231、232 が、電源電圧の範囲にある電圧  $V_{in}$  に追従するように制御する点については共通である。ここで、電圧  $V_{in}$  が、現状の電圧  $V_H$  以上高くなる場合、電圧  $V_H$ 、 $V_L$  として 1 段高いセットに切り替えられる一方、電圧  $V_L$  より低くなる場合、電圧  $V_H$ 、 $V_L$  として 1 段低いセットに切り替えられる。このため、駆動回路 (その 7) によれば、信号  $A_{in}$  の電圧  $V_{in}$  が、グランド  $Gnd$  から電圧  $V_D$  までの範囲にわたる場合、電圧切替器 300 によって、当該電圧  $V_{in}$  に応じた電圧  $V_H$ 、 $V_L$  のセットを切り替えられながら、単位回路 200 によって、ノード N2 の電圧  $Out$  が電圧  $V_{in}$  に追従するように制御されることになる。

【0143】

また、駆動回路 (その 7) によれば、スイッチ  $S_{wu}$ 、 $S_{wd}$  が互いに排他的にオンオフするので、電源の高位側電圧  $V_D$  およびグランド  $Gnd$  の間ににおいて抵抗素子  $R_1$ 、 $R_2$  を介した貫通電流が抑えられ、これにより低消費電力化が図られる。

【0144】

駆動信号 COM - A の電圧  $Out$  は 0 ~ 40V 程度で振幅するので、電圧セットを切り替えない構成であれば、単位回路 200 における電源電圧も 40V 程度必要となり、高コスト化や、回路規模の肥大化を招く。

これに対して、駆動回路 (その 7) によれば、データ d A (電圧  $V_{in}$ ) に応じて電圧セットが切り替えられて、単位回路 200 の電源電圧として給電される。このため、本実施形態では、0 ~ 40V 程度の電圧  $Out$  を出力するのにもかかわらず、単位回路 200 における電源電圧は、10.5V に抑えられるので、高コスト化や、回路規模の肥大化を防ぐことができる。

【0145】

図 21 は、駆動回路 (その 8) を含む印刷装置 (その 4) の電気的な構成を示すプロック図である。この図に示される印刷装置 (その 4) が図 17 に示した印刷装置 (その 3) と相違する点は、印刷データ S I を含む制御信号 C tr が駆動回路 120a、120b にそれぞれ供給される点である。

【0146】

図 22 は、駆動回路 (その 8) の構成を示す図である。この図に示される駆動回路 (その 8) が図 19 に示した駆動回路 (その 7) と相違する主な点は、電圧切替器 300 における電圧選択器 350 に、印刷データ S I が供給される点である。

【0147】

この点について詳述すると、駆動回路 (その 8) における電圧選択器 350 は、データ d A (電圧  $Out$ ) に応じて選択信号 Sel-A、Sel-B、Sel-C、Sel-D のいずれかを H レベルで出力する点で駆動回路 (その 7) と同様であるが、印刷データ S I から容量性負荷の大きさを推定し、選択信号 Sel-A、Sel-B、Sel-C、Sel-D を、推定した容量性負荷の大きさに応じた遅延量で切り替える。

なお、電圧選択器 350 のおける推定は、例えば次のようなものである。

すなわち、電圧選択器 350 は、選択制御部 510 (図 6 参照) におけるシフトレジスタ 512 およびラッチ回路 514 と同様な回路によって、制御部 110 からの制御信号 C tr に含まれる印刷データ S I をラッチするとともに、当該ラッチした印刷データ S I を解析

10

20

30

40

50

し、印刷周期  $T_a$  の期間  $T_1$ 、 $T_2$  のそれぞれにおいて駆動信号  $C O M - A$  が一端に印加される圧電素子  $P_{zt}$  の個数を求ることによって容量性負荷の大きさを推定する。

また、ここでいう遅延量とは、選択信号の論理レベルを切り替えるタイミングでの遅れ時間をいう。

【0148】

駆動信号  $C O M - A$  を出力する駆動回路 120aにおいて、例えば、印刷周期  $T_a$  の期間  $T_1$  でヘッドユニット 3 における全ノズルで大または中ドットを形成する場合、駆動信号  $C O M - A$  がすべての圧電素子  $P_{zt}$  の一端に印加されるので、負荷が最大となる一方で、全ノズルで小ドットを形成または非記録とする場合であれば、駆動信号  $C O M - A$  が選択されないので、負荷が最小（ゼロ）となる。同様なことは、駆動信号  $C O M - B$  を出力する駆動回路 120bについても言うことができる。10

すなわち、駆動回路 120a (120b) における容量性の負荷は、印刷データ  $S I$  で規定される印刷内容によって大きく変動する。

【0149】

ノード  $N_2$  から圧電素子  $P_{zt}$  の一端までの経路には、フレキシブルフラットケーブル 190 (図 1 参照) や選択部 520 のトランスマルチплексор 524a、524b (図 8 参照) が含まれるので、インダクタンス成分や抵抗成分などが存在する。

このため、圧電素子  $P_{zt}$  の容量や、インダクタンス成分、抵抗成分などで形成される積分回路によって、最終的に圧電素子  $P_{zt}$  の一端に印加される駆動信号  $C O M - A$  ( $C O M - B$ ) の波形が鈍る。この波形の鈍りの程度は、選択される圧電素子  $P_{zt}$  の個数が多くなるにつれて、すなわち容量性負荷が大きくなるにつれて、酷くなり（大きくなり）、信号  $A_{in}$  ( $B_{in}$ ) に対して、圧電素子  $P_{zt}$  の一端に印加される駆動信号  $C O M - A$  ( $C O M - B$ ) が遅延することになる。20

このため、駆動信号  $C O M - A$  ( $C O M - B$ ) の遅延を想定していない構成では、当該駆動信号  $C O M - A$  ( $C O M - B$ ) の目標電圧と電圧切替器 300 で選択される電圧セットとが不整合となり、波形を歪ませる可能性が高くなる。

【0150】

駆動回路（その 8）では、電圧選択器 350 が、選択信号  $Sel - A$ 、 $Sel - B$ 、 $Sel - C$ 、 $Sel - D$  の遅延量を、制御信号  $C tr$  に含まれる印刷データ  $S I$  から推定される容量性負荷が大きくなるにつれて大きくなる。このため、電圧セットが、駆動信号  $C O M - A$  ( $C O M - B$ ) の遅延に合わせて切り替えられるので、上記不整合が是正される結果、波形歪みを抑えることができる。30

【0151】

なお、切替の遅延については、電圧セットを切り替える場合を例にとって説明したが、トランジスター対を切り替える駆動回路（その 4、その 5、その 6）にも適用可能である。駆動回路（その 4、その 5、その 6）に適用する場合、特に図示しないが、例えばセレクター 280 に印刷データ  $S I$  を供給して、当該セレクター 280 が、当該印刷データ  $S I$  から容量性負荷の大きさを推定して、イネーブルするゲートセレクターを切り替えるタイミングを遅延させる構成とすれば良い。

【0152】

上述したように、駆動回路 120a (120b) における容量性負荷は、印刷データ  $S I$  で規定される印刷内容によって大きく変動する。一方で、駆動回路 120a (120b) においては、ノード  $N_2$  における電圧  $Out$  が差動增幅器 221 の正入力端 (+) に帰還される構成となっているので、上記負荷の変動によって位相回転量が大きく変化し、条件次第で異常発振することになり、安定性に欠ける。

そこで、この点を改善した駆動回路（その 9）について説明する。なお、この駆動回路（その 9）が適用される印刷装置は、図 21 で示した印刷装置（その 4）であり、印刷データ  $S I$  を含む制御信号  $C tr$  が駆動回路 120a、120b に供給される構成となっている。

【0153】

50

図23は、駆動回路（その9）の構成を示す図である。この図に示される駆動回路（その9）が図22に示した駆動回路（その8）構成と相違する点は、印刷データSIを含む制御信号Ctrが電圧切替器300ではなく、単位回路200に供給される点である。

#### 【0154】

図24は、駆動回路（その9）における単位回路200の構成を示す図である。この図に示される単位回路が図22に示した単位回路と相違する点は、解析部260およびスイッチSwcを有する点である。

スイッチSwcは、コンデンサーC0の他端とグランドGndとの間に介挿されて、解析部260から出力される信号SctrがHレベルであればオンし、当該信号SctrがLレベルであればオフする。なお、スイッチSwcは、ノードN2とコンデンサーC0の一端との間に介挿されても良い。

#### 【0155】

解析部260は、第1に、制御部110からの制御信号Ctrに含まれる印刷データSIをラッチし、第2に、当該ラッチした印刷データSIを解析し、印刷周期Taの期間T1、T2のそれぞれにおいて駆動信号COM-Aが一端に印加される圧電素子Pztの個数を求めて、当該個数に応じて信号Sctrを出力する。具体的には、解析部260は、例えば期間T1（T2）において駆動信号COM-Aが一端に印加される圧電素子Pztの個数が、例えば「0」から「m/2」（mの半分）までの範囲にあれば、タイミング信号で規定される当該期間T1（T2）において信号SctrをHレベルで出力し、当該圧電素子Pztの個数がそれ以外の範囲にあれば、信号SctrをLレベルで出力する。

ここで、信号SctrがHレベルであれば、スイッチSwcがオンするので、コンデンサーC0の他端がグランドGndに電気的に接続（有効化）されて、圧電素子Pztと並列化される。一方、信号SctrがLレベルであれば、スイッチSwcがオフするので、コンデンサーC0の他端がグランドGndから切り離されて、当該コンデンサーC0が無効化される。

#### 【0156】

1個のヘッドユニット3におけるm個の圧電素子Pztを仮にすべて並列接続したときの容量を10Cとしたとき、ノードN2に一端が接続される圧電素子Pztの個数は、印刷データSIに応じて「0」から「m」まで変化する。このとき、ノードN2からみた、容量性負荷としての圧電素子Pztの容量は、0Cから10Cまでの範囲で変化する。

#### 【0157】

ここで、駆動回路（その9）におけるコンデンサーC0の容量を便宜的に5Cとしてみる。

例えば駆動信号COM-Aを出力する駆動回路120aでみると、印刷周期Taの期間T1において駆動信号COM-Aが一端に印加される圧電素子Pztの個数が0からm/2（mの半分）までの範囲である場合、圧電素子Pztの容量は0Cから5Cまでの範囲で変動する。この場合、解析部260は信号SctrをHレベルとするので、スイッチSwcがオンして、容量5CのコンデンサーC0が圧電素子Pztに対して並列接続となる。このため、ノードN2からみた容量性負荷の総和は、5Cから10Cまでの範囲となる。

#### 【0158】

一方、期間T1において駆動信号COM-Aが印加される圧電素子Pztの個数がm/2からmまでの範囲である場合、圧電素子Pztの容量は5Cから10Cまでの範囲で変動する。この場合、解析部260は信号SctrをLレベルとするので、スイッチSwcがオフして、コンデンサーC0は圧電素子Pztに対して並列接続されない。このため、ノードN2からみた容量性負荷の総和については、5Cから10Cまでの範囲となる。

#### 【0159】

したがって、駆動回路（その9）によれば、ある期間において駆動信号COM-Aが一端に印加される圧電素子Pztの個数が0からmまで変動しても、ノードN2からみた容量性負荷は、5Cから10Cまでの範囲でしか変動しないので、上記位相回転量の変化の影響が小さくなり、駆動回路の安定化を図ることが容易となるのである。

10

20

30

40

50

なお、ここでは駆動回路 120a についてみたが、駆動回路 120b について同様であり、駆動信号 COM-B が印加される圧電素子 Pzt の個数が変動しても、ノード N2 からみた容量性負荷の変動を抑えることができる。

#### 【0160】

コンデンサー C0 の容量値の設定にあたっては、圧電素子 Pzt の容量値や個数 m だけではなく、トランジスター 231、232 におけるソース・ドレイン間の抵抗や、配線抵抗、インダクタンス成分、駆動信号 COM-A (COM-B) の周波数などが考慮される。

なお、図 24 の例では、コンデンサー C0 を 1 個としたが、2 個以上としても良い。具体的には、複数個のコンデンサーのそれぞれを、スイッチを介して圧電素子 Pzt に対して並列接続する一方で、駆動信号が一端に印加される圧電素子 Pzt の個数が多くなるにつれて、オフするスイッチ SW の個数を段階的に増加させる構成とすれば良い。

10

#### 【0161】

なお、コンデンサー C0 を有効化または無効化する技術については、図 10、図 12A、図 12B、図 14A、図 14B、図 18、図 20、後述する図 25、図 29、図 31、図 32 にも適用可能である。

#### 【0162】

駆動回路 (その 7、その 8、その 9) において、電源電圧のセット数をそれぞれ「4」としたが、「2」以上であれば良い。また、駆動回路 (その 7、その 8、その 9) において、各セットの電源電圧を不揃いとした構成でも良いし、電圧範囲のうち隣り合う範囲については一部重複させた構成でも良いし、電圧選択器 350 がデータ dA (dB) ではなく、アナログ変換後の信号 ain (bin) で判別する構成でも良い。

20

#### 【0163】

ところで、図 14A に示した駆動回路 (その 4) および図 14B に示した駆動回路 (その 5) における差動増幅器 221 や、セレクター 223 は、電源として比較的低電圧を用いることができる。このため、差動増幅器 221 やセレクター 223 を構成するトランジスター等の耐圧も低振幅の電源に合わせて低く設計できる。一方、ノード N2 の電圧 Out1 は最高で 40V 程度であり高振幅である。したがって、耐圧の低い差動増幅器 221 に、高振幅の電圧 Out1 を直接帰還することができないので、駆動回路 (その 4、その 5) では、電圧 Out1 を抵抗素子 R1、R2 で分圧し、当該分圧した電圧 Out1 を差動増幅 221 に帰還する構成となっている。

30

#### 【0164】

差動増幅器 221 の回路構成そのものは、良く知られたものであり、簡略的いえば、入力端 (+) が、構成素子であるトランジスターのうち、1 つのトランジスターのゲートに接続された構成である。このため、入力端 (+) には、少なからず容量成分が寄生するので、当該寄生する容量成分と抵抗素子 R1 とにより CR フィルタが形成されて、帰還経路に一次遅れ (ディレイ) が発生する。このようなディレイは、時間的に長くなるにつれてトランジスター対でのスイッチング周波数を低下させる方向に働いて、駆動信号 COM-A (COM-B) の波形再現性を悪化させる。

#### 【0165】

そこで次に、この点を改善した駆動回路 (その 10) について説明する。なお、駆動回路 (その 10) を含む印刷装置の電気的な構成を示すブロック図については、図 13 の印刷装置 (その 2) と同様である。

40

#### 【0166】

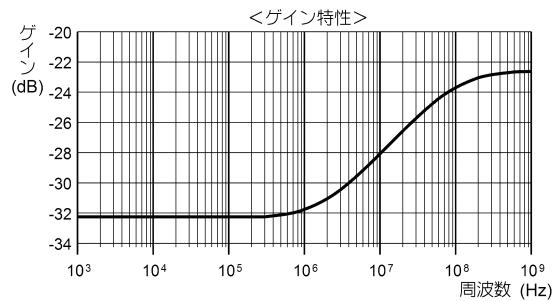

図 25 は、駆動回路 (その 10) の構成を示す図である。この図に示される駆動回路 (その 10) が図 14B に示した駆動回路 (その 5) と相違する点は、コンデンサー C1、C2 を有する点である。詳細には、駆動回路 (その 10) では、コンデンサー C1 が抵抗素子 R2 に対して並列に接続されるとともに、コンデンサー C2 が抵抗素子 R1 に対して並列に接続されて微積回路を構成している。すなわち、分圧のための抵抗素子 R1、R2 を用いつつ、コンデンサー C1、C2 を設けた微積回路によって、上記帰還経路における位相遅れを補償する構成となっている。

50

この微積回路における特性の具体例について説明する。

【0167】

図26は、微積回路における周波数 - ゲイン特性の一例を示す図であり、図27は、微積回路における周波数 - 位相特性の一例を示す図である。

なお、図27において縦軸は、位相(度)であり、周波数が10MHz付近をピークにして位相が相対的に進んでいることを示している。したがって、微積回路では、トランジスター対がスイッチングする周波数帯にわたって位相が進むので、帰還経路における位相遅れが補償される。

【0168】

なお、上述した例では、ノードN2における電圧Out1を1/10倍にしてノードN3に帰還するので、抵抗素子R1、R2の抵抗比は9:1となるが、この特性の説明では、次に説明するように、抵抗比を40:1としているので、微積回路のゲインは、トランジスター対がスイッチングしない区間ににおいて-32.25dB(0.0244倍)となっている。

10

【0169】

次に、上記微積回路における特性について検討する。

図25における微積回路を、入力側を左側に、出力側を右側にそれぞれ書き改めると、図28に示される通りとなり、抵抗素子R1とコンデンサーC2との並列接続と、抵抗素子R2とコンデンサーC1との並列接続とで表現することができる。

【0170】

20

抵抗素子R1とコンデンサーC2との並列インピーダンスZ1は、次式(1)で表すことができる。

【数1】

$$\begin{aligned} Z1 &= \frac{1}{\frac{1}{R1} + j\omega C2} \\ &= \frac{1}{1 + j\omega R1C2} \cdots (1) \end{aligned}$$

30

【0171】

また、抵抗素子R2とコンデンサーC1との並列インピーダンスZ2は、次式(2)で表すことができる。

【数2】

$$\begin{aligned} Z2 &= \frac{1}{\frac{1}{R2} + j\omega C1} \\ &= \frac{1}{1 + j\omega R2C1} \cdots (2) \end{aligned}$$

40

【0172】

ノードN2を入力とし、ノードN3を出力とした微積回路のゲインGについては、次式(3)で表すことができる。

## 【数3】

$$G = \frac{Out2}{Out1} = \frac{Z2}{Z1+Z2} = \frac{1}{\frac{Z1}{Z2} + 1}$$

$$= \frac{1}{\frac{R1(1+j\omega R2C1)}{R2(1+j\omega R1C2)} + 1} \quad \cdots (3)$$

10

## 【0173】

式(3)の虚数部分については  $R2C1 = R1C2$  とおいて除去することにより、次式(4)で表すことができる。

## 【数4】

$R2C1=R1C2$  であれば、

$$G = \frac{R2}{R1+R2} \quad \cdots (4)$$

20

## 【0174】

なお、式(4)で表されるゲイン  $G$  は、抵抗素子  $R1$ 、 $R2$  による分圧そのものであり、電圧  $Out2$  に対して電圧  $Out1$  を小さくするためには、 $R1 > R2$  とする必要がある。

## 【0175】

駆動回路(その10)によれば、ノード  $N2$  からノード  $N3$  までの抵抗素子  $R1$  を介した帰還経路と、差動増幅器  $221$  に寄生する容量成分とで生じるディレイは、当該抵抗素子  $R1$  のほか、抵抗素子  $R2$ 、コンデンサー  $C1$ 、 $C2$  で構成される微積回路によって補償されるので、トランジスター対の動作周波数を低下させないで済む。このため、駆動信号  $COM-A$  ( $COM-B$ ) の波形再現性の悪化を抑えることができる。

また、ノード  $N2$  には、異常発振防止用のコンデンサー  $C0$  が接続されるが、このコンデンサー  $C0$  は、ノード  $N2$  からみたときに負荷になるので、無駄に電力が消費される原因の1つとなる。コンデンサー  $C0$  の容量を小さくすれば、無駄な消費電力を抑えることができるが、コンデンサー  $C1$ 、 $C2$  が存在しない構成では、異常発振の可能性が高くなる。これに対して、本実施形態によれば、コンデンサー  $C1$ 、 $C2$  を含む微積回路によって、異常発振を抑えた上でコンデンサー  $C0$  の容量を小さくすることができるので、低消費電力化を図ることが可能になる。

30

## 【0176】

次に、駆動回路(その10)の応用・変形例である駆動回路(その11)について説明する。

## 【0177】

40

図29は、駆動回路(その11)を示す図である。この図に示されるように、駆動回路(その11)では、ノード  $N2$  と抵抗素子  $R1$  と間に、電圧  $Out2$  に所定係数を乗算する演算増幅器  $290$  (バッファアンプ)が設けられる。このように演算増幅器  $290$  を設けた構成によれば、ノード  $N2$  の電圧  $Out2$  が抵抗素子  $R1$ 、 $R2$  を介したリーキによって低下してしまうのを防止することができる。

## 【0178】

上述したように、ノード  $N2$  を、抵抗素子  $Ru$  でプルアップするとともに、抵抗素子  $Rd$  でプルダウンする構成では、貫通電流が流れてしまうので、図12A、図14A、図25で示した構成では、抵抗素子  $Ru$  を無効化させるスイッチ  $Swu$  が設けられ、また、図12B、図14B、図18、図20に示した構成では、さらに抵抗素子  $Rd$  を無効化させ

50

るスイッチ S w d が設けられる一方で、スイッチ S w u のオンオフは信号 O C a にしたがって制御され、スイッチ S w d のオンオフは信号 O C a の論理レベルを NOT 回路 291 により反転した信号にしたがって制御される構成であった。

ただし、信号 O C a の本来の役目は、セレクター 223 における選択の指示であって、スイッチ S w u、 S w d におけるオンオフの制御ではない。また、スイッチ S w u、 S w d や、 NOT 回路 291 などで遅延が発生すると、貫通電流が一時的に流れる可能性もある。

そこで次に、この点を改善した駆動回路（その 12）について説明する。

#### 【0179】

図 30 は、駆動回路（その 11）を含む印刷装置（その 5）の電気的な構成を示すプロック図である。この図に示される印刷装置（その 5）が、図 13 に示した印刷装置（その 2）と相違する点は、制御部 110 が、信号 P u a、 P d a を駆動回路 120a に供給するとともに、信号 P u b、 P d b を駆動回路 120b に供給する点である。 10

#### 【0180】

信号 P u a は、例えば駆動信号 C O M - A (信号 a in) が閾値 V th よりも低い電圧で一定となる期間 P 2、 P 6 (図 11 参照) で H レベルとなり、それ以外の期間 P 1、 P 3 ~ P 5 で L レベルとなる。また、信号 P d a は、駆動信号 C O M - A が閾値 V th 以上高い電圧で一定となる期間 P 4 で H レベルとなり、それ以外の期間 P 1 ~ P 3、 P 5 で L レベルとなる。

信号 P u b は、駆動信号 C O M - B (信号 b in) が閾値 V th よりも低い電圧で一定となる期間で H レベルとなり、それ以外の期間で L レベルとなる。また、信号 P d b は、駆動信号 C O M - B が閾値 V th 以上高い電圧で一定となる期間で H レベルとなり、それ以外の期間で L レベルとなる。 20

#### 【0181】

図 31 は、駆動回路（その 12）の構成を示す図である。この図に示される駆動回路（その 12）が図 14B に示した駆動回路（その 5）と相違する主な点は、スイッチ S w u のオンオフが信号 P u a にしたがって制御される点、および、スイッチ S w d のオンオフが信号 P d a にしたがって制御される点である。

#### 【0182】

駆動回路（その 12）によれば、駆動信号 C O M - A を出力する側でいえば、スイッチ S w u は、期間 P 2、 P 6 だけオンし、スイッチ S w d は期間 P 4 だけオンするので、抵抗素子 R u、 R d を介して貫通電流が流れるのを防止することができる。 30

#### 【0183】

なお、駆動信号 C O M - A を出力する駆動回路において、期間 P 2、 P 6 は、上述したようにトランジスター 232 がリニア動作となる場合である。この場合、トランジスター 231 がオフになっているので、トランジスター 232 によってノード N 2 の電圧 Out を電圧 a in に追従させるためには、ノード N 2 を抵抗素子 R u によってプルアップする必要があるが、それ以外の期間 P 1、 P 3 ~ P 5 では、ノード N 2 をプルアップする必要は特にならない。

一方、期間 P 4 は、トランジスター 231 がリニア動作となる場合である。この場合、トランジスター 232 がオフになっているので、トランジスター 231 によってノード N 2 の電圧 Out を電圧 a in に追従させるためには、ノード N 2 を抵抗素子 R d によってプルダウンする必要がある。ただし、それ以外の期間 P 1 ~ P 3、 P 5 では、ノード N 2 をプルダウンする必要は特にならない。 40

したがって、駆動回路（その 12）によれば、抵抗素子 R u によるプルアップ、および、抵抗素子 R d によるプルダウンを、それぞれ必要な期間だけ機能させている構成ということができる。

#### 【0184】

またここでは、駆動回路（その 12）として駆動信号 C O M - A を出力する側を例にとつて説明したが、駆動信号 C O M - B を出力する駆動回路 120b であれば、図 32 の括 50

弧書きで示されるように、スイッチ  $S_{w\,u}$  のオンオフが信号  $P_{u\,b}$  で制御され、スイッチ  $S_{w\,d}$  のオンオフが信号  $P_{d\,b}$  で制御される構成となる。

【0185】

なお、信号  $P_{u\,a}$  ( $P_{u\,b}$ )、 $P_{d\,a}$  ( $P_{d\,b}$ ) については、信号  $O\,C\,a$  ( $O\,C\,b$ ) と同様に、データ  $d\,A$  ( $d\,B$ ) についての離散値と、当該離散値の時間的な連続性を解析することで、制御部 110 以外の構成で生成することが可能である。

【0186】

また、図 25 の駆動回路 (その 10)、図 29 の駆動回路 (その 11) および図 31 の駆動回路 (その 12) においては、データ  $d\,A$  ( $d\,B$ ) をアナログ変換し、信号  $a\,in$  ( $b\,in$ ) として差動増幅器 221 の負入力端 (-) に供給する  $D\,A\,C\,2\,9\,3$  を設けても良い。

10

図 32 は、駆動回路 (その 12) に  $D\,A\,C\,2\,9\,3$  を設けた駆動回路 (その 13) を示す図である。駆動回路 (その 10、その 11) に  $D\,A\,C\,2\,9\,3$  を設けた例についての図示は省略する。

【0187】

以上の説明では、トランジスター対のうち、トランジスター 231 を P チャネル型とし、トランジスター 232 を N チャネル型としたが、トランジスター 231、232 を P チャネル型または N チャネル型で揃えても良い。ただし、差動増幅器 221 による出力信号や、信号  $O\,C\,a$  ( $O\,C\,b$ ) によってオフさせられるときのゲート信号などを適宜合わせる必要がある。

【0188】

また、駆動回路 (その 1、その 2、その 3) や、駆動回路 (その 7、その 8、その 9) の単位回路 200 において、ノード N2 からトランジスター 231 のドレイン端子に向かう電流を阻止するためのダイオード、および、トランジスター 232 のドレイン端子からノード N2 に向かう電流を阻止するためのダイオードをそれぞれ設けても良い。

20

【0189】

上記説明では、液体吐出装置を印刷装置として説明したが、液体を吐出して立体を造形する立体造形装置や、液体を吐出して布地を染める捺染装置などであっても良い。

【0190】

また、駆動回路については、メイン基板 100 に設けたが、駆動 I C 50 とともにキャリッジ 20 (またはヘッドユニット 3) に設ける構成としても良い。ヘッドユニット 3 の側に駆動回路を設けると、大振幅の信号を、フレキシブルフラットケーブル 190 を介して供給する必要がなくなるので、耐ノイズ性を高めることができる。

30

【0191】

さらに、上記説明では、駆動回路 120a ( $120\,b$ ) の駆動対象としてインクを吐出するための圧電素子  $P_{zt}$  を例にとって説明したが、駆動回路 120a ( $120\,b$ ) を印刷装置から切り離して考えてみたときに、駆動対象としては、圧電素子  $P_{zt}$  に限られず、例えば超音波モーターや、タッチパネル、静電スピーカー、液晶パネルなどの容量性成分を有する負荷のすべてに適用可能である。

【符号の説明】

【0192】

1 ... 印刷装置 (液体吐出装置)、3 ... ヘッドユニット、100 ... メイン基板、120a、120b ... 駆動回路、200 ... 単位回路、221 ... 差動増幅器、223 ... セレクター、231、231a、231b、231c、231d、232、232a、232b、232c、232d ... トランジスター、270a、270b、270c、270d ... ゲートセレクター、280 ... セレクター、270a、270b、270c、270d ... ゲートセレクター、280 ... セレクター、290 ... 演算増幅器、442 ... キャビティ、 $P_{zt}$  ... 圧電素子、N ... ノズル、R1、R2、Ru、Rd ... 抵抗素子、C1、C2 ... コンデンサー、 $S_{w\,u}$ 、 $S_{w\,d}$  ... スイッチ。

40

50

【図1】

【図2B】

【図2A】

【図3】

【図4】

【図5】

【図6】

【図7】

&lt;デコーダーのデコード内容&gt;

| 印刷データ<br>SI      | T1 |    | T2 |    |

|------------------|----|----|----|----|

|                  | Sa | Sb | Sa | Sb |

| 大ドット<br>→ (1, 1) | H  | L  | H  | L  |

| 中ドット<br>→ (0, 1) | H  | L  | L  | H  |

| 小ドット<br>→ (1, 0) | L  | L  | L  | H  |

| 非記録<br>→ (0, 0)  | L  | H  | L  | L  |

MSB

LSB

【図8】

【図10】

【図9】

【図 1 1】

【図 1 2 A】

【図 1 2 B】

【図 1 3】

【図 14 A】

【図 14 B】

【図 15】

【図 16】

【図 17】

【図18】

【図19】

【図20】

【図21】

【図2-2】

【図2-3】

【図2-4】

【図2-5】

【図26】

【図28】

【図27】

【図29】

【図30】

### 【図31】

【 図 3 2 】

---

フロントページの続き

(56)参考文献 特開2015-164779(JP,A)

特開2003-289227(JP,A)

米国特許第06388477(US,B1)

(58)調査した分野(Int.Cl., DB名)

B41J2/015-2/16

2/205

H03F3/217