#### (19) World Intellectual Property Organization

International Bureau

(43) International Publication Date 29 December 2005 (29.12.2005)

**PCT**

# (10) International Publication Number WO 2005/122695 A2

(51) International Patent Classification: Not classified

(21) International Application Number:

PCT/IL2005/000650

(22) International Filing Date: 19 June 2005 (19.06.2005)

(25) Filing Language: English

(26) Publication Language: English

(**30**) Priority Data: 162650

21 June 2004 (21.06.2004) IL

- (71) Applicant (for all designated States except US): CAMTEK LTD. [IL/IL]; Ramat Gavriel Industrial Zone, P.O. Box 544, 23150 Migdal HaEmek (IL).

- (72) Inventor; and

- (75) Inventor/Applicant (for US only): DERY, Nir [IL/IL]; 103/1 Avital Street, -, 20692 Yoqneam Ilit (IL).

- (74) Agent: PINK, Yakov; 34 Ben Yehuda Street, City Tower 16th Floor, 94230 Jerusalem (IL).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RU, SC, SD, SE, SG, SK, SL, SM, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, YU, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IS, IT, LT, LU, MC, NL, PL, PT, RO,

[Continued on next page]

#### (54) Title: A SYSTEM FOR MAPPING DEFECTIVE PRINTED CIRCUITS

A scrap-units-mapping system (57) Abstract: is disclosed. The system is especially designed for mapping a multi-layers PCB that contains a plurality of PCBs. The disclosed system comprised of an optical inspection system that scans each layer - both sides - of identified layers, that are intended to create a specific PCB, and marks the scrap-units on a layer map; a storage mean to store the layer maps, using any method for storing layers' information; and a combining software that combines the layer maps to create a PCB map, wherein each scrap-unit, which one of its' layers has a defect, is marked. Moreover, the system can further includes an optimization software that matches plurality of layer maps of each terrace-layer of the PCB and define sets of identified layers to join into a PCB with minimum scrap-units, enabling to collect each of the defined sets to join into a PCB.

# WO 2005/122695 A2

SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### Published:

without international search report and to be republished upon receipt of that report

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

Title: A System for Mapping Defective Printed Circuits

5

### FIELD OF THE INVENTION

The present invention relates to the field of automatic optical inspection systems and methods. More specifically, the present invention relates to a system and method for mapping PCBs.

10

#### BACKGROUND OF THE INVENTION

Automatic optical inspection systems use image processing and dedicated algorithms to inspect the surfaces of a PCB or a wafer in order to recognize defects on this surface.

15

PCBs are usually made in a way of manufacturing a single board that contains a plurality of PCBs. The production and all the whole process is done on the single board and then the single board is cut to the PCBs.

Large number of units (PCBs) can be produced on a single board and any number of them could be defective and known as "scrap-units". A single defect in one of the unit's layer is enough in order to disqualify the unit. Since the processes are done on a board scale (not on a unit scale), it is very important to identify in process the scrap-units and therefore prevent any work and material investment on a scrap-unit.

5

10

The present invention can be use either the PCB is produced using "built-up" method or "lamination" method. "Built-up" is the method in which each layer is build directly on the lower layer and "lamination" is the method in which each layer is produced individually and the layer are collected and joined into a PCB by pressure or lamination.

Therefore, it would be advantageous to have a system and a method, which uses the inspection platform to create a scrap-units map of each specific board.

The present invention makes use, in a preferred embodiment, in "a method for storing layers' information of a layers-made object", which is

patent pending and internationally published on October 2, 2003 having the publication number WO 03/081535 A1.

# SUMMARY OF THE INVENTION

The present invention is a scrap-units-mapping system and method, especially for mapping a multi-layers board that contains a plurality of PCBs.

According to the teachings of the present invention there is provided a scrap-units-mapping system that includes:

- a) an optical inspection system that scans each layer both sides of identified layers, that are intended to create a specific PCB, and marks the scrap-units on a layer map;

- b) a storage mean to store the layer maps, using any method for

storing layers' information; and

- c) combining software that combines the layer maps to create a PCB map, wherein each scrap-unit, which one of its' layers has a defect, is marked.

According to further features in the described preferred embodiment of the present invention, there is provided a scrap-units-mapping system that further includes:

- d) an optimization software that matches plurality of layer maps of each terrace-layer of the PCB and define sets of identified layers to join into a PCB with minimum scrap-units, enabling to collect each of defined sets to join into a PCB.

- e) a mechanism that collects, according to the optimization results, sets of the identified layers to join into PCBs

10

5

According to another preferred embodiment of the present invention, there is provided the scrap-units-mapping system further includes a display for displaying the PCB map.

In another preferred embodiment, there is provided the scrapunits-mapping system, wherein the scrap-units on the PCB map are marked in colors wherein each color defines the layer location of the defect.

In yet another preferred embodiment, there is provided the scrapunits-mapping system, wherein the method for storing layers' information is the method that is defined in the international publication WO 03/081535 A1.

5

According to yet another aspect of the present invention there is provided a method for scrap-units-mapping, especially for mapping a multi-layers board that contains a plurality of PCBs, including the following steps:

- a) scanning by an optical inspection system each layer both sides of identified layers that are intended to create a specific PCB and marking the scrap-units on a layer map;

- b) storing the layer maps, using any method for storing layers' information; and

- 15 c) combining said layer maps to create a PCB map, wherein each scrap-unit, which one of its' layers is defective, is marked.

The method, according to the present invention, is also provided with the additional following steps:

d) matching, by using an optimization software, plurality of layer maps of each terrace-layer of said PCB and define sets of identified layers to join into a PCB with minimum scrap-units; and

e) collecting, according to the optimization results, sets of the identified layers to join into PCBs.

The method, according to the present invention, is also provided, further includes the step of coloring the scrap-units on the PCB map by colors, wherein each color defines the defective layer.

10

5

The method, according to the present invention, is also provided, wherein storing layers' information method, as is defined in the international publication WO 03/081535 A1, is used.

The present invention successfully addresses the shortcomings of the existing technologies by providing system and method for scrap-units mapping on a PCB.

# BRIEF DESCRIPTION OF THE FIGURES

The invention is herein described, by way of example only, with reference to the accompanying drawings. With specific reference now to the drawings in detail, it is stressed that the particulars shown are by way of example and for purposes of illustrative discussion of the preferred embodiments of the present invention only, and are presented in the cause of providing what is believed to be the most useful and readily understood description of the principles and conceptual aspects of the invention. In this regard, no attempt is made to show structural details of the invention in more detail than is necessary for a fundamental understanding of the invention, the description taken with the drawings making apparent to those skilled in the art how the several forms of the invention may be embodied in practice.

In the figures:

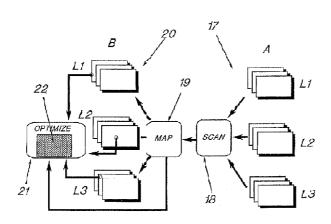

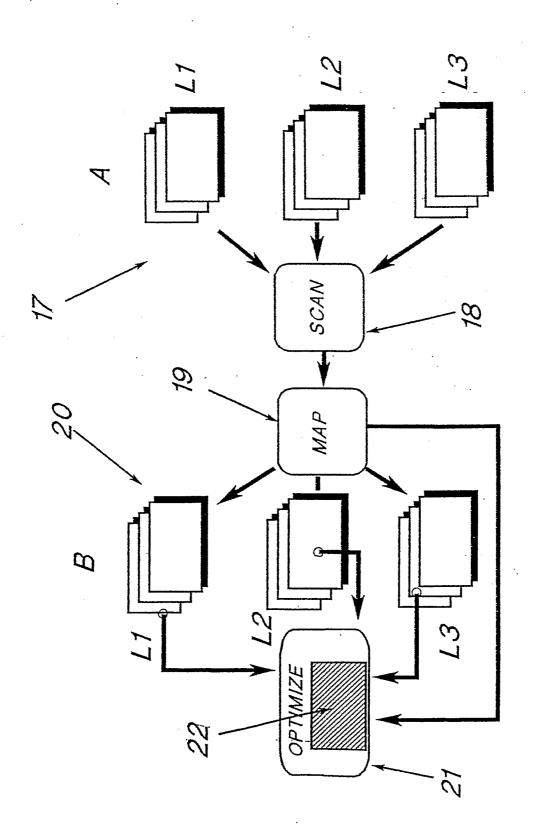

Figure 1 illustrates a flow chart of a preferred embodiment of the present invention, using "lamination" method of production.

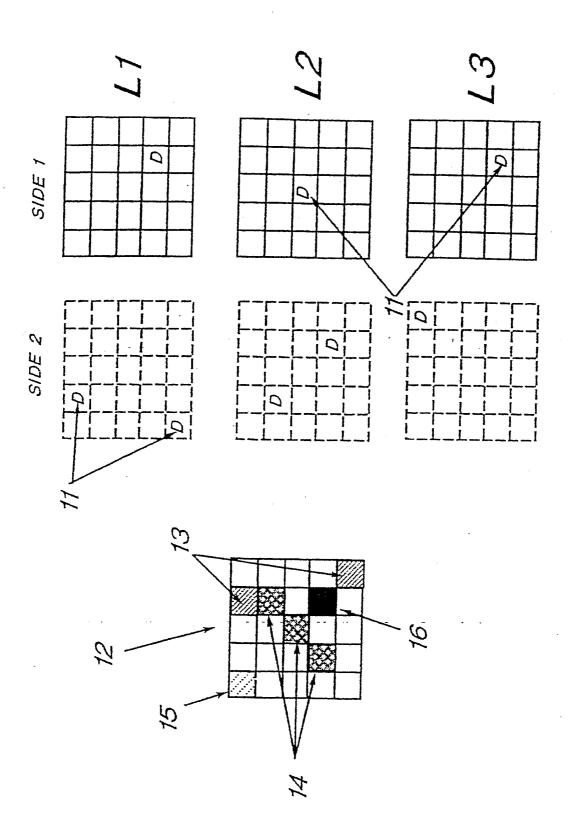

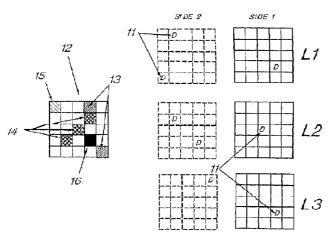

Figure 2 illustrates the mapping method, according to the present invention, using an example of two-sided and three layers board with 25 PCBs.

5

10

## DESCRIPTION OF THE PREFERED EMBODIMENTS

The present invention is a scrap-units-mapping system and method, especially for mapping a multi-layers board that contains a plurality of PCBs.

5

The system, according to the present invention, uses scanned images of the layers of a specific PCB. On each layer there are scrapunits that could be identify. Actually, the scanned image is a map of scrap-units of a single side of a single layer.

10

The system combines these maps to create a map that illustrates the scrap-units location on the PCB that will be produced from these layers. When the PCB production is finished, this map can be used for the further process of this PCB (e.g. drilling).

15

When using "lamination" method to produce a PCB, optimizing software can be used that selects, for each layer, a specific layer from a plurality of layers of the same kind in order to produce a PCB with minimum scrap-units.

The principles and operation of the system according to the present invention may be better understood with reference to the drawing and the accompanying description.

5

10

15

Referring now to the drawing, Figure 1 illustrates a flow chart of a preferred embodiment of the present invention, using "lamination" method of production. Three layers groups "A" 17, L1, L2 and L3 are input to be scanned in the scan unit 18. The images pass to the mapping unit 19 that create maps for each layer. The layers 20 pass to an output place "B" and the maps are passed to the optimize unit 21. The optimize unit and software 21 decided - in order to have a PCB with minimum scrap-units - to select the third layer of L1 to be the first layer of the PCB, the first layer of L2 to be the second layer and the second layer of L3 to be the last layer of the PCB. The optimize unit 21 collect the layers, according to its' decision and creates a PCB 22 with minimum scrap-units and creates a compatible map that marks the scrap-units to be used in the further process.

Figure 2 illustrates the mapping method, according to the present invention, using an example of two-sided and three layers board with twenty-five PCBs.

Each of the three layers of the board is scanned, having images of side 1 and side 2 of each layer L1, L2 and L3. The scrap-units 11 are marked (in the illustration by "D"). The system combines the images into a map 12, which marks the location of the scrap-units with colors that identify the defect's layer location, the defects of L1 13, the defects of layer L2 14, the defects of layer L3 15 and multi-layers defects 16.

As used herein in the specification and in the claims section that follows, the term "scrap-unit" and the like refer to the disqualify PCB-unit on a single board that contains plurality of PCBs.

15

20

10

5

Although the invention has been described in conjunction with specific embodiments thereof, it is evident that many alternatives, modifications and variations will be apparent to those skilled in the art, accordingly, it is intended to embrace all such alternatives, modifications and variations that fall within the spirit and broad scope of the appended claims.

## WHAT IS CLAIMED IS:

A scrap-units-mapping system, especially for mapping a multilayers PCB that contains a plurality of PCBs, said system comprising:

- a) an optical inspection system that scans each layer both sides

of identified layers, that are intended to create a specific

PCB, and marks the scrap-units on a layer map;

- b) a storage mean to store said layer maps, using any method for storing layers' information; and

- c) combining software that combines said layer maps to create a PCB map, wherein each scrap-unit, which one of its' layers has a defect, is marked.

- 2. The scrap-units-mapping system of claim 1, further includes:

- d) an optimization software that matches plurality of layer maps of each terrace-layer of said PCB and define sets of identified layers to join into a PCB with minimum scrap-units, enabling to collect each of said defined sets to join into a PCB.

3. The scrap-units-mapping system of claim 2, further includes:

- e) a mechanism that collects, according to said optimization results, sets of said identified layers to join into PCBs.

- 4. The scrap-units-mapping system of claim 1, further includes a display for displaying said PCB map.

- 5. The scrap-units-mapping system of claim 1, wherein the scrapunits on said PCB map are marked in colors wherein each color defines the layer location of said defect.

- 6. The scrap-units-mapping system of claim 1, wherein said method for storing layers' information is the method that is defined in the international publication WO 03/081535 A1.

- 7. A scrap-units-mapping method, especially for use for mapping a multi-layers PCB that contains a plurality of PCBs, said method comprising:

a) scanning by an optical inspection system each layer – both sides – of identified layers that are intended to create a specific PCB and marking the scrap-units on a layer map;

- b) storing said layer maps, using any method for storing layers' information; and

- c) combining said layer maps to create a PCB map, wherein each scrap-unit, which one of its' layers is defective, is marked.

- 8. The method of claim 7, further includes:

- d) matching, by using an optimization software, plurality of layer maps of each terrace-layer of said PCB and define sets of identified layers to join into a PCB with minimum scrap-units; and

- e) collecting, according to said optimization results, sets of said identified layers to join into a PCBs.

- 9. The method of claim 7, further coloring the scrap-units on said PCB map by colors, wherein each color defines the defective layer.

10. The method of claim 7, wherein storing layers' information method, as is defined in the international publication WO O3/O81535 A1, is used.

FIGURE 1

1/2

FIGURE 2

2/2