(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5723153号

(P5723153)

(45) 発行日 平成27年5月27日(2015.5.27)

(24) 登録日 平成27年4月3日(2015.4.3)

(51) Int.Cl.

F 1

|             |           |            |      |

|-------------|-----------|------------|------|

| HO1L 23/12  | (2006.01) | HO1L 23/12 | 501C |

| HO1L 25/065 | (2006.01) | HO1L 25/08 | Z    |

| HO1L 25/07  | (2006.01) |            |      |

| HO1L 25/18  | (2006.01) |            |      |

請求項の数 16 (全 14 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2010-520232 (P2010-520232)  |

| (86) (22) 出願日 | 平成20年8月1日(2008.8.1)           |

| (65) 公表番号     | 特表2010-536178 (P2010-536178A) |

| (43) 公表日      | 平成22年11月25日(2010.11.25)       |

| (86) 國際出願番号   | PCT/US2008/071994             |

| (87) 國際公開番号   | W02009/045626                 |

| (87) 國際公開日    | 平成21年4月9日(2009.4.9)           |

| 審査請求日         | 平成23年8月1日(2011.8.1)           |

| 審判番号          | 不服2013-20138 (P2013-20138/J1) |

| 審判請求日         | 平成25年10月17日(2013.10.17)       |

| (31) 優先権主張番号  | 11/834,765                    |

| (32) 優先日      | 平成19年8月7日(2007.8.7)           |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                               |

|-----------|-----------------------------------------------------------------------------------------------|

| (73) 特許権者 | 595168543<br>マイクロン テクノロジー, インク.<br>アメリカ合衆国, アイダホ州 83716<br>-9632, ボイズ, サウス フェデ<br>ラル ウエイ 8000 |

| (74) 代理人  | 100106851<br>弁理士 野村 泰久                                                                        |

| (74) 代理人  | 100074099<br>弁理士 大菅 義之                                                                        |

| (72) 発明者  | ジャン, トンビ<br>アメリカ合衆国, アイダホ州 83713<br>, ボイズ, ウエスト ランニング ブルッ<br>ク ドライブ 12680                     |

最終頁に続く

(54) 【発明の名称】スルーボディ導電性ビアを備えたパッケージ化された集積回路デバイス、及び、それを製造する方法

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体デバイスであって、

アクティブ面と前記アクティブ面の反対側の裏面とを有する第1の半導体ダイと、

前記第1の半導体ダイを封入する第1の封入材であって、前記第1の封入材は前面と前記前面と反対側の裏面とを有し、前記第1の半導体ダイの前記アクティブ面は概して前記第1の封入材の前記前面と同一平面にあり、前記第1の半導体ダイの前記裏面は前記第1の封入材に埋め込まれる、という第1の封入材と、

前記第1の封入材の前記前面上に配置されて且つ前記第1の半導体ダイの前記アクティブ面と概して同一平面にある第1の導電性ラインと、

アクティブ面と前記アクティブ面の反対側の裏面とを有する第2の半導体ダイと、

前記第2の半導体ダイを封入する第2の封入材であって、前記第2の封入材は前面と前記前面と反対側の裏面とを有し、前記第2の半導体ダイの前記アクティブ面は概して前記第2の封入材の前記前面と同一平面にあり、前記第2の半導体ダイの前記裏面は前記第2の封入材に埋め込まれる、という第2の封入材と、

前記第2の封入材の前記前面上に配置されて且つ前記第2の半導体ダイの前記アクティブ面と概して同一平面にある第2の導電性ラインであって、前記第1の封入材の前記裏面が前記第2の封入材の前記裏面を向く、という第2の導電性ラインと、

前記第1の封入材の前記前面から前記第2の封入材の前記前面まで、前記第1の封入材及び前記第2の封入材を貫通して伸びる導電性ビアであって、前記導電性ビアは、前記第

10

20

1の封入材の前記前面で前記第1の導電性ラインと直接接触し、前記第2の封入材の前記前面で前記第2の導電性ラインと直接接触する、という導電性ピアと、を含むことを特徴とする半導体デバイス。

【請求項2】

請求項1に記載の半導体デバイスにおいて、

前記導電性ピアは、第1の導電性ピアであり、

前記半導体デバイスは、さらに、前記第1の封入材の前記前面から前記第2の封入材の前面まで、前記第1の封入材及び前記第2の封入材を貫通して伸びた第2の導電性ピアを含み、前記第2の導電性ピアは、前記第1の封入材の前記前面で前記第1の導電性ラインと直接接触し、前記第2の封入材の前記前面で前記第2の導電性ラインと直接接触し、

10

前記第2の導電性ピアは、前記第1の半導体ダイと前記第2の半導体ダイから、及び、前記第1の導電性ピアから、横方向に間隔を空けて離れていて、

前記半導体デバイスは、さらに、前記第1の導電性ラインに取付けられた第1の半田ボールと、前記第2の導電性ラインに取付けられた第2の半田ボールとを含むことを特徴とする半導体デバイス。

【請求項3】

請求項1に記載の半導体デバイスにおいて、

前記導電性ピアは、前記第1の半導体ダイから、横方向に間隔を空けて離れていることを特徴とする半導体デバイス。

【請求項4】

20

請求項1に記載の半導体デバイスにおいて、

前記導電性ピアは、第1の導電性ピアであり、

前記半導体デバイスは、さらに、前記第1の封入材の前記前面から前記第2の封入材の前記前面まで、前記第1の封入材及び前記第2の封入材を貫通して伸びた第2の導電性ピアを含み、前記第2の導電性ピアは、前記第1の半導体ダイ及び前記第1の導電性ピアから、横方向に間隔を空けて離れていることを特徴とする半導体デバイス。

【請求項5】

請求項1に記載の半導体デバイスにおいて、

前記第1の半導体ダイは、さらに、前記第1の半導体ダイの前記アクティブ面に、第1のボンドパッドと第3のボンドパッドとを含み、

30

前記第1のボンドパッドは、前記第1の導電性ラインと接触し、

前記半導体デバイスは、さらに、前記第1の半導体ダイの前記アクティブ面に、前記第3のボンドパッドと接触する第3の導電性ラインを含み、

前記導電性ピアは、第1の導電性ピアであり、

前記半導体デバイスは、さらに、前記第1の封入材の前記前面から前記第2の封入材の前記前面まで伸びた第2の導電性ピアを含み、前記第2の導電性ピアは、前記第3の導電性ラインと直接接触していることを特徴とする半導体デバイス。

【請求項6】

40

請求項1に記載の半導体デバイスにおいて、さらに、

前記第1の導電性ラインと第2の導電性ラインそれぞれに取付けられた第1の半田ボールと第2の半田ボールを含むことを特徴とする半導体デバイス。

【請求項7】

半導体デバイスであって、

第1の半導体サブアセンブリと、

前記第1の半導体サブアセンブリに最も近い第2の半導体サブアセンブリであって、前記第1及び前記第2の半導体サブアセンブリが各々前側と後側を有し、その上、前記第1の半導体サブアセンブリの前記後側が前記第2の半導体サブアセンブリの前記後側と向か

50

い合う、という第2の半導体サブアセンブリと、を含み、

前記第1及び前記第2の半導体サブアセンブリが個々に、

封入材と、

前記封入材に埋め込まれた半導体ダイであって、前記半導体ダイは、概して前記第1または前記第2の半導体サブアセンブリの前記前側と同一平面にあるアクティブ面と、前記封入材に埋め込まれた裏面とを有する、という半導体ダイと、

前記個々の第1及び第2の半導体サブアセンブリの前記前側上に配置されて且つ前記半導体ダイの前記アクティブ面と概して同一平面にある導電性ラインと、

前記第1の半導体サブアセンブリの前記前側から前記第2の半導体サブアセンブリの前記前側まで、前記第1及び前記第2の半導体サブアセンブリを貫通して伸びる導電性ビアであって、前記導電性ビアが前記第1の半導体サブアセンブリの前記導電性ライン及び第2の半導体サブアセンブリの前記導電性ラインと直接接触する、という導電性ビアと、を有する

ことを特徴とする半導体デバイス。

【請求項8】

請求項7に記載の半導体デバイスにおいて、

前記半導体デバイスは、さらに、前記第1の半導体サブアセンブリの前記導電性ラインに取付けられた半田ボールを含む

ことを特徴とする半導体デバイス。

【請求項9】

請求項7に記載の半導体デバイスにおいて、

前記導電性ビアは、第1の導電性ビアであり、

前記半導体デバイスは、さらに、

前記第1の半導体サブアセンブリの前記前側から前記第2の半導体サブアセンブリの前記前側まで、前記第1及び前記第2の半導体サブアセンブリを貫通して伸びる第2の導電性ビアであって、前記第1の半導体サブアセンブリの前記半導体ダイと前記第2の半導体サブアセンブリの前記半導体ダイから、及び、前記第1の導電性ビアから横方向に間隔を空けて離れているという第2の導電性ビアを含む

ことを特徴とする半導体デバイス。

【請求項10】

請求項7に記載の半導体デバイスにおいて、さらに、

前記第1の半導体サブアセンブリの前記後側と前記第2の半導体サブアセンブリの前記後側との間に接着材を含む

ことを特徴とする半導体デバイス。

【請求項11】

請求項7に記載の半導体デバイスにおいて、

前記第1及び前記第2の半導体サブアセンブリの各々は、複数の集積回路ダイを含むことを特徴とする半導体デバイス。

【請求項12】

半導体デバイスの製造方法であって、

第1の半導体ダイを封入材で前側と後側を有する第1の半導体構造に封入する工程であって、前記第1の半導体ダイは、概して前記前側と同一平面にあるアクティブ面と、前記封入材に埋め込まれた裏面とを有する、という工程と、

前記第1の半導体構造の前記前側に第1の導電性ラインを形成する工程であって、前記第1の導電性ラインが前記第1の半導体ダイの前記アクティブ面と概して同一平面にあるという工程と、

第2の半導体ダイを封入材で前側と後側を有する第2の半導体構造に封入する工程であって、前記第2の半導体ダイは、概して前記前側と同一平面にあるアクティブ面と、前記封入材に埋め込まれた裏面とを有する、という工程と、

前記第2の半導体構造の前記前側に第2の導電性ラインを形成する工程であって、前記

10

20

30

40

50

第2の導電性ラインが前記第2の半導体ダイの前記アクティブ面と概して同一平面にある

という工程と、

前記第1の半導体構造の前記前側から前記第2の半導体構造の前記前側まで前記第1の半導体構造及び前記第2の半導体構造を貫通して伸びた導電性ビアを形成する工程であって、前記導電性ビアが前記第1の半導体構造の前記第1の導電性ライン及び前記第2の半導体構造の前記第2の導電性ラインと直接接触する、という工程と、を含むことを特徴とする方法。

【請求項13】

請求項12に記載の方法において、

前記第1の半導体ダイを封入する工程は、

10

前記第1の半導体ダイを犠牲構造に配置する工程であって、前記第1の半導体ダイの前記アクティブ面が前記犠牲構造に接触する、という工程と、

前記犠牲構造に配置された前記第1の半導体ダイを封入する工程と、

前記犠牲構造を取り除く工程と、

前記第1の半導体ダイの前記アクティブ面を露出する工程と、を含むことを特徴とする方法。

【請求項14】

請求項12に記載の方法において、

前記第2の半導体ダイを封入する工程は、

20

複数の第2の半導体ダイを前記封入材で封入する工程と、

前記封入された第2の半導体ダイを单一化する工程と、を含むことを特徴とする方法。

【請求項15】

請求項12に記載の方法において、

前記方法は、さらに、前記第1の半導体ダイと前記第2の半導体ダイを犠牲構造上に配置する工程を含み、

前記第1及び前記第2の半導体ダイを封入する工程は、

前記第1及び前記第2の半導体ダイの両方を前記封入材で封入しながら、前記第1及び前記第2の半導体ダイが前記犠牲構造上に置かれる、という工程と、

その後に、

30

前記第1及び前記第2の半導体ダイから前記犠牲構造を取り除く工程と、

前記封入された第1及び前記第2の半導体ダイを单一化する工程と、を含むことを特徴とする方法。

【請求項16】

請求項12に記載の方法において、

前記方法は、さらに、前記第1の半導体ダイ及び前記第2の半導体ダイを犠牲構造上に配置する工程を含み、

前記第1及び前記第2の半導体ダイを封入する工程は、

前記第1及び前記第2の半導体ダイの両方を前記封入材で封入しながら、前記第1及び前記第2の半導体ダイが前記犠牲構造上に置かれる、という工程と、

40

その後に、

前記第1及び前記第2の半導体ダイから前記犠牲構造を取り除く工程と、

前記封入された第1及び第2の半導体ダイを单一化して、前記第1の半導体構造及び前記第2の半導体構造を形成する工程と、

前記第1及び前記第2の半導体構造の間に接着剤を配置する工程と、を含むことを特徴とする方法。

【発明の詳細な説明】

【技術分野】

【0001】

ここで開示されるこの主題は、概して、集積回路デバイスのパッケージングの分野を対

50

象とし、特に、スルーボディ (through-body) 導電性ビアを備えたパッケージ化された集積回路デバイス、及び、それを製造するさまざまな方法を対象とする。

【背景技術】

【0002】

集積回路技術は、数多くのいろいろな機能回路を構築するために、例えば、トランジスタ、レジスタ、キャパシタなどの電気デバイスを使用する。これらの回路の複雑さは、その回路がその意図された機能を実行できるように、ますます多くの連結された電気デバイスの使用を要求する。トランジスタの数が増加するにつれて、集積回路の寸法は小さくなる。半導体産業における1つの課題は、同一および/または異なるウェハーまたはチップ上に作製された回路デバイスを、電気的に接続し且つパッケージ化する改善された方法を開発することである。一般に、半導体産業では、シリコンチップ/ダイ上により小さい表面領域を占めるトランジスタを構成することが望ましい。

10

【0003】

半導体デバイスのアセンブリの製造では、単一の半導体ダイが密封されたパッケージの各々に組み込まれるのが最も一般的である。dual inline packages (DIP), zig-zag inline packages (ZIP), small outline J-bends (SOJ), thin small outline packages (TSOP), plastic leaded chip carriers (PLCC), small outline integrated circuits (SOIC), plastic quad flat packs (PQFP), 及びinterdigitated leadframe (IDF)を含む、多くの異なるパッケージスタイルが使用される。ある半導体デバイスのアセンブリは、封入前に、例えば、回路基板などの基板に接続される。製造者は、パッケージ化された集積回路デバイスのサイズを縮小し、且つ、集積回路デバイスをパッケージ化するときのパッケージ密度を増加することを、常に迫られている。

20

【0004】

一部の例では、パッケージ化された集積回路デバイスは、プロットスペース(plot space)を節約する目的で、互いに重なって積層されている。積層されパッケージ化された集積回路デバイスを導電的に互いに接続する先行技術は、典型的には、その接続を確立するための半田ボールやワイヤボンドの形成を伴ってきた。積層されパッケージ化された集積回路デバイスを導電的に互いに接続する、新規且つ改善された技術が望まれている。

【図面の簡単な説明】

【0005】

30

本主題は、その中の同じ参照番号は同じ要素を特定する以下の添付図面とともに、以下の記載を参考することで、理解されうる。

【0006】

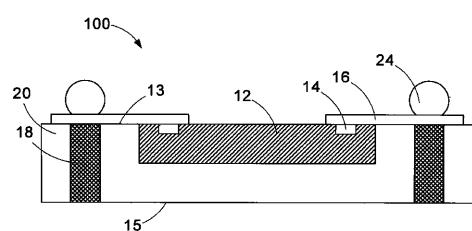

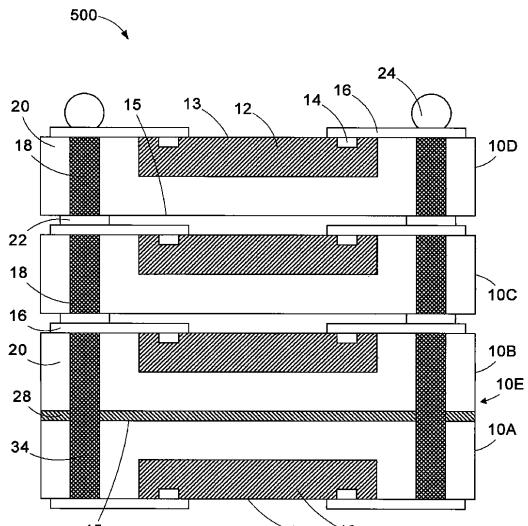

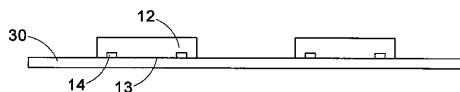

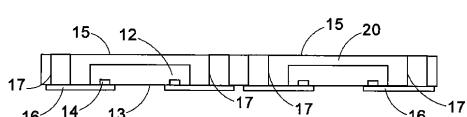

【図1】図1は、ここで記載されるように、複数の導電性のスルーボディビアを備えた、実例となるパッケージ化された集積回路ダイの概略図である。

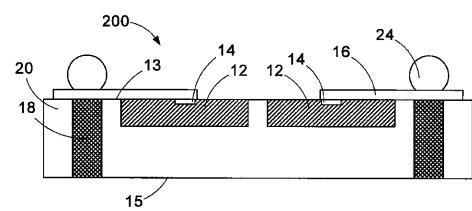

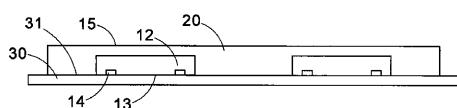

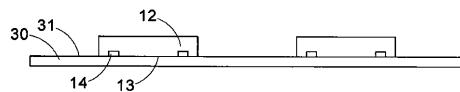

【図2】図2は、ここで記載されるように、複数の導電性のスルーボディビアを備えた、複数のダイからなる実例となるパッケージ化された集積回路の概略図である。

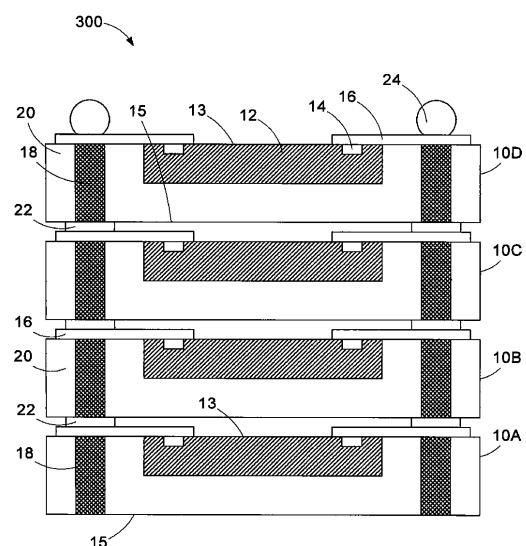

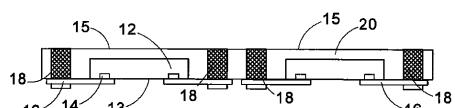

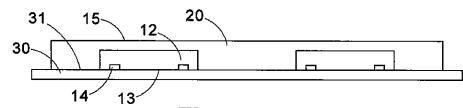

【図3】図3は、ここで開示される、実例となる積層されパッケージ化されたデバイスの概略断面図である。

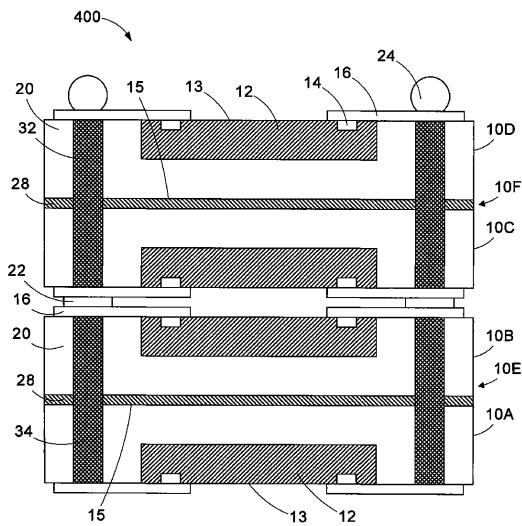

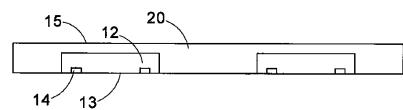

【図4】図4は、ここで開示される、別の実例となる積層されパッケージ化されたデバイスの概略断面図である。

40

【図5】図5は、ここで開示される、さらに別の実例となる積層されパッケージ化されたデバイスの概略断面図である。

【図6A】図6Aは、ここで開示される、積層されパッケージ化されたデバイスの一実例となる形成方法を概略的に描写する図である。

【図6B】図6Bは、ここで開示される、積層されパッケージ化されたデバイスの一実例となる形成方法を概略的に描写する図である。

【図6C】図6Cは、ここで開示される、積層されパッケージ化されたデバイスの一実例となる形成方法を概略的に描写する図である。

【図6D】図6Dは、ここで開示される、積層されパッケージ化されたデバイスの一実例

50

となる形成方法を概略的に描写する図である。

【図6 E】図6 Eは、ここで開示される、積層されパッケージ化されたデバイスの一実例となる形成方法を概略的に描写する図である。

【図6 F】図6 Fは、ここで開示される、積層されパッケージ化されたデバイスの一実例となる形成方法を概略的に描写する図である。

【図6 G】図6 Gは、ここで開示される、積層されパッケージ化されたデバイスの一実例となる形成方法を概略的に描写する図である。

【図6 H】図6 Hは、ここで開示される、積層されパッケージ化されたデバイスの一実例となる形成方法を概略的に描写する図である。

【図7 A】図7 Aは、ここで開示される、積層されパッケージ化されたデバイスの別の実例となる形成方法を概略的に描写する図である。 10

【図7 B】図7 Bは、ここで開示される、積層されパッケージ化されたデバイスの別の実例となる形成方法を概略的に描写する図である。

【図7 C】図7 Cは、ここで開示される、積層されパッケージ化されたデバイスの別の実例となる形成方法を概略的に描写する図である。

【図7 D】図7 Dは、ここで開示される、積層されパッケージ化されたデバイスの別の実例となる形成方法を概略的に描写する図である。

【図7 E】図7 Eは、ここで開示される、積層されパッケージ化されたデバイスの別の実例となる形成方法を概略的に描写する図である。

【図7 F】図7 Fは、ここで開示される、積層されパッケージ化されたデバイスの別の実例となる形成方法を概略的に描写する図である。 20

【図7 G】図7 Gは、ここで開示される、積層されパッケージ化されたデバイスの別の実例となる形成方法を概略的に描写する図である。

【図7 H】図7 Hは、ここで開示される、積層されパッケージ化されたデバイスの別の実例となる形成方法を概略的に描写する図である。

【図7 I】図7 Iは、ここで開示される、積層されパッケージ化されたデバイスの別の実例となる形成方法を概略的に描写する図である。

#### 【0007】

ここで開示される主題は、さまざまな変更及び代替形式を許すが、その特定の実施形態が、図面において例として示され、且つ、ここで詳細に開示される。しかしながら、ここでの特定の実施形態の記載は、発明を開示された特定の形式に制限する意図はなく、むしろ、その意図は、添付されたクレームによって定義されるように、その発明の趣旨及び範囲内にあるすべての変更、均等物、及び代替手段に及ぶことにあることは理解すべきである。 30

#### 【発明を実施するための形態】

#### 【0008】

本主題の実例となる実施形態を、以下に記載する。明確化するために、この明細書では、実際の実装のすべてのフィーチャは記載しない。当然のことながら、任意のそのような実際の実施形態の開発では、例えば、実装によって異なるシステム関連及びビジネス関連の制約への適合などの、開発の具体的な目的を達成するために、非常に多くの実装の具体的な決断がなされるに違いない。さらに、そのような開発への取り組みには手間と時間がかかることが認識されるが、それでもなお、この開示の利益を享受する当業者が負う日常的な取り組みであろう。 40

#### 【0009】

図面に示されるさまざまな領域及び構造は、精密で且つはっきりした構成及び輪郭として描写されるが、実際には、これらの領域及び構造が図面で示されるほど精密ではないことを当業者は認める。さらに、図面で描写されるさまざまなフィーチャ及びドープされた領域の相対的なサイズは、作製されたデバイス上のそれらのフィーチャまたは領域のサイズと比較して、拡大または縮小されていてもよい。それでもなお、添付された図面は、ここで開示される主題の実例を記載し、且つ、説明するために含まれる。 50

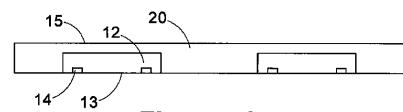

## 【0010】

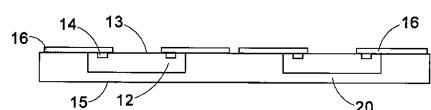

図1は、ここで記載されるように、パッケージ化された集積回路デバイス100の実例となる一実施形態を描写する。パッケージ化された集積回路デバイス100は、複数のボンドパッド14を有する集積回路ダイ12と、導電性配線ライン16（再配線層（RDL）と呼ばれることがある）と、例えば、モールド化合物材料などの、封入材料のボディ20を貫いて伸びる、少なくとも一つの導電性インターロネクション18（導電性ビアと呼ばれることがある）と、を含む。導電性ビア18は、ボディ20の厚さ、すなわち、ボディ20の前側13と後側15の間、を貫く導電性流路を規定する。導電性ビア18及び集積回路ダイ12は、多様な既知の技術及び構造を使用して、互いに導電的に接続されうる。10

描写された例では、導電性配線ライン16は、導電性ビア18を集積回路ダイ12に導電的に接続する。概略的に描写された複数の半田ボール24は、既知のプロセス技術に従って、パッケージ化された集積回路デバイス100上に形成される。半田ボール24または他の同様なコネクションは、パッケージ化された集積回路デバイス100を、例えば、プリント回路基板などの他の構造物に導電的に接続するために、採用されうる。図1では、ダイ12は、封入材料20のボディに埋め込まれる。ここで使用されるように、一つ以上のダイ12が封入材料のボディに埋め込まれることが述べられるとき、ダイ12のボディの一部分だけが封入材料内に位置付けられが必要であると理解されるべきである。特定の用途によってはその構成が必要に応じて採用されうるが、封入材料がダイ12のボディの全側面を取り囲むことはかならずしも必要ではない。

## 【0011】

20

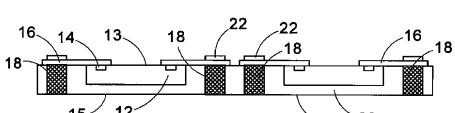

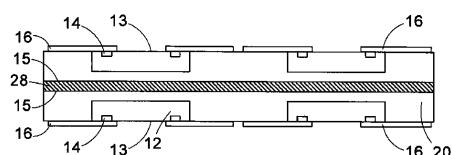

図2は、ここで記載されるように、パッケージ化された集積回路デバイス200の実例となる一実施形態を描写する。パッケージ化された集積回路デバイス200は、例えば、モールド化合物材料などの、封入材料の单一のボディ20に埋め込まれた複数の集積回路ダイ12（2つ示されている）を含む。ここで描写された実例では、ダイ12の各々は、同じ物理的なサイズを有する。しかしながら、本出願を読み終えた後で当業者によって理解されるように、ダイ12は同じ物理的なサイズである必要はなく、同じ機能を果たす必要さえない。図2に示されるダイ12の各々は、複数のボンドパッド14と、導電性配線ライン16（再配線層（RDL）と呼ばれることがある）と、封入材料のボディ20を貫いて伸びる、少なくとも一つの導電性インターロネクション18（導電性ビアと呼ばれることがある）と、を有する。デバイス200は、複数の集積回路ダイ12を含むので、マルチチップモジュール（MCM）であるとみなされうる。図1のように、概略的に描写された複数の半田ボール24は、既知のプロセス技術に従って、パッケージ化された集積回路デバイス200上に形成される。半田ボール24または他の同様なコネクションは、パッケージ化された集積回路デバイス200を、例えば、プリント回路基板などの他の構造物に導電的に接続するために、採用されうる。

30

## 【0012】

描写される実施形態では、図2の導電性ビア18の各々は、ボディ12の厚さを貫いて伸びる。導電性ビア18と埋め込まれた集積回路ダイ12との間の導電的な接続は、任意の多様な既知の技術や構造を使用して確立されてもよい。図2に示される例では、導電性ビア18の少なくとも一つが、一つ以上の配線ライン16によって、集積回路ダイ12の一つに導電的に接続され、導電性ビア18の別の一つは、同様に一つ以上の配線ライン16によって、他の集積回路ダイ12に導電的に接続される。

40

## 【0013】

本出願を読み終えた後で当業者によって認識されるように、ここで開示された方法及び技術は、実際には、ダイ12上に形成されうる任意の種類の集積回路デバイスに適用されてもよい。さらに、概略的に描写されるボンドパッド14、導電性配線ライン16、及び、スルーボディ導電性インターロネクション18の構成及び配置は、その特定の用途に応じて変更しても良い。

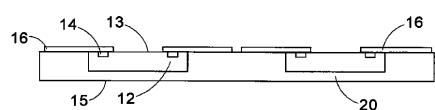

## 【0014】

図3乃至図5は、積層されパッケージ化された複数の集積回路デバイスの概略断面図で

50

ある。図3に描寫される実例では、積層されたパッケージ300は、複数の個別の埋め込みダイ10A乃至ダイ10Dを含む。図3に描寫される実例では、個別の埋め込みダイ10A乃至ダイ10Dが4つだけ実例として描寫されている。上述したように、埋め込みダイまたは個別の埋め込みダイに関しては、その構造上の要求は、ダイのボディの一部が封入材料のボディ20内に位置付けられる、少なくとも一つの集積回路ダイを含むことのみである。しかしながら、本出願を読み終えた後で当業者によって理解されるように、積層されたパッケージ300内の個別の埋め込みダイ10の数は、その特定の用途に応じて変更してもよく、つまり、当該スタック300内の個別の埋め込みダイ10の数は、図3で描寫される実例の4つよりも多くても少なくてもよい。

## 【0015】

10

図3の実例となる個別の埋め込みダイ10A乃至10Dの各々は、集積回路ダイ12と、複数のボンドパッド14と、導電性配線ライン16（再配線層（RDL）と呼ばれることがある）と、封入された材料のボディ20を貫いて伸びる、複数の導電性インターロネクション18（導電性ビアと呼ばれることがある）と、を含む。複数の導電性構造22は、さまざまな埋め込みダイ10A乃至10Dの間に電気的な導電路を提供するために、隣接する個別の埋め込みダイ間に設けられる。概略的に描寫された複数の半田ボール24は、既知のプロセス技術に従って、パッケージ化されたダイ10D上に形成される。半田ボール24または他の同様なコネクションは、積層されたパッケージ300を、例えば、プリント回路基板などの他の構造物に導電的に接続するために、採用されうる。

## 【0016】

20

本出願を読み終えた後で当業者によって認識されるように、ここで開示された方法及び技術は、実際には、ダイ12上に形成され、且つ、積層された構成でパッケージ化されうる、任意の種類の集積回路デバイスに適用されてもよい。さらに、図3で示される、概略的に描寫されるボンドパッド14、導電性インターロネクション18、及び導電性構造22の構成及び配置は、その特定の用途に応じて変更しても良い。図3で描寫される実施形態では、パッケージ化されたダイのすべてが、埋め込みダイ10の前側13の方向に置かれ、隣接する埋め込みダイ10の後側15に面している。

## 【0017】

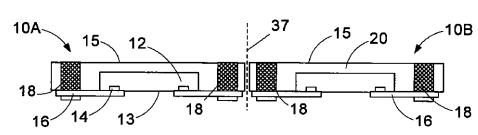

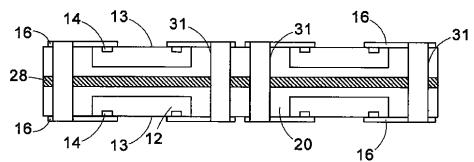

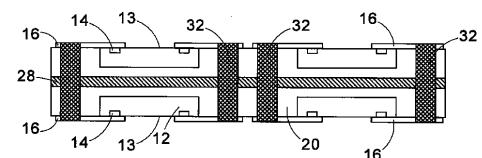

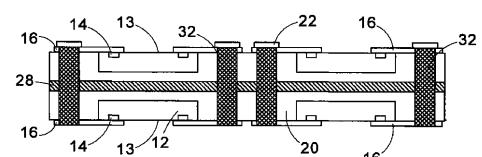

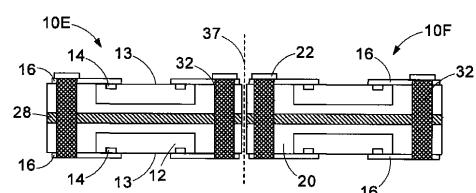

図4は、積層されパッケージ化されたデバイス400の別の実例となる実施形態を描寫する。図3で示された実施形態と同様に、図4の実施形態は、4つの実例となる個別の埋め込みダイ10A乃至ダイ10Dを含む。図4では、個別の埋め込みダイ10A乃至10Dは、図4に示される構造にアセンブリ化される前に、グループ10E及び10Fとしてアセンブリ化される。第1のグループ10Eは、個別の埋め込みダイ10A及び10Bを含み、第2のグループ10Fは、個別の埋め込みダイ10C及び10Dを含む。複数の導電性インターロネクションまたはビア32は、第1のグループ10Eを含む複数のダイ10のボディ20を貫いて伸び、複数の導電性インターロネクションまたはビア34は、第2のグループ10Fを含む複数のダイ10のボディ20を貫いて伸びる。

30

## 【0018】

複数の導電性構造22は、2つのグループ10Eと10Fの間に、電気的な導電路を提供する。各グループ内の個別の埋め込みダイ10は、接着材料28を使用して、互いに固定されうる。ここで留意すべきは、図4で描寫される実例では、隣接する埋め込みダイ10の後側15は、互いに向かい合って位置付けられることである。本出願を読み終えた後で当業者によって認識されるように、図4で描寫されるように積層されうるグループ、例えば、グループ10E及び10F、の数は、その特定の用途に応じて変更しても良く、すなわち、図4で描寫される実例の2つのグループよりも多いまたは少ないグループが、最終的な積層されたパッケージ400にアセンブリ化されうる。同様に、各グループ内の個別の埋め込みダイ10の数は、図4のグループ10E及び10F内で描寫される実例の2つよりも多い。

40

## 【0019】

図3及び図4に描寫される構造は、必要に応じて組み合わされても良い。例えば、図5

50

は、実例となる積層されパッケージ化されたデバイス 500 を描写していく、その中の下位 2 つの埋め込みダイ 10A 及び 10B は、グループ 10E としてパッケージ化され、上位 2 つの埋め込みダイ 10C 及び 10D は、図 3 に描写されるようにパッケージされる。従って、積層されパッケージ化されたデバイスの製造に関連して、プロットスペースの消費が削減され、且つ、パッケージ密度が改善されることから、ここで開示された方法及びデバイスが、高い柔軟性を提供することは明らかである。さらに、図 3 乃至図 5 では、個別の埋め込みダイ 10 の各々は、その中に埋め込まれた単一の集積回路ダイ 12 を有するように描写される。本開示の一態様に従って、個別の埋め込みダイ 10 は、図 2 で描写されるマルチチップの実施形態と同じように、複数の個別の集積回路ダイ 12 を含んでもよい。すなわち、ここで開示される方法及びデバイスは、単一または複数の集積回路ダイ 12 を含む個別の埋め込みダイ 10 に採用されてもよい。その方法は、個別の埋め込みダイの封入材料の単一のボディ 20 内に複数の集積回路ダイ 12 を埋め込むことに容易に適用し得るが、容易に参照できるように、以下の記載では、単一の集積回路ダイ 12 からなる個別の埋め込みダイ 10 を参照する。

#### 【0020】

図 6A 乃至図 6H は、ここで開示されるデバイスの一実例となる形成方法を描写する。図 6A では、複数の既知の良好な集積回路ダイ 12 は、実例となる犠牲構造 30 の上方に前側 13 を下にして置かれている。一実例では、犠牲構造 30 は、フィルムフレームであり、フィルムフレームは、そのフィルムフレーム全域に位置付けられたダイシングテープを有してもよい。その構造 30 は、後で取り除かれる点で犠牲的である。図 6B では、例えば、モールド化合物である封入材料のボディ 20 は、集積回路ダイ 12 の周囲及び構造 30 の上方に形成される。つまり、集積回路ダイ 12 は、ボディ 20 に埋め込まれる。例えば、射出成形である従来のモールディング技術が、封入材料のボディ 20 を形成するために行われてもよい。その後、図 6C に示されるように、犠牲構造 30 を取り除くことができる。ここで記載される実例では、構造 30 は、その構造 30 の一部として接着テープを使用することによって、単純に剥がされてもよい。

#### 【0021】

次に、図 6D に示されるように、導電性ライン 16 が、従来技術に従って、集積回路ダイ 12 の前側 13 及びボディ 12 の上方に形成される。当然に、導電性ライン 16 は、任意の所望の構成を有してもよく、任意の所望の材料から作られてもよい。その後、図 6E に示されるように、複数の開口またはピア 17 が、図のようにボディ 20 を貫いて形成される。開口 17 は、多様な既知の技術、例えば、レーザ掘削やエッティングなどによって、形成されてもよい。ある用途では、マスキング層（図示せず）が、開口 17 を形成するプロセスの一部として、形成されてもよい。開口 17 は、任意の所望の輪郭または構成を呈してもよい。ここで留意すべきは、ここで描写される実例では、開口 17 は、埋め込みダイ 10 のボディ 20 の後側 15 から前側 13 に向かって、形成されることである。また、この特定の例では、開口 17 は、埋め込みダイ 10 の前側 13 上に形成された導電性インターロネクション 16 を露出しているが、貫いて伸びてはいないことも留意すべきである。その後、図 6F に示されるように、開口 17 は、導電性インターロネクション 18 を形成するために、例えば、銅、アルミニウム、銀など、導電性材料で満たされる。導電性材料は、任意の多様な既知の技術、例えば、めっき、蒸着などを使用して、開口 17 内に形成されてもよい。また、その特定の用途に応じて、多様な異なる導電性材料が採用されてもよい。

#### 【0022】

図 6G では、複数の導電性構造 22 が、既知の技術を使用して、埋め込みダイ 10A 及び 10B 上に形成される。ある場合には、導電性構造 22 は、導電性インターロネクション 18 を形成するプロセスの一部として、形成されてもよい。その後、図 6H に示されるように、ダイシングまたは单一化プロセスがカット線 37 に沿って実行され、実例となる個別の埋め込みダイ 10A 及び 10B が製造される。

#### 【0023】

10

20

30

40

50

次に、個別の埋め込みダイ 10 A 及び 10 B は、多様なテストが行われ、意図される用途へのそれらの適合性が確認される。埋め込みダイ 10 A 及び 10 B がそのようなテストに首尾よく合格すると、それらは消費者に出荷される状態になる。他の用途では、テストされた埋め込みダイ 10 A 及び 10 B は、ここで描写されるように、積層されパッケージ化されたデバイス 300、400、500 にアセンブリ化されてもよい。図 3 で描写された例では、複数の個別の埋め込みダイ 10 は、図 3 に描写されるように位置付けられ、リフロープロセスが実行されて、個別の埋め込みダイ、例えば、ダイ 10 A 上の導電性構造 22 と、隣接する埋め込みダイ、例えば、ダイ 10 B 上の導電性インターフェクション 18 との間に電気的な接続が確立される。実例となる半田ボール 24 は、従来技術を使用して、実例となるダイ 10 上に形成されてもよい。半田ボール 24 は、リフロープロセス中の任意の時点で形成されてもよい。例えば、半田ボール 24 は、埋め込みダイ 10 A 乃至 10 D のすべてが図 3 に描写されるようにアセンブリ化された後に、形成されてもよい。あるいは、半田ボール 24 は、図 3 に描写されるように、他の個別の埋め込みダイとともに個別の埋め込みダイ 10 D をアセンブリ化する前に、個別の埋め込みダイ 10 D の上方に形成されてもよい。

#### 【0024】

図 7 A 乃至図 7 I は、ここで開示されるデバイスの別の実例となる形成方法を描写する。図 7 A 乃至図 7 D で描写される工程は、図 6 A 乃至図 6 D に関して前述された工程と同じである。従って、図 7 A 乃至図 7 D の詳細な解説は繰り返さない。図 7 E では、図 7 D で描写される複数の構造が、接着材料 28 を使用して互いに固定される。その後、図 7 F で、図 7 E に描写される組み合わせ構造のボディ 20 を貫いて、複数の開口またはビア 31 が形成される。開口 31 は、多様な既知の技術、例えば、レーザ掘削やエッチングなどによって、形成されてもよい。ある用途では、マスキング層（図示せず）が、開口 31 を形成するプロセスの一部として、形成されてもよい。開口 31 は、任意の所望の輪郭または構成であってもよい。ここで留意すべきは、ここで描写される実例では、開口 31 は、個別の構造の各々の前側 13 上に形成された導電性インターフェクション 16 を貫いて伸びることである。その後、図 7 G に示されるように、開口 31 は、スルーボディ導電性ビア 32 を形成するために、例えば、銅、アルミニウム、銀などの、導電性材料で満たされる。導電性材料は、任意の多様な既知の技術、例えば、めっき、蒸着などを使用して、開口 31 内に形成されてもよく、また、その特定の用途に応じて、多様な異なる導電性材料が採用されてもよい。

#### 【0025】

図 7 H では、複数の導電性構造 22 が、既知の技術を使用して、図 7 G に描写される構造上に形成される。ある場合には、導電性構造 22 は、導電性インターフェクション 32 を形成するプロセスの一部として、形成されてもよい。次に、図 7 I に示されるように、ダイシングまたは単一化プロセスがカット線 37 に沿って実行されて、実例となる個別の埋め込みのグループ 10 E 及び 10 F が製造される。

#### 【0026】

次に、埋め込みダイのグループ 10 E 及び 10 F は、多様なテストが行われて、意図される用途へのそれらの適合性が確認される。グループ 10 E 及び 10 F がそのようなテストに首尾よく合格すると、それらは消費者に出荷される状態になる。ある用途では、埋め込みダイのグループ 10 E 及び 10 F は、ここで記載されるように、積層されパッケージ化されたデバイスにアセンブリ化されてもよい。図 4 で描写された例では、埋め込みダイのグループ 10 E 及び 10 F は、図 4 に描写されるように位置付けられ、リフロープロセスが実行されて、第 1 のグループ 10 E 上の導電性構造 22 と、隣接するグループ 10 F 上の導電性ビア 32 との間に電気的な接続が確立される。実例となる半田ボール 24 は、従来技術を使用して、グループ 10 F 内の実例となる個別の埋め込みダイ上に形成されてもよい。半田ボール 24 は、リフロープロセス中の任意の時点で形成されてもよい。例えば、半田ボール 24 は、2 つの実例となるグループ 10 E 及び 10 F が図 4 に描写されるようにアセンブリ化された後に、形成されてもよい。あるいは、半田ボール 24 は、図 4

10

20

30

40

50

に描写されるように、2つのグループと一緒にアセンブリ化する前に、グループ10F内の個別の埋め込みダイの一つの上方に形成されてもよい。

【0027】

本出願を読み終えた後で当業者によって認識されるように、本開示は、個別のダイをパッケージ化し、且つ、積層されパッケージ化された集積回路デバイスを提供する、非常に効果的な手段を提供し得る。ここで実行されるプロセスの多くは、一度に個々のダイ一つでそのような動作が実行されるのとは対照的に、一度に複数のダイで実行されうる。例えば、2つの実例となるダイ12は、図6A乃至図6H及び図7A乃至図7Iで描写されるが、ここで記載されたプロセス工程は、採用されるプロセスツールのプロセス性能に応じて、任意の所望の数のダイで実行されてもよい。要するに、ウェハーレベルプロセス技術が、パッケージ化動作の効率を向上させるために採用されてもよく、つまり、プロセス動作は、同時に複数のダイで実行されうる。

10

【図1】

Figure 1

【図2】

Figure 2

【図3】

Figure 3

【図4】

Figure 4

【図5】

Figure 5

【図6A】

Figure 6A

【図6B】

Figure 6B

【図6F】

Figure 6F

【図6C】

Figure 6C

【図6G】

Figure 6G

【図6D】

Figure 6D

【図6H】

Figure 6H

【図6E】

Figure 6E

【図7A】

Figure 7A

【図 7 B】

Figure 7B

【図 7 C】

Figure 7C

【図 7 D】

Figure 7D

【図 7 E】

Figure 7E

【図 7 F】

Figure 7F

【図 7 G】

Figure 7G

【図 7 H】

Figure 7H

【図 7 I】

Figure 7I

---

フロントページの続き

(72)発明者 チア, ヤン ポー

シンガポール共和国, シンガポール 679976, バンキット ロード, ブロック 37, #1

0 03

合議体

審判長 酒井 朋広

審判官 萩原 義則

審判官 井上 信一

(56)参考文献 特開2005-5632 (JP, A)

特開2006-203079 (JP, A)

獨国特許出願公開第102005043557 (DE, A1)

(58)調査した分野(Int.Cl., DB名)

H01L25/08

H01L23/12