(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6092904号

(P6092904)

(45) 発行日 平成29年3月8日(2017.3.8)

(24) 登録日 平成29年2月17日(2017.2.17)

|                      |                |

|----------------------|----------------|

| (51) Int.Cl.         | F 1            |

| GO6F 9/305 (2006.01) | GO6F 9/30 340A |

| GO6F 7/487 (2006.01) | GO6F 7/487     |

| GO6F 17/10 (2006.01) | GO6F 17/10 S   |

請求項の数 20 外国語出願 (全 37 頁)

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2015-11008 (P2015-11008)    |

| (22) 出願日     | 平成27年1月23日 (2015.1.23)        |

| (65) 公開番号    | 特開2015-191661 (P2015-191661A) |

| (43) 公開日     | 平成27年11月2日 (2015.11.2)        |

| 審査請求日        | 平成27年1月23日 (2015.1.23)        |

| (31) 優先権主張番号 | 14/229, 183                   |

| (32) 優先日     | 平成26年3月28日 (2014.3.28)        |

| (33) 優先権主張国  | 米国 (US)                       |

|           |                                                                                    |

|-----------|------------------------------------------------------------------------------------|

| (73) 特許権者 | 591003943<br>インテル・コーポレーション<br>アメリカ合衆国 95054 カリフォルニア州・サンタクララ・ミッション カレッジ ブーレバード・2200 |

| (74) 代理人  | 110000877<br>龍華国際特許業務法人                                                            |

| (72) 発明者  | エスパサ、ロジャー<br>アメリカ合衆国 95054 カリフォルニア州・サンタクララ・ミッション カレッジ ブーレバード・2200 インテル・コーポレーション内   |

最終頁に続く

(54) 【発明の名称】プロセッサおよび方法

## (57) 【特許請求の範囲】

## 【請求項 1】

メモリサブシステムから单一の二重乗算命令をフェッチする命令フェッチユニットであり、前記二重乗算命令は3つのソースオペランド値を有する、命令フェッチユニットと、前記二重乗算命令をデコードして、单一のマイクロオペレーション( $\mu o p$ )を生成するデコードユニットと、

前記 $\mu o p$ を1回目に実行して、前記3つのソースオペランド値のうちの第1のソースオペランド値および第2のソースオペランド値を乗算して中間結果を生成し、前記 $\mu o p$ を2回目に実行して、前記中間結果を前記3つのソースオペランド値のうちの第3のソースオペランド値を用いて乗算して、最終結果を生成する実行ユニットと、10

を備えるプロセッサ。

## 【請求項 2】

前記実行ユニットは、前記 $\mu o p$ の前記2回目の実行の前に前記 $\mu o p$ を遅延する遅延バッファを含み、請求項1に記載のプロセッサ。

## 【請求項 3】

前記実行ユニットは、さらに、少なくとも1つの機能ユニットによる実行のために、前記二重乗算命令をスケジュールするリザベーションステーションを含み、前記 $\mu o p$ は、前記リザベーションステーションから第1の機能ユニットに送信され、機能ユニットによる前記実行の前に前記遅延バッファにも提供される、請求項2に記載のプロセッサ。

## 【請求項 4】

前記機能ユニットは、融合乗算および加算機能ユニットを有する、請求項3に記載のプロセッサ。

【請求項5】

前記 $\mu$  o  $p$ は、さらに、前記第1の機能ユニットが前記 $\mu$  o  $p$ の1回目の実行を完了し、前記中間結果を生成したときに前記遅延バッファから第2の機能ユニットに送信され、前記第2の機能ユニットは、前記中間結果を前記3つのソースオペランド値のうちの前記第3のソースオペランド値により乗算して、前記最終結果を生成する、請求項3または4に記載のプロセッサ。

【請求項6】

前記二重乗算命令の第1のソースオペランド値、第2のソースオペランド値、および第3のソースオペランド値は、浮動小数点値である、請求項1から5のいずれか一項に記載のプロセッサ。 10

【請求項7】

前記浮動小数点値は、単精度または倍精度浮動小数点値を有する、請求項6に記載のプロセッサ。

【請求項8】

前記二重乗算命令は、第1のソースオペランド値、第2のソースオペランド値、および第3のソースオペランド値のそれぞれの符号を示す即値を有する、請求項1から7のいずれか一項に記載のプロセッサ。

【請求項9】

前記即値は、前記第1のソースオペランド値、前記第2のソースオペランド値、および前記第3のソースオペランド値の符号を示す各ビットの値を有する3ビット値を有する、請求項8に記載のプロセッサ。 20

【請求項10】

前記リザベーションステーションは、第1の実効ポートを介して前記 $\mu$  o  $p$ の前記1回目の実行をスケジュールするための第1のリザベーションステーション部分と、第2の実効ポートを介して前記 $\mu$  o  $p$ の前記2回目の実行をスケジュールするための第2のリザベーションステーション部分と、を含む、請求項3に記載のプロセッサ。

【請求項11】

プロセッサにより実行される方法であって、

前記プロセッサにより、メモリサブシステムから单一の二重乗算命令をフェッチする段階であり、前記二重乗算命令は3つのソースオペランド値を有する、段階と、

前記プロセッサにより、单一のマイクロオペレーション( $\mu$  o  $p$ )を生成するべく前記二重乗算命令をデコードする段階と、

前記プロセッサにより、前記3つのソースオペランド値のうちの第1のソースオペランド値および第2のソースオペランド値を乗算して中間結果を生成するべく前記 $\mu$  o  $p$ を1回目に実行し、前記中間結果を前記3つのソースオペランド値のうちの第3のソースオペランド値を用いて乗算して、最終結果を生成するべく前記 $\mu$  o  $p$ を2回目に実行する段階と、

を備える方法。 40

【請求項12】

前記プロセッサにより、前記 $\mu$  o  $p$ の前記2回目の実行の前に遅延バッファで前記 $\mu$  o  $p$ を遅延する段階をさらに備える、請求項11に記載の方法。

【請求項13】

前記プロセッサにより、少なくとも1つの機能ユニットによる実行のために、前記二重乗算命令をスケジュールする段階をさらに備え、前記 $\mu$  o  $p$ は、第1の機能ユニットに送信され、機能ユニットによる前記実行の前に前記遅延バッファにも提供される、請求項12に記載の方法。

【請求項14】

前記機能ユニットは、融合乗算および加算機能ユニットを有する、請求項13に記載の

50

方法。

【請求項 1 5】

前記 μ o p は、さらに、前記第 1 の機能ユニットが前記 μ o p の 1 回目の実行を完了し、前記中間結果を生成したときに前記遅延バッファから第 2 の機能ユニットに送信され、前記第 2 の機能ユニットは、前記中間結果を前記 3 つのソースオペランド値のうちの前記第 3 のソースオペランド値により乗算して、前記最終結果を生成する、請求項 1 3 または 1 4 に記載の方法。

【請求項 1 6】

前記二重乗算命令の第 1 のソースオペランド値、第 2 のソースオペランド値、および第 3 のソースオペランド値は、浮動小数点値である、請求項 1 1 から 1 5 のいずれか一項に記載の方法。 10

【請求項 1 7】

前記浮動小数点値は、単精度または倍精度浮動小数点値を有する、請求項 1 6 に記載の方法。

【請求項 1 8】

前記二重乗算命令は、第 1 のソースオペランド値、第 2 のソースオペランド値、および第 3 のソースオペランド値のそれぞれの符号を示す即値を有する、請求項 1 1 から 1 7 のいずれか一項に記載の方法。

【請求項 1 9】

前記即値は、前記第 1 のソースオペランド値、前記第 2 のソースオペランド値、および前記第 3 のソースオペランド値の符号を示す各ビットの値を有する 3 ビット値を有する、請求項 1 8 に記載の方法。 20

【請求項 2 0】

前記スケジュールする段階は、第 1 の実効ポートを介して前記 μ o p の前記 1 回目の実行をスケジュールするための第 1 のリザベーションステーション部分と、第 2 の実効ポートを介して前記 μ o p の前記 2 回目の実行をスケジュールするための第 2 のリザベーションステーション部分と、を含むリザベーションステーションにより実行され、請求項 1 3 に記載の方法。

【発明の詳細な説明】

【技術分野】

30

【0 0 0 1】

この発明は、概して、コンピュータプロセッサの分野に関する。より具体的には、発明は、複数の乗算演算を実行するための方法及び装置に関する。

【背景技術】

【0 0 0 2】

命令セット、または命令セットアーキテクチャ (ISA) は、本来のデータタイプ、命令、レジスタアーキテクチャ、アドレスモード、メモリアーキテクチャ、割り込み及び例外処理、及び外部入出力 (I/O) を含むプログラミングに関するコンピュータアーキテクチャの一部である。ここでは、用語「命令」は、概して、マイクロ命令に対立するものとしてのマクロ命令（実行するためにプロセッサに提供される命令）またはマイクロオペレーション（プロセッサのデコーダがマクロ命令をデコードした結果）を参照することに留意すべきである。 40

【0 0 0 3】

ISA は、命令セットを実装するために用いられるプロセッサ設計技術のセットであるマイクロアーキテクチャから区別される。異なるマイクロアーキテクチャを有する複数のプロセッサは、共通の命令セットを共有する。例えば、Intel (登録商標) Pentium (登録商標) 4 プロセッサ、Intel (登録商標) Core (商標) プロセッサ、およびカリフォルニア州サニーベールのアドバンスドマイクロデバイセズからのプロセッサは、x 86 命令セット（より新しいバージョンが追加された幾つかのエクステンションを有する）のほぼ同じバージョンを実装するが、異なる内部設計を有する。例えば、I 50

S A の同じレジスターアーキテクチャは、専用の物理レジスタ、レジスタリネームメカニズム（例えば、レジスタエイリアステーブル（R A T）、リオーダバッファ（R O B）、及びリタイアメントレジスタファイルの使用）を用いて動的に割り当てられた 1 または複数の物理レジスタを含む周知の技術を用いて異なるマイクロアーキテクチャに異なる態様で実装されてよい。特に指定されない限り、レジスターアーキテクチャ、レジスタファイル、およびレジスタなるフレーズは、ここでは、ソフトウェア／プログラマにビジュアルであるそれ、および複数の命令が複数のレジスタを特定する方法を参照するために用いられる。区別が必要の場合、「論理」、「アーキテクチャ上」、または「ソフトウェアビジュアル」なる形容詞が、レジスターアーキテクチャにおけるレジスタ／ファイルを示すために用いられるとともに、異なる形容詞が、与えられたマイクロアーキテクチャにおいてレジスタを指定するために用いられる（例えば、物理レジスタ、リオーダバッファ、リタイアメントレジスタ、レジスタプール）。

#### 【 0 0 0 4 】

命令セットは、1 または複数の命令フォーマットを含む。与えられた命令フォーマットは、とりわけ、実行される演算およびその演算が実行されるオペランドを特定するために、様々なフィールド（ビットの数、ビットの位置）を定義する。幾つかの命令フォーマットは、さらに、複数の命令テンプレート（または複数のサブフォーマット）の定義を介して分解される。例えば、与えられた命令フォーマットの複数の命令テンプレートは、命令フォーマットの複数のフィールド（より少ない含まれたフィールドがあるので、含まれるフィールドは、一般的に、同じ順序であり、しかし少なくとも幾つかは異なるビット位置を有する。）の異なるサブセットを有するために定義されてよく、および／または異なつて解釈される与えられたフィールドを有するために定義されてよい。与えられた命令は、与えられた命令フォーマットを用いて（および、定義されている場合には、その命令フォーマットの複数の命令テンプレートの与えられた 1 つにおいて）表され、演算および複数のオペランドを特定する。命令ストリームは、複数の命令の固有のシーケンスである。ただし、シーケンス内の各命令は、命令フォーマットにおける命令の発生である（および、定義されている場合には、その命令フォーマットの複数の命令テンプレートの与えられた 1 つである）。

#### 【 0 0 0 5 】

科学、金融、自動ベクトル化の汎用、R M S（認識、採鉱、および合成）、およびビジュアルおよびマルチメディアアプリケーション（例えば、2 D / 3 D グラフィック、画像処理、ビデオ圧縮／解凍、音声認識アルゴリズム、およびオーディオ操作）は、頻繁に、多数のデータアイテム（「データ並列処理」として参照される）上で実行される同じ演算を必要とする。単一命令複数データ（S I M D）は、プロセッサに複数のデータアイテム上の演算を実行させる命令のタイプを参照する。S I M D 技術は、特に、レジスタ内の複数のビットを、それぞれが別個の値を表す固定サイズのデータ要素の数に論理的に分割できるプロセッサに好適である。例えば、64 ビットレジスタ内の複数のビットは、それぞれが別個の 16 ビット値を表す 4 つの別個の 16 ビットデータ要素として操作されるソースオペランドとして特定されてよい。このタイプのデータは、パックドデータタイプまたはベクトルデータタイプとして参照され、このデータタイプの複数のオペランドは、パックドデータオペランドまたはベクトルオペランドとして参照される。言い換えると、パックドデータアイテムまたはベクトルは、パックドデータ要素のシーケンスを参照し、パックドデータオペランドまたはベクトルオペランドは、S I M D 命令（パックドデータ命令またはベクトル命令としても知られる）のソースまたはデスティネーションオペランドである。

#### 【 0 0 0 6 】

例として、S I M D 命令の一タイプは、2 つのソースベクトルオペランド上で垂直式に実行されて、同じ数のデータ要素を有する同じサイズおよび同じデータエレメントの順序にあるデスティネーションベクトルオペランド（結果ベクトルオペランドとしても参照される）を生成するシングルベクトル演算を特定する。複数のソースベクトルオペランドに

10

20

30

40

50

おける複数のデータ要素は、複数のソースデータエレメントとして参照されるとともに、デスティネーションベクトルオペランド内の複数のデータ要素は、デスティネーションまたは結果データ要素と参照される。これらのソースベクトルオペランドは、同じサイズであり、同じ幅の複数のデータ要素を含み、従って、それらは同じ数のデータ要素を含む。2つのソースベクトルオペランド内の複数の同じビット位置内の複数のソースデータエレメントは、複数の組のデータ要素（対応するデータ要素としても参照される）を形成する。その SIMD 命令により指定される演算は、これらの組のソースデータエレメントのそれぞれで別個に実行されて、マッチング数の結果データ要素を生成し、従って、各組のソースデータエレメントは対応する結果データ要素を有する。演算は垂直であるので、また結果ベクトルオペランドは同じ数のデータ要素を有する同じサイズであり、結果データ要素は複数のソースベクトルオペランドとして同じデータエレメントの順序で格納されるので、複数の結果データ要素は、複数のソースベクトルオペランド内の複数のソースデータエレメントのそれらの対応する組として、結果ベクトルオペランドの複数の同じビット位置内にある。この典型的なタイプの SIMD 命令に加えて、様々な他のタイプの SIMD 命令がある（例えば、1つのみまたは2以上のソースベクトルオペランドを有する、垂直式に演算する、異なるサイズの結果ベクトルオペランドを生成する、異なるサイズのデータ要素を有する、および／または異なるデータエレメントの順序を有する）。用語デスティネーションベクトルオペランド（またはデスティネーションオペランド）は、命令により指定される演算を実行することの直接の結果として、位置（そのレジスタ又はその命令により特定されるメモリアドレス）でそのデスティネーションオペランドのストレージを含めて定義され、それにより、それは別の命令により（別の命令によるその同じ位置の仕様により）ソースオペランドとしてアクセスされてよいことを理解されるべきである。10

#### 【0007】

×86、MMX、ストリーミング SIMD エクステンション (SSE)、SSE2、SSE3、SSE4.1、および SSE4.2 命令を含む命令セットを有する Intel (登録商標) Core (商標) プロセッサにより使用されるような SIMD 技術は、アプリケーションの性能の大幅な改善を可能にした (Core および MMX は、カリフォルニア州サンタクララのインテルの登録商標または商標である)。アドバンスドベクトルエクステンション (AVX) と参照され、VEX コーディングスキームを用いる複数の SIMD エクステンションの追加的なセットも、設計され、公開されている。30

#### 【0008】

本出願に特に関連する1つの命令は、乗算命令である。高性能コンピューティングプラットフォームにおける幾つかのアルゴリズムは、幾つかの演算値を乗算する。一般に、各乗算演算は、1つの命令の実行を必要とする。

#### 【図面の簡単な説明】

#### 【0009】

本発明のより良い理解は、次の図面と併せて次の詳細な説明から得られることができる。

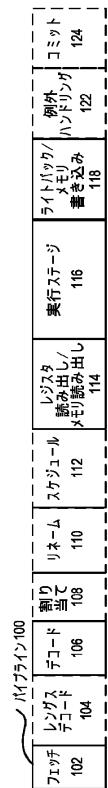

【図1A】発明の実施形態に係る典型的なインオーダフェッチ、デコード、リタイヤパイプライン、および典型的なレジスタリネーム、アウトオブオーダ発行／実行パイプラインの両方を示すブロック図である。40

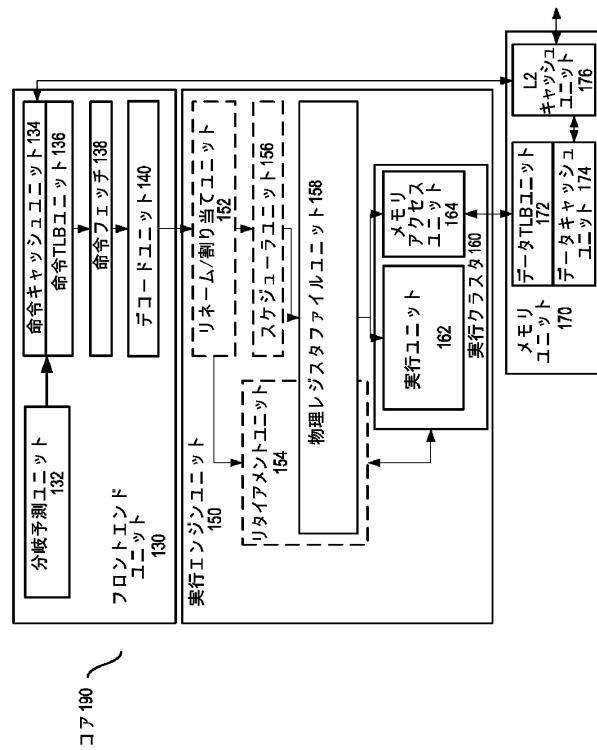

【図1B】発明の実施形態に係るインオーダフェッチ、デコード、リタイヤコアの典型的な実施形態、およびプロセッサ内に含まれる典型的なレジスタリネーム、アウトオブオーダ発行／実行アーキテクチャコアの両方を示すブロック図である。

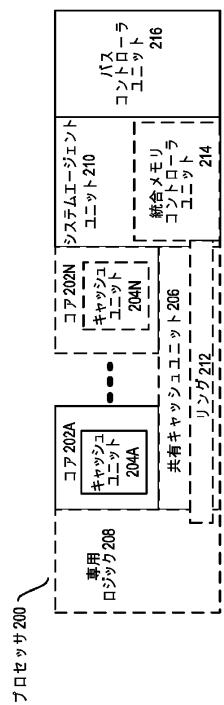

【図2】発明の実施形態に係るシングルコアプロセッサおよび統合メモリコントローラおよびグラフィックを有するマルチコアプロセッサのブロック図である。

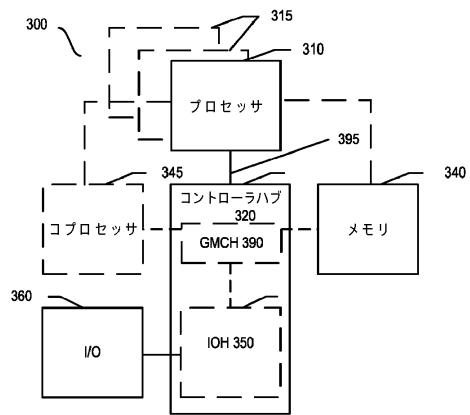

#### 【図3】本発明の一実施形態によるシステムのブロック図を示す。

#### 【図4】本発明の実施形態による第2システムのブロック図を示す。

#### 【図5】本発明の実施形態による第3システムのブロック図を示す。

#### 【図6】本発明の実施形態によるシステムオンチップ (SOC) のブロック図を示す。50

【図7】発明の実施形態に係る、ソース命令セットにおけるバイナリ命令をターゲット命令セットにおけるバイナリ命令に変換するソフトウェア命令コンバータの使用を対比するブロック図を示す。

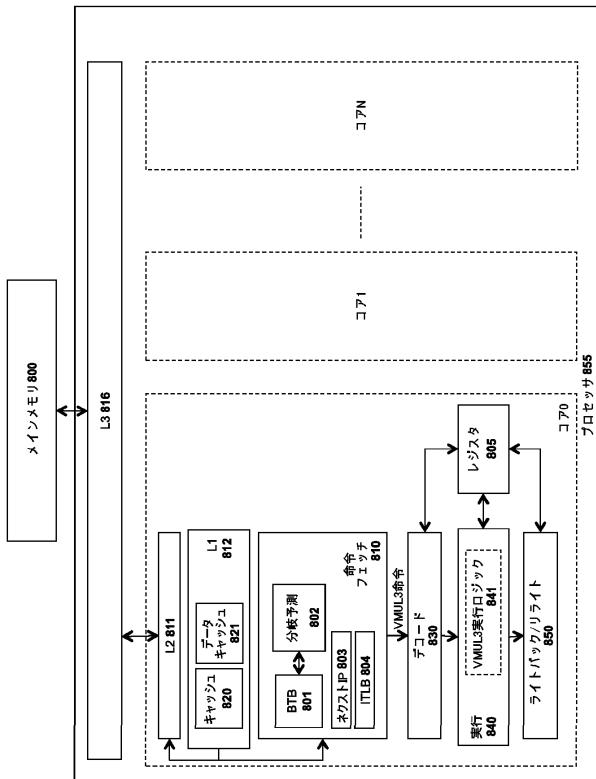

【図8】発明の実施形態が使用されてよいプロセッサーアーキテクチャの一実施形態を示す。

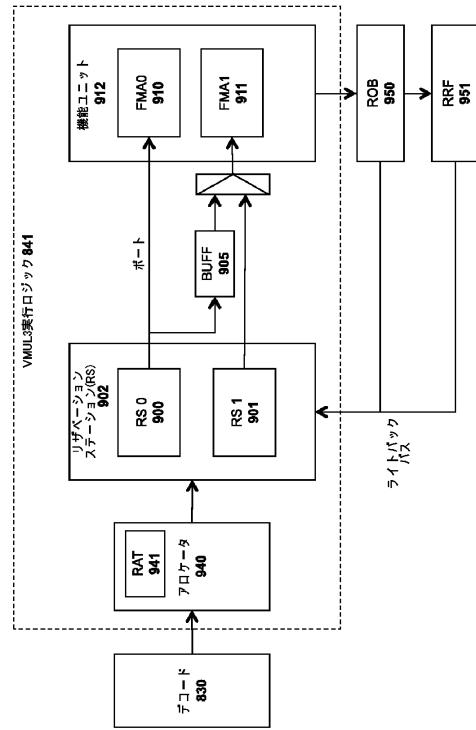

【図9A】複数の乗算演算を実行するためのアーキテクチャの一実施形態を示す。

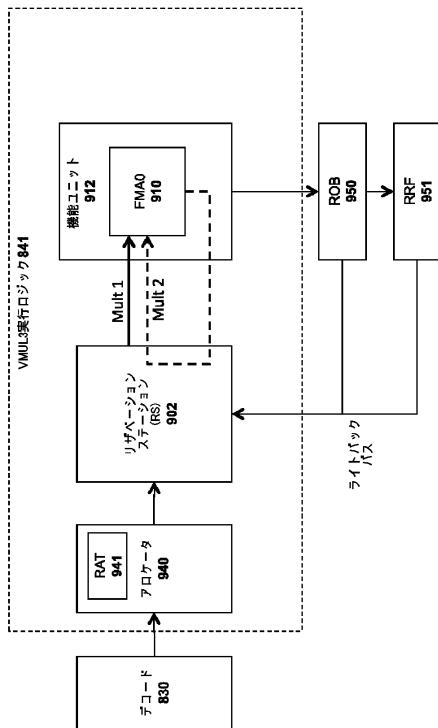

【図9B】複数の乗算演算を実行するためのアーキテクチャの別の実施形態を示す。

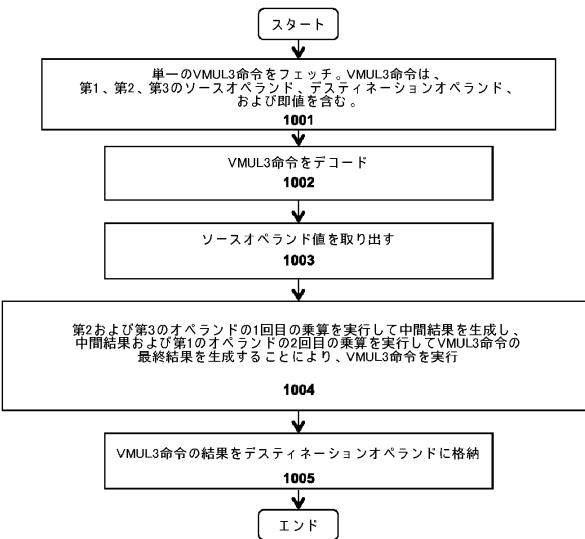

【図10】複数の乗算演算を実行するための方法の一実施形態を示す。

【図11A】発明の実施形態に係る総称ベクトル向け命令フォーマットおよびその命令テンプレートを示すブロック図である。

10

【図11B】発明の実施形態に係る総称ベクトル向け命令フォーマットおよびその命令テンプレートを示すブロック図である。

【図12A】発明の実施形態に係る典型的な特定ベクトル向け命令フォーマットのブロック図を示す。

【図12B】発明の実施形態に係る典型的な特定ベクトル向け命令フォーマットのブロック図を示す。

【図12C】発明の実施形態に係る典型的な特定ベクトル向け命令フォーマットのブロック図を示す。

【図12D】発明の実施形態に係る典型的な特定ベクトル向け命令フォーマットのブロック図を示す。

20

【図13】発明の一実施形態に係るレジスタアーキテクチャのブロック図である。

【発明を実施するための形態】

【0010】

次の説明では、説明の目的のために、多くの特定の詳細が、以下に記載される発明の複数の実施形態の完全な理解を提供するために明らかにされる。しかし、発明の複数の実施形態はこれらの特定の詳細の一部がなくても実施されてよいことは、当業者には明らかであろう。他の複数の例において、既知の構造およびデバイスは、発明の実施形態の基礎となる原理を分かりにくくしないようにブロック図形式で示される。

【0011】

典型的なプロセッサアーキテクチャおよびデータタイプ

30

図1Aは、発明の実施形態に係る典型的なインオーダフェッチ、デコード、リタイヤパイプライン、および典型的なレジスタリネームアウトオブオーダ発行／実行パイプラインの両方を示すブロック図である。図1Bは、発明の実施形態に係るインオーダフェッチ、デコード、リタイヤコアの典型的な実施形態、およびプロセッサ内に含まれる典型的なレジスタリネーム、アウトオブオーダ発行／実行アーキテクチャコアの両方を示すブロック図である。図1Aおよび図1Bにおける実線のボックスは、パイプラインおよびコアのインオーダ部分を示し、一方、破線のボックスの任意の追加は、レジスタリネーム、アウトオブオーダ発行／実行パイプライン、およびコアを示す。

【0012】

図1Aにおいて、プロセッサパイプライン100は、フェッチステージ102、レンジステコードステージ104、デコードステージ106、割り当てステージ108、リネームステージ110、スケジューリング（ディスパッチ又は発行としても知られる）ステージ112、レジスタ読み出し／メモリ読み出しステージ114、実行ステージ116、ライトバック／メモリ書き込みステージ118、例外ハンドリングステージ122、およびコミットステージ124を含む。

40

【0013】

図1Bは、実行エンジンユニット150に連結されるフロントエンドユニット130を含むプロセッサコア190を示し、両方がメモリユニット170に連結される。コア190は、縮小命令セットコンピューティング（RISC）コア、複合命令セットコンピューティング（CISC）コア、超長命令語（VLIW）コア、又はハイブリッドまたは代替

50

的コアタイプであってよい。さらに別のオプションとして、コア190は、例えば、ネットワークまたは通信コア、圧縮エンジン、コプロセッサコア、汎用コンピュータグラフィックプロセッシングユニット( GPGPU )コア、グラフィックコアなどの特定の目的のコアであってよい。

【0014】

フロントエンドユニット130は、命令キャッシュユニット134に連結される分岐予測ユニット132を含む。命令キャッシュユニット134は、命令変換索引バッファ( T L B )136に連結される。T L B 136は、命令フェッチユニット138に連結される。命令フェッチユニット138は、デコードユニット140に連結される。デコードユニット140(またはデコーダ)は、複数の命令をデコードし、出力として、1または複数のマイクロ演算、複数のマイクロコードエントリポイント、複数のマイクロ命令、その他の複数の命令、または元の複数の命令からデコードされる、そうでなければそれらを反映する、またはそれらから導出されるその他の複数の制御信号を生成してよい。デコードユニット140は、様々な異なるメカニズムを用いて実装されてよい。適当なメカニズムの例は、これに限定されるものではないが、複数のルックアップテーブル、複数のハードウェア実装、複数のプログラマブルロジックアレイ( PLA )、複数のマイクロコードリードオンリメモリ( ROM )などを含む。一実施形態では、コア190は、特定の複数のマイクロ命令のマイクロコードを(例えば、デコードユニット140内に、そうでなければフロントエンドユニット130内に)格納するマイクロコードROMまたは他の媒体を含む。デコードユニット140は、実行エンジンユニット150内でリネーム/割り当てユニット152に連結される。

【0015】

実行エンジンユニット150は、リタイアメントユニット154および1または複数のスケジューラユニット156のセットに連結されたリネーム/割り当てユニット152を含む。スケジューラユニット156は、複数の予約ステーション、中央の命令ウィンドウなどを含む任意の数の異なるスケジューラを表す。スケジューラユニット156は、物理レジスタファイルユニット158に連結される。複数の物理レジスタファイルユニット158のそれぞれは、1または複数の物理レジスタファイル、スカラ整数、スカラ浮動小数点、パックド整数、パックド浮動小数点、ベクトル整数、ベクトル浮動小数点、ステータス(例えば、実行される次の命令のアドレスである命令ポインタ)などのような1または複数の異なるデータタイプを格納する異なるものを表す。一実施形態では、物理レジスタファイルユニット158は、ベクトルレジスタユニット、書き込みマスクレジスタユニット、およびスカラレジスタユニットを備える。これらのレジスタユニットは、複数のアーキテクチャベクトルレジスタ、複数のベクトルマスクレジスタ、及び複数の汎用レジスタを提供してよい。物理レジスタファイルユニット158は、リタイアメントユニット154により重ねられて、(例えば、リオーダバッファ及びリタイアメントレジスタファイルを用いて、将来のファイル、ヒストリバッファ、及びリタイアメントレジスタファイルを用いて、レジスタマップおよび複数のレジスタのプールを用いるなど)レジスタリネームおよびアウトオブオーダ実行が実装されてよい様々な態様を示す。リタイアメントユニット154および物理レジスタファイルユニット158は、実行クラスタ160に連結される。実行クラスタ160は、1または複数の実行ユニット162のセットおよび1または複数のメモリアクセスユニット164のセットを含む。実行ユニット162は、様々な演算(例えば、シフト、加算、減算、乗算)を様々なタイプのデータ(例えば、スカラ浮動小数点、パックド整数、パックド浮動小数点、ベクトル整数、ベクトル浮動小数点)について実行してよい。幾つかの実施形態は、複数の特定の機能または複数の機能の複数のセットに専用の多くの実行ユニットを含んでよいとともに、他の実施形態は、すべての機能をすべて実行する実行ユニットの1つのみ又は複数の実行ユニットを含んでよい。特定の実施形態は、特定のタイプのデータ/複数の演算に対する別個のパイプラインを生成するので(例えば、それら自体のスケジューラユニットをそれぞれ有するスカラ整数パイプライン、スカラ浮動小数点/パックド整数/パックド浮動小数点/ベクトル整数/ベクトル

10

20

30

40

50

浮動小数点パイプライン、および／またはメモリアクセスパイプライン、物理レジスタファイルユニット、および／または実行クラスタ。別個のメモリアクセスパイプラインの場合、特定の実施形態は、このパイプラインの実行クラスタのみがメモリアクセスユニット 164 を有するように実装される。）、スケジューラユニット 156、物理レジスタファイルユニット 158、及び実行クラスタ 160 は、場合により、複数あるように示される。別個のパイプラインが用いられる場合、これらのパイプラインのうちの 1 または複数がアウトオブオーダ発行／実行され、残りがインオーダ発行／実行されてよいことは、理解されるべきである。

#### 【0016】

複数のメモリアクセスユニット 164 のセットは、メモリユニット 170 に連結される。メモリユニット 170 は、データ T L B ユニット 172 を含む。データ T L B ユニット 172 は、データキャッシュユニット 174 に連結される。データキャッシュユニット 174 は、レベル 2 (L2) キャッシュユニット 176 に連結される。一典型的な実施形態では、複数のメモリアクセスユニット 164 は、ロードユニット、ストアアドレスユニット、およびストアデータユニットを含んでよく、それぞれがメモリユニット 170 内のデータ T L B ユニット 172 に連結される。命令キャッシュユニット 134 は、さらに、メモリユニット 170 内のレベル 2 (L2) キャッシュユニット 176 に連結される。L2 キャッシュユニット 176 は、1 または複数の他のレベルのキャッシュおよび最終的にはメインメモリに連結される。

#### 【0017】

例として、典型的なレジスタリネームアウトオブオーダ発行／実行コアアーキテクチャは、次のようにパイプライン 100 を実装してよい。1) 命令フェッチ 138 が、フェッチおよびレンジスデコードステージ 102 および 104 を実行する。2) デコードユニット 140 が、デコードステージ 106 を実行する。3) リネーム／割り当てユニット 152 が、割り当てステージ 108 およびリネームステージ 110 を実行する。4) スケジューラユニット 156 が、スケジュールステージ 112 を実行する。5) 物理レジスタファイルユニット 158 およびメモリユニット 170 が、レジスタ読み出し／メモリ読み出しステージ 114 を実行する。実行クラスタ 160 が、実行ステージ 116 を実行する。6) メモリユニット 170 および物理レジスタファイルユニット 158 が、ライトバック／メモリ書き込みステージ 118 を実行する。7) 様々なユニットが、例外ハンドリングステージ 122 に関与されてよい。8) リタイアメントユニット 154 および物理レジスタファイルユニット 158 が、コミットステージ 124 を実行する。

#### 【0018】

コア 190 は、ここに記載される命令を含め、1 または複数の命令セット（例えば、 $\times$  86 命令セット（複数のより新しいバージョンに追加された幾つかの拡張を有する））、カリフォルニア州サニーベールの MIPS テクノロジーズの MIPS 命令セット、カリフォルニア州サニーベールの ARM ホールディングスの ARM 命令セット（NEON のような任意追加の複数の拡張を有する））をサポートしてよい。一実施形態では、コア 190 は、パックドデータ命令セットの拡張（例えば、AVX1、AVX2、および／または後述する総称ベクトル向け命令フォーマット（U = 0 および／または U = 1）の幾つかの形式）をサポートするロジックを含み、それにより、多くのマルチメディアアプリケーションにより用いられる複数の演算をパックドデータを用いて実行されるようにする。

#### 【0019】

コアは、マルチスレッド（演算又はスレッドの 2 またはそれより多いパラレルセットを実行）をサポートしてよいし、時間スライスされたマルチスレッド、同時マルチスレッド（ただし、单一物理コアは、物理コアが同時にマルチスレッドする複数のスレッドのそれぞれに対して論理コアを提供する）、またはそれらの組み合わせ（例えば、インテルハイパースレッド技術におけるような時間スライスされたフェッチおよびデコードおよびそのあとの同時マルチスレッド）を含む様々な態様においてそうしてよいことが理解されるべきである。

10

20

30

40

50

## 【0020】

レジスタリネームがアウトオブオーダ実行のコンテキストにおいて記載される限り、レジスタリネームがインオーダーアーキテクチャにおいて用いられてよいことが理解されるべきである。プロセッサの示された実施形態が、別個の命令およびデータキャッシュユニット 134 / 174 および共有 L2 キャッシュユニット 176 も含むのに対して、代替的な実施形態は、例えばレベル 1 (L1) 内部キャッシュまたは複数レベルの内部キャッシュのような命令およびデータの両方に対する単一の内部キャッシュを有してよい。幾つかの実施形態では、システムは、内部キャッシュとコアおよび / またはプロセッサの外部にある外部キャッシュとの組み合わせを含んでよい。代替的に、キャッシュのすべては、コアおよび / またはプロセッサの外部にあってよい。

10

## 【0021】

図 2 は、発明の実施形態に係る、1 より多いコアを有してよく、統合メモリコントローラを有してよく、また統合グラフィクスを有してよいプロセッサ 200 のブロック図である。図 2 における実線のボックスは、シングルコア 202A、システムエージェント 210、および 1 または複数のバスコントローラユニット 216 のセットを有するプロセッサ 200 を示すとともに、任意の追加の破線のボックスは、複数のマルチコア 202A-N、システムエージェントユニット 210 内の 1 または複数の統合メモリコントローラユニット 214 のセット、および専用ロジック 208 を有する代替例のプロセッサ 200 を示す。

20

## 【0022】

従って、プロセッサ 200 の異なる実装は、1) 統合グラフィクスおよび / または科学 (スループット) ロジックである専用ロジック 208 を有する CPU (1 または複数のコアを含んでよい)、および 1 または複数の汎用コアであるコア 202A-N (例えば、汎用インオーダコア、汎用アウトオブオーダコア、2 つの組み合わせ)、2) グラフィックおよび / または科学 (スループット) を主に意図する多数の専用コアであるコア 202A-N を有するコプロセッサ、および 3) 多数の汎用インオーダコアであるコア 202A-N を有するコプロセッサを含んでよい。従って、プロセッサ 200 は、例えば、ネットワークまたは通信プロセッサ、圧縮エンジン、グラフィクスプロセッサ、GPGPU (汎用グラフィック処理ユニット)、高スループット多集積コア (MIC) コプロセッサ (30 またはそれより多いコアを含む)、組み込みプロセッサなどの汎用プロセッサ、コプロセッサ、または専用プロセッサであってよい。プロセッサは、1 または複数のチップ上に実装されてよい。プロセッサ 200 は、1 または複数の基板の一部であってよいし、および / または、例えば BiCMOS、CMOS、または NMOS のような多くの処理技術のうちのいずれを用いてそれらの上に実装されてよい。

30

## 【0023】

メモリ階層は、複数の統合メモリコントローラユニット 214 のセットに連結される複数のコア、セットまたは 1 または複数の共有キャッシュユニット 206、および外部メモリ (不図示) 内に 1 または複数のレベルのキャッシュを含む。共有キャッシュユニット 206 のセットは、レベル 2 (L2)、レベル 3 (L3)、レベル 4 (L4)、または他のレベルのキャッシュ、最後のレベルのキャッシュ (LLC)、および / またはそれらの組み合わせのような 1 または複数の中間レベルキャッシュを含んでよい。一実施形態では、リングベースのインターネットユニット 212 は、統合グラフィクスロジック 208、共有キャッシュユニット 206 のセット、およびシステムエージェントユニット 210 / 統合メモリコントローラユニット 214 を相互接続するのに対して、代替的な実施形態は、そのような複数のユニットを相互接続する任意の数の周知の技術を用いてよい。一実施形態では、一貫性が、1 または複数のキャッシュユニット 206 および複数のコア 202A-N の間で維持される。

40

## 【0024】

幾つかの実施形態では、1 または複数のコア 202A-N はマルチスレッドすることができる。システムエージェント 210 は、コア 202A-N を調整および操作するそれら

50

の複数のコンポーネントを含む。システムエージェントユニット 210 は、例えば、電力制御ユニット (P C U) および表示ユニットを含んでよい。P C U は、コア 202A - N および統合グラフィクスロジック 208 の電力状態をレギュレートするのに必要なロジックおよび複数のコンポーネントであってもまたは含んでもよい。表示ユニットは、1 または複数の外部接続されたディスプレイを駆動するためのものである。

#### 【 0025 】

複数のコア 202A - N は、アーキテクチャ命令セットの観点において同種または異種であってよい。すなわち、コア 202A - N のうちの 2 またはそれより多いコアは同じ命令セットを実行できてよく、その他はその命令セットまたは異なる命令セットのサブセットのみを実行できてよい。一実施形態では、複数のコア 202A - N は、異種であり、後述する複数の「小さい」コアおよび複数の「大きい」コアの両方を含む。

#### 【 0026 】

図 3 から図 6 は、典型的なコンピュータアーキテクチャのブロック図である。ラップトップ、デスクトップ、ハンドヘルド P C、携帯用情報端末、エンジニアリングワークステーション、サーバ、ネットワークデバイス、ネットワークハブ、スイッチ、組み込みプロセッサ、デジタルシグナルプロセッサ (D S P)、グラフィックデバイス、ビデオゲームデバイス、セットトップボックス、マイクロコントローラ、携帯電話、ポータブルメディアプレーヤ、ハンドヘルドデバイス、および様々な他の電子デバイスの技術分野において既知の他のシステム設計及び構成も適当である。一般的に、ここに開示されるようなプロセッサおよび / または他の実行ロジックを組み込むことができる様々なシステムまたは電子デバイスが一般に適当である。

#### 【 0027 】

ここで図 3 を参照すると、本発明の一実施形態によるシステム 300 のブロック図が示される。システム 300 は、コントローラハブ 320 に連結される 1 または複数のプロセッサ 310、315 を含んでよい。一実施形態では、コントローラハブ 320 は、グラフィックスメモリコントローラハブ (G M C H) 390 および入出力ハブ (I O H) 350 (別個の複数のチップ上にあってよい) を含む。G M C H 390 は、メモリ 340 およびコプロセッサ 345 に連結されるメモリおよびグラフィックスコントローラを含む。I O H 350 は、入出力 (I / O) デバイス 360 を G M C H 390 に接続する。代替的に、メモリおよびグラフィックスコントローラのうちの 1 つまたは両方は、プロセッサに (ここに記載されるように) 集積され、メモリ 340 およびコプロセッサ 345 は、I O H 350 を有する單一チップ内でプロセッサ 310 およびコントローラハブ 320 に直接連結される。

#### 【 0028 】

複数の追加のプロセッサ 315 の任意の特性は、破線を用いて図 3 内に示される。各プロセッサ 310、315 は、ここに記載される処理コアの 1 または複数を含んでよく、またプロセッサ 200 の幾つかのバージョンであってよい。

#### 【 0029 】

メモリ 340 は、例えば、ダイナミックランダムアクセスメモリ (D R A M)、相変化メモリ (P C M)、または 2 つの組み合わせであってよい。少なくとも 1 つの実施形態に対して、コントローラハブ 320 は、フロントサイドバス (F S B) のようなマルチドロップバス、Qu i c k P a t h インターコネクト (Q P I) のようなポイントツーポイントインターフェース、または同様の接続 395 を介してプロセッサ 310、315 と通信する。

#### 【 0030 】

一実施形態では、コプロセッサ 345 は、例えば、高スループット M I C プロセッサ、ネットワークまたは通信プロセッサ、圧縮エンジン、グラフィックスプロセッサ、G P G P U、組み込みプロセッサなどのような専用プロセッサである。一実施形態では、コントローラハブ 320 は、統合グラフィクスアクセラレータを含んでよい。

#### 【 0031 】

10

20

30

40

50

アーキテクチャ、マイクロアーキテクチャ、熱、電力消費特性などを含むメリットメトリクスの範囲の観点において、物理リソース 310、315 の間に様々な差があるはずである。

【0032】

一実施形態では、プロセッサ 310 は、一般タイプのデータ処理演算を制御する複数の命令を実行する。複数のコプロセッサ命令は、複数の命令内に組み込まれてよい。プロセッサ 310 は、これらのコプロセッサ命令を、付属のコプロセッサ 345 により実行されるべきタイプとして認識する。従って、プロセッサ 310 は、これらのコプロセッサ命令（または複数のコプロセッサ命令を表す複数の制御信号）を、コプロセッサバスまたは他のインターフェース上でコプロセッサ 345 に発する。コプロセッサ 345 は、受信した複数のコプロセッサ命令を受け入れて実行する。

10

【0033】

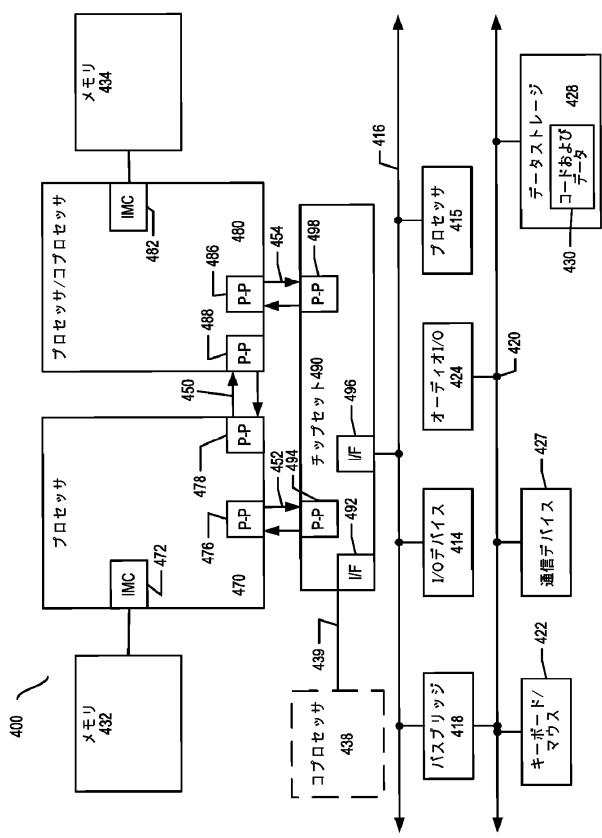

ここで図 4 を参照すると、本発明の実施形態による、第 1 のより具体的な典型的なシステム 400 のブロック図を示す。図 4 に示されるように、マイクロプロセッサシステム 400 は、ポイントツーポイントインターフェース 450 を介して連結された第 1 のプロセッサ 470 および第 2 のプロセッサ 480 を含む。プロセッサ 470 および 480 のそれぞれは、プロセッサ 200 の幾つかのバージョンであってよい。発明の一実施形態では、プロセッサ 470 および 480 はそれぞれプロセッサ 310 および 315 であり、コプロセッサ 438 はコプロセッサ 345 である。別の実施形態では、プロセッサ 470 および 480 は、それぞれ、プロセッサ 310 およびコプロセッサ 345 である。

20

【0034】

プロセッサ 470 および 480 は、それぞれ統合メモリコントローラ (IMC) ユニット 472 および 482 を含めて示されている。プロセッサ 470 は、その複数のバスコントローラユニットの一部として、ポイントツーポイント (P-P) インターフェース 476 および 478 も含む。同様に、第 2 のプロセッサ 480 は、P-P インターフェース 486 および 488 を含む。プロセッサ 470、480 は、ポイントツーポイント (P-P) インターフェース 450 を介して、P-P インターフェース回路 478、488 を用いて情報を交換してよい。図 4 に示されるように、IMC 472 および 482 は、複数のプロセッサをそれぞれメモリ、すなわちそれぞれのプロセッサにローカルに付属するメインメモリの一部であってよいメモリ 432 およびメモリ 434 に接続する。

30

【0035】

プロセッサ 470、480 は、それぞれ、ポイントツーポイントインターフェース回路 476、494、486、498 を用いて、個々の P-P インターフェース 452、454 を介してチップセット 490 と情報を交換してよい。チップセット 490 は、必要に応じて、高性能インターフェース 439 を介してコプロセッサ 438 と情報を交換してよい。一実施形態では、例えば、高スループット MIC プロセッサ、ネットワークまたは通信プロセッサ、圧縮エンジン、グラフィクスプロセッサ、GPU、組み込みプロセッサなどのようなコプロセッサ 438 は、専用プロセッサである。

【0036】

40

共有キャッシュ（不図示）は、どちらかのプロセッサまたは両方のプロセッサの外部に含まれ、さらに P-P インターフェースを介して複数のプロセッサに接続され、それにより、プロセッサが低電力モードに配置されると、どちらかまたは両方のプロセッサのローカルキャッシュ情報が共有キャッシュ内に格納されてよい。

【0037】

チップセット 490 は、インターフェース 496 を介して、第 1 のバス 416 に連結されてよい。一実施形態では、第 1 のバス 416 は、ペリフェラルコンポーネントインターフェース (PCI) バス、または PCI エクスプレスバスまたは別の第 3 世代 I/O インターフェースバスのようなバス、であってよいが、本発明の範囲はこれに限定されるものではない。

50

## 【0038】

図4に示すように、様々なI/Oデバイス414は、第1のバス416を第2のバス420に接続するバスブリッジ418とともに、第1のバス416に連結されてよい。一実施形態では、複数のコプロセッサ、複数の高スループットMICプロセッサ、GPGPUの複数のアクセラレータ（例えば、複数のグラフィクスアクセラレータまたは複数のデジタル信号処理（DSP）ユニット）、複数のフィールドプログラマブルゲートアレイ、またはいずれの他のプロセッサのような1または複数の追加のプロセッサ415は、第1のバス416に連結される。一実施形態では、第2のバス420は、ローピンカウント（LPC）バスであってよい。一実施形態では、様々なデバイスは、例えば、キーボードおよび/またはマウス422、複数の通信デバイス427、および命令/コードおよびデータ430を含んでよいディスクドライブまたは他の大容量ストレージデバイスのようなストレージユニット428を含めて、第2のバス420に連結されてよい。さらに、オーディオI/O 424は、第2のバス420に連結されてよい。なお、他のアーキテクチャも可能である。例えば、図4のポイントツーポイントアーキテクチャに代えて、システムは、マルチドロップバスまたは他のそのようなアーキテクチャを実装してよい。

## 【0039】

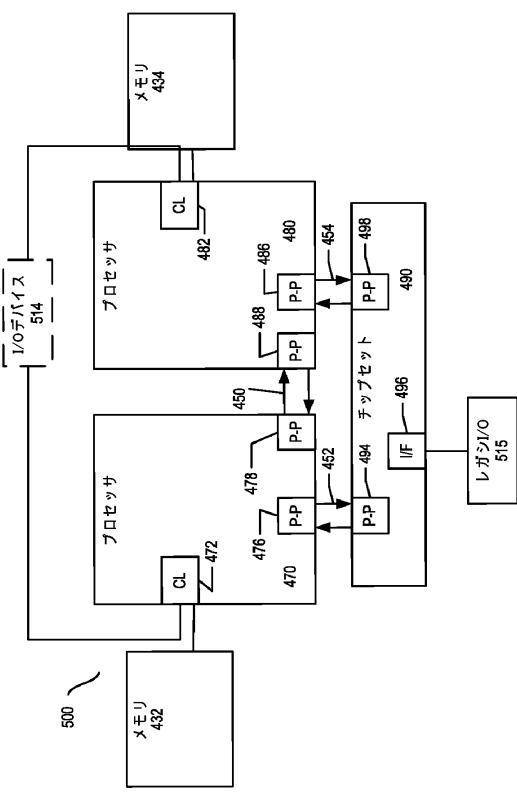

ここで図5を参照すると、本発明の実施形態による第2のより具体的な典型的なシステム500のブロック図が示される。図4および図5における同じ要素は同じ参照番号を与える、図4の特定の態様は、図5の他の態様を分かりにくくしないように図5から省略されている。

## 【0040】

図5は、プロセッサ470、480が、統合メモリおよびそれぞれI/O制御ロジック（「CL」）472および482を含んでよいことを示す。従って、CL472、482は、複数の統合メモリコントローラユニットを含み、I/O制御ロジックを含む。図5は、メモリ432、434がCL472、482に連結されるだけでなく、I/Oデバイス514も制御ロジック472、482に連結されることも示す。複数のレガシI/Oデバイス515は、チップセット490に連結される。

## 【0041】

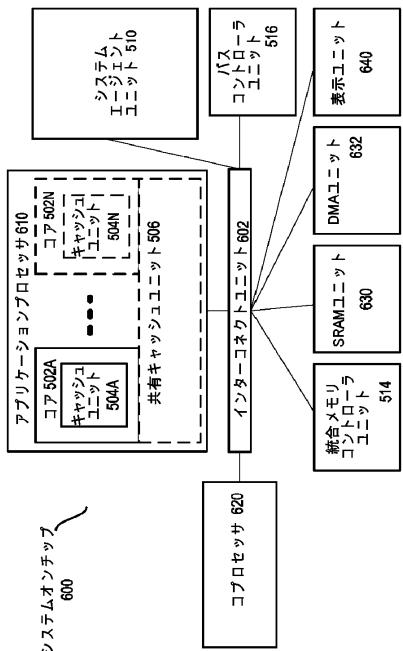

ここで図6を参照すると、本発明の実施形態によるSOC600のブロック図が示される。図2内の同様の要素は、同じ参照番号を与える。また、破線のボックスは、より高度なSOCの任意の特徴である。図6において、インターネットユニット602は、1または複数のコア502A-Nおよび共有キャッシュユニット506のセットを含むアプリケーションプロセッサ610、システムエージェントユニット510、バスコントローラユニット516、統合メモリコントローラユニット514、統合グラフィクスロジック、イメージプロセッサ、オーディオプロセッサ、およびビデオプロセッサを含んでよい1または複数のコプロセッサ620のセット、スタティックランダムアクセスメモリ（SRAM）ユニット630、ダイレクトメモリアクセス（DMA）ユニット632、および1または複数の外部ディスプレイに連結するための表示ユニット640、に連結される。一実施形態では、コプロセッサ620は、例えば、ネットワークまたは通信プロセッサ、圧縮エンジン、GPGPU、高スループットMICプロセッサ、組み込みプロセッサなどのような専用プロセッサを含む。

## 【0042】

ここに開示されるメカニズムの実施形態は、ハードウェア、ソフトウェア、ファームウェア、またはそのような複数の実装アプローチの組み合わせにおいて実装されてよい。発明の実施形態は、少なくとも1つのプロセッサ、ストレージシステム（揮発性および不揮発性メモリおよび/またはストレージ要素を含む）、少なくとも1つの入力デバイス、および少なくとも1つの出力デバイスを備える複数のプログラマブルシステム上で実行する複数のコンピュータプログラムまたはプログラムコードとして実装されてよい。

## 【0043】

図4に示されるコード430のようなプログラムコードは、ここに記載の複数の機能を

10

20

30

40

50

実行し、出力情報を生成する複数の命令を入力するために適用されてよい。出力情報は、1または複数の出力デバイスに既知の様式で適用されてよい。このアプリケーションの目的のために、処理システムは、例えば、デジタルシグナルプロセッサ (D S P)、マイクロコントローラ、特定用途向け集積回路 (A S I C)、またはマイクロプロセッサのようなプロセッサを有するいずれのシステムを含む。

【0044】

プログラムコードは、処理システムと通信するために、高級手続型またはオブジェクト指向型プログラミング言語において実装されてよい。プログラムコードは、必要に応じて、アセンブリまたは機械言語において実装されてもよい。実際、ここに記載の複数のメカニズムは、いずれの特定のプログラミング言語の範囲に限定されるものではない。いずれの場合において、言語は、コンパイル型またはインタプリタ型言語であってよい。

10

【0045】

少なくとも1つの実施形態の1または複数の態様は、機械により読み込まれると、機械に、ここに記載の技術を実行するロジックを組み立てさせるプロセッサ内の様々なロジックを表す、機械可読媒体上に格納された典型的な複数の命令により実装されてよい。「I Pコア」として知られるそのような表現は、実際にロジックまたはプロセッサを製造する複数の製造機械にロードするために、有形の機械可読媒体上に格納されて、様々な顧客または製造施設に供給されてよい。

【0046】

そのような機械可読記憶媒体は、これらに限定されないが、ハードディスク、フロッパー（登録商標）ディスクを含む他のタイプのディスク、光ディスク、コンパクトディスクリードオンリメモリ (C D - R O M)、コンパクトディスククリライタブル (C D - R W)、及び磁気光ディスクのようなストレージメディア、リードオンリメモリ (R O M)、ダイナミックランダムアクセスメモリ (D R A M) のようなランダムアクセスメモリ (R A M)、静态ランダムアクセスメモリ (S R A M)、消去可能プログラマブルリードオンリメモリ (E P R O M)、フラッシュメモリ、電気的消去可能プログラマブルリードオンリメモリ (E E P R O M)、相変化メモリ (P C M)、磁気または光カードのような半導体デバイス、または電子命令を格納するのに好適ないずれの他のタイプのメディアを含む、機械またはデバイスにより製造または形成される複数の物品の非一時的で有形の装置を含んでよい。

20

30

【0047】

従って、発明の実施形態は、複数の命令を含む、またはここに記載の構造、回路、装置、プロセッサ、および/またはシステム特徴を規定するハードウェア記述言語 (H D L) のような設計データを含む非一時的な有形の機械可読媒体も含む。そのような実施形態は、プログラム製品と参照されてもよい。

【0048】

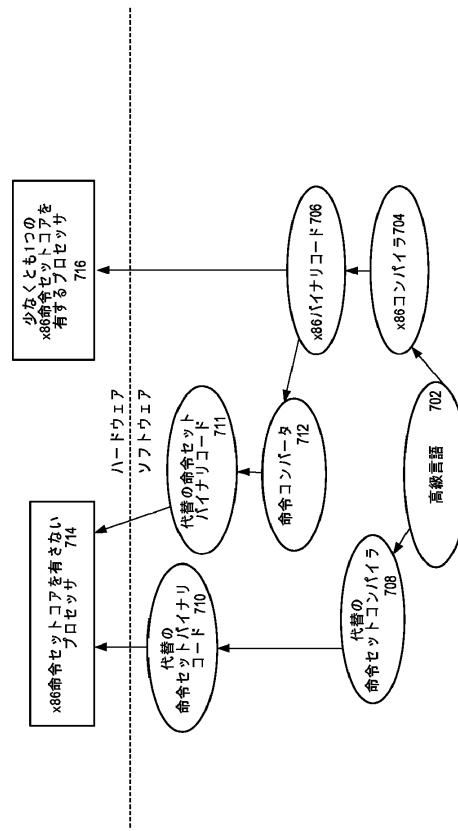

幾つかの場合では、命令コンバータは、ソース命令セットからの命令をターゲット命令セットに変換するために用いられてよい。例えば、命令コンバータは、命令を、コアにより処理される1または複数の他の命令に翻訳（例えば、静的バイナリトランスレーション、動的コンパイルを含む動的バイナリトランスレーションを用いて）、モーフィング、エミュレート、そうでなければ変換してよい。命令コンバータは、ソフトウェア、ハードウェア、ファームウェア、またはそれらの組み合わせにおいて実装されてよい。命令コンバータは、プロセッサ上に、プロセッサ外に、または一部がプロセッサ上に、一部がプロセッサ外にあってよい。

40

【0049】

図7は、発明の実施形態に係る、ソース命令セットにおけるバイナリ命令をターゲット命令セットにおけるバイナリ命令に変換するソフトウェア命令コンバータの使用を対比するブロック図である。示された実施形態では、命令コンバータは、ソフトウェア命令コンバータであるが、代替的に、命令コンバータは、ソフトウェア、ファームウェア、ハードウェア、またはそれらの様々な組み合わせにおいて実装されてよい。図7は、高級言語7

50

02におけるプログラムが、 $\times 86$ コンパイラ704を用いてコンパイルされて、少なくとも1つの $\times 86$ 命令セットコア716を用いて、プロセッサにより、本来的に実行されてよい $\times 86$ バイナリコード706を生成してよいことを示す。少なくとも1つの $\times 86$ 命令セットコア716を有するプロセッサは、互換実行する、そうでなければ、少なくとも1つの $\times 86$ 命令セットコアを用いるIntel $\times 86$ 命令セットコアの命令セットの相当の部分、または(2)少なくとも1つの $\times 86$ 命令セットコアを用いてIntel $\times 86$ 命令セットコア上で実行することを目標とされたアプリケーションまたは他のソフトウェアのオブジェクトコードのバージョンを処理することにより、少なくとも1つの $\times 86$ 命令セットコアを有するIntel $\times 86$ 命令セットコアと同じ機能を実質的に達成できるいすれのプロセッサを表す。 $\times 86$ コンパイラ704は、追加的なリンクエージ処理を用いてまたは用いないで、少なくとも1つの $\times 86$ 命令セットコア716を有するプロセッサ上で実行されることができる $\times 86$ バイナリコード706(例えば、オブジェクトコード)を生成するよう動作可能なコンパイラを表す。同様に、図7は、高級言語702におけるプログラムが、代替の命令セットコンパイラ708を用いてコンパイルされて、少なくとも1つの $\times 86$ 命令セットコア714を用いないでプロセッサ(例えば、カリフォルニア州サンベールのMIPSテクノロジーズのMIPS命令セットを実行する、および/またはカリフォルニア州サンベールのARMホールディングスのARM命令セットを実行する複数のコアを有するプロセッサ)により本来的に実行されてよい代替の命令セットバイナリコード710を生成してよいことを示す。命令コンバータ712は、 $\times 86$ バイナリコード706を、 $\times 86$ 命令セットコア714を用いないで、プロセッサにより本来的に実行されてよいコードに変換するために用いられる。この変換されたコードは、これが可能な命令コンバータは作るのが困難があるので、代替の命令セットバイナリコード710と同じである可能性は低い。しかし、変換されたコードは、一般的な演算を遂行し、代替の命令セットからの複数の命令から構成される。従って、命令コンバータ712は、エミュレーション、シミュレーション、またはいすれの他の処理を通じて、プロセッサまたは $\times 86$ 命令セットプロセッサまたはコアを有さない他の電子デバイスに、 $\times 86$ バイナリコード706を実行させるソフトウェア、ファームウェア、ハードウェア、またはそれらの組み合わせを表す。

#### 【0050】

##### 複数の乗算演算を実行するための方法および装置

以下に記載の発明の実施形態は、単一の命令において2つの乗算を実行する乗算命令のファミリーに対する複数のアーキテクチャ上の拡張を提供する。一実施形態では、複数のアーキテクチャ上の拡張は、インテル(登録商標)アーキテクチャ(IA)に提供されるが、発明の基礎となる原理はいすれの特定のISAに限定されるものではない。

#### 【0051】

既存のプロセッサアーキテクチャでは、各乗算命令は、単一の乗算演算を実行する。例えば、インテル(登録商標)アーキテクチャでは、VMULSSおよびVMULPSは、2つの単精度浮動小数点値を乗算し、VMULSDおよびVMULPDは、2つの倍精度浮動小数点値を乗算する。対照的に、ここに記載の二重乗算命令のファミリー(一実施形態においてVMUL3命令とラベルされる)は、単一の命令において2つの乗算を実行し、それにより、電力を低減し、他の複数の命令の複数のデコードスロットを解放する。一実施形態では、2つの乗算は、3つのソースオペランド上で実行される。第2及び第3のソースオペランドは、まず乗算されて、そして第1のソースオペランドにより乗算される中間結果を生成する。

#### 【0052】

図8に示されるように、発明の実施形態が実装されてよい典型的なプロセッサ855は、ここに記載の複数のVMUL3命令を実行するVMUL3実行ロジック841とともに実行ユニット840を含む。実行ユニット840が命令ストリームを実行するので、レジスタセット805は、複数のオペランド、制御データ、および他のタイプのデータに対するレジスタストレージを提供する。

10

20

30

40

50

## 【0053】

簡単のため、単一のプロセッサコア（「コア0」）の詳細が図8に示される。しかし、図8に示される各コアは、コア0のように、ロジックの同じセットを有してよいことが理解される。示されるように、各コアは、特定のキャッシュ管理ポリシーに従って複数の命令およびデータをキャッシュするための専用のレベル1（L1）キャッシュ812およびレベル2（L2）キャッシュ811を含んでよい。L1キャッシュ812は、複数の命令を格納するための別個の命令キャッシュ820およびデータを格納するための別個のデータキャッシュ821を含む。様々なプロセッサキャッシュ内に格納される複数の命令およびデータは、固定サイズ（例えば、64、128、512バイト長）であってよい複数のキャッシュラインの粒度で管理される。この典型的な実施形態の各コアは、メインメモリ800および/または共有レベル3（L3）キャッシュ816から複数の命令をフェッチするための命令フェッチユニット810、複数の命令をデコードする（例えば、複数のプログラム命令を複数のマイクロ演算または複数の「μop」にデコードする）ためのデコードユニット830、複数の命令（例えば、ここに記載されるような複数のVMUL3命令）を実行するための実行ユニット840、および複数の命令をリタイヤし、複数の結果をライトバックするためのライトバックユニット850を有する。

## 【0054】

命令フェッチユニット810は、メモリ800（または複数のキャッシュのうちの1つ）からフェッチされる次の命令のアドレスを格納するための次の命令ポインタ803、最近用いられた仮想物理命令アドレスのマップを格納して、アドレス変換の速度を向上するための命令変換索引バッファ（ITLB）804、命令分岐アドレスを投機的に予測するための分岐予測ユニット802、および分岐アドレスおよび目標アドレスを格納するための複数の分岐目標バッファ（BTB）801を含む様々な既知のコンポーネントを含む。フェッチされると、複数の命令は、デコードユニット830、実行ユニット840、およびライトバックユニット850を含む命令パイプラインの残りのステージにストリームされる。これらのユニットのそれぞれの構造および機能は、当業者に良く理解されており、発明の異なる実施形態の適切な態様を分かりにくくしないようにここでは詳細に記載されない。

## 【0055】

発明の一実施形態では、VMUL3実行ロジック841は、次のファミリーの命令を実行する。

```

VMUL3SS xmm1{k1}{z}, xmm2, xmm3/mV{er}

VMUL3PS zmm1{k1}{z}, zmm2, zmm3/B32(mV){er}

VMUL3SD xmm1{k1}{z}, xmm2, xmm3/mV{er}

VMUL3PD zmm1{k1}{z}, zmm2, zmm3/B64(mV){er}

```

ここで、xmm1 - 3およびzmm1 - 3は、単精度（32ビット）または倍精度（64ビット）浮動小数点フォーマットのいずれかで、パックドまたはスカラ浮動小数点値を格納するレジスタセット805内のレジスタである。

## 【0056】

特に、一実施形態では、VMUL3SSは、xmm1、xmm2、およびxmm3に格納される3つのスカラ、単精度浮動小数点値を乗算する。演算において、（xmm2からの）第2のオペランドは（xmm3からの）第3のオペランドにより乗算されてよく、結果は（xmm1からの）第1のオペランドにより（中間丸めを有して）乗算され、デステイネーションレジスタに格納されてよい。一実施形態では、デステイネーションレジスタは、第1のオペランド（例えば、xmm1）を格納するために用いられる同じレジスタである。

## 【0057】

一実施形態では、VMUL3PSは、zmm1、zmm2、およびzmm3に格納された3つのパックド、単精度浮動小数点値を乗算する。演算において、（zmm2からの）第2のオペランドは（zmm3からの）第3のオペランドにより乗算されてよく、結果は

( $z\ mm\ 1$ からの)第1のオペラントにより(中間丸めを有して)乗算され、デスティネーションレジスタに格納されてよい。一実施形態では、デスティネーションレジスタは、第1のオペラント(例えば、 $z\ mm\ 1$ )を格納するために用いられる同じレジスタである。

#### 【0058】

一実施形態では、 $VMUL\ 3\ SD$ は、 $x\ mm\ 1$ 、 $x\ mm\ 2$ 、および $x\ mm\ 3$ に格納された3つのスカラ、倍精度浮動小数点値を乗算する。演算において、( $x\ mm\ 2$ からの)第2のオペラントは( $x\ mm\ 3$ からの)第3のオペラントにより乗算されてよく、結果は( $x\ mm\ 1$ からの)第1のオペラントにより(中間丸めを有して)乗算され、デスティネーションレジスタに格納されてよい。一実施形態では、デスティネーションレジスタは、第1のオペラント(例えば、 $x\ mm\ 1$ )を格納するために用いられる同じレジスタである。

10

#### 【0059】

最後に、一実施形態では、 $VMUL\ 3\ PD$ は、 $z\ mm\ 1$ 、 $z\ mm\ 2$ 、および $z\ mm\ 3$ に格納された3つのパックド、倍精度浮動小数点値を乗算する。演算において、( $z\ mm\ 2$ からの)第2のオペラントは( $z\ mm\ 3$ からの)第3のオペラントにより乗算されてよく、結果は( $z\ mm\ 1$ からの)第1のオペラントにより(中間丸めを有して)乗算され、デスティネーションレジスタに格納されてよい。一実施形態では、デスティネーションレジスタは、第1のオペラント(例えば、 $z\ mm\ 1$ )を格納するために用いられる同じレジスタである。

#### 【0060】

一実施形態では、複数の $VMUL\ 3$ 命令のそれぞれの3つの即値ビット[2:0]は、複数の乗算の符号を制御するために用いられる。例えば、即値のビット0の値は、第1のオペラントの符号を制御してよい(例えば、1=負および0=正、またはその逆)。即値のビット1の値は、第2のオペラントの符号を制御してよい。また、即値のビット2の値は、第3のオペラントの符号を制御してよい。

20

#### 【0061】

一実施形態では、第1および第2のオペラントは、複数の单一命令複数データ(SIMD)レジスタから読まれ、第3のオペラントは、SIMDレジスタまたはメモリ位置から読まれることができる。

#### 【0062】

図9Aは、各 $VMUL\ 3$ の複数の $\mu\ o\ p$ に複数のリソースを割り当てるためのアロケータ940、および複数の機能ユニット912により実行される $VMUL\ 3$ の複数の $\mu\ o\ p$ をスケジュールするためのリザベーションステーション902を含む $VMUL\ 3$ 実行ロジック841の一実施形態に関連する追加的な詳細を示す。演算では、各 $VMUL\ 3$ 命令が複数の $\mu\ o\ p$ にデコードされるデコードステージ830に続いて、命令デコーダ806は、複数の $\mu\ o\ p$ をレジスタエイリアステーブル(RAT)941を含むアロケータユニット940に転送する。アウトオブオーダバイラインにおいて、アロケータユニット940は、各入力 $\mu\ o\ p$ をリオーダバッファ(ROB)950内の位置に割り当て、それにより、 $\mu\ o\ p$ の論理デスティネーションアドレスをROB950内の対応する物理デスティネーションアドレスにマッピングする。RAT941は、このマッピングを維持する。

40

#### 【0063】

$ROB\ 9\ 5\ 0$ の複数のコンテンツは、最終的に、リアルレジスタファイル(RRF)951内の複数の位置にリタイヤされてよい。RAT941は、論理アドレスにより示された値が、リタイヤの後に、 $ROB\ 9\ 5\ 0$ 内またはRRF951内の物理アドレスで見つかるかどうかを示すリアルレジスタファイルの有効ビットを格納してもよい。RRF内に見つかると、値は、現在のプロセッサのアーキテクチャ状態の一部と考えられる。このマッピングに基づいて、RAT941は、また、すべての論理ソースアドレスをROB950またはRRF951内の対応する位置に結合する。

#### 【0064】

各入力 $\mu\ o\ p$ は、また、アロケータ940により割り当てられて、リザベーションステ

10

20

30

40

50

ーション (R S ) 9 0 2 内のエントリに書き込まれる。リザベーションステーション 9 0 2 は、機能ユニット 9 1 2 による実行を待つ V M U L 3 の複数の  $\mu o p$  を組み立てる。簡単な場合において、2つの融合乗算および加算 (F M A) 機能ユニット F M A 0 9 1 0 および F M A 1 9 1 1 は、以下に記載されるように複数の V M U L 3 命令を実行する複数の乗算演算を実行する。必要に応じて、複数の結果は、ライトバックバスを介して R S 9 0 2 にライトバックされてよい。

#### 【 0 0 6 5 】

一実施形態では、複数のリザベーションステーションエントリは、複数のグループに論理的に細分され、複数のエントリを読み出すおよび書き込むためにそれぞれ必要とされるリードおよびライトポートの数を減らす。図 9 A に示される実施形態では、2つのリザベーションステーションのグループ R S 0 9 0 0 および R S 1 9 0 1 は、それぞれポート 0 および 1 を介して F M A 0 9 1 0 および F M A 1 9 1 1 機能ユニットによる V M U L 3 の複数の  $\mu o p$  の実行をスケジュールする。

#### 【 0 0 6 6 】

一実施形態では、複数の V M U L 3 命令のいずれかは、パイプラインを介して単一の  $\mu o p$  として実行されてよい。特に、 $\mu o p$  は、まず、第 2 および第 3 のオペランドの第 1 の乗算を実行して（例えば、上述のように x m m 2 / x m m 3 または z m m 2 / z m m 3 から）、中間結果を生成する F M A 0 9 1 0 ( R S 0 9 0 0 を介して) により実行される。 $\mu o p$  は、バッファユニット 9 0 5 内で遅延され、そして、F M A 1 9 1 1 ( R S 1 9 0 1 を介して) により 2 回目に実行されて、中間結果と第 1 のオペランド（例えば、x m m 1 / z m m 1 から）とを乗算する。前述のように、最終結果は、x m m 1 / z m m 1 内に格納されてよい。更に、述べたように、V M U L 3 命令の即値は、3 つのソースオペランドのそれぞれの符号を特定してよい。一実施形態では、 $\mu o p$  の第 2 の発行は、命令を再発行する前に、正確に F M A レイテンシ（例えば、5 クロックサイクル）待たされる（バッファ 9 0 5 を介して）。

#### 【 0 0 6 7 】

様々な既存のデータバイパスは、ポート 1 の F M A 1 9 1 1 に中間結果を提供するために用いられてよい。一実施形態では、中間結果は、R O B 9 5 0 、または F M A 1 9 1 1 によりそこから読み出され、用いられてよいいずれの他の記憶位置内に一時的に格納される。一実施形態では、ライトバックバスは、中間結果をポート 1 を介して F A M 1 9 1 1 に利用できるようにする R S 1 9 0 1 に中間結果を提供するために用いられてよい。しかし、発明の基礎となる原理は、中間結果を F A M 1 9 1 1 に提供する任意の特定のやり方に限定されない。さらに、R O B 9 5 0 が図 9 A に示されるように、幾つかのプロセッサの実装（例えば、複数のインオーダパイプライン）において、R O B 9 5 0 は用いられず、異なる形式のストレージが、中間結果および実行に続く最終結果を格納するために用いられてよいことが理解される。

#### 【 0 0 6 8 】

図 9 B に示されるように、2つの機能ユニットは、発明の基礎となる原理を実装するのに必要ではない。詳細には、この実施形態において、同じ機能ユニット (F M A 0 9 1 0) は、続けて 2 回、V M U L 3 の  $\mu o p$  を実行して、最終結果を生成する。すなわち、F M A 0 9 1 0 は、第 2 および第 3 のオペランドの間の第 1 の乗算を実行し、中間結果および  $\mu o p$  をそれ自体を介して戻して再循環して、第 2 の乗算（完了すると、パイプラインの残りを通過する）を実行する。一実施形態では、 $\mu o p$  の第 2 の反復は、リザベーションステーション 9 0 2 を介して送信するよう示され、再循環は、単に、機能ユニットステージ 9 1 2 内で実行される（すなわち、機能ユニットステージ 9 1 2 内で一時バッファストレージを用いて F M A 0 9 1 0 からそれ自体に直接）。さらに、別の実装では、複数の機能ユニット 9 1 2 のセット内の新しい専用の機能ユニットは、V M U L 3 命令を独立して（すなわち、融合乗算および加算機能ユニットを用いないで）実行する。

#### 【 0 0 6 9 】

上記の実施形態は、1 つの命令のみがデコードされたような、2 つの V M U L 命令を用

10

20

30

40

50

いる場合より改善された電力消費を提供する。さらに、一時的なソースが複数のバイパスを介して読み出されることが保証されたことで、データはレジスタファイルから読み出される必要はない。

#### 【0070】

幾つかの要素がともに乗算される複数のアプリケーションでは、乗算命令の数は、ここに記載の複数のVMUL3命令を利用することで2で除算されることができる。例として、ベクトル化することができる、ただし複数の浮動小数点値が乗算される長いループに対して、VMUL3は、命令数を仮想的に2減らすのに用いられてよい。

#### 【0071】

複数の乗算演算を実行するための方法の一実施形態が、図10に示される。1001にて、単一のVMUL3命令が、メモリサブシステムからフェッチされる。述べたように、VMUL3命令は、第1、第2、第3のソースオペランド、デスティネーションオペランド、および即値を含む。1002にて、VMUL3命令は、複数のμopにデコードされる。上述のように、一実施形態では、単一の乗算μopが生成されてよい（および、VMUL3命令を完了するのに必要とされる2つの乗算演算のために2回実行されてよい）。

#### 【0072】

1003にて、複数のソースオペランド値が、複数の機能ユニットによる実行のための準備として取り出される。この演算は、例えば、リザベーションステーション902および/またはアロケータユニット940により実行されてよい。

#### 【0073】

1004にて、VMUL3命令が実行される。一実施形態では、乗算μopが、一度、第2及び第3のオペランドを用いて実行されて、中間結果を生成する。μopは、そして2回目に、中間結果および第1のオペランドを用いて実行されて、最終結果（すなわち、第1、第2、及び第3のソースオペランドの乗算）を生成する。述べたように、複数のソースオペランドのそれぞれの符号は、3ビット中間値として提供されてよい。

#### 【0074】

1005にて、VMUL3命令の結果が、1または複数の続く演算のためにそこから読み出されてよいデスティネーションオペランドの位置（例えば、レジスタ）に格納される。

#### 【0075】

##### 典型的な命令フォーマット

ここに記載の命令の複数の実施形態は、異なるフォーマットで実施されてよい。更に、典型的な複数のシステム、複数のアーキテクチャ、および複数のパイプラインが以下に詳述される。命令の複数の実施形態は、そのような複数のシステム、複数のアーキテクチャ、および複数のパイプライン上で実行されてよいが、詳述されるそれらに限定されるものではない。

#### 【0076】

ベクトル向け命令フォーマットは、複数のベクトル命令（例えば、複数のベクトル演算に固有の特定の複数のフィールドがある）に好適な命令フォーマットである。複数の実施形態は、ベクトルおよびスカラ演算の両方がベクトル向け命令フォーマットを通じてサポートされるよう記載され、代替的な複数の実施形態は、ベクトル向け命令フォーマットを通じてサポートされるベクトル演算のみを用いる。

#### 【0077】

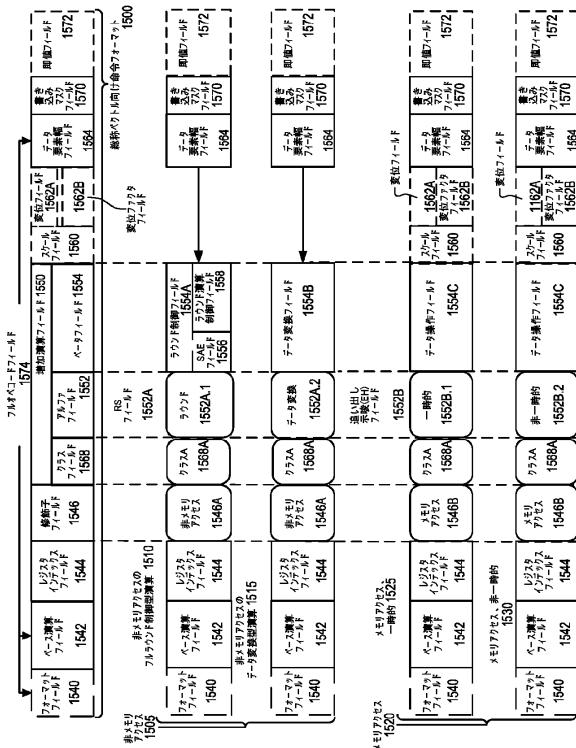

図11Aおよび図11Bは、発明の実施形態に係る総称ベクトル向け命令フォーマットおよびその複数の命令テンプレートを示すブロック図である。図11Aは、発明の実施形態に係る総称ベクトル向け命令フォーマットおよびそのクラスAの複数の命令テンプレートを示すブロック図であり、図11Bは、発明の実施形態に係る総称ベクトル向け命令フォーマットおよびそのクラスBの複数の命令テンプレートを示すブロック図である。詳細には、総称ベクトル向け命令フォーマット1500に対して、両方が非メモリアクセス1505の命令テンプレートおよびメモリアクセス1520の命令テンプレートを含

10

20

30

40

50

むクラスAおよびクラスBの命令テンプレートが定義される。ベクトル向け命令フォーマットのコンテキストにおける総称(generic)なる用語は、いずれの固有の命令セットに関連付けられていない命令フォーマットを意味する。

【0078】

発明の複数の実施形態は、ベクトル向け命令フォーマットが以下をサポートするように記載される。32ビット(4バイト)または64ビット(8バイト)データ要素幅(またはサイズ)を有する64バイトベクトルオペランド長(またはサイズ)(従って、16ダブルワードサイズ要素または代替的に8クワッドワードサイズ要素のいずれからなる64バイトベクトル)。16ビット(2バイト)または8ビット(1バイト)データ要素幅(またはサイズ)を有する64バイトベクトルオペランド長(またはサイズ)。32ビット(4バイト)、64ビット(8バイト)、16ビット(2バイト)、または8ビット(1バイト)データ要素幅(またはサイズ)を有する32バイトベクトルオペランド長(またはサイズ)。および32ビット(4バイト)、64ビット(8バイト)、16ビット(2バイト)、または8ビット(1バイト)データ要素幅(またはサイズ)を有する16バイトベクトルオペランド長(またはサイズ)。また、代替的な複数の実施形態は、より多い、より少ない、または異なるデータ要素幅(例えば、168ビット(16バイト)データ要素幅)を有するより多い、より少ない、および/または異なるベクトルオペランドサイズ(例えば、256バイトベクトルオペランド)をサポートしてよい。

10

【0079】

図11A内のクラスAの複数の命令テンプレートは、1)非メモリアクセス1505の複数の命令テンプレート内に示される非メモリアクセス、完全ラウンド制御型演算1510の命令テンプレートおよび非メモリアクセス、データ変換型演算1515の命令テンプレート、および2)メモリアクセス1520の複数の命令テンプレート内に示されるメモリアクセス、一時的1525の命令テンプレートおよびメモリアクセス、非一時的1530の命令テンプレートを含む。図11B内のクラスBの複数の命令テンプレートは、1)非メモリアクセス1505の複数の命令テンプレート内に示される非メモリアクセス、書き込みマスク制御、部分ラウンド制御型演算1516の命令テンプレートおよび非メモリアクセス、書き込みマスク制御、VSIZE型演算1517の命令テンプレート、および2)メモリアクセス1520の複数の命令テンプレート内に示されるメモリアクセス、書き込みマスク制御1527の命令テンプレートを含む。

20

30

【0080】

総称ベクトル向け命令フォーマット1500は、図11Aおよび図11Bに順に示され、以下に列挙される次の複数のフィールドを含む。

【0081】

フォーマットフィールド1540 - このフィールド内の特定の値(命令フォーマット識別子値)は、ベクトル向け命令フォーマットを、従って、命令ストリームにおけるベクトル向け命令フォーマット内の複数の命令の複数の発生をユニークに特定し。そのように、このフィールドは、総称ベクトル向け命令フォーマットのみを有する命令セットに必要とされないという意味において任意である。

【0082】

40

ベース演算フィールド1542 - そのコンテンツは、異なるベース演算を区別する。

【0083】

レジスタインデックスフィールド1544 - そのコンテンツは、直接またはアドレス生成を介して、複数のレジスタ内またはメモリ内にあるソースおよびデスティネーションオペランドの位置を特定する。これらは、P×Q(例えば、32×516、16×168、32×1024、64×1024)レジスタファイルからNのレジスタを選択するのに十分な数のビットを含む。一実施形態では、Nは3つのソースおよび1つのデスティネーションレジスタに及んでよく、代替的な複数の実施形態はより多いまたはより少ないソースおよびデスティネーションレジスタをサポートしてよい(例えば、2つのソースまでサポートしてよい。ただし、これらのソースのうちの1つはデスティネーションとしてもふる

50

まう。また、3つのソースまでサポートしてよい。ただし、これらのソースのうちの1つはデスティネーションとしてもふるまう。また、2つのソースおよび1つのデスティネーションまでサポートしてよい。)

【0084】

修飾子フィールド1546 - そのコンテンツは、そうでないものから、すなわち非メモリアクセス1505の複数の命令テンプレートおよびメモリアクセス1520の複数の命令テンプレートの間で、メモリアクセスを特定する総称ベクトル命令フォーマット内の複数の命令の複数の発生を区別する。複数のメモリアクセス演算は、(幾つかのケースでは、複数のレジスタ内の複数の値を用いてソースおよび/またはデスティネーションアドレスを特定する)メモリ階層を読み出すおよび/または書き込み、複数の非メモリアクセス演算はそれをしない(例えば、ソースおよび複数のデスティネーションはレジスタである)。一実施形態では、このフィールドは、また、3つの異なる態様の間で選択して、複数のメモリアドレス算出を実行し、代替的な複数の実施形態はより多い、より少ない、または異なる態様をサポートして、複数のメモリアドレス算出を実行してよい。

10

【0085】

増加演算フィールド1550 - そのコンテンツは、様々な異なる演算のうちのどの1つがベース演算に加えて実行されるかを区別する。このフィールドは、コンテキスト固有である。発明の一実施形態では、このフィールドは、クラスフィールド1568、アルファフィールド1552、およびベータフィールド1554に分割される。増加演算フィールド1550は、2、3、または4つの命令ではなく単一の命令において実行される複数の演算の共通グループを可能とする。

20

【0086】

スケールフィールド1560 - そのコンテンツは、メモリアドレス生成のためのインデックスフィールドのコンテンツのスケーリングを可能とする(例えば、アドレス生成に対して2のスケール乗のインデックス+ベースを用いる)。

【0087】

変位フィールド1562A - そのコンテンツは、メモリアドレス生成の一部として用いられる(例えば、アドレス生成に対して2のスケール乗のインデックス+ベース+変位を用いる)。

【0088】

30

変位ファクタフィールド1562B(なお、変位ファクタフィールド1562Bの直上の変位フィールド1562Aの並置は1または他が用いられるることを示す) - そのコンテンツは、アドレス生成の一部として用いられる。それは、メモリアクセスのサイズ(N)によりスケールされる変位ファクタを特定する。ただし、Nは、メモリアクセスにおけるバイト数である(例えば、アドレス生成に対して2のスケール乗のインデックス+ベース+スケールされた変位を用いる)。冗長下位ビットは無視され、従って、変位ファクタフィールドのコンテンツは、複数のメモリオペランドの総サイズ(N)により乗算されて、実効アドレスの計算において用いられる最終変位を生成する。Nの値は、(ここに記載の)フルオペコードフィールド1574およびデータ操作フィールド1554Cに基づいて、実行時に、プロセッサハードウェアにより決定される。変位フィールド1562Aおよび変位ファクタフィールド1562Bは、それらは非メモリアクセス1505の複数の命令テンプレートに対して用いられないという意味において任意であり、および/または異なる実施形態は2つのうちの1つのみを実装してよい、またはいずれも実装しなくてよい。

40

【0089】

データ要素幅フィールド1564 - そのコンテンツは、多くのデータ要素幅のうちのどの1つが用いられるかを区別する(幾つかの実施形態では、すべての命令に対して、他の複数の実施形態では、複数の命令のうちの幾つかのみに対して)。このフィールドは、複数のオペコードの幾つかの態様を用いて、1つのデータ要素幅のみがサポートされる、および/または複数のデータ要素幅がサポートされる場合、必要とされないという意味において任意である。

50

## 【0090】

書き込みマスクフィールド1570 - そのコンテンツは、データ要素の位置に基づいて、デスティネーションベクトルオペランド内のそのデータ要素の位置がベース演算および増加演算の結果を反映するかどうかを制御する。クラスAの複数の命令テンプレートは、差込みライトマスクをサポートし、クラスBの複数の命令テンプレートは、差込みおよびゼロ化ライトマスクの両方をサポートする。複数の差込み、ベクトルマスクは、デスティネーション内の複数の要素のいずれのセットに、いずれの演算（ベース演算および増加演算により特定される）の実行中のアップデートからプロテクトされることを可能とする。他の一実施形態では、対応するマスクビットが0を有するデスティネーションの各要素の古い値を保存する。対照的に、ゼロ化ベクトルマスクは、デスティネーション内の複数の要素のいずれのセットに、いずれの演算（ベース演算および増加演算により特定される）の実行中にゼロ化されることを可能とする。一実施形態では、対応するマスクビットが0値を有するとき、デスティネーションの要素が0にセットされる。この機能性のサブセットは、実行されている演算のベクトル長を制御する能力である（すなわち、複数の要素のスパンが1つめから最後の1つまで変更される）。しかし、変更される複数の要素が連続する必要はない。従って、書き込みマスクフィールド1570は、複数のロード、複数のストア、算術、論理等を含む複数の部分的なベクトル演算を可能とする。発明の複数の実施形態は、書き込みマスクフィールド1570のコンテンツが、用いられる書き込みマスクを含む多くの書き込みマスクレジスタのうちの1つを選択する（従って、書き込みマスクフィールド1570のコンテンツは、間接的に、実行されるマスキングを特定する）ように記載され、代替的な実施形態は、代わりにまたは追加的に、書き込みマスクフィールド1570のコンテンツに、直接、実行されるマスキングを特定させる。10 20

## 【0091】

即値フィールド1572 - そのコンテンツは、即値の指定を可能とする。このフィールドは、即値をサポートしない総称ベクトル向けフォーマットの実装において存在せず、即値を用いない複数の命令において存在しないという意味において任意である。

## 【0092】

クラスフィールド1568 - そのコンテンツは、異なるクラスの複数の命令の間で区別する。図11Aおよび図11Bを参照して、このフィールドのコンテンツは、クラスAおよびクラスBの複数の命令の間で選択する。図11Aおよび図11Bにおいて、複数の丸角の正方形は、フィールド内に特定の値があることを示すために用いられる（例えば、図11Aおよび図11Bのそれぞれにクラスフィールド1568に対してクラスA1568A及びクラスB1568B）。

## 【0093】

## クラスAの命令テンプレート

クラスAの非メモリアクセス1505の複数の命令テンプレートの場合、アルファフィールド1552は、そのコンテンツが、複数の異なる増加演算型のどの1つが実行されるかを区別するRSフィールド1552Aとして解釈され（例えば、ラウンド1552A.1およびデータ変換1552A.2はそれぞれ非メモリアクセス、ラウンドタイプ演算1510および非メモリアクセス、データ変換型演算1515の複数の命令テンプレートに対して特定される）、ベータフィールド1554は、指定される型の複数の演算のうちのいずれが実行されるかを区別する。非メモリアクセス1505の複数の命令テンプレート内には、スケールフィールド1560、変位フィールド1562A、および変位スケールフィールド1562Bは存在しない。

## 【0094】

## 非メモリアクセスの命令テンプレート - 完全ラウンド制御型演算

非メモリアクセスの完全ラウンド制御型演算1510の命令テンプレートにおいて、ベータフィールド1554は、そのコンテンツが静的丸め込みを提供するラウンド制御フィールド1554Aとして解釈される。発明の記載の複数の実施形態では、ラウンド制御フィールド1554Aは、浮動小数点例外（SAE）フィールド1556およびラウンド演

10

20

30

40

50

算制御フィールド 1558 のすべての抑制を含み、代替的な複数の実施形態は、これらのコンセプトの両方をサポートし、同じフィールドにエンコードしてよく、またはこれらのコンセプト / フィールドの 1 つまたは他を単に有する（例えば、ラウンド演算制御フィールド 1558 のみを有してよい）。

【0095】

S A E フィールド 1556 - そのコンテンツは、例外イベント報告をディスエーブルするか否かを区別する。S A E フィールド 1556 のコンテンツが可能な抑制を示すと、与えられた命令はすべての種類の浮動小数点例外フラグを報告せず、すべての浮動小数点例外処理部を立ち上げない。

【0096】

ラウンド演算制御フィールド 1558 - そのコンテンツは、複数のラウンド演算のグループのどの 1 つが実行するかを区別する（例えば、切り上げ、切り捨て、ゼロへの丸め、および最近接丸め）。従って、ラウンド演算制御フィールド 1558 は、命令に基づいてラウンド演算モードの変更を可能とする。プロセッサが複数のラウンド演算モードを指定するための制御レジスタを含む発明の一実施形態では、ラウンド演算制御フィールド 1550 のコンテンツは、そのレジスタ値を上書きする。

【0097】

非メモリアクセスの命令テンプレート：データ変換型演算

非メモリアクセスのデータ変換型演算 1515 の命令テンプレートにおいて、ベータフィールド 1554 は、そのコンテンツが多くのデータ変換（例えば、データ変換なし、スウィズル、ブロードキャスト）のうちのどの 1 つが実行されるかを区別するデータ変換フィールド 1554B として解釈される。

【0098】

クラス A のメモリアクセス 1520 の命令テンプレートの場合、アルファフィールド 1552 は、そのコンテンツが複数の追い出し示唆のうちのどの 1 つが用いられるかを区別する追い出し示唆フィールド 1552B として解釈され（図 12A では、一時的 1552B.1 および非一時的 1552B.2 は、それぞれ、メモリアクセス、一時的 1525 の命令テンプレートおよびメモリアクセス、非一時的 1530 の命令テンプレートに対して特定される）、ベータフィールド 1554 は、そのコンテンツが多くのデータ操作演算（プリミティブとも知られる）のうちのどの 1 つが実行されるかを区別するデータ操作フィールド 1554C として解釈される（例えば、操作なし、ブロードキャスト、ソースのアップコンバージョン、デスティネーションのダウンコンバージョン）。メモリアクセス 1520 の複数の命令テンプレートは、スケールフィールド 1560、任意で変位フィールド 1562A または変位スケールフィールド 1562B を含む。

【0099】

複数のベクトルメモリ命令は、変換サポートを用いて、メモリからのベクトルロードおよびメモリへのベクトルストアを実行する。正規の複数のベクトル命令を用いるように、複数のベクトルメモリ命令は、データ要素ごとの様式で、実際に転送され、書き込みマスクとして選択されるベクトルマスクの複数のコンテンツにより命令される複数の要素を用いて、メモリから / ヘデータを転送する。

【0100】

メモリアクセスの命令テンプレート - 一時的

一時的なデータは、キャッシュにより利益を得るのに十分にすぐに再利用され得るデータである。しかし、これは示唆であり、異なるプロセッサは、示唆を完全に無視することを含め、それを異なる態様で実装してよい。

【0101】

メモリアクセスの命令テンプレート - 非一時的

非一時的データは、第 1 レベルキャッシュにキャッシュすることより利益を得るのに十分にすぐに再利用され得るデータであり、削除の優先度を与えられるべきである。しかし、これは示唆であり、異なるプロセッサは、示唆を完全に無視することを含め、それを異

10

20

30

40

50

なる態様で実装してよい。

【0102】

クラスBの命令テンプレート

クラスBの命令テンプレートの場合、アルファフィールド1552は、そのコンテンツが、書き込みマスクフィールド1570により制御される書き込みマスキングが差込みまたはゼロ化であるべきかどうかを区別する書き込みマスク制御(Z)フィールド1552Cとして解釈される。

【0103】

クラスBの非メモリアクセス1505の複数の命令テンプレートの場合、ベータフィールド1554の一部は、そのコンテンツが、異なる増加演算型のうちのどの1つが実行されるかを区別するRLフィールド1557Aとして解釈され(例えば、ラウンド1557A.1およびベクトル長(VSIZE)1557A.2は、それぞれ、非メモリアクセス、書き込みマスク制御の部分ラウンド制御型演算1516の命令テンプレートおよび非メモリアクセス、書き込みマスク制御、VSIZE型演算1517の命令テンプレートに対して特定される)、ベータフィールド1554の残りは、指定される型の複数の演算のうちのどれが実行されるかを区別する。非メモリアクセス1505の複数の命令テンプレートには、スケールフィールド1560、変位フィールド1562A、および変位スケールフィールド1562Bは存在しない。

10

【0104】

非メモリアクセス、書き込みマスク制御の部分ラウンド制御型演算1516の命令テンプレートでは、ベータフィールド1554の残りは、ラウンド演算フィールド1559Aとして解釈され、例外イベント報告がディスエーブルされる(与えられた命令は、すべての種類の浮動小数点例外フラグを報告せず、すべての浮動小数点例外処理部を立ち上げない)。

20

【0105】

ラウンド演算制御フィールド1559A - ラウンド演算制御フィールド1558と同じように、そのコンテンツは、複数のラウンド演算のグループのどの1つが実行するかを区別する(例えば、切り上げ、切り捨て、ゼロへの丸め、および最近接丸め)。従って、ラウンド演算制御フィールド1559Aは、命令に基づいて、ラウンド演算モードの変更を可能とする。プロセッサがラウンド演算モードを指定するための制御レジスタを含む発明の一実施形態では、ラウンド演算制御フィールド1550のコンテンツはそのレジスタ値を上書きする。

30

【0106】

非メモリアクセス、書き込みマスク制御、VSIZE型演算1517の命令テンプレートにおいて、ベータフィールド1554の残りは、そのコンテンツが多くデータベクトル長のどの1つが実行されるか(例えば、168、256、または516バイト)を区別するベクトル長フィールド1559Bとして解釈される。

【0107】

クラスBのメモリアクセス1520の命令テンプレートの場合、ベータフィールド1554の一部は、そのコンテンツがブロードキャストタイプのデータの操作演算が実行されるか否かを区別するブロードキャストフィールド1557Bとして解釈され、ベータフィールド1554の残りはベクトル長フィールド1559Bとし解釈される。メモリアクセス1520の複数の命令テンプレートは、スケールフィールド1560、および任意で変位フィールド1562Aまたは変位スケールフィールド1562Bを含む。

40

【0108】

総称ベクトル向け命令フォーマット1500に関連して、フルオペコードフィールド1574は、フォーマットフィールド1540、ベース演算フィールド1542、およびデータ要素幅フィールド1564を含んで示される。一実施形態は、フルオペコードフィールド1574がこれらのフィールドのすべてを含むように示され、フルオペコードフィールド1574は、それらのすべてをサポートしない複数の実施形態では、これらのフィー

50

ルドのすべてより少ないフィールドを含む。フルオペコードフィールド 1574 は、演算コード（オペコード）を提供する。

【0109】

増加演算フィールド 1550、データ要素幅フィールド 1564、および書き込みマスクフィールド 1570 は、これらの特徴を、命令に基づいて、総称ベクトル向け命令フォーマットにおいて特定されるようとする。

【0110】

書き込みマスクフィールドおよびデータ要素幅フィールドの組み合わせは、それらがマスクを異なるデータ要素幅に基づいて適用されることを可能とする型付けされた複数の命令を生成する。

10

【0111】

クラス A およびクラス B 内の様々な命令テンプレートは、異なる状況において有益である。発明の幾つかの実施形態では、異なるプロセッサまたはプロセッサ内の異なるコアは、クラス A のみ、クラス B のみ、または両クラスをサポートしてよい。例えば、汎用コンピューティングのために意図された高性能汎用アウトオブオーダコアは、クラス B のみをサポートしてよく、主にグラフィックおよび / または科学（スループット）コンピューティングのために意図されたコアは、クラス A のみをサポートしてよく、両方のために意図されたコアは、両方をサポートしてよい（もちろん、両方のクラスからのすべてのテンプレートおよび命令ではなく、両方のクラスからの複数のテンプレートおよび複数の命令の幾つかのミックスを有するコアは発明の範囲内である）。また、単一のプロセッサは、すべてが同じクラスをサポートする、または異なるコアが異なるクラスをサポートするマルチコアを含んでよい。例えば、別個のグラフィックおよび複数の汎用コアを有するプロセッサにおいて、主にグラフィックおよび / または科学コンピューティングのために意図された複数のグラフィックコアの 1 つは、クラス A のみをサポートしてよく、複数の汎用コアのうちの 1 または複数は、クラス B のみをサポートする汎用コンピューティングのために意図されたアウトオブオーダ実行およびレジスタリネームを有する高性能汎用コアであってよい。別個のグラフィックコアを有さない別のプロセッサは、クラス A およびクラス B の両方をサポートする 1 または複数の汎用インオーダまたはアウトオブオーダコアを含んでよい。もちろん、1 つのクラスからの複数の機能は、発明の異なる実施形態において他のクラスに実装されてもよい。高級言語で書かれた複数のプログラムは、1) 実行のために目標プロセッサによりサポートされるクラスの複数の命令のみを有する形式、または 2) すべてのクラスの複数の命令の異なる組み合わせを用いて書かれた代替的な複数のルーチンを有し、現在コードを実行しているプロセッサによりサポートされる複数の命令に基づいて実行する複数のルーチンを選択する制御フローコードを有する形式を含む、様々な異なる実行可能な形式に入れられる（例えば、ジャストインタイムにコンパイルされるまたは静的にコンパイルされる）。

20

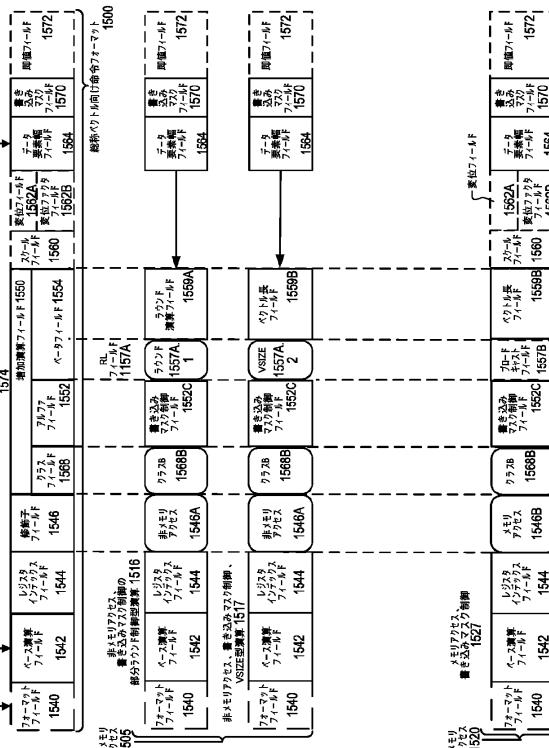

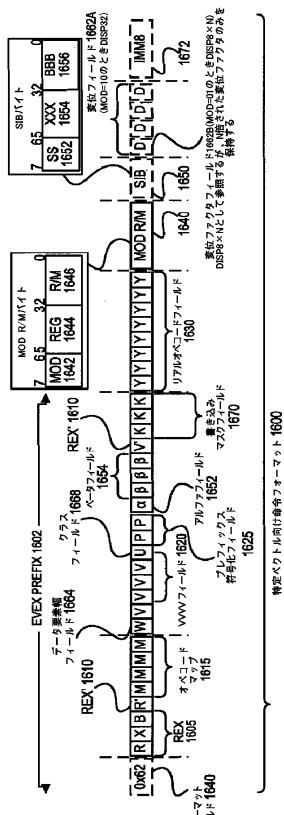

【0112】

図 12A から図 12D は、発明の複数の実施形態に係る典型的な特定ベクトル向け命令フォーマットを示すブロック図である。図 12A から図 12D は、複数のフィールドの位置、サイズ、解釈、および順序と、これらのフィールドの幾つかに対する複数の値を特定するという意味において固有である特定ベクトル向け命令フォーマット 1600 を示す。特定ベクトル向け命令フォーマット 1600 は、 $\times 86$  命令セットを拡張するために用いられてよく、従って、複数のフィールドのうちの幾つかは、既存の $\times 86$  命令セットおよびそのエクステンション（例えば、AVX）において用いられるそれらと同様または同じである。このフォーマットは、複数のエクステンションを有する既存の $\times 86$  命令セットのプレフィックス符号化フィールド、実オペコードバイトフィールド、MOD R/M フィールド、SIB フィールド、変位フィールド、および複数の即値フィールドとの一致を維持する。図 12A から図 12D からの複数のフィールドがマップされる図 11A および図 11B からの複数のフィールドが示される。

30

【0113】

40

50

発明の複数の実施形態は、説明の目的のため、総称ベクトル向け命令フォーマット1500のコンテキストにおいて特定ベクトル向け命令フォーマット1600を参照して記載されるが、発明は、特許請求の範囲に記載されたものを除いて特定ベクトル向け命令フォーマット1600に限定されるものではないことが理解されるべきである。例えば、総称ベクトル向け命令フォーマット1500は、様々なフィールドの様々な可能なサイズを予想し、特定ベクトル向け命令フォーマット1600は、固有の複数のサイズの複数のフィールドを有するように示される。具体的な例として、データ要素幅フィールド1564は、特定ベクトル向け命令フォーマット1600内の1つのビットフィールドとして示されるが、発明はこれに限定されない（すなわち、総称ベクトル向け命令フォーマット1500は、データ要素幅フィールド1564の他の複数のサイズを予想する）。 10

#### 【0114】

総称ベクトル向け命令フォーマット1500は、図12Aに順に示され、以下に列挙される次の複数のフィールドを含む。

#### 【0115】

EVEX\_Prefix(バイト0-3)1602は、4バイト形式でエンコードされる。

#### 【0116】

フォーマットフィールド1640(EVEXバイト0、ビット[7:0]) - 第1バイト(EVEXバイト0)はフォーマットフィールド1640であり、0x62(発明の一実施形態において、ベクトル向け命令フォーマットを区別するために用いられるユニークな値)を含む。 20

#### 【0117】

第2から第4バイト(EVEXバイト1-3)は、固有の機能を提供する多くのビットフィールドを含む。

#### 【0118】

REXフィールド1605(EVEXバイト1、ビット[7-5])は、EVEX.Rビットフィールド(EVEXバイト1、ビット7-R)、EVEX.Xビットフィールド(EVEXバイト1、ビット[6]-X)、および1557BEXバイト1、ビット[5]-B)からなる。EVEX.R、EVEX.X、およびEVEX.Bビットフィールドは、対応する複数のVEXビットフィールドと同じ機能性を提供し、1の補数形式を用いてエンコードされる、すなわち、ZMM0は1611Bとしてエンコードされ、ZMM15は0000Bとしてエンコードされる。当該分野において知られているように、複数の命令の他の複数のフィールドは、複数のレジスタインデックスのより低い3つのビット(r r r、x x x、およびb b b)をエンコードし、それにより、R r r r、X x x x、およびB b b bはEVEX.R、EVEX.X、およびEVEX.Bを加えることにより形成されてよい。 30

#### 【0119】

REX'フィールド1605 - これは、REX'フィールド1510の第1部分であり、拡張32レジスタセットの上位16または下位16のいずれかをエンコードするために用いられるEVEX.R'ビットフィールド(EVEXバイト1、ビット[4]-R')である。発明の一実施形態では、このビットは、以下に示されるように他とともに、その実オペコードバイトが62であるBOUND命令から区別するためにビット反転フォーマットで(既知のx86 32ビットモードで)格納され、しかし、MOD R/Mフィールド内で、MODフィールド内の11の値を受け入れない。発明の代替的な複数の実施形態は、これと反転フォーマットで以下に示される他のビットを格納しない。1の値は、下位の16のレジスタをエンコードするために用いられる。言い換えると、R'R r r rは、EVEX.R'、EVEX.R、および他の複数のフィールドからの他のRRRを結合することにより形成される。 40

#### 【0120】

オペコードマップフィールド1615(EVEXバイト1、ビット[3:0]-mmm

50

m) - そのコンテンツは、暗黙の主要なオペコードバイト (0F、0F 38、または0F 3) をエンコードする。

【0121】

データ要素幅フィールド 1664 (EVEX バイト2、ビット[7] - W) は、標記 EVEX.W により表される。EVEX.W は、データタイプ (32ビットデータ要素または64ビットデータ要素のいずれ) の粒度 (サイズ) を定義するために用いられる。

【0122】

EVEX.vvvvv1620 (EVEX バイト2、ビット[6:3] - vvvvv)。EVEX.vvvvv の役割は、以下を含んでよい。1) EVEX.vvvvv は、反転 (1 の補数) 形式で特定される第1のソースレジスタオペランドをエンコードし、2またはそれより多いソースオペランドを有する複数の命令に対して有効である。2) EVEX.vvvvv は、あるベクトルシフトに対して1の補数形式で特定されるデスティネーションレジスタオペランドをエンコードする。または、3) EVEX.vvvvv は、いずれのオペランドもエンコードせず、フィールドは残される。従って、EVEX.vvvvv フィールド 1620 は、反転 (1 の補数) 形式で格納された第1のソースレジスタ指定子の4つの下位ビットをエンコードする。命令に応じて、余分の異なる EVEX ビットフィールドは、指定子サイズを32のレジスタに拡張するために用いられる。

【0123】

EVEX.U1668 クラスフィールド (EVEX バイト2、ビット[2] - U) - EVEX.U = 0 の場合、それはクラスA または EVEX.U0 を示す。EVEX.U = 1 の場合、それはクラスB または EVEX.U1 を示す。

【0124】

プレフィックス符号化フィールド 1625 (EVEX バイト2、ビット[1:0] - p) は、ベース演算フィールドに対して追加的な複数のビットを提供する。EVEX プレフィックスフォーマットにおける複数のレガシSSSE 命令に対するサポートを提供することに加えて、これは、SIMD プレフィックスをコンパクトにする利益も有する (SIMD プレフィックスを表すバイトを必要とするのではなく、EVEX プレフィックスは2ビットのみを必要とする)。一実施形態では、レガシフォーマットおよび EVEX プレフィックスフォーマットの両方において SIMD プレフィックス (66H、F2H、F3H) を用いる複数のレガシSSSE 命令をサポートするために、これらのレガシ SIMD プレフィックスは、SIMD プレフィックス符号化フィールドにエンコードされ、デコーダのPLA に提供される前に、実行時に、レガシ SIMD プレフィックスに拡張される (従って、PLA は、これらのレガシ命令のレガシおよび EVEX フォーマットの両方を変更することなく実行することができる)。より新しい複数の命令は、EVEX プレフィックス符号化フィールドのコンテンツを直接、オペコード拡張として用いることができたが、ある実施形態は、一貫性のために、しかしこれらのレガシ SIMD プレフィックスにより特定される異なる意味を認める同様の様式で拡張する。代替的な実施形態は、2ビット SIMD プレフィックスエンコードをサポートする PLA を再設計してよく、従って、拡張を必要としない。

【0125】

アルファフィールド 1652 (EVEX バイト3、ビット[7] - EH、EVEX.EH、EVEX.rs、EVEX.RL、EVEX.write mask control、および EVEX.N としても知られ、また を用いて示される) - 先述の通り、このフィールドはコンテキスト固有である。

【0126】

ベータフィールド 1654 (EVEX バイト3、ビット[6:4] - SSSS、EVEX.S2\_0、EVEX.R2\_0、EVEX.rr1、EVEX.LL0、EVEX.LLB としても知られ、また を用いて示される) - 先述の通り、このフィールドはコンテキスト固有である。

【0127】

10

20

30

40

50

R E X ' フィールド 1610 - これは、R E X ' フィールドの残りであり、拡張 32 レジスタセットの上位 16 または下位 16 のいずれかをエンコードするために用いられてよい E V E X . V ' ビットフィールド ( E V E X バイト 3 、ビット [ 3 ] - V ' ) である。このビットは、ビット反転フォーマットで格納される。1 の値は、下位 16 のレジスタをエンコードするために用いられる。言い換えると、V ' V V V V V は、E V E X . V ' 、E V E X . V V V V . を結合することにより形成される。

【 0128 】

書き込みマスクフィールド 1670 ( E V E X バイト 3 、ビット [ 2 : 0 ] - k k k ) - そのコンテンツは、前述のとおり、複数の書き込みマスクレジスタ内のレジスタのインデックスを特定する。発明の一実施形態では、特定の値 E V E X . k k k = 000 は、特定の命令に対して書き込みマスクが用いられないことを暗示する特別な振る舞いを有する ( これは、マスキングハードウェアをバイパスするすべてのものまたはハードウェアに配線される書き込みマスクの使用を含む様々な態様において実装されてよい ) 。

【 0129 】

リアルオペコードフィールド 1630 ( バイト 4 ) は、オペコードバイトとしても知られる。オペコードの一部は、このフィールド内で特定される。

【 0130 】

M O D R / M フィールド 1640 ( バイト 5 ) は、M O D フィールド 1642 、 R e g フィールド 1644 、および R / M フィールド 1646 を含む。前述のとおり、M O D フィールド 1642 のコンテンツは、メモリアクセスおよび非メモリアクセス演算の間を区別する。 R e g フィールド 1644 の役割は、2 つの状況にまとめられることができる。すなわち、デスティネーションレジスタオペランドまたはソースレジスタオペランドのいずれかをエンコードすること、またはオペコード拡張として扱われ、いずれの命令オペランドをエンコードするために用いられない。 R / M フィールド 1646 の役割は、次を含んでよい。すなわち、メモリアドレスを参照する命令オペランドをエンコードすること、またはデスティネーションレジスタオペランドまたはソースレジスタオペランドのいずれかをエンコードすること。

【 0131 】

スケール、インデックス、ベース ( S I B ) バイト ( バイト 6 ) - 前述のとおり、スケールフィールド 1650 のコンテンツは、メモリアドレス生成のために用いられる。 S I B . x x x 1654 および S I B . b b b 1656 - これらのフィールドのコンテンツは、前に、レジスタインデックス X x x x および B b b b に関連して参照された。

【 0132 】

変位フィールド 1662A ( バイト 7 10 ) - M O D フィールド 1642 が 10 を含むと、バイト 7 - 10 は変位フィールド 1662A であり、それはレガシ 32 ビット変位 ( d i s p 32 ) と同じように機能し、バイト粒度で機能する。

【 0133 】

変位ファクタフィールド 1662B ( バイト 7 ) - M O D フィールド 1642 が 01 を含むとき、バイト 7 は変位ファクタフィールド 1662B である。このフィールドの位置は、バイト粒度で機能するレガシ x 86 命令セットの 8 ビット変位 ( d i s p 8 ) のそれと同じである。 d i s p 8 は符号拡張されるので、それは、 168 および 167 バイトオフセットの間でのみアドレスすることができる。 64 バイトキャッシュラインの観点において、 d i s p 8 は、 - 168 、 - 64 、 0 、および 64 のたった 4 つの実に有用な値にセットされることができる 8 ビットを用いる。より大きい範囲が頻繁に必要とされるので、 d i s p 32 が用いられる。しかし、 d i s p 32 は 4 バイトを必要とする。 d i s p 8 および d i s p 32 と対照的に、変位ファクタフィールド 1662B は d i s p 8 の再解釈である。変位ファクタフィールド 1662B を用いると、実際の変位は、メモリオペランドアクセスのサイズ ( N ) により乗算された変位ファクタフィールドのコンテンツにより決定される。このタイプの変位は、 d i s p 8 × N として参照される。これは、平均命令長を減らす ( 変位に対して用いられた、しかしあるかにより大きい範囲を有する单一

10

20

30

40

50

バイト）。そのような圧縮された変位は、有効な変位がメモリアクセスの粒度であるという仮定に基づくので、従って、アドレスオフセットの冗長下位ビットは、エンコードされる必要はない。言い換えると、変位ファクタフィールド 1662B は、レガシ×8 6命令セットの8ビット変位を代替する。従って、変位ファクタフィールド 1662B は、disp8 は disp8 × N に上書きされる例外のみを用いて、×86命令セットの8ビット変位と同じ様でエンコードされる（ModRM/SIBエンコードルールに変更はない）。言い換えると、（変位をメモリオペランドのサイズによりスケールして、バイト単位のアドレスオフセットを得る必要がある）ハードウェアによる変位値の解釈のみを除いて、複数のエンコードルールまたは複数のエンコード長に変更はない。即値フィールド 1672 は、前述のように動作する。

10

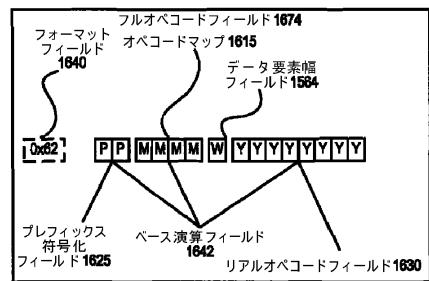

#### 【0134】

##### フルオペコードフィールド

図 12B は、発明の一実施形態に係るフルオペコードフィールド 1674 を作成する特定ベクトル向け命令フォーマット 1600 の複数のフィールドを示すブロック図である。詳細には、フルオペコードフィールド 1674 は、フォーマットフィールド 1640、ベース演算フィールド 1642、およびデータ要素幅 (W) のフィールド 1664 を含む。ベース演算フィールド 1642 は、プレフィックス符号化フィールド 1625、オペコードマップフィールド 1615、およびリアルオペコードフィールド 1630 を含む。

#### 【0135】

##### レジスタインデックスフィールド

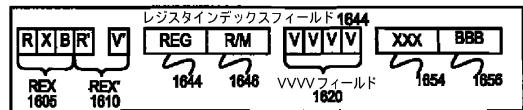

図 12C は、発明の一実施形態に係るレジスタインデックスフィールド 1644 を作成する特定ベクトル向け命令フォーマット 1600 の複数のフィールドを示すブロック図である。詳細には、レジスタインデックスフィールド 1644 は、REX フィールド 1605、REX' フィールド 1610、MODR/M.reg フィールド 1644、MODR/M.r/m フィールド 1646、VVVV フィールド 1620、××× フィールド 1654、およびbbb フィールド 1656 を含む。

20

#### 【0136】

##### 増加演算フィールド

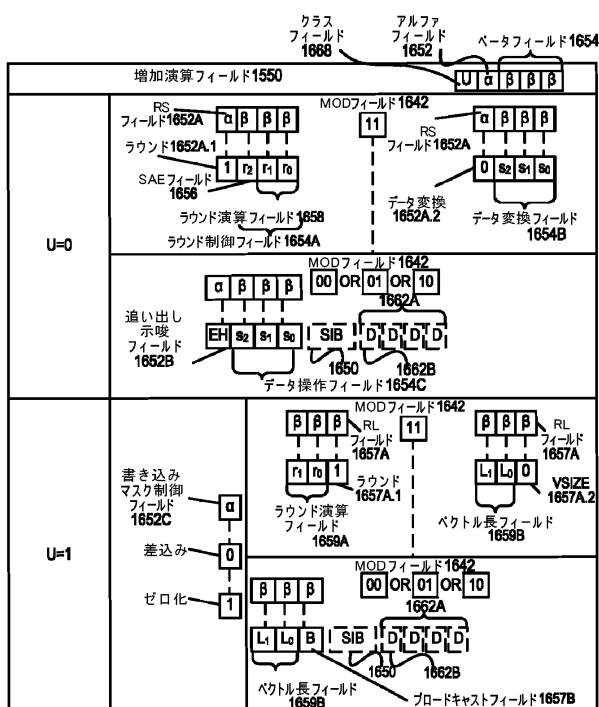

図 12D は、発明の一実施形態に係る増加演算フィールド 1650 を生成する特定ベクトル向け命令フォーマット 1600 の複数のフィールドを示すブロック図である。クラス (U) フィールド 1668 が 0 を含むと、それは EVEX.U0 (クラス A 1668A) を示す。それが 1 を含むと、それは EVEX.U1 (クラス B 1668B) を示す。U = 0 且つ MOD フィールド 1642 が 11 (非メモリアクセス演算を示す) を含むと、アルファフィールド 1652 (EVEX バイト 3、ビット [7] - EH) は rs フィールド 1652A として解釈される。rs フィールド 1652A が 1 (ラウンド 1652A.1) を含むと、ベータフィールド 1654 (EVEX バイト 3、ビット [6:4] - SSS) は、ラウンド制御フィールド 1654A として解釈される。ラウンド制御フィールド 1654A は、1 ビットの SAE フィールド 1656 および 2 ビットのラウンド演算フィールド 1658 を含む。rs フィールド 1652A が 0 (データ変換 1652A.2) を含むと、ベータフィールド 1654 (EVEX バイト 3、ビット [6:4] - SSS) は、3 ビットのデータ変換フィールド 1654B として解釈される。U = 0 且つ MOD フィールド 1642 が 00、01、または 10 (メモリアクセス演算を示す) を含むと、アルファフィールド 1652 (EVEX バイト 3、ビット [7] - EH) は、追い出し示唆 (EH) フィールド 1652B として解釈され、ベータフィールド 1654 (EVEX バイト 3、ビット [6:4] - SSS) は、3 ビットデータ操作フィールド 1654C として解釈される。

30

#### 【0137】

U = 1 のとき、アルファフィールド 1652 (EVEX バイト 3、ビット [7] - EH) は、書き込みマスク制御 (Z) フィールド 1652C として解釈される。U = 1 且つ MOD フィールド 1642 が 11 (非メモリアクセス演算を示す) を含むと、ベータフィー

40

50

ルド1654の一部( EVEXバイト3、ビット[4] - S<sub>0</sub> )は、RLフィールド1657Aとして解釈される。それが1(ラウンド1657A.1)を含むと、ベータフィールド1654の残り( EVEXバイト3、ビット[6-5] - S<sub>2-1</sub> )は、ラウンド演算フィールド1659Aとして解釈され、RLフィールド1657Aが0( VSIZE1657.A2 )を含むと、ベータフィールド1654の残り( EVEXバイト3、ビット[6-5] - S<sub>2-1</sub> )は、ベクトル長フィールド1659B( EVEXバイト3、ビット[6-5] - L<sub>1-0</sub> )として解釈される。U=1且つMODフィールド1642が00、01、または10(メモリアクセス演算を示す)を含むと、ベータフィールド1654( EVEXバイト3、ビット[6:4] - SSS )は、ベクトル長フィールド1659B( EVEXバイト3、ビット[6-5] - L<sub>1-0</sub> )およびブロードキャストフィールド1657B( EVEXバイト3、ビット[4] - B )として解釈される。

10

#### 【0138】

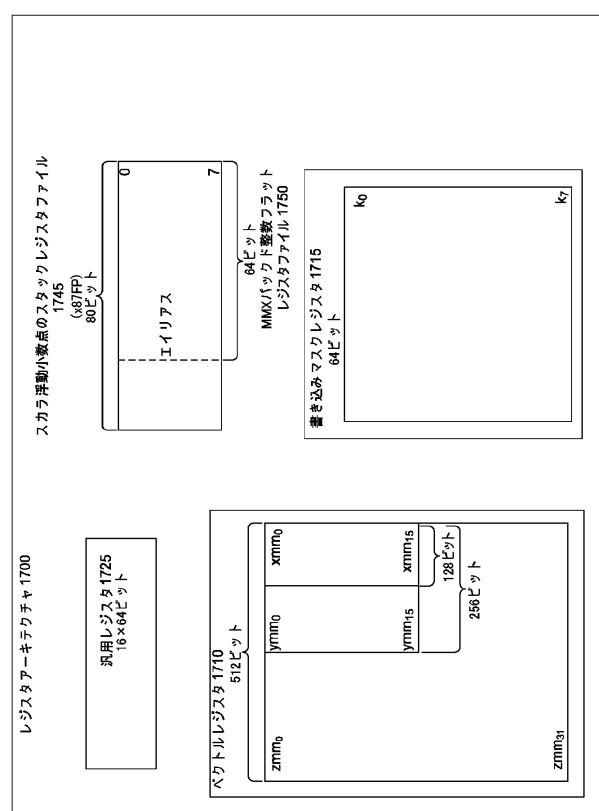

図13は、発明の一実施形態に係るレジスタアーキテクチャ1700のブロック図である。示される実施形態では、516ビット幅の32のベクトルレジスタ1710がある。これらのレジスタは、zmm0からzmm31として参照される。より低い16のzmmレジスタの下位の256ビットは、レジスタymm0-16上に上書きされる。より低い16のzmmレジスタの下位の168ビット(ymmレジスタの下位の168ビット)は、レジスタxmm0-15上に上書きされる。特定ベクトル向け命令フォーマット1600は、下の表に示されるように、これらの上書きレジスタファイル上で動作する。

#### 【0139】

【表1】

| 調整可能なベクトル長                                   | クラス          | 演算                        | レジスタ                                                                                                |

|----------------------------------------------|--------------|---------------------------|-----------------------------------------------------------------------------------------------------|

| ベクトル長<br>フィールド<br>1559Bを含まない<br>命令<br>テンプレート | A(図11A; U=0) | 1510, 1515,<br>1525, 1530 | zmmレジスタ<br>〔ベクトル長は<br>64バイト〕                                                                        |

|                                              | B(図11B; U=1) | 1516                      | zmmレジスタ<br>〔ベクトル長は<br>64バイト〕                                                                        |

| ベクトル長<br>フィールド<br>1559Bを含む命令<br>テンプレート       | B(図11B; U=1) | 1517, 1527                | ベクトル長<br>フィールド1559Bに<br>依存するzmm、<br>ymm、または<br>xmmレジスタ<br>〔ベクトル長は、<br>64バイト、<br>32バイト、<br>または16バイト〕 |

## 【0140】

言い換えると、ベクトル長フィールド1559Bは、最大長さと1または複数の他のより短い長さとの間で選択する。ただし、そのようなより短い長さのそれぞれは、前長の長さの半分であり、ベクトル長フィールド1559Bを有さない複数の命令テンプレートは、最大ベクトル長で動作する。さらに、一実施形態では、特定ベクトル向け命令フォーマット1600のクラスBの複数の命令テンプレートは、パックドまたはスカラ単／倍精度浮動小数点データおよびパックドまたはスカラ整数データで動作する。複数のスカラ演算は、zmm / ymm / xmmレジスタ内の最下位データ要素位置で実行される演算である。より高位の複数のデータ要素位置は、命令の前のそれらと同じ状態のままにされる、または実施形態に応じてゼロ化される。

## 【0141】

書き込みマスクレジスタ1715 - 示される実施形態では、それぞれが64ビットサイズの8つの書き込みマスクレジスタ(k0からk7)がある。代替的な実施形態では、書き込みマスクレジスタ1715は16ビットサイズである。前述のとおり、発明の一実施形態では、ベクトルマスクレジスタk0は、書き込みマスクとして用いられない。通常k0を示すエンコードが書き込みマスクに対して用いられると、それは、その命令に対する

10

20

30

40

50

書き込みマスキングを効率的にディスエーブルする  $0 \times F F F F$  のハードワイヤ書き込みマスクを選択する。

【 0 1 4 2 】

複数の汎用レジスタ 1725 - 示される実施形態では、複数のメモリオペランドをアドレスする既存の複数の  $\times 8$  アドレスモードとともに用いられる 16 の 64 ビット汎用レジスタがある。これらのレジスタは、 RAX、RBX、RCX、RDX、RBP、RSI 、 RDI 、 RSP 、および R8 から R15 の名前で参照される。

【 0 1 4 3 】

MMX パックド整数フラットレジスタファイル 1750 がエイリアスされるスカラ浮動小数点のスタックリジスタファイル ( $\times 8$  7 スタック) 1745 - 示される実施形態では、  $\times 8$  7 スタックは、  $\times 8$  7 命令セットエクステンションを用いて 32 / 64 / 80 ビット浮動小数点データで複数のスカラ浮動小数点演算を実行するために用いられる 8 要素スタックリジスタである。複数の MMX レジスタは、 64 ビットパックド整数データで複数の演算を実行するため、同様に MMX および XMM レジスタの間で実行される同じ複数の演算に対して複数のオペランドを保持するために用いられる。

【 0 1 4 4 】

発明の代替的な実施形態は、より広いまたはより狭い複数のレジスタを用いてよい。更に、発明の代替的な実施形態は、より多い、より少ない、または異なるレジスタファイルおよびレジスタを用いてよい。

【 0 1 4 5 】

前述の明細書では、発明は、固有の典型的な複数の実施形態を参照して記載されている。しかし、様々な修正および変更が、添付の特許請求の範囲に記載されたように発明のより広い精神及び範囲から逸脱することなくなされてよいことは明らかであろう。従って、明細書及び図面は、限定の意味ではなく例示の意味として捉えられるべきである。

【 0 1 4 6 】

発明の複数の実施形態は、上述した様々なステップを含む。複数のステップは、汎用または専用プロセッサに複数のステップを実行させるために用いられてよい複数の機械実行可能命令において実装されてよい。代替的に、これらのステップは、複数のステップを実行するためのハードワイヤードロジックを含む特定の複数のハードウェアコンポーネントにより、またはプログラムされたコンピュータコンポーネントおよびカスタムハードウェアコンポーネントの任意の組み合わせにより、実行されてよい。

【 0 1 4 7 】

ここに記載されたように、複数の命令は、特定の複数の演算を実行するよう構成された、または所定の機能性または非一時的コンピュータ可読媒体に実装されるメモリに格納された複数のソフトウェア命令を有する特定用途向け集積回路 (ASIC) のようなハードウェアの特定の複数の構成を参照してよい。従って、複数の図に示された複数の技術は、 1 または複数の電子デバイス ( 例えば、エンドステーション、ネットワーク要素等 ) 上で格納および実行されるコードおよびデータを用いて実装することができる。そのような電子デバイスは、非一時的コンピュータ機械可読記憶媒体 ( 例えば、磁気ディスク、光ディスク、ランダムアクセスメモリ、リードオンリメモリ、フラッシュメモリデバイス、相変化メモリ ) および一時的コンピュータ機械可読通信媒体 ( 例えば、搬送波、赤外線信号、デジタル信号などのような伝搬信号の電気、光、音、又は他の形式 ) のような、コンピュータ機械可読媒体を用いてコードおよびデータを ( 内部で、および / またはネットワークを介して他の電子デバイスを用いて ) 格納および通信する。さらに、そのような電子デバイスは、一般的に、 1 または複数のストレージデバイス ( 非一時的機械可読記憶媒体 ) 、ユーザ入力 / 出力デバイス ( 例えば、キーボード、タッチスクリーン、および / またはディスプレイ ) 、およびネットワーク接続のような 1 または複数の他のコンポーネントと連結された 1 または複数のプロセッサのセットを含む。複数のプロセッサのセットおよび他の複数のコンポーネントの連結は、一般的に、 1 または複数のバスおよびブリッジ ( バスコントローラとも呼ばれる ) を介される。ストレージデバイスおよびネットワークトラ

10

20

30

40

50

フィックを搬送する複数の信号は、それぞれ、1または複数の機械可読記憶媒体および機械可読通信媒体を表す。従って、与えられた電子デバイスのストレージデバイスは、一般的に、その電子デバイスの1または複数のプロセッサのセット上で実行するためのコードおよび/またはデータを格納する。もちろん、発明の実施形態の1または複数の部分は、ソフトウェア、ファームウェア、および/またはハードウェアの異なる複数の組み合わせを用いて実装されてよい。この発明の詳細な説明を通じて、説明の目的のために、多くの特定の詳細が、本発明の完全な理解を提供するために記載された。しかし、これらの特定の複数の詳細の幾つかが無くても本発明が実施されてよいことは、当業者に明らかである。特定の例において、周知の構造及び機能は、本発明の主題を分かりにくくしないよう精巧に詳細に記載されなかった。従って、発明の範囲および精神は、次の特許請求の範囲の観点において判断されるべきである。

10

【図1A】

【図1B】

【図2】

【 図 3 】

【 四 4 】

【図5】

【図6】

【図7】

【図8】

【図9 A】

【図9B】

【図10】

【図 1 1 A】

【図11B】

【図 1 2 A】

【図 1 2 B】

【図 1 2 C】

【図 1 2 D】

【図 1 3】

---

フロントページの続き

(72)発明者 ソレ、グイレム

アメリカ合衆国 95054 カリフォルニア州・サンタクララ・ミッション カレッジ ブーレ

バード・2200 インテル・コーポレーション内

(72)発明者 フェルナンデス、マネル

アメリカ合衆国 95054 カリフォルニア州・サンタクララ・ミッション カレッジ ブーレ

バード・2200 インテル・コーポレーション内

審査官 田中 幸雄

(56)参考文献 特開2011-134305 (JP, A)

Hideaki KOBAYASHI, A FAST MULTI-OPERAND MULTIPLICATION SCHEME, Proceedings of the IEEE

5th Symposium on Computer Arithmetic, IEEE, 1981年 5月16日, Pages 246-250

(58)調査した分野(Int.Cl., DB名)

G 06 F 9 / 305

G 06 F 7 / 487

G 06 F 17 / 10