(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6061556号

(P6061556)

(45) 発行日 平成29年1月18日(2017.1.18)

(24) 登録日 平成28年12月22日(2016.12.22)

(51) Int.Cl.

F 1

H04N 5/374 (2011.01)

H01L 27/146 (2006.01)H04N 5/335

H01L 27/14 A

請求項の数 19 (全 20 頁)

(21) 出願番号 特願2012-186666 (P2012-186666)

(22) 出願日 平成24年8月27日 (2012.8.27)

(65) 公開番号 特開2014-45351 (P2014-45351A)

(43) 公開日 平成26年3月13日 (2014.3.13)

審査請求日 平成27年6月8日 (2015.6.8)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100090273

弁理士 國分 孝悦

(72) 発明者 小林 秀央

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社内

(72) 発明者 黒田 享裕

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社内

審査官 鈴木 明

最終頁に続く

(54) 【発明の名称】光電変換装置

## (57) 【特許請求の範囲】

## 【請求項 1】

光電変換素子と、

前記光電変換素子のノードの電位を検出する検出手段と、

前記検出手段からのフィードバック信号を前記光電変換素子のノードにフィードバックするフィードバック手段と、

前記フィードバック手段の出力電流を増幅する電流増幅手段とを有し、

前記電流増幅手段は、

電流入力ノードと基準電位ノードとの間に抵抗性のインピーダンス素子と、

ゲートが前記電流入力ノードに接続され、ソースが前記基準電位ノードに接続された第 3 のMOSFETと、

前記電流入力ノード及び前記第3のMOSFETのソース間に接続された第1の抵抗とを有することを特徴とする光電変換装置。

## 【請求項 2】

前記検出手段は、

ゲートが前記光電変換素子のノードに接続され、ソースが電源電圧ノードに接続された第1のMOSFETと、

前記第1のMOSFETを駆動する定電流源とを有し、

前記フィードバック手段は、

前記第1のMOSFETと同一の極性であり、ソースが前記光電変換素子のノードに接

10

20

続され、ゲートが前記第1のMOSFETのドレインに接続され、ドレインから電流を出力する第2のMOSFETを有することを特徴とする請求項1記載の光電変換装置。

**【請求項3】**

前記電流増幅手段は、ソース接地回路であることを特徴とする請求項1又は2記載の光電変換装置。

**【請求項4】**

前記電流増幅手段は、ソースが前記第3のMOSFETのドレインに接続された第4のMOSFETを有することを特徴とする請求項1～3のいずれか1項に記載の光電変換装置。

**【請求項5】**

前記電流増幅手段は、前記第3のMOSFETのソース及び前記基準電位ノード間に接続された第2の抵抗を有することを特徴とする請求項1～3のいずれか1項に記載の光電変換装置。

**【請求項6】**

光電変換素子と、

前記光電変換素子のノードの電位を検出する検出手段と、

前記検出手段からのフィードバック信号を前記光電変換素子のノードにフィードバックするフィードバック手段と、

前記フィードバック手段の出力電流を増幅する電流増幅手段とを有し、

前記電流増幅手段は、

電流入力ノードと基準電位ノードとの間に抵抗性のインピーダンス素子と、

カレントミラー回路とを有し、

前記カレントミラー回路は、

ドレインが前記電流入力ノードに接続され、ソースが前記基準電位ノードに接続された第5のMOSFETと、

ソースが前記基準電位ノードに接続された第6のMOSFETと、

入力ノードが前記電流入力ノードに接続され、出力ノードが前記第5のMOSFETのゲート及び前記第6のMOSFETのゲートに接続された電圧バッファとを有することを特徴とする光電変換装置。

**【請求項7】**

前記カレントミラー回路は、

ゲート及びドレインが前記電流入力ノードに接続され、ソースが前記基準電位ノードに接続された第5のMOSFETと、

ゲートが前記電流入力ノードに接続され、ソースが前記基準電位ノードに接続された第6のMOSFETとを有することを特徴とする請求項6記載の光電変換装置。

**【請求項8】**

前記電圧バッファは、

ゲートが前記電流入力ノードに接続され、ソースが前記第5のMOSFETのゲート及び前記第6のMOSFETのゲートに接続された第7のMOSFETと、

前記第7のMOSFETを駆動する電流源とを有することを特徴とする請求項7記載の光電変換装置。

**【請求項9】**

前記第7のMOSFETは、バックゲートノード及びソースが相互に接続されていることを特徴とする請求項8記載の光電変換装置。

**【請求項10】**

前記光電変換素子、前記検出手段、前記フィードバック手段、前記第5のMOSFET及び前記電圧バッファは、受光領域の中に設けられ、

前記第6のMOSFETは、前記受光領域の外に設けられていることを特徴とする請求項6～9のいずれか1項に記載の光電変換装置。

**【請求項11】**

10

20

30

40

50

光電変換素子と、

前記光電変換素子のノードの電位を検出する検出手段と、

前記検出手手段からのフィードバック信号を前記光電変換素子のノードにフィードバックするフィードバック手段と、

前記フィードバック手段の出力電流を増幅する電流増幅手段とを有し、

前記電流増幅手段は、

電流入力ノードと基準電位ノードとの間に抵抗性のインピーダンス素子と、

カレントミラー回路とを有し、

前記カレントミラー回路は、

ゲートが前記電流入力ノードに接続され、ソースが前記基準電位ノードに接続された第 5 の M O S F E T と、 10

ゲートが前記電流入力ノードに接続され、ソースが前記基準電位ノードに接続された第 6 の M O S F E T と、

ドレインが前記電流入力ノードに接続され、ソースが前記第 5 の M O S F E T のドレインに接続された第 8 の M O S F E T と、

ゲートが前記第 8 の M O S F E T のゲートに接続され、ソースが前記第 6 の M O S F E T のドレインに接続された第 9 の M O S F E T と

を有することを特徴とする光電変換装置。

**【請求項 1 2】**

光電変換素子と、 20

前記光電変換素子のノードの電位を検出する検出手段と、

前記検出手手段からのフィードバック信号を前記光電変換素子のノードにフィードバックするフィードバック手段と、

前記フィードバック手段の出力電流を増幅する電流増幅手段とを有し、

前記電流増幅手段は、

電流入力ノードと基準電位ノードとの間に抵抗性のインピーダンス素子と、

オペアンプとを有し、

前記オペアンプは、正転入力ノードが前記電流入力ノードに接続され、反転入力ノード及び出力ノードが相互に接続され、

前記電流増幅手段は、 30

前記オペアンプの正転入力ノード及び前記基準電位ノード間に接続された第 1 の抵抗と、

前記オペアンプの反転入力ノード及び前記基準電位ノード間に接続された第 3 の抵抗と

を有することを特徴とする光電変換装置。

**【請求項 1 3】**

前記光電変換素子、前記検出手手段、前記フィードバック手段及び前記電流増幅手段が複数設けられ、

第 1 導電型の光電変換領域と、前記第 1 導電型と逆の導電型である第 2 導電型の領域とを交互に複数積層することにより、前記複数の光電変換素子が深さ方向に積層されていることを特徴とする請求項 1 ~ 1 2 のいずれか 1 項に記載の光電変換装置。 40

**【請求項 1 4】**

光電変換素子と、

前記光電変換素子のノードの電位を検出する検出手段と、

前記検出手手段からのフィードバック信号を前記光電変換素子のノードにフィードバックするフィードバック手段と、

前記フィードバック手段の出力電流を増幅する電流増幅手段とを有し、

前記電流増幅手段は、電流入力ノードと基準電位ノードとの間に抵抗性のインピーダンス素子を有し、

前記光電変換素子、前記検出手手段、前記フィードバック手段及び前記電流増幅手段が複数設けられ、 50

第1導電型の光電変換領域と、前記第1導電型と逆の導電型である第2導電型の領域とを交互に複数積層することにより、前記複数の光電変換素子が深さ方向に積層され、

前記複数の電流増幅手段は、相互に電流ゲインが異なることを特徴とする光電変換装置。

【請求項15】

前記電流増幅手段は、オペアンプを有することを特徴とする請求項14記載の光電変換装置。

【請求項16】

前記電流増幅手段は、カレントコンペア回路を有することを特徴とする請求項14記載の光電変換装置。

【請求項17】

光電変換素子と、

前記光電変換素子のノードの電位を検出する検出手段と、

前記検出手段からのフィードバック信号を前記光電変換素子のノードにフィードバックするフィードバック手段と、

前記フィードバック手段の出力電流を増幅する電流増幅手段とを有し、

前記電流増幅手段は、電流入力ノードと基準電位ノードとの間に抵抗性のインピーダンス素子を有し、

前記光電変換素子、前記検出手段、前記フィードバック手段及び前記電流増幅手段が複数設けられ、

第1導電型の光電変換領域と、前記第1導電型と逆の導電型である第2導電型の領域とを交互に複数積層することにより、前記複数の光電変換素子が深さ方向に積層され、

前記複数の電流増幅手段の各々は、

ドレインが前記電流入力ノードに接続され、ソースが前記基準電位ノードに接続された第5のMOSFETと、

ゲートが前記第5のMOSFETのゲートに接続され、ソースが前記基準電位ノードに接続された第6のMOSFETとを有し、

前記複数の電流増幅手段の前記第5のMOSFETは、相互にゲート長が等しいことを特徴とする光電変換装置。

【請求項18】

第1のノードと、電源電圧ノードに接続された第2のノードとを含む光電変換素子と、

前記光電変換素子の前記第1のノードに接続されたゲートと、前記電源電圧ノードに接続されたソースと、ドレインとを含む第1のトランジスタと、

前記第1のトランジスタの前記ドレインに接続された電流源と、

前記第1のトランジスタの前記ドレインに接続されたゲートと、前記光電変換素子の前記第1のノードに接続されたソースと、ドレインとを含み、前記第1のトランジスタと同じ極性の第2のトランジスタと、

前記第2のトランジスタの前記ドレインから出力された電流を受ける電流入力ノードと、基準電位が供給された基準電位ノードと、前記電流入力ノードが受ける電流に基づく電流を出力する第3のトランジスタとを含む回路とを有し、

前記回路は、前記電流入力ノードと前記基準電位ノードとの間に接続された抵抗を含むことを特徴とする光電変換装置。

【請求項19】

第1のノードと、電源電圧ノードに接続された第2のノードとを含む光電変換素子と、

前記光電変換素子の前記第1のノードに接続されたゲートと、前記電源電圧ノードに接続されたソースと、ドレインとを含む第1のトランジスタと、

前記第1のトランジスタの前記ドレインに接続された電流源と、

前記第1のトランジスタの前記ドレインに接続されたゲートと、前記光電変換素子の前記第1のノードに接続されたソースと、ドレインとを含み、前記第1のトランジスタと同じ極性の第2のトランジスタと、

10

20

30

40

50

前記第2のトランジスタの前記ドレインから出力された電流を受ける電流入力ノードと、基準電位が供給された基準電位ノードと、前記電流入力ノードが受ける電流に基づく電流を出力する第3のトランジスタとを含む回路とを有し、

前記回路は、前記電流入力ノードと前記基準電位ノードとの間に接続され、前記第3のトランジスタとカレントミラー回路を構成するトランジスタを含むことを特徴とする光電変換装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、光電変換装置に関する。

10

【背景技術】

【0002】

特許文献1の図1は、光電変換装置を表している。同図においては、定電流源として用いているMOSFETと、その定電流源によって駆動されるMOSFETでソース接地回路を構成しており、その駆動されるMOSFETのゲートとソース間の電圧で、フォトダイオードのアノード電位を定めている。同図において、光量が変化した際、フォトダイオードで発生する光電流が変化するので、フォトダイオードと蓄積容量間のMOSFETのゲートとソース間の電圧が変化する。この時、該MOSFETのソース(つまりフォトダイオードのアノード)電位ではなく、該MOSFETのゲートが主に変動する構成となっている。これは、該MOSFETのソースから該MOSFETのゲートへ、ソース接地回路を介して、フィードバックがかかっているためである。

20

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平7-203319号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、該MOSFETのドレインに蓄積容量を接続し、光電流で該容量上に信号電荷を充電していく際には、該容量上の電位が、露光時間に依存して上昇していく。よって、該MOSFETのドレイン電位が上昇していくため、露光時間が長すぎると上述のフィードバックが働かなくなってしまう。すなわち、長い露光時間が回路動作の安定性を崩す要因となってしまう。

30

【0005】

本発明の目的は、回路動作の安定性を向上させることができる光電変換装置を提供することである。

【課題を解決するための手段】

【0006】

本発明の光電変換装置は、光電変換素子と、前記光電変換素子のノードの電位を検出する検出手段と、前記検出手段からのフィードバック信号を前記光電変換素子のノードにフィードバックするフィードバック手段と、前記フィードバック手段の出力電流を増幅する電流増幅手段とを有し、前記電流増幅手段は、電流入力ノードと基準電位ノードとの間に抵抗性のインピーダンス素子と、ゲートが前記電流入力ノードに接続され、ソースが前記基準電位ノードに接続された第3のMOSFETと、前記電流入力ノード及び前記第3のMOSFETのソース間に接続された第1の抵抗とを有することを特徴とする。

40

【発明の効果】

【0007】

電流増幅手段の電流入力ノードの電位が露光時間に依存することを防止し、回路動作の安定性を向上させることができる。

【図面の簡単な説明】

50

## 【0008】

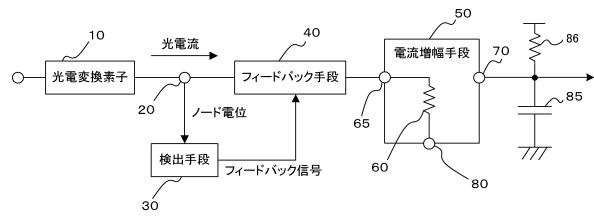

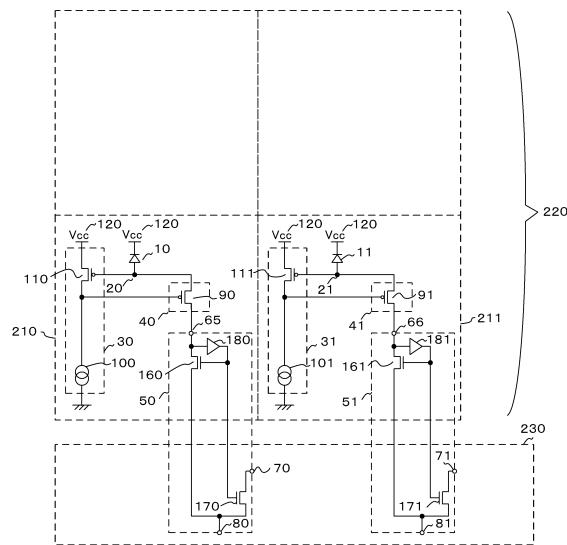

- 【図1】本発明の第1の実施形態の構成例を示す構成図である。

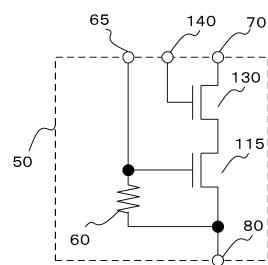

【図2】本発明の第1の実施形態の構成例を示す構成図である。

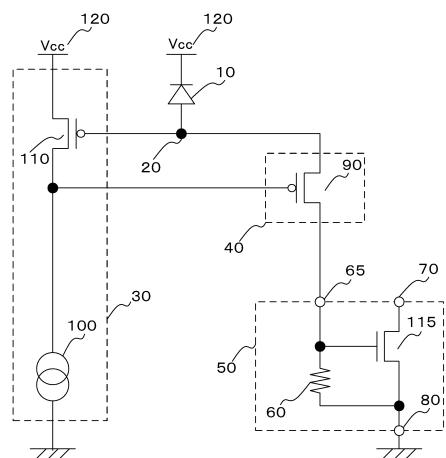

【図3】本発明の第2の実施形態の構成例を示す構成図である。

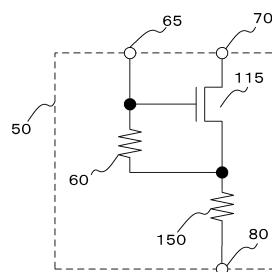

【図4】本発明の第3の実施形態の構成例を示す構成図である。

【図5】本発明の第4の実施形態の構成例を示す構成図である。

【図6】本発明の第5の実施形態の構成例を示す構成図である。

【図7】本発明の第5の実施形態の構成例を示す構成図である。

【図8】本発明の第6の実施形態の構成例を示す構成図である。

【図9】本発明の第7の実施形態の構成例を示す構成図である。

【図10】本発明の第8の実施形態の構成例を示す構成図である。

【図11】本発明の第9の実施形態の構成例を示す構成図である。

【図12】本発明の第10の実施形態の構成例を示す構成図である。

【図13】本発明の第11の実施形態の構成例を示す構成図である。

【図14】本発明の第12及び第13の実施形態の構成例を示す構成図である。

【図15】本発明の第12及び第13の実施形態の説明図である。

10

## 【発明を実施するための形態】

## 【0009】

## (第1の実施形態)

図1は、本発明の第1の実施形態に係る光電変換装置の構成例を示す図である。光電変換装置は、光電変換素子10と、光電変換素子10で発生した光電流が入力されるノード20と、ノード20の電位を検出する検出手段30と、検出手段30からのフィードバック信号をノード20にフィードバックするフィードバック手段40を有する。ノード20は、光電変換素子10のノードである。また、光電変換装置は、フィードバック手段40の出力電流を増幅する電流増幅手段50を有し、電流増幅手段50は、第1の抵抗60と、電流入力ノード65と、電流出力ノード70と、基準電位ノード80を有する。すなわち、電流増幅手段50は、電流入力ノード65と基準電位ノード80との間に第1の抵抗(抵抗性のインピーダンス素子)60を有する。また、光電変換装置は、負荷容量85及び負荷抵抗86を有する。

20

## 【0010】

図1において、光電流が入力されるノード20の電位は、検出手段30で検出され、フィードバック手段40を用いてフィードバックをかけることによって、光電流が変化した際のノード20の電位変動を低減する。また、フィードバック手段40から出力される光電流は、電流増幅手段50で増幅され、増幅した電流で後段の負荷容量85を駆動することが可能となっており、これにより動作速度を改善することが可能となっている。また、電流入力ノード65の電位は、基準電位ノード80の電位と第1の抵抗60の抵抗値と入力電流により、決まる。これにより、電流入力ノード65の電位が露光時間に依存することを防いでおり、回路動作の安定性を向上させている。以上のように、図1の光電変換装置により、回路動作の安定性を向上し、動作速度を改善した光電変換装置を提供することができる。

30

## 【0011】

図2は、図1の光電変換装置の構成例を示す回路図である。まず、図1と図2の対応について説明する。検出手段30は、定電流源100と、第1のMOSFET110とを有する。第1のMOSFET110は、ソースが電源電圧ノード120に接続され、ゲートがノード20に接続される。定電流源100は、第1のMOSFET110を駆動する電流源であり、第1のMOSFET110のドレイン及び基準電位ノード間に接続される。フィードバック手段40は、第2のMOSFET90を有する。第2のMOSFET90は、第1のMOSFET110と同一の極性であり、ソースがノード20に接続され、ゲートが第1のMOSFET110のドレインに接続され、ドレインから電流を出力する。電流増幅手段50は、ソース接地回路であり、第1の抵抗60と第3のMOSFET11

40

50

5とを有する。第3のMOSFET 115は、ドレンが電流出力ノード70に接続され、ゲートが電流入力ノード65に接続され、ソースが基準電位ノード80に接続される。第1の抵抗60は、電流入力ノード65及び第3のMOSFET 115のソース間に接続される。また、光電変換素子10は、例えばフォトダイオードであり、アノードがノード20に接続され、カソードが電源電圧ノード120に接続される。

## 【0012】

図2において、光電変換素子10で発生した光電流は、電流増幅手段50に流れ込む。光電流 $I_p$ は、第1の抵抗60により電圧に変換される。センサ照度が変化した際の光電流の変化量を $\Delta I_p$ とすると、第3のMOSFET 115のゲート及びソース間電圧 $V_{gs}$ の変化分は、次式(1)になる。ここで、Rは第1の抵抗60の抵抗値である。

10

## 【0013】

## 【数1】

$$\Delta V_{gs} = R \Delta I_p \quad \dots (1)$$

## 【0014】

また、第3のMOSFET 115のドレン電流は、一般的なMOSFETのドレン電流の式から、次式(2)になる。ここで、 $V_{th}$ は閾値である。

## 【0015】

## 【数2】

$$I_d = \frac{\beta}{2} (V_{gs} - V_{th})^2 \quad \dots (2)$$

20

## 【0016】

また、 $\beta$ は、次式(3)の通りである。

## 【0017】

## 【数3】

$$\beta = \mu_0 C_{ox} \frac{W}{L} \quad \dots (3)$$

## 【0018】

30

ここで、 $\mu_0$ はキャリアの移動度、 $C_{ox}$ は第3のMOSFET 115の単位面積当たりのゲート容量、Wは第3のMOSFET 115のゲート幅、Lは第3のMOSFET 115のゲート長である。式(2)より、第3のMOSFET 115のトランスクンダクタンス $gm$ は、次式(4)になる。

## 【0019】

## 【数4】

$$gm = \frac{\Delta I_d}{\Delta V_{gs}} = \beta(V_{gs} - V_{th}) \quad \dots (4)$$

40

## 【0020】

式(4)に式(1)を代入すると、次式(5)になる。

## 【0021】

## 【数5】

$$\frac{\Delta I_d}{\Delta I_p} = \beta(V_{gs} - V_{th})R = gm \times R \quad \dots (5)$$

## 【0022】

式(5)が電流増幅手段50の電流増幅率となる。このように、増幅した電流で電流出力ノード70に接続される後段の負荷容量85を駆動することが可能となっており、これ

50

により、動作速度を改善することが可能となっている。また、電流入力ノード 65 の電位は、第1の抵抗 60 の抵抗値と光電流により、決まる。これにより、電流入力ノード 65 の電位が露光時間に依存することを防いでおり、回路動作の安定性を向上させている。

#### 【0023】

以上のように、図2の光電変換装置により、回路動作の安定性を向上し、動作速度を改善した光電変換装置を提供することができる。

#### 【0024】

##### (第2の実施形態)

図3は、本発明の第2の実施形態に係る光電変換装置の電流増幅手段50の構成例を示す図である。但し、ここでは上述した第1の実施形態との相違点についてのみ説明する。

10

図3においては、電流増幅手段50は、図2に対して、さらに、第4のMOSFET130と電圧入力ノード140を有する。第4のMOSFET130は、ドレインが電流出力ノード70に接続され、ゲートが電圧入力ノード140に接続され、ソースが第3のMOSFET115のドレインに接続される。第4のMOSFET130が、第3のMOSFET115のドレイン電圧の変動を抑える役割を果たすことにより、電流増幅手段50の入力容量を低減し、動作速度を更に改善することが可能となる。

#### 【0025】

電流増幅手段50の入力電流となる光電流が  $I_p$  だけ変化したとき、電流出力ノード70の電位変化  $V$  は、式(5)を用いると、次式(6)になる。

#### 【0026】

##### 【数6】

$$\Delta V \approx -gm \times R \Delta I_p \times Rout \quad \dots (6)$$

#### 【0027】

ここで、Routは、電流出力ノード70の外に接続された負荷抵抗86の抵抗値である。ここで、第4のMOSFET130のトランスクンダクタンスを  $gm1$ 、出力抵抗を  $r1$  とすると、第3のMOSFET115のドレイン電圧の変動  $V_d$  は、およそ  $1/(gm1 \times r1)$  倍され、次式(7)に抑えられる。

#### 【0028】

##### 【数7】

$$\Delta V_d \approx \frac{-gm \times R \Delta I_p \times Rout}{gm1 \times r1} \quad \dots (7)$$

#### 【0029】

ここで、第3のMOSFET115のゲート及びドレイン間容量  $C_{gd}$  にはミラー効果が寄与する。よって、ミラー容量は、 $A = -V_d / R \cdot I_p$  として、 $(1 + A) C_{gd}$  となる。式(7)を用いて、Aを消去すると、次式(8)になる。

#### 【0030】

##### 【数8】

$$(1 + A) C_{gd} \approx \left(1 + \frac{gm \times Rout}{gm1 \times r1}\right) C_{gd} \quad \dots (8)$$

#### 【0031】

一方、第4のMOSFET130がない場合は、式(6)が第3のMOSFET115のドレイン電圧の変動になるので、式(6)より、 $A = -V_d / R \cdot I_p = gm \cdot Rout$  となるので、ミラー容量は式(8)よりも大きくなる。このように、第3のMOSFET115のドレイン電圧の変動を  $1/(gm1 \times r1)$  倍に抑えることにより、 $C_{gd}$  に働くミラー効果を抑え、電流増幅手段50の入力容量の低減を行っている。光電変換装置の動作速度には、増幅された電流による電流出力ノード70に接続される負荷容量の充放電だけではなく、光電流による電流入力ノード65に付随する容量の充放電も寄与する

40

50

。よって、電流増幅手段 50 の入力容量を低減し、動作速度を更に改善することが可能となる。

### 【0032】

#### (第3の実施形態)

図4は、本発明の第3の実施形態に係る光電変換装置の電流増幅手段50の構成例を示す図である。但し、ここでは上述した第1の実施形態との相違点についてのみ説明する。図4においては、電流増幅手段50は、図2に対して、さらに、第2の抵抗150を有する。第2の抵抗150は、第3のMOSFET115のソース及び基準電位ノード80間に接続される。これにより、基準電位変動によるS/Nの悪化を低減することが可能となる。

10

### 【0033】

基準電位ノード80のノード電位が、 $V_n$ だけ変動した際、第2の抵抗150の抵抗値 $R_1$ が十分大きければ、電流出力ノード70から出力される電流へのノイズ電流の混入は、およそ $V_n / R_1$ となる。一方、図2の電流増幅手段50においては、式(4)の $g_m$ を用いて、およそ $g_m \times V_n$ となる。よって、図4の電流増幅手段50は、図2の電流増幅手段50に対して、ノイズ電流を $1 / (g_m \times R_1)$ 倍に低減することができる。以上のように、基準電位変動によるS/Nの悪化を低減することが可能となる。

### 【0034】

#### (第4の実施形態)

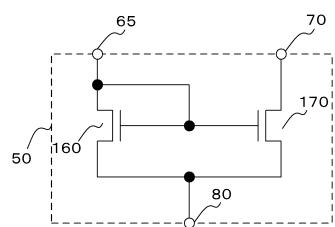

図5は、本発明の第4の実施形態に係る光電変換装置の電流増幅手段50の構成例を示す図である。但し、ここでは上述した第1の実施形態との相違点についてのみ説明する。図5においては、電流増幅手段50は、第5のMOSFET160と第6のMOSFET170を有する。第5のMOSFET160は、ドレイン及びゲートが電流入力ノード65に接続され、ソースが基準電位ノード80に接続される。第6のMOSFET170は、ドレインが電流出力ノード70に接続され、ゲートが電流入力ノード65に接続され、ソースが基準電位ノード80に接続される。これらのMOSFET160及び170はカレントミラー回路を構成し、電流を増幅することで、電流ゲインのばらつき低減、電流ゲインの光量依存低減による線形性の向上、ダイナミックレンジ向上が可能となる。

20

### 【0035】

第5のMOSFET160のゲート長を $L_1$ 、ゲート幅を $W_1$ とし、第6のMOSFET170のゲート長を $L_2$ 、ゲート幅を $W_2$ とすると、電流ゲインは、式(2)及び式(3)より、次式(9)が導出できる。

30

### 【0036】

#### 【数9】

$$\frac{\Delta I_{out}}{\Delta I_p} \approx \frac{(W_2/L_2)}{(W_1/L_1)} \quad \dots (9)$$

### 【0037】

ここで、 $I_{out}$ は電流出力ノード70から出力される電流である。式(5)の電流ゲインには、MOSFETのトランスクンダクタンス $g_m$ が含まれておらず、式(4)より閾値 $V_{th}$ が寄与するため、プロセスばらつきが大きくなる。よって、式(9)の方がプロセスばらつきの影響が小さいと考えられる。よって、電流ゲインのばらつきを低減することができる。

40

### 【0038】

また、式(4)は $Vgs$ を含んでおり、これは、電流増幅手段50の入力電流、すなわち光電流に依存する。よって、式(5)の電流ゲインは光量に依存して変化してしまうため、式(9)の方が、光量依存が小さいと考えられる。よって、電流ゲインの光量依存を低減することが可能となり、線形性を向上させることができる。

### 【0039】

50

また、図2においては、電流入力ノード65の電位は光電流Ipに対して線形で増加するのに対して、図5においては、式(2)より、平方根で増加する。よって、光電流Ipの増加に対する電流入力ノード65の電位増加が小さいため、より大きな光電流を入力することが可能となり、ダイナミックレンジ向上が可能となる。

#### 【0040】

以上のように、本実施形態は、カレントミラー回路で電流を增幅することで、電流ゲインのばらつき低減、電流ゲインの光量依存低減による線形性の向上、ダイナミックレンジ向上が可能となる。

#### 【0041】

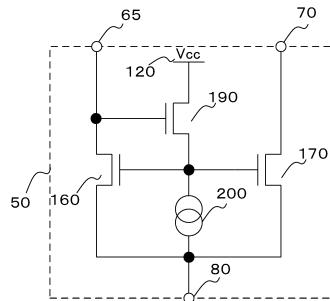

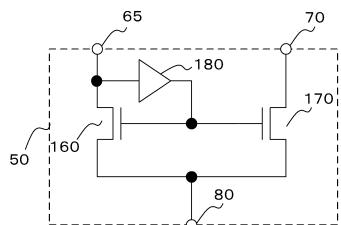

##### (第5の実施形態)

10

図6及び図7は、本発明の第5の実施形態に係る光電変換装置の電流増幅手段50の構成例を示す図である。但し、ここでは上述した第4の実施形態との相違点についてのみ説明する。図6においては、電流増幅手段50は、図5に対して、さらに、電圧バッファ180を有する。電圧バッファ180は、入力ノードが電流入力ノード65に接続され、出力ノードが第5のMOSFET160のゲート及び第6のMOSFET170のゲートに接続される。これにより、電流増幅手段50の入力容量を低減し、動作速度を更に改善することが可能となる。

#### 【0042】

電圧バッファ180は、第5のMOSFET160のゲート及びソース間容量Cgs1と、第6のMOSFET170のゲート及びソース間容量Cgs2と、ゲート及びドレイン間容量Cgd2を充放電する。よって、光電流で充放電される電流増幅手段50の入力容量は、その分、低減される。一方で、電圧バッファ180の入力容量Cin分だけ増加する。よって、 $C_{in} < C_{gs1} + C_{gs2} + C_{gd2}$ となるように、電圧バッファ180を設計することで、電流増幅手段50の入力容量を低減し、動作速度を更に改善することが可能となる。

20

#### 【0043】

図7に、図6の電圧バッファ180をソースフォロワで構成した電流増幅手段50の例を示す。図7の電流増幅手段50は、図5に対して、さらに、第7のMOSFET190と電流源200を有する。第7のMOSFET190は、ドレインが電源電圧ノード120に接続され、ゲートが電流入力ノード65に接続され、ソースが第5のMOSFET160のゲート及び第6のMOSFET170のゲートに接続される。電流源200は、第7のMOSFET190を駆動する電流源であり、第7のMOSFET190のソース及び基準電位ノード80間に接続される。第7のMOSFET190及び電流源200により、ソースフォロワを構成している。

30

#### 【0044】

第7のMOSFET190のゲート及びソース間容量をCgs3、ゲート及びドレイン間容量をCgd3、ソースフォロワのゲインをAとすると、ソースフォロワの入力容量Cinは、次式(10)になる。

#### 【0045】

##### 【数10】

40

$$C_{in} \approx C_{gd3} + (1 - A)C_{gs3} \quad \dots (10)$$

#### 【0046】

この入力容量Cinを、上述の $C_{gs1} + C_{gs2} + C_{gd2}$ より小さくなるように設計することは比較的、容易である。よって、電流増幅手段50の入力容量を低減し、動作速度を更に改善することが可能となる。

#### 【0047】

##### (第6の実施形態)

図8は、本発明の第6の実施形態に係る光電変換装置の電流増幅手段50の構成例を示

50

す図である。但し、ここでは上述した第5の実施形態との相違点についてのみ説明する。図8においては、図7に対して、電流増幅手段50中の第7のMOSFET190は、バックゲートノード及びソースが相互に接続されている。これにより、式(10)中のソースフォロワゲインAを増加させて、式(10)の入力容量Cinを低減することにより、電流増幅手段50の入力容量を更に低減し、動作速度を更に改善する。

#### 【0048】

##### (第7の実施形態)

図9は、本発明の第7の実施形態に係る光電変換装置の構成例を示す図である。但し、ここでは上述した第5の実施形態との相違点についてのみ説明する。図9においては、210及び211は単位画素領域、220は画素領域、230は周辺回路領域を表している。

10 それぞれの単位画素領域210及び211は、それぞれの光電変換素子10及び11を有している。また、それぞれの単位画素領域210及び211は、それぞれの検出手段30、31を有しており、それぞれの定電流源100、101及び、それぞれの第1のMOSFET110、111を有する。また、それぞれの単位画素領域210及び211は、それぞれのフィードバック手段40、41を有しており、それぞれの第2のMOSFET90、91を有する。単位画素領域210及び211は、それぞれの電流増幅手段50、

20 51を有し、それぞれの電流入力ノード65、66、電流出力ノード70、71及び基準電位ノード80、81、第5のMOSFET160、161及び第6のMOSFET170、171を有する。また、それぞれの単位画素領域210及び211は、それぞれの電圧バッファ180、181を有する。第5のMOSFET160及び161を単位画素領域210及び211内に配置する一方で、第6のMOSFET170及び171を周辺回路領域230に配置する。これにより、単位画素領域210及び211に光電変換素子10及び11が占める割合を増加し、感度を向上させることが可能となる。

#### 【0049】

第6のMOSFET170及び171を周辺回路領域230に配置する場合、第5のMOSFET160及び161のそれぞれのゲートと第6のMOSFET170及び171のそれぞれのゲートを接続する配線を長い距離にわたって引き回す。そのため、寄生容量が大きくなる。しかし、該配線は光電流ではなく、電圧バッファ180で駆動しているため、動作速度の悪化を抑えることが可能となる。

#### 【0050】

以上のように、第6のMOSFET170及び171を周辺回路領域230に配置することにより、動作速度の悪化を抑えつつ、単位画素領域210及び211に光電変換素子10及び11が占める割合を増加し、感度を向上させることが可能となる。画素領域220は、受光領域である。光電変換素子10, 11、検出手段30, 31、フィードバック手段40, 41、第5のMOSFET160, 161及び電圧バッファ180, 181は、画素領域220である受光領域の中に設けられる。これに対し、第6のMOSFET170及び171は、画素領域220である受光領域の外の周辺回路領域230に設けられる。

#### 【0051】

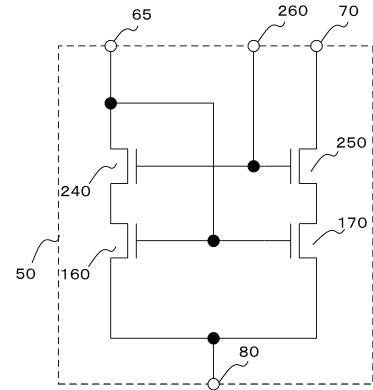

##### (第8の実施形態)

図10は、本発明の第8の実施形態に係る光電変換装置の電流増幅手段50の構成例を示す図である。但し、ここでは上述した第4の実施形態との相違点についてのみ説明する。図10においては、電流増幅手段50は、図5に対して、第8のMOSFET240と、第9のMOSFET250を有する。第8のMOSFET240は、ドレインが電流入力ノード65に接続され、ゲートが電圧入力ノード260に接続され、ソースが第5のMOSFET160のドレインに接続される。第9のMOSFET250は、ドレインが電流出力ノード70に接続され、ゲートが電圧入力ノード260に接続され、ソースが第6のMOSFET170のドレインに接続される。MOSFET240及び250が、MOSFET160及び170のドレイン電圧の変動を抑える役割を果たすことにより、電流ゲインの光量依存を低減し、線形性を向上させることが可能となる。

## 【0052】

式(9)の電流ゲインを導出した際には、ドレイン電流のドレイン及びソース間電圧V<sub>d s</sub>に対する依存性を含まない式(2)を近似的に用いた。λをチャネル長変調係数として、V<sub>d s</sub>依存を含めた式は、次式(11)になる。

## 【0053】

## 【数11】

$$I_d = \frac{\beta}{2} (V_{gs} - V_{th})^2 (1 + \lambda V_{ds}) \quad \dots (11)$$

## 【0054】

10

式(11)を用いて、改めて、式(9)のように電流ゲインを導出すると、次式(12)になる。

## 【0055】

## 【数12】

$$\frac{\Delta I_{out}}{\Delta I_p} \approx \frac{(W2/L2)}{(W1/L1)} \frac{(1 + \lambda_2 \times V_{ds2})}{(1 + \lambda_1 \times V_{ds1})} \quad \dots (12)$$

## 【0056】

20

ここで、V<sub>d s 1</sub>は第5のMOSFET160のドレイン及びソース間電圧であり、V<sub>d s 2</sub>は第6のMOSFET170のドレイン及びソース間電圧である。また、λ<sub>1</sub>は第5のMOSFET160のチャネル長変調係数であり、λ<sub>2</sub>は第6のMOSFET170のチャネル長変調係数である。図5において、V<sub>d s 1</sub>は入力電流に依存するので、光電流に依存する。また、V<sub>d s 2</sub>も光電流に依存する。よって、式(12)より、電流ゲインは光量に対して緩やかに依存する。図5においては、電流入力ノード65の電位をV<sub>i n</sub>、電流出力ノード70の電位をV<sub>o u t</sub>として、式(12)より、次式(13)になる。

## 【0057】

## 【数13】

30

$$\frac{\Delta I_{out}}{\Delta I_p} \approx \frac{(W2/L2)}{(W1/L1)} \frac{(1 + \lambda_2 \times V_{out})}{(1 + \lambda_1 \times V_{in})} \quad \dots (13)$$

## 【0058】

それに対して、図9においては、次式(14)になる。

## 【0059】

## 【数14】

$$\frac{\Delta I_{out}}{\Delta I_p} \approx \frac{(W2/L2)}{(W1/L1)} \frac{(1 + \frac{\lambda_2 \times V_{out}}{g_m 2 \times r_2})}{(1 + \frac{\lambda_1 \times V_{in}}{g_m 1 \times r_1})} \quad \dots (14)$$

## 【0060】

40

ここで、g<sub>m 1</sub>とr<sub>1</sub>はそれぞれ、第8のMOSFET240のトランスクタンスと出力抵抗、g<sub>m 2</sub>とr<sub>2</sub>はそれぞれ、第9のMOSFET250のトランスクタンスと出力抵抗である。式(13)及び式(14)より、MOSFET240及び250によって、MOSFET160及び170のドレイン電圧の変動を抑えることにより、電流ゲインの光量依存を低減し、線形性を向上させることができることがわかる。

50

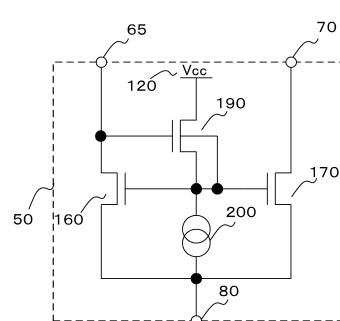

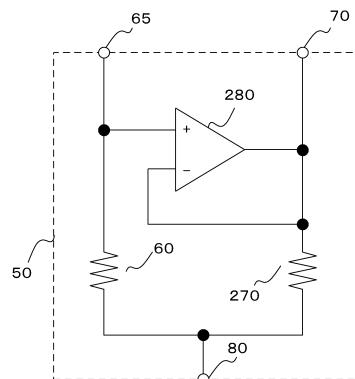

**【0061】****(第9の実施形態)**

図11は、本発明の第9の実施形態に係る光電変換装置の電流増幅手段50の構成例を示す図である。但し、ここでは上述した第1の実施形態との相違点についてのみ説明する。図11においては、電流増幅手段50は、オペアンプ280と、抵抗60及び270を有する。オペアンプ280は、正転入力ノードが電流入力ノード65に接続され、反転入力ノード及び出力ノードが電流出力ノード70に接続される。第1の抵抗60は、オペアンプ280の正転入力ノード及び基準電位ノード80間に接続される。第3の抵抗270は、オペアンプ280の反転入力ノード及び基準電位ノード80間に接続される。オペアンプ280を用いた電流増幅手段50により、電流を増幅することで、電流ゲインのばらつき低減、電流ゲインの光量依存低減による線形性の向上、が可能となる。10

**【0062】**

電流増幅手段50の入力電流となる光電流が  $I_p$  だけ変化したとき、オペアンプ280の正転入力ノードの電位変化は、第1の抵抗60の抵抗値を  $R_1$  とすると、 $R_1 \times I_p$  である。このとき、反転入力ノード電位もおよそ  $R_1 \times I_p$  だけ変化するので、電流出力ノード70の出力電流は、第3の抵抗270の抵抗値を  $R_2$  とすると、 $R_1 \times I_p / R_2$  だけ変化する。よって、電流ゲインは  $R_1 / R_2$  となる。

**【0063】**

上述のように、式(5)の電流ゲインは、 $V_{th}$  ばらつきによるプロセスばらつき及び  $V_{gs}$  の光量依存による光量依存を有するので、図11の構成によって、それらを低減することが可能となる。以上のように、オペアンプ280を用いた電流増幅手段50により、電流を増幅することで、電流ゲインのばらつき低減、電流ゲインの光量依存低減による線形性の向上、が可能となる。20

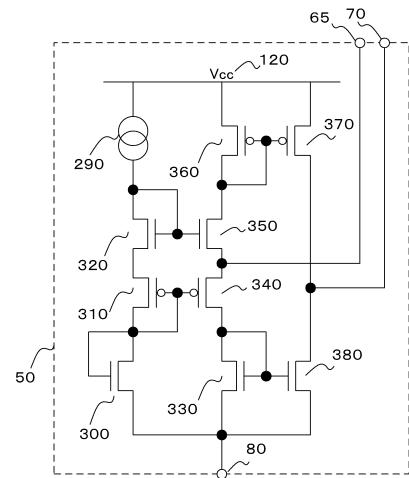

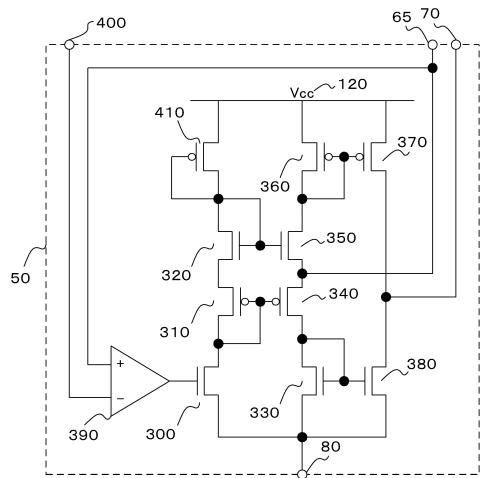

**【0064】****(第10の実施形態)**

図12は、本発明の第10の実施形態に係る光電変換装置の電流増幅手段50の構成例を示す図である。但し、ここでは上述した第1の実施形態との相違点についてのみ説明する。図12においては、電流増幅手段50は、電流源290と、MOSFET300、310、320、330、340、350、360、370、380を有している。MOSFET320は、ドレイン及びゲートが電流源290を介して電源電圧ノード120に接続される。MOSFET310は、ソースがMOSFET320のソースに接続され、ゲート及びドレインがMOSFET340のゲートに接続される。MOSFET300は、ドレイン及びゲートがMOSFET310のドレインに接続され、ソースが基準電位ノード80に接続される。MOSFET360は、ソースが電源電圧ノード120に接続され、ゲート及びドレインがMOSFET350のドレインに接続される。MOSFET350は、ゲートがMOSFET320のゲートに接続され、ソースが電流入力ノード65に接続される。MOSFET340は、ソースが電流入力ノード65に接続される。MOSFET330は、ドレイン及びゲートがMOSFET340のドレインに接続され、ソースが基準電位ノード80に接続される。MOSFET370は、ソースが電源電圧ノード120に接続され、ゲートがMOSFET360のゲートに接続され、ドレインが電流出力ノード70に接続される。MOSFET380は、ドレインが電流出力ノード70に接続され、ゲートがMOSFET330のゲートに接続され、ソースが基準電位ノード80に接続される。これらの素子により、カレントコンベア回路を構成し、電流を増幅することにより、電流ゲインのばらつき低減、電流ゲインの光量依存低減、が可能となる。30

**【0065】**

電流源290の電流値により、MOSFET300、310、320のそれぞれのゲート及びソース間の電圧が定まる。これにより、MOSFET310及び320のゲート電位が、定まる。よって、MOSFET340及び350のゲート電位が、定まる。電流入力ノード65から入力される電流がゼロのとき、MOSFET340及び350のドレイン電流は等しいが、 $I_p$  の電流を入力すると、電流入力ノード65の電位が上昇する。40

これにより、MOSFET 340 のゲート及びソース間の電圧が増加することにより、MOSFET 340 のドレイン電流が増加する。また、MOSFET 350 のゲート及びソース間の電圧が減少することにより、MOSFET 350 のドレイン電流は減少する。これらにより、MOSFET 340 及び 350 のドレイン電流の差は  $I_p$  となる。よって、MOSFET 330 及び MOSFET 360 のドレイン電流の差も  $I_p$  となる。ここで、MOSFET 330、380、360、370 のゲート長をそれぞれ  $L_1$ 、 $L_2$ 、 $L_3$ 、 $L_4$  とし、MOSFET 330、380、360、370 のゲート幅をそれぞれ  $W_1$ 、 $W_2$ 、 $W_3$ 、 $W_4$  とする。また、次式(15)とすると、電流出力ノード 70 からは、 $-A \times I_p$  の電流が出力される。よって、電流ゲインは  $-A$  となる。

【0066】

10

【数15】

$$A = \frac{\left(\frac{W_2}{L_2}\right)}{\left(\frac{W_1}{L_1}\right)} = \frac{\left(\frac{W_4}{L_4}\right)}{\left(\frac{W_3}{L_3}\right)} \quad \dots (15)$$

【0067】

上述のように、式(5)の電流ゲインは、Vth ばらつきによるプロセスばらつき及び Vgs の光量依存による光量依存を有するので、図12の構成によって、それらを低減することが可能となる。以上のように、本実施形態は、電流ゲインのばらつき低減、電流ゲインの光量依存低減による線形性の向上、が可能となる。

20

【0068】

(第11の実施形態)

図13は、本発明の第11の実施形態に係る光電変換装置の電流增幅手段50の構成例を示す図である。但し、ここでは上述した第10の実施形態との相違点についてのみ説明する。図13においては、電流增幅手段50は、図12に対して、さらに、オペアンプ390と、電圧入力ノード400と、MOSFET 410を有している。MOSFET 410は、図12の電流源290に対応する。オペアンプ390は、正転入力ノードが電流入力ノード65に接続され、反転入力ノードが電圧入力ノード400に接続され、出力ノードがMOSFET 300のゲートに接続される。これらにより、電流入力ノード65の電位を電圧入力ノード400の電位とおよそ等しく保つことにより、ノード電位の入力電流依存を抑制することが可能となる。

30

【0069】

図12においては、電流入力ノード65から入力される電流に応じて該ノード65の電位が変化し、MOSFET 340及び350のそれぞれのソース電位が変化することにより、MOSFET 340及び350のそれぞれのゲート及びソース間電圧が変化した。図13においては、MOSFET 340及び350のそれぞれのソースではなく主にゲート電位が変化することにより、MOSFET 340及び350のそれぞれのゲート及びソース間電圧が変化する。電流入力ノード65から入力される電流が  $I_p$  増加すると、該ノード65の電位が上昇しようとするが、それをオペアンプ390が検出し、MOSFET 300のゲート電位を引き上げて、ドレイン電流を増加させる。これにより、MOSFET 310及び320のそれぞれのゲート電位が低下し、MOSFET 340及び350のゲート電位は低下する。よって、MOSFET 340のゲート及びソース間電圧は増加し、MOSFET 350のゲート及びソース間電圧は減少することで、MOSFET 340及び350のドレイン電流の差分が  $I_p$  増加する。よって、電流入力ノード65のノード電位の入力電流依存を抑制することが可能となる。

40

【0070】

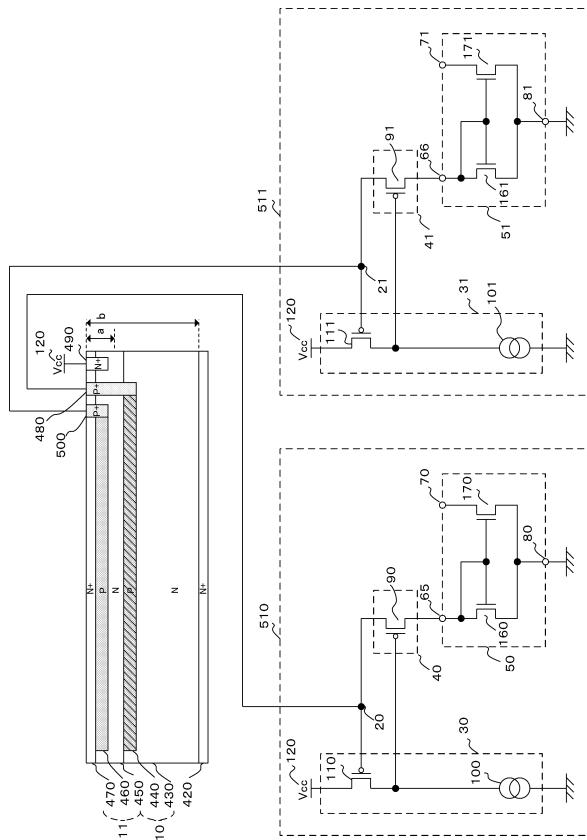

(第12の実施形態)

図14は、本発明の第12の実施形態に係る光電変換装置の構成例を示す図である。但し、ここでは上述した第4の実施形態との相違点についてのみ説明する。N<sup>+</sup>領域 420

50

上に、N型領域430、P型領域440、N型領域450、P型領域460、表面N<sup>+</sup>領域470のように、第1導電型のN型領域（光電変換領域）と第1導電型と逆の導電型である第2導電型のP型領域が交互に複数積層されている。これにより、P型領域440及び460はそれぞれ異なる深さに形成されている。シリコンに入射した光は波長の長いものほど深く侵入するので、P型領域440及び460からは異なる波長帯域の光に対する光信号を得ることができる。このように、図14においては、N型領域430、P型領域440、N型領域450が光電変換素子10を形成し、N型領域450、P型領域460、表面N<sup>+</sup>領域470が光電変換素子11を形成し、深さ方向に複数の光電変換素子10及び11が積層されている。図14においては、P型領域440及び460のそれぞれにコンタクト部480及び500を設けて、それぞれの光電変換素子10及び11から光電流を読み出す構成となっている。それぞれの光電変換素子10及び11に対して、それぞれの読み出し回路510及び511が設けられている。それぞれの読み出し回路510及び511は、それぞれの検出手段30、31を有しており、それぞれの定電流源100、101及び、それぞれの第1のMOSFET110、111を有する。また、それぞれの読み出し回路510及び511は、それぞれのフィードバック手段40、41を有しており、それぞれの第2のMOSFET90、91を有する。読み出し回路510及び511は、それぞれの電流増幅手段50、51を有し、それぞれの電流入力ノード65、66、電流出力ノード70、71、基準電位ノード80、81、第5のMOSFET160、161及び第6のMOSFET170、171を有する。また、図14においては、N型領域450、表面N<sup>+</sup>型領域470中にN型コンタクト部490を設けて、電源電圧ノード120に接続している。このように、図14においては、光電変換素子10及び11のそれぞれに対して読み出し回路510及び511を設けて、それぞれ電流増幅手段50及び51を設けている。これにより、それぞれの光電変換素子10及び11について電流増幅手段50及び51の電流ゲインを最適化し、動作速度を改善することが可能となる。

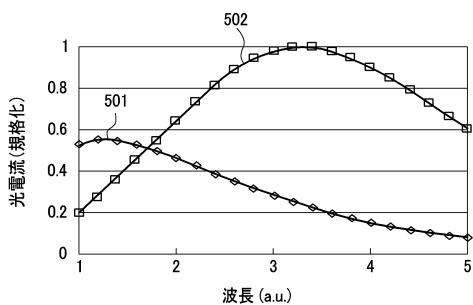

#### 【0071】

図14において、aはN型領域450の深さ方向の不純物プロファイルのピーク位置、bはN<sup>+</sup>領域420上に形成された半導体層のトータルの厚さを示している。図14において、光電変換素子10及び11の分光特性は、主に、この2つのファクターにより決まる。aとbが、ある値の場合の分光特性シミュレーション結果を図15に示す。図15において、横軸が照射光の波長、縦軸がそれぞれの光電変換素子10及び11から得られる光電流であり、波長1強にピークを持っている特性501が光電変換素子11の特性で、波長3強にピークを持っている特性502が光電変換素子10の特性である。図15のような分光特性の場合、ほとんどの分光特性の光源に対して、光電変換素子11は、光電変換素子10よりも小さな光電流しか得ることができない。しかし、電流増幅手段50よりも電流増幅手段51の電流ゲインを大きく設定することにより、電流出力ノード71の出力電流を電流出力ノード70と同等とすることが可能であり、動作速度を改善することが可能となる。すなわち、複数の電流増幅手段50及び51は、相互に電流ゲインが異なる。よって、それぞれの光電変換素子10及び11について、電流増幅手段50及び51の電流ゲインを最適化し、動作速度を改善することが可能となる。

#### 【0072】

##### （第13の実施形態）

上記の図14を用いて、本発明の第13の実施形態に係る光電変換装置について説明する。但し、ここでは上述した第12の実施形態との相違点についてのみ説明する。図14において、第5のMOSFET160及び161のゲート長を相互に等しくすることにより、分光特性の光量依存を抑制することが可能となる。

#### 【0073】

電流増幅手段50及び51の電流ゲインは式(13)のようになり、電流入力ノード65及び66の電位V<sub>in</sub>が光量に依存するので、それぞれのゲインは光量に対して緩やかに変化する。この際、第5のMOSFET160及び161のゲート長が異なると、チャネル長変調係数<sub>1</sub>が異なるために、電流ゲインは光量に対して異なる依存を示してしま

う。よって、電流出力ノード 70 及び 71 から出力される電流の比が光量に依存してしまう。ゆえに、第 5 の MOSFET 160 及び 161 のゲート長を相互に等しくすることにより、分光特性の光量依存を抑制することが可能となる。

#### 【0074】

上記の第 1 ~ 第 13 の実施形態では、光電変換素子 10 及び 11 としてホールを集めるタイプのものを用いた場合を例にとって説明したが、これに限られるものではない。光電変換素子 10 及び 11 として電子を集めタイプのものを用いた場合でも、同様な構成をとることにより同様な効果が得られる。

#### 【0075】

また、上記の第 1 ~ 第 13 の実施形態では、検出手段 30 及び 31 として、ソース接地回路を用いた場合を例にとって説明したが、これに限られるものではない。また、上記の第 1 ~ 第 13 の実施形態では、フィードバック手段 40 及び 41 として、MOSFET を用いた場合を例にとって説明したが、これに限られるものではない。また、上記の第 1 ~ 第 13 の実施形態では、電流增幅手段 50 及び 51 として、ソース接地回路もしくはカレントミラー回路もしくはオペアンプもしくはカレントコンベアを用いた場合を例にとって説明したが、これらに限られるものではない。

10

#### 【0076】

また、上記の第 5 及び第 6 の実施形態では、電圧バッファ 180 及び 181 として、ソースフォロワの場合を例にとって説明したが、これに限られるものではない。また、上記の第 13 及び第 14 の実施形態では、深さ方向に積層した光電変換素子 10 及び 11 の数を 2 の場合を例にとって説明したが、これに限られるものではない。

20

#### 【0077】

なお、上記実施形態は、何れも本発明を実施するにあたっての具体化の例を示したものに過ぎず、これらによって本発明の技術的範囲が限定的に解釈されてはならないものである。すなわち、本発明はその技術思想、又はその主要な特徴から逸脱することなく、様々な形で実施することができる。

#### 【符号の説明】

#### 【0078】

10 10 光電変換素子、20 ノード、30 検出手段、40 フィードバック手段、50 電流增幅手段、60 抵抗、65 電流入力ノード、70 電流出力ノード、80 基準電位ノード

30

【図1】

【図3】

【図2】

【図4】

【図5】

【図7】

【図6】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

---

フロントページの続き

(56)参考文献 特開平07-203319(JP,A)

特開平11-088770(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/30 - 5/378

H01L 27/14 - 27/148