## (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2009-49208 (P2009-49208A)

(43) 公開日 平成21年3月5日(2009.3.5)

| (51) Int.Cl. |         |           | F I        |     | テーマコード(参考) |

|--------------|---------|-----------|------------|-----|------------|

| HO1L         | 21/8247 | (2006.01) | HO1L 29/78 | 371 | 5F083      |

| HO1L         | 29/788  | (2006.01) | HO1L 27/10 | 434 | 5 F 1 O 1  |

HO1L 29/792 (2006.01) HO1L 27/115 (2006, 01)

> 審査請求 未請求 請求項の数 10 OL (全 14 頁)

| (21) 出願番号<br>(22) 出願日 | 特願2007-214097 (P2007-214097)<br>平成19年8月20日 (2007.8.20) | (71) 出願人 | 504378124<br>スパンション エルエルシー<br>アメリカ合衆国 カリフォルニア州 94<br>088-3453 サニーベイル デグウィン ドライブ 915 |

|-----------------------|--------------------------------------------------------|----------|-------------------------------------------------------------------------------------|

|                       |                                                        | (74)代理人  | 100087480                                                                           |

|                       |                                                        |          | 弁理士 片山 修平                                                                           |

|                       |                                                        | (74) 代理人 | 100137615                                                                           |

|                       |                                                        |          | 弁理士 横山 照夫                                                                           |

|                       |                                                        | (72) 発明者 | 井上 文彦                                                                               |

|                       |                                                        |          | 福島県会津若松市高久工業団地2番 Sp                                                                 |

ansion Japan株式会社内 (72) 発明者 相馬 春木

福島県会津若松市高久工業団地2番 Sp ansion Japan株式会社内 最終頁に続く

(54) 【発明の名称】半導体装置およびその製造方法

# (57)【要約】

【課題】仮想接地型フラッシュメモリにおいて、製造が 容易で、メモリセルの高集積化、微細化が可能な半導体 装置およびその製造方法を提供すること。

【解決手段】本発明は、半導体基板10内に延伸するよ うに設けられたビットライン12と、半導体基板10上 に設けられた電荷蓄積層16と、電荷蓄積層16上にビ ットライン12に交差して延伸するように設けられたワ ードライン22と、ワードライン22直下の半導体基板 10内であり、且つ、ビットライン12間の領域である チャネル領域24と、を具備し、チャネル領域24上に 設けられた電荷蓄積層16のワードライン22幅方向の 幅Wが、ワードライン22延伸方向のチャネル領域24 の端部 E からチャネル領域 2 4 の中央部に向かうに連れ て狭くなる半導体装置である。

【選択図】図4

## 【特許請求の範囲】

# 【請求項1】

半導体基板内に延伸するように設けられたビットラインと、

前記半導体基板上に設けられた電荷蓄積層と、

前記電荷蓄積層上に前記ビットラインに交差して延伸するように設けられたワードラインと、

前記ワードライン直下の前記半導体基板内であり、且つ、前記ビットライン間の領域であるチャネル領域と、を具備し、

前記チャネル領域上に設けられた前記電荷蓄積層の前記ワードライン幅方向の幅が、前記ワードライン延伸方向の前記チャネル領域の端部から前記チャネル領域の中央部に向かうに連れて狭くなることを特徴とする半導体装置。

【請求項2】

前記チャネル領域上に設けられた前記電荷蓄積層は、前記ワードライン延伸方向の前記チャネル領域の中央部上で分離していることを特徴とする請求項1記載の半導体装置。

# 【請求項3】

前記半導体基板と前記電荷蓄積層との間に設けられたトンネル絶縁膜と、

前記電荷蓄積層上に設けられたトップ絶縁膜と、を具備し、

前記チャネル領域上に設けられた前記電荷蓄積層は、前記トンネル絶縁膜と前記トップ 絶縁膜とに挟まれて設けられた空洞部に接していることを特徴とする請求項1または2記載の半導体装置。

【請求項4】

前記半導体基板と前記電荷蓄積層との間に設けられたトンネル絶縁膜と、

前記電荷蓄積層上に設けられたトップ絶縁膜と、を具備し、

前記チャネル領域上に設けられた前記電荷蓄積層は、前記トンネル絶縁膜と前記トップ 絶縁膜とに挟まれて設けられた絶縁膜に接していることを特徴とする請求項1または2記載の半導体装置。

## 【請求頃5】

前記電荷蓄積層は、窒化膜であることを特徴とする請求項1から4のいずれか一項記載の半導体装置。

# 【請求項6】

半導体基板内に延伸するようにビットラインを形成する工程と、

前記半導体基板上に電荷蓄積層を形成する工程と、

前記電荷蓄積層上にトップ絶縁膜を形成する工程と、

前記トップ絶縁膜上に前記ビットラインに交差して延伸するようにワードラインを形成する工程と、

前記ワードライン間で、且つ前記ビットライン間の中央部の前記トップ絶縁膜に孔部を 形成する工程と、

前記孔部から等方性エッチングを用いて前記電荷蓄積層をエッチングする工程と、を有することを特徴とする半導体装置の製造方法。

## 【請求項7】

前記電荷蓄積層をエッチングする工程は、前記ワードライン直下の前記半導体基板内であり、且つ、前記ビットライン間の領域であるチャネル領域の、前記ワードライン延伸方向の中央部上で、前記電荷蓄積層が分離するように、前記電荷蓄積層をエッチングする工程であることを特徴とする請求項6記載の半導体装置の製造方法。

## 【請求項8】

前記孔部を形成する工程は、前記ワードラインを形成する工程の後に行うことを特徴とする請求項6または7記載の半導体装置の製造方法。

## 【請求項9】

前記電荷蓄積層をエッチングする工程の後、前記電荷蓄積層をエッチングした領域に絶縁膜を形成する工程を有することを特徴とする請求項6から8のいずれか一項記載の半導

10

20

30

50

体装置の製造方法。

# 【請求項10】

前記電荷蓄積層は、窒化膜であることを特徴とする請求項6から9のいずれか一項記載の半導体装置の製造方法。

【発明の詳細な説明】

## 【技術分野】

## [0001]

本発明は、半導体装置およびその製造方法に関し、より詳細には、チャネル領域の中央部で幅が狭い電荷蓄積層を有する半導体装置およびその製造方法に関する。

## 【背景技術】

[0002]

近年、データの書き換えが可能で、電源をOFFしても記憶データを保持し続ける半導体装置である不揮発性メモリが広く利用されている。代表的な不揮発性メモリであるフラッシュメモリにおいては、メモリセルを構成するトランジスタが電荷蓄積層と呼ばれるフローティングゲートもしくは絶縁膜を有している。この電荷蓄積層に電子を蓄積させることによりデータを記憶する。絶縁膜を電荷蓄積層とするフラッシュメモリとしてONO(Oxide Nitride Oxide)膜中の窒化膜に電子を蓄積させるSONOS(Silicon Oxide Nitride Oxide Silicon)型構造のフラッシュメモリがある。特許文献1にはSONOS型構造のフラッシュメモリの1つとして、ソースとドレインとを入れ替えて対称的に動作させる仮想接地型メモリセルを有する、仮想接地型フラッシュメモリ(従来例1)が開示されている。

## [0003]

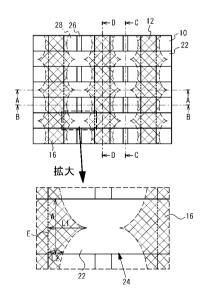

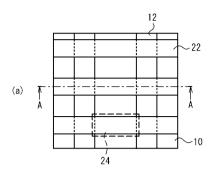

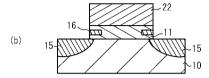

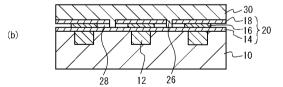

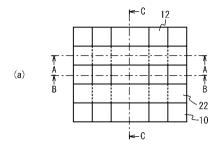

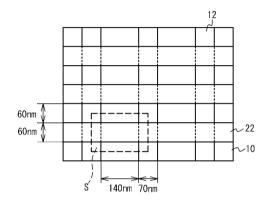

図1(a)は従来例1に係るフラッシュメモリの模式的上面図であり、図1(b)は図1(a)のA‐A間の模式的断面図である。なお、図1(a)において、ONO膜20を透視してビットライン12を図示している。図1(a)および図1(b)を参照に、半導体基板10内にビットライン12が延伸するように設けられている。半導体基板10上にトンネル絶縁膜14、電荷蓄積層16およびトップ絶縁膜18からなるONO膜20が設けられている。ONO膜20上にはワードライン22がビットライン12に交差して延伸するように設けられている。ビットライン12はソースおよびドレインを兼ねており、ワードライン22はゲートを兼ねている。ワードライン22直下の半導体基板10内で、ビットライン12間の領域がチャネル領域24となる。

# [0004]

ビットライン12(B1)をソース、ビットライン12(B2)をドレインとし、ソースとドレイン間に高電界を印加することにより、チャネル領域24を電子が流れ、電荷蓄積層16の電荷蓄積領域C1に電荷を蓄積させることができる。ソースとドレインとを入れ替えることにより、電荷蓄積領域C2に電荷を蓄積させることができる。このように、ソースとドレインとを対称的に動作させることにより、1トランジスタの電荷蓄積層16に2つの電荷蓄積領域を形成することができる。これにより、1トランジスタに2ビットを記憶させることができる。

# [0005]

近年、メモリセルの高集積化、微細化の要求が高くなっている。メモリセルの高集積化、微細化を図るには、ビットライン12間の間隔(B1とB2との間隔)を狭くする必要がある。ビットライン12間の間隔を狭くすると、電荷蓄積領域C1と電荷蓄積領域C2とが互いに接近する。このため、CBD(Complementary bit disturb)と呼ばれる現象が生じ、電荷蓄積領域C1と電荷蓄積領域C2とに蓄積した電荷が互いに干渉し合うようになる。これにより、互いの電荷の切り分け(つまり、データの読み分け)が難しくなる

# [0006]

NAND型フラッシュメモリにおいては、図2(a)に示す従来例2や図2(b)に示す従来例3の構造を採用することにより、電荷蓄積領域に蓄積した電荷が互いに干渉し合

10

20

30

40

10

20

30

40

50

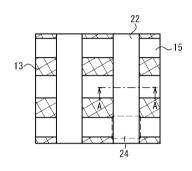

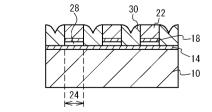

うことを抑制する方法が提案されている。図3はNAND型フラッシュメモリの模式的上面図であり、図2(a)および図2(b)は図3のA-A間に相当する箇所の模式的断面図を示している。なお、図3において、電荷蓄積層16等は図示を省略している。

## [0007]

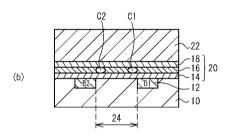

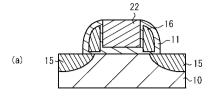

図3を参照に、素子分離領域13(図3中の網線)により、半導体基板10内にソース・ドレイン領域15が孤立して設けられている。ソース・ドレイン領域15の間に配置されるように、半導体基板10上にワードライン22が設けられている。図2(a)を参照に、半導体基板10上に酸化膜11を挟んでワードライン22が設けられており、ワードライン22の両側面に酸化膜11で覆われた電荷蓄積層16が分離して設けられている。図2(b)を参照に、半導体基板10上に酸化膜11を挟んでワードライン22が設けられており、ワードライン22の両端で、ワードライン22と半導体基板10との間に酸化膜11で覆われた電荷蓄積層16が分離して設けられている。

[0008]

図3に示すように、NAND型フラッシュメモリでは、ワードライン22を挟むように、ソース・ドレイン領域15が設けられている。これにより、ワードライン22幅方向のソース・ドレイン領域15間の領域がチャネル領域24となる。このため、ワードライン22幅方向の両端に電荷蓄積領域が形成される。よって、図2(a)や図2(b)に示すように、ワードライン22の両側面等に電荷蓄積層16を分離して形成することで、電荷蓄積領域を分離させることができる。このため、電荷蓄積領域に蓄積した電荷が干渉し合うことを抑制することができる。

【特許文献1】米国特許第6011725号明細書

【発明の開示】

【発明が解決しようとする課題】

[0009]

図2(a)や図2(b)に示すような、ワードライン22の両側面等に電荷蓄積層16を分離して形成することは容易に行うことができる。しかしながら、仮想接地型フラッシュメモリにおいては、図1(a)および図1(b)に示すように、ワードライン22直下のビットライン12間の領域がチャネル領域24となるため、電荷蓄積領域はワードライン22延伸方向のビットライン12近傍の電荷蓄積層16に形成される。このため、図2(a)や図2(b)に示すような構造を用いても、電荷蓄積領域を分離することができない。また、ワードライン22延伸方向のビットライン12近傍に形成された電荷蓄積領域を分離させるため、ワードライン22延伸方向で分離した電荷蓄積層16を形成することは難しい。

[ 0 0 1 0 ]

本発明は、上記課題に鑑みなされたものであり、仮想設置型フラッシュメモリにおいて、製造が容易で、メモリセルの高集積化、微細化が可能な半導体装置およびその製造方法を提供することを目的とする。

【課題を解決するための手段】

[0011]

本発明は、半導体基板内に延伸するように設けられたビットラインと、前記半導体基板上に設けられた電荷蓄積層と、前記電荷蓄積層上に前記ビットラインに交差して延伸するように設けられたワードラインと、前記ワードライン直下の前記半導体基板内であり、且つ、前記ビットライン間の領域であるチャネル領域と、を具備し、前記チャネル領域上に設けられた前記電荷蓄積層の前記ワードライン幅方向の幅が、前記ワードライン延伸方向の前記チャネル領域の端部から前記チャネル領域の中央部に向かうに連れて狭くなることを特徴とする半導体装置である。本発明によれば、電荷蓄積領域に蓄積した電荷の干渉を抑制することができ、メモリセルの高集積化、微細化が可能となり、且つ、製造が容易な半導体装置を得ることができる。

[ 0 0 1 2 ]

上記構成において、前記チャネル領域上に設けられた前記電荷蓄積層は、前記ワードラ

イン延伸方向の前記チャネル領域の中央部上で分離している構成とすることができる。この構成によれば、電荷蓄積領域に蓄積した電荷の干渉をより抑制することができる。

## [0013]

上記構成において、前記半導体基板と前記電荷蓄積層との間に設けられたトンネル絶縁膜と、前記電荷蓄積層上に設けられたトップ絶縁膜と、を具備し、前記チャネル領域上に設けられた前記電荷蓄積層は、前記トンネル絶縁膜と前記トップ絶縁膜とに挟まれて設けられた空洞部に接している構成とすることができる。この構成によれば、電荷蓄積領域に蓄積した電荷の干渉を抑制することができる。

# [0014]

上記構成において、前記半導体基板と前記電荷蓄積層との間に設けられたトンネル絶縁膜と、前記電荷蓄積層上に設けられたトップ絶縁膜と、を具備し、前記チャネル領域上に設けられた前記電荷蓄積層は、前記トンネル絶縁膜と前記トップ絶縁膜とに挟まれて設けられた絶縁膜に接している構成とすることができる。この構成によれば、電荷蓄積領域に蓄積した電荷の干渉を抑制することができる。

## [0015]

上記構成において、前記電荷蓄積層は、窒化膜である構成とすることができる。

## [0016]

本発明は、半導体基板内に延伸するようにビットラインを形成する工程と、前記半導体基板上に電荷蓄積層を形成する工程と、前記電荷蓄積層上にトップ絶縁膜を形成する工程と、前記トップ絶縁膜上に前記ビットラインに交差して延伸するようにワードラインを形成する工程と、前記ワードライン間で、且つ前記ビットライン間の中央部の前記トップ絶縁膜に孔部を形成する工程と、前記孔部から等方性エッチングを用いて前記電荷蓄積層をエッチングする工程と、を有することを特徴とする半導体装置の製造方法。本発明によれば、電荷蓄積領域に蓄積した電荷の干渉を抑制することができ、メモリセルの高集積化、微細化が可能な半導体装置を容易に形成することができる。

# [0017]

上記構成において、前記電荷蓄積層をエッチングする工程は、前記ワードライン直下の前記半導体基板内であり、且つ、前記ビットライン間の領域である前記チャネル領域の、前記ワードライン延伸方向の中央部上で、前記電荷蓄積層が分離するように、前記電荷蓄積層をエッチングする工程である構成とすることができる。この構成によれば、電荷蓄積領域に蓄積した電荷の干渉をより抑制させることができる。

# [0018]

上記構成において、前記孔部を形成する工程は、前記ワードラインを形成する工程の後に行う構成とすることができる。この構成によれば、ワードラインに自己整合的に孔部を形成することができる。

# [0019]

上記構成において、前記電荷蓄積層をエッチングする工程の後、前記電荷蓄積層をエッチングした領域に絶縁膜を形成する工程を有する構成とすることができる。この構成によれば、電荷蓄積領域に蓄積した電荷の干渉を抑制させることができる。

## [0020]

上記構成において、前記電荷蓄積層は、窒化膜である構成とすることができる。

## 【発明の効果】

# [0021]

本発明によれば、仮想接地型フラッシュメモリにおいて、電荷蓄積領域に蓄積した電荷の干渉を抑制することができ、メモリセルの高集積化、微細化が可能となり、且つ、製造が容易な半導体装置を得ることができる。

# 【発明を実施するための最良の形態】

# [0022]

以下、図面を参照に本発明の実施例を説明する。

# 【実施例1】

50

10

20

30

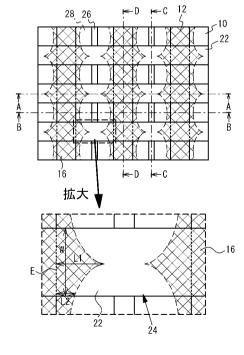

## [ 0 0 2 3 ]

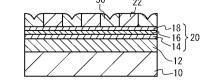

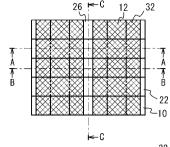

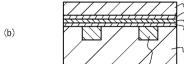

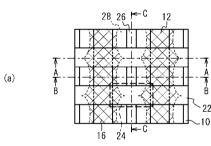

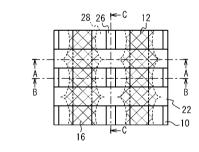

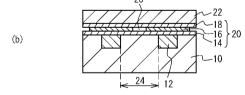

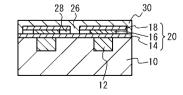

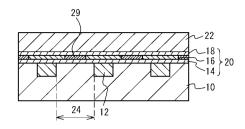

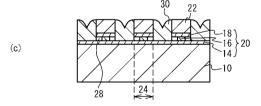

図4は実施例1に係る仮想接地型フラッシュメモリの模式的上面図であり、図5(a)は図4のA-A間の模式的断面図、図5(b)は図4のB-B間の模式的断面図、図5(c)は図4のC-C間の模式的断面図、図5(d)は図4のD-D間の模式的断面図である。なお、図4において、ワードライン22、サイドウォール層30およびトップ絶縁膜18を透視して電荷蓄積層16(図4中の網線)を図示しており、ONO膜20およびサイドウォール層30を透視してビットライン12を図示しており、サイドウォール層30を透視して孔部26を図示している。

## [0024]

図4から図5(d)を参照に、例えばP型シリコン基板(あるいは半導体基板内のP型領域)である半導体基板10内に延伸するようにビットライン12が設けられている。半導体基板10上に、例えばSiO2膜からなるトンネル絶縁膜14、例えばSiN膜からなる電荷蓄積層16、例えばSiO2膜からなるトップ絶縁膜18が順次設けられており、ONO膜20を構成している。ONO膜20上にビットライン12に交差して延伸するワードライン22が設けられている。

## [0025]

図 4 、図 5 ( a ) および図 5 ( c ) を参照に、ワードライン 2 2 直下の半導体基板 1 0 内で、ビットライン 1 2 間の領域はチャネル領域 2 4 となる。

#### [0026]

図4から図5(c)を参照に、ワードライン22間で、且つビットライン12間の中央部のトップ絶縁膜18に孔部26が設けられており、孔部26を中心として楕円状に電荷蓄積層16が除去されている。これにより、トンネル絶縁膜14とトップ絶縁膜18とに挟まれて、電荷蓄積層16の側面に接する空洞部28が形成されている。

# [ 0 0 2 7 ]

図4を参照に、楕円状に形成された空洞部28により、チャネル領域24上に設けられた電荷蓄積層16のワードライン22幅方向の幅Wが、ワードライン22延伸方向のチャネル領域24の端部Eからチャネル領域24の中央部に向かうに連れて曲線状に狭くなっている。言い換えると、端部Eの中央における、端部Eからの電荷蓄積層16の長さL1は、端部Eの端における、端部Eからの電荷蓄積層16の長さL2より長く、端部Eの中央から端部Eの端に向かうに連れて、端部Eからの電荷蓄積層16の長さはL1からL2に曲線状に短くなっている。また、チャネル領域24の中央部上で電荷蓄積層16は分離している。

## [0028]

図 5 ( b ) から図 5 ( d ) を参照に、ワードライン 2 2 の側壁に、例えば S i O  $_2$  膜からなるサイドウォール層 3 0 が設けられており、サイドウォール層 3 0 は孔部 2 6 にも埋め込まれている。

# [ 0 0 2 9 ]

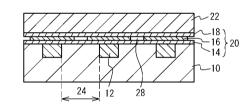

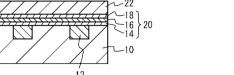

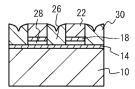

次に、図6(a)から図9(d)を用い、実施例1に係る仮想接地型フラッシュメモリの製造方法を説明する。なお、図6(a)において、ONO膜20を透視してビットライン12を図示しており、図8(a)において、ワードライン22およびトップ絶縁膜18を透視して電荷蓄積層16(図8(a)中の網線)を図示している。また、図9(a)において、サイドウォール層30の図示を省略している。

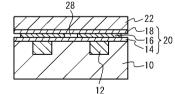

# [0030]

図 6 ( a )から図 6 ( d )を参照に、例えば P 型シリコン基板(あるいは半導体基板内の P 型領域)である半導体基板 1 0 内に、例えば砒素イオンを注入し、その後熱処理することで N 型拡散領域である、例えば幅 7 0 n m の ビットライン 1 2 を延伸するように形成する。半導体基板 1 0 上に、例えば厚さ 7 n m の S i O  $_2$  膜からなるトンネル絶縁膜 1 4 、例えば厚さ 7 n m の S i N 膜からなる電荷蓄積層 1 6 、例えば厚さ 1 0 n m の S i O  $_2$  膜からなるトップ絶縁膜 1 8 を順次形成する。トンネル絶縁膜 1 4 およびトップ絶縁膜 1 8 の形成は、例えば C V D (化学気相成長)法または熱酸化法を用いることができる。電

10

20

30

40

荷蓄積層16の形成は、例えばCVD法を用いることができる。これにより、半導体基板10上にトンネル絶縁膜14、電荷蓄積層16、トップ絶縁膜18からなるONO膜20が形成される。ONO膜20上に、例えばポリシリコンからなり幅60nmのワードライン22をビットライン12に交差して延伸するように形成する。

# [0031]

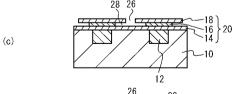

図7(a)から図7(d)を参照に、ワードライン22を覆うようにONO膜20上にフォトレジスト32を塗布する。例えばレジストシュリンクプロセスあるいは2重露光プロセスを用いて、ビットライン12間の中央部のフォトレジスト32に、例えば30nmの幅の開口部を形成する。フォトレジスト32をマスクに、例えばRIE(反応性イオンエッチング)法を用いて、トップ絶縁膜18をドライエッチングする。これにより、ワードライン22間で、且つビットライン12間の中央部に、幅30nmの孔部26が形成される。なお、トップ絶縁膜18をエッチングする際、ワードライン22もプラズマに曝されるが、ワードライン22はポリシリコンからなるため、ほとんどエッチングがされない

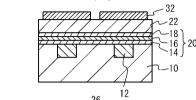

# [0032]

図8(a)から図8(d)を参照に、フォトレジスト32を除去した後、例えば150のリン酸をエッチング液とし、孔部26からこのリン酸を流入させ、ワードライン22延伸方向のチャネル領域24の中央部上で電荷蓄積層16が分離するよう、電荷蓄積層16を除去する。リン酸によるウエットエッチングは等方性エッチングであるため、電荷蓄積層16は孔部26を中心に楕円状に除去され、トンネル絶縁膜14とトップ絶縁膜18との間に、電荷蓄積層16の側面に接する空洞部28が形成される。楕円状に形成された空洞部28により、チャネル領域24上に設けられた電荷蓄積層16のワードライン22幅方向の幅が、ワードライン22延伸方向のチャネル領域24の端部からチャネル領域24の中央部に向かうに連れて曲線状に狭くなる。なお、孔部26からリン酸を流入させ電荷蓄積層16を除去する際、トンネル絶縁膜14とトップ絶縁膜18とはほとんどエッチングがされずにそのまま残存する。

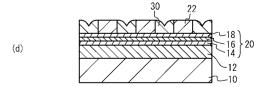

## [0033]

図 9 ( a )から図 9 ( d )を参照に、ワードライン 2 2 を覆うように半導体基板 1 0 上に S i O 2 膜を形成する。その後、S i O 2 膜を、例えば R I E 法を用いて、ワードライン 2 2 の表面が露出するまで全面エッチングする。これにより、ワードライン 2 2 の側壁に S i O 2 膜からなるサイドウォール層 3 0 が形成される。また、ビットライン 1 2 間の中央部の孔部 2 6 にもサイドウォール層 3 0 が埋め込まれる。以上により、実施例 1 に係る半導体装置が完成する。

# [0034]

実施例1によれば、図4に示すように、チャネル領域24上に設けられた電荷蓄積層16のワードライン22幅方向の幅Wが、ワードライン22延伸方向のチャネル領域24の端部Eからチャネル領域24の中央部に向かうに連れて曲線状に狭くなっている。そして、ワードライン22延伸方向のチャネル領域24の中央部上で電荷蓄積層16は分離している。このため、チャネル領域24のビットライン12近傍に形成される電荷蓄積領域を分離させることができる。また、分離した電荷蓄積層16はトンネル絶縁膜14とトップ絶縁膜18との間に設けられた空洞部28に接している。このため、電荷蓄積領域に蓄積した電荷は移動することができない。したがって、ビットライン12間の間隔が狭くなった場合でも、電荷蓄積領域に蓄積した電荷が干渉し合うことを抑制することができる。

## [0035]

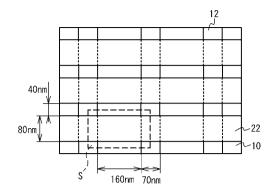

このことから、従来例1に係る仮想接地型フラッシュメモリにおいては、メモリセルSの大きさは、図10に示すように、横230nm×縦120nmであったのに対して、実施例1に係る仮想接地型フラッシュメモリでは、図11に示すように、横210nm×縦120nmにまでメモリセルSの大きさを微細化することが可能となる。

# [0036]

50

10

20

30

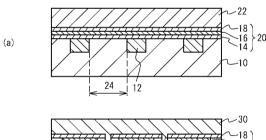

また、実施例 1 において、図 4 および図 5 (a)に示すように、チャネル領域 2 4 上に設けられた電荷蓄積層 1 6 は、トンネル絶縁膜 1 4 とトップ絶縁膜 1 8 とに挟まれて設けられた空洞部 2 8 に接している場合を例に示したがこれに限られない。図 1 2 に示すように、空洞部 2 8 の代わりに例えば S i O  $_2$  膜からなる絶縁膜 2 9 が設けられている場合でもよい。この場合でも、電荷蓄積領域に蓄積した電荷は移動することができず、電荷蓄積領域に蓄積した電荷が干渉し合うことを抑制することができる。なお、絶縁膜 2 9 は S i O  $_2$  膜に限られず、電荷の移動を阻止することができれば、その他の絶縁膜を用いてもよい。

## [0037]

絶縁膜29の形成は、図8(a)から図8(d)に示す、電荷蓄積層16をエッチングして空洞部28を形成した後、電荷蓄積層16をエッチングした領域である空洞部28に、例えば回り込み堆積が良好なLP-CVD(減圧化学気相成長)法を用いて、絶縁膜29を空洞部28に埋め込むことで形成することができる。

## [0038]

さらに、実施例1において、電荷蓄積層16はSiN膜からなる場合を例に示したがこれに限られない。SiN膜と同様に電荷を局所的に蓄積することが可能であれば、その他の材料を用いた場合でもよい。また、図4(b)に示すように、サイドウォール層30が孔部26に埋め込まれている場合を例に示したが、サイドウォール層30が孔部26に埋め込まれずに、孔部26はそのまま残存している場合でもよい。

# [0039]

実施例1の製造方法によれば、図6(a)から図6(d)に示すように、半導体基板10内に延伸するようにビットライン12を形成し、半導体基板10上にトンネル絶縁膜14、電荷蓄積層16、トップ絶縁膜18からなるONO膜20を形成し、ONO膜20とにビットライン12に交差して延伸するようにワードライン22を形成する。次に、図の中央部のトップ絶縁膜18をエッチングして孔部26を形成する。その後、図8(a)から図8(d)に示すように、ワードライン22間で、且つビットライン12間の中央部のトップ絶縁膜18をエッチングして孔部26を形成する。その後、図8(a)がら図8(d)に示すように、リン酸をエッチング液とし、孔部26から等方的に電荷でのチャネル領域24上に設けられた電荷荷層16のワードライン22幅方向の幅が、ワードライン22延伸方向でのチャネル領域24の中央部に連れて曲線状に狭くなり、ワードライン22延伸方向のチャネル領域24の中央部上で分離した電荷を容易に形成することができる。したがって、電荷蓄積領域に蓄積した電荷の干渉を抑制することができる、メモリセルの高集積化、微細化が可能な半導体装置を容易に形成することができる。

# [0040]

特に、リン酸を用いたウエットエッチングは、リン酸の温度を制御することで、電荷蓄積層 1 6 のエッチングレートを制御することができる。つまり、電荷蓄積層 1 6 のエッチング量を制御することができる。よって、リン酸の温度を制御することで、チャネル領域 2 4 のビットライン 1 2 近傍に形成される電荷蓄積領域となるべき領域の電荷蓄積層 1 6 は残存させ、ワードライン 2 2 延伸方向のチャネル領域 2 4 の中央部上で電荷蓄積層 1 6 を分離させることを容易に行うことができる。

# [ 0 0 4 1 ]

さらに、実施例1の製造方法によれば、図6(a)から図6(d)に示すように、半導体基板10上にONO膜20とワードライン22とを形成した後に、図7(a)から図7(d)に示すように、トップ絶縁膜18に孔部26を形成している。このため、ワードライン22に自己整合的にトップ絶縁膜18をエッチングして孔部26を形成することができる。つまり、ワードライン22直下のトップ絶縁膜18を残存させることができる。

## [0042]

さらに、実施例1の製造方法において、図8(a)から図8(d)に示すように、リン酸を用いて電荷蓄積層16をエッチングする場合を例に示したが、ケミカルドライエッチング等、その他の等方性エッチングを用いて電荷蓄積層16をエッチングする場合でもよ

10

20

30

40

10

20

30

40

50

い。この場合でも、電荷蓄積領域に蓄積した電荷の干渉を抑制することができ、メモリセルの高集積化、微細化が可能な半導体装置を容易に形成することができる。

## 【実施例2】

# [0043]

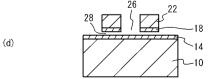

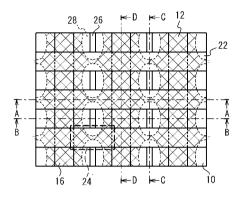

実施例 2 は、ワードライン 2 2 延伸方向のチャネル領域 2 4 の中央部上で電荷蓄積層 1 6 が分離していない場合の例である。図 1 3 は実施例 2 に係る仮想接地型フラッシュメモリの模式的上面図であり、図 1 4 (a) は図 1 3 の A - A 間の模式的断面図、図 1 4 (b) は図 1 3 の B - B 間の模式的断面図、図 1 4 (c) は図 1 3 の C - C 間の模式的断面図、図 1 4 (d) は図 1 3 の D - D 間の模式的断面図である。なお、図 1 3 において、ワードライン 2 2、サイドウォール層 3 0 およびトップ絶縁膜 1 8 を透視して電荷蓄積層 1 6 (図 1 4 中の網線)を図示しており、 O N O 膜 2 0 およびサイドウォール層 3 0 を透視して光部 2 6 を図示している。

# [0044]

図13から図14(d)を参照に、ワードライン22延伸方向のチャネル領域24の中央部上で電荷蓄積層16が分離していない。その他の構成については、実施例1と同じであり、図4から図5(d)に示しているので、説明を省略する。

#### [0045]

実施例2に係る仮想接地型フラッシュメモリの製造方法は、図8(a)から図8(d)に示す電荷蓄積層16をエッチングする工程において、ワードライン22延伸方向のチャネル領域24の中央部上で電荷蓄積層16を分離させず、ワードライン22幅方向の電荷蓄積層16の幅が狭くなるように電荷蓄積層16をエッチングする以外は実施例1と同じであり、図6(a)から図9(d)に示しているので説明を省略する。

## [0046]

実施例 2 によれば、図 1 3 から図 1 4 ( d ) に示すように、ワードライン 2 2 延伸方向のチャネル領域 2 4 の中央部上で電荷蓄積層 1 6 が分離していない。この場合でも、ワードライン 2 2 幅方向の電荷蓄積層 1 6 の幅が十分に狭い場合は、電荷蓄積領域に蓄積した電荷が移動することができない。したがって、ビットライン 1 2 間の間隔が狭くなった場合でも、電荷蓄積領域に蓄積した電荷が干渉し合うことを抑制することができ、メモリセルの高集積化、微細化を図ることができる。

## [0047]

以上、本発明の実施例について詳述したが、本発明は係る特定の実施例に限定されるものではなく、特許請求の範囲に記載された本発明の要旨の範囲内において、種々の変形・変更が可能である。

# 【図面の簡単な説明】

# [0048]

- 【図1】図1(a)は従来例1に係るフラッシュメモリの模式的上面図であり、図1(b)は図1(a)のA-A間の模式的断面図である。

- 【図2】図2(a)は従来例2に係るフラッシュメモリの模式的断面図であり、図2(b)は従来例3に係るフラッシュメモリの模式的断面図である。

- 【図3】図3はNAND型フラッシュメモリの模式的上面図である。

- 【 図 4 】 図 4 は 実 施 例 1 に 係 る フ ラ ッ シ ュ メ モ リ の 模 式 的 上 面 図 で あ る 。

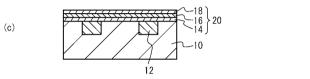

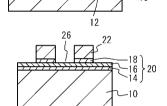

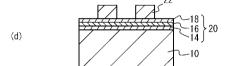

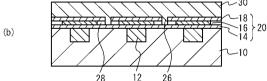

- 【図5】図5 (a)は図4のA-A間の模式的断面図、図5 (b)は図4のB-B間の模式的断面図、図5 (c)は図4のC-C間の模式的断面図、図5 (d)は図4のD-D間の模式的断面図である。

- 【図6】図6(a)は実施例1に係るフラッシュメモリの製造方法を示す模式的上面図(その1)であり、図6(b)は図6(a)のA-A間の模式的断面図、図6(c)は図6(a)のB-B間の模式的断面図、図6(d)は図6(a)のC-C間の模式的断面図である。

- 【図7】図7(a)は実施例1に係るフラッシュメモリの製造方法を示す模式的上面図(

その 2 )であり、図 7 ( b )は図 7 ( a )の A - A 間の模式的断面図、図 7 ( c )は図 7 ( a )の B - B 間の模式的断面図、図 7 ( d )は図 7 ( a )の C - C 間の模式的断面図である。

【図8】図8(a)は実施例1に係るフラッシュメモリの製造方法を示す模式的上面図(その3)であり、図8(b)は図8(a)のA-A間の模式的断面図、図8(c)は図8(a)のB-B間の模式的断面図、図8(d)は図8(a)のC-C間の模式的断面図である。

【図9】図9(a)は実施例1に係るフラッシュメモリの製造方法を示す模式的上面図(その4)であり、図9(b)は図9(a)のA-A間の模式的断面図、図9(c)は図9(a)のB-B間の模式的断面図、図9(d)は図9(a)のC-C間の模式的断面図である。

【図 1 0 】図 1 0 は従来例 1 に係るフラッシュメモリのメモリセルサイズ S を説明するための模式的上面図である。

【図 1 1 】図 1 1 は実施例 1 に係るフラッシュメモリのメモリセルサイズ S を説明するための模式的上面図である。

【図12】図12は空洞部28の代わりに絶縁膜29が設けられた場合を説明するための 模式的断面図である。

【図13】図13は実施例2に係るフラッシュメモリの模式的上面図である。

【図14】図14(a)は図13のA-A間の模式的断面図、図14(b)は図13のB-B間の模式的断面図、図14(c)は図13のC-C間の模式的断面図、図14(d)は図13のD-D間の模式的断面図である。

## 【符号の説明】

- [0049]

- 10 半導体基板

- 1 1 酸化膜

- 12 ビットライン

- 13 素子分離領域

- 1 4 トンネル絶縁膜

- 15 ソース・ドレイン領域

- 16 電荷蓄積層

- 18 トップ絶縁膜

- 20 ONO膜

- 22 ワードライン

- 2 4 チャネル領域

- 2 6 孔部

- 2 8 空洞部

- 2 9 絶縁膜

- 30 サイドウォール層

- 32 フォトレジスト

10

20

【図1】

【図2】

【図3】

【図4】

【図5】

(a)

(c)

(d)

# 【図6】

【図7】

(a)

(b)

# 【図8】

# 【図9】

(a)

(d)

(c)

【図10】

【図11】

【図12】

【図13】

【図14】

# フロントページの続き

# (72)発明者 早川 幸夫

福島県会津若松市高久工業団地2番 Spansion Japan株式会社内 Fターム(参考) 5F083 EP18 EP22 ER22 GA11 KA08 PR05 ZA21 5F101 BA45 BB02 BD02 BD10 BE07 BF05 BH13