(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6045249号

(P6045249)

(45) 発行日 平成28年12月14日(2016.12.14)

(24) 登録日 平成28年11月25日(2016.11.25)

(51) Int.Cl.

F 1

H02M 3/38 (2006.01)

H02M 3/38

3/38

A

H02M 3/28 (2006.01)

H02M 3/28

3/28

B

G03G 21/00 (2006.01)

G03G 21/00

21/00 3 9 8

請求項の数 11 (全 16 頁)

(21) 出願番号

特願2012-178352 (P2012-178352)

(22) 出願日

平成24年8月10日(2012.8.10)

(65) 公開番号

特開2014-36555 (P2014-36555A)

(43) 公開日

平成26年2月24日(2014.2.24)

審査請求日

平成27年8月4日(2015.8.4)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100123559

弁理士 梶 俊和

(74) 代理人 100066061

弁理士 丹羽 宏之

(74) 代理人 100177437

弁理士 中村 英子

(72) 発明者 平林 純

東京都大田区下丸子3丁目30番2号 キ

ヤノン株式会社内

審査官 高野 誠治

最終頁に続く

(54) 【発明の名称】電源装置及び画像形成装置

(57) 【特許請求の範囲】

【請求項 1】

一次巻線、二次巻線及び補助巻線を有するトランスと、

前記一次巻線に接続され、前記トランスへの電力の供給をオンオフするスイッチング素子と、

前記二次巻線からの出力電圧に応じた情報を前記トランスの一次側に伝達する第一伝達手段と、

を備え、

前記第一伝達手段からの前記情報に従い、前記二次巻線から所定の電力を供給する際には連続的に前記スイッチング素子がオンオフされ、前記所定の電力よりも低い電力を供給する際には間欠的に前記スイッチング素子がオンオフされる電源装置であって、

前記補助巻線に接続され、前記スイッチング素子のオン時間を決定する決定手段と、

前記補助巻線に接続され、前記決定手段の前記オン時間を切り替えるための情報を伝達する第二伝達手段と、

前記第二伝達手段からの前記情報に従い、前記決定手段によって決定される前記オン時間を切り替える切替手段と、を備え、

前記電源装置の起動時において、前記スイッチング素子がオンすることにより前記一次巻線に電力が供給される第一期間において、前記第一伝達手段からの前記情報によらず、前記スイッチング素子が間欠的にオンオフされ、前記第一期間に続く第二期間において、前記二次巻線からの出力電圧が上昇し、前記第一伝達手段からの前記情報に従い、前記ス

イッティング素子が連続的にオンオフされ、前記二次巻線からの出力電圧が目標値に達した後に、前記第二期間の後の第三期間において、前記スイッティング素子が間欠的にオンオフされるとともに、前記切替手段は前記第二伝達手段からの前記情報に従い、前記オン時間を、前記第二期間におけるオン時間よりも長くなるように変更することを特徴とする電源装置。

【請求項 2】

前記決定手段は、抵抗と、コンデンサと、を有し、

前記抵抗の抵抗値と前記コンデンサの容量とから決定される時定数によって前記オン時間を決定することを特徴とする請求項 1 に記載の電源装置。

【請求項 3】

前記切替手段は、前記抵抗の抵抗値を切り替えることにより、前記時定数を切り替えることを特徴とする請求項 2 に記載の電源装置。

【請求項 4】

前記切替手段は、前記コンデンサの容量を切り替えることにより、前記時定数を切り替えることを特徴とする請求項 2 に記載の電源装置。

【請求項 5】

前記切替手段は、C P U であって、前記 C P U は、前記決定手段に周期的なパルス信号を出力することを特徴とする請求項 1 乃至 4 のいずれか 1 項に記載の電源装置。

【請求項 6】

前記切替手段は、前記二次巻線の出力電圧を分圧する抵抗であることを特徴とする請求項 1 乃至 4 のいずれか 1 項に記載の電源装置。

【請求項 7】

前記切替手段により分圧された電圧を、所定の時間差で前記決定手段に出力する積分回路を備えることを特徴とする請求項 6 に記載の電源装置。

【請求項 8】

前記切替手段は、前記二次巻線の出力電圧にかかわらず、前記オン時間を切り替えることを特徴とする請求項 1 乃至 7 のいずれか 1 項に記載の電源装置。

【請求項 9】

記録材に画像を形成するための画像形成手段を有する画像形成装置であって、

前記画像形成装置に電力を供給する電源を有し、

前記電源は、

一次巻線、二次巻線及び補助巻線を有するトランスと、

前記一次巻線に接続され、前記トランスへの電力の供給をオンオフするスイッティング素子と、前記二次巻線からの出力電圧に応じた情報を前記トランスの一次側に伝達する第一伝達手段と、を備え、前記第一伝達手段からの前記情報に従い、前記二次巻線から所定の電力を供給する際には連続的に前記スイッティング素子がオンオフされ、前記所定の電力よりも低い電力を供給する際には間欠的に前記スイッティング素子がオンオフされる電源装置であって、

前記補助巻線に接続され、前記スイッティング素子のオン時間を決定する決定手段と、

前記補助巻線に接続され、前記決定手段の前記オン時間を切り替えるための情報を伝達する第二伝達手段と、

前記第二伝達手段からの前記情報に従い、前記決定手段によって決定される前記オン時間を切り替える切替手段と、を備え、

前記電源装置の起動時において、前記スイッティング素子がオンすることにより前記一次巻線に電力が供給される第一期間において、前記第一伝達手段からの前記情報によらず、前記スイッティング素子が間欠的にオンオフされ、前記第一期間に続く第二期間において、前記二次巻線からの出力電圧が上昇し、前記第一伝達手段からの前記情報に従い、前記スイッティング素子が連続的にオンオフされ、前記二次巻線からの出力電圧が目標値に達した後に、前記第二期間の後の第三期間において、前記スイッティング素子が間欠的にオンオフされるとともに、前記切替手段は前記第二伝達手段からの前記情報に従い、前記オン時間

10

20

30

40

50

を、前記第二期間におけるオン時間よりも長くなるように変更することを特徴とする画像形成装置。

【請求項 10】

前記画像形成装置は、画像形成手段の動作を制御するコントローラを備え、

前記電源装置は前記コントローラに電力を供給することを特徴とする請求項 9 に記載の画像形成装置。

【請求項 11】

前記画像形成装置は、画像形成手段を駆動するための駆動部を備え、

前記電源装置は前記駆動部に電力を供給することを特徴とする請求項 9 または 10 に記載の画像形成装置。

10

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電源装置及び画像形成装置に関し、特にリンクギングチョークコンバータにおけるソフトスタートと音の問題に関する。

【背景技術】

【0002】

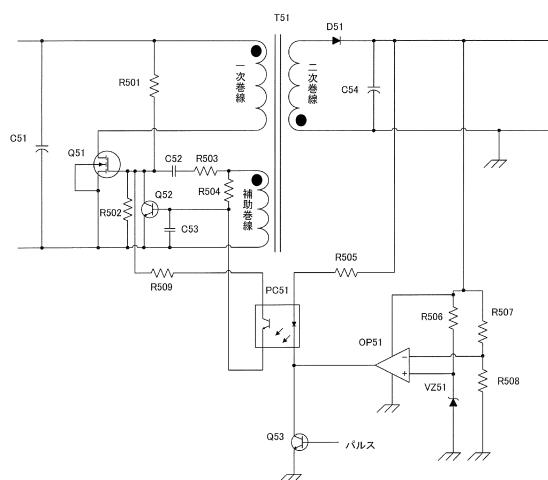

自励型回路であるリンクギングチョークコンバータ（以下、RCCとする）は、全ての部品がディスクリート部品にて構成され、安価であることから 150W 以下の電源として広く使用されている。図 8 に従来の RCC の回路例を示す。図 8 の RCC は、一次平滑コンデンサ C51、コンデンサ C52 ~ 54、トランジスタ Q52、Q53、MOSFET Q51（以下、主スイッチング素子 Q51 とする）、ダイオード D51 を備える。更に、図 8 の RCC は、フライバックトランジスタ T51、フォトカプラ PC51、オペアンプ OP51、ツエナーダイオード VZ51、抵抗 R501 ~ R509 を備える。RCC の省電力技術として、例えば特許文献 1 のように、トランジスタ Q53 にパルス信号を加えることにより、自励連続発振を強制的に止め、間欠発振させることにより軽負荷時の効率を上昇する方法が知られている。

20

【先行技術文献】

【特許文献】

【0003】

30

【特許文献 1】特許第 3697218 号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

従来型の RCC は、電源起動時に主スイッチング素子 Q51 のドレイン・ソース間電圧が最も高くなるという特徴がある。この RCC は主スイッチング素子 Q51 の最大オン時間を抵抗 R504 とコンデンサ C53 の時定数によって決定している。主スイッチング素子 Q51 が一度オンになると補助巻線に発生する電圧によりコンデンサ C53 が充電される。そして、コンデンサ C53 の電圧がトランジスタ Q52 のベース・エミッタ間電圧のしきい値を上回った時点でトランジスタ Q52 がオンになり、主スイッチング素子 Q51 がオフになる。

40

【0005】

通常、RCC の二次側から出力電圧が出ている状態では、オペアンプ OP51 によるフィードバック制御が行われ、抵抗 R509 経由でもコンデンサ C53 に充電電流が流れため、主スイッチング素子 Q51 のオン時間はより短くなる方向に制御される。RCC が連続出力できる最大出力になったとしてもオペアンプ OP51 の出力オフセット電圧によるフォトカプラ PC51 の LED の微発光によりコンデンサ C53 は充電されるため、抵抗 R504 とコンデンサ C53 だけで決まる最大オン時間には達しない。しかし電源起動時は、二次側の出力電圧が上昇していないため、抵抗 R504 とコンデンサ C53 だけで決まる最大オン時間になる。従って主スイッチング素子 Q51 のターンオフ時のドレイン

50

電流のピーク値も最大となり、このため一次巻線のリーケージインダクタンスによる主スイッチング素子Q51のドレイン・ソース間電圧の跳ね上がりも最大となる。

#### 【0006】

このため、このときのドレイン・ソース間電圧が主スイッチング素子Q51の絶対最大定格を満足するように抵抗R504とコンデンサC53の値を設定する。結果として起動後の最大出力は起動時の最大オン時間より短いオン時間で供給できる出力となり、いわば性能を出しきれない状態となる。仮に起動時の最大オン時間を起動後最大負荷時の最大オン時間と同じかそれ以下にできるのであれば、同じMOSFETとトランスで最大出力を引き上げることも可能となり有益である。

#### 【0007】

また、別の課題として、例えば特許文献1にあるような間欠発振動作を行った場合に、トランスから磁歪音が聞こえるという課題もある。間欠発振動作をするということは起動と停止を繰り返すことであり、起動時に上述した最大オン時間で駆動するため、メイントランスの磁束変化が最も大きなものとなる。起動中の発振周波数も低くなり可聴域に入るため、ユーザに不快な音として聞こえてしまう。通常、音に対する対策としてはトランスをエポキシ等で含浸する処置が取られるが、効果には限界があり、かつコストアップにもつながりRCCのメリットである安価という点が失われてしまう。

#### 【0008】

本発明は、このような状況のもとでなされたもので、起動時の主スイッチング素子のドレイン・ソース間電圧を低減させ、且つ、間欠発振動作時に発生する音を低減することを目的とする。

#### 【課題を解決するための手段】

#### 【0009】

前述の課題を解決するために、本発明は以下の構成を備える。

#### 【0010】

(1) 一次巻線、二次巻線及び補助巻線を有するトランスと、前記一次巻線に接続され、前記トランスへの電力の供給をオンオフするスイッチング素子と、前記二次巻線からの出力電圧に応じた情報を前記トランスの一次側に伝達する第一伝達手段と、を備え、前記第一伝達手段からの前記情報に従い、前記二次巻線から所定の電力を供給する際には連続的に前記スイッチング素子がオンオフされ、前記所定の電力よりも低い電力を供給する際には間欠的に前記スイッチング素子がオンオフされる電源装置であって、前記補助巻線に接続され、前記スイッチング素子のオン時間を決定する決定手段と、前記補助巻線に接続され、前記決定手段の前記オン時間を切り替えるための情報を伝達する第二伝達手段と、前記第二伝達手段からの前記情報に従い、前記決定手段によって決定される前記オン時間を切り替える切替手段と、を備え、前記電源装置の起動時において、前記スイッチング素子がオンすることにより前記一次巻線に電力が供給される第一期間において、前記第一伝達手段からの前記情報によらず、前記スイッチング素子が間欠的にオンオフされ、前記第一期間に続く第二期間において、前記二次巻線からの出力電圧が上昇し、前記第一伝達手段からの前記情報に従い、前記スイッチング素子が連続的にオンオフされ、前記二次巻線からの出力電圧が目標値に達した後に、前記第二期間の後の第三期間において、前記スイッチング素子が間欠的にオンオフされるとともに、前記切替手段は前記第二伝達手段からの前記情報に従い、前記オン時間を、前記第二期間におけるオン時間よりも長くなるように変更することを特徴とする電源装置。

(2) 記録材に画像を形成するための画像形成手段を有する画像形成装置であって、前記画像形成装置に電力を供給する電源を有し、前記電源は、一次巻線、二次巻線及び補助巻線を有するトランスと、前記一次巻線に接続され、前記トランスへの電力の供給をオンオフするスイッチング素子と、前記二次巻線からの出力電圧に応じた情報を前記トランスの一次側に伝達する第一伝達手段と、を備え、前記第一伝達手段からの前記情報に従い、前記二次巻線から所定の電力を供給する際には連続的に前記スイッチング素子がオンオフされ、前記所定の電力よりも低い電力を供給する際には間欠的に前記スイッチング素子が

オンオフされる電源装置であって、前記補助巻線に接続され、前記スイッチング素子のオン時間を決定する決定手段と、前記補助巻線に接続され、前記決定手段の前記オン時間を切り替えるための情報を伝達する第二伝達手段と、前記第二伝達手段からの前記情報に従い、前記決定手段によって決定される前記オン時間を切り替える切替手段と、を備え、前記電源装置の起動時において、前記スイッチング素子がオンすることにより前記一次巻線に電力が供給される第一期間において、前記第一伝達手段からの前記情報によらず、前記スイッチング素子が間欠的にオンオフされ、前記第一期間に続く第二期間において、前記二次巻線からの出力電圧が上昇し、前記第一伝達手段からの前記情報に従い、前記スイッチング素子が連続的にオンオフされ、前記二次巻線からの出力電圧が目標値に達した後に、前記第二期間の後の第三期間において、前記スイッチング素子が間欠的にオンオフされるとともに、前記切替手段は前記第二伝達手段からの前記情報に従い、前記オン時間を、前記第二期間におけるオン時間よりも長くなるように変更することを特徴とする画像形成装置。

10

#### 【発明の効果】

#### 【0013】

本発明によれば、起動時の主スイッチング素子のドレイン・ソース間電圧を低減させ、且つ、間欠発振動作時に発生する音を低減することができる。

#### 【図面の簡単な説明】

#### 【0014】

【図1】実施例1の電源装置の回路図

20

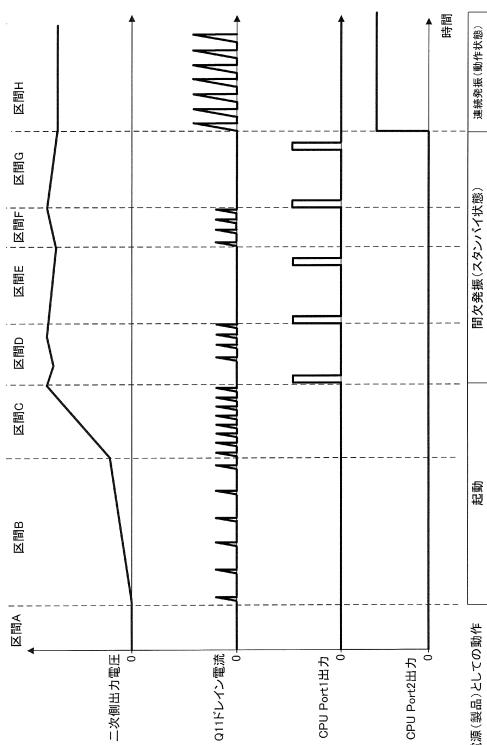

【図2】実施例1の電源装置のタイミングチャート

【図3】実施例2の電源装置の回路図

【図4】実施例3の電源装置の回路図

【図5】実施例4の電源装置のタイミングチャート

【図6】実施例5の電源装置の回路図

【図7】実施例6の画像形成装置を示す図

【図8】従来例の電源装置の回路図

#### 【発明を実施するための形態】

#### 【0015】

以下本発明を実施するための形態を、実施例により詳しく説明する。

30

#### 【実施例1】

#### 【0016】

##### 〔電源装置の構成〕

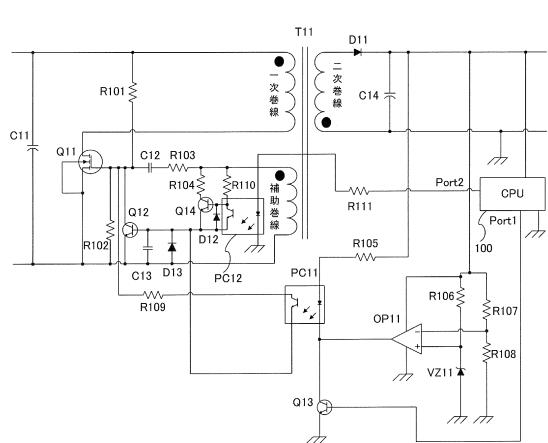

実施例1の電源装置としての自励型回路であるリンクギングチョークコンバータ（以下、RCCとする）の回路図を図1に示す。本実施例のRCCは、コンデンサC11～C14、抵抗R101～111、MOSFETQ11（以下、主スイッチング素子Q11とする）、トランジスタQ12～14、ダイオードD11～D13を備える。更に本実施例のRCCは、フライバックトランス（以下、単にトランスとする）T11、ツエナーダイオードVZ11、フォトカプラPC11～12、オペアンプOP11、中央演算処理装置（以下、CPUとする）100を備える。トランスT11は、一次巻線、二次巻線及び補助巻線を有する。

40

#### 【0017】

ダイオードD11とコンデンサC14は、トランスT11の二次巻線に発生する電圧を整流し平滑する整流平滑回路を構成する。また、抵抗R107、R108、オペアンプOP11、抵抗R106、ツエナーダイオードVZ11は、整流平滑回路の出力電圧を基準電圧と比較し、その差に応じた電圧を出力する誤差検出回路を構成する。抵抗R105、フォトカプラPC11は、誤差検出回路の出力である二次側の情報を一次側に伝達する伝達回路を構成する。更に、フォトカプラPC12、抵抗R104、抵抗R110、コンデンサC13、ダイオードD12、トランジスタQ14は、本実施例の特徴である、主スイッチング素子Q11のオン時間を決定する決定回路を構成する。

50

**【0018】**

本実施例のRCCでは、CPU100は、RCCに間欠発振動作を実行させるための信号を出力端子Port1からトランジスタQ13へ出力する。本実施例の特徴的な構成として、CPU100の出力端子Port2は、フォトカプラPC12のLEDに抵抗R111を介して接続されている。CPU100は、出力端子Port2に所定のレベルの信号を出力することによりフォトカプラPC12を制御できるようになっている。即ち、CPU100は、トランスト11の二次巻線の出力電圧に応じて、トランスト11の補助巻線に接続された決定回路が決定するオン時間切り替える切替手段として機能する。次に図2のタイミングチャートと照らし合わせながら図1のRCCの動作を説明する。

**【0019】**

10

## [電源装置の動作]

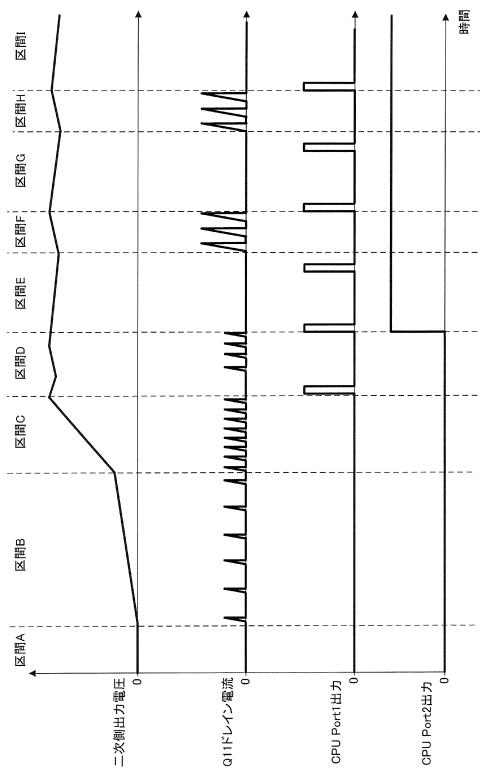

図2は、上から二次側出力電圧、主スイッチング素子Q11のドレイン電流、CPU100の出力端子Port1の出力、出力端子Port2の出力を示している。

**【0020】**

## (区間A)

図2において、区間Aは本電源回路が商用電源に接続されておらず、起動していない状態である。二次側出力電圧はゼロで、その出力電圧を電力源とするCPU100も停止しており、CPU100からの信号は出力されていない。従ってCPU100の出力端子Port2からの出力もローレベルであり、フォトカプラPC12はオフとなっている。

**【0021】**

20

## (区間B)

次に、本実施例の電源回路を商用電源に接続すると区間Bへと移行する。商用電源に接続された初期の段階では、主スイッチング素子Q11のゲート電圧を上昇させるための電流は、起動抵抗R101から供給される。主スイッチング素子Q11がオンになると、トランスト11の一次巻線に電流が流れ、補助巻線に巻線比に応じた電圧が発生する。トランスト11の二次巻線は一次巻線と巻方向が逆であり、ダイオードD11に遮られて電流は流れない。このとき、CPU100も停止しており、CPU100の出力端子Port2の出力はローレベルである。このため、フォトカプラPC12のLEDは、二次側出力電圧がゼロのため発光しておらず、フォトカプラPC12のフォトトランジスタもオフである。従って、補助巻線に発生した電圧による電流は、抵抗R110からトランジスタQ14のベース・エミッタ間を通りコンデンサC13に流れる。これによりトランジスタQ14がオンになり、抵抗R104からもトランジスタQ14のコレクタ・エミッタ間経由でコンデンサC13に電流が流れる。即ち、抵抗R104と抵抗R110は並列に接続される。

**【0022】**

30

時間と共にコンデンサC13の電圧が上昇して、トランジスタQ12のベース・エミッタ間電圧のしきい値電圧を超えると、トランジスタQ12がオンになる。トランジスタQ12がオンになると、主スイッチング素子Q11のゲート・ソース間電圧を引き下げるため、主スイッチング素子Q11はオフになる。区間Bでは、主スイッチング素子Q11のドレイン電流のピーク値は、抵抗R110のみからコンデンサC13が充電される場合に比べて小さい。

**【0023】**

40

主スイッチング素子Q11がオフになると、トランスト11は蓄えたエネルギーを放出するため、二次巻線に先程とは逆極性の電圧を発生させる。そうすると二次側のダイオードD11が導通し、コンデンサC14が充電され始める。トランスト11に蓄えられた全てのエネルギーが放出されると、自由振動により各巻線の電圧が再び反転する。トランスト11の補助巻線にも主スイッチング素子Q11をターンオンする方向の電圧が発生するが、この時点では二次側の出力電圧がほとんど上昇していないため、このとき補助巻線に発生する電圧では主スイッチング素子Q11をターンオンすることができない。結果として、二次側出力電圧がある程度上昇してくるまでは、主スイッチング素子Q11は起動抵

50

抗 R 1 0 1 からの電流供給によるオンしかできない。これが区間 B であり、起動抵抗 R 1 0 1 からの電流供給による主スイッチング素子 Q 1 1 のターンオンには時間がかかるため、主スイッチング素子 Q 1 1 のドレイン電流の波形は、1 波ずつの間隔が長くなっている。

#### 【 0 0 2 4 】

( 区間 C )

区間 C では、二次側出力電圧の上昇に伴い自由振動による補助巻線の電圧が、主スイッチング素子 Q 1 1 をターンオンするのに十分な電圧まで達し、起動抵抗 R 1 0 1 からの電流に頼らず再度オンできる。このように、連続的に主スイッチング素子 Q 1 1 がオンオフされている状態を連続発振状態と呼ぶことにする。このため、起動抵抗 R 1 0 1 のみでオンしていた区間 B に比べて、主スイッチング素子 Q 1 1 のターンオンには時間がかからず、区間 C の主スイッチング素子 Q 1 1 のドレイン電流の波形は、1 波ずつの間隔が区間 B に比べて短くなっている。

#### 【 0 0 2 5 】

また、区間 C では、CPU 1 0 0 の出力端子 Port 2 からの出力はローレベルであり、フォトカプラ P C 1 2 はオフである。このため区間 B 同様、コンデンサ C 1 3 へは抵抗 R 1 1 0 と抵抗 R 1 0 4 を介して電流が流れ、トランジスタ Q 1 2 がオフするまでの時間が短く、主スイッチング素子 Q 1 1 のオン時間が短い。このため、主スイッチング素子 Q 1 1 のドレイン電流のピーク値は、抵抗 R 1 1 0 のみからコンデンサ C 1 3 が充電される場合に比べて小さい。

#### 【 0 0 2 6 】

( 区間 D )

区間 D では、二次側出力電圧が目標値に達し、オペアンプ O P 1 1 がフィードバック制御を行っている。同時に CPU 1 0 0 も起動し、効率改善のため出力端子 Port 1 からパルス信号を出力している。CPU 1 0 0 が出力端子 Port 1 からハイレベルの信号を出力すると、トランジスタ Q 1 3 がオンになり、フォトカプラ P C 1 1 の L E D が発光する。そして、フォトカプラ P C 1 1 のフォトトランジスタがオンとなるため、トランジスタ Q 1 2 がオンになり、主スイッチング素子 Q 1 1 がオフになる。これにより連続発振状態が強制的に断たれ、電源装置は再度、抵抗 R 1 0 1 からの電流供給により起動する状態となる。このように、CPU 1 0 0 は、出力端子 Port 1 からハイレベルの信号を断続的に出力することにより、電源装置に起動と停止を繰り返させ、停止している割合を長くすることで軽負荷時の効率を改善する。このように、間欠的に主スイッチング素子 Q 1 1 がオンオフされている状態を間欠発振状態とする。区間 D 以降、CPU 1 0 0 は出力端子 Port 1 からパルス信号を出力し、RCC は間欠発振動作を行う。また、トランジスタ T 1 1 の二次側出力電圧は目標電圧に到達し、区間 D 以降、RCC は間欠発振動作を行いつつ定電圧制御を行う。

#### 【 0 0 2 7 】

ここで、区間 D では、CPU 1 0 0 は出力端子 Port 2 からローレベルの信号を出力しており、区間 B、区間 C 同様、主スイッチング素子 Q 1 1 のドレイン電流のピーク値は、抵抗 R 1 0 4 のみから充電される場合に比べて小さい。このように、間欠発振状態となつた区間 D において、ドレイン電流のピーク値が小さいことから、区間 D ではトランジスタ T 1 1 から発生する磁歪音を低減することができる。尚、磁歪音を発生させる要因については後述する。

#### 【 0 0 2 8 】

( 区間 E )

区間 E では、CPU 1 0 0 は、区間 A から区間 D までローレベルとしていた出力端子 Port 2 の出力をハイレベルにする。そうすると、フォトカプラ P C 1 2 の L E D が点灯してフォトカプラ P C 1 2 のフォトトランジスタがオンし、トランジスタ Q 1 4 のベース・エミッタ間を短絡する。これによりトランジスタ Q 1 4 はオフとなり、コンデンサ C 1 3 への電流供給経路は抵抗 R 1 1 0 のみとなる。従って、CPU 1 0 0 が出力端子 Port

10

20

30

40

50

$t_2$  からローレベルの信号を出力していたときに比べてコンデンサ C 1 3 の電圧上昇に時間がかかるようになり、結果として主スイッチング素子 Q 1 1 のオン時間が延びることになる。

#### 【 0 0 2 9 】

このように、区間 D までは、主スイッチング素子 Q 1 1 のオン時間は、抵抗 R 1 0 4、1 1 0 及びコンデンサ C 1 3 の時定数により決定されていた。即ち、並列に接続された抵抗 R 1 0 4 と R 1 1 0 の合成抵抗値とコンデンサ C 1 3 の容量によって時定数が決定されていた。これに対して区間 E 以降は、CPU 1 0 0 の出力端子 Port 2 からハイレベルの信号を出力することにより、主スイッチング素子 Q 1 1 のオン時間が、抵抗 R 1 1 0 及びコンデンサ C 1 3 の時定数により決定されるように切り替わる。即ち、本実施例では、時定数を決定している抵抗の抵抗値を切り替えることにより、スイッチング素子 Q 1 1 のオン時間を決定している時定数を切り替えている。10

#### 【 0 0 3 0 】

尚、区間 E では発振は行われていない。これは、二次側出力電圧が目標値に対して十分高い値であるため、オペアンプ O P 1 1 による通常のフィードバック制御によって発振が抑えられているためである。即ち、区間 E では、誤差検出回路及び伝達回路によりトランジスタ Q 1 2 がオンされ、主スイッチング素子 Q 1 1 がオフとなっており、ドレイン電流も 0 となっている。時間が経過し二次側出力電圧が低下してくると、オペアンプ O P 1 1 による発振の抑制が解除され、起動抵抗 R 1 0 1 からの電流によって再度発振を再開する。それが次の区間 F の部分である。20

#### 【 0 0 3 1 】

##### ( 区間 F )

区間 F では、時定数が切り替わったことによる、主スイッチング素子 Q 1 1 のオン時間が延びた効果が表れている。図 2 に示すように、主スイッチング素子 Q 1 1 のオン時間が延びて、ドレイン電流のピーク値が区間 B ~ 区間 D に比べて高くなっている。これにより電源装置は同じ間欠発振状態の区間 D より大きな出力を得ることができるようになる。

#### 【 0 0 3 2 】

また、電源起動の区間である区間 B と区間 C では、主スイッチング素子 Q 1 1 のオン時間が短く制限されているため、発振周波数が高くなる。そのためこの区間での発振周波数を人間の可聴域以上になるように設定すれば起動時や間欠動作時に聞こえる磁歪音を軽減することができる。区間 G 以後の区間の動作は、区間 E と F の動作を繰り返すこととなる。30

#### 【 0 0 3 3 】

##### ( 磁歪音を生じさせる要因 )

ここで、起動時や間欠発振動作時に聞こえる磁歪音について説明する。磁歪音は、トランジスタ T 1 1 の巻線やコアの振動を原因とし、この振動は磁束が作り出している。このため、1 回あたりのスイッチング動作で発生する磁束の最大値を小さく抑えることで振動を抑制することができ、磁歪音を低減することができる。ここで、磁束  $\Phi = L I$  （ $L$  : インダクタンス、 $I$  : 電流値）であるため、電流値  $I$  を小さくすることで振動を抑制し、磁歪音を低減することができる。このため、本実施例では、主スイッチング素子 Q 1 1 のドレイン電流のピーク値を小さくする、即ち、主スイッチング素子 Q 1 1 のオン時間を短くする。そして、電源起動時に主スイッチング素子 Q 1 1 のオン時間を短くするために、本実施例では、CPU 1 0 0 がフォトカプラ P C 1 2 のオンオフを制御し、補助巻線に接続された抵抗とコンデンサを有する回路の時定数を切り替える構成である。この構成により、電源起動時の二次側出力電圧が 0 又は低い場合に、CPU 1 0 0 がフォトカプラ P C 1 2 をオフとする。そして、主スイッチング素子 Q 1 1 のオン時間を、抵抗 R 1 0 4、1 1 0 及びコンデンサ C 1 3 の時定数によって決定することで、主スイッチング素子 Q 1 1 のオン時間を短くしている。40

#### 【 0 0 3 4 】

本実施例では、二次側出力電圧に応じて停止又は起動する CPU 1 0 0 が出力端子 Po 50

r t 2 からフォトカプラ P C 1 2 のオンオフを制御する信号を出力し、フォトカプラ P C 1 2 のオンオフに応じて、コンデンサ C 1 3 に流れる電流の経路を切り替える。尚、コンデンサ C 1 3 に流れる電流の経路を切り替えるということは、時定数を切り替えることでもある。本実施例では、C P U 1 0 0 が主スイッチング素子 Q 1 1 のオン時間を決定している時定数を切り替えることにより、電源起動時の主スイッチング素子 Q 1 1 の最大オン時間を制限している。

#### 【 0 0 3 5 】

以上、本実施例によれば、僅かな部品追加により R C C にソフトスタート機能を付与し、且つ、間欠発振動作時の音の対策とすることができます。これによってM O S F E T である主スイッチング素子 Q 1 1 の耐圧ディレーティングを広げる又はR C C の最大出力を引き上げることが可能となる。また、トランジスタ T 1 1 の含浸や電源の騒音対策を軽減することが可能となり、コストダウンに繋げることができる。このように、電源装置の起動時(区間 B、区間 C)には、C P U 1 0 0 の出力端子 P o r t 2 からローレベルの信号を出力して主スイッチング素子 Q 1 1 のオン時間を短くすることにより、ドレン・ソース間電圧を低減させる。また、間欠発振動作時(区間 D)には、C P U 1 0 0 の出力端子 P o r t 2 からローレベルの信号を出力して主スイッチング素子 Q 1 1 のオン時間を短くすることにより、磁歪音を低減することができる。以上、本実施例によれば、起動時の主スイッチング素子のドレン・ソース間電圧を低減させ、且つ、間欠発振動作時に発生する音を低減することができる。

#### 【実施例 2】

#### 【 0 0 3 6 】

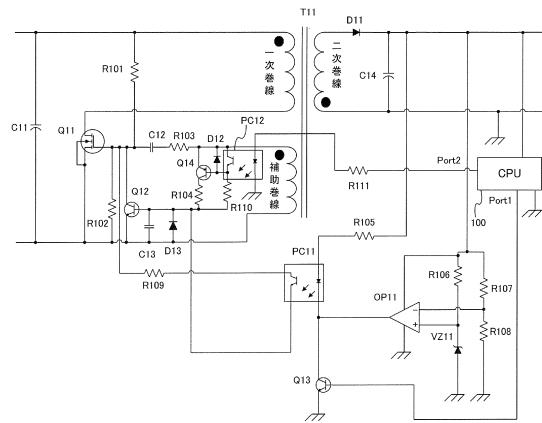

実施例 2 の R C C の構成を図 3 に示す。本実施例では、実施例 1 のトランジスタ Q 1 4 を、P N P トランジスタに変更し、抵抗 R 1 0 4、R 1 1 0、ダイオード D 1 2、フォトカプラ P C 1 2 の接続関係を変更したものである。このため、実施例 1 の図 1 と同じ構成には同じ符号を付し、説明は省略する。また、全体的な動作は実施例 1 と同じであり、説明を省略する。

#### 【 0 0 3 7 】

本実施例では、C P U 1 0 0 の出力端子 P o r t 2 からローレベルの信号を出力しフォトカプラ P C 1 2 の L E D が消灯して、フォトカプラ P C 1 2 のフォトトランジスタがオフしているときに、トランジスタ Q 1 4 がオンする。このとき、トランジスタ Q 1 4 のエミッタ・ベース間経由で抵抗 R 1 1 0 に電流が流れ、抵抗 R 1 0 4 にも電流が流れる。即ち、図 2 で説明した区間 A ~ 区間 D に相当する。

#### 【 0 0 3 8 】

一方、C P U 1 0 0 の出力端子 P o r t 2 からハイレベルの信号を出力し、フォトカプラ P C 1 2 の L E D が点灯しているときは、フォトカプラ P C 1 2 のフォトトランジスタがオンし、トランジスタ Q 1 4 のエミッタ・ベース間が短絡される。このため、トランジスタ Q 1 4 はオフとなる。その結果、コンデンサ C 1 3 を充電する電流供給経路は、抵抗 R 1 1 0 を流れる経路のみとなる。即ち、図 2 で説明した区間 E 以降に相当する。

#### 【 0 0 3 9 】

本実施例では、図 3 のように構成することにより、主スイッチング素子 Q 1 1 のオン時間を決定する時定数を、C P U 1 0 0 の出力端子 P o r t 2 からの出力信号に応じてフォトカプラ P C 1 2 により切り替える。これにより、本実施例によれば、起動時の主スイッチング素子のドレン・ソース間電圧を低減させ、且つ、間欠発振動作時に発生する音を低減することができる。

#### 【実施例 3】

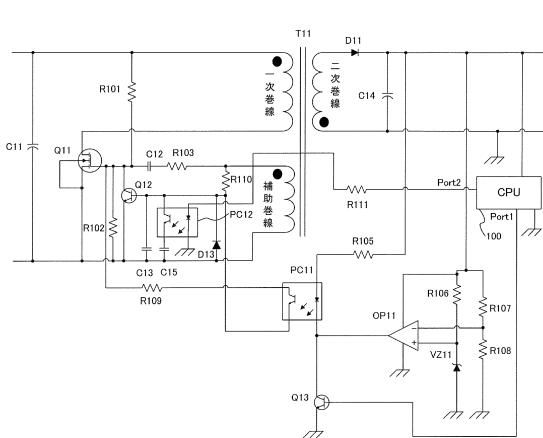

#### 【 0 0 4 0 】

実施例 3 の電源装置の構成を図 4 に示す。本実施例では、実施例 1 に対して主スイッチング素子 Q 1 1 の最大オン時間を変更する方法を、抵抗の切り替えからコンデンサの切り替えに変えたものである。具体的には実施例 1 に対して抵抗 R 1 0 4、トランジスタ Q 1 4、ダイオード D 1 2 を削除し、本実施例では、フォトカプラ P C 1 2 の接続先を変えて

10

20

30

40

50

コンデンサ C 1 5 を追加している。尚、実施例 1 の図 1 と同じ構成には同じ符号を付し、説明は省略する。

#### 【 0 0 4 1 】

C P U 1 0 0 は、出力端子 P o r t 2 からローレベルの信号を出力し、フォトカプラ P C 1 2 の L E D を消灯させ、フォトカプラ P C 1 2 のフォトトランジスタをオフする。フォトカプラ P C 1 2 がオフしているとき、抵抗 R 1 1 0 を流れる電流は全てコンデンサ C 1 3 を充電する。即ち、主スイッチング素子 Q 1 1 のオン時間は、抵抗 R 1 1 0 及びコンデンサ C 1 3 の時定数によって決定される。尚、この状態は、図 2 で説明した区間 D までに相当する。

#### 【 0 0 4 2 】

一方、C P U 1 0 0 は、出力端子 P o r t 2 からハイレベルの信号を出力し、フォトカプラ P C 1 2 の L E D を点灯させ、フォトカプラ P C 1 2 のフォトダイードをオンする。フォトカプラ P C 1 2 がオンしているとき、抵抗 R 1 1 0 を流れる電流はコンデンサ C 1 3 とコンデンサ C 1 5 の両方を充電する。即ち、フォトカプラ P C 1 2 の L E D を点灯すると、主スイッチング素子 Q 1 1 のオン時間が、抵抗 R 1 1 0 及びコンデンサ C 1 3 、 C 1 5 の時定数によって決定されるように切り替わる。このように、本実施例では、時定数を決定しているコンデンサの容量を切り替えることにより、スイッチング素子 Q 1 1 のオン時間を決定している時定数を切り替えている。そして、トランジスタ Q 1 2 のベース・エミッタ間電圧が上昇するのに時間がかかるようになるため、主スイッチング素子 Q 1 1 のオン時間を長くすることができ、実施例 1 と同等の効果を得られる。尚、この状態は、図 2 で説明した区間 E 以降に相当する。

#### 【 0 0 4 3 】

以上、本実施例によれば、起動時の主スイッチング素子のドレイン・ソース間電圧を低減させ、且つ、間欠発振動作時に発生する音を低減することができる。

#### 【 実施例 4 】

#### 【 0 0 4 4 】

実施例 4 の電源装置のタイミングチャートを図 5 に示す。尚、本実施例の電源装置の回路図は実施例 1 の図 1 と同様とし、説明は省略する。実施例 1 では、起動時の主スイッチング素子 Q 1 1 のドレイン・ソース間電圧の跳ね上がりを抑え、且つ間欠発振状態（図 2 の区間 F 等）では比較的大きな出力を取り出せることを特徴としていた。これに対し、本実施例では、間欠発振状態で取り出せる出力を抑える代わりに間欠発振状態での磁歪音を低減させる方法を示す。

#### 【 0 0 4 5 】

図 5 において、区間 A ~ D までは実施例 1 と同様であり、説明を省略する。区間 E ~ G に関し、実施例 1 では C P U 1 0 0 の出力端子 P o r t 2 の出力信号がハイレベルになっていた。本実施例では、C P U 1 0 0 の出力端子 P o r t 2 の出力信号を区間 D までと同様にローレベルのままとする。そのようにすることで間欠発振状態である区間 D ~ G の全ての区間ににおいて、主スイッチング素子 Q 1 1 のオン時間を短いまとまることができる。これにより、ドレイン電流の変化幅が小さく、従って磁束の変化量も少ないため磁歪音が低減される。

#### 【 0 0 4 6 】

また、二次側から大きな出力を取り出す必要が発生した場合には、例えば区間 H に示すように、C P U 1 0 0 の出力端子 P o r t 2 の出力信号をハイレベルとする。これにより、主スイッチング素子 Q 1 1 のオン時間を長くし、且つ C P U 1 0 0 の出力端子 P o r t 1 の出力信号をローレベルとすることでトランジスタ Q 1 3 へのパルス信号の入力を停止して連続発振動作を行わせ、電源装置としての最大出力を得ることができる。このように、C P U 1 0 0 は、磁歪音の低減を優先する場合には出力端子 P o r t 2 の出力信号をローレベルとし、大きな出力を得ることを優先する場合には出力端子 P o r t 2 の出力信号をハイレベルとすればよい。

#### 【 0 0 4 7 】

10

20

30

40

50

このように、本実施例では、CPU100が、フォトカプラPC12のLEDの点灯を任意に制御する構成とする。これにより、例えば本実施例の電源装置を製品に搭載する際には、製品において重い負荷のないスタンバイ状態において区間D～Gの制御方法を適用し、大きな出力が必要となる製品動作状態において区間Hの制御方法を適用することができる。そして、本実施例の電源装置を搭載した製品においては、スタンバイ状態では高い効率と低い磁歪音を両立させ、動作状態では大きな出力を取り出すことが可能となる。尚、図5に、電源（製品）としての動作を示す。例えば、RCRは、区間B、区間Cでは起動状態であり、区間D～区間Gでは間欠発振動作（スタンバイ状態でもある）であり、区間Hでは連続発振状態（動作状態）である。尚、実施例2のようにトランジスタQ14をPNPトランジスタとした構成や、実施例3のようにコンデンサの容量を切り替えることで時定数を切り替える構成に対して、本実施例の構成を適用してもよい。

#### 【0048】

以上、本実施例によれば、起動時の主スイッチング素子のドレイン・ソース間電圧を低減させ、且つ、間欠発振動作時に発生する音を低減することができる。

#### 【実施例5】

#### 【0049】

実施例5の電源装置の回路図を図6に示す。本実施例の電源装置では、実施例1の図1からCPU100を削除し、代わりに二次側の出力電圧を抵抗R112と抵抗R113で分圧し、抵抗R114とコンデンサC16から成る積分回路を介してフォトカプラPC12のLEDに直接接続する構成である。即ち、抵抗R112及び抵抗R113は、トランジストT11の二次巻線の出力電圧に応じて、トランジストT11の補助巻線に接続された決定回路が決定するオン時間を切り替える切替手段として機能する。尚、実施例1の図1と同じ構成には同じ符号を付し、説明を省略する。

#### 【0050】

これらの定数の設定については、次のようにする。まず、抵抗R112と抵抗R113については次のように設定する。抵抗R112と抵抗R113はフォトカプラPC12のLEDが点灯するタイミングを決める回路である。このため、二次側出力電圧が所望の電圧になったときに、抵抗R113に発生する電圧がフォトカプラPC12のLEDの順方向電圧以上となるように分圧比を設定する。

#### 【0051】

また、抵抗R114とコンデンサC16から成る積分回路は、電源装置の起動が完了する前にフォトカプラPC12のLEDが点灯してしまわないように時間差をつけるためのものである。これによりCPU100がない構成においても、電源起動時のソフトスタートが可能になる。

#### 【0052】

具体的には、起動する前は二次側出力電圧がゼロであるため、フォトカプラPC12は消灯したままであり、実施例1に示すように主スイッチング素子Q11のオン時間は短いままだとなる。従ってドレイン・ソース間電圧は抑えられた状態で電源が起動する。一方、二次側出力電圧が十分に上昇して起動が完了したときに、抵抗R112と抵抗R113によって分圧された電圧によって、フォトカプラPC12のLEDが点灯する。この場合、抵抗R114とコンデンサC16から成る積分回路によって、所定の時間差でフォトカプラPC12のLEDが点灯する。フォトカプラPC12のLEDの点灯により、主スイッチング素子Q11のオン時間の抑制が解除され、大きな出力を得ることが可能となる。

#### 【0053】

尚、実施例2のようにトランジスタQ14をPNPトランジスタとした構成や、実施例3のようにコンデンサの容量を切り替えることで時定数を切り替える構成に対して、本実施例の構成を適用してもよい。

#### 【0054】

以上、本実施例によれば、起動時の主スイッチング素子のドレイン・ソース間電圧を低減させ、且つ、間欠発振動作時に発生する音を低減することができる。

10

20

30

40

50

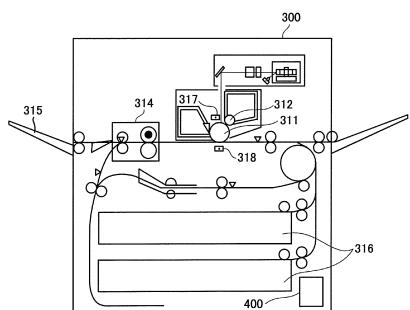

**【実施例 6】****【0055】**

実施例 1 ~ 5 で説明した電源装置である R C C は、例えば画像形成装置の低圧電源、即ちコントローラ（制御部）やモータ等の駆動部へ電力を供給する電源として適用可能である。以下に、実施例 1 ~ 5 の電源装置が適用される画像形成装置の構成を説明する。

**【0056】****[ 画像形成装置の構成 ]**

画像形成装置の一例として、レーザビームプリンタを例にあげて説明する。図 7 に電子写真方式のプリンタの一例であるレーザビームプリンタの概略構成を示す。レーザビームプリンタ 300 は、静電潜像が形成される像担持体としての感光ドラム 311、感光ドラム 311 を一様に帯電する帯電部 317（帯電手段）、感光ドラム 311 に形成された静電潜像をトナーで現像する現像部 312（現像手段）を備えている。そして、感光ドラム 311 に現像されたトナー像をカセット 316 から供給された記録材としてのシート（不図示）に転写部 318（転写手段）によって転写して、シートに転写したトナー像を定着器 314 で定着してトレイ 315 に排出する。この感光ドラム 311、帯電部 317、現像部 312、転写部 318 が画像形成部である。また、レーザビームプリンタ 300 は、実施例 1 ~ 5 で説明した電源装置である R C C 400 を備えている。尚、実施例 1 ~ 5 の R C C 400 を適用可能な画像形成装置は、図 7 に例示したものに限定されず、例えば複数の画像形成部を備える画像形成装置であってもよい。更に、感光ドラム 311 上のトナー像を中間転写ベルトに転写する一次転写部と、中間転写ベルト上のトナー像をシートに転写する二次転写部を備える画像形成装置であってもよい。

10

**【0057】**

レーザビームプリンタ 300 は、画像形成部による画像形成動作や、シートの搬送動作を制御する不図示のコントローラを備えており、実施例 1 ~ 5 に記載の R C C 400 は、例えばコントローラに電力を供給する。また、実施例 1 ~ 5 に記載の R C C 400 は、感光ドラム 311 を回転するため又はシートを搬送する各種ローラ等を駆動するためのモータ等の駆動部に電力を供給する。

20

**【0058】**

本実施例の画像形成装置は、実施例 1 ~ 5 で説明したソフトスタート機能を備える R C C 400 を備えている。このため、本実施例の画像形成装置は、商用電源からの電力供給を開始した電源起動時に、R C C 400 の主スイッチング素子 Q 11 のドレン・ソース間電圧を低減することができる。また、本実施例の画像形成装置は、省電力を実現する待機状態（例えば、省電力モードや待機モード）にある場合に、例えばコントローラのみに電力を供給する等、負荷を軽くして消費電力を低減させることができる。即ち、本実施例の画像形成装置では、省電力モード時に、実施例 1 ~ 5 で説明した R C C 400 が軽負荷時の間欠発振動作を行う。そして、画像形成装置が省電力モードで稼働している際には、実施例 1 ~ 5 で説明した構成によって、R C C 400 から発生する磁歪音を低減することができる。

30

**【0059】**

以上本実施例によれば、画像形成装置の電源装置において、起動時の主スイッチング素子のドレン・ソース間電圧を低減させ、且つ、間欠発振動作時に発生する音を低減することができる。

40

**【符号の説明】****【0060】**

|             |             |

|-------------|-------------|

| 100         | C P U       |

| C 13        | コンデンサ       |

| P C 12      | フォトカプラ      |

| Q 11        | M O S F E T |

| Q 12        | トランジスタ      |

| R 104、R 110 | 抵抗          |

50

T 1 1

トランス

【図 1】

【図 2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き

(56)参考文献 特開2000-350449(JP,A)

特開2012-010438(JP,A)

特開2005-024198(JP,A)

特開平11-235036(JP,A)

(58)調査した分野(Int.Cl., DB名)

H 02 M        3 / 00    -    3 / 44

G 03 G        21 / 00