(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2015-57215

(P2015-57215A)

(43) 公開日 平成27年3月26日(2015.3.26)

(51) Int.Cl.

A63F 7/02 (2006.01)

F 1

A 6 3 F 7/02 3 2 6 Z

A 6 3 F 7/02 3 3 4

テーマコード(参考)

2 C 0 8 8

審査請求 有 請求項の数 1 O L (全 110 頁)

(21) 出願番号 特願2014-260559 (P2014-260559)

(22) 出願日 平成26年12月24日 (2014.12.24)

(62) 分割の表示 特願2013-57756 (P2013-57756)

の分割

原出願日 平成20年5月23日 (2008.5.23)

(71) 出願人 000144153

株式会社三共

東京都渋谷区渋谷三丁目29番14号

(74) 代理人 100103090

弁理士 岩壁 冬樹

(74) 代理人 100124501

弁理士 塩川 誠人

(74) 代理人 100135161

弁理士 真野 修二

(72) 発明者 小倉 敏男

東京都渋谷区渋谷三丁目29番14号 株

式会社三共内

F ターム(参考) 2C088 AA36 AA42 BC22 BC47 BC58

EA10 EB55

(54) 【発明の名称】遊技機

## (57) 【要約】

【課題】外部接続基板などを用いて、強制的にバックアップRAMを初期化させて不正に大当たりを発生させる行為を防止することができるようとする。

【解決手段】大当たり判定用乱数(MR1)を生成するためのカウンタ(乱数回路5003が備えるカウンタ回路511。ソフトウェアカウンタである大当たり判定算出用カウンタ。)の値を更新する。また、遊技制御用マイクロコンピュータ560は、更新したカウンタの値を用いて生成された大当たり判定用乱数(MR1)にもとづいて、大当たり遊技状態に移行させるか否かを判定する。また、遊技機は、遊技制御を開始させるための指示操作に応じて遊技開始指示信号を出力する遊技開始スイッチ90を備える。そして、初期化処理によってRAM55の記憶内容が初期化された後に、遊技開始スイッチ90から遊技開始指示信号が出力されたことを条件に、カウンタの値の更新を開始する。

【選択図】図37

**【特許請求の範囲】****【請求項 1】**

各々を識別可能な複数種類の第1識別情報の可変表示を行う第1可変表示手段、または各々を識別可能な複数種類の第2識別情報の可変表示を行う第2可変表示手段に特定表示結果が導出表示されたときに遊技者にとって有利な特定遊技状態に移行可能な遊技機であって、

バックアップ電源により遊技機に対する電力供給が停止してもデータが保持されるデータ記憶手段と、

前記データ記憶手段の記憶内容を初期化するための指示操作に応じて初期化指示信号を出力する初期化操作手段と、

前記初期化操作手段から前記初期化指示信号が出力されたことにもとづいて、前記データ記憶手段の記憶内容を初期化する初期化処理手段と、

前記特定遊技状態に移行させるか否かを判定するために用いる判定用乱数を生成するためのカウンタの値を更新するカウンタ更新手段と、

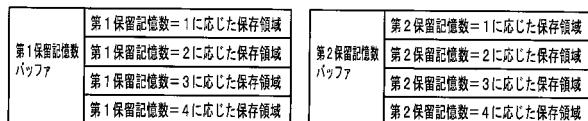

未だ開始されていない第1識別情報の可変表示について、保留記憶として記憶する第1保留記憶手段と、

未だ開始されていない第2識別情報の可変表示について、保留記憶として記憶する第2保留記憶手段と、

第1識別情報の可変表示または第2識別情報の可変表示を開始するときに、前記第1保留記憶手段または前記第2保留記憶手段に記憶された保留記憶に対応したデータを共通記憶領域に記憶させる記憶制御手段と、

前記カウンタ更新手段が更新したカウンタの値を用いて生成された前記判定用乱数にもとづいて、前記特定遊技状態に移行させるか否かを判定する遊技状態判定手段とを備え、

前記初期化操作手段は、遊技制御を開始させるための指示操作に応じて遊技開始指示信号を出力する遊技開始操作手段として兼用で用いられる

ことを特徴とする遊技機。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、各々を識別可能な複数種類の第1識別情報の可変表示を行う第1可変表示手段、または各々を識別可能な複数種類の第2識別情報の可変表示を行う第2可変表示手段に特定表示結果が導出表示されたときに遊技者にとって有利な特定遊技状態に移行可能な遊技機に関する。

**【背景技術】****【0002】**

遊技機として、遊技球などの遊技媒体を発射装置によって遊技領域に発射し、遊技領域に設けられている入賞口などの入賞領域に遊技媒体が入賞すると、所定個の賞球が遊技者に払い出されるものがある。さらに、表示状態が変化可能な可変表示部が設けられ、可変表示部の表示結果があらかじめ定められた特定表示態様となつた場合に所定の遊技価値を遊技者に与えるように構成されたものがある。

**【0003】**

なお、遊技価値とは、遊技機の遊技領域に設けられた可変入賞球装置の状態が打球が入賞しやすい遊技者にとって有利な状態になることや、遊技者にとって有利な状態になるための権利を発生させたりすることや、賞球払出の条件が成立しやすくなる状態になることがある。

**【0004】**

遊技機では、所定の移行条件が成立したときに、遊技状態を遊技者にとって有利な特定遊技状態に移行させる。例えば、パチンコ遊技機では、特別図柄を表示する可変表示部の表示結果があらかじめ定められた特定表示態様の組合せ（大当たり図柄）になることを、通常、「大当たり」という。大当たりが発生すると、例えば、大入賞口が所定回数開放して打球

10

20

30

40

50

が入賞しやすい大当たり遊技状態に移行する。

【0005】

そのような遊技機では、バックアップRAMをクリアするためのクリアスイッチが設けられ、遊技機への電源供給を開始したときにクリアスイッチがオンしていることにもとづいて、電源断前の遊技状態への復旧処理を行うことなく、バックアップRAMの記憶データをクリア（初期化）するように構成されたものがある（例えば、特許文献1参照）。

【0006】

また、そのような遊技機では、遊技開始スイッチが設けられ、遊技機への電源供給を開始した後に遊技開始スイッチが操作されなければ、遊技を開始できないように構成されたものがある。例えば、特許文献2には、遊技機への電源供給が開始された後に、遊技機の上皿に設けられた同意ボタンがオンとなったことにもとづいて、遊技を開始可能に構成することが記載されている。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2001-286649号公報（段落0098-0099、図16）

【特許文献2】特開2003-38833号公報（段落0043、段落0062、図2、図5）

【発明の概要】

【発明が解決しようとする課題】

【0008】

特許文献1に記載された遊技機では、遊技機への電源供給の開始時にクリアスイッチがオンしていることにもとづいてバックアップRAMの初期化が行われる場合には、大当たり判定などに用いる乱数の値も初期化されてしまい、不正用の外部接続基板を遊技機に接続して、大当たりが発生するタイミングで不正に信号を入力することにより不正に大当たりの発生を狙われてしまう可能性がある。

【0009】

また、特許文献2には、遊技開始スイッチがオンとなったことを条件として遊技を開始可能とすることが記載されているが、遊技機を強制的に電源断状態とさせて不正に大当たりの発生を狙われてしまう事態を防止することはできない。

【0010】

そこで、本発明は、外部接続基板などを用いて、強制的にバックアップRAMを初期化させて不正に特定遊技状態に移行させる行為を防止することができる遊技機を提供することを目的とする。

【課題を解決するための手段】

【0011】

本発明による遊技機は、各々を識別可能な複数種類の第1識別情報の可変表示を行う第1可変表示手段、または各々を識別可能な複数種類の第2識別情報の可変表示を行う第2可変表示手段に特定表示結果が導出表示されたときに遊技者にとって有利な特定遊技状態（例えば、大当たり遊技状態）に移行可能な遊技機であって、バックアップ電源により遊技機に対する電力供給が停止してもデータが保持されるデータ記憶手段（例えば、RAM55）と、データ記憶手段の記憶内容を初期化するための指示操作に応じて初期化指示信号（例えば、クリアスイッチ921の検出信号）を出力する初期化操作手段（例えば、クリアスイッチ921）と、初期化操作手段から初期化指示信号が出力されたことにもとづいて、データ記憶手段の記憶内容を初期化する初期化処理手段（例えば、遊技制御用マイクロコンピュータ560におけるステップS10～S13を実行する部分）と、特定遊技状態に移行させるか否かを判定するために用いる判定用乱数（例えば、大当たり判定用乱数MR1）を生成するためのカウンタ（例えば、乱数回路5003のカウンタ521。大当たり判定算出用乱数（ランダム2-1）をカウントアップするための大当たり判定算出用カウンタ。）の値を更新するカウンタ更新手段（例えば、乱数回路5003のクロック信号出力

10

20

30

40

50

回路 S1 が乱数発生用クロック信号 S1 を出力したことにもとづいて、乱数回路 S0 がカウンタ S2 がカウント値を更新する部分。遊技制御用マイクロコンピュータ S6 におけるステップ S2 4 を実行して大当たり判定算出用カウンタのカウント値を更新する処理を実行する部分。) と、未だ開始されていない第 1 識別情報の可変表示について、保留記憶として記憶する第 1 保留記憶手段と、未だ開始されていない第 2 識別情報の可変表示について、保留記憶として記憶する第 2 保留記憶手段と、第 1 識別情報の可変表示または第 2 識別情報の可変表示を開始するときに、第 1 保留記憶手段または第 2 保留記憶手段に記憶された保留記憶に対応したデータを共通記憶領域に記憶させる記憶制御手段と、カウンタ更新手段が更新したカウンタの値を用いて生成された判定用乱数にもとづいて、特定遊技状態に移行させるか否かを判定する遊技状態判定手段(例えば、遊技制御用マイクロコンピュータ S6 におけるステップ S6 2 , S6 3 を実行する部分)とを備え、初期化操作手段は、遊技制御を開始させるための指示操作に応じて遊技開始指示信号を出力する遊技開始操作手段として兼用で用いられることを特徴とする。

10

#### 【発明の効果】

#### 【0012】

請求項 1 に記載された遊技機では、特定遊技状態に移行させるか否かを判定するために用いる判定用乱数を生成するためのカウンタの値を更新するカウンタ更新手段と、カウンタ更新手段が更新したカウンタの値を用いて生成された判定用乱数にもとづいて、特定遊技状態に移行させるか否かを判定する遊技状態判定手段とを備え、初期化操作手段が、遊技制御を開始させるための指示操作に応じて遊技開始指示信号を出力する遊技開始操作手段として兼用で用いられるように構成されているので、外部接続基板などを用いて強制的にバックアップ RAM を初期化させることにより、初期化させてから特定遊技状態(大当たり遊技状態)に移行させると判定されるタイミングで、外部接続基板(ぶら下げ基板)から信号を入力することによって特定遊技状態に移行させることを狙われてしまうことを防止することができる。

20

#### 【図面の簡単な説明】

#### 【0013】

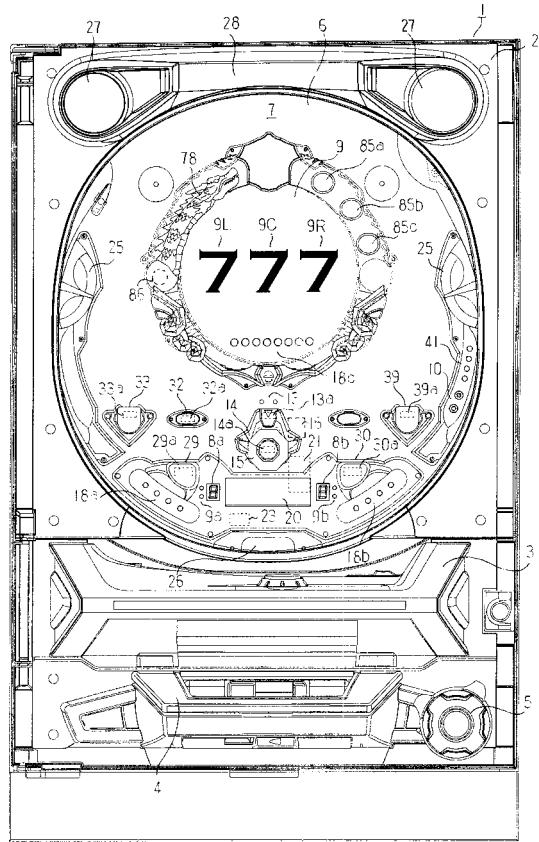

【図 1】パチンコ遊技機を正面からみた正面図である。

【図 2】パチンコ遊技機を示す背面図である。

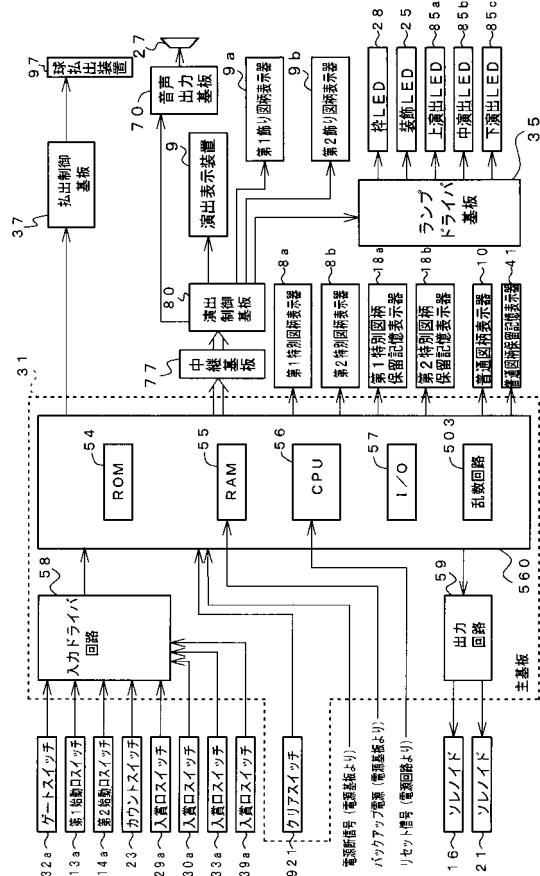

【図 3】遊技制御基板(主基板)の回路構成例を示すブロック図である。

30

【図 4】演出制御基板、ランプドライバ基板および音声出力基板の回路構成例を示すブロック図である。

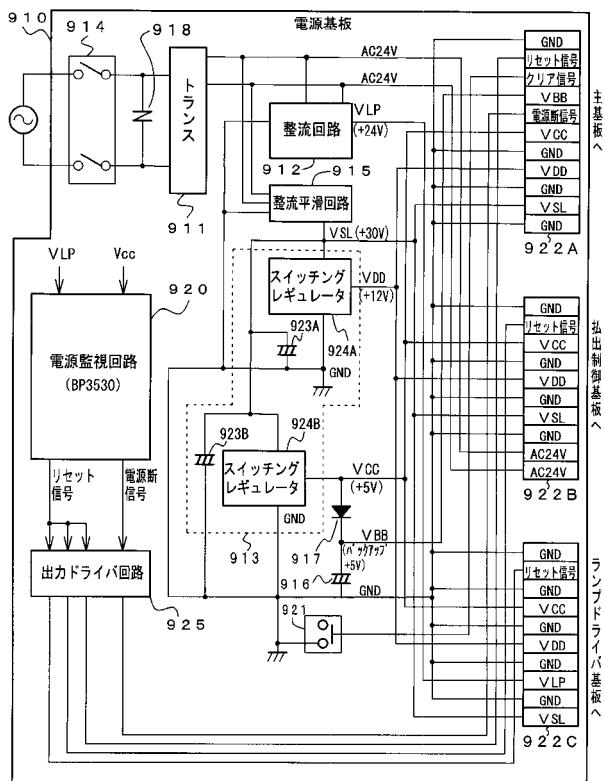

【図 5】電源基板の構成例を示すブロック図である。

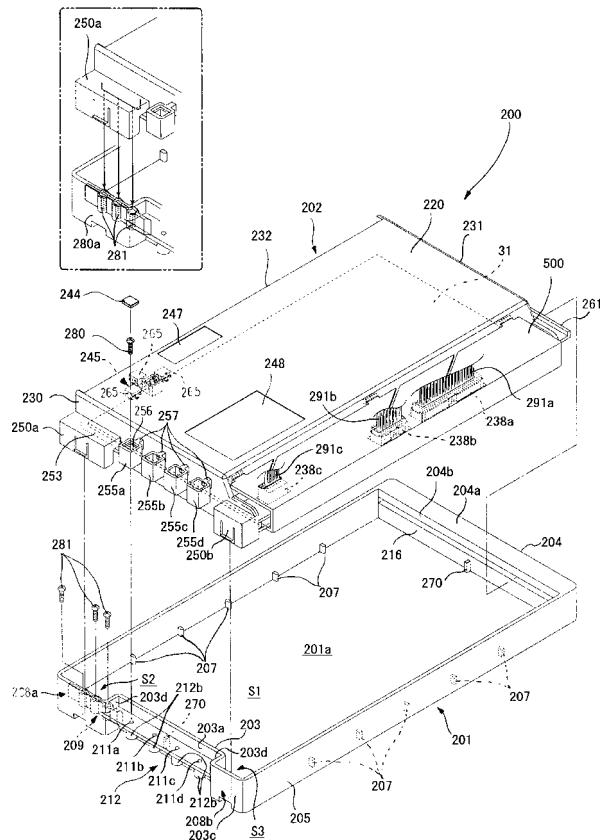

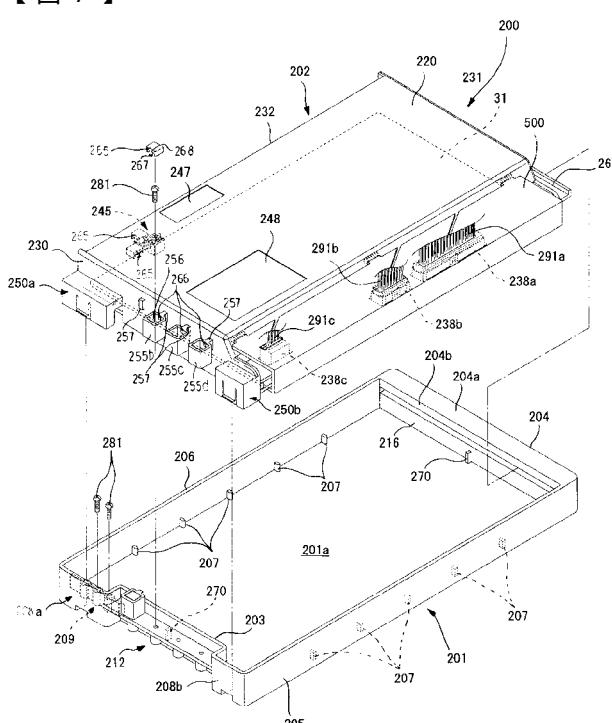

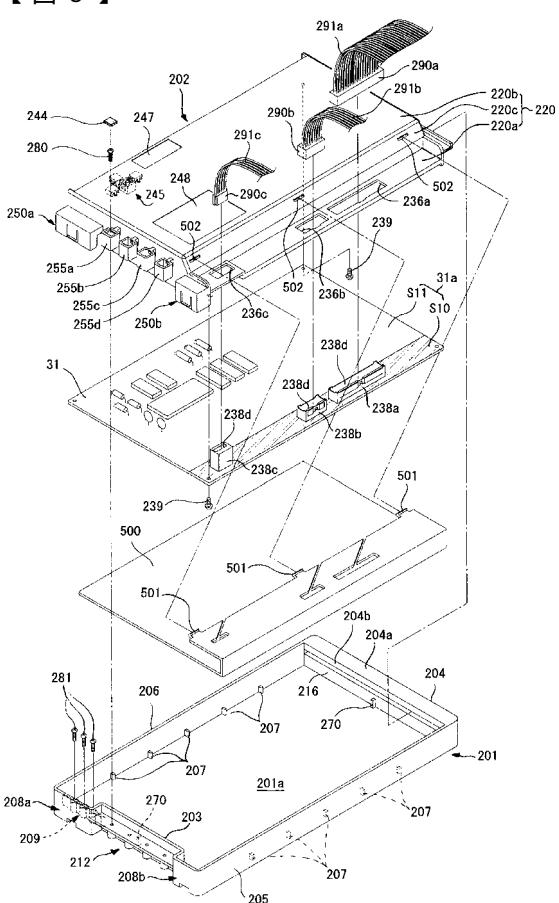

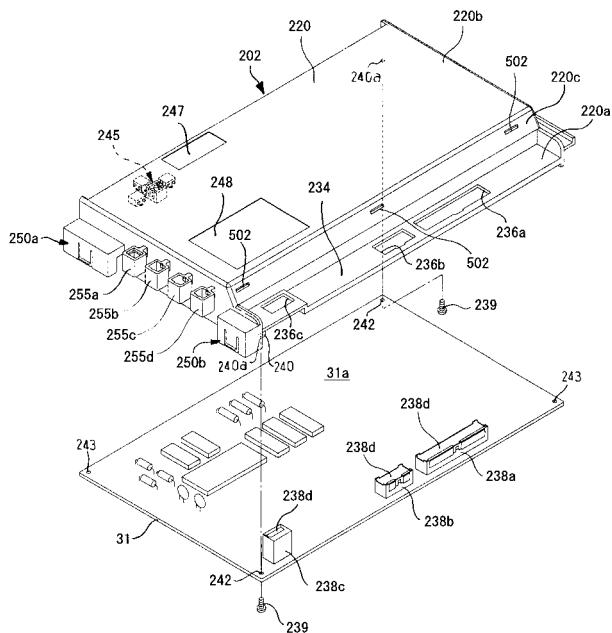

【図 6】基板収納ケースを示す分解斜視図である。

【図 7】基板収納ケースを示す分解斜視図である。

【図 8】基板収納ケースおよび主基板の組み付け状態を示す分解斜視図である。

【図 9】ケースカバーに対する主基板の取り付け状態を示す斜視図である。

【図 10】配線側コネクタの接続状況を示す斜視図である。

【図 11】コネクタ規制部材の取り付け状況を示す斜視図である。

40

【図 12】ケース本体とケースカバーとを閉鎖した状態を示す縦断面図である。

【図 13】基板収納ケースの封止状態を示す斜視図である。

【図 14】図 13 に示す基板収納ケースの A - A 断面を示す断面図である。

【図 15】基板収納ケースを示す一部破断側面図である。

【図 16】図 15 に示す基板収納ケースの B - B 断面および C - C 断面を示す断面図である。

【図 17】主基板における回路構成および主基板から演出制御基板に送信される演出制御コマンドの信号線を示すブロック図である。

【図 18】乱数回路の構成例を示すブロック図である。

【図 19】更新規則選択レジスタの例を示す説明図である。

【図 20】更新規則メモリの例を示す説明図である。

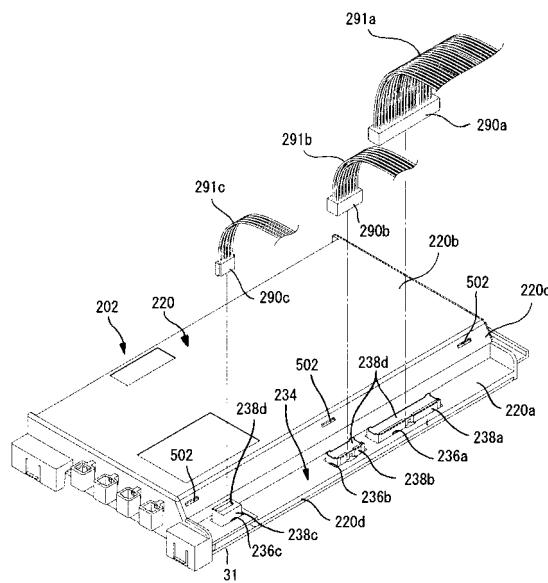

50

【図 2 1】カウント値順列変更回路が、カウンタが出力するカウント値の順列を変更する場合の例を示す説明図である。

【図 2 2】カウント値順列変更レジスタの例を示す説明図である。

【図 2 3】乱数最大値設定レジスタの例を示す説明図である。

【図 2 4】周期設定レジスタの例を示す説明図である。

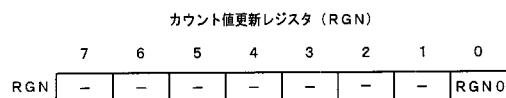

【図 2 5】カウント値更新レジスタの例を示す説明図である。

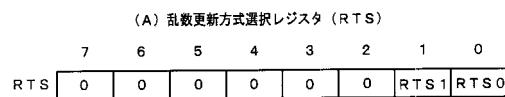

【図 2 6】乱数更新方式選択レジスタおよび乱数更新方式選択データの例を示す説明図である。

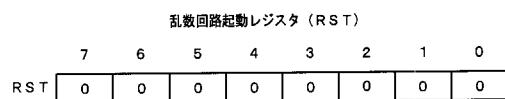

【図 2 7】乱数回路起動レジスタの例を示す説明図である。

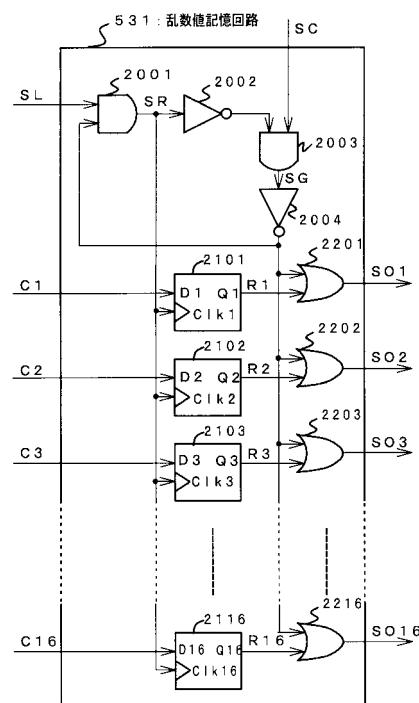

【図 2 8】乱数値記憶回路の一構成例を示す回路図である。

【図 2 9】乱数値記憶回路に各信号が入力されるタイミング、および乱数値記憶回路が各信号を出力するタイミングを示すタイミングチャートである。

【図 3 0】遊技制御用マイクロコンピュータにおける記憶領域のアドレスマップの一例を示す説明図である。

【図 3 1】ユーザプログラム管理エリアにおけるアドレスマップの一例を示す説明図である。

【図 3 2】初期値変更方式設定データの一例を示す説明図である。

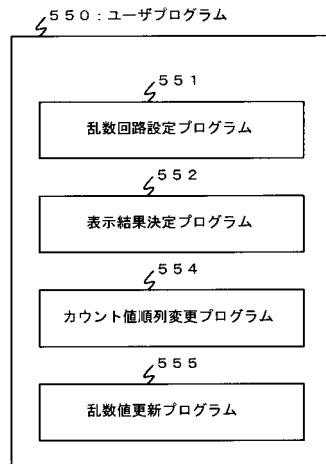

【図 3 3】ユーザプログラムの構成例を示す説明図である。

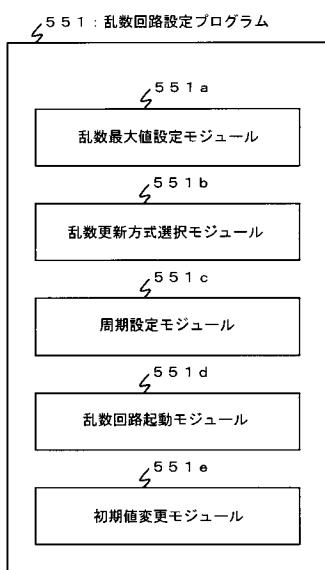

【図 3 4】乱数回路設定プログラムの構成例を示す説明図である。

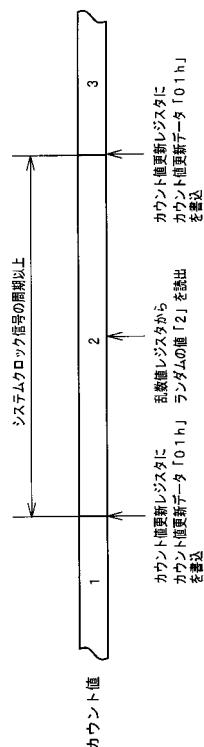

【図 3 5】第 1 の乱数更新方式が選択されている場合に、CPU がランダム R の値を更新させたりランダム R の値を読出したりする動作を示す説明図である。

【図 3 6】第 2 の乱数更新方式が選択されている場合に、CPU がランダム R の値を読出したりする動作を示す説明図である。

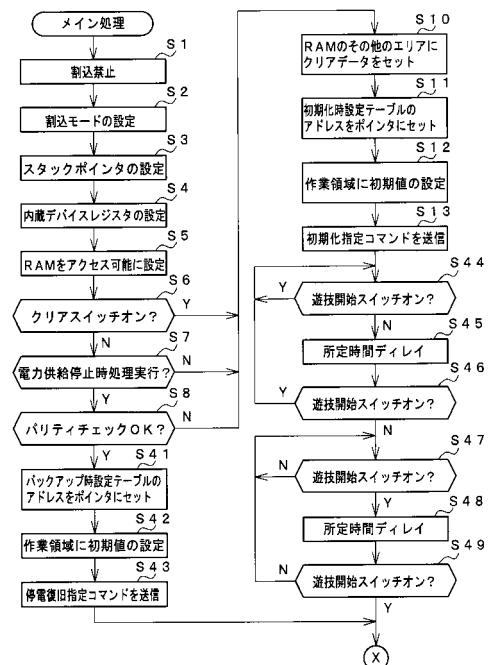

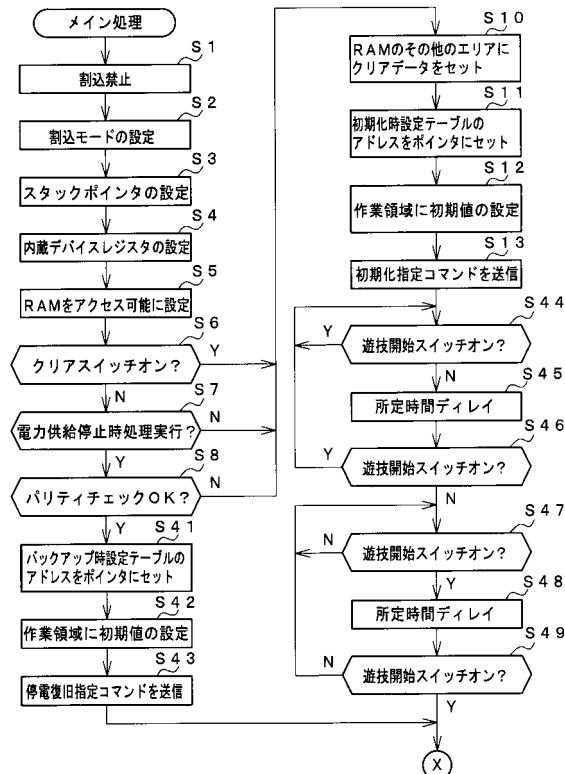

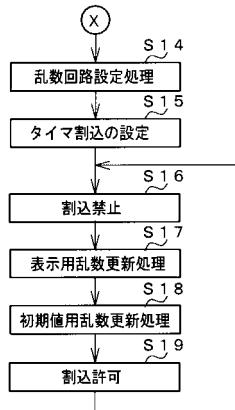

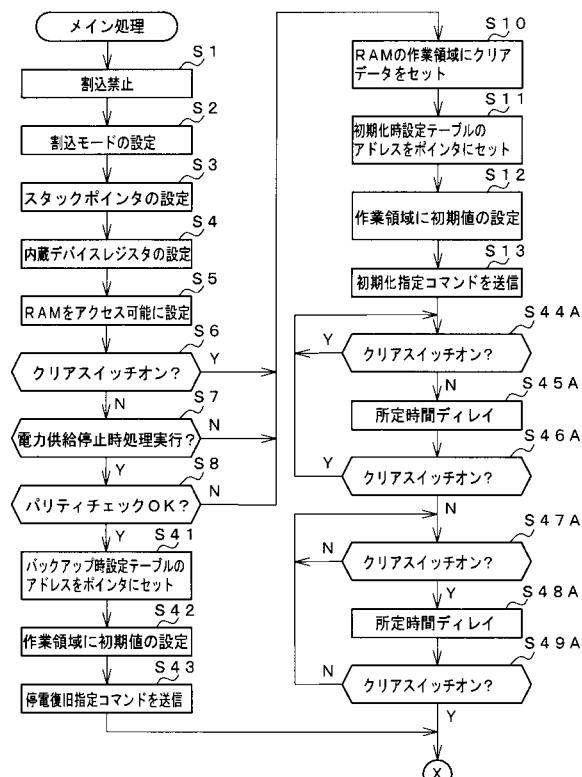

【図 3 7】遊技制御用マイクロコンピュータにおける CPU が実行するメイン処理を示すフローチャートである。

【図 3 8】遊技制御用マイクロコンピュータにおける CPU が実行するメイン処理を示すフローチャートである。

【図 3 9】演出制御コマンドの内容の一例を示す説明図である。

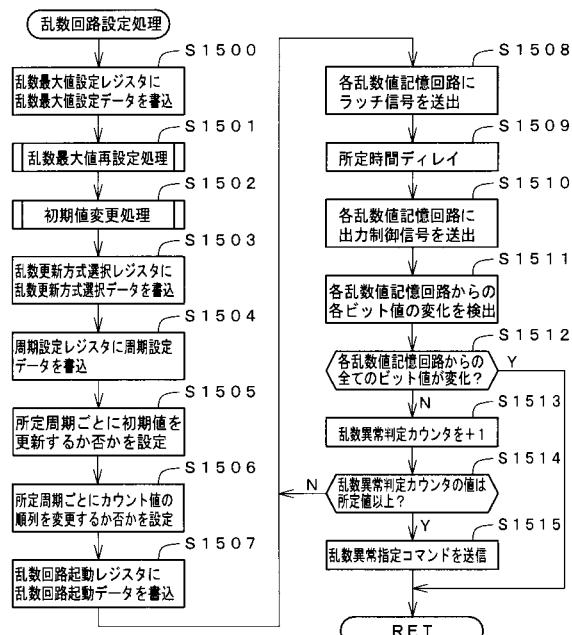

【図 4 0】乱数回路設定処理を示すフローチャートである。

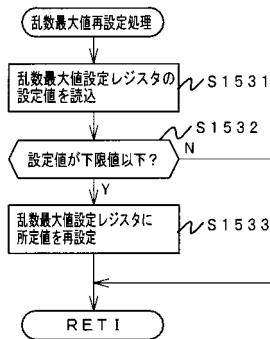

【図 4 1】乱数最大値再設定処理を示すフローチャートである。

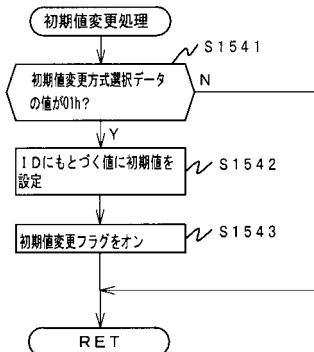

【図 4 2】初期値変更処理を示すフローチャートである。

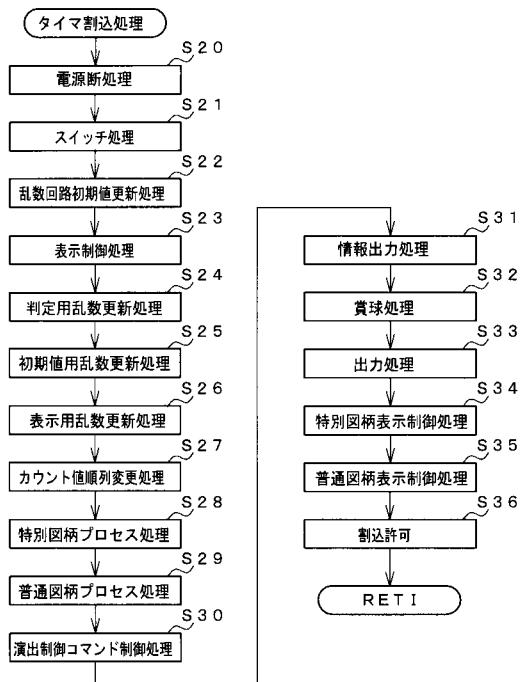

【図 4 3】2 ms タイマ割込処理を示すフローチャートである。

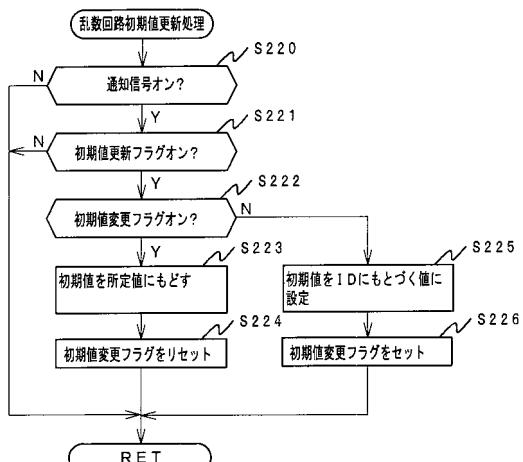

【図 4 4】乱数回路初期値更新処理を示すフローチャートである。

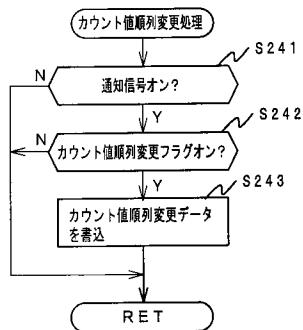

【図 4 5】カウント値順列変更処理を示すフローチャートである。

【図 4 6】各ソフトウェア乱数を示す説明図である。

【図 4 7】大当たり判定テーブルおよび大当たり種別判定テーブルを示す説明図である。

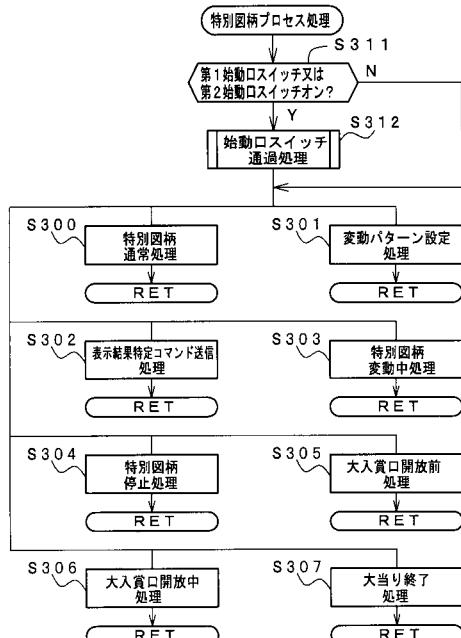

【図 4 8】特別図柄プロセス処理を示すフローチャートである。

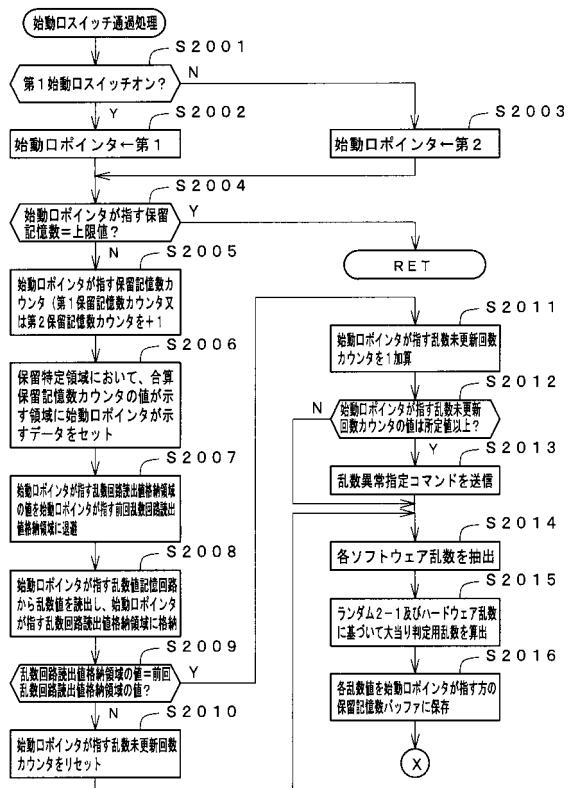

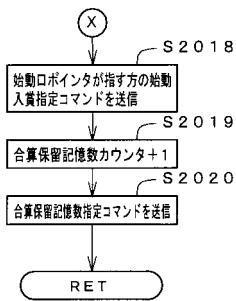

【図 4 9】始動口スイッチ通過処理を示すフローチャートである。

【図 5 0】始動口スイッチ通過処理を示すフローチャートである。

【図 5 1】保留記憶特定情報記憶領域（保留特定領域）の構成例を示す説明図である。

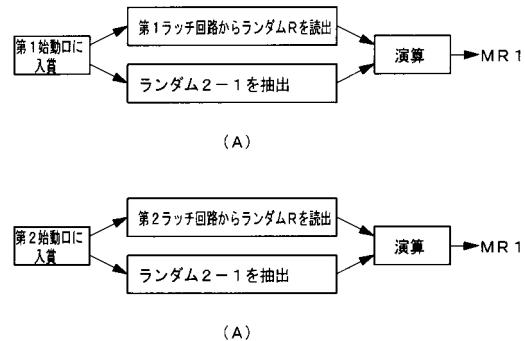

【図 5 2】大当たり判定値と比較されるランダム MR 1 の作成の仕方を示す説明図である。

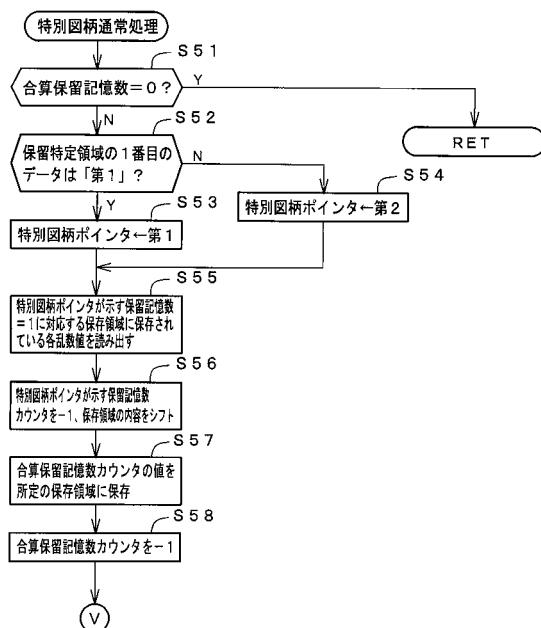

【図 5 3】特別図柄通常処理を示すフローチャートである。

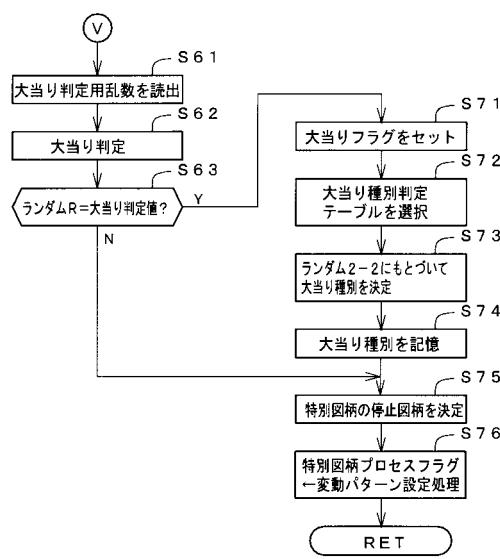

【図 5 4】特別図柄通常処理を示すフローチャートである。

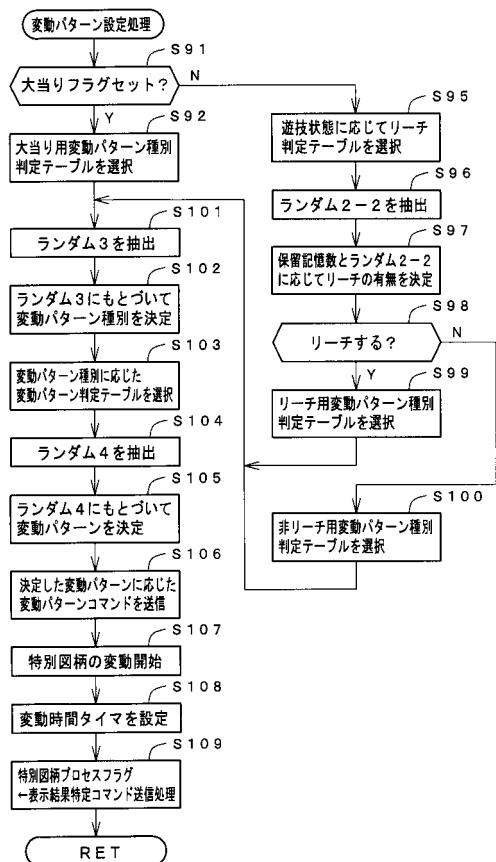

【図 5 5】変動パターン設定処理を示すフローチャートである。

【図 5 6】表示結果特定コマンド送信処理を示すフローチャートである。

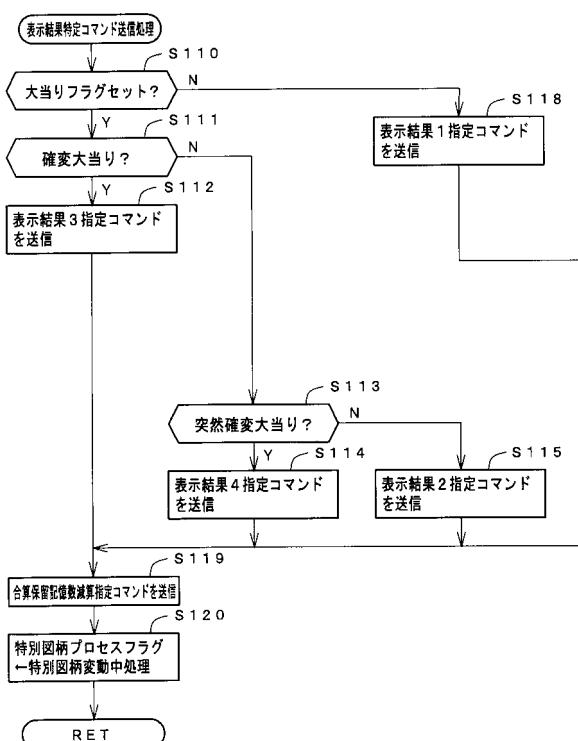

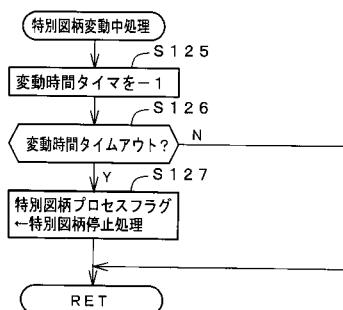

【図 5 7】特別図柄変動中処理を示すフローチャートである。

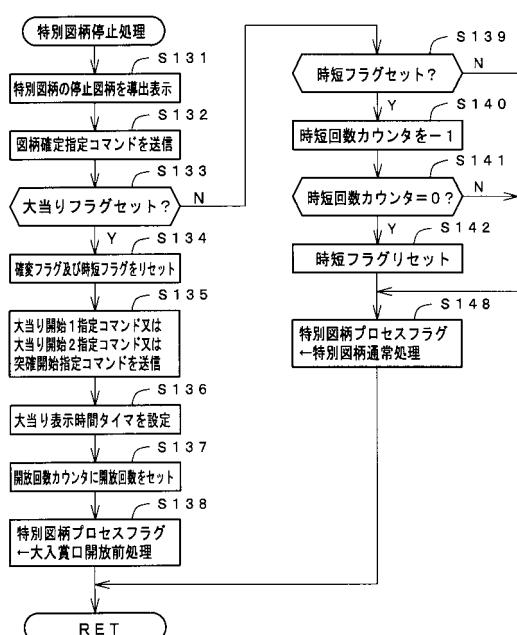

【図 5 8】特別図柄停止処理を示すフローチャートである。

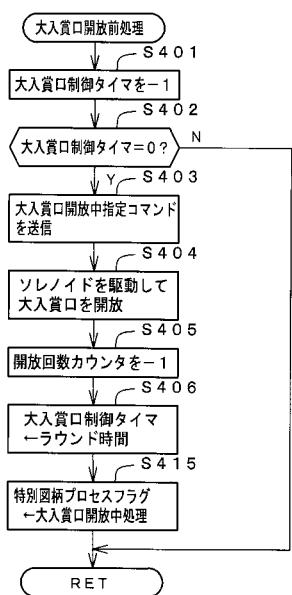

【図 5 9】大入賞口開放前処理を示すフローチャートである。

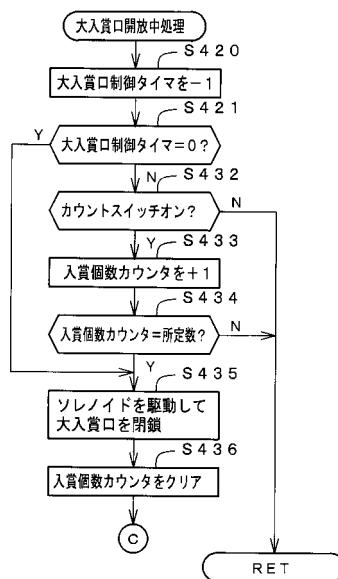

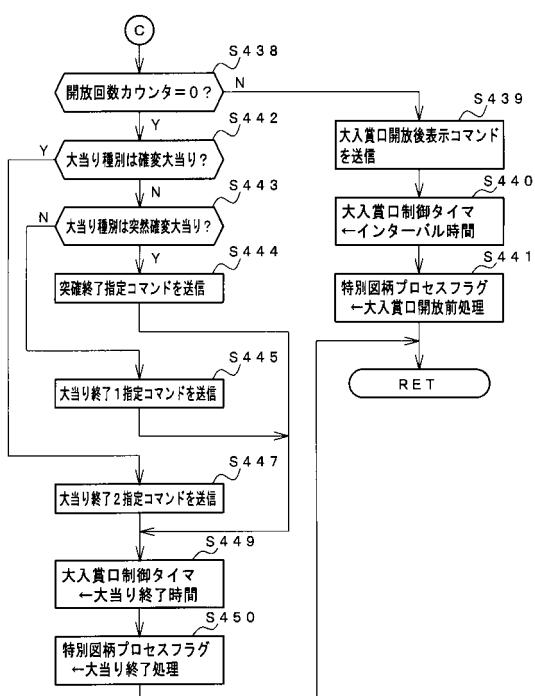

【図 6 0】大入賞口開放中処理を示すフローチャートである。

【図 6 1】大入賞口開放中処理を示すフローチャートである。

10

20

30

40

50

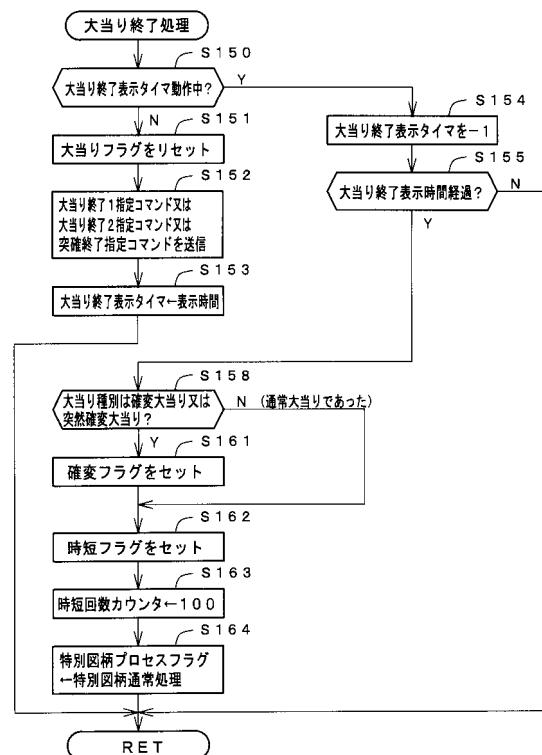

【図62】大当たり終了処理を示すフローチャートである。

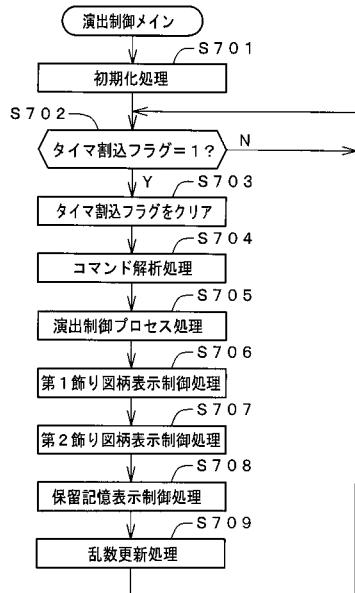

【図63】演出制御用CPUが実行する演出制御メイン処理を示すフローチャートである。

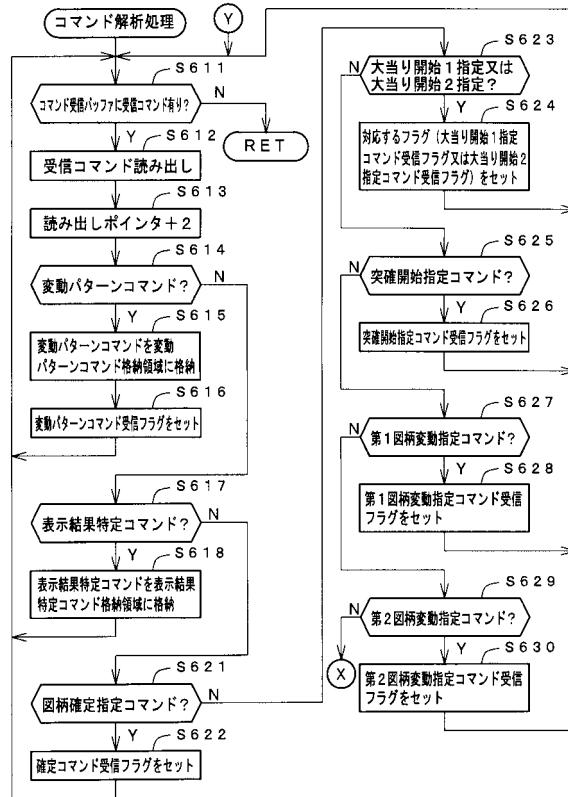

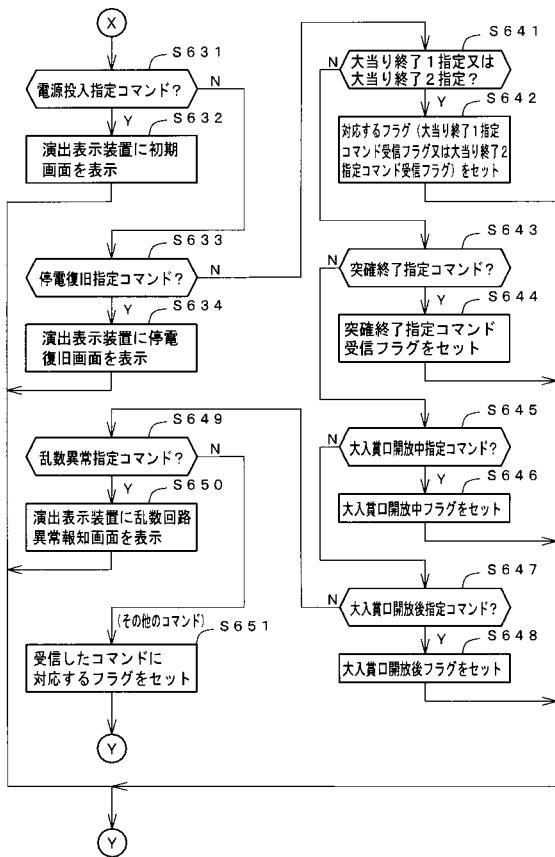

【図64】コマンド解析処理を示すフローチャートである。

【図65】コマンド解析処理を示すフローチャートである。

【図66】演出制御用マイクロコンピュータが使用する乱数を示す説明図である。

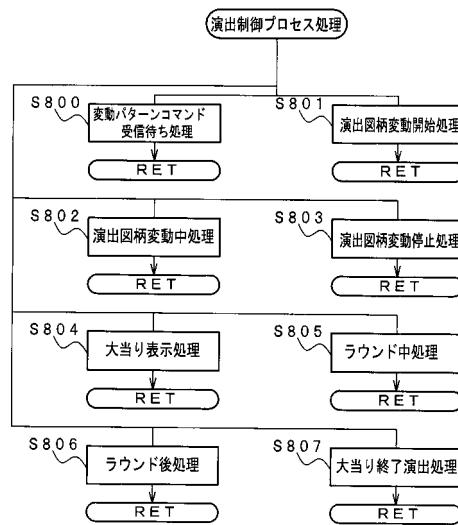

【図67】演出制御プロセス処理を示すフローチャートである。

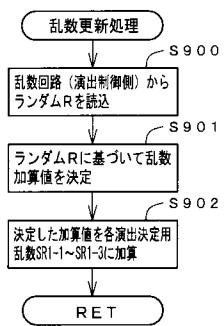

【図68】乱数更新処理を示すフローチャートである。

【図69】乱数加算値決定用のテーブルの例を示す説明図である。

【図70】クリアスイッチと遊技開始スイッチとを兼用する場合の主基板（遊技制御基板）における回路構成の例を示すブロック図である。 10

【図71】クリアスイッチと遊技開始スイッチとを兼用する場合のメイン処理を示すフローチャートである。

【図72】スロット機を正面からみた正面図である。

【発明を実施するための形態】

【0014】

以下、本発明の実施の形態を、図面を参照して説明する。まず、遊技機の一例であるパチンコ遊技機1の全体の構成について説明する。図1はパチンコ遊技機1を正面からみた正面図である。また、図2はパチンコ遊技機を示す背面図である。

【0015】

パチンコ遊技機1は、縦長の方形状に形成された外枠（図示せず）と、外枠の内側に開閉可能に取り付けられた遊技枠とで構成される。また、パチンコ遊技機1は、遊技枠に開閉可能に設けられている額縁状に形成されたガラス扉枠2を有する。遊技枠は、外枠に対して開閉自在に設置される前面枠（図示せず）と、機構部品等が取り付けられる機構板（図示せず）と、それらに取り付けられる種々の部品（後述する遊技盤6を除く）とを含む構造体である。

【0016】

ガラス扉枠2の下部表面には打球供給皿（上皿）3がある。打球供給皿3の下部には、打球供給皿3に収容しきれない遊技球を貯留する余剰球受皿4や、打球を発射する打球操作ハンドル（操作ノブ）5が設けられている。また、ガラス扉枠2の背面には、遊技盤6が着脱可能に取り付けられている。なお、遊技盤6は、それを構成する板状体と、その板状体に取り付けられた種々の部品とを含む構造体である。また、遊技盤6の前面には、打ち込まれた遊技球が流下可能な遊技領域7が形成されている。 30

【0017】

遊技領域7の中央付近には、液晶表示装置（LCD）で構成された演出表示装置9が設けられている。演出表示装置9の表示画面には、第1特別図柄または第2特別図柄の可変表示に同期した演出図柄の可変表示を行う演出図柄表示領域がある。よって、演出表示装置9は、演出図柄の可変表示を行う可変表示装置に相当する。演出図柄表示領域には、例えば「左」、「中」、「右」の3つの装飾用（演出用）の識別情報を可変表示する図柄表示エリアがある。図柄表示エリアには「左」、「中」、「右」の各図柄表示エリア9L、9C、9Rがあるが、図柄表示エリア9Aの位置は、演出表示装置9の表示画面において固定的でなくともよいし、図柄表示エリア9L、9C、9Rの3つ領域が離れてもよい。演出表示装置9は、演出制御基板に搭載されている演出制御用マイクロコンピュータによって制御される。演出制御用マイクロコンピュータが、第1特別図柄表示器8aで第1特別図柄の可変表示が実行されているときに、その可変表示に伴って演出表示装置9で演出表示を実行させ、第2特別図柄表示器8bで第2特別図柄の可変表示が実行されているときに、その可変表示に伴って演出表示装置で演出表示を実行させてるので、遊技の進行状況を把握しやすくなることができる。 40

【0018】

遊技盤6における下部の左側には、識別情報をとしての第1特別図柄を可変表示する第1

10

20

30

40

50

特別図柄表示器（第1可変表示部）8aが設けられている。この実施の形態では、第1特別図柄表示器8aは、0～9の数字を可変表示可能な簡易で小型の表示器（例えば7セグメントLED）で実現されている。すなわち、第1特別図柄表示器8aは、0～9の数字（または、記号）を可変表示するように構成されている。遊技盤6における下部の右側には、識別情報としての第2特別図柄を可変表示する第2特別図柄表示器（第2可変表示部）8bが設けられている。第2特別図柄表示器8bは、0～9の数字を可変表示可能な簡易で小型の表示器（例えば7セグメントLED）で実現されている。すなわち、第2特別図柄表示器8bは、0～9の数字（または、記号）を可変表示するように構成されている。

## 【0019】

10

小型の表示器は、例えば方形状に形成されている。また、この実施の形態では、第1特別図柄の種類と第2特別図柄の種類とは同じ（例えば、ともに0～9の数字）であるが、種類が異なっていてもよい。また、第1特別図柄表示器8aおよび第2特別図柄表示器8bは、それぞれ、例えば、00～99の数字（または、2桁の記号）を可変表示するように構成されていてもよい。

## 【0020】

以下、第1特別図柄と第2特別図柄とを特別図柄と総称することがあり、第1特別図柄表示器8aと第2特別図柄表示器8bとを特別図柄表示器（可変表示部）と総称することがある。

## 【0021】

20

第1特別図柄または第2特別図柄の可変表示は、可変表示の実行条件である第1始動条件または第2始動条件が成立（例えば、遊技球が第1始動入賞口13または第2始動入賞口14に入賞したこと）した後、可変表示の開始条件（例えば、保留記憶数が0でない場合であって、第1特別図柄および第2特別図柄の可変表示が実行されていない状態であり、かつ、大当たり遊技が実行されていない状態）が成立したことにもとづいて開始され、可変表示時間が経過すると表示結果（停止図柄）を導出表示する。なお、入賞とは、入賞口などのあらかじめ入賞領域として定められている領域に遊技球が入ったことである。また、表示結果を導出表示するとは、図柄（識別情報の例）を停止表示させることである（いわゆる再変動の前の停止を除く。）。また、この実施の形態では、第1始動入賞口13への入賞および第2始動入賞口14への入賞に関わりなく、始動入賞が生じた順に可変表示の開始条件を成立させるが、第1始動入賞口13への入賞と第2始動入賞口14への入賞のうちのいずれかを優先させて可変表示の開始条件を成立させるようにしてもよい。例えば第1始動入賞口13への入賞を優先させる場合には、第1特別図柄および第2特別図柄の可変表示が実行されていない状態であり、かつ、大当たり遊技が実行されていない状態であれば、第2保留記憶数が0でない場合でも、第1保留記憶数が0になるまで、第1特別図柄の可変表示を続けて実行する。

30

## 【0022】

第1特別図柄表示器8aの近傍には、第1特別図柄表示器8aによる第1特別図柄の可変表示時間中に、装飾用（演出用）の図柄としての第1飾り図柄の可変表示を行う第1飾り図柄表示器9aが設けられている。この実施の形態では、第1飾り図柄表示器9aは、2つのLEDで構成されている。第1飾り図柄表示器9aは、演出制御基板に搭載されている演出制御用マイクロコンピュータによって制御される。また、第2特別図柄表示器8bの近傍には、第2特別図柄表示器8bによる第2特別図柄の可変表示時間中に、装飾用（演出用）の図柄としての第2飾り図柄の可変表示を行う第2飾り図柄表示器9bが設けられている。第2飾り図柄表示器9bは、2つのLEDで構成されている。第2飾り図柄表示器9bは、演出制御基板に搭載されている演出制御用マイクロコンピュータによって制御される。

40

## 【0023】

なお、第1飾り図柄と第2飾り図柄とを、飾り図柄と総称することがあり、第1飾り図柄表示器9aと第2飾り図柄表示器9bを、飾り図柄表示器と総称することがある。

50

## 【0024】

飾り図柄の変動（可変表示）は、2つのLEDが交互に点灯する状態を継続することによって実現される。第1特別図柄表示器8aにおける第1特別図柄の可変表示と、第1飾り図柄表示器9aにおける第1飾り図柄の可変表示とは同期している。第2特別図柄表示器8bにおける第2特別図柄の可変表示と、第2飾り図柄表示器9bにおける第2飾り図柄の可変表示とは同期している。同期とは、可変表示の開始時点および終了時点が同じであって、可変表示の期間が同じであることをいう。また、第1特別図柄表示器8aにおいて大当たり図柄が停止表示されるときには、第1飾り図柄表示器9aにおいて大当たりを想起させる側のLEDが点灯されたままになる。第2特別図柄表示器8bにおいて大当たり図柄が停止表示されるときには、第2飾り図柄表示器9bにおいて大当たりを想起させる側のLEDが点灯されたままになる。なお、第1飾り図柄表示器9aおよび第2飾り図柄表示器9bの機能を、演出表示装置9で実現するようにしてもよい。すなわち、第1飾り図柄および第2飾り図柄が、演出表示装置9の表示画面において画像として可変表示されるように制御してもよい。

10

## 【0025】

演出表示装置9の下方には、第1始動入賞口13を有する入賞装置が設けられている。第1始動入賞口13に入賞した遊技球は、遊技盤6の背面に導かれ、第1始動口スイッチ13aによって検出される。

## 【0026】

また、第1始動入賞口（第1始動口）13を有する入賞装置の下方には、遊技球が入賞可能な第2始動入賞口14を有する可変入賞球装置15が設けられている。第2始動入賞口（第2始動口）14に入賞した遊技球は、遊技盤6の背面に導かれ、第2始動口スイッチ14aによって検出される。可変入賞球装置15は、ソレノイド16によって開状態とされる。可変入賞球装置15が開状態になるとによって、遊技球が第2始動入賞口14に入賞可能になり（始動入賞し易くなり）、遊技者にとって有利な状態になる。可変入賞球装置15が開状態になっている状態では、第1始動入賞口13よりも、第2始動入賞口14に遊技球が入賞しやすい。また、可変入賞球装置15が閉状態になっている状態では、遊技球は第2始動入賞口14に入賞しない。従って、可変入賞球装置15が閉状態になっている状態では、第2始動入賞口14よりも、第1始動入賞口13に遊技球が入賞しやすい。なお、可変入賞球装置15が閉状態になっている状態において、入賞はしづらいものの、入賞することは可能である（すなわち、遊技球が入賞しにくい）ように構成されていてもよい。

20

## 【0027】

以下、第1始動入賞口13と第2始動入賞口14とを総称して始動入賞口または始動口ということがある。

30

## 【0028】

可変入賞球装置15が開放状態に制御されているときには可変入賞球装置15に向かう遊技球は第2始動入賞口14に極めて入賞しやすい。そして、第1始動入賞口13は演出表示装置9の直下に設けられているが、演出表示装置9の下端と第1始動入賞口13との間の間隔をさらに狭めたり、第1始動入賞口13の周辺で釘を密に配置したり、第1始動入賞口13の周辺での釘配列を遊技球を第1始動入賞口13に導きづらくして、第2始動入賞口14の入賞率の方を第1始動入賞口13の入賞率よりもより高くするようにしてもよい。

40

## 【0029】

なお、この実施の形態では、図1に示すように、第2始動入賞口14に対してのみ開閉動作を行う可変入賞球装置15が設けられているが、第1始動入賞口13および第2始動入賞口14のいずれについても開閉動作を行う可変入賞球装置が設けられている構成であってもよい。

## 【0030】

第1飾り図柄表示器9aの側方には、第1始動入賞口13に入った有効入賞球数すなわ

50

ち第1保留記憶数（保留記憶を、始動記憶または始動入賞記憶ともいう。）を表示する4つの表示器からなる第1特別図柄保留記憶表示器18aが設けられている。第1特別図柄保留記憶表示器18aは、有効始動入賞がある毎に、点灯する表示器の数を1増やす。そして、第1特別図柄表示器8aでの可変表示が開始される毎に、点灯する表示器の数を1減らす。

#### 【0031】

第2飾り図柄表示器9bの側方には、第2始動入賞口14に入った有効入賞球数すなわち第2保留記憶数を表示する4つの表示器からなる第2特別図柄保留記憶表示器18bが設けられている。第2特別図柄保留記憶表示器18bは、有効始動入賞がある毎に、点灯する表示器の数を1増やす。そして、第2特別図柄表示器8bでの可変表示が開始される毎に、点灯する表示器の数を1減らす。

10

#### 【0032】

また、演出表示装置9の表示画面には、第1保留記憶数と第2保留記憶数との合計である合計数（合算保留記憶数）を表示する領域（以下、合算保留記憶表示部18cという。）が設けられている。合計数を表示する合算保留記憶表示部18cが設けられているので、可変表示の開始条件が成立していない実行条件の成立数の合計を把握しやすくすることができる。なお、合算保留記憶表示部18cが設けられているので、第1特別図柄保留記憶表示器18aおよび第2特別図柄保留記憶表示器18bは、設けられていなくてもよい。

20

#### 【0033】

演出表示装置9は、第1特別図柄表示器8aによる第1特別図柄の可変表示時間中、および第2特別図柄表示器8bによる第2特別図柄の可変表示時間中に、装飾用（演出用）の図柄としての演出図柄の可変表示を行う。第1特別図柄表示器8aにおける第1特別図柄の可変表示と、演出表示装置9における演出図柄の可変表示とは同期している。また、第2特別図柄表示器8bにおける第2特別図柄の可変表示と、演出表示装置9における演出図柄の可変表示とは同期している。また、第1特別図柄表示器8aにおいて大当たり図柄が停止表示されるときと、第2特別図柄表示器8bにおいて大当たり図柄が停止表示されるときには、演出表示装置9において大当たりを想起させるような演出図柄の組み合わせが停止表示される。

30

#### 【0034】

演出表示装置9の周囲の飾り部において、右側には、上演出LED85a、中演出LED85bおよび下演出LED85cが設けられている。上演出LED85a、中演出LED85bおよび下演出LED85cは、特定演出としての擬似連の演出（1回の変動期間中におけるそれぞれの再変動期間（初回変動の期間も含む。）において関連する表示演出が実行されるような演出）が実行されるときに点滅する。また、左側には、モータ86の回転軸に取り付けられ、モータ86が回転すると移動する可動部材78が設けられている。可動部材78は、擬似連の演出が実行されるときに動作する。なお、上演出LED85a、中演出LED85bおよび下演出LED85cの近傍には、各LEDの取付部分を信号させる振動モータ（図示せず）が設けられている。

40

#### 【0035】

また、図1に示すように、可変入賞球装置15の下方には、特別可変入賞球装置20が設けられている。特別可変入賞球装置20は開閉板を備え、第1特別図柄表示器8aに特定表示結果（大当たり図柄）が導出表示されたときと、第2特別図柄表示器8bに特定表示結果（大当たり図柄）が導出表示されたときに生起する特定遊技状態（大当たり遊技状態）においてソレノイド21によって開閉板が開放状態に制御されることによって、入賞領域となる大入賞口が開放状態になる。大入賞口に入賞した遊技球はカウントスイッチ23で検出される。

#### 【0036】

遊技領域6には、遊技球の入賞にもとづいてあらかじめ決められている所定数の景品遊技球の払出を行うための入賞口（普通入賞口）29, 30, 33, 39も設けられている

50

。入賞口 29, 30, 33, 39 に入賞した遊技球は、入賞口スイッチ 29a, 30a, 33a, 39a で検出される。

#### 【0037】

遊技盤 6 の右側方には、普通図柄表示器 10 が設けられている。普通図柄表示器 10 は、普通図柄と呼ばれる複数種類の識別情報（例えば、「」および「×」）を可変表示する。

#### 【0038】

遊技球がゲート 32 を通過しゲートスイッチ 32a で検出されると、普通図柄表示器 10 の表示の可変表示が開始される。この実施の形態では、上下のランプ（点灯時に図柄が視認可能になる）が交互に点灯することによって可変表示が行われ、例えば、可変表示の終了時に下側のランプが点灯すれば当りとなる。そして、普通図柄表示器 10 における停止図柄が所定の図柄（当り図柄）である場合に、可変入賞球装置 15 が所定回数、所定時間だけ開状態になる。すなわち、可変入賞球装置 15 の状態は、普通図柄の停止図柄が当り図柄である場合に、遊技者にとって不利な状態から有利な状態（第 2 始動入賞口 14 に遊技球が入賞可能な状態）に変化する。普通図柄表示器 10 の近傍には、ゲート 32 を通過した入賞球数を表示する 4 つの LED による表示部を有する普通図柄保留記憶表示器 41 が設けられている。ゲート 32 への遊技球の通過がある毎に、すなわちゲートスイッチ 32a によって遊技球が検出される毎に、普通図柄保留記憶表示器 41 は点灯する LED を 1 増やす。そして、普通図柄表示器 10 の可変表示が開始される毎に、点灯する LED を 1 減らす。

10

20

#### 【0039】

遊技盤 6 の遊技領域 7 の左右周辺には、遊技中に点滅表示される装飾 LED 25 が設けられ、下部には、入賞しなかった打球が取り込まれるアウトロ 26 がある。また、遊技領域 7 の外側の左右上部には、所定の音声出力として効果音や音声を発声する 2 つのスピーカ 27 が設けられている。遊技領域 7 の外周には、前面枠に設けられた枠 LED 28 が設けられている。

30

#### 【0040】

遊技機には、遊技者が打球操作ハンドル 5 を操作することに応じて駆動モータを駆動し、駆動モータの回転力をを利用して遊技球を遊技領域 7 に発射する打球発射装置（図示せず）が設けられている。打球発射装置から発射された遊技球は、遊技領域 7 を囲むように円形状に形成された打球レールを通って遊技領域 7 に入り、その後、遊技領域 7 を下りてくる。遊技球が第 1 始動入賞口 13 に入り第 1 始動口スイッチ 13a で検出されると、第 1 特別図柄の可変表示を開始できる状態であれば（例えば、特別図柄の可変表示が終了し、第 1 の開始条件が成立したこと）、第 1 特別図柄表示器 8a において第 1 特別図柄の可変表示（変動）が開始されるとともに、第 1 飾り図柄表示器 9a において第 1 飾り図柄の可変表示が開始され、演出表示装置 9 において演出図柄の可変表示が開始される。すなわち、第 1 特別図柄、第 1 飾り図柄および演出図柄の可変表示は、第 1 始動入賞口 13 への入賞に対応する。第 1 特別図柄の可変表示を開始できる状態でなければ、第 1 保留記憶数が上限値に達していないことを条件として、第 1 保留記憶数を 1 増やす。

30

#### 【0041】

遊技球が第 2 始動入賞口 14 に入り第 2 始動口スイッチ 14a で検出されると、第 2 特別図柄の可変表示を開始できる状態であれば（例えば、特別図柄の可変表示が終了し、第 2 の開始条件が成立したこと）、第 2 特別図柄表示器 8b において第 2 特別図柄の可変表示（変動）が開始されるとともに、第 2 飾り図柄表示器 9b において第 2 飾り図柄の可変表示が開始され、演出表示装置 9 において演出図柄の可変表示が開始される。すなわち、第 2 特別図柄、第 2 飾り図柄および演出図柄の可変表示は、第 2 始動入賞口 14 への入賞に対応する。第 2 特別図柄の可変表示を開始できる状態でなければ、第 2 保留記憶数が上限値に達していないことを条件として、第 2 保留記憶数を 1 増やす。

40

#### 【0042】

また、この実施の形態では、特別図柄変動の表示結果が確変大当りまたは突然確変大当

50

りとなったときに、遊技状態が確変状態に移行される。この確変状態では、少なくとも通常状態に比べて大当たりとすることに決定される確率が高い高確率状態となるように制御される。なお、確変状態において、高確率状態に制御するとともに、特別図柄の変動時間を短縮したり、普通図柄表示器10における停止図柄が当り図柄になる確率を高めるようにしたり、普通図柄の変動時間を短縮したり、可変入賞球装置15の開放時間と開放回数とを高めるようにしたりするようにしてもよい。この場合、確変状態において、これらのいずれか1つまたは複数が実行されるようにしてもよく、全てが実行されるようにしてもよい。

#### 【0043】

また、この実施の形態では、大当たり遊技終了後に、少なくとも普通図柄の変動時間が短縮される時短状態に制御される。なお、時短状態において、特別図柄の変動時間を短縮したり、普通図柄表示器10における停止図柄が当り図柄になる確率を高めるようにしたり、可変入賞球装置15の開放時間と開放回数とを高めるようにしたりするようにしてもよい。この場合、時短状態において、これらのいずれか1つまたは複数が実行されるようにしてもよく、全てが実行されるようにしてもよい。

#### 【0044】

次に、パチンコ遊技機1の裏面の構造について図2を参照して説明する。図2に示すように、パチンコ遊技機1裏面側では、演出表示装置9を制御する演出制御用マイクロコンピュータ110が搭載された演出制御基板80を含む変動表示制御ユニット、遊技制御用マイクロコンピュータ等が搭載された遊技制御基板（主基板）31、音声出力基板70、LEDドライバ基板（図示せず）、および、球払出制御を行なう払出制御用マイクロコンピュータ等が搭載された払出制御基板37等の各種基板が設置されている。なお、遊技制御基板31は基板収納ケース200に収納されている。また、遊技制御基板31には、遊技の開始を指示するための遊技開始スイッチ90が設けられている。

#### 【0045】

さらに、パチンコ遊技機1裏面側には、DC30V、DC21V、DC12VおよびDC5V等の各種電源電圧を作成する電源回路が搭載された電源基板910やタッチセンサ基板91Aが設けられている。電源基板910には、パチンコ遊技機1における遊技制御基板31および各電気部品制御基板（演出制御基板80および払出制御基板37）やパチンコ遊技機1に設けられている各電気部品（電力が供給されることによって動作する部品）への電力供給を実行あるいは遮断するための電力供給許可手段としての電源スイッチ、遊技制御基板31の遊技制御用マイクロコンピュータ560のRAM55をクリアするためのクリアスイッチ921が設けられている。さらに、電源スイッチの内側（基板内部側）には、交換可能なヒューズが設けられている。

#### 【0046】

また、主基板31を収納する基板収納ケース200におけるケースカバーには、四角筒状の被固定部255a～255dが、基板収納ケース200におけるケース本体201の各ねじ穴に対向する箇所に複数形成されている。それらの固定部によって第1被固定部255が構成されている。なお、第1被固定部255の役割等については後述する。また、主基板31には、遊技の開始を指示するための遊技開始スイッチ90が設けられている。

#### 【0047】

なお、電気部品制御基板には、電気部品制御用マイクロコンピュータを含む電気部品制御手段が搭載されている。電気部品制御手段は、遊技制御手段等からのコマンドとしての指令信号（制御信号）に従ってパチンコ遊技機1に設けられている電気部品（遊技用装置：球払出装置97、演出表示装置9、LEDなどの発光体、スピーカ27等）を制御する。以下、遊技制御基板31を電気部品制御基板に含めて説明を行なうことがある。その場合には、電気部品制御基板に搭載される電気部品制御手段は、遊技制御手段と、遊技制御手段等からの指令信号に従ってパチンコ遊技機1に設けられている電気部品を制御する手段とのそれぞれを指す。また、遊技制御基板31以外のマイクロコンピュータが搭載された基板をサブ基板ということがある。

10

20

30

40

50

## 【0048】

パチンコ遊技機1裏面において、上方には、各種情報をパチンコ遊技機1の外部に出力するための各端子を備えたターミナル基板159が設置されている。ターミナル基板159には、少なくとも、球切れ検出スイッチ167の出力を導入して外部出力するための球切れ用端子、賞球情報（賞球個数信号）を外部出力するための賞球用端子および球貸し情報（球貸し個数信号）を外部出力するための球貸し用端子が設けられている。

## 【0049】

貯留タンク38に貯留された遊技球は誘導レール（図示せず）を通り、カーブ樋を経て払出ケース40Aで覆われた球払出装置97に至る。球払出装置97の上方には、遊技媒体切れ検出手段としての球切れスイッチ187が設けられている。球切れスイッチ187が球切れを検出すると、球払出装置97の払出動作が停止する。球切れスイッチ187は遊技球通路内の遊技球の有無を検出するスイッチであるが、貯留タンク38内の補給球の不足を検出する球切れ検出スイッチ167も誘導レールにおける上流部分（貯留タンク38に近接する部分）に設けられている。球切れ検出スイッチ167が遊技球の不足を検知すると、遊技機設置島に設けられている補給機構からパチンコ遊技機1に対して遊技球の補給が行なわれる。10

## 【0050】

入賞にもとづく景品としての遊技球や球貸し要求にもとづく遊技球が多数払出されて打球供給皿3が満杯になると、遊技球は、余剰球誘導通路を経て余剰球受皿4に導かれる。さらに遊技球が払出されると、感知レバー（図示せず）が貯留状態検出手段としての満タンスイッチを押圧して、貯留状態検出手段としての満タンスイッチがオンする。その状態では、球払出装置内の払出モータの回転が停止して球払出装置の動作が停止するとともに打球発射装置の駆動も停止する。20

## 【0051】

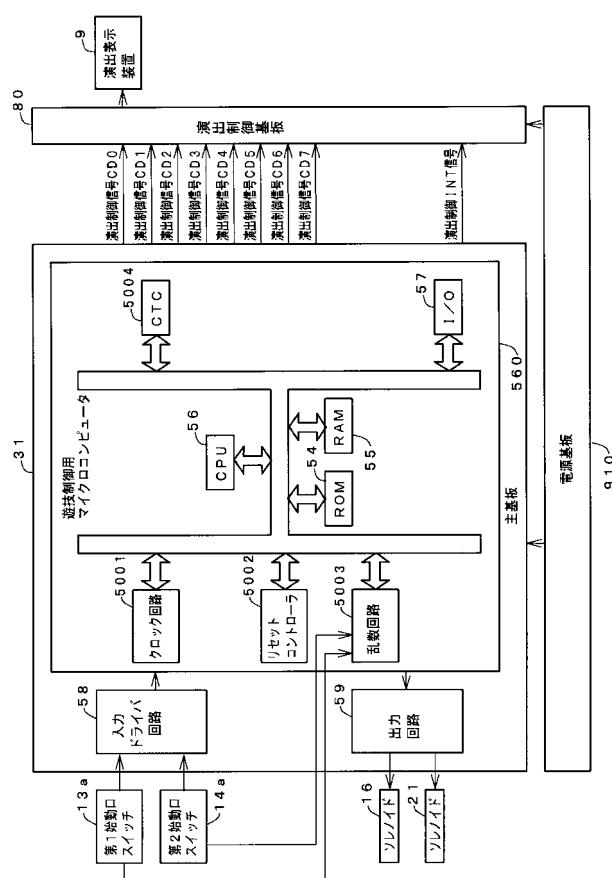

図3は、主基板（遊技制御基板）31における回路構成の一例を示すブロック図である。なお、図3は、払出制御基板37および演出制御基板80等も示されている。主基板31には、プログラムに従ってパチンコ遊技機1を制御する遊技制御用マイクロコンピュータ（遊技制御手段に相当）560が搭載されている。遊技制御用マイクロコンピュータ560は、ゲーム制御（遊技進行制御）用のプログラム等を記憶するROM54、ワークメモリとして使用される記憶手段としてのRAM55、プログラムに従って制御動作を行うCPU56およびI/Oポート部57を含む。この実施の形態では、ROM54およびRAM55は遊技制御用マイクロコンピュータ560に内蔵されている。すなわち、遊技制御用マイクロコンピュータ560は、1チップマイクロコンピュータである。1チップマイクロコンピュータには、少なくともCPU56のほかRAM55が内蔵されなければよく、ROM54は外付けであっても内蔵されていてもよい。また、I/Oポート部57は、外付けであってもよい。30

## 【0052】

さらに、遊技制御用マイクロコンピュータ560には、ハードウェア乱数（ハードウェア回路が発生する乱数）を発生する乱数回路5003が内蔵されている。この実施の形態では、後述するように、遊技制御用マイクロコンピュータ560は、乱数回路5003が発生するハードウェア乱数を用いて生成した大当たり判定用乱数にもとづいて、大当たりとするか否かを決定する。例えば、乱数回路5003において、カウンタ521は、セレクタ528を介してクロック信号出力回路524が出力した乱数発生用クロック信号SI1を入力したことにもとづいて、カウント値Cを1つずつ更新する。そして、遊技制御用マイクロコンピュータ560は、カウンタ521によって更新されたカウント値Cをハードウェア乱数として用いて大当たり判定用乱数を生成し、大当たりとするか否かを決定する。40

## 【0053】

なお、遊技制御用マイクロコンピュータ560は、乱数回路5003を内蔵しなくてもよい。この場合、例えば、遊技制御用マイクロコンピュータ560は、遊技制御用マイクロコンピュータ560に外付けで取り付けられた乱数回路からハードウェア乱数を読み込50

み、そのハードウェア乱数を用いて生成した大当たり判定用乱数にもとづいて、大当たりとするか否かを決定するようにしてもよい。

#### 【0054】

また、RAM55は、その一部または全部が電源基板910において作成されるバックアップ電源によってバックアップされている不揮発性記憶手段としてのバックアップRAMである。すなわち、遊技機に対する電力供給が停止しても、所定期間（バックアップ電源としてのコンデンサが放電してバックアップ電源が電力供給不能になるまで）は、RAM55の一部または全部の内容は保存される。特に、少なくとも、遊技状態すなわち遊技制御手段の制御状態に応じたデータ（特別図柄プロセスフラグなど）、未払出賞球数を示すデータ、判定用乱数などの各ソフトウェア乱数（後述する大当たり判定算出用乱数（ランダム2-1）や、普通図柄当たり判定用乱数（ランダム6）など）、および各ソフトウェア乱数をカウントするためのカウンタ（後述する大当たり判定算出用カウンタや、普通図柄当たり判定用カウンタなど）は、バックアップRAMに保存される。なお、後述する大当たり判定算出用乱数（ランダム2-1）とハードウェア乱数とを用いて算出される大当たり判定用乱数MR1も（ステップS2015参照）、バックアップRAMに保存される。遊技制御手段の制御状態に応じたデータとは、停電等が生じた後に復旧した場合に、そのデータにもとづいて、制御状態を停電等の発生前に復旧させるために必要なデータである。また、制御状態に応じたデータと未払出賞球数を示すデータとを遊技の進行状態を示すデータと定義する。なお、この実施の形態では、RAM55の全部が、電源バックアップされているとする。

10

20

#### 【0055】

なお、遊技制御用マイクロコンピュータ560においてCPU56がROM54に格納されているプログラムに従って制御を実行するので、以下、遊技制御用マイクロコンピュータ560（またはCPU56）が実行する（または、処理を行う）ということは、具体的には、CPU56がプログラムに従って制御を実行することである。このことは、主基板31以外の他の基板に搭載されているマイクロコンピュータについても同様である。

30

#### 【0056】

乱数回路5003は、特別図柄の可変表示の表示結果により大当たりとするか否か判定するための判定用の乱数を発生するために用いられるハードウェア回路である。乱数回路5003は、初期値（例えば、0）と上限値（例えば、65535）とが設定された数値範囲内で、数値データを、設定された更新規則に従って更新し、ランダムなタイミングで発生する始動入賞時が数値データの読み出（抽出）時であることにもとづいて、読み出される数値データが乱数値となる乱数発生機能を有する。

40

#### 【0057】

乱数回路5003は、数値データの更新範囲の選択設定機能（初期値の選択設定機能、および、上限値の選択設定機能）、数値データの更新規則の選択設定機能、および数値データの更新規則の選択切換え機能等の各種の機能を有する。このような機能によって、生成する乱数のランダム性を向上させることができる。

#### 【0058】

また、遊技制御用マイクロコンピュータ560は、乱数回路5003が更新する数値データの初期値を設定する機能を有している。例えば、ROM54等の所定の記憶領域に記憶された遊技制御用マイクロコンピュータ560のIDナンバ（遊技制御用マイクロコンピュータ560の各製品ごとに異なる数値で付与されたIDナンバ）を用いて所定の演算を行なって得られた数値データを、乱数回路5003が更新する数値データの初期値として設定する。そのような処理を行うことによって、乱数回路5003が発生する乱数のランダム性をより向上させることができる。

#### 【0059】

また、ゲートスイッチ32a、始動口スイッチ13a、カウントスイッチ23、入賞口スイッチ29a, 30a, 33a, 39aからの検出信号を遊技制御用マイクロコンピュータ560に与える入力ドライバ回路58も主基板31に搭載されている。また、可変入

50

賞球装置 15 を開閉するソレノイド 16、および大入賞口を形成する特別可変入賞球装置 20 を開閉するソレノイド 21 を遊技制御用マイクロコンピュータ 560 からの指令に従って駆動する出力回路 59 も主基板 31 に搭載されている。また、遊技の開始を指示するための遊技開始スイッチ 90 も主基板 31 に搭載されている。

#### 【0060】

また、遊技制御用マイクロコンピュータ 560 は、特別図柄を可変表示する第 1 特別図柄表示器 8a、第 2 特別図柄表示器 8b、普通図柄を可変表示する普通図柄表示器 10、第 1 特別図柄保留記憶表示器 18a、第 2 特別図柄保留記憶表示器 18b および普通図柄保留記憶表示器 41 の表示制御を行う。

#### 【0061】

なお、大当たり遊技状態の発生を示す大当たり情報等の情報出力信号をホールコンピュータ等の外部装置に対して出力する情報出力回路（図示せず）も主基板 31 に搭載されている。

#### 【0062】

この実施の形態では、演出制御基板 80 に搭載されている演出制御手段（演出制御用マイクロコンピュータで構成される。）が、中継基板 77 を介して遊技制御用マイクロコンピュータ 560 から演出内容を指示する演出制御コマンドを受信し、飾り図柄を可変表示する第 1 飾り図柄表示器 9a および第 2 飾り図柄表示器 9b と、演出図柄を可変表示する演出表示装置 9 との表示制御を行う。

#### 【0063】

また、演出制御基板 80 に搭載されている演出制御手段が、ランプドライバ基板 35 を介して、遊技盤に設けられている装飾 LED 25、および枠側に設けられている枠 LED 28 の表示制御を行うとともに、音声出力基板 70 を介してスピーカ 27 からの音出力の制御を行う。

#### 【0064】

図 4 は、中継基板 77、演出制御基板 80、ランプドライバ基板 35 および音声出力基板 70 の回路構成例を示すブロック図である。なお、図 4 に示す例では、ランプドライバ基板 35 および音声出力基板 70 には、マイクロコンピュータは搭載されていないが、マイクロコンピュータを搭載してもよい。また、ランプドライバ基板 35 および音声出力基板 70 を設げずに、演出制御に関して演出制御基板 80 のみを設けてもよい。

#### 【0065】

演出制御基板 80 は、演出制御用 CPU 101、および演出図柄プロセスフラグ等の演出に関する情報を記憶する RAM を含む演出制御用マイクロコンピュータ 100 を搭載している。なお、RAM は外付けであってもよい。この実施の形態では、演出制御用マイクロコンピュータ 100 における RAM は電源バックアップされていない。演出制御基板 80 において、演出制御用 CPU 101 は、内蔵または外付けの ROM（図示せず）に格納されたプログラムに従って動作し、中継基板 77 を介して入力される主基板 31 からの取込信号（演出制御 INT 信号）に応じて、入力ドライバ 102 および入力ポート 103 を介して演出制御コマンドを受信する。また、演出制御用 CPU 101 は、演出制御コマンドにもとづいて、VDP（ビデオディスプレイプロセッサ）109 に演出表示装置 9 の表示制御を行わせる。

#### 【0066】

この実施の形態では、演出制御用マイクロコンピュータ 100 と共に動作して演出表示装置 9 の表示制御を行う VDP 109 が演出制御基板 80 に搭載されている。VDP 109 は、演出制御用マイクロコンピュータ 100 とは独立したアドレス空間を有し、そこに VRAM をマッピングする。VRAM は、画像データを展開するためのバッファメモリである。そして、VDP 109 は、VRAM 内の画像データをフレームメモリを介して演出表示装置 9 に出力する。

#### 【0067】

演出制御用 CPU 101 は、受信した演出制御コマンドに従って CGROM（図示せず

10

20

30

40

50

) から必要なデータを読み出すための指令を V D P 1 0 9 に出力する。 C G R O M は、演出表示装置 9 に表示されるキャラクタ画像データや動画像データ、具体的には、人物、文字、図形や記号等(演出図柄を含む)、および背景画像のデータをあらかじめ格納しておくための R O M である。 V D P 1 0 9 は、演出制御用 C P U 1 0 1 の指令に応じて、 C G R O M から画像データを読み出す。そして、 V D P 1 0 9 は、読み出した画像データにもとづいて表示制御を実行する。

#### 【 0 0 6 8 】

演出制御コマンドおよび演出制御 I N T 信号は、演出制御基板 8 0 において、まず、入力ドライバ 1 0 2 に入力する。入力ドライバ 1 0 2 は、中継基板 7 7 から入力された信号を演出制御基板 8 0 の内部に向かう方向にしか通過させない(演出制御基板 8 0 の内部から中継基板 7 7 への方向には信号を通過させない)信号方向規制手段としての単方向性回路もある。

10

#### 【 0 0 6 9 】

中継基板 7 7 には、主基板 3 1 から入力された信号を演出制御基板 8 0 に向かう方向にしか通過させない(演出制御基板 8 0 から中継基板 7 7 への方向には信号を通過させない)信号方向規制手段としての単方向性回路 7 4 が搭載されている。単方向性回路として、例えばダイオードやトランジスタが使用される。図 4 には、ダイオードが例示されている。また、単方向性回路は、各信号毎に設けられる。さらに、単方向性回路である出力ポート 5 7 1 を介して主基板 3 1 から演出制御コマンドおよび演出制御 I N T 信号が出力されるので、中継基板 7 7 から主基板 3 1 の内部に向かう信号が規制される。すなわち、中継基板 7 7 からの信号は主基板 3 1 の内部(遊技制御用マイクロコンピュータ 5 6 0 側)に入り込まない。なお、出力ポート 5 7 1 は、図 3 に示された I / O ポート部 5 7 の一部である。また、出力ポート 5 7 1 の外側(中継基板 7 7 側)に、さらに、単方向性回路である信号ドライバ回路が設けられていてもよい。

20

#### 【 0 0 7 0 】

また、演出制御用 C P U 1 0 1 は、出力ポート 1 0 6 を介して、可動部材 7 8 を動作させるためにモータ 8 6 を駆動する。また、上演出 L E D 8 5 a 、中演出 L E D 8 5 b および下演出 L E D 8 5 c の近傍に設けられ各 L E D の取付部分を信号させる振動モータ 8 7 a , 8 7 b , 8 7 c を出力ポート 1 0 6 を介して駆動する。なお、振動モータ 8 7 a は上演出 L E D 8 5 a を振動させ、振動モータ 8 7 b は中演出 L E D 8 5 b を振動させ、振動モータ 8 7 c は下演出 L E D 8 5 c を振動させる。

30

#### 【 0 0 7 1 】

また、演出制御用 C P U 1 0 1 は、出力ポート 1 0 5 を介してランプドライバ基板 3 5 に対して L E D を駆動する信号を出力する。また、演出制御用 C P U 1 0 1 は、出力ポート 1 0 4 を介して音声出力基板 7 0 に対して音番号データを出力する。

30

#### 【 0 0 7 2 】

さらに、演出制御用マイクロコンピュータ 1 0 0 には、ハードウェア乱数(ハードウェア回路が発生する乱数)を発生する乱数回路 1 0 7 が内蔵されている。乱数回路 1 0 7 は、初期値(例えば、0)と上限値(例えば、6 5 5 3 5)とが設定された数値範囲内で、数値データを、設定された更新規則に従って更新する。この実施の形態では、演出制御用マイクロコンピュータ 1 0 0 は、乱数回路 1 0 7 が発生する乱数値にもとづいて加算値を決定し、決定した加算値を加算することによって、所定の演出内容(例えば、演出図柄の最終停止図柄)を決定するための演出決定用乱数(具体的には、図 6 6 に示す乱数 S R 1 - 1 ~ S R 1 - 3 )を更新する処理を行う。

40

#### 【 0 0 7 3 】

ランプドライバ基板 3 5 において、 L E D を駆動する信号は、入力ドライバ 3 5 1 を介して L E D ドライバ 3 5 2 に入力される。 L E D ドライバ 3 5 2 は、 L E D を駆動する信号にもとづいて枠 L E D 2 8 などの枠側に設けられている発光体に電流を供給する。また、遊技盤側に設けられている装飾 L E D 2 5 、上演出 L E D 8 5 a 、中演出 L E D 8 5 b および下演出 L E D 8 5 c に電流を供給する。

50

## 【0074】

音声出力基板70において、音番号データは、入力ドライバ702を介して音声合成用IC703に入力される。音声合成用IC703は、音番号データに応じた音声や効果音を発生し增幅回路705に出力する。增幅回路705は、音声合成用IC703の出力レベルを、ボリューム706で設定されている音量に応じたレベルに増幅した音声信号をスピーカ27に出力する。音声データROM704には、音番号データに応じた制御データが格納されている。音番号データに応じた制御データは、所定期間（例えば演出図柄の変動期間）における効果音または音声の出力態様を時系列的に示すデータの集まりである。

## 【0075】

次に、電源基板910の構成を図5のブロック図を参照して説明する。電源基板910には、遊技機内の各電気部品制御基板や機構部品への電力供給を許可したり遮断したりするための電源スイッチ914が設けられている。なお、電源スイッチ914は、遊技機において、電源基板910の外に設けられてもよい。電源スイッチ914が閉状態（オン状態）では、交流電源（AC24V）がトランス911の入力側（一次側）に印加される。トランス911は、交流電源（AC24V）と電源基板910の内部とを電気的に絶縁するためのものであるが、その出力電圧もAC24Vである。また、トランス911の入力側には、過電圧保護回路としてのバリスタ918が設置されている。

10

## 【0076】

電源基板910は、電気部品制御基板（主基板31、払出制御基板37および演出制御基板80等）と独立して設置され、遊技機内の各基板および機構部品が使用する電圧を生成する。この例では、AC24V、VSL（DC+30V）、VLP（DC+24V）、VDD（DC+12V）およびVCC（DC+5V）を生成する。また、バックアップ電源（VBB）すなわちバックアップRAMに記憶内容を保持させるための記憶保持手段となるコンデンサ916は、DC+5V（VCC）すなわち各基板上のIC等を駆動する電源のラインから充電される。また、+5Vラインとバックアップ+5V（VBB）ラインとの間に、逆流防止用のダイオード917が挿入される。なお、VSLは、整流平滑回路915において、整流素子でAC24Vを整流昇圧することによって生成される。VSLは、ソレノイド駆動電源になる。また、VLPは、ランプ点灯用の電圧であって、整流回路912において、整流素子でAC24Vを整流することによって生成される。

20

## 【0077】

電源電圧生成手段としてのDC-DCコンバータ913は、1つまたは複数のスイッチングレギュレータ（図5では2つのレギュレータIC924A，924Bを示す。）を有し、VSLにもとづいてVDDおよびVCCを生成する。レギュレータIC（スイッチングレギュレータ）924A，924Bの入力側には、比較的大容量のコンデンサ923A，923Bが接続されている。従って、外部からの遊技機に対する電力供給が停止したときに、VSL、VDD、VCC等の直流電圧は、比較的緩やかに低下する。

30

## 【0078】

図5に示すように、トランス911から出力されたAC24Vは、そのままコネクタ922Bに供給される。また、VLPは、コネクタ922Cに供給される。VCC、VDDおよびVSLは、コネクタ922A，922B，922Cに供給される。

40

## 【0079】

コネクタ922Aに接続されるケーブルは、主基板31に接続される。また、コネクタ922Bに接続されるケーブルは、払出制御基板37に接続される。従って、コネクタ922Aには、VBBも供給されている。例えば、コネクタ922Cに接続されるケーブルは、ランプドライバ基板35に接続される。なお、演出制御基板80には、ランプドライバ基板35を経由して各電圧が供給される。

## 【0080】

また、電源基板910には、押しボタン構造のクリアスイッチ921が搭載されている。クリアスイッチ921が押下されるとローレベル（オン状態）のクリア信号が出力され、コネクタ922Aを介して主基板31に出力される。また、クリアスイッチ921が押

50

下されていなければハイレベル（オフ状態）の信号が出力される。なお、クリアスイッチ921は、押しボタン構造以外の他の構成であってもよい。また、クリアスイッチ921は、遊技機において、電源基板910以外に設けられていてもよい。

#### 【0081】

さらに、電源基板910には、電気部品制御基板に搭載されているマイクロコンピュータに対するリセット信号を作成するとともに、電源断信号を出力する電源監視回路920と、電源監視回路920からのリセット信号を増幅してコネクタ922A，922B，922Cに出力するとともに、電源断信号を増幅してコネクタ922Bに出力する出力ドライバ回路925が搭載されている。なお、演出制御用マイクロコンピュータに対するリセット信号は、ランプドライバ基板35を経由して演出制御基板80に伝達される。また、リセット回路をそれぞれの電気部品制御基板に搭載した場合に、リセット信号をハイレベルにすることになる電圧値を異ならせるようにしてもよい（例えば、主基板31における場合を最も高くして、遊技制御用マイクロコンピュータ560に対するリセット信号がハイレベルになるタイミングを最も遅くする。）。

10

#### 【0082】

電源監視回路920からの電源断信号すなわち電源監視手段からの検出信号は、主基板31に搭載されている入力ポートを介して遊技制御用マイクロコンピュータ560に入力される。すなわち、遊技制御用マイクロコンピュータ560は、入力ポートの入力信号を監視することによって遊技機への電力供給の停止の発生を確認することができる。

20

#### 【0083】

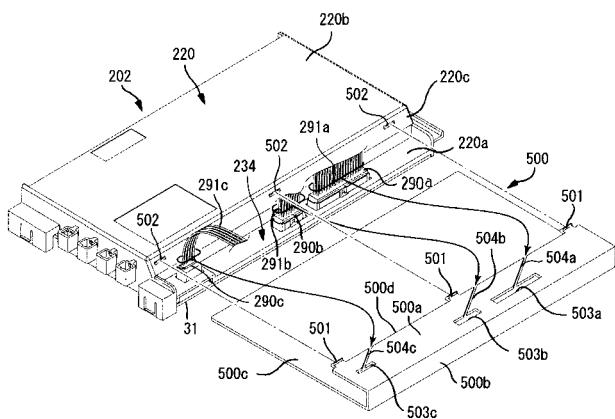

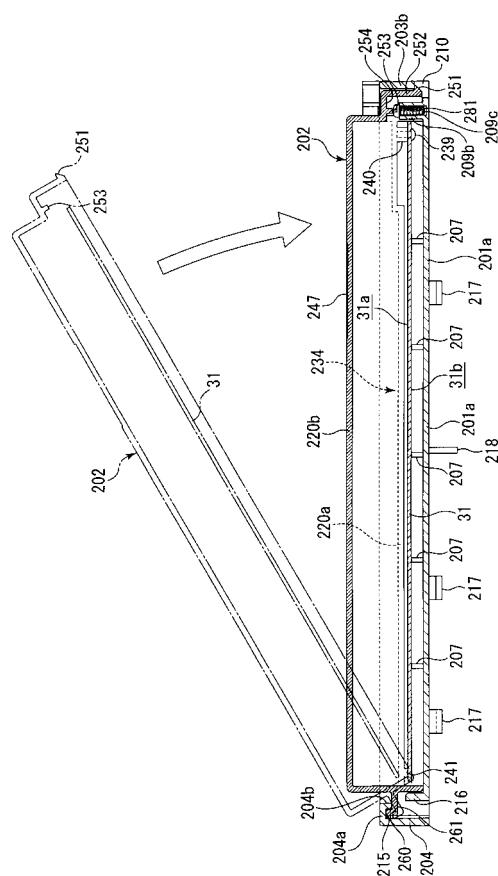

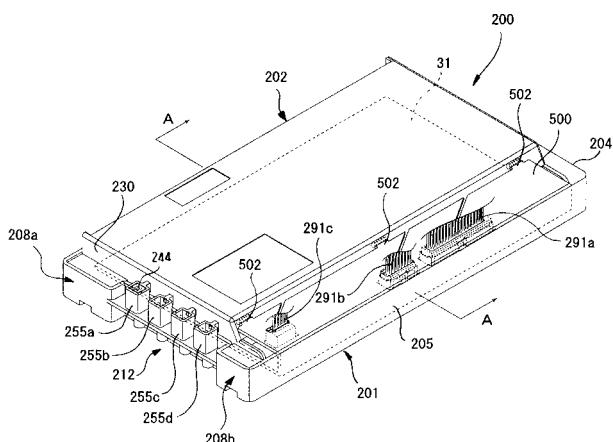

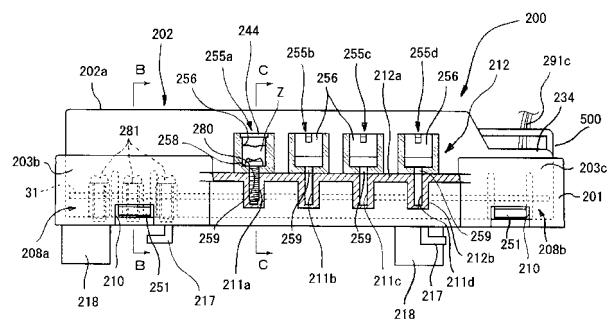

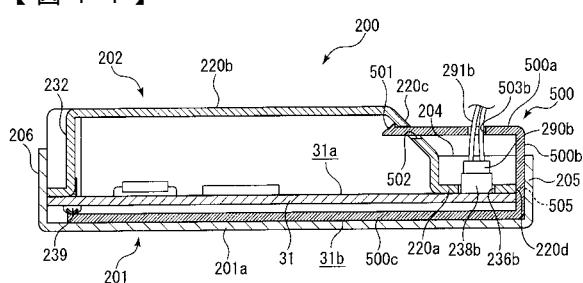

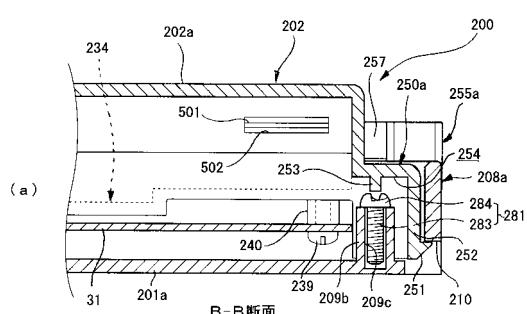

次に、主基板31を収納する基板収納ケース200の構造を説明する。図6は、基板収納ケースを示す分解斜視図であり、図7は、基板収納ケースを示す分解斜視図であるが、2回目に基板収納ケース200の封止がなされる場合の例を示す。図8は、基板収納ケース200および主基板31の組み付け状態を示す分解斜視図である。図9は、ケースカバー202に対する主基板31の取り付け状態を示す斜視図である。図10は、配線側コネクタの接続状況を示す斜視図である。図11は、コネクタ規制部材の取り付け状況を示す斜視図である。図12は、ケース本体201とケースカバー202とを閉鎖した状態を示す縦断面図である。図13は、基板収納ケース200の封止状態を示す斜視図である。図14は、図13に示す基板収納ケース200のA-A断面を示す断面図である。図15は、基板収納ケース200を示す一部破断側面図である。図16(a)は、図15に示す基板収納ケース200のB-B断面を示す断面図である。図16(b)は、図15に示す基板収納ケース200のC-C断面を示す断面図である。なお、図2に示したように、この実施の形態では、主基板31には遊技開始スイッチ90が設けられているのであるが、図6～図16に示す主基板31を収納する基板収納ケース200では、遊技開始スイッチ90の図示を省略している。

30

#### 【0084】

基板収納ケース200は、図6に示すように、主基板31の裏面側を覆うケース本体201と、主基板31の実装面31a（図12参照）側を覆うケースカバー202とを含み、主基板31を挟持するように組み付けられる。なお、主基板31の実装面31aには、遊技制御用マイクロコンピュータ560等の電子部品や、他の基板から延出された配線の一端に設けられた配線側コネクタ等が接続される基板側コネクタ238a～238c等が実装されている。なお、この実施の形態では、3つの基板側コネクタ238a～238cが例示されているが、実装されるコネクタの数は任意であり、実際には3つ以上のコネクタが実装されることがある。

40

#### 【0085】

また、基板収納ケース200は、ケースカバー202の外側に装着され、基板側コネクタ238a～238cに接続される配線側コネクタ（ハーネス側コネクタ）290a～290cの抜脱を防止するためのコネクタ規制部材500を備えている。なお、主基板31は、ケースカバー202の裏面側に取り付けられた状態で基板収納ケース200の内部に封止状態で収納される。

50

## 【0086】

ケース本体201は、透明な合成樹脂からなり、略長方形状に形成される底板201aと、底板201aの周囲を囲むように形成された側壁203～206とで、上面が開放する直方体状に成形されている。側壁205, 206の内面には、図13に示す封止状態(閉鎖状態)において主基板31の裏面周囲を支持する上下方向を向く支持リブ207が複数形成されている。また、側壁203および閉塞壁216の内面における長手方向の中央位置には、ケースカバー202を位置決めするための上下方向を向く位置決め用リブ270が形成されている。

## 【0087】

一方の短辺の側壁203は、図6に示すように、長手方向の略中央に位置する中央側壁203aと、中央側壁203aの左右側方に位置する膨出壁203b, 203cと、中央側壁203aと膨出壁203b, 203cとを連接する連接壁203dとで、略凹状に形成されている。つまり、膨出壁203b, 203cと連接壁203dとで、中央側壁203aの長手方向の左右側に、本体内部側から外側に向けて膨出する略長方形状の膨出部208a, 208bが形成されている。

## 【0088】

膨出部208a, 208bの内部は、ケース本体201の内部に形成される略長方形状の基板収納空間S1にそれぞれ連通する膨出空間S2, S3が形成されている。つまり、内部が中空状に構成されている。一方の膨出部208aの膨出空間S2内には、複数(この実施の形態では3本)の予備用ワンウェイねじ281を収納するねじ収納部209が設けられている。

## 【0089】

ねじ収納部209は、ケース本体201の底板201aから立設される側壁203よりも若干低い板状部209aと、板状部209aの長手方向に向けて所定間隔おきに形成される複数の筒状部209bとで構成される。各筒状部209bには、予備用ワンウェイねじ281のねじ部の直径よりも若干大径で、かつ、頭部の直径よりも小径の所定深さの挿入孔209cが形成されている。挿入孔209cには、上面開口から予備用ワンウェイねじ281を挿通して収納できる(図16(a)参照)。

## 【0090】

板状部209aは、長手方向の両端が、それぞれ側壁206および連接壁203dの内面に連設されている。また、板状部209aは、膨出壁203bに対して平行に、基板収納空間S1と膨出空間S2とを区画するように配設されている。また、膨出壁203b, 203cの下部には、ケースカバー202の係止爪251を係止可能な係止穴210がそれぞれ形成されている(図16(a)参照)。

## 【0091】

予備用ワンウェイねじ281は、一方向の回転によってねじ止めされる。しかし、他方向に回転させようとしても回転させることができない、すなわち、そのねじを緩めることができない機能を有するねじである。具体的には、外周に雄ねじ部が形成されたねじ部283と、ねじ部283の上端に設けられる頭部284とで構成され、ねじ部283の直径よりも頭部284の直径の方が大径になっている(図16(a)参照)。なお、ワンウェイねじ280も予備用ワンウェイねじ281と同様に構成されている。ただし、最初に固着に用いられるワンウェイねじ280の色は、予備用ワンウェイねじ281の色とは異なっている。

## 【0092】

中央側壁203aの外側には、ワンウェイねじ280がねじ止めされる複数(この実施の形態では4つ)のねじ穴211a～211dが形成される第2被固着部212が形成されている。被固着部212は、図6および図15に示すように、中央側壁203aの外側における両連接壁203d, 203d間に架設されるとともに、ねじ穴211a～211dが長手方向に向けて所定間隔おきに形成された固着片212aと、固着片212aの下面における各ねじ穴211a～211dに対応する箇所から垂下される筒状部212bと

10

20

30

40

50

で構成され、ねじ穴 211a～211d は、固着片 212a から筒状部 212b にかけて所定深さに形成されている。

#### 【0093】

固着片 212a は、側壁 203 に連設されている。固着片 212a における 3 辺が、側壁 203 における中央側壁 203a および両連接壁 203d に接している。また、固着片 212a における中央側壁 203a の反対側の長辺が、膨出壁 203b, 203d と同じ平面上にくるように形成されている。つまり、両サイドの膨出部 208a, 208b よりも外側に突出しないように形成されている。よって、誤ってケース本体 201 を落下した場合でも、第 2 被固着部 212 が両サイドの膨出部 208a, 208b によって保護されて損傷しない。

10

#### 【0094】

他方の短寸の側壁 204 には、図 6 および図 12 に示すように、その上端から内向きに連設される内向片 204a と、内向片 204a の先端から下方に垂れ下がるように形成されている垂下片 204b とが連設されている。側壁 204、内向片 204a および垂下片 204b の内面によって、ケースカバー 202 の回動枢支片を係止する下向きに開口する被係止凹部 215（図 12 参照）が長手方向に向けて形成されている。

#### 【0095】

また、図 12 に示すように、底板 201a における被係止凹部 215 の下方には開口が形成されている。そして、開口端縁部から、側壁 204 よりも高さが低い閉塞壁 216 が立ち上がるよう設けられ、封止状態においてケースカバー 202 の側壁下端と底板 201a の上面との間が外側から被覆される。

20

#### 【0096】

底板 201a の下面には、ケース本体 201 をパチンコ遊技機 1 に設けられる基板収納ケース取付板（図示せず）に取り付ける際に、基板収納ケース取付板に係止可能な複数の取付板用係止爪 217 と、取り付けの際ににおける位置決め用の位置決め片 218 とが突出するよう設けられている。

30

#### 【0097】

ケースカバー 202 は、透明な合成樹脂で形成され、図 6 および図 7 に示すように、略長方形状に形成される上板 220 と、上板 220 の周縁辺のうちの 3 つの縁辺を囲むように形成された側壁 230～232 とによって下面が開放する直方体状に形成されている。上板 220 における 2 つの長辺のうち一方側は、長手方向に向けて下方に凹設され、上板 220 の一部に所定幅を有する帯状の凹部 234 が形成されている。

#### 【0098】

具体的には、上板 220 は、図 8 および図 14 に示すように、実装面 31a との対向面（裏面）が実装面 31 にほぼ当接する位置に設けられている低被覆面部 220a と、低被覆面部 220a よりも実装面 31a から離間した位置に設けられる高被覆面部 220b と、低被覆面部 220a と高被覆面部 220b とを連設する傾斜被覆面部 220c とで構成され、低被覆面部 220a および傾斜被覆面部 220c によって凹部 234 が形成されている。

30

#### 【0099】

低被覆面部 220a は、図 8 に示すように、平面視略長方形状に形成された主基板 31 の実装面 31a における一方の長辺に沿うように形成された帯状のコネクタ実装領域 S10（図 8 において斜線で示される領域）を被覆するとともに、コネクタ実装領域 S10 に実装された複数の基板側コネクタ 238a～238c の接続口 238d および本体上部を通してケースカバー 202 の外部に通過させるためのコネクタ用開口 236a～236c が形成されている。

40

#### 【0100】

また、低被覆面部 220a の裏面は、主基板 31 が取り付けられた状態で、図 14 に示すように主基板 31 の実装面 31a にほぼ当接する。なお、各コネクタ用開口 236a～236c において、開口端縁と各種コネクタ 238a～238c の本体側面との間から針

50

金等の異物や配線等が容易に入れないように、開口端縁と各種コネクタ 238a～238c の本体側面との間は、例えば約 1mm 以内の隙間になるように形成されている。

#### 【0101】

高被覆面部 220b は、主基板 31 の実装面 31a におけるコネクタ実装領域 S10 以外のメイン部品実装領域（図中斜線で示される領域以外の領域）すなわち遊技制御用マイクロコンピュータ 560 等の電子部品や各種回路等が実装される領域の上方を被覆するために、低被覆面部 220a よりも高い位置、つまり低被覆面部 220a に比べて実装面 31a から離れた位置に配置される。

#### 【0102】

傾斜被覆面部 220c は、高被覆面部 220b の一側縁から低被覆面部 220a の一側縁に向けて下方に傾斜するように設けられている。高被覆面部 220b 側の上部には、コネクタ規制部材 500 に形成された複数の係止爪 501 が係合される複数の係合穴 502 が長手方向に向けて所定間隔おきに形成されている。

10

#### 【0103】

上板 220 の裏面四隅には、図 9 に示すように、主基板 31 を取り付けるための基板取付ねじ 239 が取り付けられるねじ穴 240a を有する取付用支柱 240 が一方の対角線上に 2 つ突出するように設けられている（図 9 では、一方のみを示す）。また、取り付けの際の位置決め用の位置決め用凸部（図示せず）が他方の対角線上に 2 つ突出するように設けられ、ケースカバー 202 の裏面側に主基板 31 を取り付けできるようになっている。

。

20

#### 【0104】

主基板 31 を取り付けるときには、主基板 31 の実装面 31a をケースカバー 202 の裏面に対向させた状態、つまり実装面 31a を上方に向かた状態でケースカバー 202 の裏面側に主基板 31 を押し当てる。そして、各コネクタ用開口 236a～236c から各コネクタ 238a～238c が通過するように、主基板 31 における位置決め用凸部に対応する 2 つの角部に形成された位置決め孔 243 をそれぞれ位置決め用凸部内に挿通して位置決めした状態で、主基板 31 の取付用支柱 240 に対応する 2 つの角部に形成されたねじ取付孔 242 に基板取付ねじ 239 を取り付け、ねじ穴 240a に基板取付ねじ 239 をねじ止めする。

#### 【0105】

ケースカバー 202 に主基板 31 を取り付けた状態において、上板 220 における低被覆面 220a の裏面と実装面 31a とが対向してほぼ当接した状態になる（図 14 参照）。よって、各コネクタ用開口 236a～236c の開口端縁と各種コネクタ 238a～238c の本体側面との間から針金等の異物や配線等を差し込んでも、遊技制御用マイクロコンピュータ等が実装されている主基板 31 の中央部に向けて進入することが困難であり、不正行為が効果的に防止される。

30

#### 【0106】

また、高被覆面 220b の裏面所定箇所には、ワンウェイねじ 280 の頭部 284 を被覆するキャップ 265 が複数繋げられたキャップ吊支体 245（図 6 および図 7 参照）を保持する四角柱状のキャップ保持部（図示せず）が下向きに設けられている。キャップ吊支体 245 におけるキャップ 265 は、予備用ワンウェイねじ 281 の頭部 284 を被覆するものであり、予備用ワンウェイねじ 281 の合計数（3 個）のキャップを有している。

。

40

#### 【0107】

図 7 に示すように、キャップ 265 には下端に係止爪 267 が形成された一対の係止片 268 が設けられている。係止爪 267 を被固着部 255b～255d の内面に形成された段部 266 に係止することによって、キャップ 265 は、被固着部 255b～255d の上面開口を閉塞するように保持される。係止爪 267 は、被固着部 255b～255d の内部に設けられている段部 266 に嵌り込んでキャップ 265 の引き抜きを防止するためのものである。

50

## 【0108】

上板220の上面には、図6および図7に示すように、パチンコ遊技機1の機種名を記した機種名シール(図示せず)を貼着するための機種名表示用凹部247と、主基板31を検査した際に書き込む「検査者」や「検査日」等の各項目が記された検査履歴シール(図示せず)を貼着するための検査名表示用凹部248が設けられている。

## 【0109】

側壁230におけるケース本体201側の膨出部208a, 208bに対応する箇所には、膨出部208a, 208bよりも一回り小さい膨出部カバー250a, 250bが外側に向けて膨出するように形成されている。膨出部カバー250a, 250bは、封止状態において膨出部208a, 208bを構成する膨出壁203b, 203cおよび連接壁203dよりも内側に入り込み、膨出空間S2, S3の上方を閉塞する。10

## 【0110】

膨出部カバー250a, 250bは、内部が中空状に形成され、一方の膨出部カバー250bの内部空間は、側壁230によりケースカバー202における基板収納空間と区画されて独立した空間となっている。他方の膨出部カバー250aの内部空間は、側壁230における膨出部カバー250aに対応する箇所が切り欠かれ、ケースカバー202の基板収納空間と連通する(図16(a)参照)。

## 【0111】

膨出部カバー250a, 250bにおける膨出部208a, 208bに形成された係止穴210に対応する壁部には、下端から上方に向けて切り欠かれた2本のスリットを介して弾性変形自在に構成された係止片252が形成されている。係止片252の下端には、係止穴210に係止可能な外向きの係止爪251が形成され、ケース本体201の上面をケースカバー202により閉鎖した状態、つまり封止状態において係止爪251が係止穴210に係止される。20

## 【0112】

また、図16(a)に示すように、ねじ収納部209に対応する膨出部カバー250aの上壁裏面254には、膨出部カバー250aの長手方向に向けて延びるねじ規制用リブ253が下方に向かって設けられている(図6参照)。具体的には、ねじ規制用リブ253は、ケース本体201の上面をケースカバー202により閉鎖した状態、つまり封止状態において、ねじ収納部209の板状部209aの直上に板状部209aと平行になるように配置されるように、膨出部カバー250aの上壁裏面254における板状部209aとの対向位置から下方に向かって設けられている。つまり、上壁裏面254における挿入孔209cの上面開口との対向位置から、挿入孔209cの上面開口に向けて所定長さ延設されている。具体的には、その下端が挿入孔209c内に挿入された各予備用ワンウェイねじ281の頭部284に近接する長さを有している。30

## 【0113】

封止状態において、膨出部カバー250aの上壁裏面254から下方に向けて延設されたねじ規制用リブ253によって、ねじ収納部209内に収納された予備用ワンウェイねじ281のねじ収納部209からの逸脱が防止される。すなわち、ねじ収納部209から予備用ワンウェイねじ281が逸脱して基板収納空間S1内に入り込み、基板を損傷させてしまうこと等が確実に防止される。40

## 【0114】

図6に示すように、側壁203における両膨出部カバー250a, 250bの間には、複数(この実施の形態では4つ)の四角筒状の被固着部255a~255dが、ケース本体201の各ねじ穴211a~211dに対応する箇所に複数形成されている。それらの固着部によって第1被固着部255が構成されている。

## 【0115】

各被固着部255a~255dは、図15および図16(b)に示すように、ワンウェイねじ280および予備用ワンウェイねじ281を挿通可能な四角柱状のねじ挿入部256と、ねじ挿入部256と側壁230とを連接する連接部(ケースカバー202の一部)50

257とで構成されている。そして、連接部257を介してねじ挿入部256が側壁230から所定距離離した状態で配置されている。よって、連接部257をニッパ等の工具で切断できる。また、連接部257は、ケースカバー202の一側縁である側壁230の外面から外方に向けて複数設けられ、各連接部257の先端に被接着部255a～255dが設けられている。

#### 【0116】

ねじ挿入部256は、上面が開口する有底の筒体であり、内部にワンウェイねじ280を収納可能な大きさを有しているとともに、底板258には、ワンウェイねじ280の頭部284の直径よりも小径の取付孔259が形成されている。取付孔259は、封止状態において、各ねじ穴211a～211dの対向位置に配置される。10

#### 【0117】

図6および図12に示すように、ケース本体201側の被係止凹部215が形成されている側壁204に対応する側壁231には、先端に被係止凹部215に係止可能な上向きの係止条260が長手方向に設けられた係止片261が、外方に向けて設けられている。

#### 【0118】

このように構成されたケース本体201およびケースカバー202は、ケース本体201の上面開口がケースカバー202で塞がれた状態において、ケース本体201の側壁205の内面と、ケースカバー202の低被覆面部220aにおける側壁205の内面との対向辺である長辺220d(図10参照)端面との間に、垂直板500bを挿通可能な間隙部505が、側壁205の内面に沿って形成される(図14参照)。20

#### 【0119】

次に、コネクタ規制部材500の構造について説明する。コネクタ規制部材500は、透明な合成樹脂材からなる板部材で形成され、図11に示すように、ケースカバー202の外側に装着可能に構成されている。板材の幅寸法は、ケースカバー202の長辺202dにおける長手方向の幅寸法よりも若干短い。コネクタ規制部材500は、装着時においてケースカバー202における低被覆面220aよりも若干大きめに形成される上板500aと、上板500aの外端から下方に向て設けられる垂直板500bと、垂直板500bの下端から上板500aと平行になるように同方向に設けられる下板500cとで、略コ字形に形成されている。

#### 【0120】

上板500aにおける長辺500dには、複数の係合穴502のそれぞれに差し込み可能に、かつ、弾性変形可能に構成される。また、先端に上向きの係止爪501が形成された係止片が上板500aとほぼ平行になるように突出して設けられ、係止片を係合穴502からケースカバー202内に通した状態において、ケースカバー202の裏面における係合穴502の上縁に係止爪501が係止されるように形成されている。30

#### 【0121】

上板500aには、各配線側コネクタ290a～290cから延びる配線291a～291cを通過させることができ細長長方形形状の配線挿通用開口503a～503cが長手方向に向けて形成されている。各配線挿通用開口503a～503cから長辺500dに向けて、各配線291a～291cを通すことが可能な配線挿通用スリット504a～504cが設けられている。40

#### 【0122】

各配線291a～291cは、いわゆるフラットケーブルである。よって、配線挿通用開口503a～503cおよび配線挿通用スリット504a～504cは、横長長方形形状に形成されている。すなわち、配線挿通用開口503a～503cは、長辺および短辺が、配線側コネクタ290a～290c本体の長辺および短辺よりも短く形成され、配線側コネクタ290a～290cを通過させることは不可能であり、かつ、配線291a～291cを通過させることができ可能に形成されている。また、配線挿通用スリット504a～504cは、配線291a～291cを配線挿通用スリット504a～504cに対して平行にした状態で長辺500d側から差し込み可能な幅寸法に形成されている。50

## 【0123】

よって、各配線 291a～291c を、長辺 500d 側から配線挿通用スリット 504a～504c 内に差し込んで配線挿通用開口 503a～503c まで引き込むことによって、配線挿通用開口 503a～503c 内に配置することができる。

## 【0124】

また、これら配線挿通用スリット 504a～504c は、配線挿通用開口 503a～503c の開口長縁辺に対して傾斜するように、かつ、互いに平行に形成されているとともに、開口長縁辺における長手方向の中央位置から長辺 500d 側に向けて斜めに延設されている。これにより、配線挿通用スリット 504a～504c を介して引き込んだ配線 291a～291c を、配線挿通用開口 503a～503c 内に斜めに進入させることができたため、配線挿通用開口 503a～503c 内にスムーズに進入させることができる。10

## 【0125】

また、開口長縁辺の長手方向の中央位置から配線挿通用スリット 504a～504c が設けられているので、配線挿通用開口 503a～503c 内に配線 291a～291c を配置した状態において、配線 291a～291c の列方向の両端が配線挿通用スリット 504a～504c との連接部から離れ、配線 291a～291c が配線挿通用スリット 504a～504c 内に逆戻りすることがない。すなわち、配線挿通用スリット 504a～504c の幅は、配線挿通用開口 503a～503c の一辺よりも狭い。

## 【0126】

下板 500c は、垂直板 500b の下端から上板 500a と同方向に向けて設けられ、その幅は、主基板 31 の短辺の幅寸法よりも若干短い。つまり、主基板 31 の裏面 31b（実装面 31a の反対面）ほぼ全域を被覆可能な長さである（図 14 参照）。20

## 【0127】

このように形成されたコネクタ規制部材 500 は、基板側コネクタ 238a～238c に接続された配線側コネクタ 290a～290c からの各配線 291a～291c を、配線挿通用スリット 504a～504c を介して配線挿通用開口 503a～503c 内を通過させた後、ケースカバー 202 に対して側方から近接させ、係止爪 501 を係合穴 502 に差し込んで一端をケースカバー 202 に係止させることによって、ケースカバー 202 に対して仮止めすることができる。

## 【0128】

この状態において、上板 500a により低被覆面部 220a の上方および外側方が上板 500a および垂直板 500b により被覆されるとともに、主基板 31 の裏面 31b が下板 500c により被覆される。30

## 【0129】

次に、このように構成されたケース本体 201 とケースカバー 202 とで、主基板 31 を内部に収納して封止状態とするとともに、コネクタ規制部材 500 により配線側コネクタ 290a～290c を抜くことを規制する状況を説明する。

## 【0130】

主基板 31 を封止状態で収納するときには、まず、ケースカバー 202 の裏面に設けられたキャップ保持部（図示せず）に、キャップ吊支体 245 を取り付けた後、主基板 31 をケースカバー 202 の裏面側に取り付ける。具体的には、図 9 に示すように、主基板 31 の実装面 31a をケースカバー 202 の裏面に対向させた状態、つまり実装面 31a を上方に向かた状態でケースカバー 202 の裏面側に押し当てる。そして、各コネクタ用開口 236a～236c に各基板側コネクタ 238a～238c が通るように、主基板 31 における位置決め用凸部 241 に対応する 2 つの角部に形成された位置決め孔 243 をそれぞれ位置決め用凸部 241 内に通して位置決めした状態で、主基板 31 の取付用支柱 240 に対応する 2 つの角部に形成されたねじ取付孔 242 に基板取付ねじ 239 を取り付け、ねじ穴 240a に基板取付ねじ 239 をねじ止めする。40

## 【0131】

図 10 に示すように、主基板 31 をケースカバー 202 の裏面側に取り付けた状態にお

いて、各コネクタ用開口 236a～236c から、各基板側コネクタ 238a～238c 本体上部がケースカバー 202 の外部に露出される。つまり、各基板側コネクタ 238a～238c の本体上面に形成された接続口 238d がケースカバー 202 の外部に上向きに開放されるため、ケースカバー 202 に配線側コネクタ 290a～290c を通すことなく、各基板側コネクタ 238a～238c の接続口 238d に各配線側コネクタ 290a～290c を差し込んで接続することができる。

#### 【0132】

次いで、図 11 に示すように、各基板側コネクタ 238a～238c に接続された各配線側コネクタ 290a～290c からの各配線 291a～291c を、長辺 500d 側から配線挿通用スリット 504a～504c 内に差し込み、配線挿通用開口 503a～503c 内を通した後、ケースカバー 202 に対して側方から近接させ、係止爪 501 を係合穴 502 に差し込んで一端をケースカバー 202 に係止させることによって、ケースカバー 202 に対して仮止めする。

#### 【0133】

このように、各基板側コネクタ 238a～238c に各配線 291a～291c の配線側コネクタ 290a～290c を接続した状態で、各配線 291a～291c を配線挿通用開口 503a～503c に簡単に通すことができる。また、配線 291a～291c における配線側コネクタ 290a～290c とは反対側の端部に設けられる配線側コネクタ（図示せず）等を、配線挿通用開口 503a～503c を通過させる必要がない上に、例えば、配線 291a～291c における配線側コネクタ 290a～290c とは反対側の端部が図示しない他の基板に対してコネクタ等を介さずに直接接続されている場合であっても、配線側コネクタ 290a～290c を配線挿通用開口 503a～503c を通過させる必要がなく、上板 500a に大きな開口を形成しなくて済む。よって、コネクタ規制部材 500 の強度低下が防止される。

#### 【0134】

ケース本体 201において、図 8 に示すように、ねじ収納部 209 の挿入孔 209c（図 16（a）参照）内に、予備用ワンウェイねじ 281 を収納しておく。このとき、各挿入孔 209c の上面開口の上方からねじ部 283 を挿入孔 209c 内に通すだけで、簡単に収納することができる。この収納状態において、ねじ部 283 は挿入孔 209c 内に完全に収納され、頭部 284 のみが挿入孔 209c の上面開口から外部に突出された状態で保持されている（図 16（a）参照）。よって、収納された予備用ワンウェイねじ 281 を使用する際に、頭部 284 を手で摘むだけで簡単に取り出すことができる。

#### 【0135】

次いで、主基板 31 が一体的に取り付けられるとともに、コネクタ規制部材 500 が外側に仮止めされたケースカバー 202 で、ケース本体 201 の上面開口を閉鎖する。具体的には、図 12 に示すように、ケースカバー 202 の一方の短辺から外方に向けて突設された係止片 260 が下を向くようにケースカバー 202 を傾斜させた状態、すなわち、主基板 31 の裏面 31b をケース本体 201 に対向させた状態で、ケース本体 201 における閉塞壁 216 の上端と垂下片 204b の下端との間に係止片 260 を差し込む。そして、係止条 260 を被係止凹部 215 内に係止させた状態で、係止部を中心としてケースカバー 202 を図中矢印方向に向けて向けて回転させ、ケースカバー 202 をケース本体 201 の側壁 203～206 により囲まれた空間内に嵌め込む。

#### 【0136】

ケース本体 201 の膨出部 208a, 208b の膨出空間 S2, S3 内に膨出部カバー 250a, 250b が嵌め込まれて、両係止爪 251 がそれぞれ係止穴 210 の開口上端縁に係止される。その結果、ケースカバー 202 の一方の短辺側が係止条 260 と被係止凹部 215 とにより係止されるとともに、他方の短辺側が係止爪 251 と係止孔 251 とにより係止され、ケースカバー 202 がケース本体 201 に対して仮止めされる。なお、この状態では、係止穴 210 の外方からそれぞれの係止爪 251 を内側に向けて押し込んで係止状態を解除すれば、ケースカバー 202 を簡単に開放させることができる。

10

20

30

40

50

## 【0137】

この状態において、膨出部カバー250aの上壁裏面254から下方に向かって設けられているねじ規制用リブ253の下端が、ねじ収納部209に収納された3本の予備用ワンウェイねじ281の頭部284に近接した状態で配置される。従って、予備用ワンウェイねじ281がねじ収納部209から逸脱して基板収納空間S1内に入り込み、主基板31の配線パターン等を傷つけて断線させてしまうこと等が防止される。

## 【0138】

また、ケースカバー202の各側壁230～233の下端が、ケース本体201の側壁203～206の上端よりも下方に深く入り込んだ状態になるので、ケース本体201とケースカバー202との間から針金等の異物を進入しにくくなる。

10

## 【0139】

また、ねじ収納部209は、膨出部208aの膨出空間S2内に設けられているので、主基板31が基板収納空間S1内におけるねじ収納部209の上端よりも下方位置に配置された状態でも（図16（b）参照）、ねじ収納部209と干渉する事がない。

## 【0140】

また、図14に示されるように、ケース本体201の側壁205の内面とケースカバー202の低被覆面部220aの長辺220dとの間に形成される間隙部505に、コネクタ規制部材500の垂直板500bが差し込まれた状態で配置される。また、下板500cの下面全域がケース本体201の底板201a上面に載置される。コネクタ規制部材500は、ケース本体201に対して安定的に保持されるとともに、主基板31の裏面31bが下板500cにより被覆される。

20

## 【0141】

つまり、ケースカバー202に対して係止爪501を介して一端側が係止されたコネクタ規制部材500は、その一部を構成する他端側の下板500cおよび垂直板500bの下部がケース内部に配置される。

## 【0142】

さらに、この状態において、ケース本体201の第2被固着部212の上方に、ケースカバー202の第1被固着部255が配置される。すなわち、固着片212aの上面に各被固着部255a～255dが載置されると、各ねじ穴211a～211dと各取付孔259とが合致し、ワンウェイねじ280を通すことが可能な状態になる。ここで、4つの被固着部255a～255dのうち、いずれか1つ（例えば、被固着部255a）のねじ挿入部256の上面開口からワンウェイねじ280を挿入し、ねじ部283の先端を取付孔259に差し込んだ状態で、マイナスドライバー等の工具によりワンウェイねじ280を時計回りにねじ込む。

30

## 【0143】

図6に示す例では、被固着部255aのねじ挿入部256の上面開口からワンウェイねじ280が挿入される。そして、ワンウェイねじ280が時計回りにねじ込まれる。

## 【0144】

すると、図15に示すように、ねじ部283の外周に形成された雄ねじのねじ切り作用によって、ねじ部283が取付孔259を貫通して、固着片212aおよび筒状部212b内に貫通形成されたねじ穴211a内にねじ止めされ、固着片212aおよび被固着部255a、つまり第2被固着部212と第1被固着部255とがワンウェイねじ280を介して固着（かしめ）される。

40

## 【0145】

すなわち、ケースカバー202は、一方の短辺側が係止条260が被係止凹部215により係止され、他方の短辺側がワンウェイねじ280を介して固着されていることにより、ケース本体201に対してケースカバー202が開放不能に固着され、主基板31は、実装面31aおよび裏面31bがこれらケース本体201およびケースカバー202により被覆された状態で、基板収納ケース200内に封止状態で収納される。

## 【0146】

50

ワンウェイねじ280を完全にねじ込んだ後、その上方から、接着剤Zをねじ挿入部256内に注入した後、キャップ244を被着部255aの上面開口に嵌め込んで、頭部284の上面に形成された溝等を被覆することにより、ワンウェイねじ280を取り外しにくくすることができる。

#### 【0147】

なお、この実施の形態では、最初の封止の際に用いられるキャップ244は、有色のキャップであり、キャップ吊支体245に繋げられた予備用のキャップ265は、最初の封止の際に用いられるキャップ244とは異なる色（透明であってもよい）のものである。よって、何らかの不正行為がなされた後に被着部255aに遊技機の中古機から入手した予備用のキャップ265を装着できたとしても、直ちにそのことが視認される。

10

#### 【0148】

有色のキャップ244を用いることに代えて、または、有色のキャップ244を用いるとともに、接着剤Zとして、色付接着剤を用いるようにしてもよい。透明な合成樹脂材からなるねじ挿入部256内に色付接着剤が注入されることによって、ワンウェイねじ280に対する何らかのアクセスがあった場合において、色付の接着剤Zが抉り取られた痕跡等が色により視認しやすくなるため、透明なねじ挿入部256の外部からでも不正行為の痕跡を発見しやすくなる。

#### 【0149】

また、ねじ挿入部256に接着剤を注入することに代えて、被着部255aの上面開口にキャップ244を載置した後、熱溶着や超音波溶着によってキャップ244を固着するようにしてもよい。溶着で固着する場合には、接着剤で固着する場合に比べて、より強固に固着される。

20

#### 【0150】

また、この封止状態を解除してケースカバー202を開放しようとする場合、ワンウェイねじ280を反時計回りに回して取り外すことができないので、ケース本体201またはケースカバー202の一部を破壊するか、あるいは、連接部257をニッパ等の工具により切断し、固着片212aにワンウェイねじ280を介して固着されている被着部255aのねじ挿入部256をケースカバー202から切り離すしかない。

#### 【0151】

つまり、破壊または切断のいずれの方法をとるにせよ、封止状態を解除してケースカバー202を開放した場合には、破壊または切断の痕跡が残る。その結果、例えば不正行為によりケースカバー202が開放された場合でも、早期のうちに不正行為が行われたことを発見することができる。よって、万が一不正な遊技制御プログラムが格納されたROMを有する主基板等にすりかえられた場合でも、早期に発見して対処することができる。従って、その状態で遊技が行われて遊技店が不利益を被ることを回避することができる。

30

#### 【0152】

なお、連接部257をニッパ等の工具により切断して正規に封止状態を解除した場合には、ねじ収納部209に収納されている予備用ワンウェイねじ281を取り出し、3つの被着部255b～255dのうち、いずれか1つ（例えば、被着部255b）のねじ挿入部256の上面開口から予備用ワンウェイねじ281を挿入し、ねじ部283の先端を取付孔259（図15および図16（a）参照）に差し込んだ状態で、マイナスドライバー等の工具により予備用ワンウェイねじ281を時計回りにねじ込む。そして、キャップ吊支体245に繋げられている複数のキャップ265から1つのキャップ265を外し、キャップ265を被着部255bの上面開口に嵌め込んで、頭部284の上面に形成された溝等を被覆する。キャップ265を装着する際に、キャップ265に下端に設けられている係止爪267を被着部255bの内面に形成された段部266に係止することによって（図7参照）、キャップ265は、被着部255bの上面開口を閉塞するよう保持される。

40

#### 【0153】

キャップ265には、キャップ265から突出するように係止爪267が設けられてい

50

るが、最初に固着に用いられるキャップ244には、係止爪267は設けられていない。また、図7に示すように2回目以降の固着に用いられる被固着部255b～255dの内面には段部266が形成されているが、図6に示すように最初の固着に用いられる被固着部255aには、段部266は形成されていない。すなわち、最初の固着に用いられるキャップ244および被固着部255aの形状は、2回目以降の固着に用いられるキャップ265および被固着部255b～255dの形状と異なっている。従って、キャップ265を被固着部255aに装着することはできない。よって、ワンウェイねじ取り外し専用の特殊な工具等でワンウェイねじ280による接合が不正に解除され、不正行為を隠すために、具体的にはケースカバーを開放した痕跡を残さないようにするために、基板に対する不正行為を行った後、遊技機の中古機から入手した予備用ワンウェイねじ281で接合部を接合したとしても、さらに、遊技機の中古機から入手した予備用のキャップ265で被固着部255aの上面を覆うことは困難である。よって、不正行為が行われたことを隠蔽することが困難になる。

#### 【0154】

なお、この実施の形態では、キャップ244の形状と予備用のキャップ265の形状とを変え、被固着部255aの形状と2回目以降の固着に用いられる被固着部255b～255dの形状とを変えることによって、他の固着部被覆部材（この例ではキャップ265）が一の収納部（この例では被固着部255a）に装着不能になるよう収納部を形成することを実現したが、キャップ244の形状と予備用のキャップ265の形状とが同じであり、被固着部255aの形状と2回目以降の固着に用いられる被固着部255b～255dの形状とが同じである場合にも、他の固着部被覆部材が一の収納部に装着不能に収納部を形成することを実現することができる。例えば、被固着部255aを、被固着部255b～255dと同様に、突出するような係止爪を有する形状にする。また、キャップ244を、予備用のキャップ265と同様に、内面に段部が形成された形状にする。そして、最初の固着の際に、被固着部255aにキャップ244を装着（被固着部255aの係止爪を、被固着部255aの段部に係合させる。）し、熱溶着や超音波溶着によってキャップ244を被固着部255aに固着する。すると、熱溶着や超音波溶着の際に、段部の形状が崩れ、係止爪を係合不能な形状に変形する。または、段部が存在しなくなる。そのような状況において、何らかの手段で被固着部255aからキャップ244を取り外してワンウェイねじ280を外した後不正行為を行ったとしても、不正行為を隠蔽するため、例えば遊技機の中古機から入手した予備用のキャップ265で被固着部255aの上面を覆うことは困難である。上記のように、キャップ265から突出する係止爪267を受け入れる段部が既に被固着部255aにおいて変形しているからである。よって、不正行為の隠蔽を困難にすることができます。その結果、不正行為をしづらくすることができる。

#### 【0155】

また、図15および図16には、ワンウェイねじ280を用いた場合の例が示されているが、予備用ワンウェイねじ281を用いる場合にも、ワンウェイねじ280を用いた場合と同様に、ケース本体201とケースカバー202とを固着することができる。ただし、予備用ワンウェイねじ281の色はワンウェイねじ280の色とは異なっているので、不正行為を行った後、遊技機の中古機から入手した予備用ワンウェイねじ281で接合部を接合したとしても、不正行為の発見は容易である。

#### 【0156】

また、ワンウェイねじ280によりケース本体201に対してケースカバー202が開放不能に固着された封止状態にされるので、ケースカバー202の外側に仮止めされたコネクタ規制部材500が、ケースカバー202から離脱不能に保持されるとともに、基板側コネクタ238a～238cに接続された配線側コネクタ290a～290cの抜脱が上板500aとの当接により規制される。

#### 【0157】

具体的には、図14に示すように、ケース本体201に対してケースカバー202が開放不能に固着された封止状態において、コネクタ規制部材500は、下板500cが主基

10

20

30

40

50

板31の裏面31bを被覆するようにその下方に配置されることによって、その上方への移動が、ケース本体201に固着されたケースカバー202の裏面側に取り付けられた主基板31との当接により規制される。

#### 【0158】

また、下板500cから上向きに連設された垂直板500bが、ケースカバー202の長辺220dとケース本体201の側壁205内面とに挟持されるとともに、係止爪501が係合穴502に係止されることによって、ケース本体201の底板201aでのスライド移動が規制されるとともに、上板500aの変形も防止される。特に、垂直板500bの外面が側壁205の内面に上下方向にわたり密着した状態で保持されるので、垂直板500bの外側への変形も防止される。つまり、下板500c、垂直板500b、ケースカバー202の長辺220dおよび側壁205によって、規制部材保持手段が構成されている。10

#### 【0159】

コネクタ規制部材500の上方および水平方向の移動が規制されることによって、コネクタ規制部材500のケースカバー202からの離脱が防止され、安定して基板収納ケース200に保持される。そして、基板収納ケース200に保持されたコネクタ規制部材500の上板500aによって、ケースカバー202における低被覆面部220aの上面が被覆されるとともに、垂直板500bの上部、傾斜被覆面部220c、ケースカバー202の一部により低被覆面部220aの上方側周面が被覆される。よって、基板側コネクタ238a～238cおよび配線側コネクタ290a～290cが外部から遮断される。従って、コネクタの接続部に対する不正行為が防止される。20

#### 【0160】

また、図14に示すように、基板側コネクタ238a～238cに接続された配線側コネクタ290a～290cの上方近傍に上板500aが配置されるので、配線側コネクタ290a～290cを基板側コネクタ238a～238cから抜脱しようとする際に、配線側コネクタ290a～290cの本体上面における配線291a～291cの延出部周囲が、上板500aの裏面における配線挿通用開口503a～503cの周囲（当接規制部）に当接される。すなわち、配線側コネクタ290a～290cの抜脱方向への移動が上板500aにより当接規制されるため、基板側コネクタ238a～238cに正規以外の不正部品が接続された配線が接続されることを効果的に防止できる。30

#### 【0161】

また、下板500cは主基板31の裏面31bを被覆可能な大きさに形成されているので、封止状態において、裏面31bに形成された配線パターン等に対する不正行為も抑制できるとともに、安定性も向上する。なお、この実施の形態では、下板500cは主基板31の裏面31bを被覆可能な大きさに形成されていたが、コネクタ規制部材500の上方への移動を主基板31の裏面31bとの当接により規制可能な長さを有していれば、裏面31b全域を被覆可能な大きさに形成されていなくてもよい。

#### 【0162】

次に、第2被固着部212と第1被固着部255とをワンウェイねじ280を介して固着して封止状態を構成した後、主基板31の故障や検査等により主基板31を取り出すために封止状態を解除し、再度封止状態とする場合について説明する。40

#### 【0163】

なお、ねじ穴211a～211dおよび被固着部255a～255dを複数形成し、繰り返し封止状態とすることができるようにするのは、例えばメーカーが主基板31を遊技店等に出荷する際に、主基板31を基板収納ケース200内に封止状態で収納するために、1つのねじ穴211a～211dおよび被固着部255a～255dを使用した後、遊技店において、上記のように主基板31が故障して交換する場合や検査等を行うために主基板31を取り出す場合等において、封止状態を解除することがあるからである。その後再度封止状態にする際に他のねじ穴211a～211dおよび被固着部255a～255dを使用するので複数必要になる。50

## 【0164】

再度封止状態にする場合には、ケースカバー202を開放したときに、キャップ吊支体245からキャップ265を1つ分離して取り出しておくとともに、ねじ収納部209から予備用ワンウェイねじ281を1本取り出しておく。そして、ケース本体201の上面開口をケースカバー202により閉鎖する。ここで、まだ連接部257が切断されていない被固着部255b～255dのうちいずれかに予備用ワンウェイねじ281を挿入し、ねじ穴211bにねじ止めして、第2被固着部212と第1被固着部255とを固着して封止状態を構成することができる。

## 【0165】

このように、第2被固着部212としてのねじ穴211a～211dおよび第1被固着部255としての被固着部255a～255dが複数設けられているので、ケース本体201やケースカバー202の一部を破壊することなく連接部257を切断するだけで、基板収納ケース200を交換すること等なく、封止状態を解除した後でも、封止状態を複数回繰り返し構成することができる。

10

## 【0166】

図17は、主基板31における回路構成および主基板31から演出制御基板80に送信される演出制御コマンドの信号線を示すブロック図である。図17に示すように、この実施の形態では、主基板31が搭載する遊技制御用マイクロコンピュータ560は、演出制御信号送信用の8本の信号線CD0～CD7を用いて、演出制御コマンドを演出制御基板80に送信する。また、主基板31と演出制御基板80との間には、ストローブ信号を送受するための演出制御INT信号の信号線も配線されている。

20

## 【0167】

主基板31には、図17に示すように、第1始動口スイッチ13aおよび第2始動口スイッチ14aからの配線が接続されている。また、主基板31には、大入賞口である特別可変入賞球装置20や、その他の入賞口への遊技球の入賞等を検出するための各種スイッチ29a, 30a, 33a, 39aからの配線も接続されている。さらに、主基板31には、可変入賞球装置15を開閉するソレノイド16、および特別可変入賞球装置20を開閉するソレノイド21への配線が接続されている。なお、第1始動口スイッチ13aおよび第2始動口スイッチ14aからの入力は、遊技制御用マイクロコンピュータ560が搭載する乱数回路5003にも、ラッチ信号として直接入力される。

30

## 【0168】

主基板31は、遊技制御用マイクロコンピュータ560、入力ドライバ回路58および出力回路59を搭載する。遊技制御用マイクロコンピュータ560は、クロック回路5001、システムリセット手段として機能するリセットコントローラ5002、乱数回路5003、ゲーム制御用のプログラム等を記憶するROM54、ワークメモリとして使用されるRAM55、プログラムに従って動作するCPU56、CPU56に割込要求信号(タイマ割込による割込要求信号)を送出するCTC5004およびI/Oポート部57を内蔵する。

40

## 【0169】

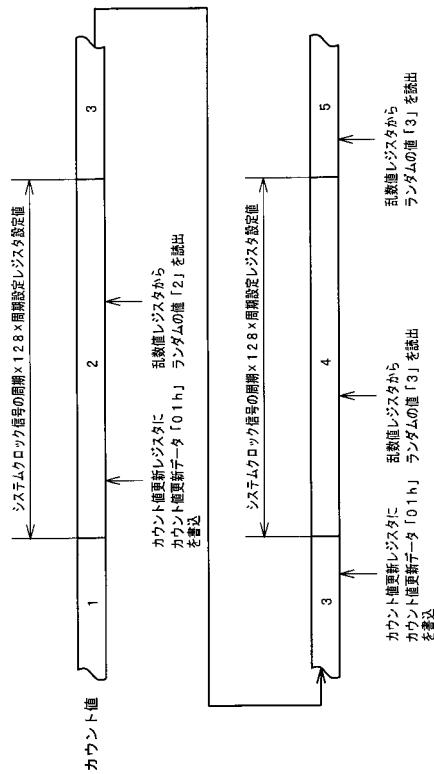

クロック回路5001は、システムクロック信号を出力するシステムクロック回路(図示せず)とは別に設けられる。この実施の形態では、遊技機が内蔵する(遊技制御用マイクロコンピュータ560の外部に設けられた)発振器が発生する所定周波数(例えば、10.0MHz)のクロック信号が遊技制御用マイクロコンピュータ560に入力され、遊技制御用マイクロコンピュータ560の各部で分周されて乱数回路5003などの各部に入力される。遊技制御用マイクロコンピュータ560のクロック回路5001は、発振器から入力したクロック信号を $2^7$ (=128)分周して生成した所定の周期の基準クロック信号CLKを、乱数回路5003に出力する。なお、この実施の形態では、遊技制御用マイクロコンピュータ560は、内蔵するシステムクロック回路が出力する所定周波数(例えば、6.0MHz)のシステムクロック信号にもとづいて動作する。従って、この実施の形態では、クロック回路5001が乱数回路5003に出力する基準クロック信号C

50

L K の周波数と、遊技制御用マイクロコンピュータ 560 の動作周波数とが異なるように構成されている。そのように構成することによって、遊技制御用マイクロコンピュータ 560 の外部からカウント値の更新周期を認識されてしまうことを防止することができ、初期化させてから大当たり遊技状態に移行させると判定されるタイミングで、外部接続基板（ぶら下げ基板）から信号を入力することによって大当たりが狙われてしまうことを防止する効果をより向上させることができる。

#### 【0170】

なお、遊技制御用マイクロコンピュータ 560 が乱数回路 5003 を内蔵するものではなく、遊技制御用マイクロコンピュータ 560 に外付けの乱数回路を用いる場合であっても、クロック回路 5001 は、システムクロック信号を出力するシステムクロック回路（図示せず）とは別に設けられる。そして、クロック回路 5001 は、遊技制御用マイクロコンピュータ 560 の外部に設けられた発振器から入力した所定周波数（例えば、10.0 MHz）のクロック信号を  $2^7$  (= 128) 分周して生成した所定の周期の基準クロック信号 CLK を、外付けの乱数回路に出力するように構成される。そのように構成されることによって、外付けの乱数回路を用いる場合であっても、クロック回路 5001 が外付けの乱数回路に出力する基準クロック信号 CLK の周波数と、遊技制御用マイクロコンピュータ 560 の動作周波数とが異なるように構成することができる。なお、外付けの乱数回路を用いる場合、クロック回路 5001 は、遊技制御用マイクロコンピュータ 560 に内蔵されるものであってもよく、遊技制御用マイクロコンピュータ 560 の外部に設けられてもよい。

10

20

30

40

#### 【0171】

また、クロック回路 5001 は、遊技制御用マイクロコンピュータ 560 の外部に設けられた発振器から入力したクロック信号を分周せずに、そのまま基準クロック信号 CLK として乱数回路 5003（または、遊技制御用マイクロコンピュータ 560 に外付けの乱数回路）に出力してもよい。そのようにしても、発振器が発生するクロック信号の周波数（例えば、10.0 MHz）と、システムクロック回路が出力するシステムクロック信号の周波数（例えば、6.0 MHz）とが異なっていれば、乱数回路 5003（または、遊技制御用マイクロコンピュータ 560 に外付けの乱数回路）に出力する基準クロック信号 CLK の周波数と、遊技制御用マイクロコンピュータ 560 の動作周波数とが異なるように構成することができる。

#### 【0172】

また、例えば、クロック回路 5001 をシステムクロック回路とは別に設けるのではなく、共通のクロック回路を用いて、CPU 56 と乱数回路 5003（または、遊技制御用マイクロコンピュータ 560 に外付けの乱数回路）とにクロック信号を出力するようにしてもよい。この場合、例えば、クロック回路と CPU 56 との間およびクロック回路と乱数回路 5003（または、遊技制御用マイクロコンピュータ 560 に外付けの乱数回路）との間に、それぞれ異なる分周数の分周器を設けるようにすればよい。例えば、クロック回路が出力するクロック信号を 2 分周器で 2 分周した信号を乱数回路 5003（または、遊技制御用マイクロコンピュータ 560 に外付けの乱数回路）に入力するようにし、クロック回路が出力するクロック信号を 3 分周器で 3 分周した信号を CPU 56 に入力するようにしてもよい。そのようにしても、乱数回路 5003（または、遊技制御用マイクロコンピュータ 560 に外付けの乱数回路）に出力する基準クロック信号 CLK の周波数と、遊技制御用マイクロコンピュータ 560 の動作周波数とが異なるように構成することができる。また、乱数回路 5003（または、遊技制御用マイクロコンピュータ 560 に外付けの乱数回路）に入力するクロック信号の周期が、CPU 56 に入力するクロック信号の周期よりも短くなるように構成してもよい。

#### 【0173】

また、CPU 56 と乱数回路に入力されるクロック信号に関しては、以下のように構成してもよい。

#### 【0174】

50

(1) 例えば、乱数回路5003が遊技制御用マイクロコンピュータ560に内蔵されている場合に、C P U 5 6 の動作クロック信号を発生するために遊技制御用マイクロコンピュータ560外部に設けられた発振器とは別に、遊技制御用マイクロコンピュータ560外部に設けられた発振器からのクロック信号が遊技制御用マイクロコンピュータ560に入力されるようにしてもよい。そして、遊技制御用マイクロコンピュータ560は、入力したクロック信号を乱数回路5003に入力し、乱数回路5003内のカウンタ521を更新するようにしてもよい。

#### 【0175】

(2) また、例えば、乱数回路5003が遊技制御用マイクロコンピュータ560に内蔵されている場合に、C P U 5 6 の動作クロック信号を発生するために、遊技制御用マイクロコンピュータ560外部に設けられた発振器からのクロック信号が遊技制御用マイクロコンピュータ560に入力するようにしてもよい。そして、遊技制御用マイクロコンピュータ560は、入力したクロック信号をC P U 5 6 および乱数回路5003に入力し、乱数回路5003内のカウンタ521を更新するようにしてもよい。この場合、遊技制御用マイクロコンピュータ560に入力された後に、C P U 5 6 に入力する前にクロック信号を分周するとともに、乱数回路5003に入力する前にクロック信号を分周するようにすればよい。

10

#### 【0176】

(3) また、例えば、乱数回路が遊技制御用マイクロコンピュータ560の外部に設けられている場合には、遊技制御用マイクロコンピュータ560の外部に設けられた1つの発振器からのクロック信号を分岐して、遊技制御用マイクロコンピュータ560と外付けの乱数回路とに入力するようにしてもよい。そして、遊技制御用マイクロコンピュータ560の外部でクロック信号を分周または遊技制御用マイクロコンピュータ560の内部でクロック信号を分周して動作クロック信号としてC P U 5 6 に入力するとともに、外付けの乱数回路に入力する前にクロック信号を分周して、外付けの乱数回路に入力するようにしてもよい。

20

#### 【0177】

(4) また、例えば、乱数回路が遊技制御用マイクロコンピュータ560の外部に設けられている場合には、遊技制御用マイクロコンピュータ560の動作クロック信号用の発振器と、外付けの乱数回路のカウンタを更新するための発振器とを、それぞれ別個に遊技制御用マイクロコンピュータ560の外部に設けるようにし、それぞれの発振器により発生させるクロック信号の周波数を異ならせるようにしてもよい。

30

#### 【0178】

上記(1)～(4)に示すように、いずれにしても遊技制御用マイクロコンピュータ560を動作させるために遊技制御用マイクロコンピュータ560に入力されるクロック信号を発生する発振器を備えるようにし、当該発振器により発生されたクロック信号によりC P U 5 6 が動作するために分周された動作クロック信号と、乱数回路(遊技制御用マイクロコンピュータ560内蔵の乱数回路5003でも、遊技制御用マイクロコンピュータ560に外付けの乱数回路でも、いずれでもよい。)に入力されるクロック信号とで周波数が異なればよい。特に、乱数回路に入力されるクロック信号の周波数の方が高周波である場合には、遊技制御用マイクロコンピュータ560から出力されるコマンドなどの信号により乱数の更新周期を認識されてしまうことを防止できるので、より好ましい。

40

#### 【0179】

リセットコントローラ5002は、ローレベルの信号が一定期間入力されたとき、C P U 5 6 および乱数回路5003に所定の初期化信号を出力して、遊技制御用マイクロコンピュータ560をシステムリセットする。

#### 【0180】

また、この実施の形態では、乱数回路5003は、16ビットの疑似乱数を発生する乱数回路である。乱数回路5003は、16ビットで発生できる範囲(すなわち、0から65535までの範囲)の値の乱数を発生する機能を備える。

50

## 【0181】

次に、乱数回路5003の構成について説明する。図18は、乱数回路5003の構成例を示すブロック図である。図18に示すように、乱数回路5003は、カウンタ521、比較器522、カウント値順列変更回路523、クロック信号出力回路524、カウント値更新信号出力回路525、乱数更新方式選択信号出力回路527、セレクタ528、乱数回路起動信号出力回路530、第1乱数値記憶回路(第1ラッチ回路)531a、および第2乱数値記憶回路(第2ラッチ回路)531aを含む。なお、以下、遊技制御用マイクロコンピュータ5003が搭載する乱数回路5003について説明するが、演出制御用マイクロコンピュータ100が搭載する乱数回路107の基本的な機能および動作についても同様である。

10

## 【0182】

この実施の形態では、乱数回路5003が発生するハードウェア乱数は、複数種類の識別情報の可変表示の表示結果を特定の表示結果とするか否か(例えば、特別図柄表示装置8の表示図柄の組み合わせを大当たり図柄の組み合わせとするか否か)を判定するための大当たり判定用乱数を生成するために用いられる。また、遊技制御用マイクロコンピュータ560は、後述するように、乱数回路5003が発生するハードウェア乱数(ランダムR)と、ソフトウェア乱数(ランダム2-1)とを用いて、大当たり判定用乱数を生成する。そして、遊技制御用マイクロコンピュータ560のCPU56は、生成した大当たり判定用乱数にもとづいて特定の表示結果とすると判定すると、遊技状態を遊技者にとって有利な特定遊技状態(例えば、大当たり遊技状態)に移行させる。なお、乱数回路5003が発生した乱数を、確変とするか否かを決定するための確変判定用乱数や、特別図柄の変動パターンを決定する変動パターン判定用乱数など、大当たり図柄以外の判定用乱数を生成するために用いてもよい。

20

## 【0183】

カウンタ(ハードウェアカウンタ)521は、セレクタ528によって選択された所定の信号を入力し、セレクタ528から入力する信号に応答してカウント値Cを出力する。この場合、カウンタ521は、所定の初期値を入力し、カウント値Cを一定の規則に従って初期値から所定の最終値まで循環的に更新して出力する。また、カウンタ521は、カウント値Cを最終値まで更新すると、カウント値Cを最終値まで更新した旨を示す通知信号をCPU56に出力する。この実施の形態では、カウンタ521から通知信号が出力されると、CPU56によって初期値が更新される。

30

## 【0184】

この実施の形態において、カウンタ521は、セレクタ528から信号を入力するごとに(セレクタ528からの信号における立ち上がりエッヂが入力されるごとに)、カウント値Cを「0」から「65535」まで1ずつカウントアップする。また、カウンタ521は、カウント値Cを「65535」までカウントアップすると、カウント値Cを最終値まで更新した旨を示す通知信号をCPU56に出力する。すると、CPU56は、カウンタ521から通知信号を入力し、初期値を更新する。そして、カウンタ521は、CPU56によって更新された初期値から「65535」まで、再びカウント値Cをカウントアップする。また、「65535」までカウントアップすると、カウンタ521は、再び「0」からカウントを開始する。そして、カウンタ521は、更新後の初期値の1つ前の値(最終値)までカウントアップすると、通知信号をCPU56に出力する。なお、この実施の形態では、比較器522は、後述するように、全てのカウント値を入力すると通知信号をカウンタ521に出力する。この場合、カウンタ521は、比較器522から通知信号を入力すると、カウント値をリセットして「0」にする。

40

## 【0185】

なお、比較器522は、入力したカウント値が乱数最大値設定レジスタ535に設定されている乱数最大値より大きいか否かを判断し、カウント値が乱数最大値より大きい(乱数最大値を超えた)と判断すると、通知信号をカウンタ521に出力してもよい。この場合、例えば、比較器522は、カウント値が乱数最大値を超えたと判断すると、クロック

50

信号出力回路 524 が次に乱数発生用クロック信号 S I 1 を出力する前に、通知信号をカウンタ 521 に出力する。例えば、乱数最大値設定レジスタ 535 に乱数最大値「256」が設定されている場合を考える。この場合、カウンタ 521 が「0」から「256」までカウントアップし、さらにカウント値「257」を出力すると、比較器 522 は、入力したカウント値「257」が乱数最大値「256」を超えたと判断し、カウンタ 521 に通知信号を出力する。比較器 522 から通知信号を入力すると、カウンタ 521 は、クロック信号出力回路 524 からの乱数発生用クロック信号 S I 1 の入力を待つことなく、カウント値を「258」に更新し出力する。以上の処理を繰り返し実行することによって、比較器 522 は、カウント値「257」から「65535」まで入力している間、カウント値が乱数最大値を超えていたと判断して、繰り返しカウンタ 521 に通知信号を出力する。そして、カウンタ 521 は、比較器 522 から通知信号を入力している間、クロック信号出力回路 524 からの乱数発生用クロック信号 S I 1 の入力を待つことなく、カウント値を繰り返し更新し出力する。そのようにすることによって、クロック信号出力回路 524 が次に乱数発生用クロック信号 S I 1 を出力するまでの間に、「257」から「65535」までカウント値を高速にカウントアップさせるように制御し、「257」から「65535」までの乱数値を読み飛ばす（第1乱数値記憶回路 531a および第2乱数値記憶回路 531b に記憶させない）ように制御する。

10

## 【0186】

カウント値順列変更回路 523 は、カウント値順列変更レジスタ（RSC）536、更新規則選択レジスタ（RRC）542 および更新規則メモリ 543 を含む。カウント値順列変更レジスタ 536 は、カウンタ 521 がカウントアップするカウント値 C の更新順である順列（初期値から最終値までの並び順）を変更させるためのカウント値順列変更データ「01h」を格納する。カウント値順列変更回路 523 は、カウント値順列変更レジスタ 536 に数値順列変更データ「01h」が格納されているとき、カウンタ 521 がカウントアップして更新するカウント値 C の順列を、カウント値順列変更データ「01h」が格納されていないときとは異なる順列に変更する。この場合、カウント値順列変更回路 523 は、数値順列変更データ「01h」が格納されているとき、カウント値の順列の変更に用いる更新規則を切り換える。また、カウント値の順列の変更に用いる更新規則を切り換えた後に、カウンタ 521 がカウント値の更新を開始すると、カウント値順列変更レジスタ 536 のカウント値順列変更データは、CPU56 によって、「01h」から初期値である「0（=00h）」に戻される（クリアされる）。

20

## 【0187】

なお、CPU56 によってカウント値順列変更データをクリアするだけでなく、乱数回路 5003 側でカウント値順列変更データをクリアするようにしてもよい。例えば、カウント値順列変更レジスタ 536 にカウント値順列変更データ「01h」が書き込まれたにもとづいて、更新規則選択レジスタ（RRC）542 にレジスタ値が設定されると、カウント値順列変更回路 523 は、カウント値順列変更レジスタ 536 のレジスタ値をクリアするようにしてもよい。

30

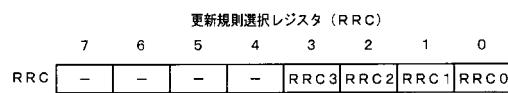

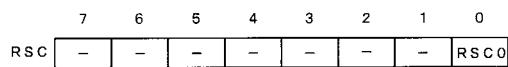

## 【0188】

図 19 は、更新規則選択レジスタ 542 の例を示す説明図である。更新規則選択レジスタ 542 は、カウンタ 521 が出力するカウント値の並び順の並べ替え（順列の変更）に用いる更新規則を設定するレジスタである。この実施の形態では、更新規則選択レジスタ 542 にレジスタ値が設定されることによって、カウンタ 521 が出力するカウント値の順列の変更に用いる更新規則が設定される。図 19 に示すように、更新規則選択レジスタ 542 は、8 ビットレジスタであり、初期値が「0（=00h）」に設定されている。また、更新規則選択レジスタ 542 は、ビット 0 ~ ビット 3 が書込および読出ともに可能な状態に構成されている。また、更新規則選択レジスタ 542 は、ビット 4 ~ ビット 7 が書込および読出ともに不可能な状態に構成されている。したがって、更新規則選択レジスタ 542 のビット 4 ~ ビット 7 に値を書き込む制御を行っても無効とされ、ビット 4 ~ ビット 7 から読み出す値は全て「0（=0000b）」である。

40

50

## 【0189】

更新規則選択レジスタ542の値（レジスタ値）は、カウント値順列変更レジスタ536にカウント値順列変更データ「01h」が書き込まれたことに応じて、レジスタ値が「0（=00h）」から「15（=0Fh）」まで循環的に更新される。すなわち、カウント値順列変更レジスタ536にカウント値順列データ「01h」が書き込まれるごとに、更新規則選択レジスタ542のレジスタ値は、「0」から「1」ずつ加算され、「15」になると再び「0」に戻る。

## 【0190】

図20は、更新規則メモリ543の例を示す説明図である。図20に示すように、更新規則メモリ543は、更新規則選択レジスタ542の値（レジスタ値）と、カウント値の更新規則とを対応付けて格納している。図20に示す例では、例えば、更新規則選択レジスタ542にレジスタ値1が設定されている場合、更新規則Bを用いて、カウンタ521が出力するカウント値の順列が変更されることが分かる。なお、図20において、更新規則Aは、カウンタ521がカウント値Cを更新する規則と同一の更新規則であり、レジスタ値「0」に対応づけて更新規則メモリ543に格納される。また、更新規則メモリ543には、カウンタ521がカウント値Cを更新する更新規則とは異なる更新規則B～Pが、レジスタ値「1」～「15」に対応づけて格納される。

10

## 【0191】

カウント値順列変更回路523は、カウント値順列変更レジスタ536にカウント値順列変更データ「01h」が書き込まれている場合、まず、カウンタ521からカウント値の最終値「65535」が最初に入力されるまで、現在設定されている更新規則に従って、そのままカウント値を出力する。そして、カウント値順列変更回路523は、カウンタ521からカウント値の最終値「65535」を入力すると、カウント値の更新規則を変更する。なお、CPU56によって初期値が変更されている場合には、カウント値順列変更回路523は、カウンタ521から変更後の最終値（初期値の1つ前の値）まで入力すると、カウント値の更新規則を変更することになる。

20

## 【0192】

カウント値順列変更回路523は、更新規則選択レジスタ542のレジスタ値に対応する更新規則を更新規則メモリ543から選択し、カウント値の順列の変更に用いる更新規則として設定する。また、カウント値順列変更回路523は、カウンタ521によって再び初期値「0」から順にカウント値の更新が開始されると、設定した更新規則に従って、カウント値の初期値から最終値までの順列を変更する。なお、CPU56によって初期値が変更されている場合には、カウント値順列変更回路523は、カウンタ521によって変更後の初期値から順にカウント値の更新が開始されると、設定した更新規則に従って、カウント値の初期値から最終値までの順列を変更することになる。そして、カウント値順列変更回路523は、変更した順列に従ってカウント値を出力する。

30

## 【0193】

なお、この実施の形態では、後述する乱数最大値設定レジスタ535に乱数最大値が設定されることによって、発生させる乱数の最大値が制限されている場合、カウント値順列変更回路523は、カウント値Cを乱数最大値以下に制限して順列を変更して出力する。例えば、乱数最大値設定レジスタ535に乱数最大値「256」が設定されているものとし、カウント値順列変更回路523が、更新規則Aから更新規則Bに変更して、カウント値の順列を変更するものとする。この場合、カウント値順列変更回路523は、比較器522の乱数最大値設定レジスタ535に設定されている乱数最大値「256」にもとづいて、更新規則Bに従って、カウント値の順列を「256 255 ... 0」に変更して出力する。

40

## 【0194】

以上のように、カウント値順列変更回路523は、カウント値順列変更レジスタ536にカウント値順列変更データ「01h」が書き込まれている場合、更新規則を切り替えて用いることによって、カウント値Cの順列を変更して出力する。そのため、乱数回路50

50

03が生成する乱数のランダム性を向上させることができる。

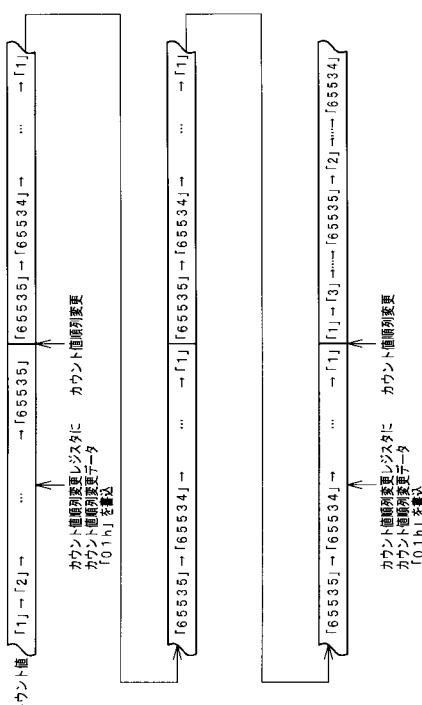

#### 【0195】

図21は、カウント値順列変更回路523が、カウンタ521が出力するカウント値の順列を変更する場合の例を示す説明図である。図21に示すように、CPU56は、所定のタイミングで、カウント値順列変更データ「01h」をカウント値順列変更レジスタ536に書き込む。すると、更新規則選択レジスタ542のレジスタ値が1加算される。例えば、更新規則選択レジスタ542のレジスタ値が「0」から「1」に更新される。レジスタ値が更新されると、カウント値順列変更回路523は、カウンタ521から最初にカウント値の最終値「65535」が入力されるまで、更新前のレジスタ値「0」に対応する「更新規則A」に従ってカウント値を更新して出力する。このとき、カウント値順列変更回路523は、更新規則Aに従って、「0 1 . . . 65535」の順列でカウント値を出力する。

10

#### 【0196】

カウンタ521からカウント値の最終値「65535」が入力されると、カウント値順列変更回路523は、更新規則メモリ543から、更新後のレジスタ値「1」に対応する「更新規則B」を選択して設定する。カウント値順列変更回路523は、カウンタ521から再び初期値「0」以降のカウント値の入力を開始すると、選択設定した「更新規則B」に従って、カウント値の順列を変更して出力する。本例では、カウント値順列変更回路523は、順列を「0 1 . . . 65535」から「65535 65534 . . . 0」に変更して、カウント値を出力する。

20

#### 【0197】

その後、カウント値順列変更レジスタ536は、後述するように、カウント値順列変更回路523が切り替え後の更新規則に従ってカウント値の更新動作を開始したことに応じてリセットされる。そして、次にカウント値順列変更データ「01h」がカウント値順列変更レジスタ536に書き込まれるまで、カウント値順列変更回路523は、「65535 65534 . . . 0」のままの順列で、カウント値を出力し続ける。

#### 【0198】

CPU56によってカウント値順列変更データ「01h」がカウント値順列変更レジスタ536に再度書き込まれると、カウント値順列変更レジスタ536のレジスタ値が「1」から「2」に更新される。そして、カウンタ521からカウント値の最終値「65535」を入力すると、カウント値順列変更回路523は、更新規則メモリ543から、レジスタ値「2」に対応する「更新規則C」を選択して設定する。カウント値順列変更回路523は、カウンタ521から再び初期値「0」以降のカウント値の入力を開始すると、選択設定した「更新規則C」に従って、カウント値の順列を更新して出力する。本例では、カウント値順列変更回路523は、順列を「65535 65534 . . . 0」から「1 3 . . . 65535 0 . . . 65534」に変更して、カウント値を出力する。

30

#### 【0199】

以上のように、カウント値順列変更レジスタ536をリセットした後、カウント値順列データ「01h」をカウント値順列変更レジスタ536に再度書き込むことによって、カウント値の順列をさらに変更することができる。

40

#### 【0200】

図22は、カウント値順列変更レジスタ536の例を示す説明図である。カウント値順列変更レジスタ536は、カウンタ521がカウントアップするカウント値の順列を変更させるためのカウント値順列変更データ「01h」を設定するレジスタである。図22に示すように、カウント値順列変更レジスタ536は、読み可能な8ビットレジスタであり、初期値が「0 (=00h)」に設定されている。また、カウント値順列変更レジスタ536は、ビット0だけが書き込みおよび読みともに可能な状態に構成されている。すなわち、カウント値順列変更レジスタ536は、ビット1～ビット7が書き込みおよび読みともに不可能な状態に構成されている。したがって、カウント値順列変更レジスタ536のビット1

50

～ビット7に値を書き込む制御を行っても無効とされ、ビット1～ビット7から読み出す値は全て「0(=0000000b)」である。

#### 【0201】

なお、カウント値順列変更レジスタ536の値は、カウント値順列変更回路523が切り替え後の更新規則に従ってカウント値の更新動作を開始したことに応じて、CPU56によってリセットされる。この場合、CPU56は、カウント値順列変更レジスタ536に書き込まれている値を、カウント値順列変更データ「01h」から初期値である「0(=00h)」に戻す。

#### 【0202】

比較器522は、ランダムRの最大値（乱数最大値）を指定するための乱数最大値設定データを格納する乱数最大値設定レジスタ(RMX)535を備える。比較器522は、乱数最大値設定レジスタ535に格納されている乱数最大値設定データに示される乱数最大値に従って、カウンタ521が更新するカウント値の更新範囲を制限する。この実施の形態では、比較器522は、カウンタ521から入力するカウント値と乱数最大値設定レジスタ535に格納されている乱数最大値設定データ（例えば「00FFh」）に示される乱数最大値（例えば「256」）とを比較する。そして、比較器522は、入力したカウント値が乱数最大値以下であると判断すると、入力したカウント値を第1乱数値記憶回路531aおよび第2乱数値記憶回路531bに出力する。

#### 【0203】

この実施の形態では、比較器522は、具体的には、以下のようないくつかの制御を行う。比較器522は、カウント値の初期値更新の際に、CPU56からカウント値の初期値をもらい、初期値から乱数最大値までのカウント値の個数を求める。例えば、カウント値の初期値が「157」であり乱数最大値が「256」である場合、比較器522は、初期値から乱数最大値までのカウント値の個数を「100個」と求める。また、比較器522は、カウント値順列変更回路523からカウント値を入力するに従って、初期値からカウント値をいくつ入力したかをカウントアップする。初期値からカウント値を入力した回数が「100回」に達すると、比較器522は、初期値「157」から最大値「256」までの全てのカウント値を入力したと判断する。そして、比較器522は、全てのカウント値を入力した旨の通知信号をカウンタ521に出力する。カウント値の個数で判断することによって、カウント値順列変更回路523によってカウント値の順列が変更されている場合であっても、比較器522は、カウント値の更新範囲を乱数最大値以下に制限し、全てのカウント値を入力した際にカウンタ521に通知信号を出力することができる。

#### 【0204】

カウント値の更新範囲を比較器522が制限する動作について説明する。なお、本例では、カウント値順列変更回路523が更新規則Aを選択し、乱数最大値設定レジスタ535に乱数最大値「256」が設定されている場合を説明する。

#### 【0205】

カウンタ521が「0」から「256」までカウント値を更新している間、カウント値順列変更回路523は、乱数最大値設定レジスタ535に設定されている乱数最大値「256」にもとづいて、更新規則Aに従って、「0」から「256」までのカウント値をそのまま比較器522に出力する。この場合、カウント値順列変更回路523は、比較器522から乱数最大値「256」の値をもらい、カウンタ521から入力するカウント値が乱数最大値より大きいか否かを判断し、更新規則が変更されているとき（例えば、更新規則B）であっても、乱数最大値設定レジスタ535に設定されている乱数最大値「256」にもとづいて、「257」から「65535」までのカウント値を比較器522に出力しない。カウンタ521は、例えば、初期値が「0」と設定されているときに、最終値「256」までカウント値を更新すると、通知信号をCPU56に出力する。通知信号を出力すると、CPU56によって、カウンタ521のカウント値の初期値が変更される。本例では、CPU56によって、初期値が「50」に変更されるものとする。

#### 【0206】

10

20

30

40

50

なお、カウント値が乱数最大値「256」より大きいか否かをカウント値順列変更回路523が判断するのではなく、比較器522が判定するようにしてもよい。この場合、例えば、比較器522は、カウント値が乱数最大値設定レジスタ535に設定されている乱数最大値より大きいか否かを判断し、カウント値が乱数最大値より大きいと判断すると、通知信号をカウンタ521に出力する。そして、比較器522は、カウント値が乱数最大値を超えたと判断すると、クロック信号出力回路524が次に乱数発生用クロック信号S11を出力する前に、通知信号をカウンタ521に出力する。そのようにすることによって、比較器522は、クロック信号出力回路524が次に乱数発生用クロック信号S11を出力するまでの間に、「257」から「65535」までカウント値を高速にカウントアップさせるようにカウンタ521を制御する。そのようにすることによって、カウント値順列変更回路523からの値が「257」未満のときだけカウント値を第1乱数値記憶回路531aおよび第2乱数値記憶回路531bに出力するようにし、カウント値順列変更回路523からの値が「257」以上のときにはカウント値を高速で更新させるようにすることができる。

#### 【0207】

更新規則Aにもとづいて、カウント値順列変更回路523から、「0」から「255」までカウント値を入力している間、比較器522は、入力するカウント値が乱数最大値「256」以下であるので、入力したカウント値をそのまま第1乱数値記憶回路531aおよび第2乱数値記憶回路531bに出力する。次に、カウント値順列変更回路523から入力するカウント値が「256」に達すると、比較器522は、入力したカウント値を第1乱数値記憶回路531aおよび第2乱数値記憶回路531bに出力するとともに、初期値から最大値までの全てのカウント値を入力した旨の通知信号をカウンタ521に出力する。具体的には、比較器522は、カウント値の初期値変更の際に、CPU56からカウント値の初期値（本例では、「0」）をもらい、初期値「0」から乱数最大値（本例では、「256」）までのカウント値の個数（本例では、「257個」）を求める。そして、カウント値順列変更回路523から入力したカウント値の個数が257個に達すると、全てのカウント値を入力した旨の通知信号をカウンタ521に出力する。なお、本例では、CPU56によって初期値が「50」に変更されるので、カウンタ521は、比較器522から通知信号を入力しても、カウント値をリセットするなく、変更後の初期値「50」からカウント値の更新を行う。

#### 【0208】

カウンタ521が変更後の初期値「50」から「256」までカウント値を更新している間、カウント値順列変更回路523は、乱数最大値設定レジスタ535に設定されている乱数最大値「256」にもとづいて、更新規則Aに従って、「50」から「256」までのカウント値をそのまま比較器522に出力する。また、カウント値順列変更回路523は、乱数最大値設定レジスタ535に設定されている乱数最大値「256」にもとづいて、「257」から「65535」までのカウント値を比較器522に出力せず、カウンタ521の更新するカウント値が1周したとき（257回更新したとき）に、カウント値順列変更レジスタ536にカウント値順列変更データが書き込まれた場合には、カウント値順列変更回路523は、カウント値の順列を変更して出力する。例えば、更新規則が更新規則Bに変更された場合、カウント値順列変更回路523は、カウント値の順列を「256 255 ... 50」に変更して出力する。

#### 【0209】

カウント値順列変更回路523から、「256」から「50」までカウント値を入力している間、比較器522は、入力したカウント値をそのまま第1乱数値記憶回路531aおよび第2乱数値記憶回路531bに出力する。次に、カウント値順列変更回路523から入力するカウント値が「50」に達すると、比較器522は、入力したカウント値を第1乱数値記憶回路531aおよび第2乱数値記憶回路531bに出力するとともに、初期値から最大値までの全てのカウント値を入力した旨の通知信号をカウンタ521に出力する。具体的には、比較器522は、カウント値の初期値変更の際に、CPU56からカウ

10

20

30

40

50

ント値の初期値（本例では、「50」）をもらい、初期値「50」から乱数最大値（本例では、「256」）までのカウント値の個数（本例では、「207個」）を求める。そして、カウント値順列変更回路523から入力したカウント値の個数が207個に達すると、全てのカウント値を入力した旨の通知信号をカウンタ521に出力する。

#### 【0210】

なお、カウント値順列変更回路523がカウント値の順列を変更した場合であっても、比較器522は、カウント値の個数が207個に達すると、通知信号をカウンタ521に出力する。そのようにすることによって、カウント値の順列が変更された場合であっても、初期値「50」から最大値「256」までの全てのカウント値を入力したことにもとづいて、通知信号をカウンタ521に出力できる。

10

#### 【0211】

比較器522から通知信号を入力すると、カウンタ521は、カウント値の初期値をリセットし「0」に戻す。そして、カウンタ521は、「0」からカウント値の更新を行う。カウンタ521の値が「0」から再び更新がされると、カウンタ521からのカウント値にもとづいて、カウント値順列変更回路523は「49」～「0」までのカウント値を比較器522に出力し、比較器522はカウント値順列変更回路523からのカウント値の入力にもとづいて第1乱数値記憶回路531aおよび第2乱数値記憶回路531bにカウント値を出力する。そして、カウンタ521は、最終値（本例では、「49」）までカウント値を更新すると、通知信号をCPU56に出力する。通知信号を出力すると、CPU56によって、カウンタ521のカウント値の初期値が再び変更される。

20

#### 【0212】

以上のような動作を繰り返すことにより、比較器522は、カウンタ521に、「0」から乱数最大値「256」まで連続的にカウント値をカウントアップさせ、「0」から「256」までの値を第1乱数値記憶回路531aおよび第2乱数値記憶回路531bにランダムR（乱数値）として記憶させる。すなわち、比較器522は、カウント値の更新範囲を乱数最大値「256」以下に制限して、カウンタ521にカウント値を更新させる。

20

#### 【0213】

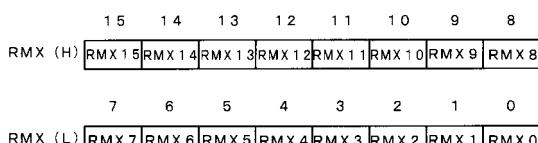

図23は、乱数最大値設定レジスタ535の例を示す説明図である。図23に示すように、乱数回路5003において、乱数最大値設定レジスタ535は、16ビットレジスタであり、初期値が「65535（=FFFh）」に設定されている。また、乱数回路5003において、乱数最大値設定レジスタ535は、ビット0～ビット15の全てのビットが書き込みおよび読み出ともに可能な状態に構成されている。

30

#### 【0214】

また、乱数最大値設定レジスタ535に下限値「512」より小さい値を指定する乱数最大値設定データ「0000h」～「01FEh」が書き込まれた場合、CPU56は、乱数最大値設定レジスタ535に、初期値「65535」を指定する乱数最大値設定データ「FFFh」を設定しなおす。すなわち、乱数最大値設定レジスタ535に設定可能な乱数最大値は「512」から「65535」まであり、CPU56は、下限値「512」より小さい値が設定されていると判断すると、乱数最大値を所定値「65535」に設定しなおす。なお、CPU56は、リセットコントローラ5002によって遊技制御用マイクロコンピュータ560がシステムリセットされるまで、乱数最大値設定データが書き込まれた乱数最大値設定レジスタ535を書き込み不可能に制御する。なお、CPU56により書き込み不可能に制御するだけでなく、乱数最大値設定レジスタ535は、データが書き込まれた後にリセット信号を入力するまで書き込み不可能となるように形成されていてもよい。

40

#### 【0215】

クロック信号出力回路524は、セレクタ528に出力するクロック信号の周期（すなわち、カウント値の更新周期）を指定するための周期設定データを格納する周期設定レジスタ（RPS）537を備える。クロック信号出力回路524は、周期設定レジスタ537に格納されている周期設定データに基づいて、遊技制御用マイクロコンピュータ560が搭載するクロック回路5001から入力する基準クロック信号CLKを分周して、乱数

50

回路 5003 内部で乱数値の生成に用いるクロック信号（乱数発生用クロック信号 S I 1）を生成する。そのようにすることによって、クロック信号出力回路 524 は、クロック信号を所定回数入力したことを条件に、カウント値 C を更新させるための乱数発生用クロック信号 S I 1 をカウンタ 521 に出力するように動作する。なお、周期設定データとは、クロック回路 5001 から入力した基準クロック信号 C L K を何分周させるかを設定するためのデータである。また、クロック出力回路 524 は、生成した乱数発生用クロック信号 S I 1 をセレクタ 528 に出力する。例えば、周期設定レジスタ 537 に周期設定データ「0 F h (= 16)」が書き込まれている場合、クロック信号出力回路 524 は、クロック回路 5001 から入力する基準クロック信号 C L K を 16 分周して乱数発生用クロック信号 S I 1 を生成する。この場合、クロック信号出力回路 524 が生成する乱数発生用クロック信号 S I 1 の周期は、「システムクロック信号の周期 × 128 × 16」となる。

10

#### 【0216】

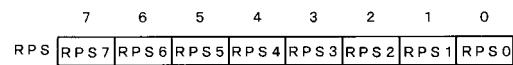

図 24 は、周期設定レジスタ 537 の例を示す説明図である。図 24 に示すように、周期設定レジスタ 537 は、8 ビットレジスタであり、初期値が「256 (= F F h)」に設定されている。また、周期設定レジスタ 537 は、書き込みおよび読み出ともに可能な状態に構成されている。

20

#### 【0217】

また、周期設定レジスタ 537 に設定される周期設定データの値は、所定の下限値が定められている。この実施の形態では、周期設定レジスタ 537 に下限値「システムクロック信号の周期 × 128 × 7」より小さい値を指定する周期設定データ「00 h ~ 06 h」が書き込まれた場合、C P U 56 は、周期設定レジスタ 537 に下限値「システムクロック信号の周期 × 128 × 7」を指定する周期設定データ「07 h」を設定しなおす。すなわち、周期設定レジスタ 537 に設定可能な周期は「システムクロック信号の周期 × 128 × 7」から「システムクロック信号の周期 × 128 × 256」までであり、C P U 56 は、下限値より小さい値が設定されていると判断すると、周期設定データを設定しなおす。なお、C P U 56 は、リセットコントローラ 5002 によって遊技制御用マイクロコンピュータ 560 がシステムリセットされるまで、周期設定データが書き込まれた周期設定レジスタ 537 を書き込み不可能に制御する。なお、C P U 56 により書き込み不可能に制御するのではなく、周期設定レジスタ 537 は、データが書き込まれた後にリセット信号を入力するまで書き込み不可能となるように形成されていてもよい。

30

#### 【0218】

なお、周期設定レジスタ 537 に下限値としての周期設定データを設定することなく、設定された周期設定データに基づいて、例えばクロック信号出力回路 524 が基準クロック信号 C L K をそのままカウンタ 521 に出力するようにしてもよい。この場合、C P U 56 は、周期設定レジスタ 537 に設定される周期設定データの値を下限値と比較して設定しなおす処理を行う必要がなくなる。また、カウンタ 521 は、クロック信号出力回路 524 から基準クロック信号 C L K を入力する毎にカウント値 C を更新することになる。

#### 【0219】

カウント値更新信号出力回路 525 は、カウント値更新データ「01 h」を格納するカウント値更新レジスタ（R G N）538 を備える。カウント値更新データとは、カウント値の更新を要求するためのデータである。カウント値更新信号出力回路 525 は、カウント値更新レジスタ 538 にカウント値更新データ「01 h」が書き込まれたことに応じて、カウント値更新信号 S I 3 をセレクタ 528 に出力する。

40

#### 【0220】

図 25 は、カウント値更新レジスタ 538 の例を示す説明図である。図 25 に示すように、カウント値更新レジスタ 538 は、読み出不能な 8 ビットレジスタであり、ビット 0 のみが書き可能な状態に構成されている。したがって、カウント値更新レジスタ 538 のビット 1 ~ ビット 7 に値を書き込む制御を行っても無効とされる。

#### 【0221】

50

乱数更新方式選択信号出力回路 527 は、乱数更新方式選択データを格納する乱数更新方式選択レジスタ（RTS）540 を備える。乱数更新方式選択データとは、ランダム R の値を更新する方式である各乱数更新方式のうち、いずれかの乱数更新方式を指定するためのデータである。乱数更新方式選択信号出力回路 527 は、乱数更新方式選択レジスタ 540 に乱数更新方式選択データが書き込まれたことに応じて、書き込まれた乱数更新方式選択データにより指定される乱数更新方式に対応する乱数更新方式選択信号を、セレクタ 528 に出力する。

#### 【0222】

図 26（A）は、乱数更新方式選択レジスタ 540 の例を示す説明図である。図 26（A）に示すように、乱数更新方式選択レジスタ 540 は、8 ビットレジスタであり、初期値が「00h」に設定されている。また、乱数更新方式選択レジスタ 540 は、ビット 0 ~ ビット 1 が書込および読出ともに可能な状態に構成されている。また、乱数更新方式選択レジスタ 540 は、ビット 2 ~ ビット 7 が書込および読出ともに不可能な状態に構成されている。したがって、乱数更新方式選択レジスタ 540 のビット 2 ~ ビット 7 に値を書き込む制御を行っても無効とされ、ビット 2 ~ ビット 7 から読み出す値は全て「0 (= 000000b)」である。

10

#### 【0223】

図 26（B）は、乱数更新方式選択レジスタ 540 に書き込まれる乱数更新方式選択データの一例の説明図である。図 26（B）に示すように、乱数更新方式選択データは、2 ビットのデータから構成される。乱数更新方式選択データ「01b」は、第 1 の乱数更新方式を指定するために用いられる。また、乱数更新方式選択データ「10b」は、第 2 の乱数更新方式を指定するために用いられる。なお、この実施の形態では、第 1 の乱数更新方式とは、カウント値更新信号出力回路 525 からカウント値更新信号 SI3 が出力されたことをトリガとして、カウント値を更新する方式である。また、第 2 の乱数更新方式とは、クロック信号出力回路 524 から乱数発生用クロック信号 SI1 が出力されたことをトリガとして、カウント値を更新する方式である。また、乱数更新方式選択データ「01b」または「10b」が乱数更新方式選択レジスタ 540 に書き込まれた場合、乱数回路 5003 は起動可能な状態となる。一方、乱数更新方式選択データ「00b」または「11b」が乱数更新方式選択レジスタ 540 に書き込まれた場合、乱数回路 5003 は起動不能な状態となる。

20

30

#### 【0224】

セレクタ 528 は、カウント値更新信号出力回路 525 から出力されるカウント値更新信号 SI3、またはクロック信号出力回路 524 から出力される乱数発生用クロック信号 SI1 のいずれかを選択してカウンタ 521 に出力する。セレクタ 528 は、乱数更新方式選択信号出力回路 527 から第 1 の乱数更新方式に対応する乱数更新方式選択信号（第 1 の乱数更新方式選択信号ともいう）が入力されると、カウント値更新信号出力回路 525 から出力されるカウント値更新信号 SI3 を選択してカウンタ 521 に出力する。一方、セレクタ 528 は、乱数更新方式選択信号出力回路 527 から第 2 の乱数更新方式に対応する乱数更新方式選択信号（第 2 の乱数更新方式選択信号ともいう）が入力されると、クロック信号出力回路 524 から出力される乱数発生用クロック信号 SI1 を選択してカウンタ 521 に出力する。なお、セレクタ 528 は、乱数更新方式選択信号出力回路 527 から第 1 の更新方式選択信号が入力されると、カウント値更新信号出力回路 525 から出力されるカウント値更新信号 SI3 に応じて、クロック信号出力回路 524 から出力される乱数発生用クロック信号 SI1 に同期した数値データの更新を指示する数値更新指示信号を、カウンタ 521 に出力してもよい。

40

#### 【0225】

乱数回路起動信号出力回路 530 は、乱数回路起動データ「80h」を格納する乱数回路起動レジスタ（RST）541 を備える。乱数回路起動データとは、乱数回路 5003 の起動を要求するためのデータである。乱数回路起動信号出力回路 530 は、乱数回路起動レジスタ 541 に乱数回路起動データ「80h」が書き込まれると、所定の乱数回路起

50

動信号をカウンタ 521 およびクロック信号出力回路 537 に出力し、カウンタ 521 およびクロック信号出力回路 524 をオンにさせる。そして、カウンタ 521 によるカウント値の更新動作とクロック信号出力回路 524 による内部クロック信号の出力動作とを開始させることによって、乱数回路 5003 を起動させる。

#### 【0226】

図 27 は、乱数回路起動レジスタ 541 の例を示す説明図である。図 27 に示すように、乱数回路起動レジスタ 541 は、8 ビットレジスタであり、初期値が「00h」に設定されている。乱数回路起動レジスタ 541 は、ビット 7 だけが書き込みおよび読み出ともに可能な状態に構成されている。また、乱数回路起動レジスタ 541 は、ビット 0 ~ ビット 6 が書き込みおよび読み出ともに不可能な状態に構成されている。すなわち、乱数回路起動レジスタ 541 のビット 0 ~ ビット 6 に値を書き込む制御を行っても無効とされ、ビット 0 ~ ビット 6 から読み出す値は全て「0 (= 000000b)」である。

10

#### 【0227】

第 1 乱数値記憶回路 531a および第 2 乱数値記憶回路 531b は、例えば 16 ビットレジスタであり、遊技制御処理における大当たり判定用乱数の生成に用いられるハードウェア乱数であるランダム R の値を格納する。第 1 乱数値記憶回路 531a は、第 1 始動口スイッチ 13a からの検出信号をラッチ信号 SL1 として入力したことに応じて、カウンタ 521 から比較器 522 を介して出力されるカウント値 C をランダム R の値として格納する。そして、第 1 乱数値記憶回路 531a は、第 1 始動口スイッチ 13a からの検出信号をラッチ信号 SL1 として入力するごとに、カウンタ 521 が更新するカウント値 C を読み込んでランダム R の値を記憶する。また、第 2 乱数値記憶回路 531b は、第 2 始動口スイッチ 14a からの検出信号をラッチ信号 SL2 として入力したことに応じて、カウンタ 521 から比較器 522 を介して出力されるカウント値 C をランダム R の値として格納する。そして、第 2 乱数値記憶回路 531b は、第 2 始動口スイッチ 13b からの検出信号をラッチ信号 SL2 として入力するごとに、カウンタ 521 が更新するカウント値 C を読み込んでランダム R の値を記憶する。

20

#### 【0228】

なお、以下、第 1 乱数値記憶回路 531a および第 2 乱数値記憶回路 531b を包括的に表現する場合、または第 1 乱数値記憶回路 531a と第 2 乱数値記憶回路 531b とのいずれかを指す場合に、単に乱数値記憶回路 531 ともいう。

30

#### 【0229】

また、この実施の形態では、後述する乱数回路設定処理（ステップ S14 参照）が実行されるときに、乱数値記憶回路 531 は、CPU56 からラッチ信号 SL0 を入力したことに応じて、カウンタ 521 から比較器 522 を介して出力されるカウント値 C をランダム R の値として格納する。

#### 【0230】

図 28 は、乱数値記憶回路 531 の一構成例を示す回路図である。乱数値記憶回路 531 は、図 28 に示すように、2 個の AND 回路 2001, 2003 と、2 個の NOT 回路 2002, 2004 と、16 個のフリップフロップ回路 2101 ~ 2116 と、16 個の OR 回路 2201 ~ 2216 を含む。

40

#### 【0231】

図 28 に示すように、AND 回路 2001 の入力端子は、ラッチ信号生成回路 533 の出力端子と NOT 回路 2004 の出力端子とに接続され、出力端子は、NOT 回路 2002 の入力端子とフリップフロップ回路 2101 ~ 2116 のクロック端子 C1k1 ~ C1k16 とに接続されている。NOT 回路 2002 の入力端子は、AND 回路 2001 の出力端子に接続され、出力端子は、AND 回路 2003 の一方の入力端子に接続されている。

#### 【0232】

AND 回路 2003 の入力端子は、NOT 回路 2002 の出力端子と遊技制御用マイクロコンピュータ 560 が搭載する CPU56 とに接続され、出力端子は、NOT 回路 20

50

0 4 の入力端子に接続されている。NOT 回路 2 0 0 4 の入力端子は、AND 回路 2 0 0 3 の出力端子に接続され、出力端子は、AND 回路 2 0 0 1 の一方の入力端子と OR 回路 2 2 0 1 ~ 2 2 1 6 の一方の入力端子とに接続されている。

#### 【0233】

フリップフロップ回路 2 1 0 1 ~ 2 1 1 6 の入力端子 D 1 ~ D 1 6 は、比較器 5 2 2 の出力端子に接続されている。フリップフロップ回路 2 1 0 1 ~ 2 1 1 6 のクロック端子 C 1 k 1 ~ C 1 k 1 6 は、AND 回路 2 0 1 の出力端子に接続され、出力端子 Q 1 ~ Q 1 6 は、OR 回路 2 2 0 1 ~ 2 2 1 6 の他方の入力端子に接続されている。

#### 【0234】

OR 回路 2 2 0 1 ~ 2 2 1 6 の入力端子は、NOT 回路 2 0 0 4 の出力端子とフリップフロップ回路 2 1 0 1 ~ 2 1 1 6 の出力端子とに接続され、出力端子は、遊技制御用マイクロコンピュータ 5 6 0 が搭載する CPU 5 6 に接続されている。10

#### 【0235】

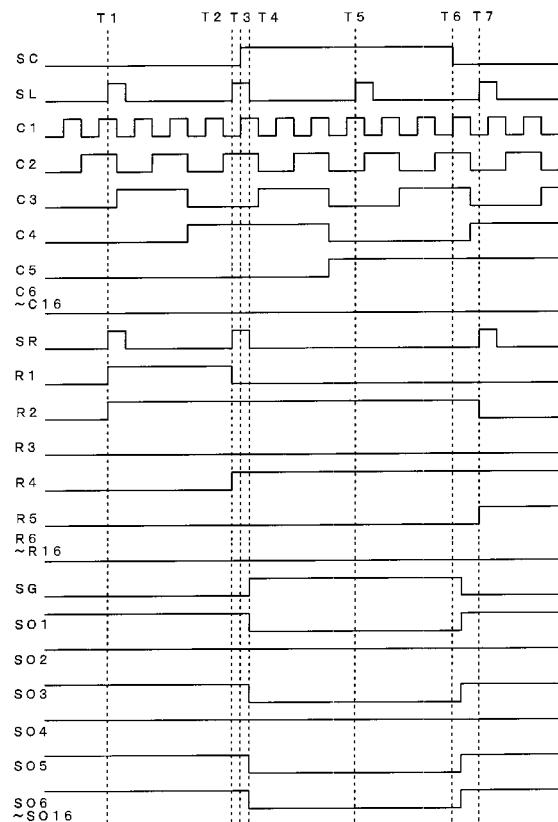

乱数値記憶回路 5 3 1 の動作について説明する。図 2 9 は、乱数値記憶回路 5 3 1 に各信号が入力されるタイミング、および乱数値記憶回路 5 3 1 が各信号を出力するタイミングを示すタイミングチャートである。図 2 9 に示すように、遊技制御用マイクロコンピュータ 5 6 0 が搭載する CPU 5 6 から出力制御信号 S C (本例では、ハイレベル信号) が入力されていない場合 (すなわち、AND 回路 2 0 3 の一方の入力端子への入力がローレベルの場合)、第 1 始動口スイッチ 1 3 a または第 2 始動口スイッチ 1 4 a からラッチ信号 S L (具体的には、第 1 始動口スイッチ 1 3 a からのラッチ信号 S L 1 、または第 2 始動口スイッチ 1 4 a からのラッチ信号 S L 2 ) が入力されると (図 2 9 に示す例では、タイミング T 1 , T 2 , T 7 のとき)、AND 回路 2 0 0 1 の 2 つの入力端子への入力はともにハイレベルとなる。そのため、AND 回路 2 0 0 1 の出力端子から出力される信号 S R はハイレベルとなる。そして、AND 回路 2 0 0 1 から出力された信号 S R は、フリップフロップ回路 2 1 0 1 ~ 2 1 1 6 のクロック端子 C 1 k 1 ~ C 1 k 1 6 に入力される。20

#### 【0236】

フリップフロップ回路 2 1 0 1 ~ 2 1 1 6 は、クロック端子 C 1 k 1 ~ C 1 k 1 6 から入力される信号 S R の立ち上がりエッヂに応答して、比較器 5 2 2 から入力端子 D 1 ~ D 1 6 を介して入力されるカウント値 C のビットデータ C 1 ~ C 1 6 を乱数値のビットデータ R 1 ~ R 1 6 としてラッチして記憶する。また、フリップフロップ回路 2 1 0 1 ~ 2 1 1 6 は、記憶するランダム R のビットデータ R 1 ~ R 1 6 を出力端子 Q 1 ~ Q 1 6 から出力する。30

#### 【0237】

出力制御信号 S C が入力されていない場合 (図 2 9 に示す例では、タイミング T 3 までの期間およびタイミング T 6 以降の期間)、AND 回路 2 0 0 3 の一方の入力端子への入力がローレベルとなるので、AND 回路 2 0 0 3 の出力端子から出力される信号 S G はローレベルとなる。AND 回路 2 0 0 3 が出力する信号 S G は、NOT 回路 2 0 0 4 において反転され、ハイレベルの信号とされる。そして、OR 回路 2 2 0 1 ~ 2 2 1 6 の一方の入力端子に、NOT 回路 2 0 0 4 からハイレベルの信号が入力される。

#### 【0238】

以上のように、OR 回路 2 2 0 1 ~ 2 2 1 6 の一方の入力端子への入力がハイレベルとなるので、他方の入力端子に入力される信号がハイレベルであるかローレベルであるかに関わらず、OR 回路 2 2 0 1 ~ 2 2 1 6 はハイレベルの信号を出力する。すなわち、入力されるランダム R のビットデータ R 1 ~ R 1 6 の値が「0」であるか「1」であるかに関わらず、OR 回路 2 2 0 1 ~ 2 2 1 6 から出力される信号 S O 1 ~ S O 1 6 は、全てハイレベル ('1') となる。そのようにすることによって、乱数値記憶回路 5 3 1 から出力される値は、常に「6 5 5 3 5 (= 1 1 1 1 1 1 1 1 1 1 1 1 1 b )」となり、乱数値記憶回路 5 3 1 からランダム R を読み出すことができない状態となる。すなわち、乱数値記憶回路 5 3 1 から乱数を読み出そうとしても、乱数値記憶回路 5 3 1 から常に同じ値「6 5 5 3 5」しか読み出せない状態となり、出力制御信号 S C が入力されていない場4050

合、乱数値記憶回路 531 は、読み出不能（ディセイブル）状態となる。

#### 【0239】

ラッチ信号生成回路 533 からラッチ信号 SL が入力されていないときに、CPU56 から出力制御信号 SC が入力されると（図 29 に示す例では、タイミング T4 からタイミング T6 までの期間）、AND 回路 2003 の 2 つの入力端子への入力がともにハイレベルとなるので、AND 回路 2003 の出力端子から出力される信号 SG はハイレベルとなる。AND 回路 2003 が出力する信号 SG は、NOT 回路 2004 において反転され、ローレベルの信号とされる。そして、OR 回路 2201～2216 の一方の入力端子に、NOT 回路 2004 からローレベルの信号が入力される。

#### 【0240】

以上のように、OR 回路 2201～2216 の一方の入力端子への入力がローレベルとなるので、他方の入力端子に入力される信号がハイレベルの場合、OR 回路 2201～2216 の出力端子からハイレベルの信号が出力される。また、OR 回路 2201～2216 の他方の入力端子に入力される信号がローレベルの場合、OR 回路 2201～2216 からローレベルの信号が出力される。すなわち、OR 回路 2201～2216 の他方の入力端子に入力されるランダム R のビットデータ R1～R16 の値は、OR 回路 2201～2216 の出力端子からそのまま（すなわち、ビットデータ R1～R16 の値が「1」のときは「1」が、「0」のときは「0」）出力される。そのようにすることによって、乱数値記憶回路 531 からのランダム R の読み出しが可能となる。すなわち、出力制御信号 SC が入力されている場合、乱数値記憶回路 531 は、読み出可能（イネイブル）状態となる。

10

20

#### 【0241】

ただし、CPU56 から出力制御信号 SC が入力される前に、第 1 始動口スイッチ 13a または第 2 始動口スイッチ 14a からラッチ信号 SL が入力されている場合、AND 回路 2003 の一方の入力端子への入力がローレベルとなるので、ラッチ信号 SL が入力されている状態のまままで、出力制御信号 SC が入力されても（図 29 に示す例では、タイミング T3 からタイミング T4 の期間）、AND 回路 2003 の出力端子から出力される信号 SG はローレベルのままとなる。AND 回路 2003 が出力する信号 SG は、NOT 回路 2004 において反転され、ハイレベルの信号とされる。そして、OR 回路 2201～2216 の一方の入力端子に、NOT 回路 2004 からハイレベルの信号が入力される。

#### 【0242】

以上のように、OR 回路 2201～2216 の一方の入力端子への入力がハイレベルとなるので、他方の入力端子に入力される信号がハイレベルであるかローレベルであるかに関わらず、OR 回路 2201～2216 から出力される信号 SO1～SO16 は全てハイレベルとなる。そして、出力制御信号 SC が入力されているにも関わらず、乱数値記憶回路 531 からランダム R を読み出すことができない状態のままとなる。すなわち、ラッチ信号 SL が入力されている場合、乱数値記憶回路 531 は、出力制御信号 SC を受信不可能な状態となる。

30

#### 【0243】