(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7559552号

(P7559552)

(45)発行日 令和6年10月2日(2024.10.2)

(24)登録日 令和6年9月24日(2024.9.24)

(51)国際特許分類

H 03 B 5/32 (2006.01)

F I

H 03 B

5/32

J

請求項の数 8 (全23頁)

(21)出願番号 特願2020-218552(P2020-218552)

(22)出願日 令和2年12月28日(2020.12.28)

(65)公開番号 特開2022-103739(P2022-103739)

A)

(43)公開日 令和4年7月8日(2022.7.8)

審査請求日 令和5年11月6日(2023.11.6)

(73)特許権者 000002369

セイコーエプソン株式会社

東京都新宿区新宿四丁目1番6号

(74)代理人 100179475

弁理士 仲井 智至

(74)代理人 100216253

弁理士 松岡 宏紀

(74)代理人 100225901

弁理士 今村 真之

(72)発明者 山本 壮洋

長野県諏訪市大和3丁目3番5号 セイ

コーエプソン株式会社内

審査官 石田 昌敏

最終頁に続く

(54)【発明の名称】 回路装置及び発振器

## (57)【特許請求の範囲】

## 【請求項1】

振動子の一端に電気的に接続される第1ノードと、前記振動子の他端に電気的に接続される第2ノードとに電気的に接続され、前記振動子を発振させることで発振信号を生成する発振回路と、

前記第1ノードに接続され、前記第1ノードから前記発振信号が入力され、前記発振信号を波形整形したクロック信号を出力する波形整形回路と、

調整データに基づき可変に調整したバイアス電圧を前記第1ノードに供給することにより、前記クロック信号のデューティー比を調整するデューティー調整回路と、を含み、

前記発振回路は、

一端が前記第1ノードに接続され、容量値が固定である固定容量キャパシターと、

一端が前記固定容量キャパシターの他端に接続され、容量値が可変である可変容量素子と、を含み、

前記可変容量素子の一端及び他端の一方に温度補償電圧が入力され、

前記デューティー調整回路は、前記可変容量素子の一端及び他端の他方に基準電圧を供給することを特徴とする回路装置。

## 【請求項2】

請求項1に記載の回路装置において、前記デューティー調整回路は、電源ノードとグラウンドノードの間に直列接続された複数の抵抗を有し、前記複数の抵抗

により分圧された複数の分圧電圧を出力する分圧回路と、

前記複数の分圧電圧のいずれかである第1分圧電圧を前記バイアス電圧として選択し、前記複数の分圧電圧のいずれかである第2分圧電圧を前記基準電圧として選択する選択回路と、を含み、

前記温度補償電圧をV C M Pとし、前記基準電圧をV R E Fとしたときに、前記複数の分圧電圧は、V C M P - V R E Fが0Vよりも大きくなる電圧、及び、V C M P - V R E Fが0V以下になる電圧を含むことを特徴とする回路装置。

【請求項3】

請求項1又は2に記載の回路装置において、

前記調整データを記憶する不揮発性メモリーを含み、

前記デューティー調整回路は、

前記不揮発性メモリーに記憶された前記調整データにより設定される電圧の前記バイアス電圧を生成することを特徴とする回路装置。

【請求項4】

請求項1乃至3のいずれか一項に記載の回路装置において、

前記発振回路の電源電圧は、前記波形整形回路の電源電圧以上の電圧であることを特徴とする回路装置。

【請求項5】

請求項2に記載の回路装置において、

前記デューティー調整回路は、

V C M P - V R E Fが0Vよりも大きくなる前記基準電圧を供給することを特徴とする回路装置。

【請求項6】

請求項2に記載の回路装置において、

前記デューティー調整回路は、

V C M P - V R E Fが0V以下になる前記基準電圧を供給することを特徴とする回路装置。

【請求項7】

請求項1乃至6のいずれか一項に記載の回路装置において、

前記クロック信号をバッファリングして出力クロック信号を外部に出力する出力バッファー回路を含むことを特徴とする回路装置。

【請求項8】

請求項1乃至7のいずれか一項に記載の回路装置と、

前記振動子と、

を含むことを特徴とする発振器。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、回路装置及び発振器等に関する。

【背景技術】

【0002】

従来より、水晶振動子等の振動子を発振させる発振回路を有する回路装置が知られている。このような回路装置では、発振信号に基づき生成されるクロック信号のデューティー比の高精度化が望まれる。例えば特許文献1では、電源電圧の2分の1程度のバイアス電圧を出力するバイアス回路が、出力回路の入力端子に設けられており、これにより振幅の高電圧側又は低電圧側での波形の歪みを高いマージンで低減し、出力波形のデューティー比を50%に調整し易くすることが可能な発振回路を実現している。

【先行技術文献】

【特許文献】

【0003】

10

20

30

40

50

【文献】特開 2008 - 35302 号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、特許文献 1 の発振回路では、出力回路に入力される信号の波形自体に非線形の歪みが生じる場合などにおいて、クロック信号のデューティー比を高精度に調整することができなかった。

【課題を解決するための手段】

【0005】

本開示の一態様は、振動子の一端に電気的に接続される第 1 ノードと、前記振動子の他端に電気的に接続される第 2 ノードとに電気的に接続され、前記振動子を発振させることで発振信号を生成する発振回路と、前記第 1 ノードに接続され、前記第 1 ノードから前記発振信号が入力され、前記発振信号を波形整形したクロック信号を出力する波形整形回路と、調整データに基づき可変に調整したバイアス電圧を前記第 1 ノードに供給することにより、前記クロック信号のデューティー比を調整するデューティー調整回路と、を含む回路装置に関係する。

10

【0006】

また本開示の他の態様は、上記に記載の回路装置と、前記振動子と、を含む発振器に関係する。

【図面の簡単な説明】

20

【0007】

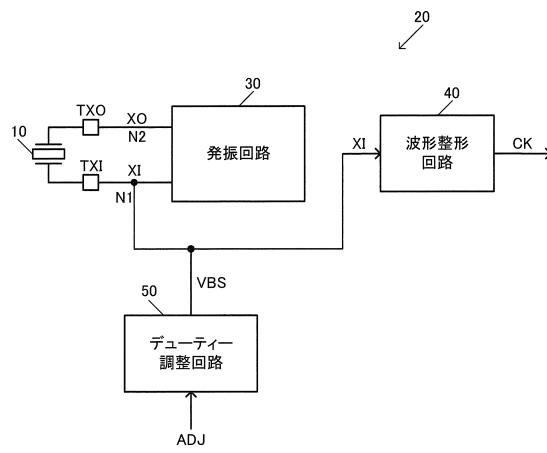

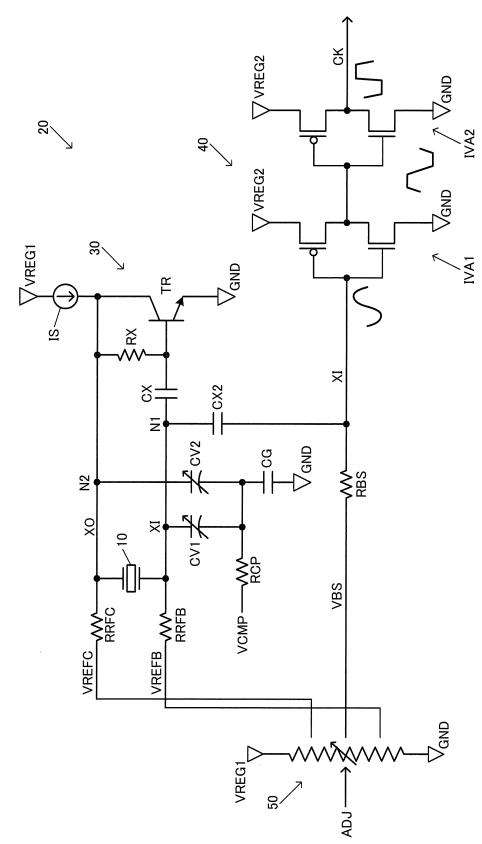

【図 1】本実施形態の回路装置の構成例。

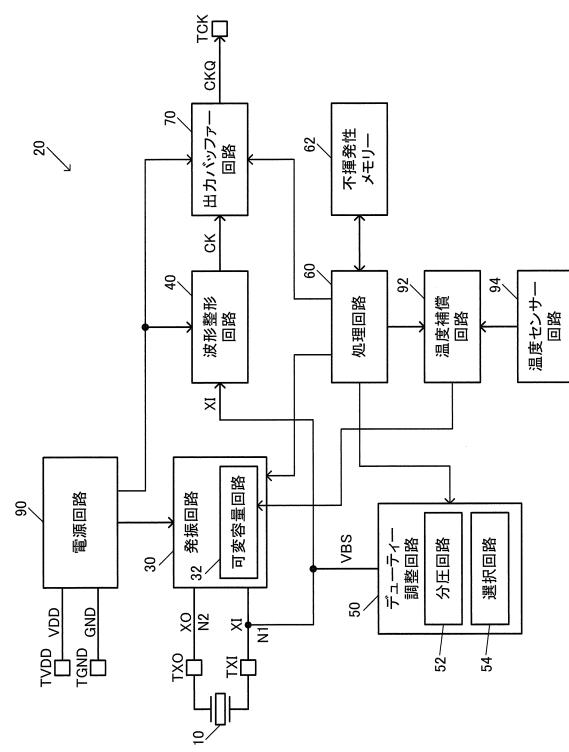

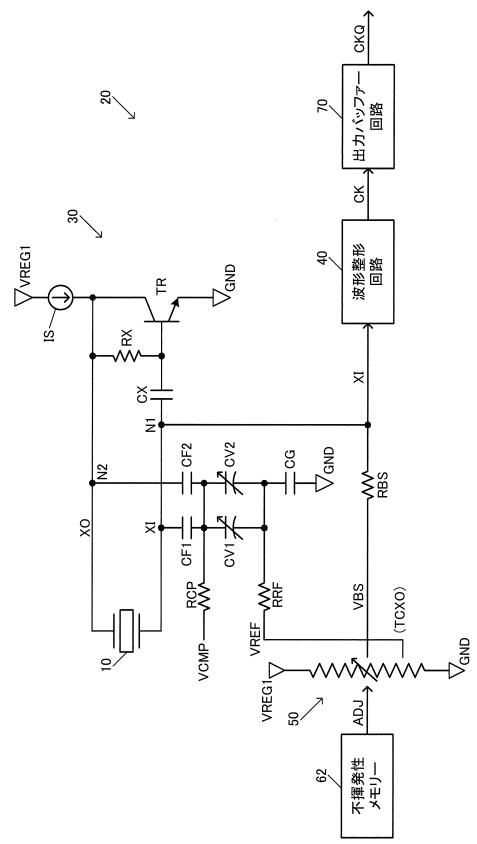

【図 2】本実施形態の回路装置の詳細な構成例。

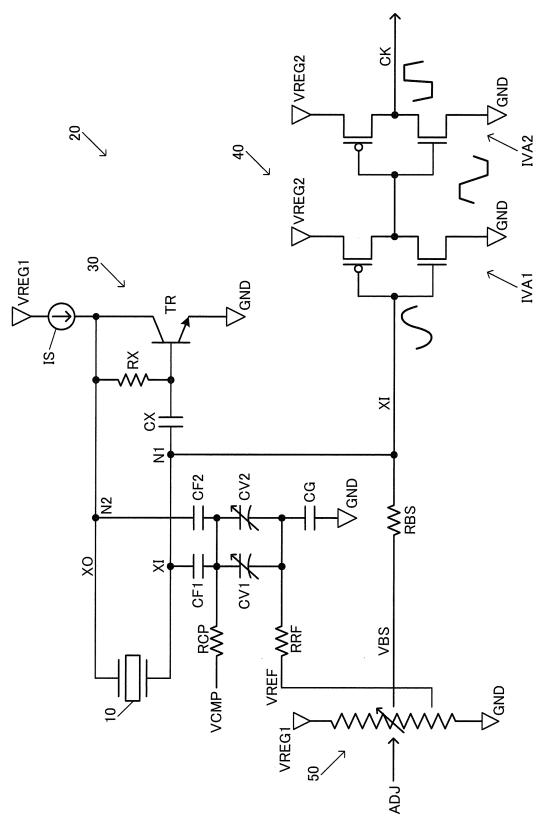

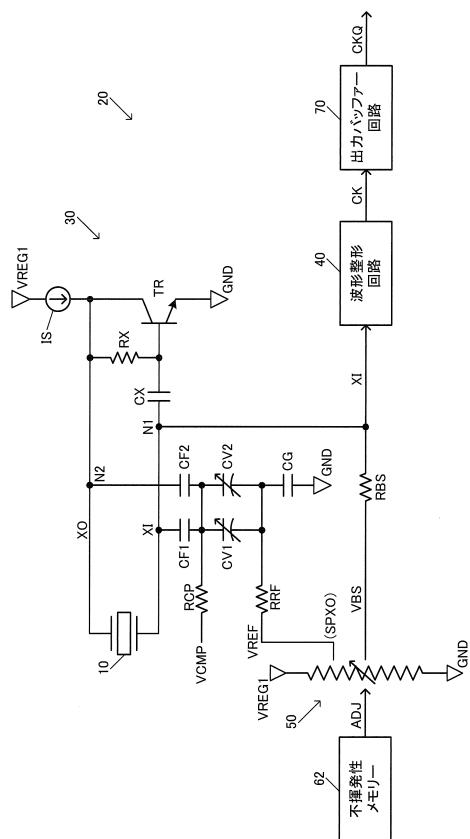

【図 3】本実施形態の回路装置の更に詳細な構成例。

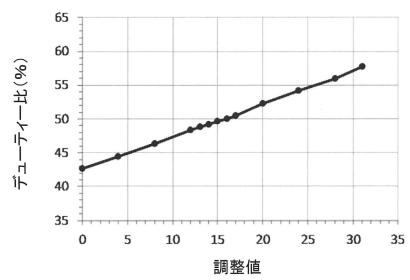

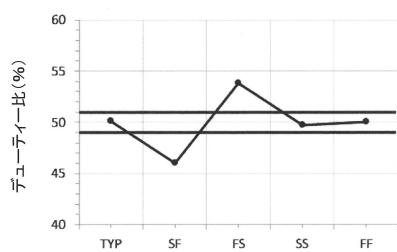

【図 4】調整データの調整値とデューティー比の関係を示すグラフ。

【図 5】クロック信号のデューティー比のプロセス変動を示すグラフ。

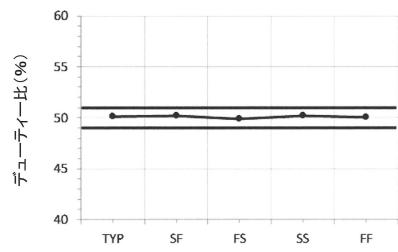

【図 6】デューティー調整回路のデューティー調整を行った場合のデューティー比のプロセス変動を示すグラフ。

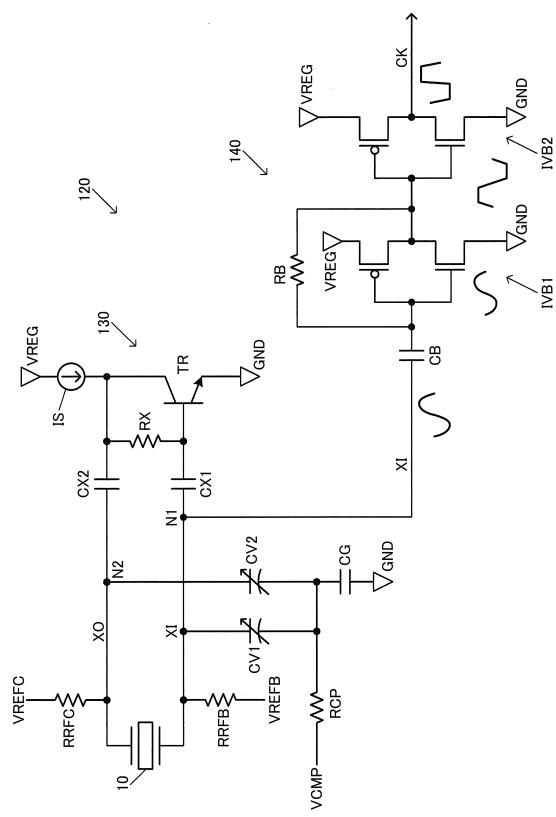

【図 7】本実施形態の第 1 比較例の回路装置の構成例。

30

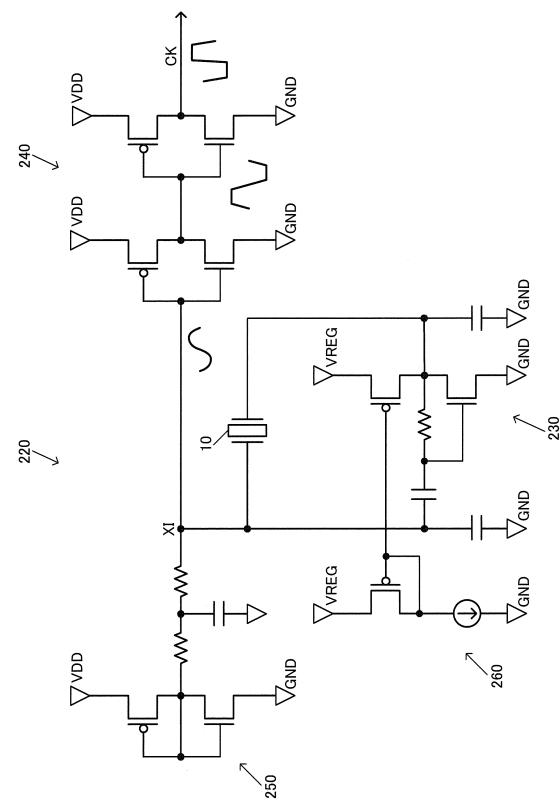

【図 8】本実施形態の第 2 比較例の回路装置の構成例。

【図 9】本実施形態の回路装置の変形例。

【図 10】本実施形態の回路装置の変形例。

【図 11】本実施形態の回路装置の変形例。

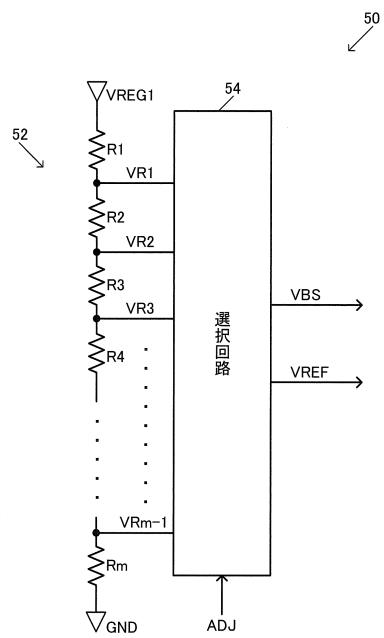

【図 12】デューティー調整回路の構成例。

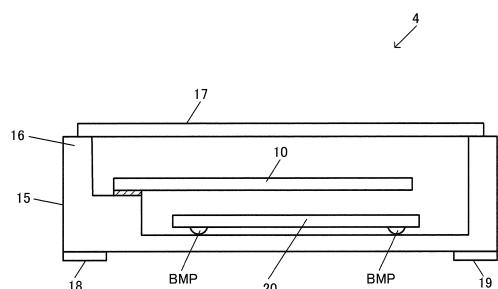

【図 13】発振器の構造例。

【発明を実施するための形態】

【0008】

以下、本実施形態について説明する。なお、以下に説明する本実施形態は、特許請求の範囲の記載内容を不当に限定するものではない。また本実施形態で説明される構成の全てが必須構成要素であるとは限らない。

40

【0009】

1. 回路装置

図 1 に本実施形態の回路装置 20 の構成例を示す。本実施形態の回路装置 20 は、発振回路 30 と波形整形回路 40 とデューティー調整回路 50 を含む。また後述の図 13 で説明するように本実施形態の発振器 4 は、振動子 10 と回路装置 20 を含む。振動子 10 は回路装置 20 に電気的に接続されている。例えば振動子 10 及び回路装置 20 を収納するパッケージの内部配線、ボンディングワイヤー又は金属バンプ等を用いて、振動子 10 と回路装置 20 は電気的に接続されている。

【0010】

振動子 10 は、電気的な信号により機械的な振動を発生する素子である。振動子 10 は

50

、例えば水晶振動片などの振動片により実現できる。例えば振動子 10 は、カット角が A T カットや S C カットなどの厚みすべり振動する水晶振動片、音叉型水晶振動片、或いは双音叉型水晶振動片などにより実現できる。例えば振動子 10 は、恒温槽を備えない温度補償型水晶発振器 (T C X O) に内蔵されている振動子であってもよいし、恒温槽を備える恒温槽型水晶発振器 (O C X O) に内蔵されている振動子であってもよい。或いは振動子 10 は、S P X O (Simple Packaged Crystal Oscillator) の発振器に内蔵される振動子であってもよい。なお本実施形態の振動子 10 は、例えば厚みすべり振動型、音叉型、又は双音叉型以外の振動片や、水晶以外の材料で形成された圧電振動片などの種々の振動片によっても実現できる。例えば振動子 10 として、S A W (Surface Acoustic Wave) 共振子や、シリコン基板を用いて形成されたシリコン製振動子としてのM E M S (Micro Electro Mechanical Systems) 振動子等を採用してもよい。

#### 【0011】

回路装置 20 は、I C (Integrated Circuit) と呼ばれる集積回路装置である。例えば回路装置 20 は、半導体プロセスにより製造される I C であり、半導体基板上に回路素子が形成された半導体チップである。

#### 【0012】

発振回路 30 は振動子 10 を発振させる回路である。例えば発振回路 30 は、振動子 10 の一端に電気的に接続される第 1 ノード N 1 と、振動子 10 の他端に電気的に接続される第 2 ノード N 2 とに電気的に接続され、振動子 10 を発振させることで発振信号 X I 、X O を生成する。具体的には、発振回路 30 は、振動子 10 の一端に電気的に接続される端子 T X I と、振動子 10 の他端に電気的に接続される端子 T X O に電気的に接続され、振動子 10 を発振させることで発振信号 X I 、X O を生成する。端子 T X I は第 1 端子であり、端子 T X O は第 2 端子である。端子 T X I 、T X O は I C である回路装置 20 の例えばパッドである。発振回路 30 は、例えば、端子 T X I と端子 T X O との間に設けられた発振用の駆動回路と、キャパシターや抵抗などの受動素子により実現できる。駆動回路は、例えばC M O S のインバーター回路やバイポーラトランジスターにより実現できる。駆動回路は、発振回路 30 のコア回路であり、駆動回路が、振動子 10 を電圧駆動又は電流駆動することで、振動子 10 を発振させる。発振回路 30 としては、例えばインバーター型、ピアース型、コルピツ型、又はハートレー型などの種々のタイプの発振回路を用いることができる。また発振回路 30 には、可変容量回路が設けられ、この可変容量回路の容量の調整により、発振周波数を調整できるようになっている。可変容量回路は、例えばバラクターなどの可変容量素子により実現できる。或いは可変容量回路を、容量値がバイナリーに重み付けされたキャパシターアレイと、キャパシターアレイに接続されるスイッチアレイとにより実現することも可能である。可変容量回路は、例えば端子 T X I が接続される第 1 信号線に電気的に接続される。発振回路 30 は、端子 T X I が接続される第 1 信号線に電気的に接続される第 1 可変容量回路と、端子 T X O が接続される第 2 信号線に電気的に接続される第 2 可変容量回路を有していてもよい。なお本実施形態における接続は電気的な接続である。電気的な接続は、電気信号が伝達可能に接続されていることであり、電気信号による情報の伝達が可能となる接続である。電気的な接続は受動素子等を介した接続であってもよい。

#### 【0013】

波形整形回路 40 は、発振信号 X I の波形整形を行う回路であり、発振信号 X I が入力されて、クロック信号 C K を出力するバッファー回路である。例えば波形整形回路 40 は、第 1 ノード N 1 に接続され、第 1 ノード N 1 から発振信号 X I が入力され、発振信号 X I を波形整形したクロック信号 C K を出力する。例えば波形整形回路 40 は、正弦波の発振信号 X I を波形整形して、矩形波のクロック信号 C K を出力する。波形整形回路 40 は、例えば複数のインバーター回路などにより構成できる。

#### 【0014】

デューティー調整回路 50 はクロック信号 C K のデューティー比を調整する回路である。デューティー調整回路 50 は、バイアス電圧 V B S を調整するバイアス電圧調整回路と

10

20

30

40

50

言うこともできる。例えばデューティー調整回路 50 は、調整データ A D J に基づき可変に調整したバイアス電圧 V B S を第 1 ノード N 1 に供給することにより、クロック信号 C K のデューティー比を調整する。クロック信号 C K のデューティー比が調整されることで、後述の図 2 の回路装置 20 の出力クロック信号 C K Q のデューティー比も調整されることになる。デューティー比はデューティーサイクルとも呼ばれる。なお本実施形態ではデューティー比を単にデューティーと記載する場合もある。デューティー調整回路 50 は、例えば調整データ A D J が第 1 調整値である場合には、第 1 調整値に対応する第 1 電圧値のバイアス電圧 V B S を生成し、調整データ A D J が第 2 調整値である場合には、第 2 調整値に対応する第 2 電圧値のバイアス電圧 V B S を生成する。即ちデューティー調整回路 50 は、調整データ A D J により電圧値が可変に設定されるバイアス電圧 V B S を、第 1 ノード N 1 に供給する。

#### 【 0 0 1 5 】

デューティー調整回路 50 が、発振信号 X I の出力ノードである第 1 ノード N 1 にバイアス電圧 V B S を供給することで、発振信号 X I は、バイアス電圧 V B S を中心に変化する交流信号になる。例えば発振信号 X I は、不図示のキャパシターにより D C カットされた交流信号となっており、デューティー調整回路 50 からのバイアス電圧 V B S により、この交流信号の中心電圧が設定される。そして、このようにバイアス電圧 V B S が設定された発振信号 X I が、波形整形回路 40 に入力されて、波形整形されることで、矩形波のクロック信号 C K が生成される。

#### 【 0 0 1 6 】

この場合に調整データ A D J は、クロック信号 C K のデューティー比が例えば 50 % になるような調整値に設定されている。なおクロック信号 C K のデューティー比は出力クロック信号 C K Q のデューティー比でもある。例えば半導体の製造プロセスの変動がティピカルである場合には、バイアス電圧 V B S が、波形整形回路 40 の電源電圧の 1 / 2 程度の電圧に設定されるような調整値に調整データ A D J が設定される。また波形整形回路 40 が有するインバーター回路を構成する P 型トランジスターと N 型トランジスターのプロセス変動が Fast や Slow であっても、クロック信号 C K のデューティー比が 50 % になるように、調整データ A D J の調整値が設定される。こうすることで、プロセス変動があった場合にも、デューティー比が 50 % になるように調整されたクロック信号 C K を生成できるようになる。

#### 【 0 0 1 7 】

図 2 に本実施形態の回路装置 20 の詳細な構成例を示す。図 2 に示すように回路装置 20 は、図 1 の構成に加えて、処理回路 60 、不揮発性メモリー 62 、出力バッファー回路 70 、電源回路 90 、温度補償回路 92 、温度センサー回路 94 を含むことができる。

#### 【 0 0 1 8 】

処理回路 60 は、種々の制御処理を行う制御回路であり、例えばロジック回路により実現される。例えば処理回路 60 は、回路装置 20 の全体の制御を行ったり、回路装置 20 の動作シーケンスの制御を行う。また処理回路 60 は、発振回路 30 、出力バッファー回路 70 、温度補償回路 92 等の回路装置 20 の各回路プロックの制御を行う。また処理回路 60 は、不揮発性メモリー 62 の読み出し制御や書き込み制御を行う。処理回路 60 は、例えばゲートアレイ等の自動配置配線による A S I C ( Application Specific Integrated Circuit ) の回路により実現できる。

#### 【 0 0 1 9 】

不揮発性メモリー 62 は、回路装置 20 で用いられる各種の情報を記憶する。不揮発性メモリー 62 は、例えば F A M O S ( Floating gate Avalanche injection MOS ) メモリー又は M O N O S ( Metal-Oxide- Nitride-Oxide-Silicon ) メモリー等の E E P R O M により実現できるが、これに限らず、O T P ( One Time Programmable ) メモリー又はヒューズ型 R O M 等であってもよい。

#### 【 0 0 2 0 】

不揮発性メモリー 62 は、図 1 の調整データ A D J を記憶する。そして不揮発性メモリ

10

20

30

40

50

－62から処理回路60を介して読み出された調整データADJが、デューティー調整回路50に入力され、デューティー調整回路50は、調整データADJに応じて可変に設定されるバイアス電圧VBSを生成して第1ノードN1に供給する。このように本実施形態の回路装置20は、調整データADJを記憶する不揮発性メモリー62を含み、デューティー調整回路50は、不揮発性メモリー62に記憶された調整データADJにより設定される電圧のバイアス電圧VBSを生成する。なお不揮発性メモリー62は、後述するように温度補償用の情報についても記憶する。

#### 【0021】

出力バッファー回路70は、波形整形回路40からのクロック信号CKをバッファリングして出力クロック信号CKQとして出力する。即ち出力バッファー回路70は、発振信号XIに基づく出力クロック信号CKQをクロック端子TCKに出力する。そして、この出力クロック信号CKQがクロック端子TCKから発振器4の外部端子を介して外部に出力される。例えば出力バッファー回路70は、シングルエンドのCMOSの信号形式で出力クロック信号CKQを出力する。例えば不図示の出力イネーブル端子を介して入力される出力イネーブル信号がアクティブである場合に、出力バッファー回路70は出力クロック信号CKQを出力する。一方、出力バッファー回路70は、出力イネーブル信号が非アクティブである場合には、出力クロック信号CKQを例えばローレベルなどの固定電圧レベルに設定する。これによりクロック端子TCKの電圧レベルが固定電圧レベルに設定される。なお信号がアクティブとは、例えば正論理の場合にはハイレベルであり、負論理の場合にはローレベルである。また信号が非アクティブとは、例えば正論理の場合にはローレベルであり、負論理の場合にはハイレベルである。また図2では出力バッファー回路70は、1つの出力クロック信号CKQを出力しているが、クロック信号CKをバッファリングすることで複数の出力クロック信号を出力するようにしてもよい。この場合に、複数の出力クロック信号の中には、例えば位相が異なるクロック信号、具体的には位相が180度異なるクロック信号が含まれていてもよい。また出力バッファー回路70が、CMOS以外の信号形式で出力クロック信号CKQを出力するようにしてもよい。

10

20

30

#### 【0022】

電源回路90は、電源端子TVD0からの電源電圧VDDが供給され、グランド端子TGN0からグランド電圧であるGN0が供給されて、回路装置20の各回路ブロックに対して各回路ブロック用の電源電圧を供給する。例えば電源回路90は、レギュレーターを有しており、レギュレーターは、電源電圧VDDに基づき生成したレギュレート電源電圧を回路装置20の各回路ブロックに供給する。例えば電源回路90は、発振回路30に対して第1レギュレート電源電圧を供給し、波形整形回路40や出力バッファー回路70に第1レギュレート電源電圧とは異なる第2レギュレート電源電圧を供給する。また電源回路90は、デューティー調整回路50、処理回路60、不揮発性メモリー62、温度補償回路92、温度センサー回路94に対しても各種のレギュレート電源電圧を供給する。また電源回路90は基準電圧生成回路や基準電流生成回路も有している。

#### 【0023】

温度補償回路92は、発振回路30の発振周波数の温度補償を行う。発振周波数の温度補償は発振回路30の発振信号XI、XOの温度補償である。具体的には温度補償回路92は、温度センサー回路94からの温度検出情報に基づいて温度補償を行う。例えば温度補償回路92は、温度センサー回路94からの温度検出電圧に基づいて温度補償電圧を生成し、生成された温度補償電圧を発振回路30に出力することで、発振回路30の発振周波数の温度補償を行う。例えば温度補償回路92は、発振回路30が有する可変容量回路32に対して、可変容量回路32の容量制御電圧となる温度補償電圧を出力し、可変容量回路32の容量を調整することで、温度補償を行う。この場合には発振回路30の可変容量回路32は、バラクター等の可変容量素子により実現される。温度補償は、温度変動による発振周波数の変動を抑制して補償する処理である。例えば温度補償回路92は、多項式近似によるアナログ方式の温度補償を行う。例えば振動子10の周波数温度特性を補償する温度補償電圧が多項式により近似される場合に、温度補償回路92は、当該多項式の

40

50

係数情報に基づいてアナログ方式の温度補償を行う。アナログ方式の温度補償は、例えばアナログ信号である電流信号や電圧信号の加算処理等により実現される温度補償である。具体的には不揮発性メモリー 6 2 には、温度補償用の多項式の係数情報が記憶されており、処理回路 6 0 が、この係数情報を不揮発性メモリー 6 2 から読み出して、例えば温度補償回路 9 2 のレジスターに設定する。そして温度補償回路 9 2 は、レジスターに設定された係数情報に基づいてアナログ方式の温度補償を行う。なお温度補償回路 9 2 がデジタル方式の温度補償を行うようにしてもよい。この場合には温度補償回路 9 2 は、温度センサー回路 9 4 の温度検出情報である温度検出データに基づいてデジタルの温度補償処理を行う。例えば温度補償回路 9 2 は、温度検出データに基づいて周波数調整データを求める。そして、求められた周波数調整データに基づいて、発振回路 3 0 の可変容量回路 3 2 の容量値が調整されることで、発振回路 3 0 の発振周波数の温度補償処理が実現される。この場合には発振回路 3 0 の可変容量回路は、バイナリーに重み付けされた複数のキャパシターを有するキャパシターアレイと、スイッチアレイとにより実現される。また不揮発性メモリー 6 2 は、温度検出データと周波数調整データの対応を表すルックアップテーブルを記憶しており、温度補償回路 9 2 は、処理回路 6 0 により不揮発性メモリー 6 2 から読み出されたルックアップテーブルを用いて、温度データから周波数調整データを求める温度補償処理を行う。

#### 【 0 0 2 4 】

温度センサー回路 9 4 は、温度を検出するセンサー回路である。具体的には温度センサー回路 9 4 は、環境の温度に応じて変化する温度依存電圧を、温度検出電圧として出力する。例えば温度センサー回路 9 4 は、温度依存性を有する回路素子を利用して温度検出電圧を生成する。具体的には温度センサー回路 9 4 は、P N 接合の順方向電圧が有する温度依存性を用いることで、温度に依存して電圧値が変化する温度検出電圧を出力する。P N 接合の順方向電圧としては、例えばバイポーラートランジスターのベース・エミッター間電圧などを用いることができる。なおデジタル方式の温度補償処理を行う場合には、温度センサー回路 9 4 は、環境温度などの温度を測定し、その結果を温度検出データとして出力する。温度検出データは、温度に対して例えば単調増加又は単調減少するデータである。

#### 【 0 0 2 5 】

またデューティー調整回路 5 0 は分圧回路 5 2 と選択回路 5 4 を含む。分圧回路 5 2 は、電源電圧とグランド電圧の電圧分圧を行うことで、複数の分圧電圧を出力する。例えば分圧回路 5 2 は、電源ノードとグランドノードの間に直列接続された複数の抵抗を有し、複数の抵抗により分圧された複数の分圧電圧を出力する。即ち分圧回路 5 2 は抵抗ラダー回路等により実現される。電源ノードは電源電圧が供給されるノードであり、グランドノードはグランドが供給されるノードである。そして選択回路 5 4 は、複数の分圧電圧のいずれかである第 1 分圧電圧をバイアス電圧 V B S として選択する。即ち選択回路 5 4 は、調整データ A D J に基づいて、複数の分圧電圧の第 1 分圧電圧をバイアス電圧 V B S として選択する。また選択回路 5 4 は、複数の分圧電圧のいずれかである第 2 分圧電圧を後述する基準電圧 V R E F として選択する。

#### 【 0 0 2 6 】

図 3 に回路装置 2 0 の更に詳細な構成例を示す。図 3 では発振回路 3 0 は、電流源 I S 、バイポーラートランジスター T R 、抵抗 R X 、キャパシター C X を含む。電流源 I S とバイポーラートランジスター T R は V R E G 1 の電源ノードとグランドノードとの間に直列に設けられる。これらの電流源 I S 、バイポーラートランジスター T R により発振回路 3 0 の駆動回路が構成される。電流源 I S は例えばバイアス電圧がゲートに入力される C M O S のトランジスターなどにより実現できる。抵抗 R X は、バイポーラートランジスター T R のコレクターノードとベースノードとの間に設けられる。キャパシター C X は、バイポーラートランジスター T R のベースノードと第 1 ノード N 1 との間に設けられる。

#### 【 0 0 2 7 】

また図 3 では、発振回路 3 0 は、図 2 の可変容量回路 3 2 として、バラクター等により実現される可変容量素子 C V 1 、 C V 2 と、容量値が固定である固定容量のキャパシター

10

20

30

40

50

CF1、CF2を含む。具体的には発振回路30は、一端が第1ノードN1に接続される固定容量のキャパシターCF1と、一端が固定容量のキャパシターCF1の他端に接続され、容量値が可変である可変容量素子CV1を含む。また発振回路30は、一端が第2ノードN2に接続される固定容量のキャパシターCF2と、一端が固定容量のキャパシターCF2の他端に接続され、容量値が可変である可変容量素子CV2を含む。可変容量素子CV1、CV2の他端とグランドノードとの間には、キャパシターCGが設けられる。そして図2の温度補償回路92からの温度補償電圧VCMRが抵抗RCRを介して、可変容量素子CV1、CV2の一端に供給される。また基準電圧VREFが抵抗RRFを介して、可変容量素子CV1、CV2の他端に供給される。このようにすることで、可変容量素子CV1、CV2に対して、温度補償電圧VCMRと基準電圧VREFの電圧差に対応する電圧が印加される。これにより可変容量素子CV1、CV2が温度補償電圧VCMRに応じた容量に設定されて、発振回路30の発振周波数の温度補償が実現される。なお図3では、バイアス電圧VBSを供給するデューティー調整回路50が、この基準電圧VREFも供給している。

#### 【0028】

デューティー調整回路50は、VREG1の電源ノードとグランドノードとの間に設けられるラダー抵抗回路により実現され、ラダー抵抗回路による分圧電圧であるバイアス電圧VBSを出力する。またデューティー調整回路50は、上述のように温度補償用の基準電圧VREFを出力する。そしてバイアス電圧VBSは、抵抗RBSを介して第1ノードN1に供給される。このバイアス電圧VBSにより、交流信号である発振信号XIの中心電圧が設定され、バイアス電圧VBSを中心に変化する例えば正弦波の発振信号XIが波形整形回路40に入力されるようになる。

#### 【0029】

波形整形回路40は、バッファーハイゲートとなる複数のインバーター回路IV A1、IV A2を含む。インバーター回路IV A1、IV A2の各々は、VREG2の電源ノードとグランドノードとの間に直列に設けられたP型トランジスター及びN型トランジスターにより構成される。そしてバイアス電圧VBSによりバイアス点が設定された発振信号XIが、波形整形回路40の初段のインバーター回路IV A1に対して入力信号として入力される。即ち発振信号XIが、インバーター回路IV A1を構成するP型トランジスターのゲートとN型トランジスターのゲートに入力される。そしてインバーター回路IV A1の出力信号が、次段のインバーター回路IV A2に入力され、インバーター回路IV A2がクロック信号CKを出力する。これにより発振信号XIを波形整形した矩形波のクロック信号CKが波形整形回路40から出力されるようになる。なお、一例としては、温度補償電圧VCMRは例えば0.9Vの電圧を中心として、温度検出結果に応じて変化する電圧である。基準電圧VREFは例えば0.3V~0.4V程度の電圧である。VREG1の電源電圧は例えば1.2Vであり、VREG2の電源電圧は例えば1.0Vである。バイアス電圧VBSは、例えば波形整形回路40のVREG2の電源電圧の1/2程度の電圧である0.5Vを中心に例えば±0.1Vの範囲で調整される電圧である。

#### 【0030】

以上のように本実施形態の回路装置20は、振動子10に接続される第1ノードN1及び第2ノードN2に接続され、発振信号XI、XOを生成する発振回路30と、第1ノードN1から発振信号XIが入力され、クロック信号CKを出力する波形整形回路40と、調整データADJに基づき可変に調整したバイアス電圧VBSを第1ノードN1に供給するデューティー調整回路50を含む。そして、調整データADJにより可変に調整されるバイアス電圧VBSを中心に変化する発振信号XIが、波形整形回路40に入力されて波形整形されることで、クロック信号CKのデューティー比が調整されるようになる。このようにすれば、波形整形回路40を構成するP型トランジスターとN型トランジスターのしきい値電圧等のプロセス変動や、発振波形の歪み具合や、或いは後段の回路でデューティー比のズレを加味して、クロック信号CKのデューティー比を調整できるようになり、回路装置20からの出力クロック信号CKQのデューティー比も調整できるようになる。

これによりデューティー比を例えれば 50 % に近づけることが可能になり、高精度なデューティー調整を実現できるようになる。

【 0 0 3 1 】

例えば図 4 は調整データ A D J の調整値とデューティー比の関係を示すグラフである。図 4 では例えば 5 ビットの調整データ A D J により  $50\% \pm 8\%$  を例えれば 32 段階で刻むようなデューティー調整が行われ、分解能が 0.4 % のデューティー調整が行われる。

【 0 0 3 2 】

図 5 はデューティー調整回路 50 によるデューティー調整を行わなかった場合のデューティー比のプロセス変動のコーナーシミュレーション結果を示すグラフである。ここで T Y P はティピカルケースである。S F は、N 型トランジスターが S l o w であり、P 型トランジスターが F a s t であるケースであり、F S は、N 型トランジスターが F a s t であり、P 型トランジスターが S l o w であるケースである。S S は、N 型トランジスター及び P 型トランジスターが共に S l o w であるケースであり、F F は、N 型トランジスター及び P 型トランジスターが共に F a s t であるケースである。図 5 に示すように、半導体の製造プロセスの変動により、デューティー比は  $50\% \pm 5\%$  程度の範囲で変動する。

10

【 0 0 3 3 】

一方、図 6 はデューティー調整回路 50 によるデューティー調整を行った場合のデューティー比のプロセス変動のコーナーシミュレーション結果を示すグラフである。図 6 に示すように、デューティー調整回路 50 が調整データ A D J に基づき可変に設定されるバイアス電圧 V B S を供給することで、例えばデューティー比の変動が  $50\% \pm 1\%$  以内の範囲になるというような高精度なデューティー調整を実現できるようになる。

20

【 0 0 3 4 】

図 7 に本実施形態の第 1 比較例の回路装置 120 を示す。第 1 比較例の回路装置 120 の発振回路 130 では、第 1 ノード N 1 とバイポーラトランジスター T R のベースノードとの間のキャパシター C X 1 に加えて、第 2 ノード N 2 とバイポーラトランジスター T R のコレクターノードとの間にキャパシター C X 2 が設けられている。また可変容量素子 C V 1 は、一端が第 1 ノード N 1 に接続され、他端が温度補償電圧 V C M P の供給ノードに接続され、可変容量素子 C V 2 は、一端が第 2 ノード N 2 に接続され、他端が温度補償電圧 V C M P の供給ノードに接続される。また発振信号 X I のノードである第 1 ノード N 1 に対して基準電圧 V R E F B が供給され、発振信号 X O のノードである第 2 ノード N 2 に対して基準電圧 V R E F C が供給される。これにより発振信号 X I は、基準電圧 V R E F B を中心に変化する発振信号になり、発振信号 X O は、基準電圧 V R E F C を中心に変化する発振信号になる。基準電圧 V R E F B は例えば 0.4 V であり、基準電圧 V R E F C は例えば 1.2 V である。

30

【 0 0 3 5 】

そして図 7 の第 1 比較例では、第 1 ノード N 1 と波形整形回路 140 の入力ノードとの間に D C カット用のキャパシター C B が設けられている。これにより、発振信号 X I の D C 成分がカットされ、A C 成分が波形整形回路 140 に入力されるようになる。そして波形整形回路 140 はインバーター回路 I V B 1、I V B 2 を含み、初段のインバーター回路 I V B 1 は、その出力ノードと入力ノードとの間に帰還抵抗 R B が設けられている。このような帰還抵抗 R B を設けることで、初段のインバーター回路 I V B 1 は、自己バイアスによりバイアス点が設定されるようになる。

40

【 0 0 3 6 】

このように図 7 の第 1 比較例では、発振信号 X I のノードである第 1 ノード N 1 に対して、温度補償用の基準電圧 V R E F B が印加されており、発振信号 X I は基準電圧 V R E F B を中心として変化する発振信号になる。ここで、基準電圧 V R E F B は例えば可変容量素子 C V 1 の感度を最適にする電圧に調整されており、波形整形回路 140 の初段のインバーター回路 I V B 1 のしきい値電圧とは一致しない。一例としては第 1 比較例ではインバーター回路 I V B 1 に対して  $V R E G = 1.5 V$  となる電源電圧が供給されているため、インバーター回路 I V B 1 のしきい値電圧は  $V R E G / 2 = 0.75 V$  程度になる。

50

一方、基準電圧 V R E F B は可変容量素子 C V 1 の感度が最適になるように、例えば V R E F B = 0 . 4 V に調整されているため、インバーター回路 I V B 1 のしきい値電圧と、発振信号 X I の中心電圧となる基準電圧 V R E F B が一致しない。また基準電圧 V R E F B は、可変容量素子であるバラクターの製造バラツキ等に応じて調整されるものであり、インバーター回路 I V B 1 等を構成する P 型トランジスター、N 型トランジスターの製造バラツキに応じて調整されるものではない。

#### 【 0 0 3 7 】

このため図 7 の第 1 比較例では、インバーター回路 I V B 1 の入力ノードに D C カットの用のキャパシター C B を設けて、発振信号 X I の D C 成分をカットして、発振信号 X I の A C 成分のみをインバーター回路 I V B 1 に入力する必要があった。そして初段のインバーター回路 I V B 1 では、その出力ノードと入力ノードを帰還抵抗 R B を介して接続することで、自己バイアスによりバイアス点が調節される。しかしながら、このような自己バイアスによるバイアス点の調節では、発振信号 X I の波形に非線形の歪みが生じると、クロック信号 C K のデューティー比が変動してしまい、デューティー比の高精度化を実現できないという問題がある。例えば図 7 の第 1 比較例では、デューティー比のバラツキの実力値は 5 0 % ± 4 % 程度であり、例えば 5 0 % ± 1 % 以内というような高精度なデューティー比を実現することができない。例えばクロック信号 C K をバッファリングした出力クロック信号 C K Q に基づいて、外部の処理装置が処理を行う場合に、当該処理装置が、出力クロック信号 C K Q の立ち上がりエッジだけではなく、立ち下がりエッジも用いて処理を行うような用途がある。このような用途では、5 0 % ± 4 % 程度のデューティー比では適正な処理を実行できないため、5 0 % ± 1 % 以内というような高精度なデューティー比を要求される場合があるが、図 7 の第 1 比較例ではこのような要求に応えることができない。

#### 【 0 0 3 8 】

この点、図 3 の本実施形態の回路装置 2 0 では、発振信号 X I の第 1 ノード N 1 と可変容量素子 C V 1 との間に、D C カット用のキャパシター C F 1 が設けられる。また発振信号 X O の第 2 ノード N 2 と可変容量素子 C V 2 との間にも、D C カット用のキャパシター C F 2 が設けられる。このようにすることで、温度補償用の基準電圧 V R E F の設定に依存しないバイアス電圧 V B S の設定が可能になり、発振信号 X I をバイアス電圧 V B S を中心として変化する発振信号にすることが可能になる。

#### 【 0 0 3 9 】

例えば基準電圧 V R E F を調整することで、可変容量素子 C V 1、C V 2 が最適な感度になるように調整できる。この場合に、第 1 ノード N 1 の容量は、可変容量素子 C V 1 とキャパシター C F 1 の直列容量になり、第 2 ノード N 2 の容量は、可変容量素子 C V 2 とキャパシター C F 2 の直列容量になる。しかしながら、キャパシター C F 1、C F 2 の容量を十分に大きくすることで、可変容量素子 C V 1、C V 2 を用いて第 1 ノード N 1、第 2 ノード N 2 の容量を、環境温度に応じた適切な容量に調整することが可能になる。

#### 【 0 0 4 0 】

そして本実施形態では、バイアス電圧 V B S については、基準電圧 V R E F とは無関係に、調整データ A D J を用いてデューティー調整回路 5 0 により、クロック信号 C K のデューティー比が 5 0 % に近づくような適切な電圧に調整できる。

#### 【 0 0 4 1 】

例えば P 型トランジスターと N 型トランジスターのしきい値電圧等のプロセス変動により、図 3 の波形整形回路 4 0 の初段のインバーター回路 I V A 1 のしきい値電圧が、電源電圧である V R E G 2 の 2 分の 1 の電圧よりも低い電圧になったとする。例えば N 型トランジスターが F a s t であり、P 型トランジスターが S l o w になるようなプロセス変動があると、インバーター回路 I V A 1 のしきい値電圧が、V R E G 2 の 2 分の 1 の電圧よりも低い電圧になる。このときに、バイアス電圧 V B S が V R E G 2 の 2 分の 1 の電圧のままであると、クロック信号 C K のデューティー比が 5 0 % よりも大きくなってしまう事態が発生する。この場合にも本実施形態では、デューティー調整回路 5 0 が、調整データ

10

20

30

40

50

ADJに基づいて、バイアス電圧VBSを、VRG2の2分の1の電圧よりも低い電圧に設定する。このようにすれば、インバーター回路IVA1のしきい値電圧がプロセス変動により低い電圧になった場合にも、それに応じて、発振信号XIの中心電圧となるバイアス電圧VBSが低くなるため、クロック信号CKのデューティー比を50%に近づけることが可能になる。従って、デューティー比の変動が50%±1%以内となるような高精度なデューティー調整を実現できる。

#### 【0042】

一方、P型トランジスターやN型トランジスターのしきい値電圧等のプロセス変動により、波形整形回路40の初段のインバーター回路IVA1のしきい値電圧が、VRG2の2分の1の電圧よりも高い電圧になったとする。例えばP型トランジスターがFastであり、N型トランジスターがSlowになるようなプロセス変動があると、インバーター回路IVA1のしきい値電圧が、VRG2の2分の1の電圧よりも高い電圧になる。このときに、バイアス電圧VBSがVRG2の2分の1の電圧のままであると、クロック信号CKのデューティー比が50%よりも小さくなってしまう事態が発生する。この場合にも本実施形態では、デューティー調整回路50が、調整データADJに基づいてバイアス電圧VBSを、VRG2の2分の1の電圧よりも高い電圧に設定する。このようにすれば、インバーター回路IVA1のしきい値電圧がプロセス変動により高い電圧になった場合にも、それに応じて、発振信号XIの中心電圧となるバイアス電圧VBSが高くなるため、クロック信号CKのデューティー比を50%に近づけることが可能になる。従って、デューティー比の変動が50%±1%以内となるような高精度なデューティー調整を実現できる。

#### 【0043】

また図3では、図7の第1比較例で設けられているDCカット用のキャパシターCBを設ける必要がないため、DCカット用のキャパシターCBと入力容量の分圧による発振振幅の減衰も抑えられるため、低ノイズフロア化を実現できるようになる。また図7に示すような帰還抵抗RBが不要になるため、帰還抵抗RBを原因とする異常発振も防止できるようになる。

#### 【0044】

図8に本実施形態の第2比較例の回路装置220を示す。この第2比較例は前述の特許文献1の回路に対応するものであり、発振回路230と波形整形回路240とバイアス回路250と定電流回路260が設けられる。この第2比較例ではバイアス回路250は波形整形回路240のレプリカの回路であり、バイアス回路250が出力するバイアス電圧は、供給される電源電圧VDDに依存する。例えばバイアス回路250はVDDの2分の1程度のバイアス電圧を出力する。しかしながら、クロック信号CKのデューティー比は、初段のインバーター回路のP型トランジスターN型トランジスターのしきい値電圧についての例えは±0.1V程度のバラツキによる変動だけではなく、後段の回路によってもデューティー比は変動し、発振波形の歪みによってもデューティー比が変動してしまう。従って、図8の第2比較例では、このような種々の変動要因を加味した高精度のデューティー調整を実現できないという問題がある。また図8の第2比較例は、バイアス回路250がVDDの2分の1程度のバイアス電圧を出力するだけであり、調整データに基づいてバイアス電圧を調整するような調整回路が存在しない。

#### 【0045】

この点、本実施形態の回路装置20では、調整データADJに基づいてバイアス電圧VBSを可変に調整できる。即ち、調整データADJに基づいてバイアス電圧VBSを調整する回路であるデューティー調整回路50が設けられる。従って、例えば図3の初段のインバーター回路IVA1でのP型トランジスターN型トランジスターのしきい値電圧等のバラツキに加えて、後段の回路でのデューティー比のズレや、発振波形の歪み具合等を加味して、バイアス電圧VBSを調整して、クロック信号CKのデューティー比を調整できるため、図8の第2比較例等に比べて、高精度のデューティー調整が可能になる。

#### 【0046】

10

20

30

40

50

10 例えば本実施形態の回路装置 20 は、調整データ A D J を記憶する不揮発性メモリー 6 2 を含み、デューティー調整回路 50 は、不揮発性メモリー 6 2 に記憶された調整データ A D J により設定される電圧のバイアス電圧 V B S を生成する。例えばデューティー調整回路 50 は、不揮発性メモリー 6 2 に記憶された調整データ A D J が第 1 調整値である場合には、第 1 調整値に対応する第 1 電圧値のバイアス電圧 V B S を生成し、調整データ A D J が第 2 調整値である場合には、第 2 調整値に対応する第 2 電圧値のバイアス電圧 V B S を生成する。このようにすれば、最適なデューティー比を設定できる調整データ A D J を不揮発性メモリー 6 2 に記憶しておき、回路装置 20 の実動作時に、不揮発性メモリー 6 2 から読み出された調整データ A D J に応じたバイアス電圧 V B S をデューティー調整回路 50 が供給することで、例えば  $50\% \pm 1\%$  というような高精度のデューティー調整を実現できるようになる。具体的には、回路装置 20 の製造時等における検査工程において、出力クロック信号 C K Q のデューティー比を測定し、測定結果に基づいて調整データ A D J を決定して、不揮発性メモリー 6 2 に書き込む。例えば調整データ A D J は、プロセス変動によるトランジスターのしきい値電圧等のバラツキのみならず、発振波形の非線形歪み等も考慮して決定される。そして回路装置 20 の実動作時には、測定結果に基づき決定された調整データ A D J が不揮発性メモリー 6 2 から読み出されて、調整データ A D J に応じたバイアス電圧 V B S を、デューティー調整回路 50 が供給することで、例えば  $50\% \pm 1\%$  以内となるような高精度のデューティー調整を実現できるようになる。

#### 【 0 0 4 7 】

20 また本実施形態では、図 3 に示す発振回路 30 の電源電圧である V R E G 1 は、波形整形回路 40 の電源電圧である V R E G 2 以上の電圧となっている。即ち V R E G 1  $>$  V R E G 2 の関係が成り立つ。一例としては V R E G 1 は 1.2 V であり、V R E G 2 は 1 V である。

#### 【 0 0 4 8 】

一方、図 8 の第 2 比較例では、発振回路 230 の電源電圧である V R E G は 1.2 V であり、波形整形回路 240 やバイアス回路 250 の電源電圧である V D D は 1.8 ~ 5 V であり、V R E G < V D D の関係が成り立っている。このため波形整形回路 240 に入力される発振信号 X I の振幅電圧が、波形整形回路 240 の電源電圧 V D D よりも小さくなり、波形整形回路 240 の初段のインバーター回路の出力信号の立ち上がり波形や立ち下がり波形が急峻にならず、鈍った波形になってしまふ。そして初段のインバーター回路の出力信号が鈍った波形になると、次段のインバーター回路の P 型トランジスターや N 型トランジスターのしきい値電圧等のバラツキが原因で、デューティー比が変動してしまう。

#### 【 0 0 4 9 】

これに対して本実施形態では、発振回路 30 の電源電圧である V R E G 1 は、波形整形回路 40 の電源電圧である V R E G 2 以上の電圧となっている。従って、波形整形回路 40 に入力される発振信号 X I の振幅を、波形整形回路 40 の駆動電圧範囲内で可能な限り大きくすることが可能になる。即ち V R E G 2 で設定される波形整形回路 40 の駆動電圧範囲内において、フルスイングの振幅の発振信号 X I を、波形整形回路 40 の初段のインバーター回路 I V A 1 に入力できるようになる。従って、初段のインバーター回路 I V A 1 の P 型トランジスター及び N 型トランジスターの両方がオンになる期間が殆ど無くなることにより、インバーター回路 I V A 1 の出力信号の立ち上がり波形や立ち下がり波形が急峻になる。この結果、次段のインバーター回路 I V A 2 の P 型トランジスターや N 型トランジスターのしきい値電圧等のバラツキを原因とするデューティー比のバラツキを低減できるようになる。また発振信号 X I の振幅の揺らぎによる A M ノイズは、波形整形回路 40 の波形整形により、位相ノイズである P M ノイズに変換される。この点、本実施形態のように V R E G 1  $>$  V R E G 2 として、発振信号 X I の振幅を、波形整形回路 40 の駆動電圧範囲内で可能な限り大きくすれば、A M ノイズから P M ノイズへの変換度合いを低減でき、クロック信号 C K の信号品質を向上できる。また波形整形回路 40 と後段の出力バッファーレベル 70 は、同じ V R E G 2 の電源電圧で動作するが、V R E G 2 の電源電圧を、発振回路 30 の電源電圧である V R E G 1 よりも低くすることで、出力バッファーレベル 70 の出力電圧を下げる

路 7 0 での電力消費を低減できる。例えば出力バッファー回路 7 0 は、外部の大きな負荷を駆動するため、他の回路ブロックに比べて消費電力が大きいが、V R E G 2 をV R E G 1 よりも低い電圧とすることで、その分だけ消費電力を低減することも可能になる。

#### 【 0 0 5 0 】

また図 3 に示すように本実施形態では、発振回路 3 0 は、一端が第 1 ノード N 1 に接続され、容量値が固定である固定容量のキャパシター C F 1 と、一端が固定容量のキャパシター C F 1 の他端に接続され、容量値が可変である可変容量素子 C V 1 を含む。そして可変容量素子 C V 1 の一端及び他端の一方に、温度補償電圧 V C M P が入力され、一端及び他端の他方に、基準電圧 V R E F が入力される。例えば図 3 では、可変容量素子 C V 1 の一端に温度補償電圧 V C M P が入力され、可変容量素子 C V 1 の他端に基準電圧 V R E F が入力されている。なおグランドノード側である可変容量素子 C V 1 の他端に、温度補償電圧 V C M P を入力し、キャパシター C F 1 側である可変容量素子 C V 1 の一端に、基準電圧 V R E F を入力してもよい。また可変容量素子 C V 2 についても可変容量素子 C V 1 と同様の接続構成になっているが、ここでは詳細な説明を省略する。

10

#### 【 0 0 5 1 】

このような構成によれば、可変容量素子 C V 1 に対して、温度補償電圧 V C M P と基準電圧 V R E F の電圧差に対応する電圧を印加できるようになり、基準電圧 V R E F を基準とした温度補償電圧 V C M P により、可変容量素子 C V 1 の容量値を変化させて、発振回路 3 0 の発振周波数の温度補償を実現できるようになる。また固定容量のキャパシター C F 1 を設けることで、バイアス電圧 V B S と基準電圧 V R E F を独立に調整することが可能になる。即ちバイアス電圧 V B S を変化させることによるデューティー調整と同時に、バラクター等の可変容量素子 C V 1 の基準電圧 V R E F についても独立に調整できるようになる。例えばクロック信号 C K のデューティー比が 50 % に近づくように、バイアス電圧 V B S を変化させるデューティー調整を行いながら、基準電圧 V R E F については、可変容量素子 C V 1 の両端の電位差が 0 V よりも大きくなり、且つ、感度が最適になるように調整することが可能になる。

20

#### 【 0 0 5 2 】

また本実施形態では、デューティー調整回路 5 0 は、バイアス電圧を第 1 ノード N 1 に出力すると共に、基準電圧 V R E F を、可変容量素子 C V 1 の一端及び他端の他方に出力する。例えば図 3 では、可変容量素子 C V 1 の一端に温度補償電圧 V C M P が入力されており、デューティー調整回路 5 0 は、可変容量素子 C V 1 の他端に基準電圧 V R E F を出力している。なお可変容量素子 C V 1 の他端に温度補償電圧 V C M P を入力し、デューティー調整回路 5 0 が、可変容量素子 C V 1 の一端に基準電圧 V R E F を出力してもよい。

30

#### 【 0 0 5 3 】

このような構成とすれば、1 つのデューティー調整回路 5 0 を用いて、バイアス電圧 V B S を供給してクロック信号 C K のデューティー比を調整できると共に、温度補償用の基準電圧 V R E F も供給して発振周波数の温度補償を実現できるようになる。別の言い方をすれば、温度補償用の基準電圧 V R E F を供給するデューティー調整回路 5 0 を有効利用して、バイアス電圧 V B S についても供給してデューティー比を調整できるようになる。これにより、回路の共用化や回路装置 2 0 の小規模化を実現したり、回路装置 2 0 の低消費電力化を実現できるようになる。

40

#### 【 0 0 5 4 】

具体的には後述の図 1 2 で詳細に説明するように、デューティー調整回路 5 0 は、電源ノードとグランドノードの間に直列接続された複数の抵抗を有し、複数の抵抗により分圧された複数の分圧電圧を出力する分圧回路 5 2 と、複数の分圧電圧のいずれかをバイアス電圧 V B S として選択する選択回路 5 4 を含む。即ち、分圧回路 5 2 はラダー抵抗回路により実現され、選択回路 5 4 は、ラダー抵抗回路である分圧回路 5 2 により生成された複数の分圧電圧の中から、入力された調整データ A D J に基づきバイアス電圧 V B S を選択して、第 1 ノード N 1 に供給する。このような構成によれば、例えば V R E G 1 の電源電圧と G N D との間の複数の分圧電圧を分圧回路 5 2 により生成し、生成された複数の分圧

50

電圧の中から調整データ A D J に応じた電圧を選択することで、発振信号 X I の中心電圧となるバイアス電圧 V B S を生成できるようになる。

【 0 0 5 5 】

そして本実施形態では選択回路 5 4 は、分圧回路 5 2 からの複数の分圧電圧のいずれかである第 1 分圧電圧をバイアス電圧 V B S として選択し、複数の分圧電圧のいずれかである第 2 分圧電圧を基準電圧 V R E F として選択する。このようにすれば、複数の分圧電圧の中から選択回路 5 4 により選択された第 1 分圧電圧を、バイアス電圧 V B S として第 1 ノード N 1 に供給することで、クロック信号 C K のデューティー比を調整できるようになる。そして複数の分圧電圧の中から選択回路 5 4 により選択された第 2 分圧電圧を、基準電圧 V R E F として供給することで、可変容量素子 C V 1 を適切な感度範囲で動作させて、発振周波数の温度補償を実現できるようになる。またバイアス電圧 V B S の生成と基準電圧 V R E F の生成のために、分圧回路 5 2 として 1 つのラダー抵抗回路を設ければ済むため、バイアス電圧用の第 1 ラダー抵抗回路と基準電圧用の第 2 ラダー抵抗回路を設ける場合に比べて、回路装置 2 0 の回路面積の小面積化を実現できるようになる。また第 1 ラダー抵抗回路と第 2 ラダー抵抗回路を設ける場合に比べて、電源ノードからグランドノードに流れる電流を例えば 2 分の 1 程度にすることが可能になるため、回路装置 2 0 の低消費電力化も実現できる。

【 0 0 5 6 】

2. 変形例

本実施形態の回路装置 2 0 は、以上に説明した構成例に限定されず、種々の変形実施が可能である。以下、本実施形態の種々の変形例について説明する。

【 0 0 5 7 】

例えば図 9 の変形例では、発振回路 3 0 の構成等が図 3 とは異なっている。例えば図 9 では、図 3 の固定容量のキャパシター C F 1、C F 2 は設けられていない。そして可変容量素子 C V 1 の一端が第 1 ノード N 1 に接続され、可変容量素子 C V 1 の他端に温度補償電圧 V C M P が供給される。また可変容量素子 C V 2 の一端が第 2 ノード N 2 に接続され、可変容量素子 C V 2 の他端に温度補償電圧 V C M P が供給される。そして第 1 ノード N 1 には、デューティー調整回路 5 0 から抵抗 R R F B を介して基準電圧 V R E F B が供給され、第 2 ノード N 2 には、デューティー調整回路 5 0 から抵抗 R R F C を介して基準電圧 V R E F C が供給される。これにより可変容量素子 C V 1 の両端には、温度補償電圧 V C M P と基準電圧 V R E F B の電圧差に対応する電圧が印加され、可変容量素子 C V 2 の両端には、温度補償電圧 V C M P と基準電圧 V R E F C の電圧差に対応する電圧が印加されるようになる。また発振信号 X I は基準電圧 V R E F B を中心として変化する発振信号になり、発振信号 X O は基準電圧 V R E F C を中心として変化する発振信号になる。また図 9 では、第 1 ノード N 1 と波形整形回路 4 0 の入力ノードの間に、D C カット用のキャパシター C X 2 が設けられている。このようなキャパシター C X 2 を設けることで、発振信号 X I の D C 成分がカットされて、A C 成分だけが波形整形回路 4 0 側に伝達されるようになる。そして発振信号 X I の A C 成分の信号に対して、デューティー調整回路 5 0 によりバイアス点となるバイアス電圧 V B S が設定され、バイアス電圧 V B S を中心に変化する発振信号 X I を、波形整形回路 4 0 に入力できるようになる。

【 0 0 5 8 】

図 1 0、図 1 1 では、回路装置 2 0 は、クロック信号 C K をバッファリングして出力クロック信号 C K Q を外部に出力する出力バッファー回路 7 0 を含む。出力バッファー回路 7 0 は、例えば波形整形回路 4 0 よりも駆動能力が高いバッファー回路を有しており、クロック信号 C K を、この高い駆動能力のバッファー回路によりバッファリングした信号が、出力クロック信号 C K Q として回路装置 2 0 の外部に出力される。このようにすれば、外部負荷が大きい場合にも、適正な駆動波形の出力クロック信号 C K Q を当該外部負荷に供給して駆動することが可能になる。

【 0 0 5 9 】

また図 1 0 では、デューティー調整回路 5 0 は、温度補償電圧を V C M P とし、基準電

10

20

30

40

50

圧をVREFとしたときに、VCOMP-VREFが0Vよりも大きくなる基準電圧VREFを供給する。例えば可変容量素子CV1に0Vよりも大きな電圧が印加されるように基準電圧VREFを供給する。同様に、可変容量素子CV2に0Vよりも大きな電圧が印加されるように基準電圧VREFを供給する。

#### 【0060】

図10では、温度補償電圧VCOMPは、例えば0.9Vを中心として温度に応じて3次特性等で変化する電圧になっている。そしてデューティー調整回路50は、VCOMP-VREFが0Vよりも大きくなるように、図10では例えば0.3Vの基準電圧VREFを可変容量素子CV1に供給する。これにより可変容量素子CV1には、0Vよりも大きな電圧であるVCOMP-VREFが印加されるようになる。従って、可変容量素子CV1の容量が、適切な感度範囲で温度補償電圧VCOMPに応じて可変に変化するようになる。同様に、可変容量素子CV2にも、0Vよりも大きな電圧であるVCOMP-VREFが印加されるようになり、可変容量素子CV2の容量が、適切な感度範囲で温度補償電圧VCOMPに応じて可変に変化するようになる。これにより、回路装置20を、TCXO用の回路装置として用いることが可能になり、TCXOの発振器を実現できるようになる。

#### 【0061】

一方、図11では、デューティー調整回路50は、VCOMP-VREFが0V以下になる基準電圧VREFを供給する。例えば可変容量素子CV1に0V以下の電圧が印加されるように基準電圧VREFを供給する。同様に、可変容量素子CV2に0V以下の電圧が印加されるように基準電圧VREFを供給する。図11では、例えば0.6V程度の温度補償電圧VCOMPが供給される。このためデューティー調整回路50は、VCOMP-VREFが0V以下になるように、図11では例えば0.9Vの基準電圧VREFを可変容量素子CV1に供給する。これにより可変容量素子CV1には、0V以下の電圧であるVCOMP-VREFが印加されるようになる。同様に、可変容量素子CV2にも0V以下のVCOMP-VREFが印加されるようになる。これにより、回路装置20を、SPXO用の回路装置として用いることが可能になり、SPXOの発振器を実現できるようになる。

#### 【0062】

例えばデューティー調整回路50は、バイアス電圧VBSとして0.5V±0.1V程度の電圧を供給する。従って、TCXOを実現する図10では、分圧回路52のラダー抵抗回路において基準電圧VREFが出力される電圧分割タップは、バイアス電圧VBSが出力される電圧分割タップよりも、グランドノード側のタップになる。一方、SPXOを実現する図11では、分圧回路52のラダー抵抗回路において基準電圧VREFが出力される電圧分割タップは、バイアス電圧VBSが出力される電圧分割タップよりも、VREG1の電源ノード側のタップになる。このように本実施形態によれば、分圧回路52のラダー抵抗回路においてバイアス電圧VBSが出力される電圧分割タップの位置を切り替えるだけで、同じ回路装置20を、図10のようにTCXO用の回路装置として使用したり、図11のようにSPXO用の回路装置として使用できるようになる。従って、回路装置20をTCXOとSPXOで共用して使用することが可能になる。

#### 【0063】

図12にデューティー調整回路50の構成例を示す。デューティー調整回路50は、分圧回路52と選択回路54を含む。分圧回路52は、VREG1の電源ノードとグランドノードの間に直列接続された複数の抵抗R1～Rmを有し、複数の抵抗R1～Rmにより分圧された複数の分圧電圧VR1～VRm-1を出力する。そして選択回路54は、調整データADJに基づいて、複数の分圧電圧VR1～VRm-1のいずれかをバイアス電圧VBSとして選択する。この選択回路54は例えばトーナメント方式で電圧選択を行う複数のセレクター回路により実現できる。具体的には選択回路54は、複数の分圧電圧VR1～VRm-1のいずれかである第1分圧電圧をバイアス電圧VBSとして選択し、複数の分圧電圧VR1～VRm-1のいずれかである第2分圧電圧を基準電圧VREFとして選択して出力する。これにより1つのデューティー調整回路50を用いて、デューティー調整用のバイアス電圧VBSと温度補償用の基準電圧VREFの両方を供給できるよう

10

20

30

40

50

なり、回路の共用化を図れるようになる。

【0064】

3. 発振器

図13に本実施形態の発振器4の構造例を示す。発振器4は、振動子10と、回路装置20と、振動子10及び回路装置20を収容するパッケージ15を有する。パッケージ15は、例えばセラミック等により形成され、その内側に収容空間を有しており、この収容空間に振動子10及び回路装置20が収容されている。収容空間は気密封止されており、望ましくは真空に近い状態である減圧状態になっている。パッケージ15により、振動子10及び回路装置20を衝撃、埃、熱、湿気等から好適に保護することができる。

【0065】

パッケージ15はベース16とリッド17を有する。具体的にはパッケージ15は、振動子10及び回路装置20を支持するベース16と、ベース16との間に収容空間を形成するようにベース16の上面に接合されたリッド17により構成されている。そして振動子10は、ベース16の内側に設けられた段差部に端子電極を介して支持されている。また回路装置20は、ベース16の内側底面に配置されている。具体的には回路装置20は、能動面がベース16の内側底面に向くように配置されている。能動面は回路装置20の回路素子が形成される面である。また回路装置20の端子にバンプBMPが形成されている。そして回路装置20は、導電性のバンプBMPを介してベース16の内側底面に支持される。導電性のバンプBMPは例えば金属バンプであり、このバンプBMPやパッケージ15の内部配線や端子電極などを介して、振動子10と回路装置20が電気的に接続される。また回路装置20は、バンプBMPやパッケージ15の内部配線を介して、発振器4の外部端子18、19に電気的に接続される。外部端子18、19は、パッケージ15の外側底面に形成されている。外部端子18、19は、外部配線を介して外部デバイスに接続される。外部配線は、例えば外部デバイスが実装される回路基板に形成される配線などである。これにより外部デバイスに対してクロック信号などを出力できるようになる。

【0066】

なお図13では、回路装置20の能動面が下方に向くように回路装置20がフリップ実装されているが、本実施形態はこのような実装には限定されない。例えば回路装置20の能動面が上方に向くように回路装置20を実装してもよい。即ち能動面が振動子10に対向するように回路装置20を実装する。或いは、発振器4は、ウェハレベルパッケージ(WLP)の発振器であってもよい。この場合には発振器4は、半導体基板と、半導体基板の第1面と第2面との間を貫通する貫通電極とを有するベースと、半導体基板の第1面に対して、金属バンプ等の導電性の接合部材を介して固定される振動子10と、半導体基板の第2面側に再配置配線層等の絶縁層を介して設けられる外部端子を含む。そして半導体基板の第1面又は第2面に、回路装置20となる集積回路が形成される。この場合には、振動子10及び集積回路が配置された複数のベースが形成された第1半導体ウェハーと、複数のリッドが形成された第2半導体ウェハーとを貼りつけることで、複数のベースと複数のリッドを接合し、その後にダイシングソー等によって発振器4の個片化を行う。このようにすれば、ウェハレベルパッケージの発振器4の実現が可能になり、高スループット、且つ、低成本での発振器4の製造が可能になる。

【0067】

以上に説明したように本実施形態の回路装置は、振動子の一端に電気的に接続される第1ノードと、振動子の他端に電気的に接続される第2ノードとに電気的に接続され、振動子を発振させることで発振信号を生成する発振回路と、第1ノードに接続され、第1ノードから発振信号が入力され、発振信号を波形整形したクロック信号を出力する波形整形回路を含む。また回路装置は、調整データに基づき可変に調整したバイアス電圧を第1ノードに供給することにより、クロック信号のデューティー比を調整するデューティー調整回路を含む。

【0068】

本実施形態では、第1ノード及び第2ノードを介して電気的に接続される振動子を発振

10

20

30

40

50

回路が発振させることで発振信号が生成され、第1ノードでの発振信号が波形整形回路に入力されて波形整形され、クロック信号が生成されるようになる。このとき、デューティー調整回路が、調整データに基づき可変に調整したバイアス電圧を第1ノードに供給する。これにより、第1ノードでの発振信号はバイアス電圧を中心変化する発振信号になる。従って、クロック信号が最適なデューティー比になるように、調整データに基づき、発振信号のバイアス電圧を調整して、当該発振信号を波形整形回路に入力できるようになるため、デューティー比を高精度に調整できるようになる。

【0069】

また本実施形態では、調整データを記憶する不揮発性メモリーを含み、デューティー調整回路は、不揮発性メモリーに記憶された調整データにより設定される電圧のバイアス電圧を生成してもよい。

10

【0070】

このようにすれば、最適なデューティー比を調整できる調整データを不揮発性メモリーに記憶し、回路装置の実動作時に、不揮発性メモリーから当該調整データを読み出すことで、高精度のデューティー調整を実現できるようになる。

【0071】

また本実施形態では、発振回路の電源電圧は、波形整形回路の電源電圧以上の電圧であつてもよい。

【0072】

このようにすれば、波形整形回路に入力される発振信号の振幅を、波形整形回路の駆動電圧範囲内で可能な限り大きくすることができ、波形整形後の信号の波形を急峻にすることができるため、デューティー比のバラツキを低減できるようになる。

20

【0073】

また本実施形態では、デューティー調整回路は、電源ノードとグランドノードの間に直列接続された複数の抵抗を有し、複数の抵抗により分圧された複数の分圧電圧を出力する分圧回路と、複数の分圧電圧のいずれかをバイアス電圧として選択する選択回路とを含んでもよい。

【0074】

このようにすれば、電源電圧とグランドとの間の複数の分圧電圧を分圧回路により生成し、生成された複数の分圧電圧の中から調整データに応じた電圧を選択することで、調整データに応じたバイアス電圧を生成できるようになる。

30

【0075】

また本実施形態では、発振回路は、一端が第1ノードに接続され、容量値が固定である固定容量キャパシターと、一端が固定容量キャパシターの他端に接続され、容量値が可変である可変容量素子と、を含み、可変容量素子の一端及び他端の一方に、温度補償電圧が入力され、他方に、基準電圧が入力されてもよい。

【0076】

このようにすれば、基準電圧を基準とした温度補償電圧により、可変容量素子の容量値を変化させて、発振回路の発振周波数の温度補償を実現できるようになる。また固定容量キャパシターを設けることで、基準電圧とバイアス電圧を独立に調整して、発振信号の温度補償とデューティー調整を実現できるようになる。

40

【0077】

また本実施形態では、デューティー調整回路は、バイアス電圧を第1ノードに出力すると共に、基準電圧を他方に出力してもよい。

【0078】

このような構成とすれば、1つのデューティー調整回路を用いて、バイアス電圧を供給してクロック信号のデューティー比を調整できると共に、温度補償用の基準電圧も供給して発振周波数の温度補償を実現できるようになる。

【0079】

また本実施形態では、デューティー調整回路は、電源ノードとグランドノードの間に直

50

列接続された複数の抵抗を有し、複数の抵抗により分圧された複数の分圧電圧を出力する分圧回路と、複数の分圧電圧のいずれかである第1分圧電圧をバイアス電圧として選択し、複数の分圧電圧のいずれかである第2分圧電圧を基準電圧として選択する選択回路と、を含んでもよい。

【0080】

このようにすれば、複数の分圧電圧の中から選択された第1分圧電圧を、バイアス電圧として供給することで、クロック信号のデューティー比を調整できるようになると共に、複数の分圧電圧の中から選択された第2分圧電圧を、基準電圧として供給することで、発振周波数の温度補償を実現できるようになる。

【0081】

また本実施形態では、デューティー調整回路は、温度補償電圧をV<sub>CMP</sub>とし、基準電圧をV<sub>REF</sub>としたときに、V<sub>CMP</sub> - V<sub>REF</sub>が0Vよりも大きくなる基準電圧を供給してもよい。

【0082】

このようにすれば、可変容量素子に対して、0Vよりも大きな電圧であるV<sub>CMP</sub> - V<sub>REF</sub>が印加され、可変容量素子の容量が温度補償電圧に応じて可変に変化するようになるため、温度補償機能を有する発振器等の実現が可能になる。

【0083】

また本実施形態では、デューティー調整回路は、温度補償電圧をV<sub>CMP</sub>とし、基準電圧をV<sub>REF</sub>としたときに、V<sub>CMP</sub> - V<sub>REF</sub>が0V以下になる基準電圧を供給してもよい。

10

【0084】

このようにすれば、可変容量素子に対して、0V以下の電圧であるV<sub>CMP</sub> - V<sub>REF</sub>が印加されるようになり、温度補償機能を有しない発振器等の実現が可能になる。

【0085】

また本実施形態では、クロック信号をバッファリングして出力クロック信号を外部に出力する出力バッファー回路を含んでもよい。

20

【0086】

このようにすれば、外部負荷が大きい場合にも、適正な駆動波形の出力クロック信号を当該外部負荷に供給して駆動できるようになる。

30

【0087】

また本実施形態は、上記の回路装置と、振動子とを含む発振器に関係する。

【0088】

なお、上記のように本実施形態について詳細に説明したが、本開示の新規事項および効果から実体的に逸脱しない多くの変形が可能であることは当業者には容易に理解できるであろう。従って、このような変形例はすべて本開示の範囲に含まれるものとする。例えば、明細書又は図面において、少なくとも一度、より広義または同義な異なる用語と共に記載された用語は、明細書又は図面のいかなる箇所においても、その異なる用語に置き換えることができる。また本実施形態及び変形例の全ての組み合わせも、本開示の範囲に含まれる。また回路装置、発振器の構成・動作等も本実施形態で説明したものに限定されず、種々の変形実施が可能である。

40

【符号の説明】

【0089】

4...発振器、10...振動子、15...パッケージ、16...ベース、17...リッド、18...外部端子、19...外部端子、20...回路装置、30...発振回路、32...可変容量回路、40...波形整形回路、50...デューティー調整回路、52...分圧回路、54...選択回路、60...処理回路、62...不揮発性メモリー、70...出力バッファー回路、90...電源回路、92...温度補償回路、94...温度センサー回路、120...回路装置、130...発振回路、140...波形整形回路、220...回路装置、230...発振回路、240...波形整形回路、250...バイアス回路、260...定電流回路、

50

A D J ...調整データ、B M P ... バンプ、C B ... C F 1、C F 2、C G ... キャパシター、C K ... クロック信号、C K Q ... 出力クロック信号、C V 1 ... 可変容量素子、C V 2 ... 可変容量素子、C X、C X 1、C X 2 ... キャパシター、I S ... 電流源、I V A 1、I V A 2、I V B 1、I V B 2 ... インバーター回路、N 1 ... 第1ノード、N 2 ... 第2ノード、V C M P ... 温度補償電圧、R 1 ~ R m - 1 ... 抵抗、R B ... 帰還抵抗、R B S、R C P、R R F、R R F B、R R F C、R X ... 抵抗、T C K ... クロック端子、T G N D ... グランド端子、T R ... バイポーラートランジスター、T V D D ... 電源端子、T X I、T X O ... 端子、V B S ... バイアス電圧、V D D ... 電源電圧、V R 1 ~ V R m - 1 ... 分圧電圧、V R E F、V R E F B、V R E F C ... 基準電圧、X I、X O ... 発振信号

【図面】

【図1】

【図2】

10

20

30

40

50

【図3】

【図4】

10

20

30

【図5】

【図6】

40

50

【図 7】

【図 8】

【図 9】

【図 10】

10

20

30

40

50

【 図 1 1 】

【図12】

【図13】

10

20

30

40

50

---

フロントページの続き

- (56)参考文献

- 特開2003-338710 (JP, A)

特開2018-067830 (JP, A)

特開2018-046460 (JP, A)

特開2015-126280 (JP, A)

特開2005-094644 (JP, A)

特開2008-035302 (JP, A)

中国特許出願公開第107294513 (CN, A)

- (58)調査した分野 (Int.Cl., DB名)

- H03B 5/30 - 5/42