(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3925253号

(P3925253)

(45) 発行日 平成19年6月6日(2007.6.6)

(24) 登録日 平成19年3月9日(2007.3.9)

(51) Int.C1.

F 1

HO1L 29/808 (2006.01)

HO1L 21/337 (2006.01)

HO1L 29/80

C

請求項の数 76 (全 72 頁)

(21) 出願番号 特願2002-71944 (P2002-71944)

(22) 出願日 平成14年3月15日 (2002.3.15)

(65) 公開番号 特開2003-273126 (P2003-273126A)

(43) 公開日 平成15年9月26日 (2003.9.26)

審査請求日 平成14年10月21日 (2002.10.21)

(73) 特許権者 000002130

住友電気工業株式会社

大阪府大阪市中央区北浜四丁目5番33号

(74) 代理人 100064746

弁理士 深見 久郎

(74) 代理人 100085132

弁理士 森田 俊雄

(74) 代理人 100083703

弁理士 仲村 義平

(74) 代理人 100091409

弁理士 伊藤 英彦

(74) 代理人 100099922

弁理士 甲田 一幸

最終頁に続く

(54) 【発明の名称】横型接合型電界効果トランジスタおよびその製造方法

## (57) 【特許請求の範囲】

## 【請求項1】

半導体基板上に位置する第1導電型不純物を含む第1半導体層と、

前記第1半導体層の上に位置し、前記第1半導体層の不純物濃度よりも高い濃度の第2導電型不純物を含む第2半導体層と、

前記第2半導体層の上に位置し、第1導電型不純物を含む第3半導体層と、

前記第3半導体層の上に位置し、第2導電型不純物を含む第4半導体層と、

前記第4半導体層の上に位置し、第1導電型不純物を含む第5半導体層と、

前記第5半導体層中において所定の間隔を隔てて、下面が前記第2半導体層にまで延在するように設けられ、前記第2半導体層および前記第4半導体層の不純物濃度よりも高い濃度の第2導電型の不純物を含むソース／ドレイン領域層と、 10

前記第3半導体層中の前記ソース／ドレイン領域層の間において、下面が前記第2半導体層にまで延在するように設けられ、前記第2半導体層の不純物濃度よりも高い第1導電型の不純物濃度を含む第1ゲート電極層と、

前記第5半導体層中の前記ソース／ドレイン領域層の間において、下面が前記第4半導体層にまで延在するように設けられ、前記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ、同電位を有する第2ゲート電極層と、

を備える横型接合型電界効果トランジスタ。

## 【請求項2】

前記第2半導体層と、前記第3半導体層と、前記第4半導体層と、前記第5半導体層との

10

20

不純物濃度と膜厚さとがほぼ同じである、請求項 1 に記載の横型接合型電界効果トランジスタ。

**【請求項 3】**

前記第 1 半導体層の最上部と前記第 1 ゲート電極層の最下部との間の間隔が、前記第 2 半導体層と前記第 1 ゲート電極層との接合における拡散電位で広がる空乏層の間隔よりも小さく、

前記第 3 半導体層の最上部と前記第 2 ゲート電極層の最下部との間の間隔が、前記第 4 半導体層と前記第 2 ゲート電極層との接合における拡散電位で広がる空乏層の間隔よりも小さいことを特徴とする、請求項 1 または 2 に記載の横型接合型電界効果トランジスタ。

**【請求項 4】**

前記第 3 半導体層と前記第 4 半導体層との間に、前記第 2 半導体層と前記第 3 半導体層と前記第 1 ゲート電極層とほぼ同じ構造である単位トランジスタ構造を 1 つまたは 2 以上備える、請求項 1 から 3 のいずれかに記載の横型接合型電界効果トランジスタ。

**【請求項 5】**

半導体基板上に位置する第 1 導電型不純物を含む第 1 半導体層と、

前記第 1 半導体層の上に位置し、前記第 1 半導体層の不純物濃度よりも高い濃度の第 2 導電型不純物を含む第 2 半導体層と、

前記第 2 半導体層の上に位置し、第 1 導電型不純物を含む第 3 半導体層と、

前記第 3 半導体層の上に位置し、第 2 導電型不純物を含む第 4 半導体層と、

前記第 4 半導体層の上に位置し、第 1 導電型不純物を含む第 5 半導体層と、

前記第 5 半導体層中において所定の間隔を隔てて、下面が前記第 2 半導体層にまで延在するように設けられ、前記第 2 半導体層および第 4 半導体層の不純物濃度よりも高い濃度の第 2 導電型の不純物を含むソース / ドレイン領域層と、

前記第 3 半導体層中の前記ソース / ドレイン領域層の間において、下面が前記第 2 半導体層にまで延在するように設けられ、前記第 2 半導体層の不純物濃度よりも高い第 1 導電型の不純物濃度を含む第 1 ゲート電極層と、

前記第 5 半導体層中の前記ソース / ドレイン領域層の間において、下面が前記第 4 半導体層にまで延在するように設けられ、前記第 1 ゲート電極層とほぼ同じ不純物濃度を有し、かつ、同電位を有する第 2 ゲート電極層と、

前記第 1 半導体層と前記第 1 ゲート電極層とに挟まれた前記第 2 半導体層に、前記第 1 ゲート電極層とほぼ同じ不純物濃度を有し、かつ、同電位を有する第 1 導電型の第 1 不純物注入領域と、

前記第 3 半導体層と前記第 2 ゲート電極層とに挟まれた前記第 4 半導体層に、前記第 1 ゲート電極層とほぼ同じ不純物濃度を有し、かつ、同電位を有する第 1 導電型の第 2 不純物注入領域と、

を備える横型接合型電界効果トランジスタ。

**【請求項 6】**

前記第 2 半導体層と、前記第 3 半導体層と、前記第 4 半導体層と、前記第 5 半導体層との不純物濃度と膜厚さとがほぼ同じである、請求項 5 に記載の横型接合型電界効果トランジスタ。

**【請求項 7】**

前記第 1 半導体層の最上部と前記第 1 不純物注入領域の最下部との間の間隔が、前記第 2 半導体層と前記第 1 不純物注入領域との接合における拡散電位で広がる空乏層の間隔よりも小さく、

前記第 1 不純物注入領域の最上部と前記第 1 ゲート電極層の最下部との間の間隔が、前記第 2 半導体層と前記第 1 ゲート電極層との接合における拡散電位で広がる空乏層の間隔の 2 倍よりも小さく、

前記第 3 半導体層の最上部と前記第 2 不純物注入領域の最下部との間の間隔が、前記第 4 半導体層と前記第 2 不純物注入領域との接合における拡散電位で広がる空乏層の間隔よりも小さく、

10

20

30

40

50

前記第2不純物注入領域の最上部と前記第2ゲート電極層の最下部との間の間隔が、前記第4半導体層と前記第2ゲート電極層との接合における拡散電位で広がる空乏層の間隔の2倍よりも小さいことを特徴とする、請求項5または6に記載の横型接合型電界効果トランジスタ。

**【請求項8】**

前記第2半導体層には、前記第1不純物注入領域が複数層設けられ、前記第4半導体層には、前記第2不純物注入領域が複数層設けられる、請求項5から7のいずれかに記載の横型接合型電界効果トランジスタ。

**【請求項9】**

前記第3半導体層と前記第4半導体層との間に、前記第2半導体層と前記第3半導体層と前記第1ゲート電極層と前記第1不純物注入領域とほぼ同じ構造である単位トランジスタ構造を1つまたは2以上備える、請求項5から8のいずれかに記載の横型接合型電界効果トランジスタ。 10

**【請求項10】**

半導体基板上に位置する第1導電型不純物を含む第1半導体層と、前記第1半導体層の上に位置し、前記第1半導体層の不純物濃度よりも高い濃度の第2導電型不純物を含む第2半導体層と、

前記第2半導体層の上に位置し、第1導電型不純物を含む第3半導体層と、

前記第3半導体層の上に位置し、第2導電型不純物を含む第4半導体層と、

前記第4半導体層の上に位置し、第1導電型不純物を含む第5半導体層と、 20

前記第5半導体層中において所定の間隔を隔てて、下面が前記第2半導体層にまで延在するように設けられ、前記第2半導体層および第4半導体層の不純物濃度よりも高い濃度の第2導電型の不純物を含むソース／ドレイン領域層と、

前記第3半導体層中の前記ソース／ドレイン領域層の間において、下面が前記第2半導体層にまで延在し、上面が前記第4半導体層にまで延在するように設けられ、前記第2半導体層および前記第4半導体層の不純物濃度よりも高い第1導電型の不純物濃度を含む第1ゲート電極層と、前記第5半導体層中の前記ソース／ドレイン領域層の間において、下面が前記第4半導体層にまで延在するように設けられ、前記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ、同電位を有する第2ゲート電極層と、

を備える横型接合型電界効果トランジスタ。 30

**【請求項11】**

前記第2半導体層と前記第3半導体層と前記第4半導体層と、前記第5半導体層との不純物濃度と膜厚さとがほぼ同じである、請求項10に記載の横型接合型電界効果トランジスタ。

**【請求項12】**

前記第1半導体層の最上部と前記第1ゲート電極層の最下部との間の間隔が、前記第2半導体層と前記第1ゲート電極層との接合における拡散電位で広がる空乏層の間隔よりも小さく、

前記第1ゲート電極層の最上部と前記第2ゲート電極層の最下部との間の間隔が、前記第4半導体層と前記第1ゲート電極層との接合における拡散電位で広がる空乏層の間隔の2倍よりも小さいことを特徴とする、請求項10または11に記載の横型接合型電界効果トランジスタ。 40

**【請求項13】**

前記第4半導体層と前記第5半導体層との間に、前記第3半導体層と前記第4半導体層と前記第1ゲート電極層とほぼ同じ構造である単位トランジスタ構造を1つまたは2以上備える、請求項10から12のいずれかに記載の横型接合型電界効果トランジスタ。

**【請求項14】**

半導体基板上に位置する第1導電型不純物を含む第1半導体層と、

前記第1半導体層の上に位置し、前記第1半導体層の不純物濃度よりも高い濃度の第2導電型不純物を含む第2半導体層と、

前記第2半導体層の上に位置し、第1導電型不純物を含む第3半導体層と、

前記第3半導体層の上に位置し、第2導電型不純物を含む第4半導体層と、

前記第4半導体層の上に位置し、第1導電型不純物を含む第5半導体層と、

前記第5半導体層中において所定の間隔を隔てて、下面が前記第2半導体層にまで延在する

ように設けられ、前記第2半導体層および第4半導体層の不純物濃度よりも高い濃度の

第2導電型の不純物を含むソース／ドレイン領域層と、

前記第3半導体層中の前記ソース／ドレイン領域層の間ににおいて、下面が前記第2半導体層

にまで延在し、上面が前記第4半導体層にまで延在するよう設けられ、前記第2半導体層

および前記第4半導体層の不純物濃度よりも高い不純物濃度を含む第1ゲート電極層と、

前記第5半導体層中の前記ソース／ドレイン領域層の間ににおいて、下面が前記第4半導体層

にまで延在するよう設けられ、前記第1ゲート電極層とほぼ同じ不純物濃度を有し、

かつ、同電位を有する第1導電型の第2ゲート電極層と、

前記第1半導体層と前記第1ゲート電極層とに挟まれた前記第2半導体層に、前記第1ゲート

電極層とほぼ同じ不純物濃度を有し、かつ、同電位を有する第1導電型の第1不純物注入領域と、

前記第1ゲート電極層と前記第2ゲート電極層とに挟まれた前記第4半導体層に、前記第1ゲート

電極層とほぼ同じ不純物濃度を有し、かつ同電位を有する第1導電型の第2不純物注入領域と、

を備える、横型接合型電界効果トランジスタ。

**【請求項15】**

前記第2半導体層と、前記第3半導体層と、前記第4半導体層と、前記第5半導体層との

不純物濃度と膜厚さとがほぼ同じである、請求項14に記載の横型接合型電界効果トラン

ジスタ。

**【請求項16】**

前記第1半導体層の最上部と前記第1不純物注入領域の最下部との間の間隔が、前記第2

半導体層と前記第1不純物注入領域との接合における拡散電位で広がる空乏層の間隔よりも

小さく、

前記第1不純物注入領域の最上部と前記第1ゲート電極層の最下部との間隔が、前記第2

半導体層と前記第1ゲート電極層との接合における拡散電位で広がる空乏層の間隔の2倍

よりも小さく、

前記第1ゲート電極層の最上部と前記第2不純物注入領域の最下部との間の間隔が、前記

第4半導体層と前記第2不純物注入領域との接合における拡散電位で広がる空乏層の間隔

の2倍よりも小さく、

前記第2不純物注入領域の最上部と前記第2ゲート電極層の最下部との間の間隔が、前記

第4半導体層と前記第2ゲート電極層との接合における拡散電位で広がる空乏層の間隔の

2倍よりも小さいことを特徴とする、請求項14または15のいずれかに記載の横型接合

型電界効果トランジスタ。

**【請求項17】**

前記第2半導体層には、前記第1不純物注入領域が複数層設けられ、前記第4半導体層には、

前記第2不純物注入領域が複数層設けられる、請求項14から16のいずれかに記載の横型接合

型電界効果トランジスタ。

**【請求項18】**

前記第4半導体層と前記第5半導体層との間に、前記第3半導体層と前記第4半導体層と

前記第1ゲート電極層と前記第2不純物注入領域とほぼ同じ構造である単位トランジスタ

構造を1つまたは2以上備える、請求項14から17のいずれかに記載の横型接合型電界

効果トランジスタ。

**【請求項19】**

半導体基板上に位置する第1導電型不純物を含む第1半導体層と、

前記第1半導体層の上に位置し、前記第1半導体層の不純物濃度よりも高い濃度の第2導

電型不純物を含む第2半導体層と、

前記第2半導体層の上に位置し、第1導電型不純物を含む第3半導体層と、

前記第3半導体層の上に位置し、第2導電型不純物を含む第4半導体層と、

前記第4半導体層の上に位置し、第1導電型不純物を含む第5半導体層と、

前記第5半導体層中において所定の間隔を隔てて、下面が前記第2半導体層にまで延在するように設けられ、前記第2半導体層および第4半導体層の不純物濃度よりも高い濃度の第2導電型の不純物を含むソース／ドレイン領域層と、

前記第5半導体層中の前記ソース／ドレイン領域層の間において、下面が前記第2半導体層にまで延在するように設けられ、前記第2半導体層の不純物濃度よりも高い第1導電型の不純物濃度を含む第1ゲート電極層と、

前記第5半導体層中の前記ソース／ドレイン領域層の間において、下面が前記第2半導体層にまで延在するように前記第1ゲート電極層に隣接して設けられ、前記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ、同電位を有する第1導電型の第2ゲート電極層と、

、

を備える横型接合型電界効果トランジスタ。

**【請求項20】**

前記第2半導体層と、前記第3半導体層と、前記第4半導体層と、前記第5半導体層との不純物濃度と膜厚さとがほぼ同じである、請求項19に記載の横型接合型電界効果トランジスタ。

**【請求項21】**

前記第1ゲート電極層と前記第2ゲート電極層との間の間隔が、前記第2半導体層と前記第1ゲート電極層との接合における拡散電位で広がる空乏層の間隔、および前記第4半導体層と前記第1ゲート電極層との接合における拡散電位で広がる空乏層の間隔の2倍よりも小さいことを特徴とする、請求項19または20に記載の横型接合型電界効果トランジスタ。

**【請求項22】**

前記第1ゲート電極層と前記第2ゲート電極層との間に、下面が前記第2半導体層にまで延在するように設けられ、前記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ、同電位を有する第1導電型の不純物注入領域を1つ備える、請求項19から21のいずれかに記載の横型接合型電界効果トランジスタ。

**【請求項23】**

前記第1ゲート電極層と前記不純物注入領域との間の間隔および前記不純物注入領域と前記第2ゲート電極層との間隔が、前記第2半導体層と前記第1ゲート電極層との接合における拡散電位で広がる空乏層の間隔、および前記第4半導体層と前記第1ゲート電極層との接合における拡散電位で広がる空乏層の間隔の2倍よりも小さいことを特徴とする、請求項22に記載の横型接合型電界効果トランジスタ。

**【請求項24】**

前記不純物注入領域が2以上設けられる、請求項23に記載の横型接合型電界効果トランジスタ。

**【請求項25】**

前記第1ゲート電極層に最も近接する前記不純物注入領域と前記第1ゲート電極層との間の間隔、前記不純物注入領域同士の間隔、および前記第2ゲート電極層に最も近接する前記不純物注入領域と前記第2ゲート電極層との間の間隔が、いずれも、前記第2半導体層と前記第1ゲート電極層との接合における拡散電位で広がる空乏層の間隔、および前記第4半導体層と前記第1ゲート電極層との接合における拡散電位で広がる空乏層の間隔の2倍よりも小さいことを特徴とする、請求項24に記載の横型接合型電界効果トランジスタ。

**【請求項26】**

前記第4半導体層と前記第5半導体層との間に、前記第3半導体層と前記第4半導体層とほぼ同じ構造を1つ以上有する、請求項19から25のいずれかに記載の横型接合型電界

10

20

30

40

50

効果トランジスタ。

【請求項 27】

半導体基板上に位置する第1導電型不純物を含む第1半導体層と、

前記第1半導体層の上に位置し、第1導電型不純物を含む第2半導体層と、

前記第1半導体層の上に、かつ、前記第2半導体層に隣接して位置し、第2導電型不純物を含む第3半導体層と、

前記第2半導体層および前記第3半導体層中において所定の間隔を隔てて設けられ、前記第3半導体層の不純物濃度よりも高い濃度の第2導電型の不純物を含むソース／ドレイン領域層と、

前記第2半導体層中の前記ソース／ドレイン領域層の間ににおいて、その一方の側面が前記第3半導体層にまで延在するように設けられ、前記第1半導体層の不純物濃度よりも高い第1導電型の不純物濃度を含むゲート電極層と、

を備える横型接合型電界効果トランジスタ。

【請求項 28】

前記第2半導体層と、前記第3半導体層との不純物濃度と膜厚さとがほぼ同じである、請求項27に記載の横型接合型電界効果トランジスタ。

【請求項 29】

前記ゲート電極層と、前記第3半導体層の前記ゲート電極層と接しない面との間隔が、前記第3半導体層と前記ゲート電極層との接合における拡散電位で拡がる空乏層の間隔よりも小さいことを特徴とする、請求項27または28に記載の横型接合型電界効果トランジスタ。

【請求項 30】

半導体基板上に位置する第1導電型不純物を含む第1半導体層と、

前記第1半導体層の上に位置し、第1導電型不純物を含む第2半導体層と、

前記第1半導体層の上に、かつ、前記第2半導体層に隣接して位置し、第2導電型不純物を含む第3半導体層と、

前記第1半導体層の上に、かつ、前記第3半導体層に隣接して位置し、第1導電型不純物を含む第4半導体層と、

前記第1半導体層の上に、かつ、前記第4半導体層に隣接して位置し、第2導電型不純物を含む第5半導体層と、

前記第2半導体層、前記第3半導体層、前記第4半導体層および前記第5半導体層中において所定の間隔を隔てて設けられ、前記第3半導体層および前記第5半導体層の不純物濃度よりも高い濃度の第2導電型の不純物を含むソース／ドレイン領域層と、

前記第2半導体層中の前記ソース／ドレイン領域層の間ににおいて、その一方の側面が前記第3半導体層にまで延在するように設けられ、前記第3半導体層の不純物濃度よりも高い第1導電型の不純物濃度を含む第1ゲート電極層と、前記第4半導体層中の前記ソース／ドレイン領域層の間ににおいて、その一方の側面が前記第5半導体層にまで延在するように設けられ、前記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ、同電位を有する第1導電型の第2ゲート電極層と、を備える横型接合型電界効果トランジスタ。

【請求項 31】

前記第2半導体層と、前記第3半導体層と、前記第4半導体層と、前記第5半導体層との不純物濃度と膜厚さとがほぼ同じである、請求項30に記載の横型接合型電界効果トランジスタ。

【請求項 32】

前記第1ゲート電極層と、前記第3半導体層の前記第1ゲート電極層と接しない面との間の間隔が、前記第3半導体層と前記第1ゲート電極層との接合における拡散電位で広がる空乏層の間隔よりも小さく、

前記第2ゲート電極層と前記第5半導体層の前記第2ゲート電極層と接しない面との間隔が、前記第5半導体層と前記第2ゲート電極層との接合における拡散電位で広がる空乏層の間隔よりも小さいことを特徴とする、請求項30または31に記載の横型接合型電界効

10

20

30

40

50

果トランジスタ。

【請求項 3 3】

前記第 3 半導体層と前記第 4 半導体層との間に、前記第 4 半導体層と前記第 5 半導体層と前記第 2 ゲート電極層とほぼ同じ構造である単位トランジスタ構造を 1 つ以上備える、請求項 20 から 32 のいずれかに記載の横型接合型電界効果トランジスタ。

【請求項 3 4】

半導体基板上に位置する第 1 導電型不純物を含む第 1 半導体層と、

前記第 1 半導体層の上に位置し、第 1 導電型不純物を含む第 2 半導体層と、

前記第 1 半導体層の上に、かつ、前記第 2 半導体層に隣接して位置し、前記第 2 導電型不純物を含む第 3 半導体層と、10

前記第 1 半導体層の上に、かつ、前記第 3 半導体層に隣接して位置し、第 1 導電型不純物を含む第 4 半導体層と、

前記第 2 半導体層、前記第 3 半導体層および前記第 4 半導体層中において所定の間隔を隔てて設けられ、前記第 3 半導体層の不純物濃度よりも高い濃度の第 2 導電型の不純物を含むソース／ドレイン領域層と、

前記第 2 半導体層中の前記ソース／ドレイン領域層の間において、その一方の側面が前記第 3 半導体層にまで延在するように設けられ、前記第 3 半導体層の不純物濃度よりも高い第 1 導電型の不純物濃度を含むゲート電極層と、

を備える横型接合型電界効果トランジスタ。

【請求項 3 5】

前記第 2 半導体層と、前記第 3 半導体層と、前記第 4 半導体層との不純物濃度と膜厚さとがほぼ同じである、請求項 34 に記載の横型接合型電界効果トランジスタ。20

【請求項 3 6】

前記ゲート電極層と前記第 4 半導体層との間の間隔が、前記第 3 半導体層と前記ゲート電極層との接合における拡散電位で広がる空乏層の間隔よりも小さいことを特徴とする、請求項 34 または 35 に記載の横型接合型電界効果トランジスタ。

【請求項 3 7】

前記第 3 半導体層と前記第 4 半導体層との間に前記第 2 半導体層と前記第 3 半導体層と前記ゲート電極層とほぼ同じ構造である単位トランジスタ構造を 1 つまたは 2 以上備える、請求項 34 から 36 のいずれかに記載の横型接合型電界効果トランジスタ。30

【請求項 3 8】

半導体基板上に位置する第 1 導電型不純物を含む第 1 半導体層と、

前記第 1 半導体層の上に位置し、第 1 導電型不純物を含む第 2 半導体層と、

前記第 1 半導体層の上に、かつ、前記第 2 半導体層に隣接して位置し、第 2 導電型不純物を含む第 3 半導体層と、

前記第 2 半導体層および前記第 3 半導体層中において所定の間隔を隔てて設けられ、前記第 3 半導体層の不純物濃度よりも高い濃度の第 2 導電型の不純物を含むソース／ドレイン領域層と、40

前記第 2 半導体層中の前記ソース／ドレイン領域層の間において、その一方の側面が前記第 3 半導体層にまで延在するように設けられ、前記第 3 半導体層の不純物濃度よりも高い第 1 導電型の不純物濃度を含むゲート電極層と、

前記ゲート電極層と前記第 3 半導体層の前記ゲート電極層と接しない面とに挟まれた前記第 3 半導体層に、前記ゲート電極層とほぼ同じ不純物濃度を有し、かつ、同電位を有する第 1 導電型の不純物注入領域と、

を備える横型接合型電界効果トランジスタ。

【請求項 3 9】

前記第 2 半導体層と、前記第 3 半導体層との不純物濃度と膜厚さとがほぼ同じである、請求項 38 に記載の横型接合型電界効果トランジスタ。

【請求項 4 0】

前記ゲート電極層と前記不純物注入領域との最も大きく接する面同士の間隔が、前記第 3 50

半導体層と前記ゲート電極層との接合における拡散電位で広がる空乏層の間隔の2倍よりも小さく、

前記不純物注入領域と、前記第3半導体層の前記ゲート電極層と接しない面との間の間隔が、前記第3半導体層と前記ゲート電極層との接合における拡散電位で広がる空乏層の間隔よりも小さいことを特徴とする、請求項38または39に記載の横型接合型電界効果トランジスタ。

#### 【請求項41】

前記第3半導体層には、前記不純物注入領域が複数層設けられる、請求項38から40のいずれかに記載の横型接合型電界効果トランジスタ。

#### 【請求項42】

半導体基板上に位置する第1導電型不純物を含む第1半導体層と、

10

前記第1半導体層の上に位置し、第1導電型不純物を含む第2半導体層と、

前記第1半導体層の上に、かつ、前記第2半導体層に隣接して位置し、第2導電型不純物を含む第3半導体層と、

前記第1半導体層の上に、かつ、前記第3半導体層に隣接して位置し、第1導電型不純物を含む第4半導体層と、

前記第1半導体層の上に、かつ前記第4半導体層に隣接して位置し、第2導電型不純物を含む第5半導体層と、

前記第2半導体層、前記第3半導体層、前記第4半導体層および前記第5半導体層中において所定の間隔を隔てて設けられ、前記第3半導体層および前記第5半導体層の不純物濃度よりも高い濃度の第2導電型の不純物を含むソース／ドレイン領域層と、

20

前記第2半導体層中の前記ソース／ドレイン領域層の間において、その一方の側面が前記第3半導体層にまで延在するように設けられ、前記第3半導体層の不純物濃度よりも高い第1導電型の不純物濃度を含む第1ゲート電極層と、

前記第4半導体層中の前記ソース／ドレイン領域層の間においてその一方の側面が前記第5半導体層にまで延在するように設けられ、前記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ同電位を有する第2ゲート電極層と、

前記第4半導体層と前記第1ゲート電極層とに挟まれた前記第3半導体層に、前記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ同電位を有する第1導電型の第1不純物注入領域と、

30

前記第2ゲート電極層と、前記第5半導体層の前記第2ゲート電極層と接しない面とに挟まれた前記第5半導体層に、前記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ、同電位を有する第1導電型の第2不純物注入領域と、

を備える横型接合型電界効果トランジスタ。

#### 【請求項43】

前記第2半導体層と、前記第3半導体層と、前記第4半導体層と、前記第5半導体層との不純物濃度と膜厚さとがほぼ同じである、請求項42に記載の横型接合型電界効果トランジスタ。

#### 【請求項44】

前記第1ゲート電極層と前記第1不純物注入領域との最も近接する面同士の間隔が、前記第3半導体層と前記第1ゲート電極層との接合における拡散電位で広がる空乏層の間隔の2倍よりも小さく、

40

前記第1不純物注入領域と、前記第3半導体層の前記第1ゲート電極層と接しない面との間の間隔が、前記第3半導体層と前記第1ゲート電極層との接合における拡散電位で広がる空乏層の間隔よりも小さく、

前記第2ゲート電極層と前記第2不純物注入領域との最も近接する面同士の間隔が、前記第5半導体層と前記第2ゲート電極層との接合における拡散電位で広がる空乏層の間隔の2倍よりも小さく、

前記第2不純物注入領域と、前記第5半導体層の前記第2ゲート電極層と接しない面との間の間隔が、前記第5半導体層と前記第2ゲート電極層との接合における拡散電位で広が

50

る空乏層の間隔よりも小さいことを特徴とする、請求項 4 2 または 4 3 に記載の横型接合型電界効果トランジスタ。

**【請求項 4 5】**

前記第 3 半導体層には、前記第 1 不純物注入領域が複数層設けられ、前記第 5 半導体層には、前記第 2 不純物注入領域が複数層設けられる、請求項 4 2 から 4 4 のいずれかに記載の横型接合型電界効果トランジスタ。

**【請求項 4 6】**

前記第 3 半導体層と前記第 4 半導体層との間に、前記第 4 半導体層と前記第 5 半導体層と前記第 2 ゲート電極層と前記第 2 不純物注入領域とほぼ同じ構造である単位トランジスタ構造を 1 つ以上備える、請求項 4 2 から 4 5 のいずれかに記載の横型接合型電界効果トランジスタ。10

**【請求項 4 7】**

半導体基板上に位置する第 1 導電型不純物を含む第 1 半導体層と、

前記第 1 半導体層の上に位置し、第 1 導電型不純物を含む第 2 半導体層と、

前記第 1 半導体層の上に、かつ、前記第 2 半導体層に隣接して位置し、第 2 導電型不純物を含む第 3 半導体層と、20

前記第 1 半導体層の上に、かつ、前記第 3 半導体層に隣接して位置し、第 1 導電型不純物を含む第 4 半導体層と、

前記第 2 半導体層、前記第 3 半導体層および前記第 4 半導体層中において所定の間隔を隔てて設けられ、前記第 3 半導体層の不純物濃度よりも高い濃度の第 2 導電型の不純物を含むソース / ドレイン領域層と、20

前記第 2 半導体層中の前記ソース / ドレイン領域層の間において、その一方の側面が前記第 3 半導体層にまで延在するように設けられ、前記第 3 半導体層の不純物濃度よりも高い第 1 導電型の不純物濃度を含むゲート電極層と、

前記第 4 半導体層と前記ゲート電極層とに挟まれた前記第 3 半導体層に、前記ゲート電極層とほぼ同じ不純物濃度を有し、かつ同電位を有する第 1 導電型の不純物注入領域と、を備える横型接合型電界効果トランジスタ。20

**【請求項 4 8】**

前記第 2 半導体層と、前記第 3 半導体層と、前記第 4 半導体層の不純物濃度と膜厚さとがほぼ同じである、請求項 4 7 に記載の横型接合型電界効果トランジスタ。30

**【請求項 4 9】**

前記ゲート電極層と前記不純物注入領域との間の間隔が、前記第 3 半導体層と前記ゲート電極層との接合における拡散電位で広がる空乏層の間隔の 2 倍よりも小さく、

前記不純物注入領域と前記第 4 半導体層との間の間隔が、前記第 3 半導体層と前記ゲート電極層との接合における拡散電位で広がる空乏層の間隔よりも小さいことを特徴とする、請求項 4 7 または 4 8 に記載の横型接合型電界効果トランジスタ。30

**【請求項 5 0】**

前記第 3 半導体層には、前記不純物注入領域が複数層設けられる、請求項 4 7 から 4 9 のいずれかに記載の横型接合型電界効果トランジスタ。40

**【請求項 5 1】**

前記第 3 半導体層と前記第 4 半導体層との間に、前記第 2 半導体層と前記第 3 半導体層と前記ゲート電極層と前記不純物注入領域とほぼ同じ構造である単位トランジスタ構造を 1 つまたは 2 以上備える、請求項 4 7 から 5 0 のいずれかに記載の横型接合型電界効果トランジスタ。40

**【請求項 5 2】**

半導体基板上に位置する第 1 導電型不純物を含む第 1 半導体層と、

前記第 1 半導体層の上に位置し、第 1 導電型不純物を含む第 2 半導体層と、

前記第 1 半導体層の上に、かつ、前記第 2 半導体層に隣接して位置し、第 2 導電型不純物を含む第 3 半導体層と、50

前記第 1 半導体層の上に、かつ、前記第 3 半導体層に隣接して位置し、第 1 導電型不純物

を含む第4半導体層と、

前記第2半導体層、前記第3半導体層および前記第4半導体層中において所定の間隔を隔てて設けられ、前記第3半導体層の不純物濃度よりも高い濃度の第2導電型の不純物を含むソース／ドレイン領域層と、

前記第2半導体層中の前記ソース／ドレイン領域層の間において、その一方の側面が前記第3半導体層にまで延在するように設けられ、前記第3半導体層の不純物濃度よりも高い第1導電型の不純物濃度を含む第1ゲート電極層と、

前記第4半導体層中の前記ソース／ドレイン領域層の間において、その一方の側面が前記第3半導体層にまで延在するように設けられ、前記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ同電位を有する第1導電型の第2ゲート電極層と、

を備える横型接合型電界効果トランジスタ。10

**【請求項53】**

前記第2半導体層と、前記第3半導体層と、前記第4半導体層との不純物濃度と膜厚さとがほぼ同じである、請求項52に記載の横型接合型電界効果トランジスタ。

**【請求項54】**

前記第1ゲート電極層と、前記第2ゲート電極層の最も近接する面同士の間隔が、前記第3半導体層と前記第1ゲート電極層との接合における拡散電位で広がる空乏層の間隔の2倍よりも小さいことを特徴とする、請求項52または53に記載の横型接合型電界効果トランジスタ。

**【請求項55】**

半導体基板上に位置する第1導電型不純物を含む第1半導体層と、20

前記第1半導体層の上に位置し、第1導電型不純物を含む第2半導体層と、

前記第1半導体層の上に、かつ、前記第2半導体層に隣接して位置し、第2導電型不純物を含む第3半導体層と、

前記第1半導体層の上に、かつ前記第3半導体層に隣接して位置し、第1導電型不純物を含む第4半導体層と、

前記第1半導体層の上に、かつ前記第4半導体層に隣接して位置し、第2導電型不純物を含む第5半導体層と、

前記第1半導体層の上に、かつ、前記第5半導体層に隣接して位置し、第1導電型不純物を含む第6半導体層と、30

前記第2半導体層、前記第3半導体層、前記第4半導体層、前記第5半導体層および前記第6半導体層中において所定の間隔を隔てて設けられ、前記第3半導体層および前記第5半導体層の不純物濃度よりも高い濃度の第2導電型の不純物を含むソース／ドレイン領域層と、

前記第2半導体層中の前記ソース／ドレイン領域層の間において、その一方の側面が前記第3半導体層にまで延在するように設けられ、前記第3半導体層の不純物濃度よりも高い第1導電型の不純物濃度を含む第1ゲート電極層と、

前記第4半導体層中の前記ソース／ドレイン領域層の間においてその一方の側面が前記第3半導体層にまで延在し、他方の側面が前記第5半導体層にまで延在するように設けられ、前記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ同電位を有する第1導電型の第2ゲート電極層と、40

前記第6半導体層の前記ソース／ドレイン領域層の間においてその一方の側面が前記第5半導体層にまで延在するように設けられ、前記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ、同電位を有する第1導電型の第3ゲート電極層と、

を備える横型接合型電界効果トランジスタ。

**【請求項56】**

前記第2半導体層と、前記第3半導体層と、前記第4半導体層と、前記第5半導体層と、前記第6半導体層との不純物濃度と膜厚さとがほぼ同じである、請求項55に記載の横型接合型電界効果トランジスタ。

**【請求項57】**

10

20

30

40

50

前記第1ゲート電極層と、前記第2ゲート電極層の最も近接する面同士の間隔が、前記第3半導体層と前記第1ゲート電極層との接合における拡散電位で広がる空乏層の間隔の2倍よりも小さく、

前記第2ゲート電極層と前記第3ゲート電極層の最も近接する面同士の間隔が、前記第3半導体層と前記第1ゲート電極層との接合における拡散電位で広がる空乏層の間隔の2倍よりも小さいことを特徴とする、請求項55または56に記載の横型接合型電界効果トランジスタ。

#### 【請求項58】

前記第5半導体層と前記第6半導体層との間に、前記第4半導体層と前記5半導体層と前記第2ゲート電極層とほぼ同じ構造である単位トランジスタ構造を1つ以上備える、請求項55から57のいずれかに記載の横型接合型電界効果トランジスタ。10

#### 【請求項59】

半導体基板上に位置する第1導電型不純物を含む第1半導体層と、

前記第1半導体層上に位置し、第1導電型不純物を含む第2半導体層と、

前記第1半導体層の上に、かつ、前記第2半導体層に隣接して位置し、第2導電型不純物を含む第3半導体層と、

前記第1半導体層の上に、かつ、前記第3半導体層に隣接して位置し、第1導電型不純物を含む第4半導体層と、

前記第2半導体層、前記第3半導体層および前記第4半導体層中において所定の間隔を隔てて設けられ、前記第3半導体層の不純物濃度よりも高い濃度の第2導電型の不純物を含むソース／ドレイン領域層と、20

前記第2半導体層中の前記ソース／ドレイン領域層の間において、その一方の側面が前記第3半導体層にまで延在するように設けられ、前記第3半導体層の不純物濃度よりも高い第1導電型の不純物濃度を含む第1ゲート電極層と、

前記第4半導体層中の前記ソース／ドレイン領域層の間において、その一方の側面が前記第3半導体層にまで延在するように設けられ、前記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ同電位を有する第2ゲート電極層と、

前記第1ゲート電極層と前記第2ゲート電極層とに挟まれた前記第3半導体層に、前記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ同電位を有する第1導電型の不純物注入領域と、30

を備える横型接合型電界効果トランジスタ。

#### 【請求項60】

前記第2半導体層と前記第3半導体層と前記第4半導体層との不純物濃度と膜厚さとがほぼ同じである、請求項59に記載の横型接合型電界効果トランジスタ。

#### 【請求項61】

前記第1ゲート電極層と、前記不純物注入領域の最も近接する面同士の間隔が、前記第3半導体層と前記第1ゲート電極層との接合における拡散電位で広がる空乏層の間隔の2倍よりも小さく、

前記不純物注入領域と、前記第2ゲート電極層の最も近接する面同士の間隔が、前記第3半導体層と前記第1ゲート電極層との接合における拡散電位で広がる空乏層の間隔の2倍よりも小さいことを特徴とする、請求項59または60に記載の横型接合型電界効果トランジスタ。40

#### 【請求項62】

前記第3半導体層には、前記不純物注入領域が複数層設けられる、請求項59から61のいずれかに記載の横型接合型電界効果トランジスタ。

#### 【請求項63】

半導体基板上に位置する第1導電型不純物を含む第1半導体層と、

前記第1半導体層の上に位置し、第1導電型不純物を含む第2半導体層と、

前記第1半導体層の上に、かつ、前記第2半導体層に隣接して位置し、第2導電型不純物を含む第3半導体層と、50

前記第1半導体層の上にかつ前記第3半導体層に隣接して位置し、第1導電型不純物を含む第4半導体層と、

前記第1半導体層の上に、かつ、前記第4半導体層に隣接して位置し、第2導電型不純物を含む第5半導体層と、

前記第1半導体層の上に、かつ、前記第5半導体層に隣接して位置し、第1導電型不純物を含む第6半導体層と、

前記第2半導体層、前記第3半導体層、前記第4半導体層、前記第5半導体層および前記第6半導体層中において所定の間隔を隔てて設けられ、前記第3半導体層および前記第5半導体層の不純物濃度よりも高い濃度の第2導電型の不純物を含むソース／ドレイン領域層と、

前記第2半導体層中の前記ソース／ドレイン領域層の間ににおいて、その一方の側面が前記第3半導体層にまで延在するように設けられ、前記第3半導体層の不純物濃度よりも高い第1導電型の不純物濃度を含む第1ゲート電極層と、

前記第4半導体層中の前記ソース／ドレイン領域層の間ににおいて、その一方の側面が前記第3半導体層にまで延在し、他方の側面が前記第5半導体層にまで延在するように設けられ、前記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ同電位を有する第1導電型の第2ゲート電極層と、

前記第6半導体層中の前記ソース／ドレイン領域層の間ににおいて、その一方の側面が前記第5半導体層にまで延在するように設けられ、前記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ、同電位を有する第1導電型の第3ゲート電極層と、

前記第1ゲート電極層と前記第2ゲート電極層とに挟まれた前記第3半導体層に、前記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ、同電位を有する第1導電型の第1不純物注入領域と、

前記第2ゲート電極層と前記第3ゲート電極層とに挟まれた前記第5半導体層に、前記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ同電位を有する第1導電型の第2不純物注入領域と、

を備える横型接合型電界効果トランジスタ。

**【請求項64】**

前記第2半導体層と、前記第3半導体層と、前記第4半導体層と、前記第5半導体層と、前記第6半導体層との不純物濃度と膜厚さとがほぼ同じである、請求項63に記載の横型接合型電界効果トランジスタ。

**【請求項65】**

前記第1ゲート電極層と、前記第1不純物注入領域の最も近接する面同士の間隔が、前記第3半導体層と前記第1ゲート電極層との接合における拡散電位で広がる空乏層の間隔の2倍よりも小さく、

前記第1不純物注入領域と、前記第2ゲート電極層の最も近接する面同士の間隔が、前記第3半導体層と前記第1ゲート電極層との接合における拡散電位で広がる空乏層の間隔の2倍よりも小さく、

前記第2ゲート電極層と、前記第2不純物注入領域の最も近接する面同士の間隔が、前記第3半導体層と前記第1ゲート電極層との接合における拡散電位で広がる空乏層の間隔の2倍よりも小さく、

前記第2不純物注入領域と、前記第3ゲート電極層の最も近接する面同士の間隔が、前記第3半導体層と前記第1ゲート電極層との接合における拡散電位で広がる空乏層の間隔の2倍よりも小さいことを特徴とする、請求項63または64に記載の横型接合型電界効果トランジスタ。

**【請求項66】**

前記第3半導体層には、前記第1不純物注入領域が複数層設けられる、前記第5半導体層には、前記第2不純物注入領域が複数層設けられる、請求項63から65のいずれかに記載の横型接合型電界効果トランジスタ。

**【請求項67】**

10

20

30

40

50

前記第5半導体層と前記第6半導体層との間に、前記第4半導体層と前記第5半導体層と前記第2ゲート電極層と前記第2不純物注入領域とほぼ同じ構造である単位トランジスタ構造を1つ以上備える、請求項63から66のいずれかに記載の横型接合型電界効果トランジスタ。

**【請求項68】**

半導体基板上に、第1導電型不純物を含む第1半導体層を形成する工程と、

前記第1半導体層の上に、前記第1半導体層の不純物濃度よりも高い濃度の第2導電型不純物を含む第2半導体層を形成する工程と、

前記第2半導体層の上に、第1導電型不純物を含む第3半導体層を形成する工程と、

前記第2半導体層と前記第3半導体層とにまたがるように、第3半導体層の所定領域に不純物を導入して、前記第2半導体層の不純物濃度よりも高い第1導電型の不純物濃度を含む第1ゲート電極層を形成する工程と、

前記第3半導体層の上に、第2導電型不純物を含む第4半導体層を形成する工程と、

前記第4半導体層の上に、第1導電型不純物を含む第5半導体層を形成する工程と、

前記第5半導体層の所定領域に不純物を導入して、下面が前記第4半導体層にまで延在し、前記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ、同電位を有する第2ゲート電極層を形成する工程と、

前記第1ゲート電極層および前記第2ゲート電極層の両側において、前記第5半導体層に不純物を導入して、下面が前記第2半導体層にまで延在し、前記第2半導体層および前記第4半導体層の不純物濃度よりも高い濃度の第2導電型の不純物を含むソース／ドレイン領域層を形成する工程と、

を備える、横型接合型電界効果トランジスタの製造方法。

**【請求項69】**

半導体基板上に、第1導電型不純物を含む第1半導体層を形成する工程と、

前記第1半導体層の上に、前記第1半導体層の不純物濃度よりも高い濃度の第2導電型不純物を含む第2半導体層を形成する工程と、

前記第2半導体層の所定領域に不純物を導入して、前記第2半導体層内に第1導電型の第1不純物注入領域を形成する工程と、

前記第2半導体層の上に、第1導電型不純物を含む第3半導体層を形成する工程と、

前記第2半導体層と前記第3半導体層とにまたがるように不純物を導入して、前記第2半導体層の不純物濃度よりも高い第1導電型の不純物濃度を含む第1ゲート電極層を形成する工程と、

前記第3半導体層の上に、第2導電型不純物を含む第4半導体層を形成する工程と、前記第4半導体層の所定領域に不純物を導入して、前記第4半導体層内に前記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ、同電位を有する第1導電型の第2不純物注入領域を形成する工程と、

前記第4半導体層の上に、第1導電型不純物を含む第5半導体層を形成する工程と、

前記第5半導体層の所定領域に不純物を導入して、下面が前記第4半導体層にまで延在するように設けられ、前記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ、同電位を有する第2ゲート電極層を形成する工程と、

前記第1ゲート電極層および前記第2ゲート電極層の両側において、前記第5半導体層の所定領域に不純物を導入して、下面が前記第2半導体層にまで延在するように設けられ、前記第2半導体層および第4半導体層の不純物濃度よりも高い濃度の第2導電型の不純物を含むソース／ドレイン領域層を形成する工程と、を備える横型接合型電界効果トランジスタの製造方法。

**【請求項70】**

半導体基板上に、第1導電型不純物を含む第1半導体層を形成する工程と、

前記第1半導体層の上に、前記第1半導体層の不純物濃度よりも高い濃度の第2導電型不純物を含む第2半導体層を形成する工程と、

前記第2半導体層の上に、第1導電型不純物を含む第3半導体層を形成する工程と、

10

20

30

40

50

前記第3半導体層の上に、第2導電型不純物を含む第4半導体層を形成する工程と、

前記第4半導体層の所定領域に不純物を導入し、下面が前記第2半導体層にまで延在し、

上面が前記第4半導体層にまで延在し、前記第2半導体層および前記第4半導体層の不純

物濃度よりも高い第1導電型の不純物濃度を含む第1ゲート電極層を形成する工程と、

前記第4半導体層の上に、第1導電型不純物を含む第5半導体層を形成する工程と、

前記第5半導体層の所定領域に不純物を導入し、下面が前記第4半導体層にまで延在する

ように設けられ、前記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ、同電位を有

する第2ゲート電極層を形成する工程と、

前記第1ゲート電極層および前記第2ゲート電極層の両側において、前記第5半導体層の

所定領域に不純物を導入して、下面が前記第2半導体層にまで延在するように設けられ、

前記第2半導体層および第4半導体層の不純物濃度よりも高い濃度の第2導電型の不純物

を含むソース／ドレイン領域層と、

を備える横型接合型電界効果トランジスタの製造方法。

**【請求項 7 1】**

半導体基板の上に、第1導電型不純物を含む第1半導体層を形成する工程と、

前記第1半導体層の上に、前記第1半導体層の不純物濃度よりも高い濃度の第2導電型不

純物を含む第2半導体層を形成する工程と、

前記第2半導体層の上に、第1導電型不純物を含む第3半導体層を形成する工程と、

前記第3半導体層の上に、第2導電型不純物を含む第4半導体層を形成する工程と、

前記第4半導体層の所定領域に不純物を導入して、下面が前記第2半導体層にまで延在し

、上面が前記第4半導体層にまで延在し、前記第2半導体層および前記第4半導体層の

不純物濃度よりも高い不純物濃度を含む第1ゲート電極層を形成する工程と、

前記第2半導体層の所定領域に不純物を導入して、前記第2半導体層内に、前記第1ゲー

ト電極層とほぼ同じ不純物濃度を有し、かつ同電位を有する第1導電型の第1不純物注入

領域を形成する工程と、

前記第4半導体層の上に、第1導電型不純物を含む第5半導体層を形成する工程と、

前記第5半導体層の所定領域に不純物を導入して、下面が前記第4半導体層にまで延在す

るように設けられ、前記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ、同電位を

有する第1導電型の第2ゲート電極層を形成する工程と、

前記第4半導体層の所定領域に不純物を導入して、前記第4半導体層内に、前記第1ゲー

ト電極層とほぼ同じ不純物濃度を有し、かつ同電位を有する第1導電型の第2不純物注入

領域を形成する工程と、

前記第1ゲート電極層および前記第2ゲート電極層の両側において、下面が前記第2半導

体層にまで延在するように設けられ、前記第2半導体層および第4半導体層の不純物濃度

よりも高い濃度の第2導電型の不純物を含むソース／ドレイン領域層を形成する工程と、

を備える、横型接合型電界効果トランジスタの製造方法。

**【請求項 7 2】**

半導体基板上に、第1導電型不純物を含む第1半導体層を形成する工程と、

前記第1半導体層の上に、前記第1半導体層の不純物濃度よりも高い濃度の第2導電型不

純物を含む第2半導体層を形成する工程と、

前記第2半導体層の上に、第1導電型不純物を含む第3半導体層を形成する工程と、

前記第3半導体層の上に、第2導電型不純物を含む第4半導体層を形成する工程と、

前記第4半導体層の上に、第1導電型不純物を含む第5半導体層を形成する工程と、

前記第5半導体層中の所定領域に不純物を導入することにより、下面が前記第2半導体層

にまで延在するように設けられ、前記第2半導体層の不純物濃度よりも高い第1導電型の

不純物濃度を含み、前記基板の平面方向に沿って互いに所定の間隔を隔てて配置される第

1ゲート電極層および第2ゲート電極層を形成する工程と、

前記第5半導体層中の所定領域に不純物を導入することにより、前記第1ゲート電極層お

よび前記第2ゲート電極層の配置方向に沿って前記第1ゲート電極層および前記第2ゲー

ト電極層を両側から挟みこみ、下面が前記第2半導体層にまで延在するように設けられ、

10

20

30

40

50

前記第2半導体層および第4半導体層の不純物濃度よりも高い濃度の第2導電型の不純物を含むソース／ドレイン領域層を形成する工程と、

を備える横型接合型電界効果トランジスタの製造方法。

**【請求項73】**

半導体基板上に、第1導電型不純物を含む第1半導体層を形成する工程と、

前記第1半導体層の上に、第2導電型不純物を含む半導体層を形成する工程と、

前記半導体層中の所定領域に、前記基板の平面方向に沿って所定の間隔を隔てて第1導電型不純物を導入することにより、第1導電型不純物を含む第2半導体層と第2導電型不純物を含む第3半導体層とを形成する工程と、

前記第2半導体層および前記第3半導体層中の所定領域に不純物を導入することにより、

前記第2半導体層および前記第3半導体層にまたがるように設けられ、前記第1半導体層の不純物濃度よりも高い第1導電型の不純物濃度を含むゲート電極層を形成する工程と、

前記第2半導体層および前記第3半導体層の所定領域に不純物を導入することにより、前記第2半導体層および前記第3半導体層が配置される方向に沿うとともに、前記ゲート電極層を挟み込み、前記第3半導体層の不純物濃度よりも高い濃度の第2導電型の不純物を含むソース／ドレイン領域層を形成する工程と、

を備える横型接合型電界効果トランジスタの製造方法。

**【請求項74】**

半導体基板上に、第1導電型不純物を含む第1半導体層を形成する工程と、

前記第1半導体層の上に、第2導電型不純物を含む半導体層を形成する工程と、

前記半導体層中の所定領域に、前記基板の平面方向に沿って所定の間隔を隔てて第1導電型不純物を導入することにより、第1導電型不純物を含む第2半導体層と第2導電型不純物を含む第3半導体層とを形成する工程と、

前記第2半導体層および前記第3半導体層中の所定領域に不純物を導入することにより、

前記第2半導体層および前記第3半導体層にまたがるように設けられ、前記第3半導体層の不純物濃度よりも高い第1導電型の不純物濃度を含むゲート電極層と、前記第3半導体層の中に、前記ゲート電極層とほぼ同じ不純物濃度を有し、かつ、同電位を有する第1導電型の不純物注入領域とを形成する工程と、

前記第2半導体層および前記第3半導体層の所定領域に不純物を導入することにより、前記第2半導体層および前記第3半導体層が配置される方向に沿うとともに、前記ゲート電極層および不純物注入領域を挟み込み、前記第3半導体層の不純物濃度よりも高い濃度の第2導電型の不純物を含むソース／ドレイン領域層を形成する工程と、

を備える横型接合型電界効果トランジスタの製造方法。

**【請求項75】**

半導体基板上に、第1導電型不純物を含む第1半導体層を形成する工程と、

前記第1半導体層の上に、第2導電型不純物を含む半導体層を形成する工程と、

前記半導体層中の所定領域に、前記基板の平面方向に沿って所定の間隔を隔てて第1導電型不純物を導入することにより、第1導電型不純物を含む第2半導体層、第2導電型不純物を含む第3半導体層、および、第1導電型不純物を含む第4半導体層を形成する工程と、

前記第2半導体層、前記第3半導体層、および、前記第4半導体層中の所定領域に不純物を導入することにより、前記第2半導体層および前記第3半導体層にまたがるように設けられ、前記第3半導体層の不純物濃度よりも高い第1導電型の不純物濃度を含む第1ゲート電極層と、前記第3半導体層および前記第4半導体層にまたがるように設けられ、前記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ同電位を有する第1導電型の第2ゲート電極層とを形成する工程と、前記第2半導体層、前記第3半導体層、および、前記第4半導体層の所定領域に不純物を導入することにより、前記第2半導体層、前記第3半導体層、前記第4半導体層、および、前記第4半導体層が配置される方向に沿うとともに、前記1ゲート電極層および前記第2ゲート電極層を挟み込み、前記第3半導体層の不純物濃度よりも高い濃度の第2導電型の不純物を含むソース／ドレイン領域層を形成する工程と、

10

20

30

40

50

を備える横型接合型電界効果トランジスタの製造方法。

【請求項 7 6】

半導体基板上に、第1導電型不純物を含む第1半導体層を形成すると、

前記第1半導体層の上に、第2導電型不純物を含む半導体層を形成する工程と、

前記半導体層中の所定領域に、前記基板の平面方向に沿って所定の間隔を隔てて第1導電型不純物を導入することにより、第1導電型不純物を含む第2半導体層、第2導電型不純物を含む第3半導体層、および、第1導電型不純物を含む第4半導体層を形成する工程と、

前記第2半導体層、前記第3半導体層、および、前記第4半導体層中の所定領域に不純物を導入することにより、前記第2半導体層および前記第3半導体層にまたがるように設けられ、前記第3半導体層の不純物濃度よりも高い第1導電型の不純物濃度を含む第1ゲート電極層と、前記第3半導体層および前記第4半導体層にまたがるように設けられ、前記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ同電位を有する第1導電型の第2ゲート電極層と、前記第1ゲート電極層および前記第2ゲート電極層に挟まれた前記第3半導体層に、前記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ同電位を有する第1導電型の不純物注入領域とを形成する工程と、

前記第2半導体層、前記第3半導体層、および、前記第4半導体層の所定領域に不純物を導入することにより、前記第2半導体層、前記第3半導体層、および、前記第4半導体層が配置される方向に沿うとともに、前記1ゲート電極層、前記第2ゲート電極層および不純物注入領域を挟み込み、前記第3半導体層の不純物濃度よりも高い濃度の第2導電型の不純物を含むソース／ドレイン領域層を形成する工程と、

を備える横型接合型電界効果トランジスタの製造方法。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

この発明は、横型接合型電界効果トランジスタに関し、より特定的には、良好な耐圧性能を維持したままオン抵抗を低減可能とする横型接合型電界効果トランジスタの構造およびその製造方法に関する。

【0002】

【従来の技術】

横型接合型電界効果トランジスタ（以下、J F E T（Junction Field Effect Transistor）と称する）は、キャリアが通過するチャネル領域の側部に設けられたp-n接合に、ゲート電極から逆バイアス電圧を印加することにより、p-n接合からの空乏層をチャネル領域へ広げ、チャネル領域のコンダクタンスを制御してスイッチング等の動作を行う。このうち、横型J F E Tは、チャネル領域においてキャリアが素子表面に平行に移動するものを行う。

【0003】

チャネルのキャリアは電子（n型）でも正孔（p型）でもよいが、通常、半導体基板にSiCを用いるJ F E Tにおいては、チャネル領域をn型不純物領域とすることが多いため、以後の説明では便宜上、チャネルのキャリアは電子、したがってチャネル領域はn型不純物領域として話を進めるが、チャネル領域をp型不純物領域とする場合もあることは言うまでもない。

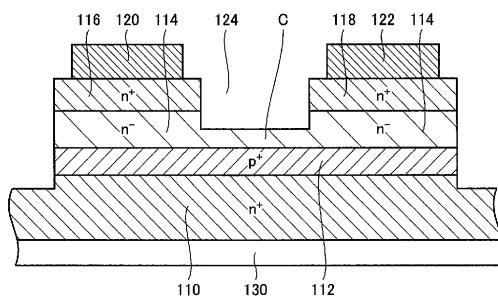

【0004】

図72は、従来の横型J F E Tを示す断面図である（米国特許登録番号5,264,713 Junction Field-Effect Transistor Formed in Silicon Carbide）。n型SiC基板110の上にp<sup>+</sup>型のエピタキシャル層112が配置され、その上にn-型のチャネル層114が形成されている。チャネル層114の上には、トレチ124をはさんで、一方にn<sup>+</sup>型のソース領域116が、また他方にはn<sup>+</sup>型のドレイン領域118が配置され、それぞれの上にソース電極120とドレイン電極122とが配置されている。SiC基板110の裏面側には、ゲートコンタクト層130が形成され、その上にゲート電極（図示せず）が設け

10

20

30

30

40

50

られている。ソース／ドレイン領域 116, 118 を通りチャネル層 114 の中にいたる深さを有するトレンチ 124 が設けられ、トレンチ 124 の底部と第 1 導電型のエピタキシャル層 112 との間の、第 2 導電型のエピタキシャル層 114 にはチャネル（C）が形成されている。

#### 【0005】

エピタキシャル層 112 における p 型不純物の濃度の値は、チャネルを含むエピタキシャル層 114 における n 型の濃度の値よりも高く、接合部への逆バイアス電圧の印加により空乏層がチャネルに向けて拡大する構成となっている。空乏層がチャネルを塞いだとき、電流がチャネルを通過することができないため、オフ状態となる。このため、逆バイアス電圧の大きさを加減することにより、空乏層がチャネル領域を遮断するか否か制御することが可能となる。この結果、たとえば、ゲート・ソース間の逆バイアス電圧を加減することにより、電流のオンオフ制御を行なうことが可能となる。

#### 【0006】

また、Theory of Semiconductor Superjunction Devices (Jpn.J.Appl.Phys.Vol.36(1997) Part.1, No.10. Oct. 1997 pp.6254-6262) には、MOS 型電界効果トランジスタのチャネル - ドレイン間を p 型半導体層と n 型半導体層とを交互に積み重ねた構造（重接合構造）として、オフ状態でのドレインへの電圧印加時の電圧分布を平行平板コンデンサに近づけることにより、素子耐圧の向上とオン抵抗の増加抑制 / 低下とを両立することが可能であることが理論的に述べられている。

#### 【0007】

【発明が解決しようとする課題】

しかしながら、上記構成からなる横型 JFET において、さらなる特性の向上の要求のひとつとして、オン抵抗の低下が挙げられる。特に、ノーマリオフ型タイプの横型 JFET においては、オン抵抗の低下が強く望まれている。

#### 【0008】

しかし、図 7.2 に示す構造において、オン抵抗の低下を期待して、p<sup>+</sup>型のエピタキシャル層 112 の最上部とゲートコンタクト層 130 の最下部との間隔を広げると、オフするのに必要なゲート電圧の絶対値が大きくなるため、その間隔の拡大には限界があり、オン抵抗の低下にも限界がある。

#### 【0009】

また、ノーマリオフ型とする場合、その間隔はチャネル層 114 とゲートコンタクト層 130 との接合における拡散電位で広がる空乏層の間隔よりも小さくする必要があるので、自ずとその間隔の拡大には限界があり、オン抵抗の低下にも限界が生じる。

#### 【0010】

したがって、この発明は、上記課題を解決するためになされたものであり、良好な耐圧性能を維持したままオン抵抗を低減可能とする構造を有する横型接合型電界効果トランジスタを提供することを目的とする。

#### 【0011】

#### 【課題を解決するための手段】

上記目的を達成するため、この発明に基づいた横型接合型電界効果トランジスタの 1 つの局面においては、半導体基板上に位置する第 1 導電型不純物を含む第 1 半導体層と、上記第 1 半導体層の上に位置し、上記第 1 半導体層の不純物濃度よりも高い濃度の第 2 導電型不純物を含む第 2 半導体層と、上記第 2 半導体層の上に位置し、第 1 導電型不純物を含む第 3 半導体層と、上記第 3 半導体層の上に位置し、第 2 導電型不純物を含む第 4 半導体層と、上記第 4 半導体層の上に位置し、第 1 導電型不純物を含む第 5 半導体層と、上記第 5 半導体層中において所定の間隔を隔てて、下面が上記第 2 半導体層にまで延在するように設けられ、上記第 2 半導体層および上記第 4 半導体層の不純物濃度よりも高い濃度の第 2 導電型の不純物を含むソース／ドレイン領域層と、上記第 3 半導体層中の上記ソース／ドレイン領域層の間ににおいて、下面が上記第 2 半導体層にまで延在するように設けられ、上記第 2 半導体層の不純物濃度よりも高い第 1 導電型の不純物濃度を含む第 1 ゲート電極層

10

20

30

40

50

と、上記第5半導体層中の上記ソース／ドレイン領域層の間ににおいて、下面が上記第4半導体層にまで延在するように設けられ、上記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ、同電位を有する第2ゲート電極層とを備える。

#### 【0012】

また、この発明に基づいた横型接合型電界効果トランジスタの製造方法の1つの局面においては、半導体基板上に、第1導電型不純物を含む第1半導体層を形成する工程と、上記第1半導体層の上に、上記第1半導体層の不純物濃度よりも高い濃度の第2導電型不純物を含む第2半導体層を形成する工程と、上記第2半導体層の上に、第1導電型不純物を含む第3半導体層を形成する工程と、上記第2半導体層と上記第3半導体層とにまたがるように、第3半導体層の所定領域に不純物を導入して、上記第2半導体層の不純物濃度よりも高い第1導電型の不純物濃度を含む第1ゲート電極層を形成する工程と、上記第3半導体層の上に、第2導電型不純物を含む第4半導体層を形成する工程と、上記第4半導体層の上に、第1導電型不純物を含む第5半導体層を形成する工程と、上記第5半導体層の所定領域に不純物を導入して、下面が上記第4半導体層にまで延在し、上記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ、同電位を有する第2ゲート電極層を形成する工程と、上記第1ゲート電極層および上記第2ゲート電極層の両側において、上記第5半導体層に不純物を導入して、下面が上記第2半導体層にまで延在し、上記第2半導体層および上記第4半導体層の不純物濃度よりも高い濃度の第2導電型の不純物を含むソース／ドレイン領域層を形成する工程とを備える。

#### 【0013】

上記構成からなる横型接合型電界効果トランジスタおよびその製造方法によれば、半導体基板上の各半導体層の積層方向である縦方向に沿ってトランジスタ構造を形成することになるため、従来の構造に対して、さらに素子のオン抵抗を下げることが可能になる。

#### 【0014】

上記発明において好ましくは、上記第2半導体層と、上記第3半導体層と、上記第4半導体層と、上記第5半導体層との不純物濃度と膜厚さとがほぼ同じである。この構成により、横型接合型電界効果トランジスタのオン抵抗を最小にし、耐圧値を最大に設定することが可能になる。

#### 【0015】

また、上記発明においてさらに好ましくは、上記第1半導体層の最上部と上記第1ゲート電極の最下部との間の間隔が、上記第2半導体層と上記第1ゲート電極層との接合における拡散電位で広がる空乏層の間隔よりも小さく、上記第3半導体層の最上部と上記第2ゲート電極層の最下部との間の間隔が、上記第4半導体層と上記第2ゲート電極層との接合における拡散電位で広がる空乏層の間隔よりも小さい。この構成により、ノーマリオフ型の横型接合型電界効果トランジスタを実現させることができる。

#### 【0016】

また、上記発明においてさらに好ましくは、上記第3半導体層と上記第4半導体層との間に、上記第2半導体層と上記第3半導体層と上記第1ゲート電極層とほぼ同じ構造である単位トランジスタ構造を1つまたは2以上備える。この構成により、横型接合型電界効果トランジスタ内に単位トランジスタを3以上積層させることができる。

#### 【0017】

上記目的を達成するため、この発明に基づいた横型接合型電界効果トランジスタの他の局面においては、半導体基板上に位置する第1導電型不純物を含む第1半導体層と、上記第1半導体層の上に位置し、上記第1半導体層の不純物濃度よりも高い濃度の第2導電型不純物を含む第2半導体層と、上記第2半導体層の上に位置し、第1導電型不純物を含む第3半導体層と、上記第3半導体層の上に位置し、第2導電型不純物を含む第4半導体層と、上記第4半導体層の上に位置し、第1導電型不純物を含む第5半導体層と、上記第5半導体層中において所定の間隔を隔てて、下面が上記第2半導体層にまで延在するように設けられ、上記第2半導体層および第4半導体層の不純物濃度よりも高い濃度の第2導電型の不純物を含むソース／ドレイン領域層と、上記第3半導体層中の上記ソース／ドレイン

10

20

30

40

50

領域層の間において、下面が上記第2半導体層にまで延在するように設けられ、上記第2半導体層の不純物濃度よりも高い第1導電型の不純物濃度を含む第1ゲート電極層と、上記第5半導体層中の上記ソース／ドレイン領域層の間において、下面が上記第4半導体層にまで延在するように設けられ、上記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ、同電位を有する第2ゲート電極層と、上記第1半導体層と上記第1ゲート電極層とに挟まれた上記第2半導体層に、上記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ、同電位を有する第1導電型の第1不純物注入領域と、上記第3半導体層と上記第2ゲート電極層とに挟まれた上記第4半導体層に、上記第1ゲート電極とほぼ同じ不純物濃度を有し、かつ、同電位を有する第1導電型の第2不純物注入領域とを備える。

## 【0018】

10

また、この発明に基づいた横型接合型電界効果トランジスタの製造方法の他の局面においては、半導体基板上に、第1導電型不純物を含む第1半導体層を形成する工程と、上記第1半導体層の上に、上記第1半導体層の不純物濃度よりも高い濃度の第2導電型不純物を含む第2半導体層を形成する工程と、上記第2半導体層の所定領域に不純物を導入して、上記第2半導体層内に第1導電型の第1不純物注入領域を形成する工程と、上記第2半導体層の上に、第1導電型不純物を含む第3半導体層を形成する工程と、上記第2半導体層と上記第3半導体層とにまたがるように不純物を導入して、上記第2半導体層の不純物濃度よりも高い第1導電型の不純物濃度を含む第1ゲート電極層を形成する工程と、上記第3半導体層の上に、第2導電型不純物を含む第4半導体層を形成する工程と、上記第4半導体層の所定領域に不純物を導入して、上記第4半導体層内に上記第1ゲート電極とほぼ同じ不純物濃度を有し、かつ、同電位を有する第1導電型の第2不純物注入領域を形成する工程と、上記第4半導体層の上に、第1導電型不純物を含む第5半導体層を形成する工程と、上記第5半導体層の所定領域に不純物を導入して、下面が上記第4半導体層にまで延在するように設けられ、上記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ、同電位を有する第2ゲート電極層を形成する工程と、上記第1ゲート電極層および上記第2ゲート電極層の両側において、上記第5半導体層の所定領域に不純物を導入して、下面が上記第2半導体層にまで延在するように設けられ、上記第2半導体層および第4半導体層の不純物濃度よりも高い濃度の第2導電型の不純物を含むソース／ドレイン領域層を形成する工程とを備える。

## 【0019】

20

上記構成からなる横型接合型電界効果トランジスタおよびその製造方法によれば、半導体基板上の各半導体層の積層方向である縦方向に沿ってトランジスタ構造を形成することになるため、従来の構造に対して、さらに素子のオン抵抗を下げることが可能になる。

## 【0020】

30

上記発明において好ましくは、上記第2半導体層と、上記第3半導体層と、上記第4半導体層と、上記第5半導体層との不純物濃度と膜厚さとがほぼ同じである。この構成により、横型接合型電界効果トランジスタのオン抵抗を最小にし、耐圧値を最大に設定することが可能になる。

## 【0021】

40

上記発明において好ましくは、上記第1半導体層の最上部と上記第1不純物注入領域の最下部との間の間隔が、上記第2半導体層と上記第1不純物注入領域との接合における拡散電位で広がる空乏層の間隔よりも小さく、上記第1不純物注入領域の最上部と上記第1ゲート電極層の最下部との間の間隔が、上記第2半導体層と上記第1ゲート電極層との接合における拡散電位で広がる空乏層の間隔の2倍よりも小さく、上記第3半導体層の最上部と上記第2不純物注入領域の最下部との間の間隔が、上記第4半導体層と上記第2不純物注入領域との接合における拡散電位で広がる空乏層の間隔よりも小さく、上記第2不純物注入領域の最上部と上記第2ゲート電極層の最下部との間の間隔が、上記第4半導体層と上記第2ゲート電極層との接合における拡散電位で広がる空乏層の間隔の2倍よりも小さい。この構成により、ノーマリオフ型の横型接合型電界効果トランジスタを実現させることができ可能になる。

50

**【0022】**

また、好ましくは、上記第2半導体層には、上記第1不純物注入領域が複数層設けられ、上記第4半導体層には、上記第2不純物注入領域が複数層設けられる。このように、不純物注入領域を複数層設けることにより、第2および第4半導体層を最大限に利用して、総チャネル幅を広くしオン抵抗を下げつつ、かつ、ノーマリオフ型の横型接合型トランジスタを実現させることが可能になる。

**【0023】**

上記発明において好ましくは、上記第3半導体層と上記第4半導体層との間に、上記第2半導体層と上記第3半導体層と上記第1ゲート電極層と上記第1不純物注入領域とほぼ同じ構造である単位トランジスタ構造を1つまたは2以上備える。この構成により、横型接合型電界効果トランジスタ内に単位トランジスタを3以上積層させることができることになる。

10

**【0024】**

上記目的を達成するため、この発明に基づいた横型接合型電界効果トランジスタの他の局面においては、半導体基板上に位置する第1導電型不純物を含む第1半導体層と、上記第1半導体層の上に位置し、上記第1半導体層の不純物濃度よりも高い濃度の第2導電型不純物を含む第2半導体層と、上記第2半導体層の上に位置し、第1導電型不純物を含む第3半導体層と、上記第3半導体層の上に位置し、第2導電型不純物を含む第4半導体層と、上記第4半導体層の上に位置し、第1導電型不純物を含む第5半導体層と、上記第5半導体層中において所定の間隔を隔てて、下面が上記第2半導体層にまで延在するように設けられ、上記第2半導体層および第4半導体層の不純物濃度よりも高い濃度の第2導電型の不純物を含むソース／ドレイン領域層と、上記第3半導体層中の上記ソース／ドレイン領域層の間において、下面が上記第2半導体層にまで延在し、上面が上記第4半導体層にまで延在するように設けられ、上記第2半導体層および上記第4半導体層の不純物濃度よりも高い第1導電型の不純物濃度を含む第1ゲート電極層と、上記第5半導体層中の上記ソース／ドレイン領域層の間において、下面が上記第4半導体層にまで延在するように設けられ、上記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ、同電位を有する第2ゲート電極層とを備える。

20

**【0025】**

また、この発明に基づいた横型接合型電界効果トランジスタの製造方法のさらに他の局面においては、半導体基板上に、第1導電型不純物を含む第1半導体層を形成する工程と、上記第1半導体層の上に、上記第1半導体層の不純物濃度よりも高い濃度の第2導電型不純物を含む第2半導体層を形成する工程と、上記第2半導体層の上に、第1導電型不純物を含む第3半導体層を形成する工程と、上記第3半導体層の上に、第2導電型不純物を含む第4半導体層を形成する工程と、上記第4半導体層の所定領域に不純物を導入し、下面が上記第2半導体層にまで延在し、上面が上記第4半導体層にまで延在し、上記第2半導体層および上記第4半導体層の不純物濃度よりも高い第1導電型の不純物濃度を含む第1ゲート電極層を形成する工程と、上記第4半導体層の上に、第1導電型不純物を含む第5半導体層を形成する工程と、上記第5半導体層の所定領域に不純物を導入し、下面が上記第4半導体層にまで延在するように設けられ、上記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ、同電位を有する第2ゲート電極層を形成する工程と、上記第1ゲート電極層および上記第2ゲート電極層の両側において、上記第5半導体層の所定領域に不純物を導入して、下面が上記第2半導体層にまで延在するように設けられ、上記第2半導体層および第4半導体層の不純物濃度よりも高い濃度の第2導電型の不純物を含むソース／ドレイン領域層とを備える。

30

**【0026】**

上記構成からなる横型接合型電界効果トランジスタおよびその製造方法によれば、半導体基板上の各半導体層の積層方向である縦方向に沿ってトランジスタ構造を形成することになるため、従来の構造に対して、さらに素子のオン抵抗を下げることが可能になる。

40

**【0027】**

上記発明において好ましくは、上記第2半導体層と上記第3半導体層と上記第4半導体層

50

と、上記第5半導体層との不純物濃度と膜厚さとがほぼ同じである。この構成により、横型接合型電界効果トランジスタのオン抵抗を最小にし、耐圧値を最大に設定することが可能になる。

**【0028】**

上記発明において好ましくは、上記第1半導体層の最上部と上記第1ゲート電極層の最下部との間の間隔が、上記第2半導体層と上記第1ゲート電極層との接合における拡散電位で広がる空乏層の間隔よりも小さく、上記第1ゲート電極層の最上部と上記第2ゲート電極層の最下部との間の間隔が、上記第4半導体層と上記第1ゲート電極層との接合における拡散電位で広がる空乏層の間隔の2倍よりも小さい。この構成により、ノーマリオフ型の横型接合型電界効果トランジスタを実現させることが可能になる。

10

**【0029】**

上記発明において好ましくは、上記第4半導体層と上記第5半導体層との間に、上記第3半導体層と上記第4半導体層と上記第1ゲート電極層とほぼ同じ構造である単位トランジスタ構造を1つまたは2以上備える。この構成により、横型接合型電界効果トランジスタ内に単位トランジスタを3以上積層させることができることになる。

**【0030】**

上記目的を達成するため、この発明に基づいた横型接合型電界効果トランジスタの他の局面においては、半導体基板上に位置する第1導電型不純物を含む第1半導体層と、上記第1半導体層の上に位置し、上記第1半導体層の不純物濃度よりも高い濃度の第2導電型不純物を含む第2半導体層と、上記第2半導体層の上に位置し、第1導電型不純物を含む第3半導体層と、上記第3半導体層の上に位置し、第2導電型不純物を含む第4半導体層と、上記第4半導体層の上に位置し、第1導電型不純物を含む第5半導体層と、上記第5半導体層中において所定の間隔を隔てて、下面が上記第2半導体層にまで延在するように設けられ、上記第2半導体層および第4半導体層の不純物濃度よりも高い濃度の第2導電型の不純物を含むソース／ドレイン領域層と、上記第3半導体層中の上記ソース／ドレイン領域層の間ににおいて、下面が上記第2半導体層にまで延在し、上面が上記第4半導体層にまで延在するように設けられ、上記第2半導体層および上記第4半導体層の不純物濃度よりも高い不純物濃度を含む第1ゲート電極層と、上記第5半導体層中の上記ソース／ドレイン領域の間ににおいて、下面が上記第4半導体層にまで延在するように設けられ、上記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ、同電位を有する第1導電型の第2ゲート電極層と、上記第1半導体層と上記第1ゲート電極層とに挟まれた上記第2半導体層に、上記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ、同電位を有する第1導電型の第1不純物注入領域と、上記第1ゲート電極層と上記第2ゲート電極層とに挟まれた上記第4半導体層に、上記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ同電位を有する第1導電型の第2不純物注入領域とを備える。

20

**【0031】**

また、この発明に基づいた横型接合型電界効果トランジスタの製造方法のさらに他の局面においては、半導体基板の上に、第1導電型不純物を含む第1半導体層を形成する工程と、上記第1半導体層の上に、上記第1半導体層の不純物濃度よりも高い濃度の第2導電型不純物を含む第2半導体層を形成する工程と、上記第2半導体層の上に、第1導電型不純物を含む第3半導体層を形成する工程と、上記第3半導体層の上に、第2導電型不純物を含む第4半導体層を形成する工程と、上記第4半導体層の所定領域に不純物を導入して、下面が上記第2半導体層にまで延在し、上面が上記第4半導体層にまで延在し、上記第2半導体層および上記第4半導体層の不純物濃度よりも高い不純物濃度を含む第1ゲート電極層を形成する工程と、上記第2半導体層の所定領域に不純物を導入して、上記第2半導体層内に第1導電型の第1不純物注入領域を形成する工程と、上記第4半導体層の上に、第1導電型不純物を含む第5半導体層を形成する工程と、上記第5半導体層の所定領域に不純物を導入して、下面が上記第4半導体層にまで延在するように設けられ、上記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ、同電位を有する第1導電型の第2ゲート電極層を形成する工程と、上記第4半導体層の所定領域に不純物を導入して、上記第4

30

40

50

半導体層内に、上記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ同電位を有する第1導電型の第2不純物注入領域を形成する工程と、上記第1ゲート電極層および上記第2ゲート電極層の両側において、下面が上記第2半導体層にまで延在するように設けられ、上記第2半導体層および第4半導体層の不純物濃度よりも高い濃度の第2導電型の不純物を含むソース／ドレイン領域層を形成する工程とを備える。

#### 【0032】

上記構成からなる横型接合型電界効果トランジスタおよびその製造方法によれば、半導体基板上の各半導体層の積層方向である縦方向に沿ってトランジスタ構造を形成することになるため、従来の構造に対して、さらに素子のオン抵抗を下げることが可能になる。

#### 【0033】

上記発明において好ましくは、上記第2半導体層と、上記第3半導体層と、上記第4半導体層と、上記第5半導体層との不純物濃度と膜厚さとがほぼ同じである。この構成により、横型接合型電界効果トランジスタのオン抵抗を最小にし、耐圧値を最大に設定することが可能になる。

#### 【0034】

また、上記発明においてさらに好ましくは、上記第1半導体層の最上部と上記第1不純物注入領域の最下部との間の間隔が、上記第2半導体層と上記第1不純物注入領域との接合における拡散電位で広がる空乏層の間隔よりも小さく、上記第1不純物注入領域の最上部と上記第1ゲート電極層の最下部との間隔が、上記第2半導体層と上記第1ゲート電極層との接合における拡散電位で広がる空乏層の間隔の2倍よりも小さく、上記第1ゲート電極層の最上部と上記第2不純物注入領域の最下部との間の間隔が、上記第4半導体層と上記第2不純物注入領域との接合における拡散電位で広がる空乏層の間隔の2倍よりも小さく、上記第2不純物注入領域の最上部と上記第2ゲート電極層の最下部との間の間隔が、上記第4半導体層と上記第2ゲート電極層との接合における拡散電位で広がる空乏層の間隔の2倍よりも小さい。この構成により、ノーマリオフ型の横型接合型電界効果トランジスタを実現させることが可能になる。

#### 【0035】

また、好ましくは、上記第2半導体層には、上記第1不純物注入領域が複数層設けられ、上記第4半導体層には、上記第2不純物注入領域が複数層設けられる。このように、不純物注入領域を複数層設けることにより、第2および第4半導体層を最大限に利用して、総チャネル幅を広くしオン抵抗を下げつつ、かつ、ノーマリオフ型の横型接合型トランジスタを実現させることができる。

#### 【0036】

また、上記発明においてさらに好ましくは、上記第4半導体層と上記第5半導体層との間に、上記第3半導体層と上記第4半導体層と上記第1ゲート電極層と上記第2不純物注入領域とほぼ同じ構造である単位トランジスタ構造を1つまたは2以上備える。この構成により、横型接合型電界効果トランジスタ内に単位トランジスタを3以上積層させることができることになる。

#### 【0037】

上記目的を達成するため、この発明に基づいた横型接合型電界効果トランジスタの他の局面においては、半導体基板上に位置する第1導電型不純物を含む第1半導体層と、上記第1半導体層の上に位置し、上記第1半導体層の不純物濃度よりも高い濃度の第2導電型不純物を含む第2半導体層と、上記第2半導体層の上に位置し、第1導電型不純物を含む第3半導体層と、上記第3半導体層の上に位置し、第2導電型不純物を含む第4半導体層と、上記第4半導体層の上に位置し、第1導電型不純物を含む第5半導体層と、上記第5半導体層中において所定の間隔を隔てて、下面が上記第2半導体層にまで延在するように設けられ、上記第2半導体層および第4半導体層の不純物濃度よりも高い濃度の第2導電型の不純物を含むソース／ドレイン領域層と、上記第5半導体層中の上記ソース／ドレイン領域層の間において、下面が上記第2半導体層にまで延在するように設けられ、上記第2半導体層の不純物濃度よりも高い第1導電型の不純物濃度を含む第1ゲート電極層と、上

10

20

30

40

50

記第5半導体層中の上記ソース／ドレイン領域層の間において、下面が上記第2半導体層にまで延在するように上記第1ゲート電極層に隣接して設けられ、上記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ、同電位を有する第1導電型の第2ゲート電極層とを備える。

#### 【0038】

また、この発明に基づいた横型接合型電界効果トランジスタの製造方法のさらに他の局面においては、半導体基板上に、第1導電型不純物を含む第1半導体層を形成する工程と、上記第1半導体層の上に、上記第1半導体層の不純物濃度よりも高い濃度の第2導電型不純物を含む第2半導体層を形成する工程と、上記第2半導体層の上に、第1導電型不純物を含む第3半導体層を形成する工程と、上記第3半導体層の上に、第2導電型不純物を含む第4半導体層を形成する工程と、上記第4半導体層の上に、第1導電型不純物を含む第5半導体層を形成する工程と、上記第5半導体層中の所定領域に不純物を導入することにより、下面が上記第2半導体層にまで延在するように設けられ、上記第2半導体層の不純物濃度よりも高い第1導電型の不純物濃度を含み、上記基板の平面方向に沿って互いに所定の間隔を隔てて配置される第1ゲート電極層および第2ゲート電極層を形成する工程と、上記第5半導体層中の所定領域に不純物を導入することにより、上記第1ゲート電極層および上記第2ゲート電極層の配置方向に沿って上記第1ゲート電極層および上記第2ゲート電極層を両側から挟みこみ、下面が上記第2半導体層にまで延在するように設けられ、上記第2半導体層および第4半導体層の不純物濃度よりも高い濃度の第2導電型の不純物を含むソース／ドレイン領域層を形成する工程とを備える。

10

20

#### 【0039】

上記構成からなる横型接合型電界効果トランジスタおよびその製造方法によれば、複数の横型J F E Tにおいてp n接合を縦方向に配置し、ゲート電極層を横方向に配置した構成が採用されているため、従来の構造に対して、さらに素子のオン抵抗を下げることが可能になる。

#### 【0040】

上記発明において好ましくは、上記第2半導体層と、上記第3半導体層と、上記第4半導体層と、上記第5半導体層との不純物濃度と膜厚さとがほぼ同じである。この構成により、横型接合型電界効果トランジスタのオン抵抗を最小にし、耐圧値を最大に設定することが可能になる。

30

#### 【0041】

また、上記発明においてさらに好ましくは、上記第1ゲート電極層と上記第2ゲート電極層との間の間隔が、上記第2半導体層と上記第1ゲート電極層との接合における拡散電位で広がる空乏層の間隔、および上記第4半導体層と上記第1ゲート電極層との接合における拡散電位で広がる空乏層の間隔の2倍よりも小さい。この構成により、ノーマリオフ型の横型接合型電界効果トランジスタを実現させることができる。

#### 【0042】

また、上記発明においてさらに好ましくは、上記第1ゲート電極層と上記第2ゲート電極層との間に、下面が上記第2半導体層にまで延在するように設けられ、上記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ、同電位を有する第1導電型の不純物注入領域を1つ備える。この構成によりチャネル数が増加し、さらにオン抵抗を下げることが可能になる。

40

#### 【0043】

また、上記発明においてさらに好ましくは、上記第1ゲート電極層と上記不純物注入領域との間の間隔および上記不純物注入領域と上記第2ゲート電極層との間隔が、上記第2半導体層と上記第1ゲート電極層との接合における拡散電位で広がる空乏層の間隔、および上記第4半導体層と上記第1ゲート電極層との接合における拡散電位で広がる空乏層の間隔の2倍よりも小さい。この構成により、ノーマリオフ型の横型接合型電界効果トランジスタを実現させることができる。

#### 【0044】

50

また、上記発明においてさらに好ましくは、上記不純物注入領域が2以上設けられる。この構成によりチャネル数が増加し、さらにオン抵抗を下げることが可能になる。

#### 【0045】

また、上記発明においてさらに好ましくは、上記第1ゲート電極層に最も近接する上記不純物注入領域と上記第1ゲート電極層との間の間隔、上記不純物注入領域同士の間隔、および上記第2ゲート電極層に最も近接する上記不純物注入領域と上記第2ゲート電極層との間の間隔が、いずれも、上記第2半導体層と上記第1ゲート電極層との接合における拡散電位で広がる空乏層の間隔、および上記第4半導体層と上記第1ゲート電極層との接合における拡散電位で広がる空乏層の間隔の2倍よりも小さい。この構成により、ノーマリオフ型の横型接合型電界効果トランジスタを実現させることが可能になる。

10

#### 【0046】

また、上記発明においてさらに好ましくは、上記第4半導体層と上記第5半導体層との間に、上記第3半導体層と上記第4半導体層とほぼ同じ構造を1つ以上有する。この構成により、半導体基板上において隣接する横方向に沿って配置されるトランジスタ構造の数が増加し、さらにオン抵抗を下げることが可能になる。

#### 【0047】

上記目的を達成するため、この発明に基づいた横型接合型電界効果トランジスタの他の局面においては、半導体基板上に位置する第1導電型不純物を含む第1半導体層と、上記第1半導体層の上に位置し、第1導電型不純物を含む第2半導体層と、上記第1半導体層の上に、かつ、上記第2半導体層に隣接して位置し、第2導電型不純物を含む第3半導体層と、上記第2半導体層および上記第3半導体層中において所定の間隔を隔てて設けられ、上記第3半導体層の不純物濃度よりも高い濃度の第2導電型の不純物を含むソース／ドレイン領域層と、上記第2半導体層中の上記ソース／ドレイン領域層の間において、その一方の側面が上記第3半導体層にまで延在するように設けられ、上記上記第1半導体層の不純物濃度よりも高い第1導電型の不純物濃度を含むゲート電極層とを備える。

20

#### 【0048】

また、この発明に基づいた横型接合型電界効果トランジスタの製造方法のさらに他の局面においては、半導体基板上に、第1導電型不純物を含む第1半導体層を形成する工程と、上記第1半導体層の上に、第2導電型不純物を含む半導体層を形成する工程と、上記半導体層中の所定領域に、上記基板の平面方向に沿って所定の間隔を隔てて第1導電型不純物を導入することにより、第1導電型不純物を含む第2半導体層と第2導電型不純物を含む第3半導体層とを形成する工程と、上記第2半導体層および上記第3半導体層中の所定領域に不純物を導入することにより、上記第2半導体層および上記第3半導体層にまたがるように設けられ、上記第1半導体層の不純物濃度よりも高い第1導電型の不純物濃度を含むゲート電極層を形成する工程と、

30

上記第2半導体層および上記第3半導体層の所定領域に不純物を導入することにより、上記第2半導体層および上記第3半導体層が配置される方向に沿うとともに、上記ゲート電極層を挟み込み、上記第3半導体層の不純物濃度よりも高い濃度の第2導電型の不純物を含むソース／ドレイン領域層を形成する工程とを備える。

40

#### 【0049】

上記構成からなる横型接合型電界効果トランジスタおよびその製造方法によれば、半導体基板上に設けられる各半導体層が、半導体基板上において隣接する横方向に沿って配置されることにより、基板の平面方向に沿ってトランジスタ構造を形成することになるため、従来の構造に対して、さらに素子のオン抵抗を下げることが可能になる。

#### 【0050】

上記発明において好ましくは、上記第2半導体層と、上記第3半導体層との不純物濃度と膜厚さとがほぼ同じである。この構成により、横型接合型電界効果トランジスタのオン抵抗を最小にし、耐圧値を最大に設定することが可能になる。

#### 【0051】

また、上記発明において好ましくは、上記ゲート電極層と、上記第3半導体層の上

50

記ゲート電極層と接しない面との間隔が、上記第3半導体層と上記ゲート電極層との接合における拡散電位で広がる空乏層の間隔よりも小さい。この構成により、ノーマリオフ型の横型接合型電界効果トランジスタを実現させることができる。

#### 【0052】

上記目的を達成するため、この発明に基づいた横型接合型電界効果トランジスタの他の局面においては、半導体基板上に位置する第1導電型不純物を含む第1半導体層と、上記第1半導体層の上に位置し、第1導電型不純物を含む第2半導体層と、上記第1半導体層の上に、かつ、上記第2半導体層に隣接して位置し、第2導電型不純物を含む第3半導体層と、上記第1半導体層の上に、かつ、上記第3半導体層に隣接して位置し、第1導電型不純物を含む第4半導体層と、上記第1半導体層の上に、かつ、上記第4半導体層に隣接して位置し、第2導電型不純物を含む第5半導体層と、上記第2半導体層、上記第3半導体層、上記第4半導体層および上記第5半導体層中において所定の間隔を隔てて設けられ、上記第3半導体層および上記第5半導体層の不純物濃度よりも高い濃度の第2導電型の不純物を含むソース／ドレイン領域層と、上記第2半導体層中の上記ソース／ドレイン領域層の間ににおいて、その一方の側面が上記第3半導体層にまで延在するように設けられ、上記第3半導体層の不純物濃度よりも高い第1導電型の不純物濃度を含む第1ゲート電極層と、上記第4半導体層中の上記ソース／ドレイン領域層の間ににおいて、その一方の側面が上記第5半導体層にまで延在するように設けられ、上記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ、同電位を有する第1導電型の第2ゲート電極層とを備える。10

#### 【0053】

上記構成からなる横型接合型電界効果トランジスタによれば、半導体基板上に設けられる各半導体層が、半導体基板上において隣接する横方向に沿って配置されることにより、基板の平面方向に沿ってトランジスタ構造を形成することになるため、従来の構造に対して、さらに素子のオン抵抗を下げることが可能になる。20

#### 【0054】

上記発明において好ましくは、上記第2半導体層と、上記第3半導体層と、上記第4半導体層と、上記第5半導体層との不純物濃度と膜厚さとがほぼ同じである。この構成により、横型接合型電界効果トランジスタのオン抵抗を最小にし、耐圧値を最大に設定することが可能になる。

#### 【0055】

また、上記発明においてさらに好ましくは、上記第1ゲート電極と、上記第3半導体層の上記第1ゲート電極層と接しない面との間の間隔が、上記第3半導体層と上記第1ゲート電極層との接合における拡散電位で広がる空乏層の間隔よりも小さく、上記第2ゲート電極層と上記第5半導体層の上記第2ゲート電極層と接しない面との間隔が、上記第5半導体層と上記第2ゲート電極層との接合における拡散電位で広がる空乏層の間隔よりも小さい。この構成により、ノーマリオフ型の横型接合型電界効果トランジスタを実現させることができ可能になる。30

#### 【0056】

また、上記発明においてさらに好ましくは、上記第3半導体層と上記第4半導体層との間に、上記第4半導体層と上記第5半導体層と上記第2ゲート電極層とほぼ同じ構造である単位トランジスタ構造を1つ以上備える。この構成により、横型接合型電界効果トランジスタ内に単位トランジスタを3以上設けることが可能になる。40

#### 【0057】

上記目的を達成するため、この発明に基づいた横型接合型電界効果トランジスタの他の局面においては、半導体基板上に位置する第1導電型不純物を含む第1半導体層と、上記第1半導体層の上に位置し、第1導電型不純物を含む第2半導体層と、上記第1半導体層の上に、かつ、上記第2半導体層に隣接して位置し、上記第2導電型不純物を含む第3半導体層と、上記第1半導体層の上に、かつ、上記第3半導体層に隣接して位置し、第1導電型不純物を含む第4半導体層と、上記第2半導体層、上記第3半導体層および上記第4半導体層中において所定の間隔を隔てて設けられ、上記第3半導体層の不純物濃度よりも高50

い濃度の第2導電型の不純物を含むソース／ドレイン領域層と、上記第2半導体層中の上記ソース／ドレイン領域層の間ににおいて、その一方の側面が上記第3半導体層にまで延在するように設けられ、上記第3半導体層の不純物濃度よりも高い第1導電型の不純物濃度を含むゲート電極層とを備える。

【0058】

上記構成からなる横型接合型電界効果トランジスタによれば、半導体基板上に設けられる各半導体層が、半導体基板上において隣接する横方向に沿って配置されることにより、基板の平面方向に沿ってトランジスタ構造を形成することになるため、従来の構造に対して、さらに素子のオン抵抗を下げることが可能になる。

【0059】

上記発明において好ましくは、上記第2半導体層と、上記第3半導体層と、上記第4半導体層との不純物濃度と膜厚さとがほぼ同じである。この構成により、横型接合型電界効果トランジスタのオン抵抗を最小にし、耐圧値を最大に設定することが可能になる。

【0060】

また、上記発明において好ましくは、上記ゲート電極層と上記第4半導体層との間の間隔が、上記第3半導体層と上記ゲート電極層との接合における拡散電位で広がる空乏層の間隔よりも小さい。この構成により、ノーマリオフ型の横型接合型電界効果トランジスタを実現させることができることになる。

【0061】

また、上記発明において好ましくは、上記第3半導体層と上記第4半導体層との間に上記第2半導体層と上記第3半導体層と上記ゲート電極層とほぼ同じ構造である単位トランジスタ構造を1つまたは2以上備える。この構成により、横型接合型電界効果トランジスタ内に単位トランジスタを3以上設けることが可能になる。

【0062】

上記目的を達成するため、この発明に基づいた横型接合型電界効果トランジスタの他の局面においては、半導体基板上に位置する第1導電型不純物を含む第1半導体層と、上記第1半導体層の上に位置し、第1導電型不純物を含む第2半導体層と、上記第1半導体層の上に、かつ、上記第2半導体層に隣接して位置し、第2導電型不純物を含む第3半導体層と、上記第2半導体層および上記第3半導体層中において所定の間隔を隔てて設けられ、上記第3半導体層の不純物濃度よりも高い濃度の第2導電型の不純物を含むソース／ドレイン領域層と、上記第2半導体層中の上記ソース／ドレイン領域層の間ににおいて、その一方の側面が上記第3半導体層にまで延在するように設けられ、上記第3半導体層の不純物濃度よりも高い第1導電型の不純物濃度を含むゲート電極層と、上記ゲート電極層と上記第3半導体層の上記ゲート電極層と接しない面とに挟まれた上記第3半導体層に、上記ゲート電極層とほぼ同じ不純物濃度を有し、かつ、同電位を有する第1導電型の不純物注入領域とを備える。

【0063】

また、この発明に基づいた横型接合型電界効果トランジスタの製造方法のさらに他の局面においては、半導体基板上に、第1導電型不純物を含む第1半導体層を形成する工程と、上記第1半導体層の上に、第2導電型不純物を含む半導体層を形成する工程と、上記半導体層中の所定領域に、上記基板の平面方向に沿って所定の間隔を隔てて第1導電型不純物を導入することにより、第1導電型不純物を含む第2半導体層と第2導電型不純物を含む第3半導体層とを形成する工程と、上記第2半導体層および上記第3半導体層中の所定領域に不純物を導入することにより、上記第2半導体層および上記第3半導体層にまたがるように設けられ、上記第3半導体層の不純物濃度よりも高い第1導電型の不純物濃度を含むゲート電極層と、上記第3半導体層の中に、上記ゲート電極層とほぼ同じ不純物濃度を有し、かつ、同電位を有する第1導電型の不純物注入領域とを形成する工程と、上記第2半導体層および上記第3半導体層の所定領域に不純物を導入することにより、上記第2半導体層および上記第3半導体層が配置される方向に沿うとともに、上記ゲート電極層および不純物注入領域を挟み込み、上記第3半導体層の不純物濃度よりも高い濃度の第2導電

10

20

30

40

50

型の不純物を含むソース／ドレイン領域層を形成する工程とを備える。

【0064】

上記構成からなる横型接合型電界効果トランジスタおよびその製造方法によれば、半導体基板上に設けられる各半導体層が、半導体基板上において隣接する横方向に沿って配置されることにより、基板の平面方向に沿ってトランジスタ構造を形成することになるため、従来の構造に対して、さらに素子のオン抵抗を下げることが可能になる。

【0065】

上記発明において好ましくは、上記第2半導体層と、上記第3半導体層との不純物濃度と膜厚さとがほぼ同じである。この構成により、横型接合型電界効果トランジスタのオン抵抗を最小にし、耐圧値を最大に設定することが可能になる。

10

【0066】

また、上記発明において好ましくは、上記ゲート電極層と上記不純物注入領域との最も大きく接する面同士の間隔が、上記第3半導体層と上記ゲート電極層との接合における拡散電位で広がる空乏層の間隔の2倍よりも小さく、上記不純物注入領域と、上記第3半導体層の上記ゲート電極層と接しない面との間の間隔が、上記第3半導体層と上記ゲート電極層との接合における拡散電位で広がる空乏層の間隔よりも小さい。この構成により、ノーマリオフ型の横型接合型電界効果トランジスタを実現させることが可能になる。

【0067】

また、好ましくは、上記第3半導体層には、上記不純物注入領域が複数層設けられる。このように、不純物注入領域を複数層設けることにより、総チャネル幅を広くしオン抵抗を下げつつ、かつ、ノーマリオフ型の横型接合型トランジスタを実現させることが可能になる。

20

【0068】

上記目的を達成するため、この発明に基づいた横型接合型電界効果トランジスタの他の局面においては、半導体基板上に位置する第1導電型不純物を含む第1半導体層と、上記第1半導体層の上に位置し、第1導電型不純物を含む第2半導体層と、上記第1半導体層の上に、かつ、上記第2半導体層に隣接して位置し、第2導電型不純物を含む第3半導体層と、上記第1半導体層の上に、かつ、上記第3半導体層に隣接して位置し、第1導電型不純物を含む第4半導体層と、上記第1半導体層の上に、かつ上記第4半導体層に隣接して位置し、第2導電型不純物を含む第5半導体層と、上記第2半導体層、上記第3半導体層、上記第4半導体層および上記第5半導体層中において所定の間隔を隔てて設けられ、上記第3半導体層および上記第5半導体層の不純物濃度よりも高い濃度の第2導電型の不純物を含むソース／ドレイン領域層と、上記第2半導体層中の上記ソース／ドレイン領域層の間において、その一方の側面が上記第3半導体層にまで延在するように設けられ、上記第3半導体層の不純物濃度よりも高い第1導電型の不純物濃度を含む第1ゲート電極層と、上記第4半導体層中の上記ソース／ドレイン領域層の間においてその一方の側面が上記第5半導体層にまで延在するように設けられ、上記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ同電位を有する第2ゲート電極層と、上記第4半導体層と上記第1ゲート電極層とに挟まれた上記第3半導体層に、上記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ同電位を有する第1導電型の第1不純物注入領域と、上記第2ゲート電極層と、上記第5半導体層の上記第2ゲート電極層と接しない面とに挟まれた上記第5半導体層に、上記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ、同電位を有する第1導電型の第2不純物注入領域とを備える。

30

【0069】

上記構成からなる横型接合型電界効果トランジスタによれば、半導体基板上に設けられる各半導体層が、半導体基板上において隣接する横方向に沿って配置されることにより、基板の平面方向に沿ってトランジスタ構造を形成することになるため、従来の構造に対して、さらに素子のオン抵抗を下げることが可能になる。

40

【0070】

上記発明において好ましくは、上記第2半導体層と、上記第3半導体層と、上記第4半導

50

体層と、上記第5半導体層との不純物濃度と膜厚さとがほぼ同じである。この構成により、横型接合型電界効果トランジスタのオン抵抗を最小にし、耐圧値を最大に設定することが可能になる。

#### 【0071】

また、上記発明においてさらに好ましくは、上記第1ゲート電極層と上記第1不純物注入領域との最も近接する面同士の間隔が、上記第3半導体層と上記第1ゲート電極層との接合における拡散電位で広がる空乏層の間隔の2倍よりも小さく、上記第1不純物注入領域と、上記第3半導体層の上記第1ゲート電極層と接しない面との間の間隔が、上記第3半導体層と上記第1ゲート電極層との接合における拡散電位で広がる空乏層の間隔よりも小さく、上記第2ゲート電極層と上記第2不純物注入領域との最も近接する面同士の間隔が、上記第5半導体層と上記第2ゲート電極層との接合における拡散電位で広がる空乏層の間隔の2倍よりも小さく、上記第2不純物注入領域と、上記第5半導体層の上記第2ゲート電極層と接しない面との間の間隔が、上記第5半導体層と上記第2ゲート電極層との接合における拡散電位で広がる空乏層の間隔よりも小さい。この構成により、ノーマリオフ型の横型接合型電界効果トランジスタを実現させることが可能になる。10

#### 【0072】

また、好ましくは、上記第3半導体層には、上記第1不純物注入領域が複数層設けられ、上記第5半導体層には、上記第2不純物注入領域が複数層設けられる。このように、不純物注入領域を複数層設けることにより、総チャネル幅を広くしオン抵抗を下げつつ、かつ、ノーマリオフ型の横型接合型トランジスタを実現させることが可能になる。20

#### 【0073】

また、上記発明においてさらに好ましくは、上記第3半導体層と上記第4半導体層との間に、上記第4半導体層と上記第5半導体層と上記第2ゲート電極層と上記第2不純物注入領域とほぼ同じ構造である単位トランジスタ構造を1つ以上備える。この構成により、横型接合型電界効果トランジスタ内に単位トランジスタを3以上設けることが可能になる。

#### 【0074】

上記目的を達成するため、この発明に基づいた横型接合型電界効果トランジスタの他の局面においては、半導体基板上に位置する第1導電型不純物を含む第1半導体層と、上記第1半導体層の上に位置し、第1導電型不純物を含む第2半導体層と、上記第1半導体層の上に、かつ、上記第2半導体層に隣接して位置し、第2導電型不純物を含む第3半導体層と、上記第1半導体層の上に、かつ、上記第3半導体層に隣接して位置し、第1導電型不純物を含む第4半導体層と、上記第2半導体層、上記第3半導体層および上記第4半導体層中において所定の間隔を隔てて設けられ、上記第3半導体層の不純物濃度よりも高い濃度の第2導電型の不純物を含むソース／ドレイン領域層と、上記第2半導体層中の上記ソース／ドレイン領域層の間ににおいて、その一方の側面が上記第3半導体層にまで延在するように設けられ、上記第3半導体層の不純物濃度よりも高い第1導電型の不純物濃度を含むゲート電極層と、上記第4半導体層と上記ゲート電極層とに挟まれた上記第3半導体層に、上記ゲート電極層とほぼ同じ不純物濃度を有し、かつ同電位を有する第1導電型の不純物注入領域とを備える。30

#### 【0075】

上記構成からなる横型接合型電界効果トランジスタによれば、半導体基板上に設けられる各半導体層が、半導体基板上において隣接する横方向に沿って配置されることにより、基板の平面方向に沿ってトランジスタ構造を形成することになるため、従来の構造に対して、さらに素子のオン抵抗を下げることが可能になる。40

#### 【0076】

上記発明において好ましくは、上記第2半導体層と、上記第3半導体層と、上記第4半導体層の不純物濃度と膜厚さとがほぼ同じである。この構成により、横型接合型電界効果トランジスタのオン抵抗を最小にし、耐圧値を最大に設定することが可能になる。

#### 【0077】

また、上記発明においてさらに好ましくは、上記ゲート電極層と上記不純物注入領域との50

間の間隔が、上記第3半導体層と上記ゲート電極層との接合における拡散電位で広がる空乏層の間隔の2倍よりも小さく、上記不純物注入領域と上記第4半導体層との間の間隔が、上記第3半導体層と上記ゲート電極層との接合における拡散電位で広がる空乏層の間隔よりも小さい。この構成により、ノーマリオフ型の横型接合型電界効果トランジスタを実現させることが可能になる。

#### 【0078】

また、好ましくは、上記第3半導体層には、上記不純物注入領域が複数層設けられる。このように、不純物注入領域を複数層設けることにより、総チャネル幅を広くしオン抵抗を下げつつ、かつ、ノーマリオフ型の横型接合型トランジスタを実現させることが可能になる。

10

#### 【0079】

また、上記発明においてさらに好ましくは、上記第3半導体層と上記第4半導体層との間に、上記第2半導体層と上記第3半導体層と上記ゲート電極層と上記不純物注入領域とほぼ同じ構造である単位トランジスタ構造を1つまたは2以上備える。この構成により、横型接合型電界効果トランジスタ内に単位トランジスタを3以上設けることが可能になる。

#### 【0080】

上記目的を達成するため、この発明に基づいた横型接合型電界効果トランジスタの他の局面においては、半導体基板上に位置する第1導電型不純物を含む第1半導体層と、上記第1半導体層の上に位置し、第1導電型不純物を含む第2半導体層と、上記第1半導体層の上に、かつ、上記第2半導体層に隣接して位置し、第2導電型不純物を含む第3半導体層と、上記第1半導体層の上に、かつ、上記第3半導体層に隣接して位置し、第1導電型不純物を含む第4半導体層と、上記第2半導体層、上記第3半導体層および上記第4半導体層中において所定の間隔を隔てて設けられ、上記第3半導体層の不純物濃度よりも高い濃度の第2導電型の不純物を含むソース／ドレイン領域層と、上記第2半導体層中の上記ソース／ドレイン領域層の間ににおいて、その一方の側面が上記第3半導体層にまで延在するように設けられ、上記第3半導体層の不純物濃度よりも高い第1導電型の不純物濃度を含む第1ゲート電極層と、上記第4半導体層中の上記ソース／ドレイン領域層の間ににおいて、その一方の側面が上記第3半導体層にまで延在するように設けられ、上記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ同電位を有する第1導電型の第2ゲート電極層とを備える。

20

#### 【0081】

また、この発明に基づいた横型接合型電界効果トランジスタの製造方法のさらに他の局面においては、半導体基板上に、第1導電型不純物を含む第1半導体層を形成する工程と、上記第1半導体層の上に、第2導電型不純物を含む半導体層を形成する工程と、上記半導体層中の所定領域に、上記基板の平面方向に沿って所定の間隔を隔てて第1導電型不純物を導入することにより、第1導電型不純物を含む第2半導体層、第2導電型不純物を含む第3半導体層、および、第1導電型不純物を含む第4半導体層を形成する工程と、上記第2半導体層、上記第3半導体層、および、上記第4半導体層中の所定領域に不純物を導入することにより、上記第2半導体層および上記第3半導体層にまたがるように設けられ、上記第3半導体層の不純物濃度よりも高い第1導電型の不純物濃度を含む第1ゲート電極層と、上記第3半導体層および上記第4半導体層にまたがるように設けられ、上記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ同電位を有する第1導電型の第2ゲート電極層とを形成する工程と、上記第2半導体層、上記第3半導体層、および、上記第4半導体層の所定領域に不純物を導入することにより、上記第2半導体層、上記第3半導体層、および、上記第4半導体層、および、上記第4半導体層が配置される方向に沿うとともに、上記1ゲート電極層および上記第2ゲート電極層を挟み込み、上記第3半導体層の不純物濃度よりも高い濃度の第2導電型の不純物を含むソース／ドレイン領域層を形成する工程とを備える。

30

#### 【0082】

上記構成からなる横型接合型電界効果トランジスタおよびその製造方法によれば、半導体基板上に設けられる各半導体層が、半導体基板上において隣接する横方向に沿って配置さ

40

50

れることにより、基板の平面方向に沿ってトランジスタ構造を形成することになるため、従来の構造に対して、さらに素子のオン抵抗を下げることが可能になる。

#### 【0083】

上記発明において好ましくは、上記第2半導体層と、上記第3半導体層と、上記第4半導体層との不純物濃度と膜厚さとがほぼ同じである。この構成により、横型接合型電界効果トランジスタのオン抵抗を最小にし、耐圧値を最大に設定することが可能になる。

#### 【0084】

また、上記発明においてさらに好ましくは、上記第1ゲート電極層と、上記第2ゲート電極層の最も近接する面同士の間隔が、上記第3半導体層と上記第1ゲート電極層との接合における拡散電位で広がる空乏層の間隔の2倍よりも小さく、この構成により、ノーマリオフ型の横型接合型電界効果トランジスタを実現させることが可能になる。10

#### 【0085】

上記目的を達成するため、この発明に基づいた横型接合型電界効果トランジスタの他の局面においては、半導体基板上に位置する第1導電型不純物を含む第1半導体層と、上記第1半導体層の上に位置し、第1導電型不純物を含む第2半導体層と、上記第1半導体層の上に、かつ、上記第2半導体層に隣接して位置し、第2導電型不純物を含む第3半導体層と、上記第1半導体層の上に、かつ上記第3半導体層に隣接して位置し、第1導電型不純物を含む第4半導体層と、上記第1半導体層の上に、かつ上記第4半導体層に隣接して位置し、第2導電型不純物を含む第5半導体層と、上記第1半導体層の上に、かつ、上記第5半導体層に隣接して位置し、第1導電型不純物を含む第6半導体層と、上記第2半導体層、上記第3半導体層、上記第4半導体層、上記第5半導体層および上記第6半導体層中において所定の間隔を隔てて設けられ、上記第3半導体層および上記第5半導体層の不純物濃度よりも高い濃度の第2導電型の不純物を含むソース／ドレイン領域層と、上記第2半導体層中の上記ソース／ドレイン領域層の間ににおいて、その一方の側面が上記第3半導体層にまで延在するように設けられ、上記第3半導体層の不純物濃度よりも高い第1導電型の不純物濃度を含む第1ゲート電極層と、上記第4半導体層中の上記ソース／ドレイン領域層の間ににおいてその一方の側面が上記第3半導体層にまで延在し、他方の側面が上記第5半導体層にまで延在するように設けられ、上記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ同電位を有する第1導電型の第2ゲート電極層と、上記第6半導体層の上記ソース／ドレイン領域層の間ににおいてその一方の側面が上記第5半導体層にまで延在するように設けられ、上記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ、同電位を有する第1導電型の第3ゲート電極層とを備える。20

#### 【0086】

上記構成からなる横型接合型電界効果トランジスタによれば、半導体基板上に設けられる各半導体層が、半導体基板上において隣接する横方向に沿って配置されることにより、基板の平面方向に沿ってトランジスタ構造を形成することになるため、従来の構造に対して、さらに素子のオン抵抗を下げることが可能になる。30

#### 【0087】

上記発明において好ましくは、上記第2半導体層と、上記第3半導体層と、上記第4半導体層と、上記第5半導体層と、上記第6半導体層との不純物濃度と膜厚さとがほぼ同じである。この構成により、横型接合型電界効果トランジスタのオン抵抗を最小にし、耐圧値を最大に設定することが可能になる。40

#### 【0088】

また、上記発明においてさらに好ましくは、上記第1ゲート電極層と、上記第2ゲート電極層の最も近接する面同士の間隔が、上記第3半導体層と上記第1ゲート電極層との接合における拡散電位で広がる空乏層の間隔の2倍よりも小さく、上記第2ゲート電極層と上記第3ゲート電極層の最も近接する面同士の間隔が、上記第3半導体層と上記第1ゲート電極層との接合における拡散電位で広がる空乏層の間隔の2倍よりも小さい。この構成により、ノーマリオフ型の横型接合型電界効果トランジスタを実現させることができることになる。50

**【0089】**

また、上記発明においてさらに好ましくは、上記第5半導体層と上記第6半導体層との間に、上記第4半導体層と上記5半導体層と上記第2ゲート電極層とほぼ同じ構造である単位トランジスタ構造を1つ以上備える。この構成により、横型接合型電界効果トランジスタ内に単位トランジスタを3以上設けることが可能になる。

**【0090】**

上記目的を達成するため、この発明に基づいた横型接合型電界効果トランジスタの他の局面においては、半導体基板上に位置する第1導電型不純物を含む第1半導体層と、上記第1半導体層上に位置し、第1導電型不純物を含む第2半導体層と、上記第1半導体層の上に、かつ、上記第2半導体層に隣接して位置し、第2導電型不純物を含む第3半導体層と、上記第1半導体層の上に、かつ、上記第3半導体層に隣接して位置し、第1導電型不純物を含む第4半導体層と、上記第2半導体層、上記第3半導体層および上記第4半導体層中において所定の間隔を隔てて設けられ、上記第3半導体層の不純物濃度よりも高い濃度の第2導電型の不純物を含むソース／ドレイン領域層と、上記第2半導体層中の上記ソース／ドレイン領域層の間において、その一方の側面が上記第3半導体層にまで延在するように設けられ、上記第3半導体層の不純物濃度よりも高い第1導電型の不純物濃度を含む第1ゲート電極層と、上記第4半導体層中の上記ソース／ドレイン領域層の間において、その一方の側面が上記第3半導体層にまで延在するように設けられ、上記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ同電位を有する第2ゲート電極層と、上記第1ゲート電極層と上記第2ゲート電極層とに挟まれた上記第3半導体層に、上記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ同電位を有する第1導電型の不純物注入領域とを備える。

10

20

**【0091】**

また、この発明に基づいた横型接合型電界効果トランジスタの製造方法のさらに他の局面においては、半導体基板上に、第1導電型不純物を含む第1半導体層を形成すると、上記第1半導体層の上に、第2導電型不純物を含む半導体層を形成する工程と、上記半導体層中の所定領域に、上記基板の平面方向に沿って所定の間隔を隔てて第1導電型不純物を導入することにより、第1導電型不純物を含む第2半導体層、第2導電型不純物を含む第3半導体層、および、第1導電型不純物を含む第4半導体層を形成する工程と、上記第2半導体層、上記第3半導体層、および、上記第4半導体層中の所定領域に不純物を導入することにより、上記第2半導体層および上記第3半導体層にまたがるように設けられ、上記第3半導体層の不純物濃度よりも高い第1導電型の不純物濃度を含む第1ゲート電極層と、上記第3半導体層および上記第4半導体層にまたがるように設けられ、上記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ同電位を有する第1導電型の第2ゲート電極層と、上記第1ゲート電極層および上記第2ゲート電極層に挟まれた上記第3半導体層に、上記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ同電位を有する第1導電型の不純物注入領域とを形成する工程と、上記第2半導体層、上記第3半導体層、および、上記第4半導体層の所定領域に不純物を導入することにより、上記第2半導体層、上記第3半導体層、上記第3半導体層、および、上記第4半導体層が配置される方向に沿うとともに、上記1ゲート電極層、上記第2ゲート電極層および不純物注入領域を挟み込み、上記第3半導体層の不純物濃度よりも高い濃度の第2導電型の不純物を含むソース／ドレイン領域層を形成する工程とを備える。

30

40

**【0092】**

上記構成からなる横型接合型電界効果トランジスタおよびその製造方法によれば、半導体基板上に設けられる各半導体層が、半導体基板上において隣接する横方向に沿って配置されることにより、基板の平面方向に沿ってトランジスタ構造を形成することになるため、従来の構造に対して、さらに素子のオン抵抗を下げることが可能になる。

**【0093】**

上記発明において好ましくは、上記第2半導体層と上記第3半導体層と上記第4半導体層との不純物濃度と膜厚さとがほぼ同じである。この構成により、横型接合型電界効果トランジ

50

ンジスタのオン抵抗を最小にし、耐圧値を最大に設定することが可能になる。

**【0094】**

また、上記発明においてさらに好ましくは、上記第1ゲート電極層と、上記不純物注入領域の最も近接する面同士の間隔が、上記第3半導体層と上記第1ゲート電極層との接合における拡散電位で広がる空乏層の間隔の2倍よりも小さく、上記不純物注入領域と、上記第2ゲート電極の最も近接する面同士の間隔が、上記第3半導体層と上記第1ゲート電極層との接合における拡散電位で広がる空乏層の間隔の2倍よりも小さい。この構成により、ノーマリオフ型の横型接合型電界効果トランジスタを実現させることが可能になる。

**【0095】**

また、好ましくは、上記第3半導体層には、上記不純物注入領域が複数層設けられる。このように、不純物注入領域を複数層設けることにより、総チャネル幅を広くしオン抵抗を下げつつ、かつ、ノーマリオフ型の横型接合型トランジスタを実現させることが可能になる。

**【0096】**

上記目的を達成するため、この発明に基づいた横型接合型電界効果トランジスタの他の局面においては、半導体基板上に位置する第1導電型不純物を含む第1半導体層と、上記第1半導体層の上に位置し、第1導電型不純物を含む第2半導体層と、上記第1半導体層の上に、かつ、上記第2半導体層に隣接して位置し、第2導電型不純物を含む第3半導体層と、上記第1半導体層の上にかつ上記第3半導体層に隣接して位置し、第1導電型不純物を含む第4半導体層と、上記第1半導体層の上に、かつ、上記第4半導体層に隣接して位置し、第2導電型不純物を含む第5半導体層と、上記第1半導体層の上に、かつ、上記第5半導体層に隣接して位置し、第1導電型不純物を含む第6半導体層と、上記第2半導体層、上記第3半導体層、上記第4半導体層、上記第5半導体層および上記第6半導体層中において所定の間隔を隔てて設けられ、上記第3半導体層および上記第5半導体層の不純物濃度よりも高い濃度の第2導電型の不純物を含むソース／ドレイン領域層と、上記第2半導体層中の上記ソース／ドレイン領域層の間において、その一方の側面が上記第3半導体層にまで延在するように設けられ、上記第3半導体層の不純物濃度よりも高い第1導電型の不純物濃度を含む第1ゲート電極層と、上記第4半導体層中の上記ソース／ドレイン領域層の間において、その一方の側面が上記第3半導体層にまで延在し、他方の側面が上記第5半導体層にまで延在するように設けられ、上記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ同電位を有する第1導電型の第2ゲート電極層と、上記第6半導体層中の上記ソース／ドレイン領域層の間において、その一方の側面が上記第5半導体層にまで延在するように設けられ、上記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ、同電位を有する第1導電型の第3ゲート電極層と、上記第1ゲート電極層と上記第2ゲート電極層とに挟まれた上記第3半導体層に、上記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ、同電位を有する第1導電型の第1不純物注入領域と、上記第2ゲート電極と上記第3ゲート電極層とに挟まれた上記第5半導体層に、上記第1ゲート電極層とほぼ同じ不純物濃度を有し、かつ同電位を有する第1導電型の第2不純物注入領域とを備える。

**【0097】**

上記構成からなる横型接合型電界効果トランジスタによれば、半導体基板上に設けられる各半導体層が、半導体基板上において隣接する横方向に沿って配置されることにより、基板の平面方向に沿ってトランジスタ構造を形成することになるため、従来の構造に対して、さらに素子のオン抵抗を下げることが可能になる。

**【0098】**

上記発明において好ましくは、上記第2半導体層と、上記第3半導体層と、上記第4半導体層と、上記第5半導体層と、上記第6半導体層との不純物濃度と膜厚さとがほぼ同じである。この構成により、横型接合型電界効果トランジスタのオン抵抗を最小にし、耐圧値を最大に設定することが可能になる。

**【0099】**

また、上記発明においてさらに好ましくは、上記第1ゲート電極層と、上記第1不純物注

10

20

30

40

50

入領域の最も近接する面同士の間隔が、上記第3半導体層と上記第1ゲート電極層との接合における拡散電位で広がる空乏層の間隔の2倍よりも小さく、上記第1不純物注入領域と、上記第2ゲート電極層の最も近接する面同士の間隔が、上記第3半導体層と上記第1ゲート電極層との接合における拡散電位で広がる空乏層の間隔の2倍よりも小さく、上記第2ゲート電極層と、上記第2不純物注入領域の最も近接する面同士の間隔が、上記第3半導体層と上記第1ゲート電極層との接合における拡散電位で広がる空乏層の間隔の2倍よりも小さく、上記第2不純物注入領域と、上記第3ゲート電極層の最も近接する面同士の間隔が、上記第3半導体層と上記第1ゲート電極層との接合における拡散電位で広がる空乏層の間隔の2倍よりも小さい。この構成により、ノーマリオフ型の横型接合型電界効果トランジスタを実現させることができる。

10

## 【0100】

また、好ましくは、上記第3半導体層には、上記第1不純物注入領域が複数層設けられる、上記第5半導体層には、上記第2不純物注入領域が複数層設けられる。このように、不純物注入領域を複数層設けることにより、第2および第4半導体層を最大限に利用して、総チャネル幅を広くしオン抵抗を下げつつ、かつ、ノーマリオフ型の横型接合型トランジスタを実現させることができる。

## 【0101】

また、上記発明においてさらに好ましくは、上記第5半導体層と上記第6半導体層との間に、上記第4半導体層と上記第5半導体層と上記第2ゲート電極層と上記第2不純物注入領域とほぼ同じ構造である単位トランジスタ構造を1つ以上備える。この構成により、横型接合型電界効果トランジスタ内に単位トランジスタを3以上設けることが可能になる。

20

## 【0102】

## 【発明の実施の形態】

以下、本発明に基づいた各実施の形態における横型接合型電界効果トランジスタの構造およびその製造方法について、図を参照しながら説明する。

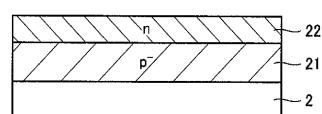

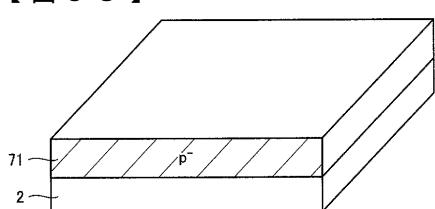

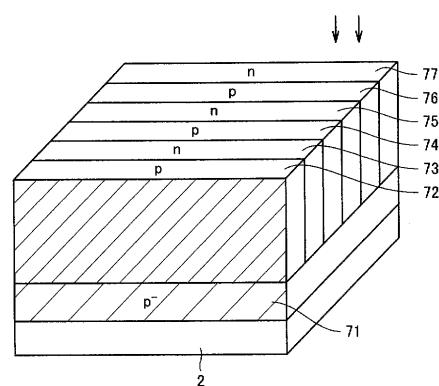

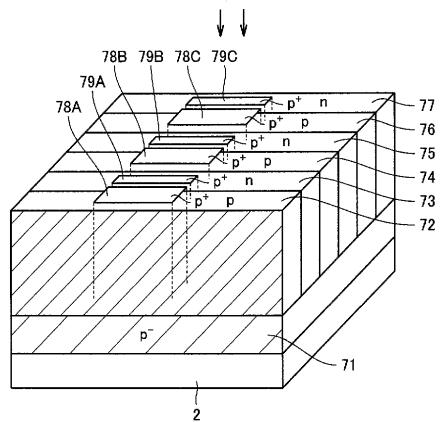

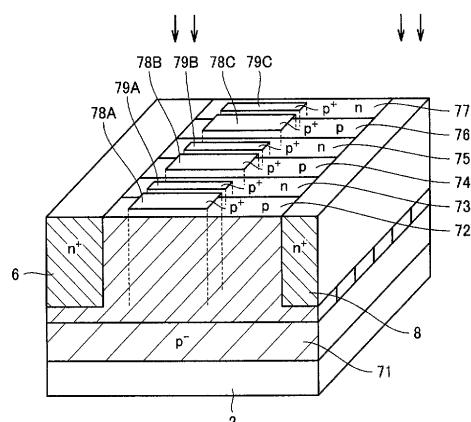

## 【0103】

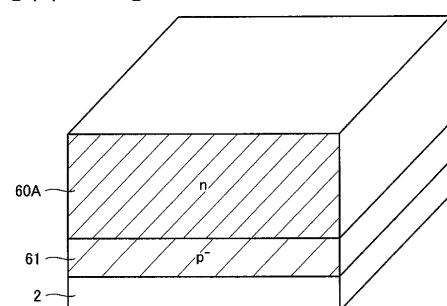

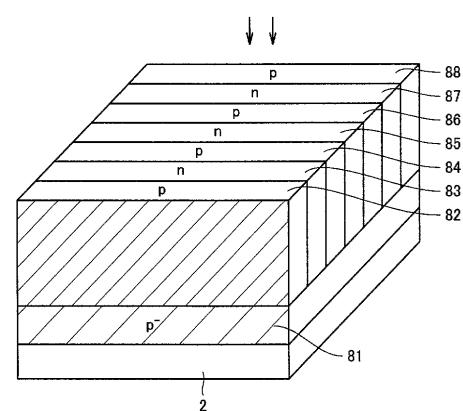

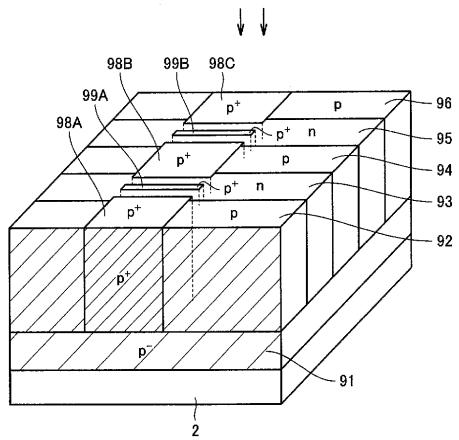

## (実施の形態1)

## (横型接合型電界効果トランジスタ100の構造)

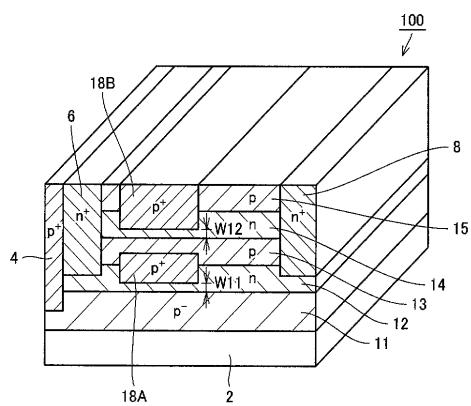

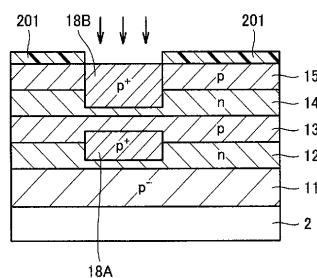

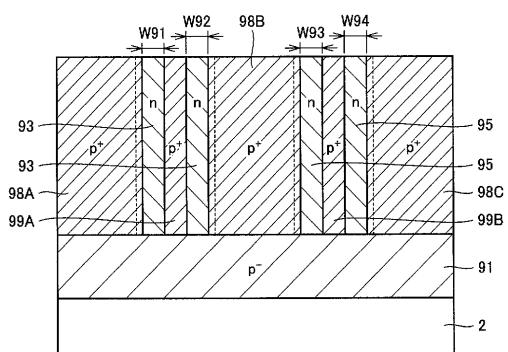

以下、実施の形態1における横型接合型電界効果トランジスタ100の構造について、図1を参照して説明する。なお、図1は本実施の形態における横型接合型電界効果トランジスタ100の構造を示す断面図である。

30

## 【0104】

本実施の形態における横型接合型電界効果トランジスタ100の構造的特徴は、pn接合およびゲート電極層を縦方向に配置するようにしたものである。ここで、本明細書中において、縦方向とは基板の深さ方向に沿った方向を意味し、横方向とは基板の主面に並行な方向を意味する。

## 【0105】

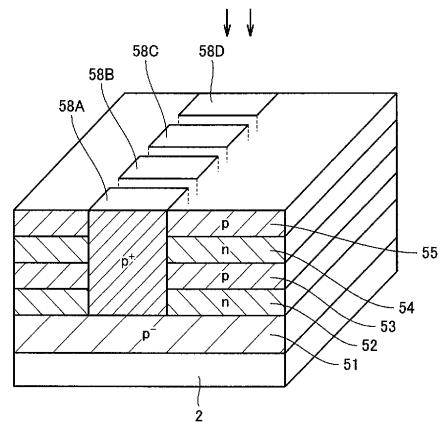

この横型接合型電界効果トランジスタ100は、Si等からなる半導体基板2の上に位置するp型不純物を含む第1半導体層11と、この第1半導体層11の上に、第1半導体層11の不純物濃度よりも高い濃度のn型不純物を含む第2半導体層12と、この第2半導体層12の上に位置し、p型不純物を含む第3半導体層13、この第3半導体層13の上に位置し、n型不純物を含む第4半導体層14と、この第4半導体層14の上に位置し、p型不純物を含む第5半導体層15とが設けられている。

40

## 【0106】

ここで、第1半導体層11の材質はSiC、膜厚は $3\text{ }\mu\text{m} \sim 4\text{ }\mu\text{m}$ 程度、不純物濃度は $1 \times 10^{16}\text{ cm}^{-3}$ 程度に設けられ、第2半導体層12、第3半導体層13、第4半導体層14、および、第5半導体層15の材質はSiC、膜厚は $0.5\text{ }\mu\text{m} \sim 1.0\text{ }\mu\text{m}$ 程度、不純物濃度は $1 \times 10^{17}\text{ cm}^{-3} \sim 3 \times 10^{17}\text{ cm}^{-3}$ 程度に設けられる。

## 【0107】

第5半導体層15の中において所定の間隔を隔てて、下面が第2半導体層12にまで延在

50

するように設けられ、第2半導体層12および第4半導体層14の不純物濃度よりも高い濃度のn型の不純物を含むソース／ドレイン領域層6，8が設けられる。ソース／ドレイン領域層6，8の不純物濃度は $1 \times 10^{19} \text{ cm}^{-3}$ ～ $1 \times 10^{20} \text{ cm}^{-3}$ 程度に設けられる。

#### 【0108】

第3半導体層13中のソース／ドレイン領域層6，8の間には、第2半導体層12および第3半導体層13にまたがるように、下面が第2半導体層12にまで延在するように設けられ、第2半導体層12の不純物濃度よりも高いp型の不純物濃度を含む第1ゲート電極層18Aが設けられている。

#### 【0109】

第5半導体層15中のソース／ドレイン領域層6，8の間には、下面が第4半導体層14にまで延在するように設けられ、第1ゲート電極層18Aとほぼ同じ不純物濃度を有し、かつ、同電位を有するp型の不純物を含む第2ゲート電極層18Bが設けられている。第1ゲート電極層18Aおよび第2ゲート電極層18Bの不純物濃度は $3 \times 10^{18} \text{ cm}^{-3}$ ～ $1 \times 10^{20} \text{ cm}^{-3}$ 程度に設けられる。

#### 【0110】

なお、ソース領域層6の外側には、第1半導体層11にまで延在するp型の不純物濃度を含む不純物領域層4が設けられている。この不純物領域層4の不純物濃度は $3 \times 10^{18} \text{ cm}^{-3}$ ～ $1 \times 10^{20} \text{ cm}^{-3}$ 程度に設けられる。

#### 【0111】

なお、ノーマリオフ型の横型接合型電界効果トランジスタを実現させるためには、第1半導体層11の最上部と第1ゲート電極18Aの最下部との間の間隔(w11)が、第2半導体層12と1ゲート電極層18Aとの接合における拡散電位で広がる空乏層の間隔よりも小さくなるように設け、第3半導体層13の最上部と上記第2ゲート電極層18Bの最下部との間の間隔w12が、第4半導体層14と第2ゲート電極層18Bとの接合における拡散電位で広がる空乏層の間隔よりも小さくなるように設ければ良い。

#### 【0112】

(横型接合型電界効果トランジスタ100の製造方法)

次に、上記構成からなる横型接合型電界効果トランジスタ100の製造方法について、図2～図7を参照して説明する。なお、図2～図7は図1に示す断面構造にしたがった製造工程を示す断面図である。

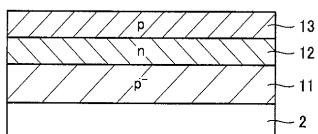

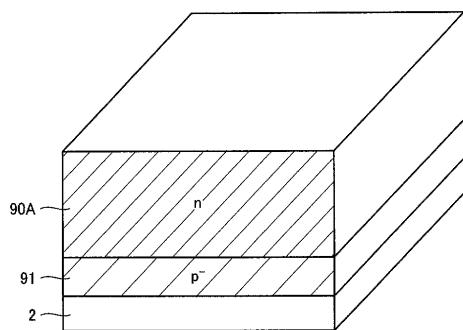

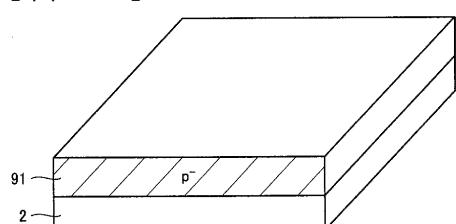

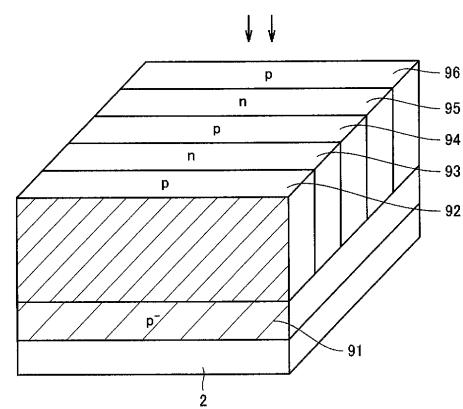

#### 【0113】

図2を参照して、Si等からなる半導体基板2上に、p型不純物を含む厚さ $3 \mu\text{m}$ ～ $4 \mu\text{m}$ 程度、不純物濃度が $1 \times 10^{16} \text{ cm}^{-3}$ 程度のSiCからなる第1半導体層11をエピタキシャル成長により形成する。その後、この第1半導体層11の上に、n型不純物を含む厚さ約 $0.5 \mu\text{m}$ 程度、不純物濃度が第1半導体層11よりも高い約 $3 \times 10^{17} \text{ cm}^{-3}$ 程度のSiCからなる第2半導体層12をエピタキシャル成長により形成する。その後、第2半導体層12の上に、p型不純物を含む厚さ約 $0.5 \mu\text{m}$ 程度、不純物濃度が約 $3 \times 10^{17} \text{ cm}^{-3}$ 程度のSiCからなる第3半導体層13をエピタキシャル成長により形成する。

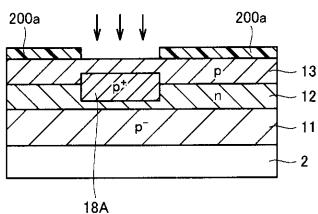

#### 【0114】

次に、図3を参照して、第3半導体層13の上に、所定の開口パターンを有する酸化膜200aを形成し、この酸化膜200aをマスクにして、p型の不純物を第3半導体層13に導入して、第2半導体層12と第3半導体層13とにまたがる領域に、第2半導体層12の不純物濃度よりも高い $3 \times 10^{18} \text{ cm}^{-3}$ ～ $1 \times 10^{20} \text{ cm}^{-3}$ 程度のp型不純物を含む第1ゲート電極層18Aを形成する。なお、この時の、p型の不純物の注入は、注入エネルギー約700keV、注入量約 $3 \times 10^{14} \text{ cm}^{-2}$ 、および、注入エネルギー約500keV、注入量約 $3 \times 10^{14} \text{ cm}^{-2}$ の2段階に分けて行なう。

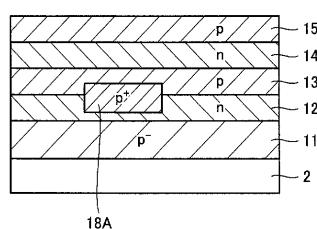

#### 【0115】

次に、図4を参照して、酸化膜200aを除去した後、第3半導体層13の上に、n型不純物を含む厚さ $0.5 \mu\text{m}$ 程度、不純物濃度が約 $3 \times 10^{17} \text{ cm}^{-3}$ 程度のSiCからな

10

20

30

40

50

る第4半導体層14をエピタキシャル成長により形成する。その後、この第4半導体層14の上に、p型不純物を含む厚さ約0.5μm程度、不純物濃度が約 $3 \times 10^{17} \text{ cm}^{-3}$ 程度のSiCからなる第5半導体層15を形成する。

#### 【0116】

次に、図5を参照して、第5半導体層15の上に、所定の開口パターンを有する酸化膜201を形成し、この酸化膜201をマスクにして、p型の不純物を第5半導体層15に導入して、下面が第4半導体層14にまで延在し、第1ゲート電極層18Aとほぼ同じ $3 \times 10^{18} \text{ cm}^{-3} \sim 1 \times 10^{20} \text{ cm}^{-3}$ 程度のp型不純物を含み、かつ、同電位を有する第2ゲート電極層18Bを形成する。なお、この時の、p型の不純物の注入は、第1段階が注入エネルギー約700keV、注入量約 $3 \times 10^{14} \text{ cm}^{-2}$ 、第2段階が注入エネルギー約500keV、注入量約 $3 \times 10^{14} \text{ cm}^{-2}$ 、第3段階が注入エネルギー約280keV、注入量約 $5 \times 10^{14} \text{ cm}^{-2}$ 、第4段階が注入エネルギー約140keV、注入量約 $5 \times 10^{14} \text{ cm}^{-2}$ 、第5段階が注入エネルギー約70keV、注入量約 $4 \times 10^{14} \text{ cm}^{-2}$ 、第6段階が注入エネルギー約30keV、注入量約 $3 \times 10^{14} \text{ cm}^{-2}$ の第6段階に分けて行なう。

10

#### 【0117】

次に、図6を参照して、酸化膜201を除去した後、再び、第5半導体層15の上に、所定の開口パターンを有する酸化膜202を形成し、この酸化膜202をマスクにして、第1ゲート電極層18Aおよび第2ゲート電極層18Bの両側において、第5半導体層15に不純物を導入して、下面が第2半導体層12にまで延在し、第2半導体層12および前記第4半導体層14の不純物濃度よりも高い $1 \times 10^{19} \text{ cm}^{-3} \sim 1 \times 10^{20} \text{ cm}^{-3}$ 程度のn型の不純物を含むソース／ドレイン領域層6，8を形成する。

20

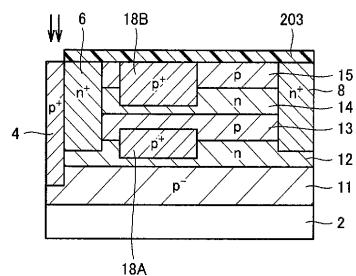

#### 【0118】

次に、図7を参照して、酸化膜202を除去した後、再び、第5半導体層15の上に、所定の開口パターンを有する酸化膜203を形成し、この酸化膜202をマスクにして、ソース／ドレイン領域層6の外側の領域において、第5半導体層15に不純物を導入して、下面が第1半導体層11にまで延在し、 $3 \times 10^{18} \text{ cm}^{-3} \sim 1 \times 10^{20} \text{ cm}^{-3}$ 程度のp型の不純物を含む不純物領域層4を形成する。その後、図示していないが、表面熱酸化・開口・Ni電極形成、絶縁層形成（OCD等）、コンタクトホール開口・A1配線・パッド形成、熱処理、オーミックコンタクト形成等の工程を経ることにより、図1に示す本実施の形態における横型接合型電界効果トランジスタ100が完成する。

30

#### 【0119】

##### (作用効果)

以上、上記構成からなる横型JFETおよびその製造方法によれば、複数の横型JFETが、縦方向に積層された構成が採用されているため、従来の構造に対して、さらに素子のオン抵抗を下げることが可能になる。また、第2半導体層12と、第3半導体層13と、第4半導体層14と、第5半導体層15との不純物濃度および膜厚さを略同じ値にすることにより、横型JFETのオン抵抗を最小にし、耐圧値を最大に設定することを可能としている。

#### 【0120】

なお、第3半導体層13と第4半導体層14との間に、第2半導体層12と第3半導体層13と第1ゲート電極層18Aとほぼ同じ構造である単位トランジスタ構造を1つまたは2以上さらに設ける構造を採用することにより、横型JFETの特性をより向上させることができ可能になる。

40

#### 【0121】

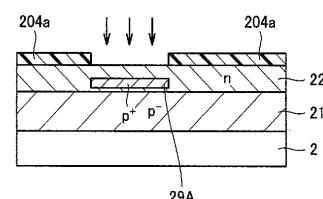

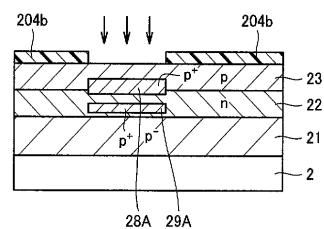

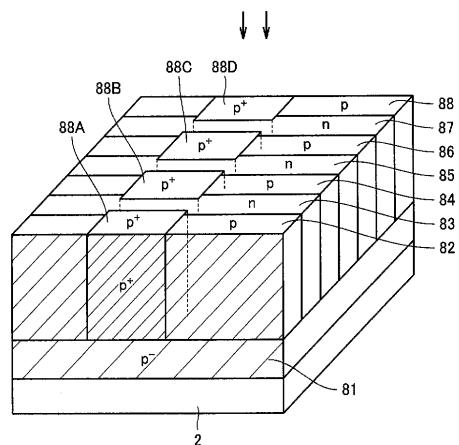

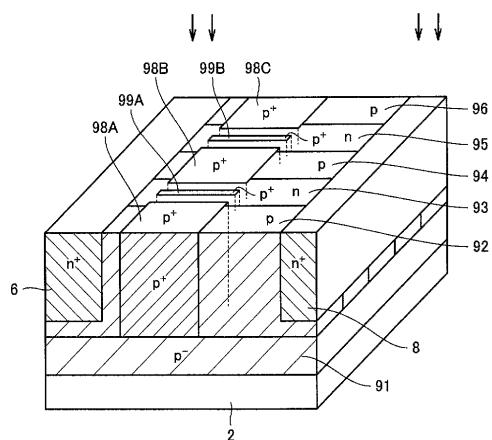

##### (実施の形態2)

##### (横型接合型電界効果トランジスタ200の構造)

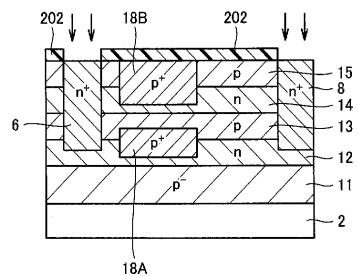

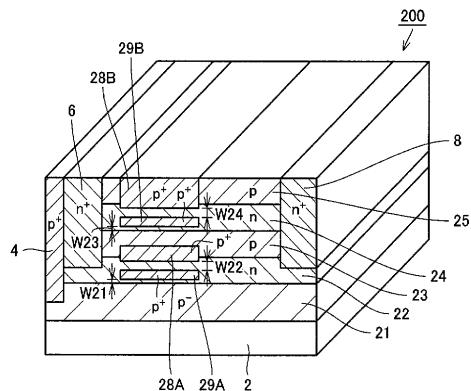

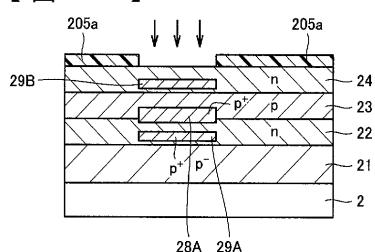

以下、実施の形態2における横型接合型電界効果トランジスタ200の構造について、図8を参照して説明する。なお、図8は本実施の形態における横型接合型電界効果トランジスタ200の構造を示す断面図である。

#### 【0122】

本実施の形態における横型接合型電界効果トランジスタ200の構造的特徴は、上記横型接合型電界効果トランジスタ100と同様に、p n接合およびゲート電極層を縦方向に配置するようにしたものである。

#### 【0123】

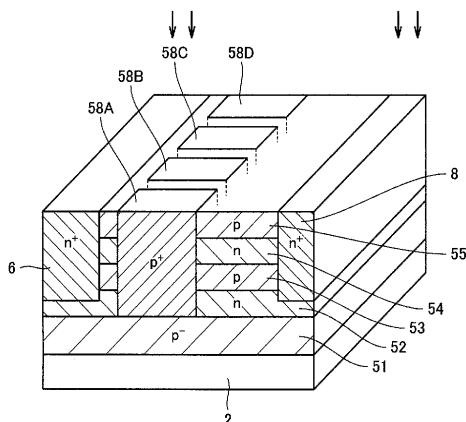

この横型接合型電界効果トランジスタ200は、Si等からなる半導体基板2の上に位置するp型不純物を含む第1半導体層21と、この第1半導体層21の上に、第1半導体層21の不純物濃度よりも高い濃度のn型不純物を含む第2半導体層22と、この第2半導体層22の上に位置し、p型不純物を含む第3半導体層23と、この第3半導体層23の上に位置し、n型不純物を含む第4半導体層24と、この第4半導体層24の上に位置し、p型不純物を含む第5半導体層25とが設けられている。10

#### 【0124】

ここで、第1半導体層21の材質はSiC、膜厚は3μmから4μm程度、不純物濃度は $1 \times 10^{16} \text{ cm}^{-3}$ 程度に設けられ、第2半導体層22、第3半導体層23、第4半導体層24、および、第5半導体層25の材質はSiC、膜厚は0.5μm～1.0μm程度、不純物濃度は $1 \times 10^{17} \text{ cm}^{-3} \sim 3 \times 10^{17} \text{ cm}^{-3}$ 程度に設けられる。

#### 【0125】

第5半導体層25中において所定の間隔を隔てて、下面が上記第2半導体層22にまで延在するように設けられ、第2半導体層22および第4半導体層24の不純物濃度よりも高い濃度のn型の不純物を含むソース／ドレイン領域層6，8が設けられる。ソース／ドレイン領域層6，8の不純物濃度は $1 \times 10^{19} \text{ cm}^{-3} \sim 1 \times 10^{20} \text{ cm}^{-3}$ 程度に設けられる。20

。

#### 【0126】

第3半導体層23中のソース／ドレイン領域層6，8の間には、下面が第2半導体層22にまで延在するように設けられ、第2半導体層22の不純物濃度よりも高いp型の不純物濃度を含む第1ゲート電極層28Aが設けられている。

#### 【0127】

第5半導体層25中のソース／ドレイン領域層6，8の間には、下面が第4半導体層24にまで延在するように設けられ、第1ゲート電極層28Aとほぼ同じ不純物濃度を有し、かつ、同電位を有するp型の不純物を含む第2ゲート電極層28Bが設けられている。第1ゲート電極層28Aおよび第2ゲート電極層28Bの不純物濃度は $3 \times 10^{18} \text{ cm}^{-3} \sim 1 \times 10^{20} \text{ cm}^{-3}$ 程度に設けられる。30

#### 【0128】

また、第1半導体層21と第1ゲート電極層28Aとに挟まれた第2半導体層22には、第1ゲート電極層28Aとほぼ同じ不純物濃度を有し、かつ、同電位を有するp型の第1不純物注入領域29Aが設けられている。さらに、第3半導体層23と第2ゲート電極層28Bとに挟まれた第4半導体層24に、第1ゲート電極28Aとほぼ同じ不純物濃度を有し、かつ、同電位を有するp型の第2不純物注入領域29Bが設けられている。なお、図8においては、第1不純物注入領域29Aおよび第2不純物注入領域29Bを一層設ける場合を図示しているが、総チャネル幅を広くしオン抵抗を下げつつ、かつ、ノーマリオフ型の横型接合型トランジスタを実現させる観点から、半導体層内に第1不純物注入領域29Aおよび第2不純物注入領域29Bをそれぞれ複数層設けることも可能である。40

#### 【0129】

なお、ソース領域層6の外側には、第1半導体層21にまで延在するp型の不純物濃度を含む不純物領域層4が設けられている。この不純物領域層4の不純物濃度は $3 \times 10^{18} \text{ cm}^{-3} \sim 1 \times 10^{20} \text{ cm}^{-3}$ 程度に設けられる。

#### 【0130】

なお、ノーマリオフ型の横型接合型電界効果トランジスタを実現させるためには、第1半導体層21の最上部と第1不純物注入領域29Aの最下部との間の間隔w21が、第2半導体層22と第1不純物注入領域29Aとの接合における拡散電位で広がる空乏層の間隔よりも小さくなるように設け、第1不純物注入領域29Aの最上部と上記第1ゲート電極

層 28 A の最下部との間の間隔 (w 22) が、第2半導体層22と第1ゲート電極層28 Aとの接合における拡散電位で広がる空乏層の間隔の2倍よりも小さくなるように設け、第3半導体層23の最上部と第2不純物注入領域29Bの最下部との間の間隔 (w 23) が、第4半導体層24と第2不純物注入領域29Bとの接合における拡散電位で広がる空乏層の間隔よりも小さくなるように設け、第2不純物注入領域29Bの最上部と第2ゲート電極層28Bの最下部との間の間隔 (w 24) が、第4半導体層24と第2ゲート電極層28Bとの接合における拡散電位で広がる空乏層の間隔の2倍よりも小さくなるように設ければ良い。

#### 【0131】

(横型接合型電界効果トランジスタ200の製造方法)

10

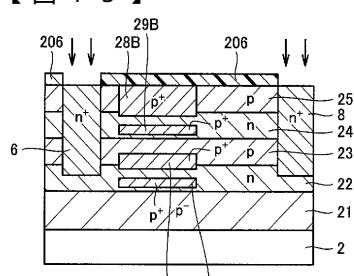

次に、上記構成からなる横型接合型電界効果トランジスタ200の製造方法について、図9～図16を参照して説明する。なお、図9～図16は図8に示す断面構造にしたがった製造工程を示す断面図である。

#### 【0132】

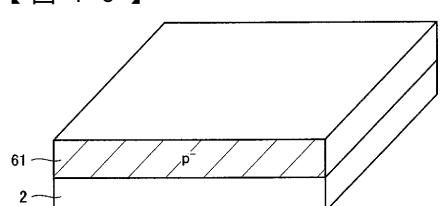

図9を参照して、Si等からなる半導体基板2上に、p型不純物を含む厚さ $3\text{ }\mu\text{m}\sim4\text{ }\mu\text{m}$ 程度、不純物濃度が $1\times10^{16}\text{ cm}^{-3}$ 程度のSiCからなる第1半導体層21をエピタキシャル成長により形成する。その後、この第1半導体層21の上に、n型不純物を含む厚さ約 $0.5\text{ }\mu\text{m}$ 程度、不純物濃度が第1半導体層21よりも高い約 $3\times10^{17}\text{ cm}^{-3}$ 程度のSiCからなる第2半導体層22をエピタキシャル成長により形成する。

#### 【0133】

次に、図10を参照して、第2半導体層22の上に、所定の開口パターンを有する酸化膜204aを形成し、この酸化膜204aをマスクにして、p型の不純物を第2半導体層22に導入して、第2半導体層22内に、 $3\times10^{18}\text{ cm}^{-3}\sim1\times10^{20}\text{ cm}^{-3}$ 程度のp型不純物を含む第1不純物注入領域29Aを形成する。なお、この時の、p型の不純物の注入条件は、注入エネルギー約270keV、注入量約 $7\times10^{13}\text{ cm}^{-2}$ 程度である。

20

#### 【0134】

その後、図11を参照して、酸化膜204aを除去した後、第2半導体層22の上に、p型不純物を含む厚さ約 $0.5\text{ }\mu\text{m}$ 程度、不純物濃度が約 $3\times10^{17}\text{ cm}^{-3}$ 程度のSiCからなる第3半導体層23をエピタキシャル成長により形成する。

#### 【0135】

次に、第3半導体層23の上に、所定の開口パターンを有する酸化膜204bを形成し、この酸化膜204bをマスクにして、p型の不純物を第3半導体層23に導入して、第2半導体層22と第3半導体層23とにまたがる領域に、第2半導体層22の不純物濃度よりも高い $3\times10^{18}\text{ cm}^{-3}\sim1\times10^{20}\text{ cm}^{-3}$ 程度のp型不純物を含む第1ゲート電極層28Aを形成する。なお、この時の、p型の不純物の注入条件は、注入エネルギー約350keV、注入量約 $1\times10^{14}\text{ cm}^{-2}$ 程度である。

30

#### 【0136】

次に、図12を参照して、酸化膜204bを除去した後、第3半導体層23の上に、n型不純物を含む厚さ約 $0.5\text{ }\mu\text{m}$ 程度、不純物濃度が第1半導体層21よりも高い $3\times10^{17}\text{ cm}^{-3}$ 程度のSiCからなる第4半導体層24を形成する。

40

#### 【0137】

その後、第4半導体層24の上に、所定の開口パターンを有する酸化膜205aを形成し、この酸化膜205aをマスクにして、p型の不純物を第4半導体層24に導入して、第4半導体層24内に、 $3\times10^{18}\text{ cm}^{-3}\sim1\times10^{20}\text{ cm}^{-3}$ 程度のp型不純物を含む第2不純物注入領域29Bを形成する。なお、この時の、p型の不純物の注入条件は、注入エネルギー270keV、注入量 $7\times10^{13}\text{ cm}^{-2}$ 程度である。

#### 【0138】

次に、図13を参照して、第4半導体層24の上に、p型不純物を含む厚さ約 $0.5\text{ }\mu\text{m}$ 程度、不純物濃度が約 $3\times10^{17}\text{ cm}^{-3}$ 程度のSiCからなる第5半導体層25をエピタキシャル成長により形成する。

50

## 【0139】

次に、図14を参照して、第5半導体層25の上に、所定の開口パターンを有する酸化膜205bを形成し、この酸化膜205bをマスクにして、p型の不純物を第5半導体層25に導入して、第4半導体層24と第5半導体層25とにまたがる領域に、第2半導体層22の不純物濃度よりも高い $3 \times 10^{18} \text{ cm}^{-3}$ ～ $1 \times 10^{20} \text{ cm}^{-3}$ 程度のp型不純物を含む第2ゲート電極層28Bを形成する。なお、この時の、p型の不純物の注入は、第1段階が注入エネルギー約350keV、注入量約 $1 \times 10^{14} \text{ cm}^{-2}$ 、第2段階が注入エネルギー約250keV、注入量約 $2 \times 10^{14} \text{ cm}^{-2}$ 、第3段階が注入エネルギー約140keV、注入量約 $5 \times 10^{14} \text{ cm}^{-2}$ 、第4段階が注入エネルギー約70keV、注入量約 $4 \times 10^{14} \text{ cm}^{-2}$ 、第5段階が注入エネルギー約30keV、注入量約 $3 \times 10^{14} \text{ cm}^{-2}$ の第5段階に分けて行なう。

10

## 【0140】

次に、図15を参照して、酸化膜205bを除去した後、再び、第5半導体層25の上に、所定の開口パターンを有する酸化膜206を形成し、この酸化膜206をマスクにして、第1不純物注入領域29A、第2不純物注入領域29B、第1ゲート電極層28A、および、第2ゲート電極層28Bの両側において、第5半導体層25に不純物を導入して、下面が第2半導体層22にまで延在し、第2半導体層22および前記第4半導体層24の不純物濃度よりも高い $1 \times 10^{19} \text{ cm}^{-3}$ ～ $1 \times 10^{20} \text{ cm}^{-3}$ 程度のn型の不純物を含むソース／ドレイン領域層6，8を形成する。

## 【0141】

次に、図16を参照して、酸化膜206を除去した後、再び、第5半導体層25の上に、所定の開口パターンを有する酸化膜207を形成し、この酸化膜207をマスクにして、ソース／ドレイン領域層6の外側の領域において、第5半導体層25に不純物を導入して、下面が第1半導体層21にまで延在し、 $3 \times 10^{18} \text{ cm}^{-3}$ ～ $1 \times 10^{20} \text{ cm}^{-3}$ 程度のp型の不純物を含む不純物領域層4を形成する。その後、図示していないが、表面熱酸化・開口・Ni電極形成、絶縁層形成（OCD等）、コンタクトホール開口・A1配線・パッド形成、熱処理、オーミックコンタクト形成等の工程を経ることにより、図8に示す本実施の形態における横型接合型電界効果トランジスタ200が完成する。

## 【0142】

## (作用効果)

以上、上記構成からなる横型JFETおよびその製造方法によれば、複数の横型JFETが、縦方向に積層された構成が採用されているため、従来の構造に対して、さらに素子のオン抵抗を下げることが可能になる。また、第2半導体層22と、第3半導体層23と、第4半導体層24と、第5半導体層25との不純物濃度および膜厚さを略同じ値にすることにより、横型JFETのオン抵抗を最小にし、耐圧値を最大に設定することを可能としている。

## 【0143】

なお、第3半導体層23と第4半導体層24との間に、第2半導体層22と第3半導体層23と第1ゲート電極層28Aと第1不純物注入領域29Aとほぼ同じ構造である単位トランジスタ構造を1つまたは2以上さらに設ける構造を採用することにより、横型JFETの特性をより向上させることが可能になる。

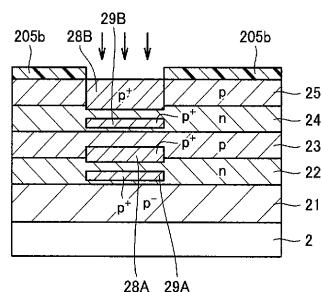

## 【0144】

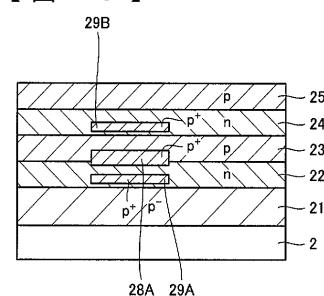

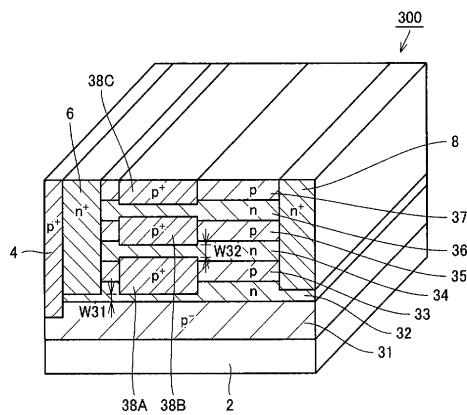

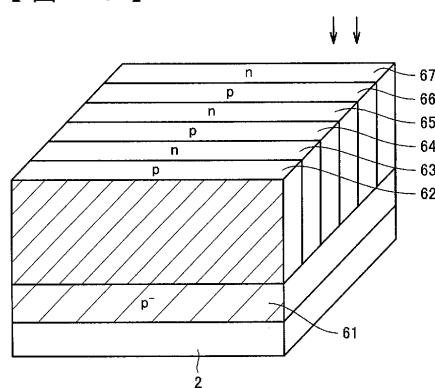

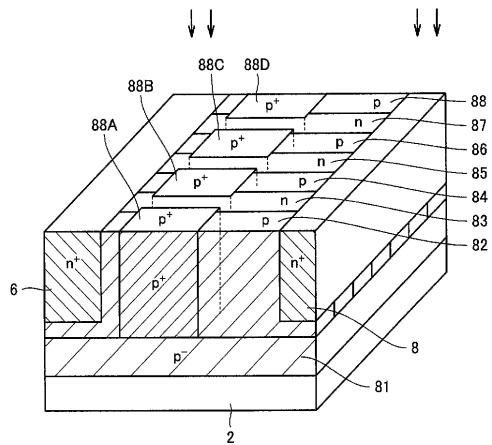

## (実施の形態3)

## (横型接合型電界効果トランジスタ300の構造)

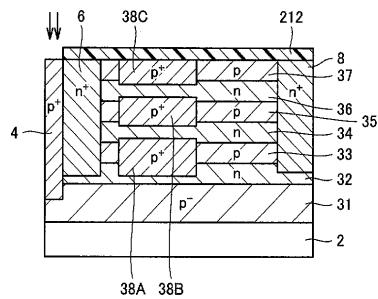

以下、実施の形態3における横型接合型電界効果トランジスタ300の構造について、図17を参照して説明する。なお、図17は本実施の形態における横型接合型電界効果トランジスタ300の構造を示す断面図である。

## 【0145】

本実施の形態における横型接合型電界効果トランジスタ300の構造的特徴は、上記横型接合型電界効果トランジスタ100と同様に、pn接合およびゲート電極層を縦方向に配

10

20

30

40

50

置するようにしたものである。

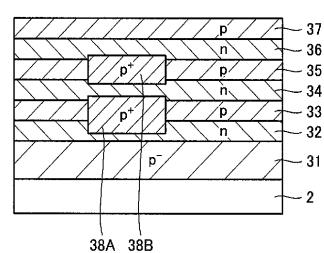

**【0146】**

この横型接合型電界効果トランジスタ300は、Si等からなる半導体基板2上に位置するp型不純物を含む第1半導体層31と、この第1半導体層31の上に、第1半導体層31の不純物濃度よりも高い濃度のn型不純物を含む第2半導体層32と、この第2半導体層32の上に位置し、p型不純物を含む第3半導体層33と、この第3半導体層33の上に位置し、n型不純物を含む第4半導体層34と、この第4半導体層34の上に位置し、p型不純物を含む第5半導体層35と、この第5半導体層35の上に位置し、n型不純物を含む第6半導体層36と、この第6半導体層36の上に位置し、p型不純物を含む第7半導体層37とが設けられている。

10

**【0147】**

ここで、第1半導体層31の材質はSiC、膜厚は $3\text{ }\mu\text{m} \sim 4\text{ }\mu\text{m}$ 程度、不純物濃度は $1 \times 10^{16}\text{ cm}^{-3}$ 程度に設けられ、第2半導体層32、第3半導体層33、第4半導体層34、第5半導体層35、第6半導体層36、および、第7半導体層37の材質はSiC、膜厚は $0.5\text{ }\mu\text{m} \sim 1.0\text{ }\mu\text{m}$ 程度、不純物濃度は $1 \times 10^{17}\text{ cm}^{-3} \sim 3 \times 10^{17}\text{ cm}^{-3}$ 程度に設けられる。

**【0148】**

第7半導体層37中において所定の間隔を隔てて、下面が上記第2半導体層32にまで延在するように設けられ、上記第2半導体層32、第4半導体層34、および第6半導体層36の不純物濃度よりも高い濃度のn型の不純物を含むソース／ドレイン領域層6，8が設けられる。ソース／ドレイン領域層6，8の不純物濃度は $1 \times 10^{19}\text{ cm}^{-3} \sim 1 \times 10^{20}\text{ cm}^{-3}$ 程度に設けられる。

20

**【0149】**

第3半導体層33中のソース／ドレイン領域層6，8の間には、下面が第2半導体層32にまで延在し、上面が第4半導体層34にまで延在するように設けられ、第2半導体層32および第4半導体層34の不純物濃度よりも高いp型の不純物濃度を含む第1ゲート電極層38Aが設けられている。

**【0150】**

第5半導体層35中のソース／ドレイン領域層6，8の間には、下面が第4半導体層34にまで延在し、上面が第6半導体層36にまで延在するように設けられ、第4半導体層34および第6半導体層36の不純物濃度よりも高いp型の不純物濃度を含む第2ゲート電極層38Bが設けられている。

30

**【0151】**

第7半導体層37中のソース／ドレイン領域層6，8の間には、下面が第6半導体層にまで延在するように設けられ、第1ゲート電極層38Aおよび第2ゲート電極層38Bとほぼ同じ不純物濃度を有し、かつ、同電位を有するp型の不純物を含む第3ゲート電極層と38Cが設けられている。

**【0152】**

第1ゲート電極層38A、第2ゲート電極層38B、および、第3ゲート電極層38Cの不純物濃度は $3 \times 10^{18}\text{ cm}^{-3} \sim 1 \times 10^{20}\text{ cm}^{-3}$ 程度に設けられる。

40

**【0153】**

なお、ソース領域層6の外側には、第1半導体層31にまで延在するp型の不純物濃度を含む不純物領域層4が設けられている。この不純物領域層4の不純物濃度は $3 \times 10^{18}\text{ cm}^{-3} \sim 1 \times 10^{20}\text{ cm}^{-3}$ 程度に設けられる。

**【0154】**

なお、ノーマリオフ型の横型接合型電界効果トランジスタを実現させるためには、第1半導体層31の最上部と第1ゲート電極層38Aの最下部との間の間隔(w31)が、第2半導体層32と第1ゲート電極層38Aとの接合における拡散電位で広がる空乏層の間隔よりも小さくなるように設け、第1ゲート電極層38Aの最上部と第2ゲート電極層38Bの最下部との間の間隔(w32)が、第4半導体層34と第1ゲート電極層38Aとの

50

接合における拡散電位で広がる空乏層の間隔の2倍よりも小さくなるように設ければ良い。

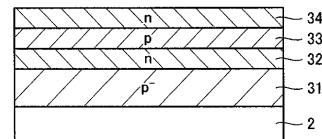

### 【0155】

(横型接合型電界効果トランジスタ300の製造方法)

次に、上記構成からなる横型接合型電界効果トランジスタ300の製造方法について、図18～図25を参照して説明する。なお、図18～図25は図17に示す断面構造にしたがった製造工程を示す断面図である。

### 【0156】

図18を参照して、Si等からなる半導体基板2上に、p型不純物を含む厚さ3μm～4μm程度、不純物濃度が $1 \times 10^{16} \text{ cm}^{-3}$ 程度のSiCからなる第1半導体層31をエピタキシャル成長により形成する。その後、この第1半導体層31の上に、n型不純物を含む厚さ0.5μm～1.0μm程度、不純物濃度が第1半導体層31よりも高い $1 \times 10^{17} \text{ cm}^{-3} \sim 3 \times 10^{17} \text{ cm}^{-3}$ 程度のSiCからなる第2半導体層32をエピタキシャル成長により形成する。その後、第2半導体層32の上に、p型不純物を含む厚さ0.5μm～1.0μm程度、不純物濃度が $1 \times 10^{17} \text{ cm}^{-3} \sim 3 \times 10^{17} \text{ cm}^{-3}$ 程度のSiCからなる第3半導体層33をエピタキシャル成長により形成する。その後、第3半導体層33の上に、n型不純物を含む厚さ0.5μm～1.0μm程度、不純物濃度が $1 \times 10^{17} \text{ cm}^{-3} \sim 3 \times 10^{17} \text{ cm}^{-3}$ 程度のSiCからなる第4半導体層34をエピタキシャル成長により形成する。

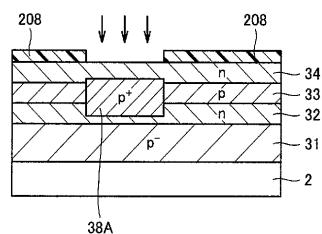

### 【0157】

次に、図19を参照して、第4半導体層34の上に、所定の開口パターンを有する酸化膜208を形成し、この酸化膜208をマスクにして、p型の不純物を第4半導体層34の所定領域に不純物を導入し、下面が第2半導体層32にまで延在し、上面が第4半導体層34にまで延在し、第2半導体層32および第4半導体層34の不純物濃度よりも高い $3 \times 10^{18} \text{ cm}^{-3} \sim 1 \times 10^{20} \text{ cm}^{-3}$ 程度のp型不純物を含む第1ゲート電極層38Aを形成する。

### 【0158】

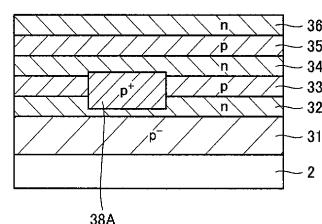

次に、図20を参照して、第4半導体層34の上に、p型不純物を含む厚さ0.5μm～1.0μm程度、不純物濃度が $1 \times 10^{17} \text{ cm}^{-3} \sim 3 \times 10^{17} \text{ cm}^{-3}$ 程度のSiCからなる第5半導体層35を形成する。その後、第5半導体層35の上に、n型不純物を含む厚さ0.5μm～1.0μm程度、不純物濃度が $1 \times 10^{17} \text{ cm}^{-3} \sim 3 \times 10^{17} \text{ cm}^{-3}$ 程度のSiCからなる第6半導体層36をエピタキシャル成長により形成する。

### 【0159】

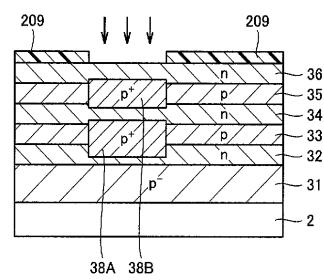

次に、図21を参照して、第6半導体層36の上に、所定の開口パターンを有する酸化膜209を形成し、この酸化膜209をマスクにして、p型の不純物を第6半導体層36の所定領域に不純物を導入し、下面が第4半導体層34にまで延在し、上面が第6半導体層36にまで延在し、第4半導体層34および第6半導体層36の不純物濃度よりも高い $3 \times 10^{18} \text{ cm}^{-3} \sim 1 \times 10^{20} \text{ cm}^{-3}$ 程度のp型不純物を含む第2ゲート電極層38Bを形成する。

### 【0160】

次に、図22を参照して、酸化膜209を除去した後、第6半導体層36の上に、p型不純物を含む厚さ0.5μm～1.0μm程度、不純物濃度が $1 \times 10^{17} \text{ cm}^{-3} \sim 3 \times 10^{17} \text{ cm}^{-3}$ 程度のSiCからなる第7半導体層37をエピタキシャル成長により形成する。

### 【0161】

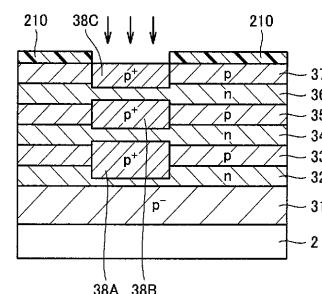

次に、図23を参照して、第7半導体層37の上に、所定の開口パターンを有する酸化膜210を形成し、この酸化膜210をマスクにして、p型の不純物を第7半導体層37の所定領域に不純物を導入し、下面が第6半導体層36にまで延在し、第6半導体層36の不純物濃度よりも高い $3 \times 10^{18} \text{ cm}^{-3} \sim 1 \times 10^{20} \text{ cm}^{-3}$ 程度のp型不純物を含む第3ゲート電極層38Cを形成する。

### 【0162】

10

20

30

40

50

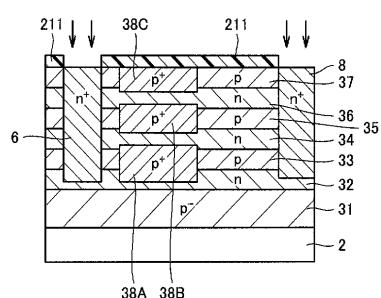

次に、図24を参照して、酸化膜210を除去した後、再び、第7半導体層37の上に、所定の開口パターンを有する酸化膜211を形成し、この酸化膜211をマスクにして、第1ゲート電極層38A、第2ゲート電極層38B、および、第3ゲート電極層38Cの両側において、第7半導体層37に不純物を導入して、下面が第2半導体層32にまで延在し、第2半導体層32および前記第4半導体層34の不純物濃度よりも高い $1 \times 10^{19} \text{ cm}^{-3}$ ～ $1 \times 10^{20} \text{ cm}^{-3}$ 程度のn型の不純物を含むソース／ドレイン領域層6，8を形成する。

#### 【0163】

次に、図25を参照して、酸化膜211を除去した後、再び、第7半導体層37の上に、所定の開口パターンを有する酸化膜212を形成し、この酸化膜212をマスクにして、ソース／ドレイン領域層6の外側の領域において、第7半導体層37に不純物を導入して、下面が第1半導体層31にまで延在し、 $3 \times 10^{18} \text{ cm}^{-3}$ ～ $1 \times 10^{20} \text{ cm}^{-3}$ 程度のp型の不純物を含む不純物領域層4を形成する。その後、図示していないが、表面熱酸化・開口・N<sub>i</sub>電極形成、絶縁層形成（OCD等）、コンタクトホール開口・A1配線・パット形成、熱処理、オーミックコンタクト形成等の工程を経ることにより、図17に示す本実施の形態における横型接合型電界効果トランジスタ300が完成する。

#### 【0164】

##### (作用効果)

以上、上記構成からなる横型JFETおよびその製造方法によれば、複数の横型JFETが、縦方向に積層された構成が採用されているため、従来の構造に対して、さらに素子のオン抵抗を下げることが可能になる。また、第2半導体層32と、第3半導体層33と、第4半導体層34と、第5半導体層35と、第6半導体層36と、第7半導体層37との不純物濃度および膜厚さを略同じ値にすることにより、横型JFETのオン抵抗を最小にし、耐圧値を最大に設定することを可能としている。

#### 【0165】

なお、第4半導体層34と第5半導体層35との間に、第3半導体層33と第4半導体層34と第1ゲート電極層38Aとほぼ同じ構造である単位トランジスタ構造を1つまたは2以上さらに設ける構造を採用することにより、横型JFETの特性をより向上させることが可能になる。

#### 【0166】

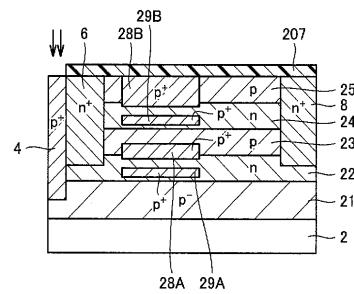

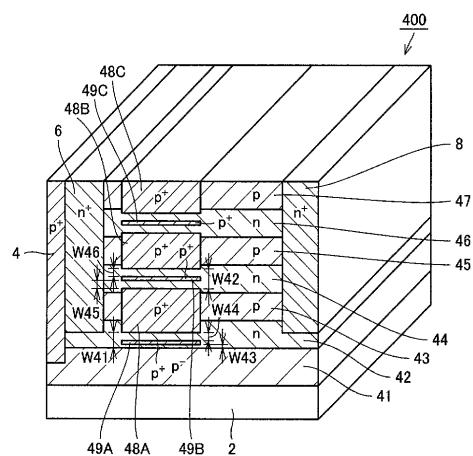

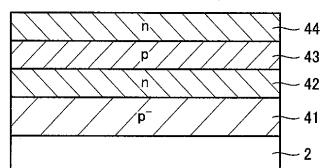

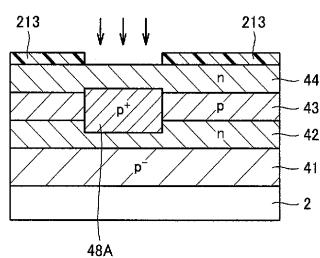

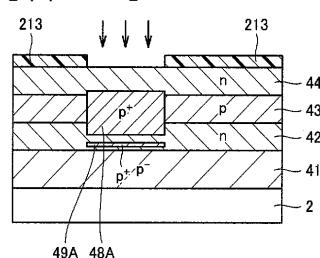

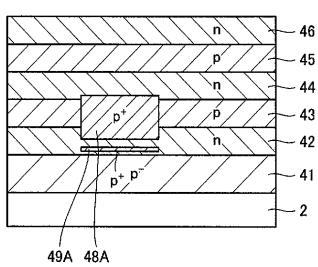

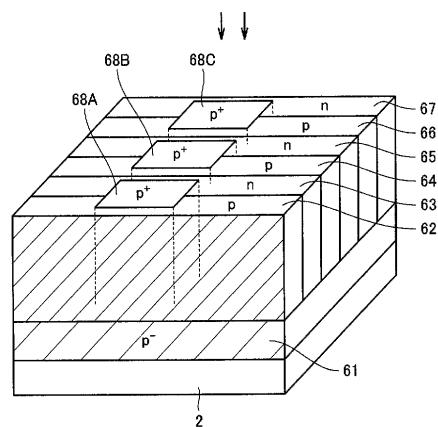

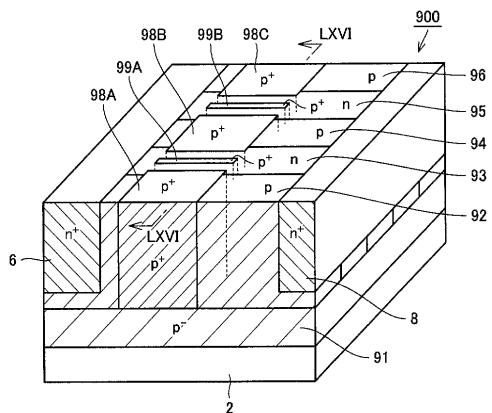

##### (実施の形態4)

##### (横型接合型電界効果トランジスタ400の構造)

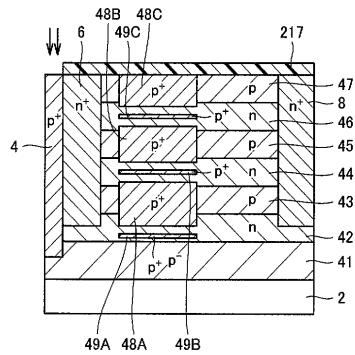

以下、実施の形態4における横型接合型電界効果トランジスタ400の構造について、図26を参照して説明する。なお、図26は本実施の形態における横型接合型電界効果トランジスタ400の構造を示す断面図である。

#### 【0167】

本実施の形態における横型接合型電界効果トランジスタ400の構造的特徴は、上記横型接合型電界効果トランジスタ100と同様に、pn接合およびゲート電極層を縦方向に配置するようにしたものである。

#### 【0168】

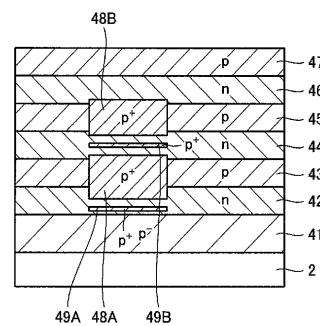

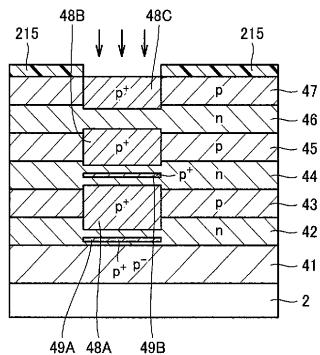

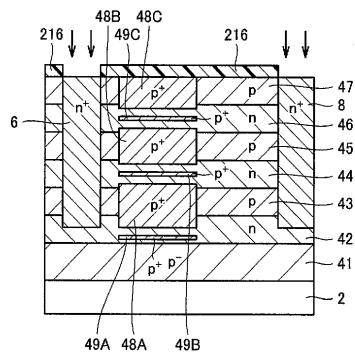

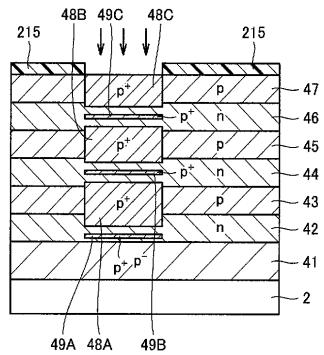

この横型接合型電界効果トランジスタ400は、Si等からなる半導体基板2の上に位置するp型不純物を含む第1半導体層41と、この第1半導体層41の上に位置し、第1半導体層41の不純物濃度よりも高い濃度のn型不純物を含む第2半導体層42と、この第2半導体層42の上に位置し、p型不純物を含む第3半導体層43と、この第3半導体層43の上に位置し、n型不純物を含む第4半導体層44と、この第4半導体層44の上に位置し、p型不純物を含む第5半導体層45と、この第5半導体層45の上に位置し、n型不純物を含む第6半導体層46と、この第6半導体層46の上に位置し、p型不純物を含む第7半導体層47とが設けられている。

#### 【0169】

ここで、第1半導体層41の材質はSiC、膜厚は3μm～4μm程度、不純物濃度は1

10

20

30

40

50

$\times 10^{16} \text{ cm}^{-3}$  程度に設けられ、第2半導体層42、第3半導体層43、第4半導体層44、第5半導体層45、第6半導体層46、および、第7半導体層47の材質はSiC、膜厚は $0.5 \mu\text{m} \sim 1.0 \mu\text{m}$ 程度、不純物濃度は $1 \times 10^{17} \text{ cm}^{-3} \sim 3 \times 10^{17} \text{ cm}^{-3}$ 程度に設けられる。

#### 【0170】

第7半導体層47において所定の間隔を隔てて、下面が第2半導体層42にまで延在するように設けられ、第2半導体層42、第4半導体層44、および、第6半導体層46の不純物濃度よりも高い濃度のn型の不純物を含むソース／ドレイン領域層6，8が設けられる。ソース／ドレイン領域層6，8の不純物濃度は $1 \times 10^{19} \text{ cm}^{-3} \sim 1 \times 10^{20} \text{ cm}^{-3}$ 程度に設けられる。

10

#### 【0171】

第3半導体層43中のソース／ドレイン領域層6，8の間には、下面が第2半導体層42にまで延在し、上面が上記第4半導体層44にまで延在するように設けられ、第2半導体層42、上記第4半導体層44、および、第6半導体層46の不純物濃度よりも高い不純物濃度を含む第1ゲート電極層48Aが設けられている。

#### 【0172】

第5半導体層45中のソース／ドレイン領域層6，8の間には、下面が第4半導体層44にまで延在し、上面が上記第6半導体層46にまで延在するように設けられ、第1ゲート電極層48Aとほぼ同じ不純物濃度を有し、かつ、同電位を有するp型の不純物を含む第2ゲート電極層48Bが設けられている。

20

#### 【0173】

第7半導体層47中のソース／ドレイン領域6，8の間において、下面が第6半導体層46にまで延在するように設けられ、第1ゲート電極層48Aおよび第2ゲート電極層48Bとほぼ同じ不純物濃度を有し、かつ、同電位を有するp型の第3ゲート電極層48Cが設けられている。第1ゲート電極層48A、第2ゲート電極層48B、および、第3ゲート電極層48Cの不純物濃度は $3 \times 10^{18} \text{ cm}^{-3} \sim 1 \times 10^{20} \text{ cm}^{-3}$ 程度に設けられる。

#### 【0174】

また、第1半導体層41と第1ゲート電極層48Aとに挟まれた第2半導体層42に、第1ゲート電極層48Aとほぼ同じ不純物濃度を有し、かつ、同電位を有するp型の第1不純物注入領域49Aが設けられ、第1ゲート電極層48Aと第2ゲート電極層48Bとに挟まれた第4半導体層44に、第1ゲート電極層48Aとほぼ同じ不純物濃度を有し、かつ同電位を有するp型の第2不純物注入領域49Bが設けられ、第2ゲート電極層48Bと第3ゲート電極層48Cとに挟まれた第6半導体層46に、第1ゲート電極層48Aおよび第2ゲート電極層48Bとほぼ同じ不純物濃度を有し、かつ同電位を有するp型の第3不純物注入領域49Cが設けられている。なお、図26においては、第1不純物注入領域49A、第2不純物注入領域49B、および、第3不純物注入領域49Cを一層設ける場合を図示しているが、総チャネル幅を広くしオン抵抗を下げつつ、かつ、ノーマリオフ型の横型接合型トランジスタを実現させる観点から、半導体層内に第1不純物注入領域49A、第2不純物注入領域49B、および、第3不純物注入領域49Cをそれぞれ複数層設けることも可能である。

30

#### 【0175】

なお、ソース領域層6の外側には、第1半導体層41にまで延在するp型の不純物濃度を含む不純物領域層4が設けられている。この不純物領域層4の不純物濃度は $3 \times 10^{18} \text{ cm}^{-3} \sim 1 \times 10^{20} \text{ cm}^{-3}$ 程度に設けられる。

40

#### 【0176】

なお、ノーマリオフ型の横型接合型電界効果トランジスタを実現させるためには、第1半導体層41の最上部と第1ゲート電極層48Aの最下部との間の間隔(w41)が、第2半導体層42と第1ゲート電極層48Aとの接合における拡散電位で広がる空乏層の間隔よりも小さくなるように設け、第1ゲート電極層48Aの最上部と第2ゲート電極層48Bの最下部との間の間隔(w42)が、第4半導体層44と第1ゲート電極層48Aとの

50

接合における拡散電位で広がる空乏層の間隔と、第4半導体層44と第2ゲート電極層48Bとの接合における拡散電位で広がる空乏層の間隔との和よりも小さくなるように設ければ良い。

#### 【0177】

さらに好ましくは、第1半導体層41の最上部と第1不純物注入領域49Aの最下部との間の間隔(w43)が、第2半導体層42と第1不純物注入領域49Aとの接合における拡散電位で広がる空乏層の間隔よりも小さく、第1不純物注入領域49Aの最上部と第1ゲート電極層48Aの最下部との間隔(w44)が、第2半導体層42と第1ゲート電極層48Aとの接合における拡散電位で広がる空乏層の間隔の2倍よりも小さくなるように設け、第1ゲート電極層48Aの最上部と第2不純物注入領域49Bの最下部との間の間隔(w45)が、第4半導体層と第2不純物注入領域49Bとの接合における拡散電位で広がる空乏層の間隔の2倍よりも小さくなるように設け、第2不純物注入領域49Bの最上部と第2ゲート電極層48Bの最下部との間の間隔(w46)が、第4半導体層44と第2ゲート電極層48Bとの接合における拡散電位で広がる空乏層の間隔の2倍よりも小さくなるように設ければ良い。10

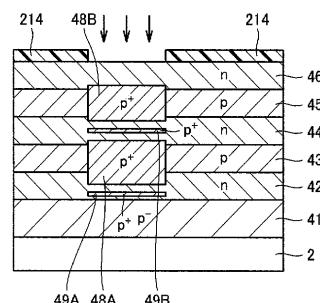

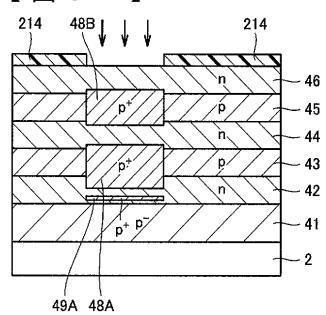

#### 【0178】

(横型接合型電界効果トランジスタ400の製造方法)

次に、上記構成からなる横型接合型電界効果トランジスタ400の製造方法について、図27～図37を参照して説明する。なお、図27～図37は図26に示す断面構造にしたがった製造工程を示す断面図である。20

#### 【0179】

図27を参照して、Si等からなる半導体基板2上に、p型不純物を含む厚さ $3\text{ }\mu\text{m} \sim 4\text{ }\mu\text{m}$ 程度、不純物濃度が $1 \times 10^{16}\text{ cm}^{-3}$ 程度のSiCからなる第1半導体層41をエピタキシャル成長により形成する。その後、この第1半導体層41の上に、n型不純物を含む厚さ $0.5\text{ }\mu\text{m} \sim 1.0\text{ }\mu\text{m}$ 程度、不純物濃度が第1半導体層41よりも高い $1 \times 10^{17}\text{ cm}^{-3} \sim 3 \times 10^{17}\text{ cm}^{-3}$ 程度のSiCからなる第2半導体層42をエピタキシャル成長により形成する。その後、第2半導体層42の上に、p型不純物を含む厚さ $0.5\text{ }\mu\text{m} \sim 1.0\text{ }\mu\text{m}$ 程度、不純物濃度が $1 \times 10^{17}\text{ cm}^{-3} \sim 3 \times 10^{17}\text{ cm}^{-3}$ 程度のSiCからなる第3半導体層43をエピタキシャル成長により形成する。その後、第3半導体層43の上に、n型不純物を含む厚さ $0.5\text{ }\mu\text{m} \sim 1.0\text{ }\mu\text{m}$ 程度、不純物濃度が $1 \times 10^{17}\text{ cm}^{-3} \sim 3 \times 10^{17}\text{ cm}^{-3}$ 程度のSiCからなる第4半導体層44をエピタキシャル成長により形成する。30

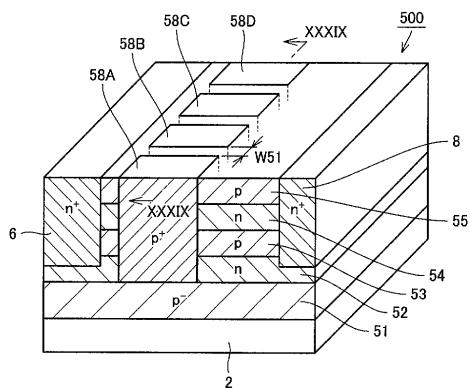

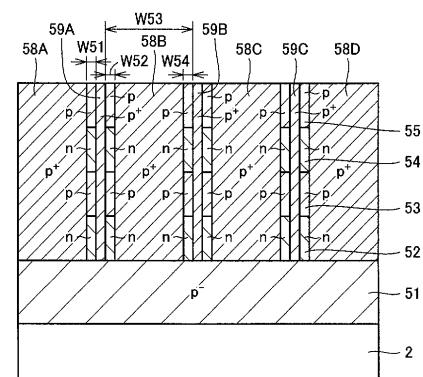

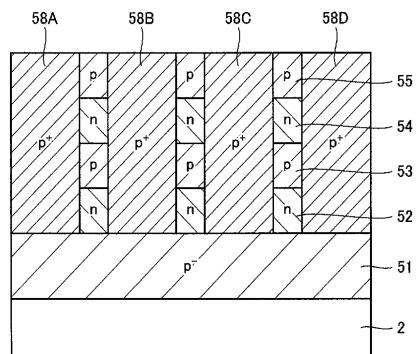

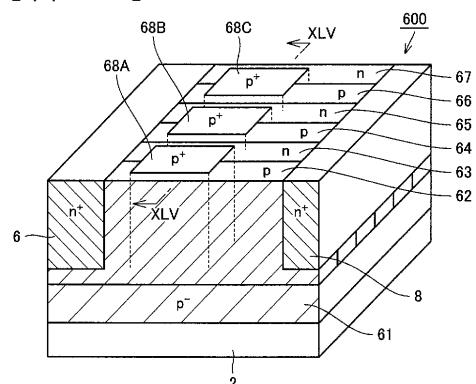

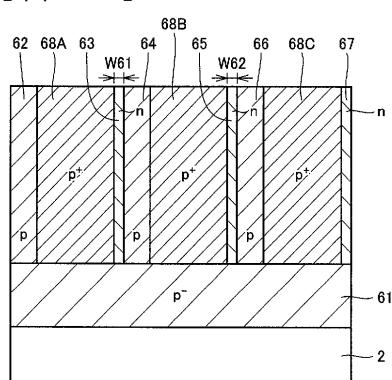

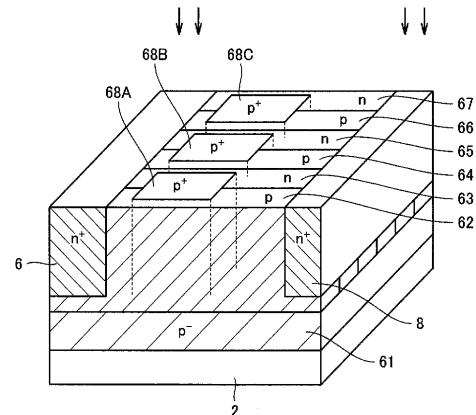

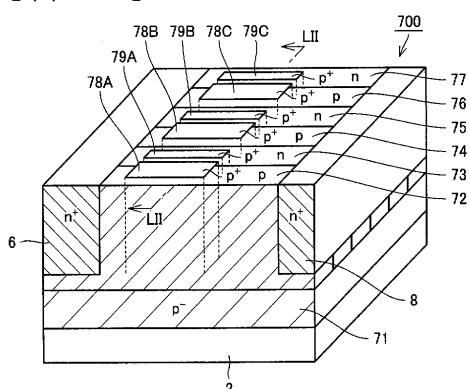

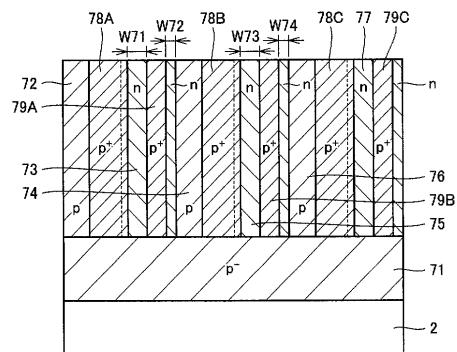

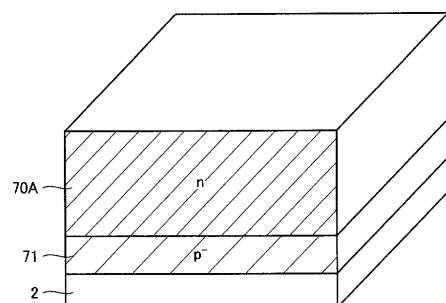

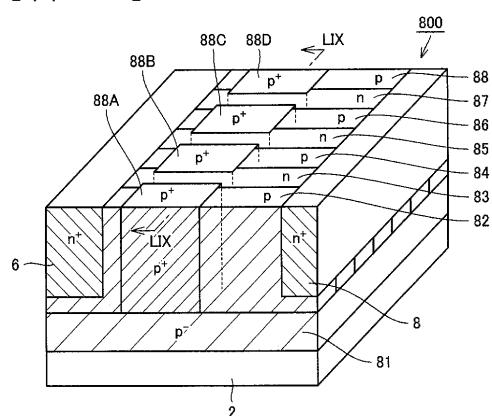

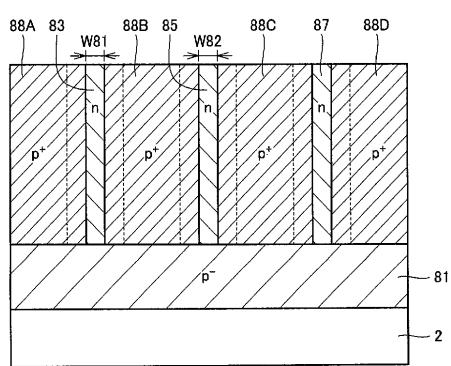

#### 【0180】