등록특허 10-2706325

(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2024년09월12일

(11) 등록번호 10-2706325

(24) 등록일자 2024년09월09일

- (51) 국제특허분류(Int. Cl.)

*H01L 21/02* (2006.01) *H01L 21/28* (2006.01)

*H01L 21/285* (2006.01) *H01L 29/417* (2006.01)

*H01L 29/49* (2006.01) *H01L 29/66* (2006.01)

*H01L 29/786* (2006.01)

- (52) CPC특허분류

*H01L 21/02274* (2013.01)

*H01L 21/0262* (2013.01)

- (21) 출원번호 10-2018-7023363

- (22) 출원일자(국제) 2017년01월10일

심사청구일자 2022년01월06일

- (85) 번역문제출일자 2018년08월13일

- (65) 공개번호 10-2018-0095115

- (43) 공개일자 2018년08월24일

- (86) 국제출원번호 PCT/US2017/012872

- (87) 국제공개번호 WO 2017/123552

국제공개일자 2017년07월20일

- (30) 우선권주장

62/278,955 2016년01월14일 미국(US)

15/359,325 2016년11월22일 미국(US)

- (56) 선행기술조사문헌

KR1020120003379 A\*

- \*는 심사관에 의하여 인용된 문헌

전체 청구항 수 : 총 12 항

심사관 : 노병규

## (54) 발명의 명칭 산소 빈자리를 불소 처리하는 IGZO 부동화 방법

**(57) 요약**

본 개시내용의 실시예들은 일반적으로, 금속 산화물 층을 갖는 TFT를 형성하기 위한 방법들에 관한 것이다. 방법은, 금속 산화물 층을 형성하는 단계, 및 불소 함유 가스 또는 플라즈마로 금속 산화물 층을 처리하는 단계를 포함할 수 있다. 금속 산화물 층의 불소 처리는 금속 산화물 채널 층 내의 산소 빈자리들을 채우는 것을 도우며, 이는, 더 안정된 TFT를 초래하고 TFT에서의 네거티브 임계 전압을 방지한다.

**대표도** - 도5a

(52) CPC특허분류

*H01L 21/28194* (2013.01)

*H01L 21/28556* (2013.01)

*H01L 29/41733* (2013.01)

*H01L 29/4908* (2013.01)

*H01L 29/66742* (2013.01)

*H01L 29/786* (2021.01)

(72) 발명자

**원, 태경**

미국 95129 캘리포니아 새너제이 벨베데레 레인

1054

**장, 쑤에나**

미국 95124 캘리포니아 새너제이 로스 가토스 알마

덴 로드 1791

---

**성, 원호**

충청남도 아산시 남부로 353, 114동 404호 ( 풍기동, 동일하이빌아파트)

**림, 로드니 순령**

미국 94015 캘리포니아 데일리 시티 세인트 프란시스 불러바드 324

## 명세서

### 청구범위

#### 청구항 1

방법으로서,

기판 위에 게이트 전극을 형성하는 단계;

상기 게이트 전극 위에 게이트 유전체 층을 증착하는 단계;

상기 게이트 유전체 층 위에 금속 산화물 반도체 층을 증착하는 단계; 그 다음,

상기 금속 산화물 반도체 층을 어닐링(annealing)하는 단계; 그 다음,

산소 빈자리(vacancy)들을 채우기 위해 상기 금속 산화물 반도체 층을 제1 불소 라디칼(radical)들에 노출시키는 단계; 그 다음,

상기 금속 산화물 반도체 층 위에 전도성 층을 증착하는 단계를 포함하고,

상기 방법은 상기 금속 산화물 반도체 층을 어닐링하는 단계 이전에 산소 빈자리들을 채우기 위해 상기 금속 산화물 반도체 층을 제2 불소 라디칼들에 노출시키는 단계를 더 포함하며, 상기 제2 불소 라디칼들은 제2 원격 플라즈마에서 생성되는, 방법.

#### 청구항 2

방법으로서,

기판 위에 게이트 전극을 형성하는 단계;

상기 게이트 전극 위에 게이트 유전체 층을 증착하는 단계;

상기 게이트 유전체 층 위에 금속 산화물 반도체 층을 증착하는 단계; 그 다음,

상기 금속 산화물 반도체 층을 어닐링하는 단계; 그 다음,

산소 빈자리들을 채우기 위해 상기 금속 산화물 반도체 층을 제1 불소 라디칼들에 노출시키는 단계; 그 다음,

상기 금속 산화물 반도체 층 위에 전도성 층을 증착하는 단계를 포함하고,

상기 방법은 상기 금속 산화물 반도체 층을 어닐링하는 단계 이전에 산소 빈자리들을 채우기 위해 상기 금속 산화물 반도체 층을 제2 불소 라디칼들에 노출시키는 단계를 더 포함하며, 상기 제2 불소 라디칼들은 상기 금속 산화물 반도체 층이 배치되는 챔버 내에서 점화(ignite)된 제2 플라즈마에서 생성되는, 방법.

#### 청구항 3

제1항 또는 제2항에 있어서,

상기 제1 불소 라디칼들은 제1 원격 플라즈마에서 생성되는, 방법.

#### 청구항 4

제1항 또는 제2항에 있어서,

상기 제1 불소 라디칼들은, 상기 금속 산화물 반도체 층이 배치되는 챔버 내에서 점화된 제1 플라즈마에서 생성되는, 방법.

#### 청구항 5

제1항 또는 제2항에 있어서,

상기 산소 빈자리들을 채우기 위해 상기 금속 산화물 반도체 층을 상기 제1 불소 라디칼들에 노출시키는

단계는,

원격 플라즈마 소스 내로 불소 함유 가스를 유동시키는 단계 – 상기 불소 함유 가스는, 2000 sccm(standard cubic centimeters per minute) 내지 6000 sccm의 범위의 유량을 가짐 –;

상기 원격 플라즈마 소스에서 산소 및 실리콘 없는 불소 함유 플라즈마를 형성하는 단계 – 상기 원격 플라즈마 소스는, 0.2 W/cm<sup>2</sup> 내지 0.6 W/cm<sup>2</sup>의 범위의 전력 밀도를 가짐 –; 및

프로세싱 영역 내로 상기 불소 함유 플라즈마를 유동시키는 단계 – 상기 기판은, 섭씨 150 도 내지 섭씨 350 도의 범위의 온도를 가짐 –;

를 포함하는, 방법.

## 청구항 6

제5항에 있어서,

상기 산소 빙자리들을 채우기 위해 상기 금속 산화물 반도체 층을 상기 제1 불소 라디칼들에 노출시키는 단계는

플라즈마 강화 화학 기상 증착 챔버에서 수행되고, 상기 플라즈마 강화 화학 기상 증착 챔버 내부의 압력은 200 mTorr 내지 900 mTorr의 범위인, 방법.

## 청구항 7

방법으로서,

기판 위에 게이트 전극을 형성하는 단계;

상기 게이트 전극 위에 게이트 유전체 층을 증착하는 단계;

상기 게이트 유전체 층 위에 금속 산화물 반도체 층을 증착하는 단계; 그 다음,

산소 빙자리들을 채우기 위해 상기 금속 산화물 반도체 층을 어닐링하는 단계; 그 다음,

상기 금속 산화물 반도체 층을 제1 불소 함유 가스에 노출시키는 단계; 및 그 다음,

상기 금속 산화물 반도체 층 위에 전도성 층을 증착하는 단계를 포함하고,

상기 방법은 상기 금속 산화물 반도체 층을 어닐링하는 단계 이전에 산소 빙자리들을 채우기 위해 상기 금속 산화물 반도체 층을 제2 불소 함유 가스에 노출시키는 단계를 더 포함하는, 방법.

## 청구항 8

제7항에 있어서,

상기 제1 불소 함유 가스는 NF<sub>3</sub>, CF<sub>4</sub>, 또는 F<sub>2</sub>를 포함하는, 방법.

## 청구항 9

방법으로서,

기판 위에 금속 산화물 층을 증착하는 단계;

상기 금속 산화물 층을 제1 불소 라디칼들 또는 제1 불소 함유 가스에 노출시키는 단계;

상기 금속 산화물 층 상에 게이트 유전체 층을 증착하는 단계;

상기 금속 산화물 층 위에 층간(inter-layer) 유전체 층을 증착하는 단계;

상기 층간 유전체 층 상에 금속 층을 증착하는 단계;

상기 금속 산화물 층을 상기 제1 불소 라디칼들 또는 상기 제1 불소 함유 가스에 노출시키는 단계 이후에 상기 금속 산화물 층을 예칭하는 단계; 및,

상기 금속 산화물 층을 예칭하는 단계 이후에 상기 금속 산화물 층을 제2 불소 라디칼들 또는 제2 불소 함유 가스에 노출시키는 단계를 포함하며, 상기 제2 불소 라디칼들은 제2 원격 플라즈마에서 생성되는, 방법.

**청구항 10**

방법으로서,

기판 위에 금속 산화물 층을 증착하는 단계;

상기 금속 산화물 층을 제1 불소 라디칼들 또는 제1 불소 함유 가스에 노출시키는 단계;

상기 금속 산화물 층 상에 게이트 유전체 층을 증착하는 단계;

상기 금속 산화물 층 위에 충간 유전체 층을 증착하는 단계;

상기 충간 유전체 층 상에 금속 층을 증착하는 단계;

상기 금속 산화물 층을 상기 제1 불소 라디칼들 또는 상기 제1 불소 함유 가스에 노출시키는 단계 이후에 상기 금속 산화물 층을 예칭하는 단계; 및

상기 금속 산화물 층을 예칭하는 단계 이후에 상기 금속 산화물 층을 제2 불소 라디칼들 또는 제2 불소 함유 가스에 노출시키는 단계를 포함하며, 상기 제2 불소 라디칼들은 상기 금속 산화물 층이 배치되는 챔버 내에서 점화된 제2 플라즈마에서 생성되는, 방법.

**청구항 11**

제9항 또는 제10항에 있어서,

상기 제1 불소 라디칼들은 제1 원격 플라즈마에서 생성되는, 방법.

**청구항 12**

제9항 또는 제10항에 있어서,

상기 제1 불소 라디칼들은 상기 금속 산화물 층이 배치되는 챔버 내에서 점화된 제1 플라즈마에서 생성되는, 방법.

**청구항 13**

삭제

**청구항 14**

삭제

**청구항 15**

삭제

**청구항 16**

삭제

**청구항 17**

삭제

**청구항 18**

삭제

**발명의 설명****기술 분야**

[0001] 본 개시내용의 실시예들은 일반적으로 박막 트랜지스터(TFT; thin film transistor)를 형성하기 위한 방법들에 관한 것으로, 더 구체적으로는, 금속 산화물 층을 갖는 TFT를 형성하기 위한 방법들에 관한 것이다.

## 배경 기술

[0002]

[0002] 아연 산화물(ZnO) 및 인듐 갈륨 아연 산화물(IGZO)과 같은 금속 산화물 반도체들은, 그들의 높은 캐리어 이동도(mobility), 낮은 프로세싱 온도들, 및 광학적 투명성으로 인해 디바이스에 제조에 있어 매력적이다. 금속 산화물 반도체(MO-TFT)들로 제조된 TFT들은, 광학 디스플레이들을 위한 액티브-메트릭스 어드레싱 방식(active-matrix addressing scheme)들에서 특히 유용하다. 금속 산화물 반도체들의 낮은 프로세싱 온도는, 폴리에틸렌 테레프탈레이트(PET) 및 폴리에틸렌 나프탈레이트(PEN)와 같은 비싸지 않은 플라스틱 기판들 상에서의 디스플레이 백플레인(backplane)들의 형성을 허용한다. 산화물 반도체 TFT들의 투명성은, 개선된 굀셀 애퍼처(aperture)들 및 더 밝은 디스플레이들을 초래한다.

[0003]

[0003] 그러나, 금속 산화물 층, 이를테면 금속 산화물 채널 층은, 층 내의 산소 빈자리(vacancy)들의 형성에 취약하며, 산소 빈자리들의 형성은 불안정한 TFT들을 초래한다. 게다가, 산소 빈자리들의 형성은 또한, 산소 빈자리들이 금속 산화물 재료들의 공여체(donor)들이므로, 네거티브(negative) 임계 전압을 야기한다.

[0004]

[0004] 따라서, 안정된 금속 산화물 TFT들을 형성하기 위한 당업계의 필요성이 존재한다.

## 발명의 내용

[0005]

[0005] 본 개시내용의 실시예들은 일반적으로, 금속 산화물 층을 갖는 TFT를 형성하기 위한 방법들에 관한 것이다. 방법은, 금속 산화물 층을 형성하는 단계, 및 불소 함유 가스 또는 플라즈마로 금속 산화물 층을 처리하는 단계를 포함할 수 있다. 금속 산화물 층의 불소 처리는 금속 산화물 채널 층 내의 임의의 산소 빈자리들을 채우며, 이는, 더 안정된 TFT를 초래하고 TFT에서의 네거티브 임계 전압을 방지한다.

[0006]

[0006] 일 실시예에서, 방법은, 기판 위에 게이트 전극을 형성하는 단계, 게이트 전극 위에 게이트 유전체 층을 증착하는 단계, 게이트 유전체 층 위에 금속 산화물 층을 증착하는 단계, 제1 원격 플라즈마를 생성하는 단계, 제1 불소 라디칼(radical)들로 금속 산화물 층을 처리하는 단계, 및 금속 산화물 층 위에 전도성 층을 증착하는 단계를 포함한다.

[0007]

[0007] 다른 실시예에서, 방법은, 기판 위에 금속 산화물 층을 증착하는 단계, 제1 불소 라디칼들 또는 제1 불소 함유 가스로 금속 산화물 층을 처리하는 단계, 금속 산화물 층 상에 게이트 유전체 층을 증착하는 단계, 금속 산화물 층 위에 층간(inter-layer) 유전체 층을 증착하는 단계, 및 층간 유전체 층 상에 금속 층을 증착하는 단계를 포함한다.

[0008]

[0008] 다른 실시예에서, 방법은, 기판 위에 게이트 전극을 형성하는 단계, 게이트 전극 위에 게이트 유전체 층을 증착하는 단계, 게이트 유전체 층 위에 금속 산화물 층을 증착하는 단계, 불소 함유 가스로 금속 산화물 층을 처리하는 단계, 및 금속 산화물 층 위에 전도성 층을 증착하는 단계를 포함한다.

## 도면의 간단한 설명

[0009]

[0009] 본 개시내용의 상기 인용된 특징들이 상세하게 이해될 수 있는 방식으로, 위에서 간략하게 요약된 본 개시내용의 보다 구체적인 설명이 실시예들을 참조하여 이루어질 수 있으며, 이러한 실시예들 중 일부가 첨부된 도면들에 예시되어 있다. 하지만, 첨부된 도면들은 본 개시내용의 단지 통상적인 실시예들을 예시하는 것이므로 본 개시내용의 범위를 제한하는 것으로 간주되지 않아야 한다는 것이 유의되어야 하는데, 이는 본 개시내용이 다른 균등하게 유효한 실시예들을 허용할 수 있기 때문이다.

[0010] 도 1은 본원에 개시된 실시예들에 따른 물리 기상 증착 챕터의 개략적인 횡단면도이다.

[0011] 도 2는 본원에 개시된 실시예들에 따른 플라즈마 강화 화학 기상 증착 챕터의 개략적인 횡단면도이다.

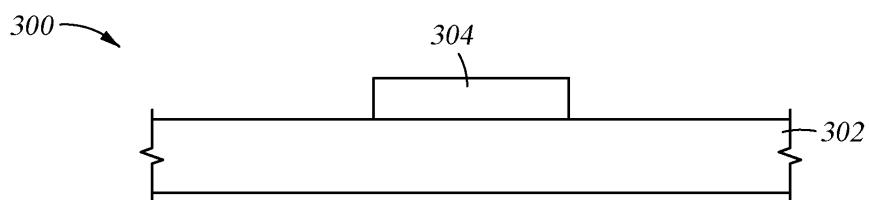

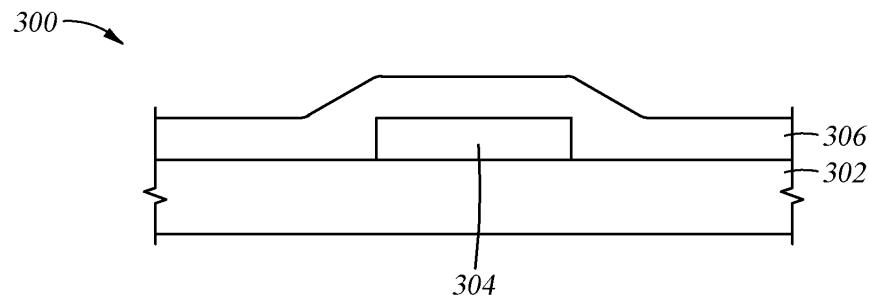

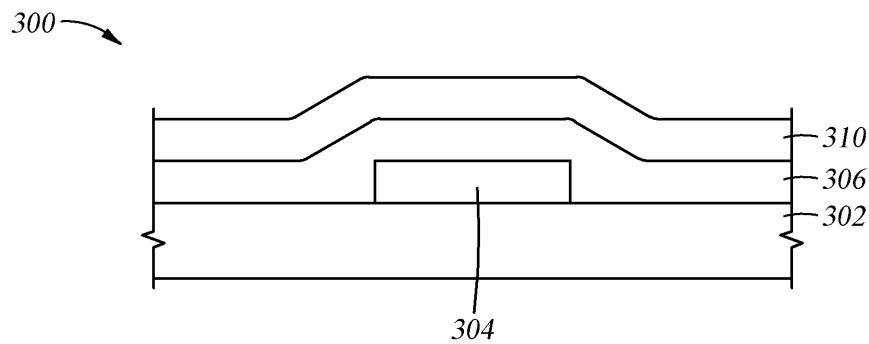

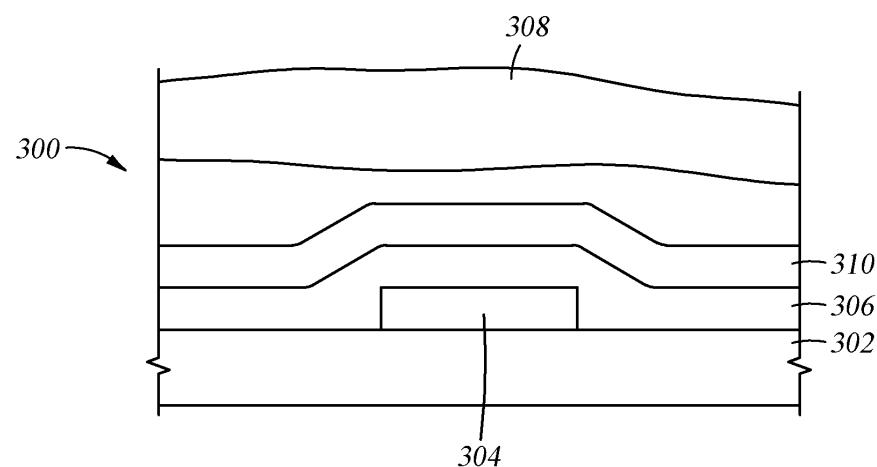

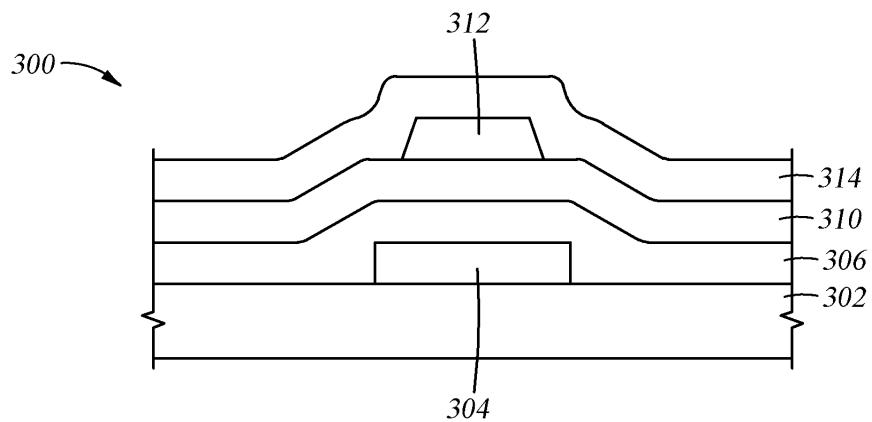

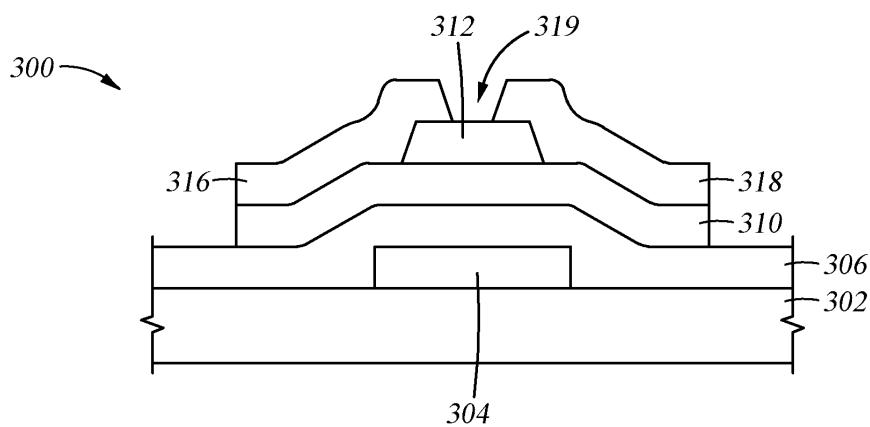

[0012] 도 3a-3g는 본원에 개시된 실시예들에 따른 제조의 다양한 스테이지들에서의 TFT의 개략적인 횡단면도들이다.

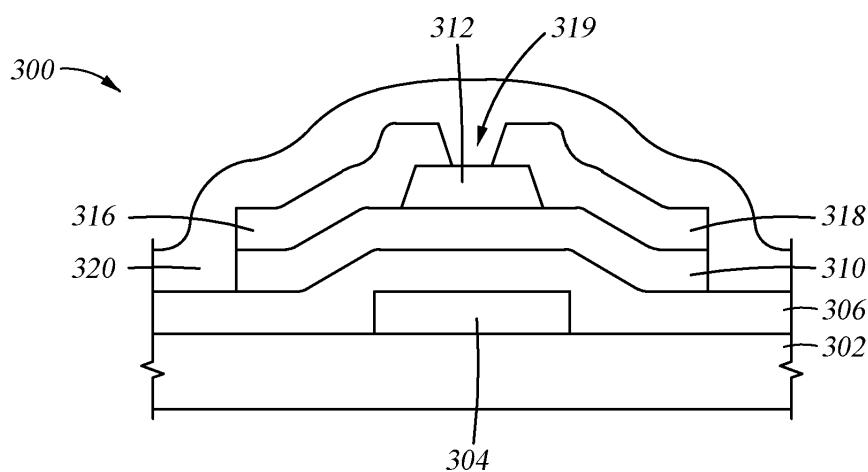

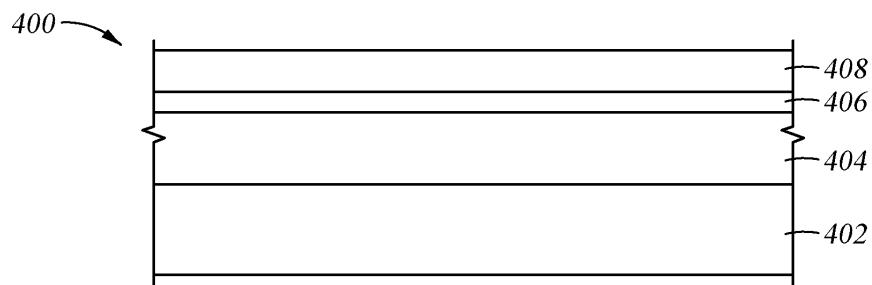

[0013] 도 4a-4f는 본원에 개시된 실시예들에 따른 제조의 다양한 스테이지들에서의 TFT의 개략적인 횡단면도들이다.

[0014] 도 5a-5c는 본원에 개시된 실시예들에 따라 도 3a-3g에 도시된 TFT를 형성하기 위한 프로세스들을 도시하는 흐름도들이다.

[0015] 이해를 용이하게 하기 위해, 가능한 모든 경우에, 도면들에 대해 공통된 동일한 엘리먼트들을 지정하기

위해 동일한 참조 번호들이 사용되었다. 부가적으로, 일 실시예의 엘리먼트들은, 본원에서 설명되는 다른 실시 예들에서의 활용을 위해 유리하게 적응될 수 있다.

### 발명을 실시하기 위한 구체적인 내용

[0010]

[0016] 본 개시내용의 실시예들은 일반적으로, 금속 산화물 층을 갖는 TFT를 형성하기 위한 방법들에 관한 것이다. 방법은, 금속 산화물 층을 형성하는 단계, 및 불소 함유 가스 또는 플라즈마로 금속 산화물 층을 처리하는 단계를 포함할 수 있다. 금속 산화물 층의 불소 처리는 금속 산화물 채널 층 내의 산소 빈자리들을 채우는 것을 도우며, 이는, 더 안정된 TFT를 초래하고 TFT에서의 네거티브 임계 전압을 방지한다.

[0011]

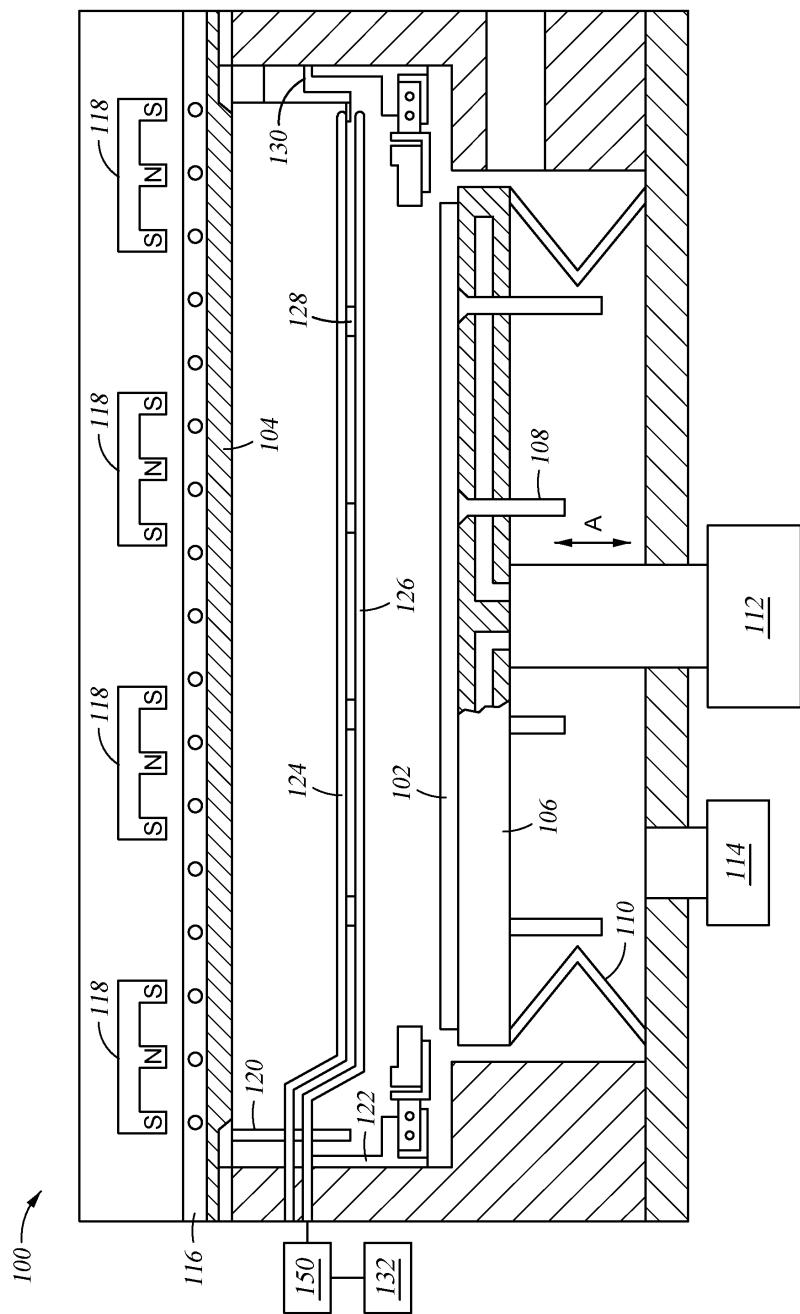

[0017] 도 1은 본원에 개시된 실시예들에 따른 물리 기상 증착(PVD) 챔버(100)의 개략적인 횡단면도이다. 챔버(100)는 진공 펌프(114)에 의해 진공배기(evacuate)될 수 있다. 챔버(100) 내에서, 기판(102)은 타겟(target)(104)에 대향하게 배치될 수 있다. 기판(102)은, 챔버(100) 내에서 서셉터(susceptor)(106) 상에 배치될 수 있다. 서셉터(106)는, 액추에이터(actuator)(112)에 의해, 화살표들("A")로 도시된 바와 같이 상승 및 하강될 수 있다. 서셉터(106)는, 기판(102)을 프로세싱 포지션으로 상승시키도록 상승될 수 있고 그리고 기판(102)이 챔버(100)로부터 제거될 수 있도록 하강될 수 있다. 리프트 핀(lift pin)들(108)은, 서셉터(106)가 하강된 포지션에 있을 때 서셉터(106) 위로 기판(102)을 상승시킨다. 프로세싱 동안 접지 스트랩(strap)들(110)이 서셉터(106)를 접지시킬 수 있다. 서셉터(106)는, 균일한 증착에 도움이 되도록 프로세싱 동안 상승될 수 있다.

[0012]

[0018] 타겟(104)은 하나 이상의 타겟들을 포함할 수 있다. 일 실시예에서, 타겟(104)은 대면적 스퍼터링 타겟일 수 있다. 다른 실시예에서, 타겟(104)은 복수의 타일(tile)들일 수 있다. 또 다른 실시예에서, 타겟(104)은 복수의 타겟 스트립(strip)들일 수 있다. 또 다른 실시예에서, 타겟(104)은 하나 이상의 원통형 로터리(rotary) 타겟들일 수 있다. 타겟(104)은, 본딩(bonding) 층(도시되지 않음)에 의해 백킹(backing) 플레이트(116)에 본딩될 수 있다. 백킹 플레이트(116) 위에 하나 이상의 마그네트론(magnetron)들(118)이 배치될 수 있다. 마그네트론들(118)은, 선형 운동 또는 2 차원 경로로 백킹 플레이트(116)를 가로질러 스캐닝할 수 있다. 챔버의 벽들은, 암공간 차폐부(dark space shield)(120) 및 챔버 차폐부(122)에 의해 증착으로부터 차폐될 수 있다.

[0013]

[0019] 기판(102)에 걸쳐 균일한 스퍼터링 증착을 제공하는 것을 돋기 위해, 타겟(104)과 기판(102) 사이에 애노드(anode)(124)가 배치될 수 있다. 일 실시예에서, 애노드(124)는, 아크 스프레이팅된(arc sprayed) 알루미늄으로 코팅된, 비드 블래스팅된(bead blasted) 스테인리스 강일 수 있다. 일 실시예에서, 애노드(124)의 일 일부는, 브래킷(bracket)(130)에 의해 챔버 벽에 장착될 수 있다. 애노드(124)는, 하천된 이온들이 통상적으로 접지 전위에 있는 챔버 벽들보다는 타겟에 끌어당겨지도록, 타겟(104)과 반대인 전하를 제공한다. 타겟(104)과 기판(102) 사이에 애노드(124)를 제공함으로써, 플라즈마가 더 균일할 수 있고, 이는 증착에 도움이 될 수 있다. 박피를 감소시키기 위해, 하나 이상의 애노드들(124)을 통해 냉각 유체가 제공될 수 있다. 애노드들(124)의 팽창 및 수축의 양을 감소시킴으로써, 애노드들(124)로부터의 재료의 박피가 감소될 수 있다. 더 작은 기판들 및 그에 따른 더 작은 프로세싱 챔버들의 경우, 챔버 벽들이 접지를 위한 경로 및 균일한 플라즈마 분포를 제공하기에 충분할 수 있으므로, 프로세싱 공간에 걸쳐 있는 애노드들(124)은 필요하지 않을 수 있다.

[0014]

[0020] 반응성 스퍼터링의 경우, 챔버(100) 내에 반응성 가스를 제공하는 것이 유익할 수 있다. 하나 이상의 가스 도입 투브들(126)이 또한 타겟(104)과 기판(102) 사이에서 챔버(100)를 가로지르는 거리에 걸쳐 있을 수 있다. 더 작은 기판들 및 그에 따른 더 작은 챔버들의 경우, 심지어 종래의 가스 도입 수단을 통해 가스 분배가 가능할 수 있으므로, 프로세싱 공간에 걸쳐 있는 가스 도입 투브들(126)은 필요하지 않을 수 있다. 가스 도입 투브들(126)은, 가스 패널(132)로부터 스퍼터링 가스들을 도입할 수 있다. 일부 실시예들에서, 가스 도입 투브들(126)과 가스 패널(132) 사이에 원격 플라즈마 소스(150)가 커플링될 수 있고, 가스 도입 투브들(126)은, 원격 플라즈마 소스(150)에 의해 생성되는 원격 플라즈마를 챔버(100) 내로 도입하는 데 사용될 수 있다. 가스 도입 투브들(126)은, 하나 이상의 커플링들(128)에 의해 애노드들(124)과 커플링될 수 있다. 커플링(128)은, 가스 도입 투브들(126)이 전도식으로(conductively) 냉각되는 것을 허용하기 위해 열 전도성 재료로 제조될 수 있다. 부가적으로, 가스 도입 투브들(126)이 접지되고 애노드들로서 기능하도록, 커플링(128)이 또한 전기 전도성을 갖을 수 있다.

[0015]

[0021] 반응성 스퍼터링 프로세스는, PVD 챔버(100) 내의 기판에 대향하게 아연 스퍼터링 타겟을 배치하는 것을 포함할 수 있다. 아연 스퍼터링 타겟은 실질적으로, 아연, 또는 아연과 도핑 엘리먼트를 포함할 수 있다.

사용될 수 있는 적절한 도편트(dopant)들은, Al, Sn, Ga, Ca, Si, Ti, Cu, Ge, In, Ni, Mn, Cr, V, Mg, Si<sub>x</sub>N<sub>y</sub>, Al<sub>x</sub>O<sub>y</sub>, 및 SiC를 포함한다. 일 실시예에서, 도편트는 알루미늄을 포함한다. 반면, 기판은, 플라스틱, 종이, 폴리머, 유리, 스테인리스 강, 및 이들의 조합들일 수 있다. 기판이 플라스틱일 때, 약 섭씨 180 도 미만의 온도에서 반응성 스퍼터링이 발생할 수 있다.

[0016] [0022] 스퍼터링 프로세스 동안, 아르곤, 질소 함유 가스, 및 산소 함유 가스가 아연 타겟을 반응성 스퍼터링 하기 위해 챔버에 제공될 수 있다. B<sub>2</sub>H<sub>6</sub>, CO<sub>2</sub>, CO, CH<sub>4</sub> 및 이들의 조합들과 같은 부가적인 첨가제(additive)들이 또한 스퍼터링 동안 챔버에 제공될 수 있다. 일 실시예에서, 질소 함유 가스는 N<sub>2</sub>를 포함한다. 다른 실시예에서, 질소 함유 가스는 N<sub>2</sub>O, NH<sub>3</sub>, 또는 이들의 조합들을 포함한다. 일 실시예에서, 산소 함유 가스는 O<sub>2</sub>를 포함한다. 다른 실시예에서, 산소 함유 가스는 N<sub>2</sub>O를 포함한다. 질소 함유 가스의 질소 및 산소 함유 가스의 산소는, 스퍼터링 타겟으로부터의 아연과 반응하여 아연, 산소, 및 질소를 포함하는 금속 산화물 층을 기판 상에 형성한다. 일 실시예에서, 금속 산화물 층은 IGZO 층이다.

[0017] [0023] 금속 산화물 층의 형성 이후, 금속 산화물 층은, PVD 챔버(100)에서 불소 함유 가스 또는 플라즈마에 의해 처리될 수 있다. 불소 함유 가스는, 가스 패널(132)에 의해 PVD 챔버(100)에 도입될 수 있다. 불소 함유 가스는, 임의의 적절한 불소 함유 가스, 이를테면 NF<sub>3</sub>, CF<sub>4</sub> 또는 F<sub>2</sub>를 포함할 수 있다. 불소 함유 플라즈마는, 원격 플라즈마 소스(150)에 의해 PVD 챔버(100)에 도입되는 원격 플라즈마일 수 있다. 불소 함유 가스, 이를테면, NF<sub>3</sub>, CF<sub>4</sub>, F<sub>2</sub>, 또는 임의의 적절한 불소 함유 가스가 가스 패널(132)로부터 원격 플라즈마 소스(150) 내로 유동될 수 있고 그리고 불소 라디칼들을 갖는 불소 함유 플라즈마를 형성하도록 여기(excite)될 수 있다. 불소 함유 플라즈마는, 가스 도입 튜브들(126)을 통해 금속 산화물 층을 처리하는 데 사용될 수 있다.

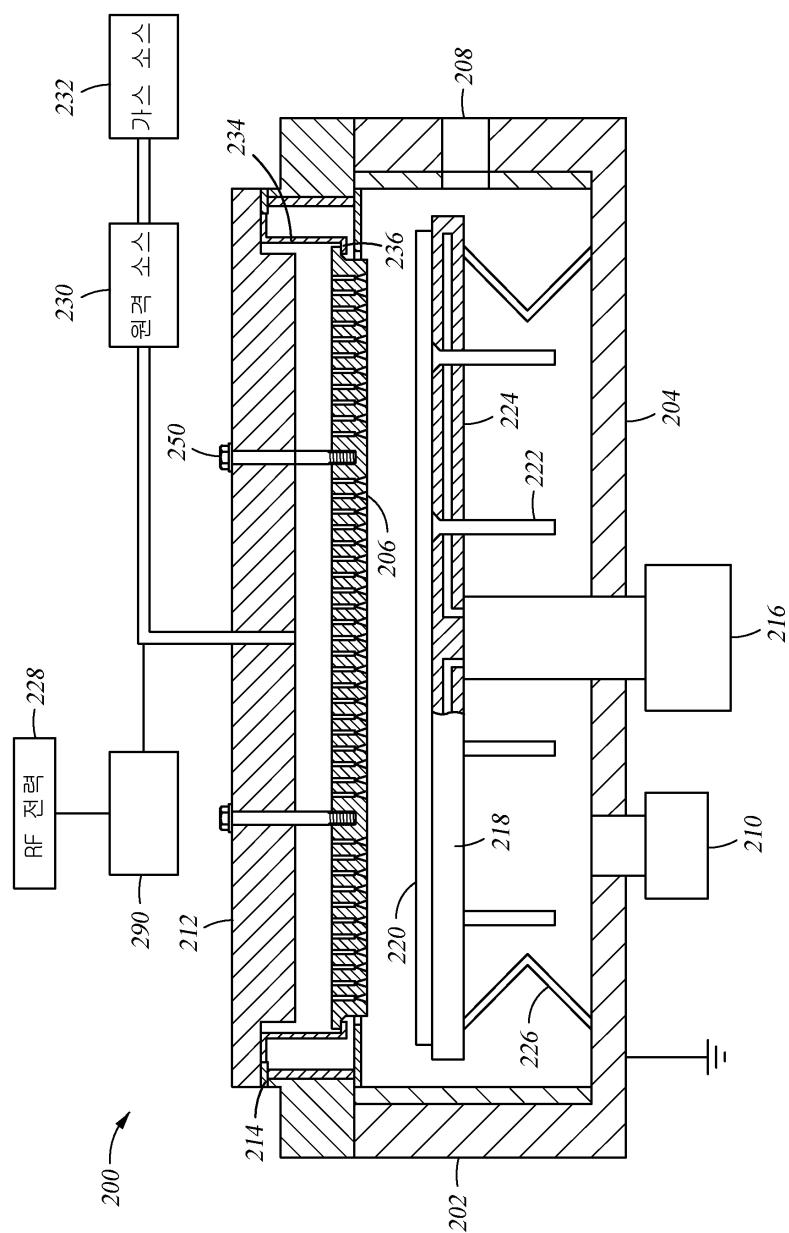

[0018] [0024] 도 2는 본원에 개시된 실시예들에 따른 플라즈마 강화 화학 기상 증착(PECVD) 챔버(200)의 개략적인 횡 단면도이다. PECVD 챔버(200)는 일반적으로, 프로세스 볼륨을 정의하는, 벽들(202), 최하부(204), 및 샤워헤드(showerhead)(206)를 포함한다. 프로세스 볼륨 내에 기판 지지부(218)가 배치된다. 프로세스 볼륨은, 기판(220)이 PECVD 챔버(200) 안팎으로 이송될 수 있도록, 슬릿 벨브 개구(208)를 통해 액세스된다. 기판 지지부(218)는, 기판 지지부(218)를 상승 및 하강시키기 위해 액추에이터(216)에 커플링될 수 있다. 기판(220)을 기판 지지부(218)의 기판 수용 표면으로 또는 그로부터 이동시키기 위해, 기판 지지부(218)를 통해 리프트 핀들(222)이 이동가능하게 배치된다. 기판 지지부(218)는 또한, 기판 지지부(218)를 미리결정된 온도에서 유지하기 위해, 가열 및/또는 냉각 엘리먼트들(224)을 포함할 수 있다. 기판 지지부(218)는 또한, 기판 지지부(218)의 주변부에 RF 복귀 경로를 제공하기 위해, RF 복귀(return) 스트랩들(226)을 포함할 수 있다.

[0019] [0025] 샤워헤드(206)는, 체결 메커니즘(250)에 의해 백킹(backing) 플레이트(212)에 커플링된다. 샤워헤드(206)는, 샤워헤드(206)의 처짐(sag)을 방지하고 그리고/또는 진직도/곡률(straightness/curvature)을 제어하는 것을 돋기 위해, 하나 또는 그 초과의 체결 메커니즘들(250)에 의해 백킹 플레이트(212)에 커플링될 수 있다.

[0020] [0026] 샤워헤드(206)의 가스 통로들을 통해 샤워헤드(206)와 기판(220) 사이의 프로세싱 영역으로 가스를 제공하기 위해, 가스 소스(232)가 백킹 플레이트(212)에 커플링된다. 미리결정된 압력에서 프로세스 볼륨을 제어하기 위해, 진공 펌프(210)가 PECVD 챔버(200)에 커플링된다. 샤워헤드(206)에 RF 전류를 제공하기 위해, RF 소스(228)가 매치(match) 네트워크(290)를 통해 백킹 플레이트(212)에 그리고/또는 샤워헤드(206)에 커플링된다. RF 전류는, 샤워헤드(206)와 기판 지지부(218) 사이의 가스들로부터 플라즈마가 생성될 수 있도록, 샤워헤드(206)와 기판 지지부(218) 사이에 전기장을 생성한다. 일 실시예에서, 가스 소스(232)에 의해 불소 함유 가스가 프로세싱 영역에 제공되고, 불소 함유 가스는, 기판(220) 상의 금속 산화물 층을 처리하는 데 사용될 수 있다. 다른 실시예에서, 불소 함유 가스는, 샤워헤드(206)에 제공되는 RF 소스(228)에 의해 여기되어 프로세싱 영역에 불소 함유 플라즈마를 형성할 수 있으며, 기판(220) 상의 금속 산화물 층을 처리하기 위해 불소 라디칼들이 사용될 수 있다.

[0021] [0027] 가스 소스(232)와 백킹 플레이트(212) 사이에 원격 플라즈마 소스(230), 이를테면 유도성으로 커플링된 원격 플라즈마 소스(230)가 또한 커플링될 수 있다. 기판들을 프로세싱하는 사이에, 원격 플라즈마 소스(230)에 세정 가스가 제공되어 원격 플라즈마가 생성될 수 있다. 원격 플라즈마로부터의 라디칼들은 PECVD 챔버(200)에 제공되어 PECVD 챔버(200) 컴포넌트들을 세정할 수 있다. 세정 가스는, 샤워헤드(206)에 제공되는 RF 소스(228)에 의해 추가로 여기될 수 있다. 일부 실시예들에서, 원격 플라즈마 소스(230)는, 불소 함유 플라즈

마를 형성하기 위해 불소 함유 가스를 여기시키는 데 사용될 수 있으며, 원격으로 형성된 불소 함유 플라즈마가 샤크헤드(206)를 통해 프로세싱 영역에 진입할 수 있다. 원격으로 형성된 불소 함유 플라즈마의 불소 라디칼들이 기판(220) 상의 금속 산화물 층을 처리하는 데 사용될 수 있다.

[0022] 샤크헤드(206)는, 샤크헤드 서스펜션(suspension)(234)에 의해 백킹 플레이트(212)에 부가적으로 커플링될 수 있다. 일 실시예에서, 샤크헤드 서스펜션(234)은 플렉서블 금속 스커트(flexible metal skirt)이다. 샤크헤드 서스펜션(234)은, 그 위에 샤크헤드(206)가 놓일 수 있는 립(lip)(236)을 가질 수 있다. 백킹 플레이트(212)는, PECVD 챔버(200)를 시일링(seal)하도록 벽들(202)과 커플링되는 엣지(ledge)(214)의 상부 표면 상에 놓일 수 있다.

[0023] 도 3a-3g는 본원에 개시된 실시예들에 따른 제조의 다양한 스테이지들에서의 TFT(300)의 개략적인 횡단면도들이다. TFT(300)는 기판(302)을 포함할 수 있다. 일 실시예에서, 기판(302)은 유리일 수 있다. 다른 실시예에서, 기판(302)은 폴리머일 수 있다. 다른 실시예에서, 기판(302)은 플라스틱일 수 있다. 또 다른 실시예에서, 기판(302)은 금속, 이를테면 스테인리스 강 시트일 수 있다.

[0024] 기판 위에, 게이트 전극(304)이 형성될 수 있다. 게이트 전극(304)과 기판(302) 사이에 열 산화물 층이 있을 수 있다. 게이트 전극(304)은, TFT(300) 내의 전하 캐리어들의 이동을 제어하는 전기 전도성 층일 수 있다. 게이트 전극(304)은, 알루미늄, 몰리브덴, 텉스텐, 크롬, 탄탈룸, 또는 이들의 조합들과 같은 금속으로 제조될 수 있다. 게이트 전극(304)은, 스퍼터링, 리소그래피, 및 에칭을 포함하는 종래의 증착 기법들을 사용하여 형성될 수 있다. 게이트 전극(304)은, 기판(302) 위에 전도성 층을 증착하는 블랭킷(blanket)에 의해 형성될 수 있다. 전도성 층은, 스퍼터링에 의해 증착될 수 있다. 그 후, 전도성 층 위에 포토레지스트 층이 증착될 수 있다. 포토레지스트 층은 패터닝(pattern)되어 마스크를 형성할 수 있다. 게이트 전극(304)은, 전도성 층의 마스킹되지 않은(unmasked) 부분들을 에칭하여 제거(etching away)하여, 기판(302) 위에 게이트 전극(304)을 남김으로써 형성될 수 있다.

[0025] 도 3b에 도시된 바와 같이, 게이트 전극(304) 위에, 게이트 유전체 층(306)이 증착될 수 있다. 게이트 유전체 층(306)은, 게이트 전극(304) 상에 직접 증착될 수 있다. 게이트 유전체 층(306)은, TFT(300)의 서브 임계 스윙(swing) 또는 슬로프(slope) 및 임계 전압( $V_{th}$ )에 영향을 미친다. 실리콘 기반 TFT들(즉, 비정질 실리콘과 같은 실리콘 기반 반도체 층을 갖는 TFT들)의 경우, 게이트 유전체 층(306)은, TFT가 불량하게 수행되는 것을 야기하는 게이트 전압의 제로 볼트로부터  $V_{th}$ 가 멀리 떨어져 있기 때문에, 실리콘 산화물을 포함할 수 없다. 그러나, 금속 산화물 TFT들의 경우, 실리콘 산화물이 유효 게이트 유전체 층(306)으로서 기능할 수 있다는 것을 알게 되었다. 실리콘 산화물 내의 산소가 금속 산화물 층을 불리하게 변경하지 않을 수 있으며, 그에 따라, TFT가 실패하지 않을 수 있다. 일 실시예에서, 게이트 유전체 층(306)은 실리콘 질화물을 포함할 수 있다. 다른 실시예에서, 게이트 유전체 층(306)은 실리콘 산화물을 포함할 수 있다. 다른 실시예에서, 게이트 유전체 층(306)은 실리콘 산질화물을 포함할 수 있다. 다른 실시예에서, 게이트 유전체 층(306)은  $\text{Al}_2\text{O}_3$ 을 포함할 수 있다. 게이트 유전체 층(306)은, PECVD를 포함하는 잘 알려진 증착 기법들에 의해 증착될 수 있다. 일 실시예에서, 게이트 유전체 층(306)은 PVD에 의해 증착될 수 있다.

[0026] 도 3c에 도시된 바와 같이, 금속 산화물 층(310)은, 게이트 유전체 층(306) 상에 그와 직접 접촉하도록 증착될 수 있다. 금속 산화물 층(310)은, 최종 TFT 구조에서의 능동(active) 채널일 수 있다. 금속 산화물 층(310)은, 산소, 질소, 및 아연, 갈륨, 카드뮴, 인듐, 주석, 및 이들의 조합들로 이루어진 그룹으로 선택되는 하나 이상의 엘리먼트들을 포함할 수 있다. 일 실시예에서, 금속 산화물 층(310)은  $\text{ZnO}$ 를 포함할 수 있다. 일 실시예에서, 금속 산화물 층(310)은 IGZO이다. 금속 산화물 층(310)은, 도 1에 도시된 PVD 챔버(100)를 사용하여 스퍼터링에 의해 증착될 수 있다.

[0027] 금속 산화물 층(310)이 증착된 후, 금속 산화물 층(310) 상에서 어닐링(annealing) 프로세스가 수행될 수 있다. 어닐링 프로세스는, 금속 산화물 층(310)이 증착되는 챔버에서 수행될 수 있다. 어닐링 프로세스는, 상부에 금속 산화물 층(310)이 배치된 기판의 온도를, 기판의 표면에 걸쳐 공기(air)를 유동시키면서 약 한 시간 동안 약 섭씨 350 도로 유지하는 것을 포함할 수 있다. 어닐링 프로세스 이전 또는 이후에, 산소가 금속 산화물 층(310)로부터 벗어나 산소 빙자리들을 형성할 수 있다. 산소 빙자리들을 채우고 그리고/또는 금속 산화물 층(310)로부터 산소가 벗어나는 것을 방지하기 위해, 금속 산화물 층(310)은 불소 함유 가스 또는 플라즈마에 의해 처리될 수 있다.

[0028] 금속 산화물 층(310)의 처리는, 도 3d에 도시된 바와 같이, 불소 함유 가스 또는 플라즈마(308)에 금속

산화물 층(310)을 노출시키는 것을 포함할 수 있다. 산소 빈자리들을 불소 함유 가스로부터의 불소 가스 분자들 또는 불소 함유 플라즈마로부터의 불소 라디칼들이 채울 수 있고, 이들은 금속 산화물 층(310)을 부동화(passivate)시켜 산소 분자들이 금속 산화물 층(310)을 벗어나는 것을 방지할 수 있다. 금속 산화물 층(310)의 처리 프로세스는, 금속 산화물 층(310)의 표면 상에 재료의 층을 형성하지 않는다. 처리 프로세스는, 금속 산화물 층(310) 내에 불소 가스 분자들 또는 불소 라디칼들을 확산(diffuse)시키는 것을 포함할 수 있다. 일 실시예에서, 금속 산화물 층(310)은, 불소 함유 가스, 이를테면  $\text{NF}_3$ ,  $\text{CF}_4$ ,  $\text{F}_2$ , 또는 임의의 적절한 불소 함유 가스에 노출될 수 있다. 불소 함유 가스는, 산소가 없거나 실리콘이 없을 수 있다. 다른 실시예에서, 금속 산화물 층(310)은, 불소 라디칼들을 포함하는 플라즈마에 노출될 수 있다. 불소 함유 플라즈마는 원격으로 또는 인 시튜(in situ)로 형성될 수 있다. 불소 함유 플라즈마는, 금속 산화물 층(310)이 배치되는 프로세스 챔버 또는 원격 플라즈마 소스 내로 불소 함유 가스, 이를테면  $\text{NF}_3$ ,  $\text{CF}_4$ ,  $\text{F}_2$ , 또는 임의의 적절한 불소 함유 가스를 유동시킴으로써 형성될 수 있다. 그런 다음, RF 전력에 의해 불소 함유 가스가 여기되고, 프로세스 챔버의 외부에(즉, 원격으로) 또는 프로세스 챔버의 내부에(즉, 인 시튜로) 불소 함유 플라즈마가 형성된다. 불소 함유 플라즈마는, 산소가 없거나 실리콘이 없을 수 있다.

[0029] [0035] 불소 함유 가스 또는 플라즈마에 의한 금속 산화물 층(310)의 처리 시간, 즉, 금속 산화물 층(310)이 불소 함유 가스 또는 불소 함유 플라즈마에 노출되는 시간은, 약 10 초 내지 약 100 초, 이를테면 약 20 초 내지 약 60 초의 범위일 수 있다. 금속 산화물 층(310)의 처리는, 금속 산화물 층(310)이 증착되는 챔버, 이를테면 도 1에 도시된 PVD 챔버(100)에서 수행될 수 있다. 대안적으로, 금속 산화물 층(310)의 처리는, 후속 층이 증착되는 챔버, 이를테면 도 2에 도시된 PECVD 챔버(200)에서 수행될 수 있다. 일 실시예에서, 금속 산화물 층(310)은, 원격 플라즈마를 사용하여 PECVD 챔버(200)와 유사한 PECVD 챔버에서 처리된다. 이러한 실시예에서,  $\text{NF}_3$  및 Ar 가스들이 원격 플라즈마 소스, 이를테면 원격 플라즈마 소스(230)로 유동된다.  $\text{NF}_3$  가스는 약 2000 sccm(standard cubic centimeters per minute) 내지 약 6000 sccm의 범위의 유량을 가질 수 있고, Ar 가스는 약 2000 sccm 내지 약 6000 sccm의 범위의 유량을 가질 수 있다. 일 실시예에서,  $\text{NF}_3$  가스 유량 및 Ar 가스 유량 둘 모두가 4000 sccm이다. 원격 플라즈마 소스는, 약  $0.2 \text{ W/cm}^2$  내지 약  $0.6 \text{ W/cm}^2$ 의 범위, 이를테면 약  $0.4 \text{ W/cm}^2$ 의 전력 밀도를 가질 수 있다. PECVD 챔버 내부의 압력은, 약 200 mTorr 내지 약 900 mTorr, 이를테면 약 500 mTorr 내지 약 600 mTorr의 범위일 수 있다. 금속 산화물 층(310)이 상부에 배치되는 기판은, 약 섭씨 150 도 내지 약 섭씨 350도, 이를테면 약 섭씨 220 도 내지 약 섭씨 240 도의 범위의 온도로 가열될 수 있다.

[0030] [0036] 다음으로, 도 3e에 도시된 바와 같이, 불소 처리된 금속 산화물 층(310) 상에 에칭 정지(etch stop) 층(312)이 증착될 수 있고, 에칭 정지 층(312)은, 금속 산화물 층(310)의 일부분을 커버하도록 패터닝될 수 있다. 에칭 정지 층(312)은, 유전체 재료, 이를테면 실리콘 산화물, 알루미늄 산화물, 실리콘 질화물, 또는 다른 적절한 재료로 제조될 수 있다. 에칭 정지 층(312)은, 도 1에 도시된 PVD 챔버(100)와 같은 PVD 챔버, 또는 도 2에 도시된 PECVD 챔버(200)와 같은 PECVD 챔버에서 증착될 수 있다. 도 3e에 도시된 바와 같이, 에칭 정지 층(312) 및 처리된 금속 산화물 층(310) 상에 전도성 층(314)이 증착될 수 있다. 전도성 층(314)은, 전기 전도성 금속, 이를테면 알루미늄, 텅스텐, 몰리브덴, 크롬, 탄탈륨, 및 이들의 조합들로 제조될 수 있다. 전도성 층(314)은, PVD에 의해 증착될 수 있다.

[0031] [0037] 전도성 층(314)이 증착된 후에, 도 3f에 도시된 바와 같이, 전도성 층(314)의 에칭하여 제거된 부분들에 의해, 소스 전극(316), 드레인 전극(318), 및 능동 채널(319)이 정의될 수 있다. 불소 처리된 금속 산화물 층(310)의 부분들이 또한 에칭에 의해 제거되어 게이트 유전체 층(306)의 부분들을 노출시킬 수 있다. 에칭 정지 층(312)은, 에칭 동안 능동 채널(319)을 과도한 플라즈마 노출로부터 보호하도록 기능한다.

[0032] [0038] 다음으로, 도 3g에 도시된 바와 같이, 게이트 유전체 층(306)의 노출된 부분들 상에 부동화 층(320)이 증착되며, 소스 전극(316), 드레인 전극(318), 및 부동화 층(320)이 또한 능동 채널(319)에 증착된다. 부동화 층(320)은, 실리콘 산화물, 실리콘 산질화물, 실리콘 탄화물, 비정질 탄소, 또는 임의의 다른 적절한 재료를 포함할 수 있다. TFT(300)는 바텀 게이트(bottom gate) TFT일 수 있다. 불소 함유 가스 또는 플라즈마 처리는, 임의의 적절한 TFT의 금속 산화물 층 상에 수행될 수 있다. 일부 실시예들에서, 불소 함유 가스 또는 플라즈마 처리는, 탑 게이트(top gate) TFT의 금속 산화물 층 상에 수행된다.

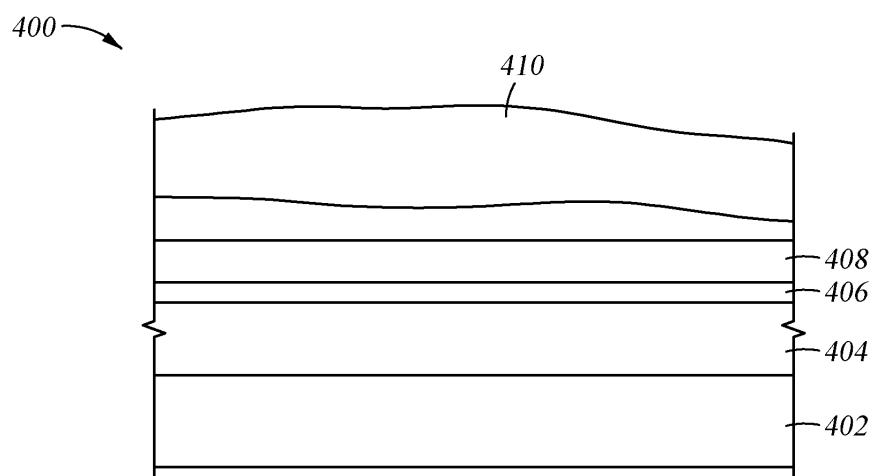

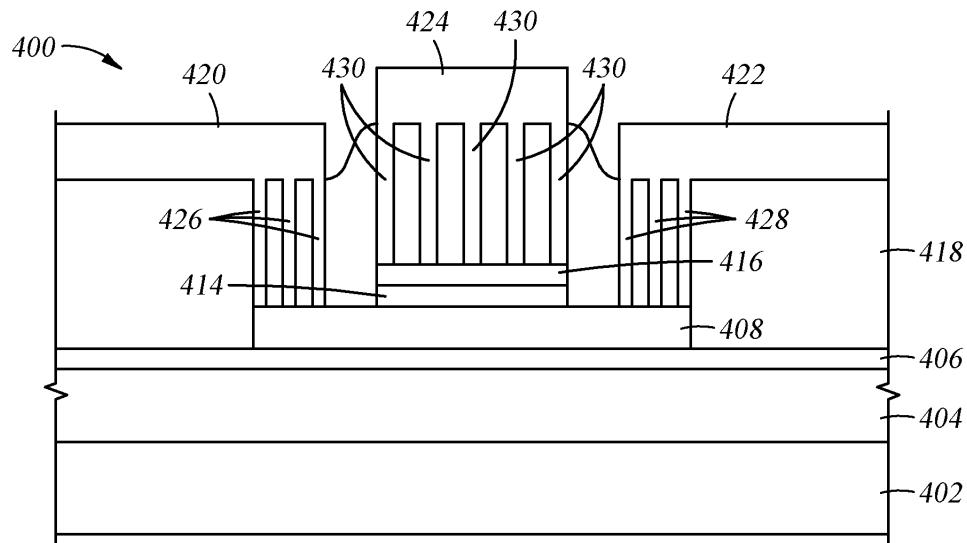

[0033] [0039] 도 4a-4f는 본원에 개시된 실시예들에 따른 제조의 다양한 스테이지들에서의 TFT(400)의 개략적인 횡단 면도들이다. TFT(400)는, 탑 게이트 TFT일 수 있고 그리고 기판(402)을 포함할 수 있다. 기판(402)은, 기판

(302)과 동일한 재료로 제조될 수 있다. 열 산화물 층(404)이 기판(402) 상에 형성될 수 있고, 열 산화물 층(404)은 기판(402)과 직접 접촉할 수 있다. 실리콘 산화물 층(406)이 열 산화물 층(404) 상에 형성될 수 있고, 실리콘 산화물 층(406)은 열 산화물 층(404)과 직접 접촉할 수 있다. 금속 산화물 층(408)이 기판(402) 위에, 이를테면 실리콘 산화물 층(406) 상에 중착되어 그와 직접 접촉할 수 있다. 금속 산화물 층(408)이 기판(402) 위에, 이를테면 실리콘 산화물 층(406) 상에 중착되어 그와 직접 접촉할 수 있다. 금속 산화물 층(408)은, 최종 TFT 구조에서의 능동 채널일 수 있다. 금속 산화물 층(408)은, 금속 산화물 층(310)과 동일한 재료로 제조될 수 있고 그리고 금속 산화물 층(310)을 중착하는 데 사용된 프로세스와 동일한 프로세스에 의해 중착될 수 있다. 금속 산화물 층(408)이 중착된 이후에, 산소 빙자리들을 채우고 그리고/또는 금속 산화물 층(408)으로부터 산소가 벗어나는 것을 방지하기 위해, 금속 산화물 층(408)은 불소 함유 가스 또는 플라즈마에 의해 처리될 수 있다. 금속 산화물 층(408)의 불소 가스 또는 플라즈마 처리는, 금속 산화물 층(310)의 불소 가스 또는 플라즈마 처리와 동일할 수 있는데, 이를테면, 도 4b에 도시된 바와 같이, 금속 산화물 층(408)을 불소 함유 가스 또는 플라즈마(410)에 노출시키는 것이다. 불소 함유 가스 또는 플라즈마(410)는, 도 3d에 도시된 불소 함유 가스 또는 플라즈마(308)와 동일할 수 있다.

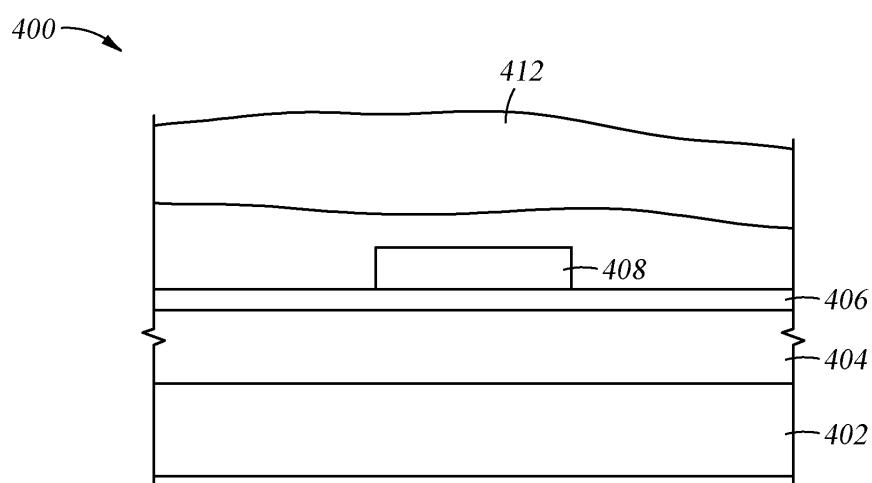

[0034] 다음으로, 도 4c에 도시된 바와 같이, 불소 처리된 금속 산화물 층(408)은, 이를테면, 금속 산화물 층(408)의 부분들이 제거되도록 에칭함으로써, 실리콘 산화물 층(406)의 부분들을 노출시키도록 패터닝될 수 있다. 금속 산화물 층(408)의 부분들의 에칭에 후속하여, 금속 산화물 층(408)은 다시 불소 함유 가스 또는 플라즈마(412)에 의해 처리될 수 있다. 불소 함유 가스 또는 플라즈마(412)는, 도 3d에 도시된 불소 함유 가스 또는 플라즈마(308)와 동일할 수 있다. 금속 산화물 층(408)의 처리 프로세스 조건들은, 금속 산화물 층(310)의 처리 프로세스 조건들과 동일할 수 있다. 제2 불소 함유 가스 또는 플라즈마 처리 이전에 어닐링 프로세스가 패터닝된 금속 산화물 층(408) 상에 수행될 수 있다.

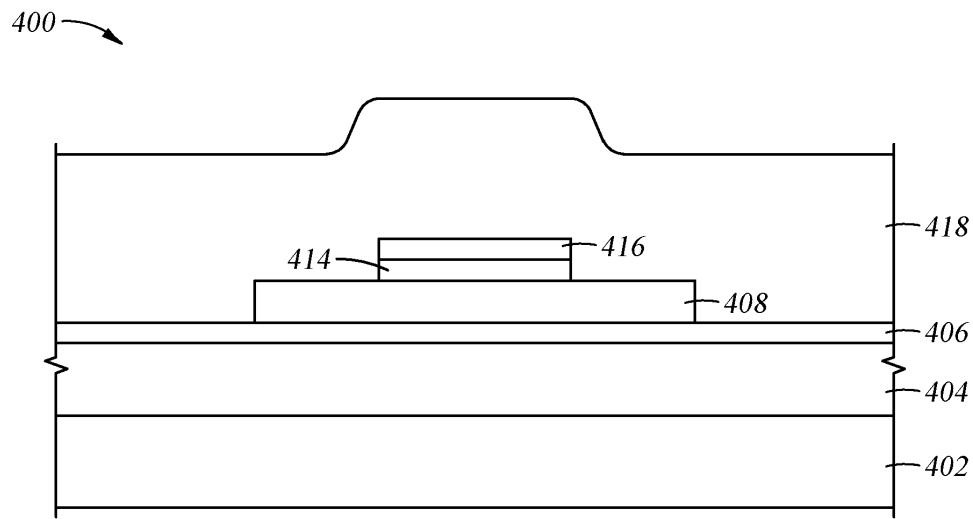

[0035] 다음으로, 도 4d에 도시된 바와 같이, 처리된 금속 산화물 층(408) 상에 게이트 유전체 층(414)이 중착될 수 있다. 게이트 유전체 층(414)은, 게이트 유전체 층(306)과 동일한 재료로 제조될 수 있다. 게이트 유전체 층(414) 상에 게이트 접촉 층(416)이 중착될 수 있고, 게이트 접촉 층(416)은, 게이트 전극(304)과 동일한 재료로 제조될 수 있다. 게이트 유전체 층(414) 및 게이트 접촉 층(416)은, 이를테면, 게이트 유전체 층(414) 및 게이트 접촉 층(416)의 부분들이 제거되도록 에칭함으로써, 금속 산화물 층(408)의 부분들을 노출시키도록 패터닝될 수 있다. 노출된 실리콘 산화물 층(406), 노출된 금속 산화물 층(408), 및 게이트 접촉 층(416) 상에 충간 유전체(ILD; inter-layer dielectric) 층(418)이 중착될 수 있다. ILD 층(418)은, 실리콘 산화물과 같은 임의의 적절한 유전체 재료로 제조될 수 있다.

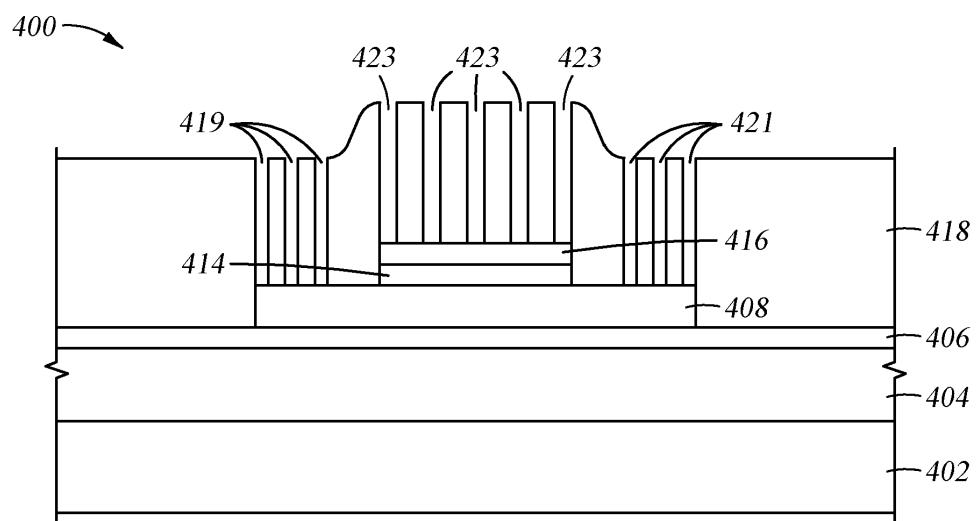

[0036] 도 4e에 도시된 바와 같이, 복수의 접촉 홀(hole)들(419, 421, 423)이 ILD 층(418)에 형성될 수 있다. 접촉 홀들(419, 421, 423)은, 예칭과 같은 임의의 적절한 방법에 의해 형성될 수 있다. 복수의 접촉 홀들(419, 421)의 형성에 기인하여 금속 산화물 층(408)의 부분들이 노출될 수 있고, 복수의 접촉 홀들(423)의 형성에 기인하여 게이트 접촉 층(416)의 부분들이 노출될 수 있다. 접촉 홀들(419, 421, 423)은 각각, 도 4e에 도시된 바와 같이, 금속으로 채워져 접촉부들(426, 428, 430)을 형성할 수 있다. 복수의 접촉부들(426, 428, 430)은 게이트 전극(304)과 동일한 재료로 제조될 수 있다. 복수의 접촉부들(426, 428)은 금속 산화물 층(408)과 직접 접촉할 수 있고, 복수의 접촉부들(430)은 게이트 접촉 층(416)과 직접 접촉할 수 있다. ILD 층(418) 상에 금속 층이 중착될 수 있고, 금속 층은, 소스 전극(420), 드레인 전극(422), 및 게이트 전극(424)을 정의하도록 패터닝될 수 있다. 소스 전극(420), 드레인 전극(422), 및 게이트 전극(424)은, 게이트 전극(304)과 동일한 재료로 제조될 수 있다. 소스 전극(420)은 복수의 접촉부들(426)과 직접 접촉할 수 있고, 드레인 전극(422)은 복수의 접촉부들(428)과 직접 접촉할 수 있고, 그리고 게이트 전극(424)은 복수의 접촉부들(430)과 직접 접촉할 수 있다. 게이트 전극(424)이 금속 산화물 층(408) 위에 형성되므로, TFT(400)는 탑 게이트 TFT일 수 있다.

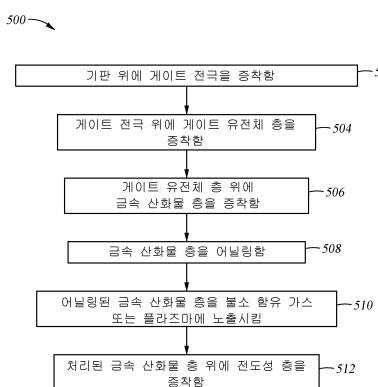

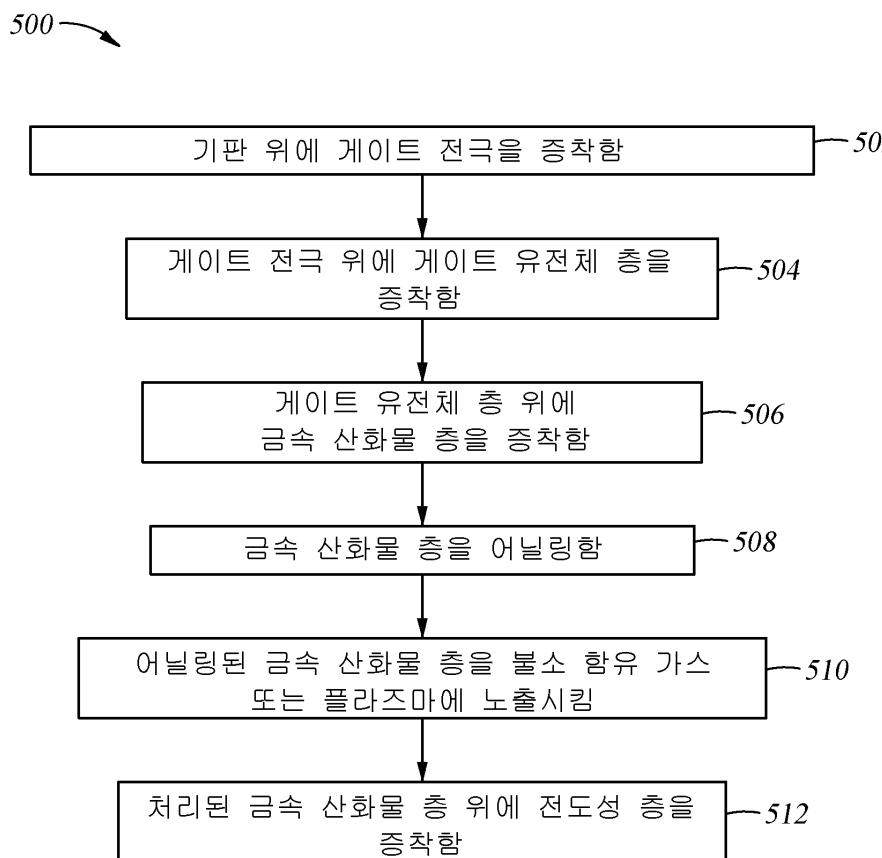

[0037] 도 5a-5c는 본원에 개시된 실시예들에 따라 도 3a-3g에 도시된 TFT(300)를 형성하기 위한 프로세스들을 도시하는 흐름도들이다. 도 5a에 도시된 바와 같이, 프로세스(500)는, 기판 위에 게이트 전극을 중착하는 블록(502)으로 시작된다. 게이트 전극은 게이트 전극(304)일 수 있고, 기판은 도 3a에 도시된 기판(302)일 수 있다. 다음으로, 블록(504)에서, 게이트 전극 위에 게이트 유전체 층이 중착된다. 게이트 유전체 층은, 도 3b에 도시된 게이트 유전체 층(306)일 수 있다. 블록(506)에 도시된 바와 같이, 금속 산화물 층, 이를테면 도 3c에 도시된 금속 산화물 층(310)이 게이트 유전체 층 위에 중착될 수 있다. 금속 산화물 층의 중착에 후속하여, 블록(508)에 도시된 바와 같이, 금속 산화물 층이 어닐링될 수 있다. 다음으로, 블록(510)에 도시된 바와 같이, 금속 산화물 층이 불소 함유 가스 또는 플라즈마, 이를테면 도 3d에 도시된 불소 함유 가스 또는 플라즈마(308)에 노출된다. 마지막으로, 블록(512)에 도시된 바와 같이, 처리된 금속 산화물 층 위에 전도성 층, 이를테면 전도성 층(314)이 중착될 수 있다.

[0038]

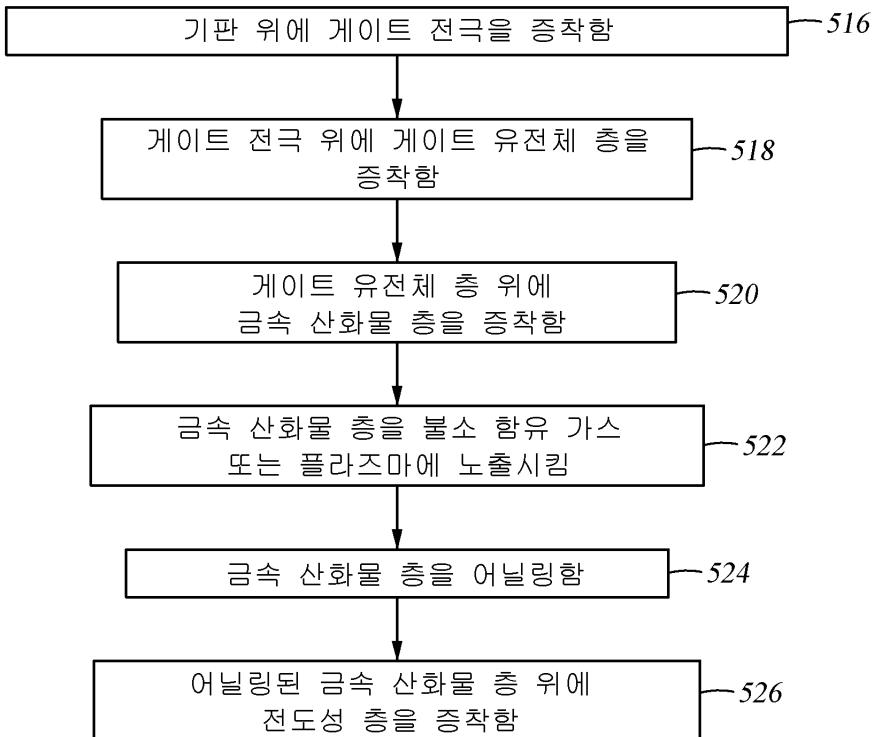

[0044] 도 5b에 도시된 바와 같이, 프로세스(514)는, 기판 위에 게이트 전극을 증착하는 블록(516)으로 시작된다. 게이트 전극은 게이트 전극(304)일 수 있고, 기판은 도 3a에 도시된 기판(302)일 수 있다. 다음으로, 블록(518)에서, 게이트 전극 위에 게이트 유전체 층이 증착된다. 게이트 유전체 층은, 도 3b에 도시된 게이트 유전체 층(306)일 수 있다. 블록(520)에 도시된 바와 같이, 금속 산화물 층, 이를테면 도 3c에 도시된 금속 산화물 층(310)이 게이트 유전체 층 위에 증착될 수 있다. 금속 산화물 층의 증착에 후속하여, 블록(522)에 도시된 바와 같이, 금속 산화물 층이 불소 함유 가스 또는 플라즈마, 이를테면 도 3d에 도시된 불소 함유 가스 또는 플라즈마(308)에 노출될 수 있다. 다음으로, 블록(524)에 도시된 바와 같이, 처리된 금속 산화물 층이 어닐링될 수 있다. 마지막으로, 블록(526)에 도시된 바와 같이, 처리되고 어닐링된 금속 산화물 층 위에 전도성 층, 이를테면 전도성 층(314)이 증착될 수 있다.

[0039]

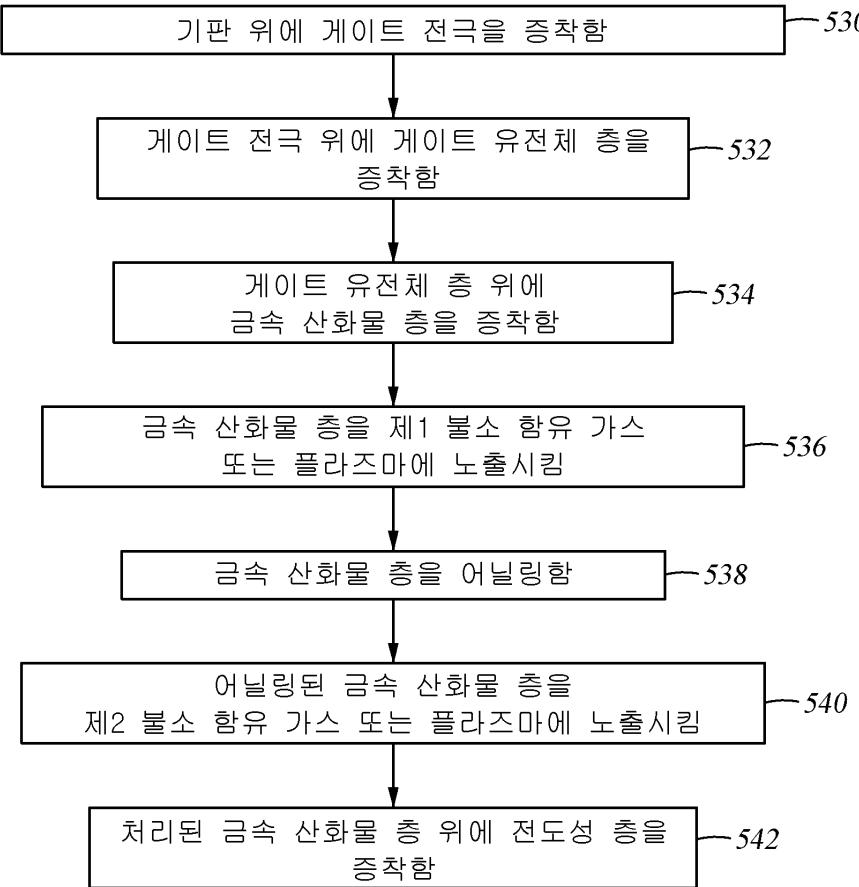

[0045] 도 5c에 도시된 바와 같이, 프로세스(528)는, 기판 위에 게이트 전극을 증착하는 블록(530)으로 시작된다. 게이트 전극은 게이트 전극(304)일 수 있고, 기판은 도 3a에 도시된 기판(302)일 수 있다. 다음으로, 블록(532)에서, 게이트 전극 위에 게이트 유전체 층이 증착된다. 게이트 유전체 층은, 도 3b에 도시된 게이트 유전체 층(306)일 수 있다. 블록(534)에 도시된 바와 같이, 금속 산화물 층, 이를테면 도 3c에 도시된 금속 산화물 층(310)이 게이트 유전체 층 위에 증착될 수 있다. 금속 산화물 층의 증착에 후속하여, 블록(536)에 도시된 바와 같이, 금속 산화물 층이 제1 불소 함유 가스 또는 플라즈마, 이를테면 도 3d에 도시된 불소 함유 가스 또는 플라즈마(308)에 노출될 수 있다. 다음으로, 블록(538)에 도시된 바와 같이, 처리된 금속 산화물 층이 어닐링될 수 있다. 처리된 금속 산화물 층의 어닐링에 후속하여, 블록(540)에 도시된 바와 같이, 어닐링된 금속 산화물 층이 제2 불소 함유 가스 또는 플라즈마, 이를테면 도 3d에 도시된 불소 함유 가스 또는 플라즈마(308)에 다시 노출될 수 있다. 마지막으로, 블록(542)에 도시된 바와 같이, 처리된 금속 산화물 층 위에 전도성 층, 이를테면 전도성 층(314)이 증착될 수 있다.

[0040]

[0046] 요약하면, TFT를 형성하기 위한 방법은, 불소 함유 가스 또는 플라즈마로 금속 산화물 층을 처리하는 단계를 포함한다. 불소 함유 가스 또는 플라즈마 처리는, 금속 산화물 층 상에 수행되는 어닐링 프로세스 이전에, 이후에, 또는 이전 및 이후 둘 모두에 수행될 수 있다. 불소 함유 가스 또는 플라즈마 처리는, 산소 빙자리들을 채우고 산소 분자들이 금속 산화물 층을 벗어나는 것을 방지하도록 금속 산화물 층을 부동화시키는 것을 돋는다. 산소 빙자리들이 감소되면, 네거티브 임계 전압이 방지되고 더 안정된 TFT가 초래된다.

[0041]

[0047] 전술한 내용들이 본 개시내용의 실시예들에 관한 것이지만, 본 개시내용의 다른 그리고 추가적인 실시 예들이 본 개시내용의 기본적인 범위로부터 벗어나지 않으면서 안출될 수 있으며, 본 개시내용의 범위는 하기의 청구항들에 의해 결정된다.

도면

도면1

도면2

도면3a

도면3b

도면3c

도면3d

도면3e

도면3f

도면3g

도면4a

도면4b

도면4c

## 도면4d

## 도면4e

## 도면4f

## 도면5a

## 도면5b

514 ↗

## 도면5c

528 ↗