(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3708974号

(P3708974)

(45) 発行日 平成17年10月19日(2005.10.19)

(24) 登録日 平成17年8月12日(2005.8.12)

(51) Int.C1.<sup>7</sup>

F 1

|            |            |   |

|------------|------------|---|

| HO4N 7/24  | HO4N 7/13  | Z |

| HO3M 7/40  | HO3M 7/40  |   |

| HO4N 5/92  | HO4N 11/04 | Z |

| HO4N 11/04 | HO4N 5/92  | H |

請求項の数 3 (全 14 頁)

(21) 出願番号

特願平6-64885

(22) 出願日

平成6年4月1日(1994.4.1)

(65) 公開番号

特開平7-79432

(43) 公開日

平成7年3月20日(1995.3.20)

審査請求日

平成13年3月15日(2001.3.15)

審判番号

不服2004-20872(P2004-20872/J1)

審判請求日

平成16年10月7日(2004.10.7)

(31) 優先権主張番号

042173

(32) 優先日

平成5年4月2日(1993.4.2)

(33) 優先権主張国

米国(US)

(73) 特許権者 391000807

アールシーエー トムソン ライセンシング コーポレイション

RCA THOMSON LICENSING CORPORATION

アメリカ合衆国 ニュージャージ州 08

540 プリンストン インデペンデンス

・ウエイ 2

(74) 復代理人 100120581

弁理士 市原 政喜

(74) 代理人 100077481

弁理士 谷 義一

(74) 代理人 100088915

弁理士 阿部 和夫

最終頁に続く

(54) 【発明の名称】コード化ビデオ信号の処理装置

## (57) 【特許請求の範囲】

## 【請求項 1】

コードワード・データストリームを、優先順位付けされた第1および第2のコードワード・シーケンスにセグメント化する、ビデオ信号処理システムの装置であって、

一連のデータ・グループを含むビデオ信号コードワード・データストリームを供給すると共に、前記ビデオ信号コードワード・データストリームの各コードワードと同時に、関連したコードワードのビット長を示す長さワードを供給する手段と、

前記ビデオ信号コードワード・データストリームに応答して分析インターバル期間中に動作することにより、データ・グループ内の第1および第2のコードワードを分けるためのプライオリティ・ブレークポイントを判定する分析手段を含み、該プライオリティ・ブレークポイントが挿入された出力コードワード・データストリームを出力するコードワード処理手段と、

前記コードワード処理手段から前記出力コードワード・データストリームを受信し、前記出力コードワード・データストリームのフォーマットを、優先順位付けされた第1および第2のデータ・チャネルを介して伝送するために前記優先順位付けされた第1および第2のコードワード・シーケンスに変換する伝送処理手段と、

前記分析インターバル期間中に、空白コードワードであって該コードワードに関連した長さワードがゼロ値を示す空白コードワード、を生成する手段と、

前記コードワード処理手段によって前記ビデオ信号コードワード・データストリームの処理が行われる前段において、前記空白コードワードを前記ビデオ信号コードワード・デ

ータストリーム中に挿入する手段と、

を具備したことを特徴とする装置。

【請求項 2】

請求項 1 に記載の装置において、

前記ビデオ信号は、複数のイメージ・スライスをそれぞれ含む複数のイメージ・フレームから構成されたイメージ情報を内容とするテレビジョン信号であり、

前記分析インターバル期間はイメージ・スライス・インターバルを含む、ことを特徴とする装置。

【請求項 3】

請求項 1 に記載の装置において、

前記ビデオ信号コードワード・データストリームを供給する手段から供給された前記ビデオ信号コードワード・データストリームは M P E G 符号化フォーマットに準拠しており、

前記传送処理手段は、コードワードを传送用データセルにパッキング処理する際、前記空白コードワードを無視する、

ことを特徴とする装置。

【発明の詳細な説明】

【0 0 0 1】

【産業上の利用分野】

本発明はコード化ビデオ信号を処理するための装置に関し、特に、可変長コード化 (variable length coding - VLC) の対象となるビデオ信号を、M P E G 標準に従って優先順位付けするための装置に関する。 20

【0 0 0 2】

なお、本明細書の記述は本件出願の優先権の基礎たる米国特許出願第 0 8 / 0 4 2 , 1 7 3 号 (1993 年 4 月 2 日出願) の明細書の記載に基づくものであって、当該米国特許出願の番号を参照することによって当該米国特許出願の明細書の記載内容が本明細書の一部分を構成するものとする。

【0 0 0 3】

【背景技術】

米国特許第 5,122,875 号 (Raychaudhuri 他) は、M P E G 準拠 (MPEG-like) 可変長コード化の対象となる高品位テレビジョン (high-definition television - HDTV) 信号を処理するためのシステムを記載している。M P E G とは、国際標準化機構 (International Organization for Standardization - ISO) によって確立された標準化コード形式である。この標準は、I S O 文書 ISO/IEC DIS 11172 「デジタル記憶媒体用の動画および関連オーディオのコード化」 (Coding for Moving Pictures and Associated Audio for Digital Storage Media) に述べられており、1991 年 11 月 23 日改訂に記載されている。なお、この文書は、一般的コード形式の説明部分に関しては、引用により本明細書の一部を構成するものである。Raychaudhuri システムは、コードワード (codeword) を高プライオリティと低プライオリティのコードワード・シーケンスに分割するプライオリティ・セレクタ (priority selector) を含んでいる。高プライオリティと低プライオリティのコードワード・シーケンスは、それぞれイメージ再生にとって相対的に大きい重要度と小さい重要度をもつ圧縮ビデオ・データに対応している。 30

【0 0 0 4】

プライオリティ・セレクタは、あるイメージ・スライス (image slice) のときの高プライオリティと低プライオリティのセグメント間のブレークポイント (breakpoint) を計算するためにコードワードを分析する。以下の説明で明らかのように、「スライス」とは、M P E G コード化構文の階層の 1 つに対応するイメージ・セグメントである。コードワード・データストリームがトランスポート・プロセッサ (transport processor) に渡されると、このプロセッサはコードワード・データを各々がヘッダとペイロード (payload) セクションを含んでいるトランスポート・セル (transportcell) にパックし、出力として H P デー 40

タストリームと S P データストリームを送出する。

【 0 0 0 5 】

データ優先順位付けシステム(data prioritizing system)においてプライオリティ・セレクタに望まれていることは、そのオペレーションを同期化して必要なタイミング条件を単純化することである。例えば、必要とするクロックを1つだけにすることである。プライオリティ・セレクタに望まれているもう1つは、優先順位付けされたデータがトランスポータ・プロセッサによって受信され、パックされて出力チャネルに送出されるとき、そのデータストリームがM P E Gなどの標準的データ形式との互換性を失わないように、コードワード・データストリームを処理することである。

【 0 0 0 6 】

10

【発明の概要】

本発明による装置はコードワード・プライオリタイザ(codeword prioritizer)に組み込まれ、所定のコードワード相互間の関係に従って、コードワード・データストリームを複数のコードワード・シーケンスにセングメント化することを容易にする。本明細書に開示している好適実施例によれば、コードワード・プライオリタイザは、コードワード・シーケンスを分析して、高プライオリティ(H P)コードワードと標準プライオリティ(S P)コードワード間のどこにブレークポイントを設定すべきかを判断するために休止(pause)したときのインターバル期間に、空白コードワード(null codeword)をコードワード・データストリームに挿入する。この空白ワードは、その後に続くトランスポータ・プロセッサがコードワードをセルにパックするとき無視することにより、M P E G フォーマットとの互換性を保つようにしている。

【 0 0 0 7 】

20

【実施例】

以下、図面を参照して本発明の実施例を詳細に説明する。

【 0 0 0 8 】

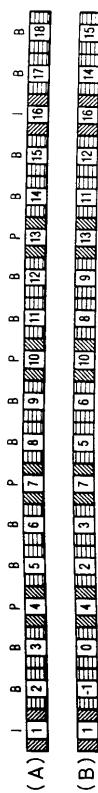

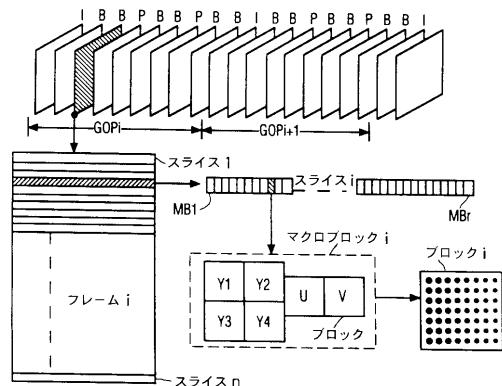

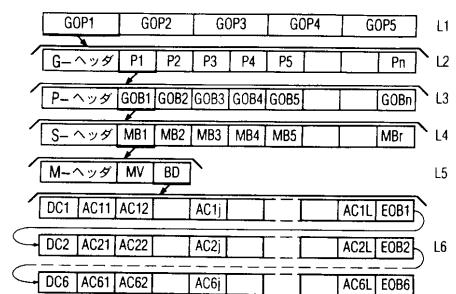

図1に示すように、高品位テレビジョン・ソース10からのディジタル・ビデオ・データは、プロセッサ14においてM P E G 準拠の可変長コード化(つまり、データ圧縮)の処理を受ける。データ・ソース10は、一連のオリジナル・イメージ・フィールド/フレーム・データ(図2(A)に図示)を並べ替え、これにより、図2(B)に示すような出力を得る。並べ替えられたシーケンス(データ列)はプロセッサ/コンプレッサ14に入力され、このプロセッサ/コンプレッサはM P E G 準拠のフォーマットに従ってコード化された圧縮フレームのシーケンスを出力する。このフォーマット(形式)は階層構造になっており、図5には簡略形式で示されている。M P E G 階層形式(h i e r a r c h i c a l f o r m a t)は複数の層からなり、各層はそれぞれのヘッダ情報をもっている。名目上、各ヘッダは開始コード(start code)、それぞれの層に関するデータ、およびヘッダ拡張部分を追加するための予備を含んでいる。ヘッダ情報の多く(上記のM P E G 文書に示されているもの)は、M P E G システム環境において同期をとる目的で必要になるものである。圧縮されたビデオ・データ、つまり、図5に示すように階層形式の可変長コード化(V L C)された並列コードワードは、プロセッサ14からF I F O プライオリティ分析バッファ(FIFO priority analysis buffer)22に入力される。このバッファは、プライオリティ・プロセッサ(priority processor)20の分析回路によって分析される直前にコードワードをストアする。

30

【 0 0 0 9 】

40

プロセッサ14は、プライオリティ・プロセッサ20が必要とするコードワード・タイプ・データを含んでいるコードワードを作成する。具体的には、プロセッサ14は各並列入力コードワードを、7ビットのタイプ・フィールドおよび15ビットのバリュー・フィールドを示す並列22ビットの等価フォーマットに変換するために複数のR O Mを採用している。タイプ・フィールドは、M P E G 階層内で意味と相対的プライオリティが異なるコードワードを区別する情報、つまり、タイプ別にコードワードを区別する情報を収めている。バリュー・フィールドは、特定コードワード・タイプの量的情情報を収めている。バリ

50

ユー・フィールドの 15 ビットは、すべてが常に使用されるとは限らない。例えば、タイプ「15」はモーション・ベクトル(motion vector)であり、このタイプに関連する 9 ビット値はベクトルの大きさを示している。また、プロセッサ 14 は、各コードワードと同時に、そのコードワードの長さを示す長さ(Length)ワードを、並列ビット形式で別々のバス上に送出する。米国特許第 5,122,875 号 (Raychaudhuri) には、M P E G 準拠の階層構造化された圧縮ビデオ・データを出力するために、エレメント 14 として使用できるコンプレッサ装置の例が開示されている。

#### 【0010】

プロセッサ 14 からの 22 ビット・コードワードは、(有効な)新しいコードワードがいつ受信できる準備状態にあるかをバッファ 22 に知らせる、プロセッサ 14 からの W R I T E 信号と一緒に、プライオリティ・プロセッサ 20 に非同期的に送られる。書き込みイネーブル(許可)クロック(ライト E N )は、有効なコードワードをバッファ 22 に書き込むためのものである。システム・クロック・ジェネレータ 25 によって生成される 23.6 MHz のリード信号は、プライオリティ・プロセッサ 20 のすべてのエレメントによって使用される単一システム・クロックである。読み取りイネーブル(許可)信号(リード E N )は、バッファ 22 がユニット 14 からデータを受信しようとしていることを制御ユニット 24 が検出したとき、制御ユニット 24 によって生成され、それ以外のときは禁止とされる。リード・イネーブル信号(リード E N )の他の特性は後に説明する。

#### 【0011】

プライオリティ・プロセッサ 20 は、一度に 1 スライスごとにコードワード・データストリームを分析し、そして、このプライオリティ・プロセッサが、各スライスを H P セグメントと S P セグメントに優先順位付けするブレークポイント値を計算しているときの分析インターバル期間に、空白コードワード(null codeword - 長さがゼロと指定されているコードワード)をスライスとスライスの間に挿入する。最終的には、これらのセグメントはトランスポート・プロセッサ(transport processor) 50 によって H P セルまたは S P セルにパックされる。スライス(slice)とは、図 4 と図 5 に示すように、M P E G 規定のイメージ・セグメントである。これについては、図 4 および図 5 を参照して後述する。空白コードワードを含めて、各コードワードには、関連したコードワードのビット長を指定する並列長さワードが関連づけられている。空白コードワードは、プロセッサ 14 によってコードワードが生成されないときのインターバル期間(つまり、モーションまたはイメージ・ディテールがほとんど、あるいはまったくないインターバル期間)にも挿入される。空白コードワードはプロセッサ 20 の同期オペレーションを容易にし、単一システム・クロック(リード)の使用を可能にする。空白コードワードは、データ・パック・オペレーション時にはトランスポート・プロセッサ 50 によって無視されるが、これは、各空白コードワードに関連づけられた長さワードには、ゼロの値が割り当てられているためである。

#### 【0012】

バッファ 22 は従来の設計構造にすることが可能である。例えば、バッファ 22 は、それぞれの部分に 15 ビットのバリュー・コードワードを受け入れるための対の並列化 8 ビット幅バッファと、7 ビットのタイプ・コードワードを受け入れるための 8 ビット幅バッファとで構成することが可能である。この目的に適した 8 ビット幅ユニット(バッファ)としては、Integrated Device Technology 社製の IDT 型 72241 バッファがある。これらの 8 ビット・ユニットからのバッファされた出力は、それぞれの D フリップフロップを経由して、バッファ 22 のバリューおよびタイプ・コードワード出力に送ることが可能である。D フリップフロップはリード信号によってクロックがとられ、それぞれの 8 ビット・バッファの出力端から送られてきたデータをその「D」入力端に受信する。リード・イネーブル(リード E N )信号は、8 ビット・バッファから出力 D フリップフロップへのデータ・フローを許可または禁止するゲートを制御するために使用される。

#### 【0013】

コードワードは、リード・クロックに同期して、一度に 1 コードワードずつバッファ 22 から読み出されるが、この読み出しがスライスとスライスの間では中止される。タイム・マ

10

20

30

40

50

ルチプレクサ(time multiplexer)2 8 は、バッファ2 2 が空であるときのインターバル期間に、また、プライオリティ・ブレークポイントがあるスライスで計算されているときの分析インターバル期間バッファ2 2 が読み出されていないときに、空白コードワードをバッファ2 2 からのデータストリーム中に挿入する。空白コードワードとその関連(ゼロ)長さワードは、コンパレータおよび空白コードワード・ジェネレータ2 6 によって生成される。ユニット2 6 のコンパレータ部分はバッファ2 2 の出力をモニタし、ピクチャ開始(Picture Start) コードワード(これは、各ピクチャ・フレームの直前に現れる)およびスライス開始(Slice Start) コードワード(これは各イメージ・スライスの直前に現れる)が現れると、それを検出するようにプログラムされている。例えば、スライス開始コードワードが現れたときは、あるスライス(N)がバッファ2 2 から読み出され、次のスライス(N+1)がバッファ2 2 に書き込まれる直前にあることを示している。ブレークポイント・アナライザ(breakpoint analyser)4 2 がスライス・データを分析するためには、一定数のクロック・サイクルが必要であり、その終了時に、バッファ2 2 はリード・イネーブル(リード EN)信号を受けて再び読み出すことが許可され、空白コードワード生成は中止される。空白コードワードとその関連並列長さワードは、タイム・マルチプレクサ2 8 の一方の入力端に入力され、他方の入力端には、バッファ2 2 からのタイプおよびバリュー・データ出力が入力される。

## 【0014】

レジスタ3 0 はリード・システム・クロックと同期して動作し、マルチプレクサ2 8 がクロックで動作するデバイスではなく、そのために時間遅延が起こったとき発生するタイミング差を埋め合わせるために、データストリームのタイミングを調整する働きをする。レジスタ3 0 の同期コードワード出力は、コンパレータおよびフラグ・ジェネレータ3 2 を経由してコードワード・バッファ3 6 の一方の入力端に、また、3クロック期間遅延ネットワーク(three-clock period delay network)3 4 を経由してコードワード・バッファ3 6 の他方の入力端に入力される。ユニット3 2 のコンパレータ部分は、4つの関連インジケータ(フラグ)を生成する目的で4つのコードワード・タイプを検出するようにプログラムされており、これらのコードワード・タイプがトランスポート・プロセッサ5 0 によって受信されたとき、該当のマークが付けられるようになっている。トランスポート・プロセッサが必要とする4つのフラグは、グループ開始(Group Start) フラグ、ピクチャ開始(Picture Start) フラグ、レコード・ヘッダ(Record Header) フラグおよびマクロブロック・アドレス・インクリメント(Macroblock Address Increment) フラグである。これらのフラグはコードワード・ストリームと並列に伝達される。

## 【0015】

ユニット3 2 は、“I”フレーム(これは図4と図5に示されているが、同図を参照して後述する)のピクチャ開始コードワードより1コードワード前にグループ開始フラグを生成する。従って、このフラグは2クロックだけ遅延してコードワード・バッファ3 6 に渡される。グループ開始フラグは、ピクチャ開始コードワードより1コードワード前に、空白コードワードと同時に現れる。ピクチャ開始フラグは、すべてのフレーム(図4のI、P、Bフレーム)のピクチャ開始コードワードと同時に生成される。ピクチャ開始フラグは、ピクチャ開始コードワード・タイプが検出されると生成され、このフラグは、ピクチャ開始コードワードとタイミングを合わせるために、3クロック期間だけ遅延してコードワード・バッファ3 6 に渡される。レコード・ヘッダ・フラグは、スライス開始コードワードより1コードワード前に、すべてのスライスの開始時に生成され、空白コードワードと同時に現れるが、空白コードワードは、あとで、マルチプレクサ4 1 のオペレーションによってプライオリティ・ブレークポイント値に置き換えられる。レコード・ヘッダ・コードワードは、関連スライスのプライオリティ・ブレークポイントを示す値を含んでいる。ユニット3 2 のコンパレータはスライス開始タイプ・コードワードを検出し、2クロックだけ遅延してスライス開始フラグをバッファ3 6 に出力する。レコード・ヘッダ・コードワードが所定のクロック・サイクル数のあとでコードワード・バッファ3 6 から現れると、現スライスのプライオリティ・ブレークポイント値がアナライザ4 2 から得られ、

10

20

30

40

50

レコード・ヘッダと同時に現れた空白コードワードのバリュー・フィールド中にマルチブレクサ41によって挿入される。バッファ36のフラグ出力ラインはマルチブレクサ41の制御入力端に入力され、その結果、プライオリティ・ブレークポイント値は、レコード・ヘッダ・フラグがバッファ36のフラグ出力ラインに現れたとき、レコード・ヘッダと同時に現れた空白ワードのバリュー・フィールド中に挿入される。ブレークポイント値は、レコード・ヘッダ・フラグに関連づけられた空白ワードのバリュー・フィールド中に挿入され、この値は、トランポート・プロセッサ50がレコード・ヘッダ自身を作るとき、トランスポート・プロセッサ50によって使用される。マクロブロック・アドレス・インクリメント・インジケータ・フラグはマクロブロックの開始を示しており、マクロブロック・アドレス・インクリメント・コードワード・タイプが検出されたときマクロブロック・アドレス・インクリメント・コードワードと同時に生成される。10

#### 【0016】

コードワード・バッファ36は、一定数のクロック期間(clock period)の長さになっている。この例では、クロック期間は8192である。コードワードが遅延回路34からバッファ36に入るとき、ユニット32によって生成されたフラグは、それぞれのコードワードとタイミングが合わされて、コードワードと一緒にバッファ36内を伝わっていく。バッファ36の長さは一定で、長いために、ブレークポイント・アナライザ42とその関連回路は、十分な時間的余裕をもってスライス内のコードワードの統計を処理し、コードワードがバッファ36から現れたときコードワードを優先順位付けするためのプライオリティ・ブレークポイント値を生成することができる。20

#### 【0017】

バッファ36からの正しくタイミング合わせされたコードワードとフラグはプライオリティ・フラグ・ジェネレータ40のそれぞれの入力端に並列に送られる。このジェネレータ40には、ブレークポイント・アナライザ42からプライオリティ・ブレークポイント値も入力される。ユニット40からの出力コードワードは、ユニット48によってプロセッサ14の入力に逆変換されてコードワード形式に戻され、各々がヘッダとデータ(ペイロード)セクションをもつHPセルとSPセル、つまり、トランスポート・パケットに、トランスポート・プロセッサ50によって配列される。トランスポート・プロセッサ50からのHPパケットとSPパケットは出力プロセッサ55によって処理されてから、データ・チャネル上を送られる。図3および米国特許第5,122,875号(Raychaudhuri他)に示されているように、出力プロセッサ55は、レート・バッファ(rate buffer)、誤り訂正およびモデム・ネットワークを含むことが可能である。また、Raychaudhuri特許には、MPEG準拠の階層エンコード、優先順位付けを目的としたコードワード分析、およびトランスポート処理のために使用できるネットワークも記載されているが、これらについて後述する。30

#### 【0018】

スライス・プライオリティ・ブレークポイントおよびその結果として優先順位付けされるHPとSPビットストリームを設定するためには、プライオリティ処理回路にはそのスライスのデータ統計が必要であり、この統計は、次のスライス・インターバル期間に新しいコードワードがプライオリティ・プロセッサに入力されたとき変更が行われた場合、その変更の影響を受けない必要がある。この問題を解決するアーキテクチャの1つとして、「ピンポン」方式で動作する2つのプライオリティ分析入力バッファを使用しているものがある。このアーキテクチャによれば、現スライスのコードワードは一方のバッファに書き込まれ、前のスライスのコードワードは他方のバッファから読み出されるようになっている。この種の二重バッファ構成は、前掲のRaychaudhuri特許に記載されているシステムで使用されている。二重バッファ手法は効率面では十分であるが、2つのバッファが必要になるために、ハードウェア面で高価である。さらに、タイミング制御信号を生成するための回路は、可変長コード化スライス・コードワードが一般に、異なる長さになっているために、複雑な構造になっている。図1に示すプライオリティ・プロセッサは、使用する入力バッファが入力バッファ22の1つだけであるので、アーキテクチャが単純化され、低コ4050

ストである。また、エンコーダ 1 2 がデータを送信していないときのインターバルを利用するようになっている。

#### 【0019】

制御ユニット 2 4 からバッファ 2 2 に与えられる読み取り許可（イネーブル）信号（リード E N ）により、単一バッファ 2 2 からなる入力バッファ構成の実現が可能になっている。前述したように、リード・イネーブル信号は、バッファ 2 2 から読み取られるコードワードがないとき、および、バッファ 2 2 が空のときは、現れない。そのときは、空白コードワードがマルチブレクサ 2 8 からデータストリーム中に挿入されるので、コードワード・データストリームは同期を維持している。バッファ 2 2 は、リード・イネーブル信号がブレークポイント分析インターバルの終了時に現れたとき、データの読み出しを開始し、この読み出しは、通常、入力コードワード・ストリーム中にブレークポイント（break）が現れ（つまり、ディテールがほとんど、あるいはまったくないイメージが現れたとき）、その結果、バッファ 2 2 に残っているコードワードがなくなるまで続けられ、コードワードがなくなると、リード・イネーブル信号は禁止され、空白コードワードがユニット 2 6 , 2 8 からデータストリーム中に挿入される。リード・イネーブル信号は、制御ユニット 2 4 がバッファ 2 2 の出力端に現れたピクチャ開始コードワード・タイプまたはスライス開始コードワード・タイプを検出したときも（例えば、コンパレータにより）禁止される。この状態が起きたときは、バッファ読み取りオペレーションが中止される直前にバッファ 2 2 から読み出されていたデータは、すべてが前のスライス（N ）のものであり、新しいスライス（N + 1 ）が開始する直前にあることを意味する。

10

#### 【0020】

これらのコードワード・タイプの検出は、コードワード自体がクロックに合わせてバッファ 2 2 から読み出される前に行われ、そして、そのコードワードはリード・イネーブル信号が禁止されている間、バッファ 2 2 の出力レジスタに残っている。このアクションが必要なのは、スライスの終了を検出するために、次のスライス開始コードワードまたはピクチャ開始コードワードをモニタする必要があるためである。従って、検出された特定のコードワードは、それが現スライス・インターバルの終了を検出するために使用される場合であっても、次のスライス・インターバルまでバッファ 2 2 に残っている。リード・イネーブル信号が禁止されている間、プライオリティ・プロセッサは分析モードにあり、到来したコードワードは、事前に決めた容量に達するまでバッファ 2 2 内にバックアップがとられ、容量まで達すると、トランスポート・レディ（Transport Ready）制御信号が禁止され、データをこれ以上受け付けることができないことをユニット 1 4 に通知する。

20

#### 【0021】

スライス・プライオリティ・ブレークポイントを判断するには、ブレークポイント・アナライザ 4 2 とデュアル・ポートのランダム・アクセス・メモリ（R A M ）4 4 との間でやりとりが行われる。このやりとりはスライス・インターバル期間に行われ、各スライス分析インターバルが終了するたびにクリアされる。スライス・データ累積（slice data accumulation）モードにあるときは、入力バッファ 2 2 がデータを読み出している間、R A M 4 4 はスライス・コードワード・タイプ・データを第 1 アドレス・ポートから受け取る。分析インターバルでそのコードワード・タイプがこれまでに現れるたびに累積された関連長さワードは、R A M 4 4 の第 1 データ・ポートからアキュムレータに送られる。長さワードは、可変長コードワードの生成と同時にプロセッサ 1 4 によって生成される。この長さワードはそれぞれの関連コードワードのビット長を示しており、上記アキュムレータの他方の入力ノードへ送られる。上記アキュムレータの出力は、分析インターバルのその時点における特定コードワード・タイプの更新された総コードワード・ビット数を含んでおり、第 2 データ・ポートからR A M 4 4 にリストアされる。データ分析モードにあるときは、R A M 4 4 データとアドレスのソースは変更される。最高プライオリティ・コードワード・タイプであることを示すアドレス 0 から、最低プライオリティ・コードワード・タイプであることを示す最高コードワード・タイプ値までをカウントするインクリメンタ出力は、R A M 4 4 の第 1 アドレス・ポートへ送られる。従って、第 1 データ・ポートか

30

40

50

らは、プライオリティが順次に低くなっていくコードワード・タイプごとの累積ビット長が上記アキュムレータの一方の入力ノードへ送られる。上記アキュムレータの他方の入力端はアキュムレータの出力端からフィードバックされるので、該アキュムレータは、重要度が低くなっていく各コードワード・タイプの総ビット長の総和をとることになる。総和が H P F R A C B I T S (下述する) 信号の値まで達すると、総和が H P F R A C B I T S 値を越える原因となったビット長合計をもつコードワード・タイプが記録され、その分析インターバルのプライオリティ・ブレークポイント用に使用される。R A M 4 4 の第 2 アドレス・ポートにはインクリメンタ・カウントの遅延されたバージョンが入力され、一方、第 2 データ・ポートはロケーションをクリアし、R A M を次の分析インターバルのアキュムレータ・モードの準備状態にするためにゼロ値を送信する。

10

#### 【 0 0 2 2 】

それぞれのコードワード・タイプについて R A M 4 4 によって累積され、ストアされた長さ値は、R A M 4 4 の第 2 データ・ポートからアナライザ 4 2 へ送られる。データ質問 (data interrogation) 信号 I N T E R R は、アナライザ 4 2 から R A M 4 4 の第 2 アドレス・ポートへ送られる。この質問信号を受けると、R A M 4 4 は、コードワード・タイプと長さデータを累積している途中で次のメモリ・アドレスまでインクリメントするので、次のアドレスからのデータは分析のためにユニット 4 2 へ送られる。最高プライオリティ・データに対応する最高アドレスから始めて、R A M 4 4 は重要度が低くなっていく各コードワード・タイプのコードワード長さ値を累積していく。この累算は入力信号 H P F R A C B I T S で指定されたアドレスに達するまで続けられ、累積されたコードワード長さ値はアナライザ 4 2 に出力される。

20

#### 【 0 0 2 3 】

アナライザ 4 2 は、累積された長さ値と入力信号 H P F R A C B I T S 値を関数として、プライオリティ・ブレークポイントを判断する。この信号は、分析しているスライスの高プライオリティ・チャネルで送るべき目標ビット数を、ユニット 4 2 内のブレークポイント判断回路に通知する。信号 H P F R A C B I T S は、現在分析中のスライスに含まれるビット数と、アルゴリズムにより判断され、高プライオリティ対総ビット数の比率をパーセントで表したパラメータ H P F R A C との積である。H P F R A C は基本的には、例えば、エンコーダ・レート・バッファから受け取ったビット割振り情報とバッファ占有情報を関数として、あるフレーム・インターバル期間に動的に計算されたデータ分割 (data split) パラメータである。分析中のスライスのビット数はマイクロプロセッサ (図示せず) によって計算されるが、パラメータ H P F R A C は米国特許第 5,144,425 号 (Joseph) に記載されているように計算することが可能である。この Joseph 特許には、長さとタイプ・コードワードと、H P F R A C パラメータに対応する値とに応答するブレークポイント・アナライザおよびアキュムレータを含む装置も記載されている。

30

#### 【 0 0 2 4 】

スライス N のコードワードがユニット 4 2 によって分析されている間 (この時点で、空白ワードがデータ・ストリーム中に挿入される)、後続のスライスのコードワードがユニット 1 4 から送られてくると、ユニット 2 2 内のバッファに入れられる。リード・イネーブル信号は分析インターバル期間中禁止されるので、次のスライスでバッファ 2 2 にストアされるコードワード量は増加を続けていく。しかし、これは問題とはならない。つまり、上述したように、ユニット 1 4 は相当量のデータをバッファ 2 2 に送る能力があるが、データは、処理中のイメージがほとんど、あるいはまったくディテールまたはモーション情報をもっていないときのように、比較的長い時間期間の間、存在しないことがよくあるからである。これらのアイドル期間を利用すれば、バッファ 2 2 は、次のデータ・バーストがユニット 1 4 から送られてくる前に、不足分を取り戻し、最終的には読み出しプロセスを通して空にすることが可能になる。

40

#### 【 0 0 2 5 】

ユニット 1 4 が次のコードワードのバーストをバッファ 2 2 へ送る準備状態にあるとき、バッファ 2 2 が一杯か、あるいはほとんど一杯になっていることが起こる。その場合には

50

、バッファ22からのTRANSPORT READY信号が禁止され、ユニット14に関連する出力バッファにデータを送信しないように指示する。これにより、ユニット14の出力バッファは読み出しを行う代わりに、一杯になったままになっている。これは、ユニット14とプライオリティ・プロセッサ20との間でデータが失われるのを防止する安全機構の働きをする。バッファ22の容量が十分に大きければ、TRANSPORT READY信号が使用されることはまれである。

#### 【0026】

これまでに説明してきたシステムでは、非同期入力コードワードは、空白ワードを挿入することによって同期コードワード・データストリームに変換されるので、その後に続くハードウェアは、共通クロックを受けて動作することができる。必要なハードウェアは、单一入力のFIFOバッファ、デュアル・ポートRAMおよびアナライザだけあれば十分であるので、単純化され、しかも、エンコーダからのデータストリームを停止させる回数を最小限にすることができる。

#### 【0027】

プライオリティ・フラグ・ジェネレータ(priority flag generator)40は高プライオリティ・フラグと標準プライオリティ・フラグを生成し、これらのフラグはそれぞれ、プライオリティ・ブレークポイントによって判断された高プライオリティと標準プライオリティのコードワード・シーケンスが存在することを示している。この目的のために、フラグ・ジェネレータ40は、アナライザ42からプライオリティ・ブレークポイントを受けて動作するコンパレータ・ネットワークを備えている。また、ユニット40は前述したようにレコード・ヘッダ・フラグと他のフラグをバッファ36から、タイプおよびバリュー・コードワード(CW)をバッファ36とマルチプレクサ41を経由して受信する。これらのコードワードには、コードワード・バッファ36からのレコード・ヘッダ・フラグが現れたときにマルチプレクサ41によって挿入されたプライオリティ・ブレークポイント値が各スライスのレコード・ヘッダ空白コードワード・バリュー・フィールドに入っている。各スライスのレコード・ヘッダに入っているプライオリティ・ブレークポイント値は、HP/SPプライオリティ・ブレークポイントがどこに(つまり、スライスのどのコードワード・タイプに)現れるかを示しているので、受信側でデコードを行うことが容易になる。トランスポート・プロセッサ50は、ユニット40によって生成されたHPフラグとSPフラグを使用して、その入力コードワード・データストリームを出力HPおよびSPデータストリームに分割する。HPフラグのあとに置かれたコードワードは出力HPデータ経路に送られ、SPフラグのあとに置かれたコードワードは出力SPデータ経路に送られる。ユニット40からの並列出力データは、マルチプレクサ41からのコードワードとバッファ36からのいくつかのフラグ(これらはユニット40によってほぼ未変更のままである)およびユニット40によって生成され、正しくタイミング合わせされたHPフラグとSPフラグを含んでいる。

#### 【0028】

トランスポート・プロセッサ50に入力される前に、ユニット40からの出力コードワード・データストリームはブロック48によって処理され、このブロックでは、ユニット14によるコードワード処理とは逆の処理が行われる。ユニット48は、フラグなどのある種のデータストリーム構成要素を未変更のまま引き渡す。タイプおよびバリュー・コード・データは、ユニット48内のそれぞれのROMによって最大32ビット長までの可変長コードワードに変換される。プライオリティ・プロセッサ20からトランスポート・プロセッサ50へ渡される並列データは、コードワード、長さワード、ユニット32によって生成されたものを含むフラグ、およびユニット40によって生成されたHP、SPフラグを含んでいる。トランスポート・プロセッサ50はHPフラグとSPフラグを受け取ると、プライオリティ・プロセッサ20からのコードワード・データストリームを、ペイロードとヘッダ・セクションを含むデータ・パケットのHPおよびSPストリームに分割し、これらは図3に示すように、出力プロセッサ55によって処理される。トランスポート・プロセッサ50が優先順位付けされた出力HPおよびSPデータストリームをどのように

10

20

30

40

50

作成するかの詳しい説明は、米国特許第5,231,486号(A.A. Acampora)に記載されている。

### 【0029】

図3は、本発明においてHDTVエンコード・システムを採用した装置の例を示したものである。図3に示すシステムは単一のビデオ入力信号を処理しているが、ルミナンス(luminance)成分とクロミナンス(chrominance)成分は別々に処理され、ルミナンス・モーション・ベクトルは圧縮されたクロミナンス成分を生成するために使用されることはある。圧縮されたルミナンス成分とクロミナンス成分はインターブされて、マクロブロックが作られてからコードワード・プライオリティの解析が行われる。

### 【0030】

図2(A)に示す一連のイメージ・フィールド/フレーム・シーケンスは回路305に入力され、フィールド/フレームは図2(B)に示すように並べ替えられる。並べ替えられたシーケンスはコンプレッサ310に入力され、MPEG準拠の形式(フォーマット)にコード化された圧縮フレーム・シーケンスが生成される。この形式は階層形式になっているが、図5には簡略形式で示されている。MPEG階層形式は、各々がそれぞれのヘッダ情報をもつ複数の層からなっている。名目上、各ヘッダは開始コード、それぞれの層に関するデータ、およびヘッダ拡張部分追加用の予備を含んでいる。

### 【0031】

システムによって出力されるMPEG準拠の信号について説明すると、それがなにを意味するかは、(a)ビデオ信号の連続するピクチャ・フィールド/フレームはI、P、Bコード化シーケンスに従ってコード化されることと、(b)ピクチャ・レベルのコード化データはMPEG準拠のスライスまたはブロック・グループでコード化されることであり、その場合、フィールド/フレーム当たりのスライス数は変化することがあり、またスライスあたりのマクロブロック数は変化することがある。Iコード化フレームはフレーム内で圧縮されるフレームであり、この場合、イメージを再生するためにIフレーム圧縮データだけが必要になる。Pコード化フレームはフォワード・モーション補償予測法(forward motion compensated predictive method)に従ってコード化され、この場合、Pフレーム・コード化データは現フレームおよび現フレームの前に現れたIまたはPフレームから生成される。Bコード化フレームは双方向モーション補償予測法(bidirectionally motion compensated predictive method)に従ってコード化される。Bコード化フレーム・データは、現フレームおよび現フレームの前後に現れたIとPフレームから生成される。

### 【0032】

このシステムのコード化出力信号は、フィールド/フレームのグループ、つまり、ボックスL1の行により示されるピクチャのグループ(GOP)にセグメント化される(図5)。各GOP(L2)はヘッダとそのあとに置かれたピクチャ・データのセグメントを含んでいる。GOPヘッダは、水平方向と垂直方向のピクチャ・サイズに関するデータ、アスペクト比、フィールド/フレーム・レート(field/frame rate)、ビット・レート(bit rate)などを含んでいる。

### 【0033】

それぞれのピクチャ・フィールド/フレームに対応するピクチャ・データ(L3)は、ピクチャ・ヘッダとそのあとに置かれたスライス・データ(L4)を含んでいる。ピクチャ・ヘッダはフィールド/フレーム番号とピクチャ・コード・タイプを含んでいる。各スライス(L4)はスライス・ヘッダとそのあとに置かれた複数のデータ・ブロックMBiを含んでいる。スライス・ヘッダはグループ番号と量子化(quantization)パラメータを含んでいる。

### 【0034】

各ブロックMBi(L5)はマクロブロックを表し、ヘッダとそのあとに置かれたモーション・ベクトルおよびコード化係数(coded coefficient)を含んでいる。MBiヘッダはマクロブロック・アドレス、マクロブロック・タイプおよび量子化パラメータを含んでいる。コード化係数は層L6に示されている。各マクロブロックは6ブロックを含んでいる

10

20

30

40

50

。つまり、4つのルミナンス・ブロック、1つのUクロミナンス・ブロック、1つのVクロミナンス・ブロックである(図4参照)。ブロックは、例えば、 $8 \times 8$ のピクセル・マトリックスを表し、これに対して離散コサイン変換(discrete cosine transform - DCT)が施される。4つのルミナンス・ブロックは、例えば、 $16 \times 16$ ピクセル・マトリックスを表す隣接ルミナンス・ブロックの $2 \times 2$ マトリックスになっている。クロミナンス(UとV)ブロックは、4つのルミナンス・ブロックと同じ総面積を表している。つまり、圧縮前に、クロミナンス信号は、ルミナンスに対して水平方向と垂直方向に2のファクター(factor of two)だけサブサンプリングされる。データのスライスは、隣接するマクロブロック・グループで表された面積に対応するイメージの矩形部分を表すデータに対応している。フレームは、垂直方向の60スライス×水平方向の6スライスからなる、360スライスのラスタ・スキャンを含むことが可能である。

#### 【0035】

ブロック係数は、一度に1ブロックずつ、DCTによって得られる。DC係数が最初に現れ、次に、それぞれのDCT AC係数が相対的重要度の順に現れる。ブロック終わりコードEOPは、連続して現れる各データ・ブロックの終わりに付加される。

#### 【0036】

コンプレッサ310からのデータはプライオリタイザ(prioritizer)311によって処理されてからトランスポート・プロセッサ312に送られ、トランスポート・プロセッサはデータを高プライオリティ(HP)構成要素と標準プライオリティ(SP)構成要素にセグメント化する。これらの構成要素は、レート・バッファ(rate buffer)313, 314を経由してそれぞれのフォワード・エラー・コード化ユニット(forward error coding unit)315, 316に入力される。レート・コントローラ(rate controller)318はバッファ313, 314とやりとりして、コンプレッサ310から与えられた平均データ・レートを調整する。そのあと、信号は伝送モデム317に送られ、そこでHPおよびSPデータは、標準6MHz NTSCテレビ・チャネル内のそれぞれの搬送波を直交振幅変調(quadrature amplitude modulate)する。

#### 【0037】

最後に、上述してきた実施例と特許請求の範囲との関係を示すために、カッコ書きにより、その対応関係を以下に示す。

#### 【0038】

『ビデオ信号処理システムにおいて、コードワード・データストリームを優先順位付けされた第1および第2のコードワード・シーケンスにセグメント化することを容易にする装置であって、

一連のデータ・グループを含むビデオ信号コードワード・データストリームを供給する手段(14)と、

前記コードワード・データストリームに応答し、分析インタバル期間に動作して、あるデータ・グループ内のコードワードとコードワードとの間のプライオリティ・ブレークポイントを判断する分析手段(42)を含むコードワード処理手段(30~36, 40~44)と、

前記分析インタバル期間に空白コードワードを生成する手段(26)と、

前記空白コードワードを含めて、出力コードワード・データストリームを前記コードワード処理手段から受信し、該データストリームのフォーマットを、優先順位付けされた第1および第2ノデータ・チャネルを介して伝送するのに適した形式の前記優先順位付けされた第1および第2のコードワード・シーケンスに変換するための伝送処理手段(50)とを具備したことを特徴とする装置。』。

#### 【0039】

##### 【図面の簡単な説明】

【図1】高品位テレビ・データなどのビデオ・データを処理するためのシステムにおいて、本発明によるプライオリティ・プロセッサ搭載装置を含んでいる部分を示すブロック図である。

10

20

30

40

50

【図2】コード化ビデオ信号のイメージ・フィールド／フレーム・シーケンスを絵で表した図である。

【図3】本発明によるコードワード・プライオリタイザ搭載装置を含むHDTVコード化システムを示すブロック図である。

【図4】図3に示すシステムに含まれるコード化/圧縮装置によって作成されるデータブロック生成を絵で表した図である。

【図5】図3に示すシステムに含まれるコード化／圧縮装置から得られるデータ形式を一般化して絵で表した図である。

## 【符号の説明】

- |     |                          |    |

|-----|--------------------------|----|

| 1 4 | プロセッサ                    | 10 |

| 2 6 | コンパレータおよび空白コードワード・ジェネレータ |    |

| 3 0 | レジスタ                     |    |

| 3 2 | コンパレータおよびフラグ・ジェネレータ      |    |

| 3 4 | クロック期間遅延ネットワーク           |    |

| 3 6 | コードワード・バッファ              |    |

| 4 0 | プライオリティ・フラグ・ジェネレータ       |    |

| 4 1 | マルチプレクサ                  |    |

| 4 2 | ブレークポイント・アナライザ           |    |

| 4 4 | R A M                    |    |

| 5 0 | トランスポート・プロセッサ            | 20 |

〔 叴 1 〕

( 义 2 )

【図3】

【図4】

【図5】

---

フロントページの続き

(72)発明者 ロナルド ジョゼフ コルチンスキ

アメリカ合衆国 08610 ニュージャージー州 ハミルトン ジェラマイア アヴェニュー 6

7

合議体

審判長 原 光明

審判官 藤内 光武

審判官 西谷 憲人

(56)参考文献 米国特許第5122875(US,A)

特開平2-214280(JP,A)