(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5118940号

(P5118940)

(45) 発行日 平成25年1月16日(2013.1.16)

(24) 登録日 平成24年10月26日(2012.10.26)

(51) Int.Cl.

H02M 3/155 (2006.01)

F 1

H02M 3/155

H

請求項の数 1 (全 21 頁)

(21) 出願番号 特願2007-286365 (P2007-286365)

(22) 出願日 平成19年11月2日 (2007.11.2)

(65) 公開番号 特開2009-118578 (P2009-118578A)

(43) 公開日 平成21年5月28日 (2009.5.28)

審査請求日 平成22年10月28日 (2010.10.28)

(73) 特許権者 000116024

ローム株式会社

京都府京都市右京区西院溝崎町21番地

(74) 代理人 100085501

弁理士 佐野 静夫

(74) 代理人 100134555

弁理士 林田 英樹

(72) 発明者 和智 貴嗣

京都市右京区西院溝崎町21番地 ローム

株式会社内

審査官 今井 貞雄

(56) 参考文献 特開2006-262103 (JP, A)

)

最終頁に続く

(54) 【発明の名称】電源装置

## (57) 【特許請求の範囲】

## 【請求項 1】

帰還入力される出力電圧と所定の基準電圧との差分を増幅するエラーアンプの出力信号が小さくなるように、出力トランジスタのスイッチング制御を行うことで、入力電圧から所望の出力電圧を生成する電源装置であって、

前記エラーアンプの出力段は、カレントミラー回路を用いて電流信号を出力する構成とされており、前記カレントミラー回路の出力側トランジスタには、抵抗とコンデンサを並列接続して成るブースト回路が接続されていることを特徴とする電源装置。

## 【発明の詳細な説明】

## 【技術分野】

10

## 【0001】

本発明は、入力電圧から所望の出力電圧を生成する電源装置に関するものである。

## 【背景技術】

## 【0002】

従来より、入力電圧から所望の出力電圧を生成する手段としては、高精度で高効率が得られるスイッチング電源装置が広く一般に用いられている。

## 【0003】

なお、上記に関連する従来技術の一例としては、本願出願人による特許文献1、2を挙げることができる。

## 【特許文献1】特開2004-23846号公報

20

【特許文献 2】特開 2004-48835 号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

ところで、上記のスイッチング電源装置は、スイッチング動作によって得られたパルス電圧を LC フィルタで平滑化して、所望の出力電圧を生成する。そのため、出力電圧の発振を防止するには、出力電圧の帰還制御に際して適切な位相補償を行う必要があり、従来のスイッチング電源装置では、 LC フィルタを構成するインダクタや出力コンデンサ、或いは、エラーアンプに接続される位相補償用の抵抗やコンデンサとして、高価で大型の素子を用いなければならず、コストアップや装置規模の増大が招かれていた。

10

【0005】

本発明は、上記の問題点に鑑み、安価な構成でありながら、出力電圧の帰還制御に際して適切な位相補償を行うことが可能な電源装置を提供することを目的とする。

【課題を解決するための手段】

【0006】

上記目的を達成すべく、本発明に係る電源装置は、帰還入力される出力電圧と所定の基準電圧との差分を増幅するエラーアンプの出力信号が小さくなるように、出力トランジスタのスイッチング制御を行うことで、入力電圧から所望の出力電圧を生成する電源装置であって、前記エラーアンプの出力段は、カレントミラー回路を用いて電流信号を出力する構成とされており、前記カレントミラー回路の出力側トランジスタには、抵抗とコンデンサを並列接続して成るブースト回路が接続されている構成（第 1 の構成）とされている。

20

【発明の効果】

【0007】

本発明に係る電源装置であれば、安価な構成でありながら、出力電圧の帰還制御に際して適切な位相補償を行うことが可能となる。

【発明を実施するための最良の形態】

【0008】

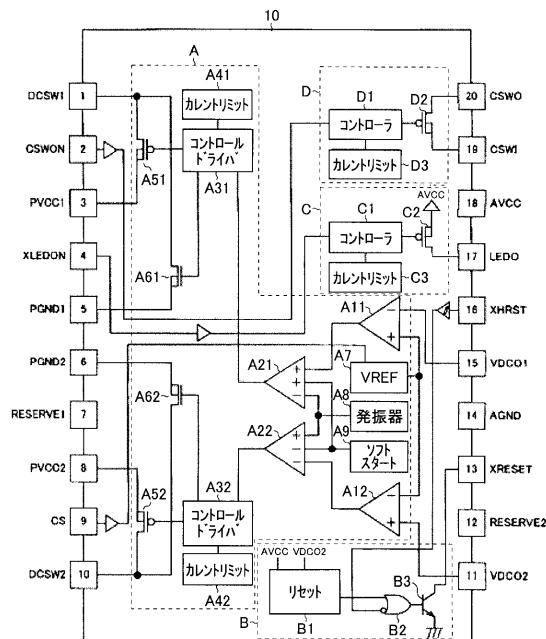

図 1 は、本発明に係る半導体装置の一実施形態を示すブロック図である。

【0009】

まず、本実施形態の半導体装置 10 の概要について述べる。

30

【0010】

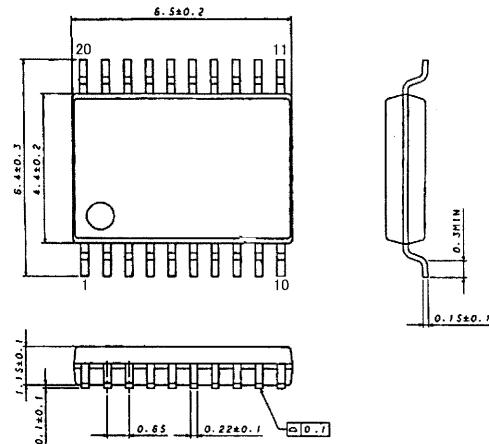

図 1 に示す半導体装置 10 は、DVD [Digital Versatile Disc] ドライブや CD [Compact Disc] ドライブなど、光ディスクドライブ用途向けのシステム電源 LSI である。第 1 の特徴は、3.3 [V] 出力の同期整流型降圧 DC / DC コンバータを内蔵している点である。第 2 の特徴は、1.5 [V] 出力の同期整流型降圧 DC / DC コンバータを内蔵している点である。第 3 の特徴は、各チャンネルの DC / DC コンバータを逆相スイッチング動作させることでリップル干渉を抑制している点である。第 4 の特徴は、ソフトスタート機能 (1 [ms] (Typ.)) を内蔵している点である。第 5 の特徴は、出力電流リミッタや短絡保護機能を内蔵している点である。第 6 の特徴は、エラーアンプの位相補償機能を内蔵している点である。第 7 の特徴は、動作周波数を 3.0 [MHz] (Typ.) としている点である。第 8 の特徴は、リセット回路を内蔵している点である。第 9 の特徴は、リセット検出に際して、アナログ電源電圧 AVCC と DC / DC コンバータ出力を監視している点である。第 10 の特徴は、リセット遅延時間 (50 [ms] (Typ.)) をカウントするためのタイマ回路を内蔵している点である。第 11 の特徴は、LED [Light Emitting Diode] ドライバ用の P チャネル型 MOS [Metal Oxide Semiconductor] 電界効果トランジスタを内蔵している点である。第 12 の特徴は、P チャネル型 MOS 電界効果トランジスタを用いたカレントスイッチを内蔵している点である。第 13 の特徴は、シャットダウン機能を内蔵している点である。第 14 の特徴は、図 2 に示すパッケージを採用している点である。なお、図 2 中に記載した寸法値の単位はミリメートルである。

40

【0011】

50

上記の特徴を有する本実施形態の半導体装置 10 は、図 1 に示すように、DC / DC コンバータ部 A と、リセット部 B と、LED ドライバ部 C と、カレントスイッチ部 D と、を集積化して成る。

【0012】

DC / DC コンバータ部 A は、エラーアンプ A11、A12 と、PWM [ Pulse Width Modulation ] コンバレータ A21、A22 と、コントロールドライバ A31、A32 と、カレントリミット回路 A41、A42 と、P チャネル型 MOS 電界効果トランジスタ A51、A52 と、N チャネル型 MOS 電界効果トランジスタ A61、A62 と、基準電圧生成回路 A7 と、発振器 A8 と、ソフトスタート回路 A9 と、を有して成る。なお、DC / DC コンバータ部 A は、1.5 [ V ] の出力電圧を生成する第 1 の DC / DC コンバータと、3.3 [ V ] の出力電圧を生成する第 2 の DC / DC コンバータを用いて、2 チャンネルの出力電圧を生成するものである。10

【0013】

リセット部 B は、リセット制御回路 B1 と、論理和演算器 B2 と、n p n 型バイポーラトランジスタ B3 と、を有して成る。

【0014】

LED ドライバ部 C は、コントローラ C1 と、P チャネル型 MOS 電界効果トランジスタ C2 と、カレントリミット回路 C3 と、を有して成る。

【0015】

カレントスイッチ部 D は、コントローラ D1 と、P チャネル型 MOS 電界効果トランジスタ D2 と、カレントリミット回路 D3 と、を有して成る。20

【0016】

また、本実施形態の半導体装置 10 は、外部との電気的接続を確立する手段として、20 本の外部端子 (1 ピン ~ 20 ピン) を有して成る。

【0017】

図 3 は、外部端子のピン番号、端子名、及び、機能を示した対応表である。また、図 4 は、外部端子のピン番号、端子名、等価回路、及び、機能を示した対応表である。

【0018】

DC SW1 端子 (1 ピン) は、1.5 [ V ] の出力電圧を生成する DC / DC コンバータのスイッチング端子である。なお、DC SW1 端子と PGND1 端子 (5 ピン) との間には、静電保護用クランパが接続されている。30

【0019】

CSWON 端子 (2 ピン) は、カレントスイッチ制御端子であり、CSWON 端子がハイレベルとされているときに、カレントスイッチ部 C がオン状態となる。なお、CSWON 端子は、TTL [ Transistor-Transistor-Logic ] レベル入力端子とされており、その信号経路には、静電保護用抵抗 (4 [ k ] (Typ.)) が接続されている。また、CSWON 端子と AVCC 端子 (18 ピン) との間、及び、CSWON 端子と AGND 端子 (14 ピン) との間には、それぞれ静電保護用ダイオードが接続されている。また、CSWON 端子と AGND 端子との間には、プルダウン抵抗 (100 [ k ] (Typ.)) が接続されている。40

【0020】

PVCC1 端子 (3 ピン) は、1.5 [ V ] の出力電圧を生成する DC / DC コンバータ用の電源入力端子である。なお、PVCC1 端子と AVCC 端子との間には、静電保護用ダイオードが接続されている。また、PVCC1 端子と PGND1 端子との間や、AVCC 端子と PGND1 端子との間には、それぞれ静電保護用クランパが接続されている。

【0021】

XLEDON 端子 (4 ピン) は、LED ドライバ制御端子であり、XLEDON 端子がロー レベルとされているとき、LED ドライバ部 C がオン状態となる。なお、XLEDON 端子は、TTL レベル入力端子とされており、その信号経路には、静電保護用抵抗 (4 [ k ] (Typ.)) が接続されている。また、XLEDON 端子と AVCC 端子との間、50

及び、XLEDON端子とAGND端子との間には、それぞれ静電保護用ダイオードが接続されている。また、XLEDON端子とAGND端子との間には、プルダウン抵抗(100 [k] (Typ.))が接続されている。

【0022】

P G N D 1 端子(5ピン)は、1.5 [V]の出力電圧を生成するDC/DCコンバータ用のGND端子である。

【0023】

P G N D 2 端子(6ピン)は、3.3 [V]の出力電圧を生成するDC/DCコンバータ用のGND端子である。

【0024】

R E S E R V E 1 端子(7ピン)は、通常時には用いられないリザーブ端子であり、通常時には接地しておくことが望ましい。

10

【0025】

P V C C 2 端子(8ピン)は、3.3 [V]の出力電圧を生成するDC/DCコンバータ用の電源入力端子である。なお、P V C C 2 端子とAVCC端子との間には、静電保護用ダイオードが接続されている。また、P V C C 2 端子とP G N D 2 端子との間や、AVCC端子とP G N D 2 端子との間には、それぞれ静電保護用クランパが接続されている。

【0026】

C S 端子(9ピン)は、チップセレクト端子であり、C S 端子がハイレベルであるときに、半導体装置10が動作状態となる。なお、C S 端子は、TTLレベル入力端子とされており、その信号経路には、静電保護用抵抗(4 [k] (Typ.))が接続されている。また、C S 端子とAVCC端子との間、及び、C S 端子とAGND端子との間には、それぞれ静電保護用ダイオードが接続されている。

20

【0027】

D C S W 2 端子(10ピン)は、3.3 [V]の出力電圧を生成するDC/DCコンバータのスイッチング端子である。なお、D C S W 2 端子とP G N D 2 端子との間には、静電保護用クランパが接続されている。

【0028】

V D C O 2 端子(11ピン)は、3.3 [V]の出力電圧を生成するDC/DCコンバータ用のフィードバック端子である。

30

【0029】

R E S E R V E 2 端子(12ピン)は、通常時には用いられないリザーブ端子であり、通常時には接地しておくことが望ましい。

【0030】

X R E S E T 端子(13ピン)は、リセット出力端子である。なお、X R E S E T 端子は、オープンコレクタ出力形式とされている。また、X R E S E T 端子とAVCC端子との間、及び、X R E S E T 端子とAGND端子との間には、それぞれ静電保護用ダイオードが接続されている。

【0031】

A G N D 端子(14ピン)は、アナログGND端子である。

40

【0032】

V D C O 1 端子(15ピン)は、1.5 [V]の出力電圧を生成するDC/DCコンバータ用のフィードバック端子である。

【0033】

X H R S T 端子(16ピン)は、外部リセット端子であり、X H R S T 端子がローレベルとされているとき、リセット部Bがリセット状態となる。なお、X H R S T 端子は、TTLレベルヒステリシス入力端子とされており、その信号経路には、静電保護用抵抗(4 [k] (Typ.))が接続されている。また、X H R S T 端子とAVCC端子との間、及び、X H R S T 端子とAGND端子との間には、それぞれ静電保護用ダイオードが接続されている。

50

## 【0034】

LEDO端子(17ピン)は、LEDドライバ出力端子である。

## 【0035】

AVCC端子(18ピン)は、アナログ電源端子である。

## 【0036】

CSWI端子(19ピン)は、カレントスイッチ入力端子である。

## 【0037】

CSWO端子(20ピン)は、カレントスイッチ出力端子である。

## 【0038】

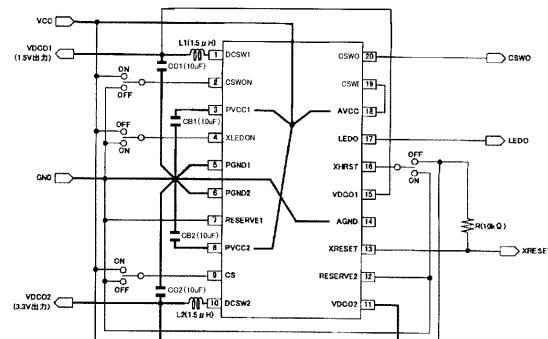

次に、外部端子の端子処理について、図5に示す応用回路図を参照しながら、詳細な説明を行う。 10

## 【0039】

図5は、外部端子の端子処理を説明するための応用回路図である。

## 【0040】

基板パターンについて、PVCC1端子、PVCC2端子、及び、AVCC端子は、基板上の電源に接続することが望ましい。また、PGND1端子、PGND2端子及び、AGND端子は、基板上のGNDに1ポイントで接続することが望ましい。また、PVCC1端子、PVCC2端子、及び、AVCC端子には、太く短い配線を行い、インピーダンスを十分低くすることが望ましい。また、PGND1端子、PGND2端子、及び、AGND端子についても、太く短い配線を行い、インピーダンスを十分低くすることが望ましい。DC/DCコンバータの出力電圧(VDCO1、VDCO2)については、図示のように出力コンデンサCO1、CO2の両端から取り出すことが望ましい。また、DC/DCコンバータは、基板パターンや周辺部品により性能が影響を受けるため、周辺回路の設計は十分検討することが望ましい。 20

## 【0041】

外付け素子について、PVCC端子とPGND1端子及びPGND2端子との間に接続されるバイパスコンデンサCB1、CB2としては、等価直列抵抗(ESR[Equivalent Series Resistance])の低いセラミックコンデンサを使用し、かつ、できる限り半導体装置10の近傍に配置することが望ましい。また、これに限らず、インダクタやコンデンサ等の外付け素子は、できる限り半導体装置10の近傍に配置し、特に大電流が流れる部分については、太く短い配線を行うことが望ましい。 30

## 【0042】

図6は、上記構成から成る半導体装置10の電気的特性を示す表である。なお、図6に示した電気的特性は、特に指定のない限り、PVCC1=PVCC2=AVCC=5.0[V]、周囲温度Ta=25[°C]での数値を示している。

## 【0043】

次に、上記構成から成る半導体装置10の諸機能について説明する。

## 【0044】

まず、DC/DCコンバータ部Aの機能について説明する。

## 【0045】

DC/DCコンバータ部Aは、第1出力電圧VDCO1を生成する第1の同期整流型DC/DCコンバータと、第2出力電圧VDCO2を生成する第2の同期整流型DC/DCコンバータと、を有して成る。 40

## 【0046】

外付け素子としては、降圧用のインダクタンスL1、L2(推奨1.5[μH])、出力コンデンサCO1、CO2(推奨10[μF])、並びに、PVCC1端子とPGND1端子との間、及び、PVCC2端子とPGND2端子との間にそれぞれ接続されるバイパスコンデンサCB1、CB2(推奨10[μF])を必要とする(図5を参照)。

## 【0047】

DC/DCコンバータ部Aは、UVLO[Under Voltage Lock Out]解除電圧(3.7

50

5 [ V ] (Typ. ) ) で動作を開始する。

【 0 0 4 8 】

エラーアンプ A 1 1 は、非反転入力端 ( + ) に印加される基準電圧  $V_{REF}$  と、反転入力端 ( - ) に印加される出力電圧  $V_{DCO1}$  との差分を増幅して、誤差電圧  $V_{err1}$  を生成する。 PWM コンパレータ A 2 1 は、第 1 非反転入力端 ( + ) に印加される誤差電圧  $V_{err1}$  と第 2 非反転入力端 ( + ) に印加されるソフトスタート電圧  $V_{ss}$  のいずれか低い方と、反転入力端 ( - ) に印加される鋸波電圧  $V_{saw}$  とを比較し、その結果に応じたデューティ比の比較信号  $V_{cmp1}$  を生成する。コントロールドライバ A 3 1 は、比較信号  $V_{cmp1}$  に基づいてトランジスタ 5 1、6 1 のオン / オフ制御を行い、DCSW1 端子にパルス電圧を生成する。これを外付けの LC フィルタ (図 5 の L 1、CO1) で平滑化することにより、第 1 出力電圧  $V_{DCO1}$  (1.5 [ V ] (Typ. ) ) を生成する。

10

【 0 0 4 9 】

エラーアンプ A 1 2 は、反転入力端 ( - ) に印加される基準電圧  $V_{REF}$  と、非反転入力端 ( - ) に印加される出力電圧  $V_{DCO2}$  との差分を増幅して、誤差電圧  $V_{err2}$  を生成する。 PWM コンパレータ A 2 2 は、第 1 反転入力端 ( - ) に印加される誤差電圧  $V_{err2}$  と第 2 反転入力端 ( - ) に印加されるソフトスタート電圧  $V_{ss}$  のいずれか低い方と、非反転入力端 ( + ) に印加される鋸波電圧  $V_{saw}$  とを比較し、その結果に応じたデューティ比の比較信号  $V_{cmp2}$  を生成する。コントロールドライバ A 3 2 は、比較信号  $V_{cmp2}$  に基づいてトランジスタ 5 2、6 2 のオン / オフ制御を行い、DCSW2 端子にパルス電圧を生成する。これを外付けの LC フィルタ (図 5 の L 2、CO2) で平滑化することにより、第 2 出力電圧  $V_{DCO2}$  (3.3 [ V ] (Typ. ) ) を生成する。

20

【 0 0 5 0 】

なお、DC / DC コンバータ部 A は、第 1、第 2 の DC / DC コンバータを互いに逆相でオン / オフ制御する構成とされている。このような構成とすることにより、第 1、第 2 の DC / DC コンバータ相互間のリップル干渉を抑制することが可能となる。

【 0 0 5 1 】

また、DC / DC コンバータ部 A の最大出力電流については、許容損失を超えないよう に、500 [ mA ] 程度が想定されている。

【 0 0 5 2 】

また、DC / DC コンバータ部 A の起動時には、ソフトスタート回路 A 9 (1.0 [ ms ] (Typ. ) ) の働きによって、第 1 出力電圧  $V_{DCO1}$ 、及び、第 2  $V_{DCO2}$  を徐々に立ち上げるように、トランジスタ 5 1、6 1 及びトランジスタ 5 2、6 2 のスイッチング制御が行われる。

30

【 0 0 5 3 】

すなわち、DC / DC コンバータ部 A の起動直後には、出力電圧  $V_{DCO1}$ 、 $V_{DCO2}$  がゼロであるため、誤差電圧  $V_{err1}$ 、 $V_{err2}$  が極めて大きくなる。従って、誤差電圧  $V_{err1}$ 、 $V_{err2}$  と鋸波電圧  $V_{saw}$  を比較すると、比較信号  $V_{cmp1}$ 、 $V_{cmp2}$  のデューティ比が過大となり、負荷に過大な電流が流れてしまうことになる。

【 0 0 5 4 】

そこで、本実施形態の半導体装置 10 は、誤差電圧  $V_{err1}$ 、 $V_{err2}$  とは別に、ソフトスタート電圧  $V_{ss}$  を PWM コンパレータ A 2 1、A 2 2 に入力しておき、ソフトスタート電圧  $V_{ss}$  が誤差電圧  $V_{err1}$ 、 $V_{err2}$  よりも低いときには、誤差電圧  $V_{err1}$ 、 $V_{err2}$  に依らず、より低いソフトスタート電圧  $V_{ss}$  と鋸波電圧  $V_{saw}$  との比較結果に応じて、比較信号  $V_{cmp1}$ 、 $V_{cmp2}$  のデューティ比を決定する構成とされている。

40

【 0 0 5 5 】

なお、本実施形態の半導体装置 10 において、ソフトスタート回路 A 9 は、コンデンサに所定の定電流を流し込むことで、装置の起動後から緩やかに上昇を開始するソフトスタート電圧  $V_{ss}$  を生成する構成とされている。

【 0 0 5 6 】

このように、ソフトスタート回路 A 9 を備えた構成であれば、装置の起動時における負荷への過大電流を防止することが可能となる。

【0057】

次に、リセット部 B の機能について説明する。

【0058】

リセット部 B は、セットに搭載される D S P [Digital Signal Processor] などにリセット信号を送出する手段である。なお、リセット信号の出力端に相当する X R E S E T 端子は、トランジスタ B 3 のオープンコレクタ出力であり、外部素子として、プルアップ抵抗 R (10 [kΩ]) を必要とする(図 5 を参照)。

【0059】

リセット制御回路 B 1 は、アナログ電源電圧 A V C C が 3.7 [V] (Typ.) 以下、或いは、第 2 出力電圧 V D C O 2 が 2.7 [V] (Typ.) 以下であることを検出したとき、論理和演算器 B 2 の第 1 入力端に印加する制御信号をハイレベルとし、トランジスタ B 3 をオンさせる。これにより、X R E S E T 端子は、ローレベル(リセット状態)となる。

【0060】

また、リセット制御回路 B 1 は、半導体装置 10 の起動時には、アナログ電源電圧 A V C C と第 2 出力電圧 V D C O 2 の起動が検出されてから、半導体装置 10 に内蔵されているタイマ回路(不図示)によって 50 [ms] (Typ.) がカウントされた後に、トランジスタ B 3 をオフさせて、X R E S E T 端子をハイレベル(リセット解除)とする。

【0061】

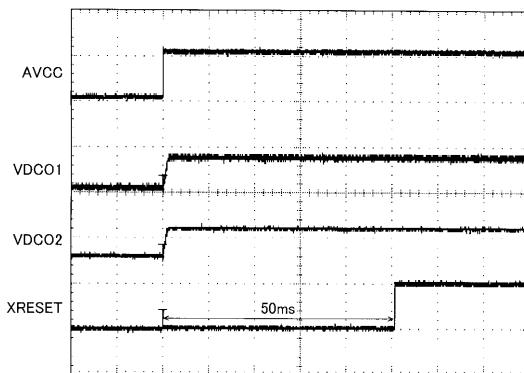

図 7 は、リセット部 B の起動動作を説明するためのタイミングチャートであり、上から順に、A V C C 端子、V D C O 1 端子、V D C O 2 端子、及び、X R E S E T 端子の各電圧波形が示されている。

【0062】

また、X H R S T 端子は、論理和演算器 B 2 の第 2 入力端(反転入力端)に接続されている。従って、X H R S T 端子をローレベルとすることで、トランジスタ B 3 は、リセット制御回路 B 1 からの制御信号に依ることなく、オン状態に遷移され、X R E S E T 端子は、ローレベル(リセット状態)とされる。なお、X H R S T 端子を用いたリセット制御の場合、先述のタイマ回路(50 [ms] (Typ.))は動作しない。

【0063】

次に、L E D ドライバ部 C の機能について説明する。

【0064】

L E D ドライバ部 C は、セットに搭載される L E D の点消灯制御を行う手段であり、X L E D O N 端子がローレベルのときにオン状態となる。なお、L E D ドライバ部 C に内蔵されるトランジスタ C 2 のオン抵抗は、最大 10 [Ω] であり、最大出力電流としては、50 [mA] 程度が想定されている。

【0065】

次に、カレントスイッチ部 D の機能について説明する。

【0066】

カレントスイッチ部 D は、セットに搭載されるピックアップ(特にレーザダイオード)への電源供給をオン/オフ制御する手段であり、C S W O N 端子がハイレベルのときにオン状態となる。なお、C S W I 端子側にアナログ電源電圧 A V C C などを印加し、C S W O 端子側に負荷を接続する形で使用される。また、カレントスイッチ部 D に内蔵されるトランジスタ D 2 のオン抵抗は、最大 1.0 [Ω] であり、最大出力電流としては、100 [mA] 程度が想定されている。

【0067】

上記したように、本実施形態の半導体装置 10 は、2 チャンネルの D C / D C コンバータ部 A に加えて、リセット部 B 、L E D ドライバ部 C 、及び、カレントスイッチ部 D を 1 チップに内蔵した構成とされている。このような構成とすることにより、システム電源 I C 周辺部の回路群を 1 チップ化することができ、D V D や C D の電源部を容易に構成する

10

20

30

40

50

ことが可能となる。

【0068】

また、本実施形態の半導体装置10であれば、リセット部B、LEDドライバ部C、及び、カレントスイッチ部Dを各単体のIC、ないしは、ディスクリート部品で形成する構成に比べて、セット規模の縮小や応答速度の向上、及び、消費電力の低減を実現することが可能となる。

【0069】

次に、出力電圧VDCO1、VDCO2の起動について説明する。

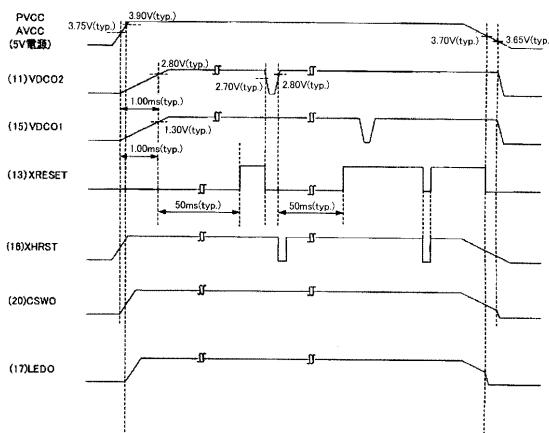

【0070】

図8は、出力電圧の起動波形を示すタイミングチャートであり、上から順に、電源端子(PVCC、AVCC)、VDCO2端子、VDCO1端子、XRESET端子、XHRS端子、CSWO端子、及び、LEDO端子の各電圧波形を示している。なお、図8は、CS=5[V]、CSWON=5[V]、XLEDON=0[V]に設定されている場合の様子を示したものである。

10

【0071】

電源端子(PVCC、AVCC)の電圧レベルが3.75[V]に達すると、UVLOが解除され、DC/DCコンバータ部Aが動作を開始する。このとき、第1のDC/DCコンバータと第2のDC/DCコンバータは、同時に起動される。なお、ソフトスタート期間は1[m s]に設定されている。また、半導体装置10の起動に際して、DC/DCコンバータ部Aの各出力は、軽負荷の状態としておくことが望ましい。

20

【0072】

リセット部Bは、アナログ電源電圧AVCCと第2出力電圧VDCO2の双方を監視しており、それぞれが3.7[V]、2.7[V]に達してから所定期間(50[m s])の経過後に、XRESET端子をハイレベル(リセット解除)とする(図7を参照)。

【0073】

リセット状態が解除された後、例えば、第2出力電圧VDCO2が2.7[V]を下回ると、リセット部Bは、XRESET端子をローレベル(リセット状態)とし、その後、第2出力電圧VDCO2が2.8[V]を上回ると、その時点から50[m s]経過した後に、リセット部Bは、XRESET端子をハイレベル(リセット解除)とする。一方、第1出力電圧VDCO1は監視されていないため、これが低下した場合でも、XRESET端子がローレベル(リセット状態)とされることはない。

30

【0074】

また、XHRS端子によるホストリセットに関して、XHRS端子がローレベルとされている間、リセット部Bは、XRESET端子をローレベル(リセット状態)とし、XHRS端子がハイレベルに戻された時点で、リセット部Bは、XRESET端子を同時にハイレベル(リセット解除)とする。ただし、電圧モニタによるリセット解除から50[m s]以内の期間は、XHRS端子によるホストリセットが無効とされている。

【0075】

次に、過電流/短絡保護機能について説明する。

【0076】

40

DC/DCコンバータ部A、LEDドライバ部C、及び、カレントスイッチ部Dの各出力動作を制御するコントロールドライバA31、A32、コントローラC1、及び、コントローラD1には、過電流/短絡保護機能を実現する手段として、カレントリミット回路A41、A42、C3、D3が各々接続されている。すなわち、XRESET端子以外の各出力端子には、いずれも過電流/短絡保護機能が内蔵されているので、突発的なGNDショートによる破壊から半導体装置10を保護することが可能となる。

【0077】

まず、DC/DCコンバータ部Aの過電流検出動作について説明する。

【0078】

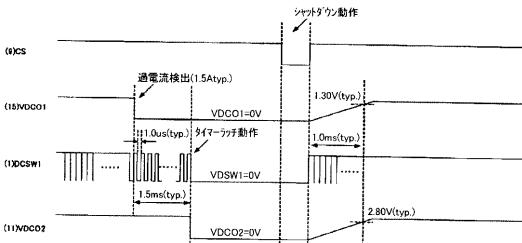

図9は、DC/DCコンバータ部Aの過電流検出動作を説明するためのタイミングチャ

50

ートであり、上から順に、CS端子、VDCO1端子、DCSW1端子、及び、VDCO2端子の各電圧波形を示している。なお、図9では、第1出力電圧VDCO1を生成する第1のDC/DCコンバータで過電流が生じた際の様子が例示されている。

#### 【0079】

カレントリミット回路A41で過電流(1.5[A](Typ.))が検出されると、所定期間(1.0[μs](Typ.))だけ、PVCC端子から出力コンデンサCO1への充電が禁止され、第1出力電圧VDCO1の生成動作が停止される。一方、カレントリミット回路A42で過電流が検出されていない限り、第2出力電圧VDCO2の生成動作は継続される。第1出力電圧VDCO1の生成動作を停止してから上記所定期間が経過すると、第1出力電圧VDCO1の生成動作が再開され、カレントリミット回路A41で再度の過電流判定が行われる。このとき、過電流状態が解消されなければ、先述と同様、所定期間だけ、第1出力電圧VDCO1の生成動作が停止される。

10

#### 【0080】

このような状態が所定期間(1.5[m s](Typ.))だけ継続すると、短絡保護機能(タイマーオフラッシュ機能)が働いて、第1出力電圧VDCO1と第2出力電圧VDCO2の生成動作がいずれも停止される。DC/DCコンバータ部Aの出力動作を再開するためには、半導体装置10に対して電源を再投入するか、或いは、CS端子を用いたシャットダウン動作を行えばよい。

#### 【0081】

なお、第2出力電圧VDCO2を生成する第2のDC/DCコンバータで過電流が生じた場合には、第2出力電圧VDCO2の生成動作が断続的に停止された後、最終的には、第1出力電圧VDCO1と第2出力電圧VDCO2の生成動作がいずれも停止される。

20

#### 【0082】

次に、LEDドライバ部Cの過電流検出動作について説明する。なお、カレントスイッチ部Dの過電流検出動作についても、LEDドライバ部Cと同様であるため、重複した説明は省略する。

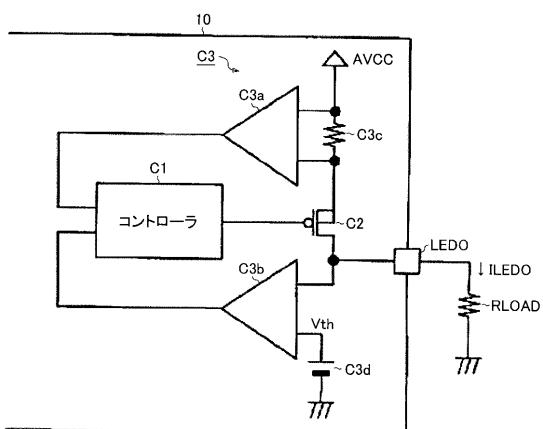

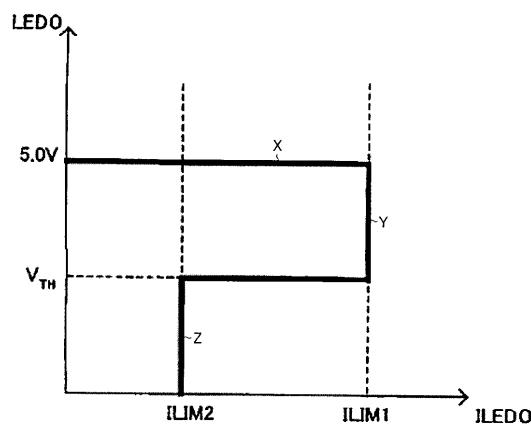

#### 【0083】

図10は、LEDドライバ部Cに内蔵されたカレントリミット回路C3の一構成例を示す回路図である。また、図11は、LEDに対する出力電流ILEDと出力電圧LEDとの関係を示す相関図である。

30

#### 【0084】

図10に示すように、カレントリミット回路C3は、コンパレータC3a、C3bと、センス抵抗C3cと、直流電圧源C3dと、を有して成る。コンパレータC3aは、センス抵抗C3cの両端電圧(出力電流ILEDの大小に応じて変動する電圧信号)が所定値に達しているか否かを判定する手段であり、コンパレータC3bは、出力電圧LEDが所定値Vthに達しているか否かを判定する手段である。

#### 【0085】

コントローラC1は、コンパレータC3aの出力信号に基づいて、出力電流ILEDが第1閾値ILIM1に達しているか否かを判断し、出力電流ILEDが第1閾値ILIM1に達していなければ、出力電圧LEDを所定値(5.0[V])に維持するように、トランジスタC2の導通度(オン抵抗)を制御する(図11の定電圧制御期間Xを参照)。一方、出力電流ILEDが第1閾値に達していると判断した場合、コントローラC1は、出力電流ILEDを第1閾値ILIM1に維持するように、トランジスタC2の導通度(オン抵抗)を制御して、出力電圧LEDを低下させていく。

40

#### 【0086】

このとき、コントローラC1は、コンパレータC3bの出力信号に基づいて、出力電圧LEDが閾値電圧Vthを下回っているか否かを判断し、出力電圧LEDが閾値電圧Vthを下回っていなければ、引き続き、出力電流ILEDを第1閾値ILIM1に維持するように、トランジスタC2の導通度(オン抵抗)を制御して、出力電圧LEDを低下させる(図11の第1電流制限期間Yを参照)。一方、出力電圧LEDが閾値電圧

50

$V_{th}$ を下回っていると判断した場合、コントローラC1は、出力電流ILEDを第1閾値ILIM1よりも低い第2閾値ILIM2に維持するように、トランジスタC2の導通度（オン抵抗）を制御して、出力電圧LEDをさらに低下させていく（図11の第2電流制限期間Zを参照）。

【0087】

このように、2段階のカレントリミット動作を行うことにより、半導体装置10の安全性を高めることが可能となる。なお、LED端子で過電流が検出された場合でも、他の出力端子（VDCO1端子、VDCO2端子、及び、CSWO端子）については、通常動作が継続される。

【0088】

次に、過電圧ミュート機能について説明する。

【0089】

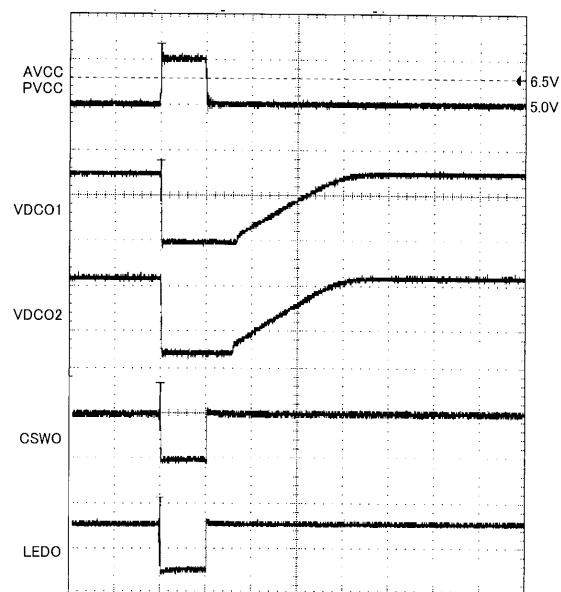

図12は、過電圧ミュート機能を説明するためのタイミングチャートであり、上から順番に、電源端子（AVCC、PVCC）、VDCO1端子、VDCO2端子、CSWO端子、及び、LED端子の各電圧波形が示されている。

【0090】

図1では明示していないが、半導体装置10には、過電圧による半導体装置10の誤動作を防止する手段として、過電圧ミュート回路が内蔵されている。図12に示すように、電源電圧（AVCC、PVCC）が6.5[V]（Typ.）以上になると、過電圧ミュート機能が働き、DC/DCコンバータ部Aはスイッチングを停止する。これにより、過電圧による半導体装置10の誤動作を防止することが可能となる。

【0091】

次に、UVLO機能について説明する。

【0092】

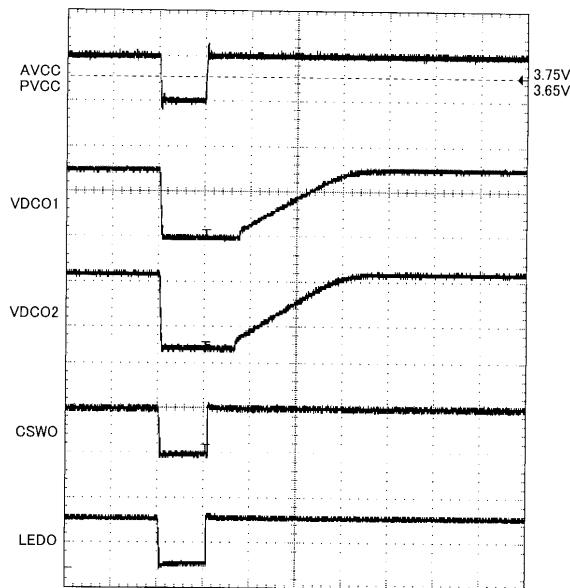

図13は、UVLO機能を説明するためのタイミングチャートであり、上から順番に、電源端子（AVCC、PVCC）、VDCO1端子、VDCO2端子、CSWO端子、及び、LED端子の各電圧波形が示されている。

【0093】

図1では明示していないが、半導体装置10には、減電圧による半導体装置10の誤動作を防止する手段として、UVLO回路が内蔵されている。図13に示すように、電源電圧（AVCC、PVCC）が3.65[V]（Typ.）以下（LEDドライバ部Cは3.70[V]（Typ.）以下）になると、UVLO機能が働き、DC/DCコンバータ部Aはスイッチングを停止する。これにより、減電圧による半導体装置10の誤動作を防止することが可能となる。なお、電源電圧（AVCC、PVCC）が3.75[V]（Typ.）以上（LEDドライバ部Cは3.90[V]（Typ.）以上）に戻ると、シャットダウンが解除されて、出力電圧の生成動作が再起動される。

【0094】

次に、CS端子を用いたシャットダウン機能について説明する。

【0095】

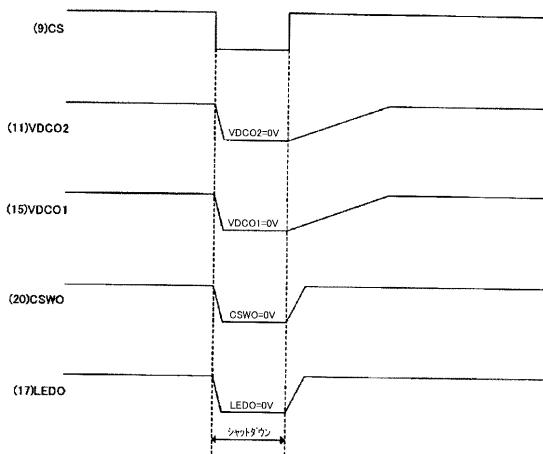

図14は、CS端子を用いたシャットダウン機能を説明するためのタイミングチャートであり、上から順番に、CS端子、VDCO2端子、VDCO1端子、CSWO端子、及び、LED端子の各電圧波形が示されている。なお、図14は、AVCC = PVCC = 5[V]、CSWON = 5[V]、XLEDON = 0[V]に設定されている場合の様子を示したものである。

【0096】

図14に示すように、CS端子がローレベルとされたときには、先述の保護機能（UVLO機能など）が動作したときと同様、DC/DCコンバータ部Aがスイッチングを停止する。また、LEDドライバ部Cやカレントスイッチ部Dの出力も0[V]となる。その後、CS端子がハイレベルとされたときには、シャットダウンが解除されて、各々の出力動作が再開される。

10

20

30

40

50

## 【0097】

なお、上記のシャットダウンに際して、VDCO1端子及びVDCO2端子の各端子電圧は、DC/DCコンバータ部Aの出力段を形成するローサイドスイッチ（トランジスタA61、A62）のオン抵抗を介してディスチャージされる。また、CSWO端子及びLEDO端子の各端子電圧は、半導体装置10に内蔵された抵抗（図1には不図示）を介してディスチャージされる。

## 【0098】

次に、サーマルシャットダウン機能について説明する。

## 【0099】

図1では明示していないが、半導体装置10には、その熱的破壊を防止する手段としてサーマルシャットダウン回路が内蔵されている。チップ温度が $T_{jmax} = 175$  [ ] (Typ.)に達すると、サーマルシャットダウン機能が働き、DC/DCコンバータ部Aはスイッチングを停止する。このような制御により、半導体装置10を熱的暴走から保護することが可能となる。

10

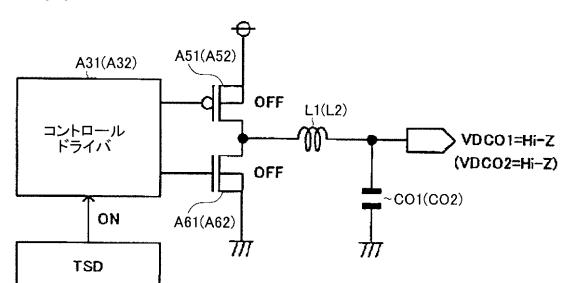

## 【0100】

なお、上記のサーマルシャットダウン時には、図15に示すように、DC/DCコンバータ部Aの出力段を形成するハイサイドのトランジスタ（A51、A52）とローサイドのトランジスタ（A61、A62）がいずれもオフ状態とされ、VDCO1端子及びVDCO2端子がいずれもハイインピーダンス状態とされる。すなわち、先述のCS端子を用いたシャットダウン時と異なり、サーマルシャットダウン時には、VDCO1端子及びVDCO2端子の各端子電圧がディスチャージされることなく維持される。従って、異常高温下でローサイドのトランジスタ（A61、A62）に電流が流れることはないので、素子の破壊やさらなる温度上昇を回避することが可能となる。なお、LEDO端子及びCSWO端子の各端子電圧については、先述のCS端子を用いたシャットダウン時と同様、半導体装置10に内蔵された抵抗（図1には不図示）を介してディスチャージされる。

20

## 【0101】

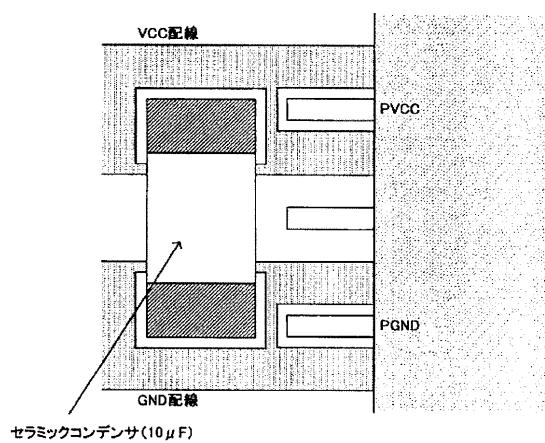

次に、DC/DCコンバータ部Aの位相補償について説明する。

## 【0102】

半導体装置10は、エラーアンプA11、A12の位相補償を装置内部で行っており、インダクタL1、L2及び出力コンデンサCO1、CO2については、安定動作を行うために推奨値（1.5 [  $\mu$ H]、10 [  $\mu$ F] 以上）を用いることが望ましい。入力コンデンサは、ESRの低い10 [  $\mu$ F] 以上のセラミックコンデンサを使用することが望ましい。なお、重負荷時でも安定動作を行えるように、PVC端子とPGND端子との間のバイパスコンデンサCB1、CB2は、図16に示すように、半導体装置10から最小となる距離に配置することが望ましい。出力コンデンサCO1、CO2としては、セラミックコンデンサを使用することが可能であり、これにより低ノイズ及び低リップルの電源を構成することができる。また、DC/DCコンバータ部Aの出力は、図5に示したように、できる限り出力コンデンサCO1、CO2の両端から取り出すことが望ましい。

30

## 【0103】

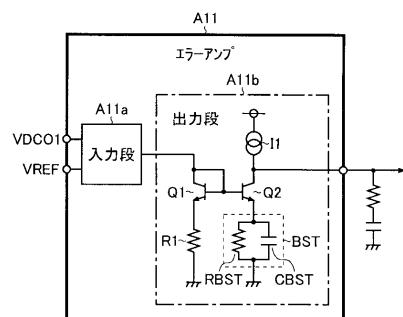

次に、エラーアンプA11、A12内部での位相補償について説明する。

40

## 【0104】

図17は、エラーアンプA11の一構成例（特に出力段周辺）を示す回路図である。なお、エラーアンプA12は、エラーアンプA11と同様の構成であるため、ここでは重複した説明を省略する。

## 【0105】

本構成例のエラーアンプA11は、出力電圧帰還型の電流出力アンプであり、第1出力電圧VDCO1と基準電圧VREFが差動入力される入力段A11aと、入力段A11aからの電圧信号を電流信号に変換して出力する出力段A11bと、を有して成る。

## 【0106】

出力段A11bは、コレクタが入力段A11aの出力端に接続されるn-p-n型バイポー

50

ラトランジスタQ1と、ベースがトランジスタQ1のベース及びコレクタに接続されるn-p-n型バイポーラトランジスタQ2と、トランジスタQ1のエミッタと接地端との間に接続される抵抗R1と、トランジスタQ2のコレクタと電源端との間に接続される定電流源I1と、トランジスタQ2のエミッタと接地端との間に接続されるブースト回路BSTとを有して成り、トランジスタQ2のコレクタから電流信号を出力する構成とされている。なお、ブースト回路BSTは、抵抗RBSTとコンデンサCBSTを並列接続して成る。

#### 【0107】

このように、エラーアンプA11の出力段A11bは、一対のトランジスタQ1、Q2から成るカレントミラー回路を用いて電流信号を出力する構成であり、これにブースト回路BSTが挿入された形となっている。

10

#### 【0108】

ブースト回路BSTは、電流信号の周波数が低周波数領域であるときには、所定のインピーダンスを有する抵抗回路として機能し、電流信号の周波数が高周波数領域であるときには、そのインピーダンスが低下して、トランジスタQ2のエミッタと接地端との間を交流的に短絡するバイパス回路として機能する。

#### 【0109】

従って、電流信号の周波数が高周波数領域であるときには、トランジスタQ1、Q2から成るカレントミラー回路のミラー比が大きくなるので、エラーアンプA11のゲインを高めることができとなり、延いては、位相余裕（ゲインが0[dB]であるときの位相）を維持することが可能となる。

20

#### 【0110】

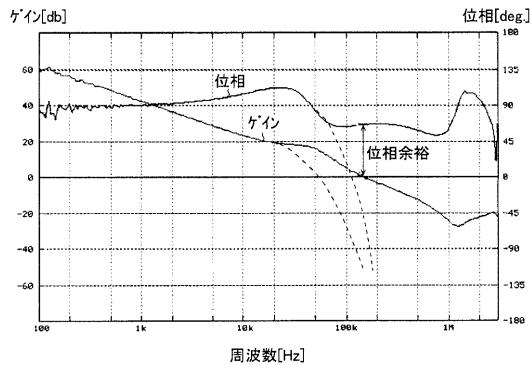

図18は、エラーアンプA11の周波数特性を示す図であり、横軸は周波数、縦軸は位相とゲインを示している。なお、本図では、インダクタL1及び出力コンデンサCO1の特性値を各々1.5[μH]、10[μF]に設定した場合の周波数特性を示している。また、図中の実線は本発明（ブースト回路あり）の挙動を示すものであり、破線は従来構成（ブースト回路なし）の挙動を示すものである。

20

#### 【0111】

図18に示すように、本発明の構成であれば、インダクタL1及び出力コンデンサCO1として特性値の小さい素子を用いた場合であっても、エラーアンプA11の位相余裕を十分に維持することができるので、上記の特性値が多少ばらついても、DC/DCコンバータを安定に動作させることが可能となる。また、エラーアンプA11の出力端に接続する位相補償コンデンサの容量値を数[pF]まで小さくすることもできるため、これを半導体装置10に内蔵することが可能となる。

30

#### 【0112】

次に、動作周波数の安定化技術について説明する。

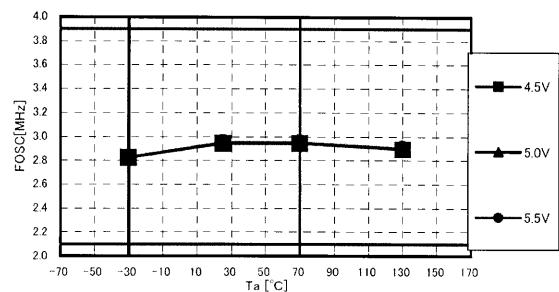

#### 【0113】

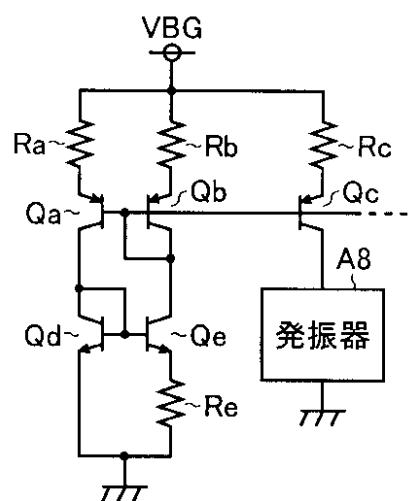

周囲温度や電源電圧の変動に伴って、DC/DCコンバータ部Aの動作周波数が所望の設定値(3[MHz])から大きく変動してしまうと、先述の位相補償に影響を及ぼし、出力リップルが増大してしまう。そこで、半導体装置10では、発振器A8の発振周波数を決定する定電流Icの温度特性並びに電源電圧特性をいずれもフラットとするように、定電流源の回路構成に工夫を凝らしている。

40

#### 【0114】

図19は、定電流源の一構成例を示す回路図である。

#### 【0115】

本図に示すように、本構成例の定電流源は、p-n-p型バイポーラトランジスタトランジスタQa、Qb、Qcと、n-p-n型バイポーラトランジスタQd、Qeとを有して成る。

#### 【0116】

トランジスタQa、Qb、Qcのエミッタは、それぞれ、抵抗Ra、Rb、Rcを介して、バンドギャップ電圧VBGの印加端に接続されている。トランジスタQa、Qb、Qcのベースは、いずれもトランジスタQbのコレクタに接続されている。トランジスタQ

50

a のコレクタは、トランジスタ Q d のコレクタに接続されている。トランジスタ Q b のコレクタは、トランジスタ Q e のコレクタに接続されている。トランジスタ Q e のコレクタは、発振器 A 8 の定電流入力端に接続されている。トランジスタ Q d 、 Q e のベースは、いずれもトランジスタ Q d のコレクタに接続されている。トランジスタ Q d のエミッタは接地端に接続されている。トランジスタ Q e のエミッタは、抵抗 R e を介して接地端に接続されている。

【 0 1 1 7 】

上記したように、本構成例の定電流源は、定電流 I c の電源電圧特性をフラットするために、バンドギャップ電源回路で生成されたバンドギャップ電圧 V B G を駆動電圧として用いている。

10

【 0 1 1 8 】

また、本構成例の定電流源は、トランジスタ Q d のベース・エミッタ間降下電圧 V f の温度特性と、抵抗 R e の温度特性を互いに相殺させることで、定電流 I c の温度特性をフラットとしている。

【 0 1 1 9 】

このような定電流源を用いることにより、図 2 0 で示すように、DC / DC コンバータ部 A の動作周波数を所望の設定値 (3 [MHz]) に維持することが可能となる。

【 0 1 2 0 】

次に、DC / DC コンバータ部 A の特性向上について説明する。

【 0 1 2 1 】

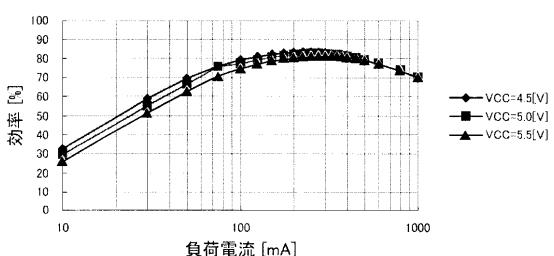

DC / DC コンバータ部 A の動作周波数が高速であるほど、出力端に接続されるインダクタ L 1 、 L 2 や出力コンデンサ C O 1 、 C O 2 の特性値を小さくしても、図 2 1 に示すように、出力リップルを小さく抑えることができる。一方、DC / DC コンバータ部 A の動作周波数を高速にすると、スイッチング損失が大きくなり、変換効率が低下してしまう。

20

【 0 1 2 2 】

そこで、DC / DC コンバータ部 A では、動作周波数を従来の 1.5 [MHz] から 3 [MHz] まで高めた上で、その変換効率を低下させない工夫を凝らしている。

【 0 1 2 3 】

まず、トランジスタ A 5 1 、 A 6 1 、及び、トランジスタ A 5 2 、 A 6 2 を同時オフさせる期間 (デッドタイム) の最適化を行い、スイッチング損失の低減を行っている。

30

【 0 1 2 4 】

動作周波数を 3 [MHz] に設定した場合、PWM 信号の周期は、333.3 [ns] となり、PWM 信号の最小パルス幅は、60 [ns] 前後 (最小デューティ 20 %) となる。従って、PWM 信号のデッドタイムとしては、5 ~ 10 [ns] という極めて短い時間を正確に設定しなければならない。

【 0 1 2 5 】

なお、従来構成では、抵抗とコンデンサから成る RC 時定数回路を用いて、デッドタイムを設定していたが、このような構成では、素子ばらつきの影響が大きいため、デッドタイムを正確に設定することができない。

【 0 1 2 6 】

そこで、本発明では、素子ディレイ (トランジスタから成るインバータの論理反転遅延時間) を用いて、PWM 信号のデッドタイムを設定する構成とされている。このような構成とすることにより、RC 時定数回路を用いる従来構成に比べて、PWM 信号のデッドタイムを正確に設定することができるので、DC / DC コンバータ部 A のスイッチング損失を低減することが可能となる。

40

【 0 1 2 7 】

図 2 2 は、負荷電流と変換効率の相関関係を示す図である。本図に示すように、半導体装置 1 0 であれば、DC / DC コンバータ部 A の動作周波数を 3 [MHz] に設定し、インダクタ L 1 、 L 2 や出力コンデンサ C O 1 、 C O 2 の特性値を小さく設定しても、十分高い効率 (特に負荷電流として数百 [mA] を流す高負荷領域における効率) を得ること

50

が可能となる。

【0128】

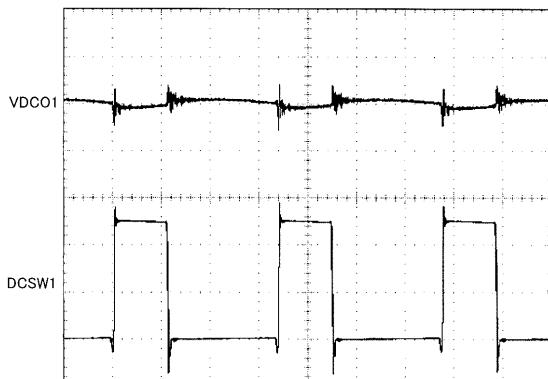

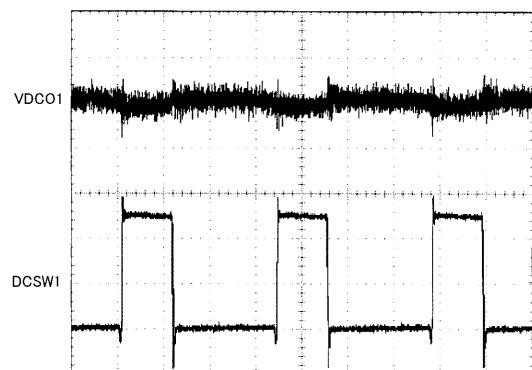

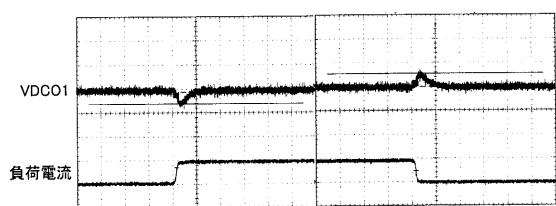

また、P W M信号のデッドタイムを合わせ込む過程で、トランジスタA51、A61、及び、トランジスタA52、A62のゲートに付随する寄生コンデンサの容量値を見積もることができたため、これに応じてドライバの電流能力を調整し、スルーレートの最適化を行っている。このような調整により、出力スパイクノイズの低減（図23の例では、第1出力電圧V D C O 1について、 $p p$ 値 = 20 [mV]程度まで低減）や、出力負荷応答の改善（図24の例では、第1出力電圧V D C O 1について、 $V$  = 25 [mV]程度に改善）を実現することが可能となる。

【0129】

10

なお、上記の実施形態では、D V D ドライブやC D ドライブなど、光ディスクドライブ用途向けのシステム電源L S Iに本発明を適用した構成を例に挙げて説明を行ったが、本発明の適用対象はこれに限定されるものではなく、その他の電源装置にも広く適用することが可能である。

【0130】

また、本発明の構成は、上記実施形態のほか、発明の主旨を逸脱しない範囲で種々の変更を加えることが可能である。

【産業上の利用可能性】

【0131】

20

本発明は、例えば、D V D ドライブやC D ドライブなど、光ディスクドライブ用途向けのシステム電源L S Iに好適な技術である。

【図面の簡単な説明】

【0132】

【図1】は、本発明に係る半導体装置の一実施形態を示すブロック図である。

【図2】は、半導体装置10の外形寸法図である。

【図3】は、外部端子のピン番号、端子名、及び、機能を示した対応表である。

【図4】は、外部端子のピン番号、端子名、等価回路、及び、機能を示した対応表である。

【図5】は、外部端子の端子処理を説明するための応用回路図である。

【図6】は、半導体装置10の電気的特性を示す表である。

30

【図7】は、リセット部Bの起動動作を説明するためのタイミングチャートである。

【図8】は、出力電圧の起動波形を示すタイミングチャートである。

【図9】は、D C / D C コンバータ部Aの過電流検出動作を説明するためのタイミングチャートである。

【図10】は、L E D ドライバ部Cに内蔵されたカレントリミット回路C3の一構成例を示す回路図である。

【図11】は、出力電流I L E D Oと出力電圧L E D Oの関係を示す相関図である。

【図12】は、過電圧ミュート機能を説明するためのタイミングチャートである。

【図13】は、U V L O機能を説明するためのタイミングチャートである。

【図14】は、C S 端子を用いたシャットダウン機能を説明するためのタイミングチャートである。

40

【図15】は、サーマルシャットダウン時のスイッチング状態を示す回路図である。

【図16】は、バイパスコンデンサC B 1、C B 2の一配置例を示す模式図である。

【図17】は、エラーアンプの一構成例（特に出力段周辺）を示す回路図である。

【図18】は、エラーアンプA11の周波数特性を示す図である。

【図19】は、定電流源の一構成例を示す回路図である。

【図20】は、動作周波数の温度特性を示す図である。

【図21】は、D C / D C コンバータ部Aの出力リップルを示す図である。

【図22】は、負荷電流と変換効率の相関関係を示す図である。

【図23】は、D C / D C コンバータ部Aの出力スパイクノイズを示す図である。

50

【図24】は、DC/DCコンバータ部Aの出力負荷応答を示す図である。

【符号の説明】

【0133】

|                 |                     |    |

|-----------------|---------------------|----|

| 10              | 半導体装置(システム電源LSI)    |    |

| A               | DC/DCコンバータ部         |    |

| A 11、A 12       | エラーアンプ              |    |

| A 11 a          | 入力段                 |    |

| A 11 b          | 出力段                 |    |

| A 21、A 22       | PWMコンパレータ           | 10 |

| A 31、A 32       | コントロールドライバ          |    |

| A 41、A 42       | カレントリミット回路          |    |

| A 51、A 52       | Pチャネル型MOS電界効果トランジスタ |    |

| A 61、A 62       | Nチャネル型MOS電界効果トランジスタ |    |

| A 7             | 基準電圧生成回路            |    |

| A 8             | 発振器                 |    |

| A 9             | ソフトスタート回路           |    |

| B               | リセット部               |    |

| B 1             | リセット制御回路            |    |

| B 2             | 論理和演算器              |    |

| B 3             | n-p-n型バイポーラトランジスタ   | 20 |

| C               | LEDドライバ部            |    |

| C 1             | コントローラ              |    |

| C 2             | Pチャネル型MOS電界効果トランジスタ |    |

| C 3             | カレントリミット回路          |    |

| C 3 a、C 3 b     | コンパレータ              |    |

| C 3 c           | センス抵抗               |    |

| C 3 d           | 直流電圧源               |    |

| D               | カレントスイッチ部           |    |

| D 1             | コントローラ              |    |

| D 2             | Pチャネル型MOS電界効果トランジスタ | 30 |

| D 3             | カレントリミット回路          |    |

| L 1、L 2         | インダクタ               |    |

| C O 1、C O 2     | 出力コンデンサ             |    |

| C B 1、C B 2     | バイパスコンデンサ           |    |

| Q 1、Q 2         | n-p-n型バイポーラトランジスタ   |    |

| R 1             | 抵抗                  |    |

| I 1             | 定電流源                |    |

| B S T           | ブースト回路              |    |

| R B S T         | 抵抗                  |    |

| C B S T         | コンデンサ               | 40 |

| Q a、Q b、Q c     | p-n-p型バイポーラトランジスタ   |    |

| Q d、Q e         | n-p-n型バイポーラトランジスタ   |    |

| R a、R b、R c、R e | 抵抗                  |    |

【図1】

【図2】

【図3】

| 端子 NO. | 端子名      | 機能                                |

|--------|----------|-----------------------------------|

| 1      | DCSW1    | 1.5V 出力 DC/DC コンバータスイッチング端子       |

| 2      | CSWON    | カレントスイッチ制御端子(CSWON=High にて ON 状態) |

| 3      | PVCC1    | 1.5V 出力 DC/DC コンバータ用電源入力端子        |

| 4      | XLEDON   | LED ドライバ制御端子(XLEDON=Low にて ON 状態) |

| 5      | PGND1    | 1.5V 出力 DC/DC コンバータ用 GND 端子       |

| 6      | PGND2    | 3.3V 出力 DC/DC コンバータ用 GND 端子       |

| 7      | RESERVE1 | 弊社リザーブ端子                          |

| 8      | PVCC2    | 3.3V 出力 DC/DC コンバータ用電源入力端子        |

| 9      | CS       | チップセレクト端子(CS=High にて IC 効動)       |

| 10     | DCSW2    | 3.3V 出力 DC/DC コンバータスイッチング端子       |

| 11     | VDCO1    | 3.3V 出力 DC/DC コンバータ用フィードバック端子     |

| 12     | RESERVE2 | 弊社リザーブ端子                          |

| 13     | XRESET   | リセット出力端子                          |

| 14     | AGND     | アナログ GND 端子                       |

| 15     | VDCO1    | 1.5V 出力 DC/DC コンバータ用フィードバック端子     |

| 16     | XHRST    | 外部リセット端子(XHRST=Low にてリセット状態)      |

| 17     | LEDO     | LED ドライバ出力端子                      |

| 18     | AVCC     | アナログ電源端子                          |

| 19     | CSWI     | カレントスイッチ入力端子                      |

| 20     | CSWO     | カレントスイッチ出力端子                      |

【図4】

| 端子 NO.      | 端子名                   | 等価回路 | 機能                                            |

|-------------|-----------------------|------|-----------------------------------------------|

| 2<br>4<br>9 | CSWON<br>XLEDON<br>CS |      | TTLレベル入力端子<br>※1 (2)CSWON,(4)XLEDON ブルダウントラップ |

| 16          | XHRST                 |      | TTLレベルヒステリシス入力端子                              |

| 10          | DCSW1<br>DCSW2        |      | 同期整流用パワーモスドライバ<br>※1 静破保護用クランバ                |

| 13          | XRESET                |      | オープンコレクタ出力                                    |

| 3<br>8      | PVCC1<br>PVCC2        |      | 各電源入力端子保護ダイオード<br>※1 静破保護用クランバ                |

【図5】

【図6】

| 項目                 | 記号        | 条件                                                    | 値           | 単位  |

|--------------------|-----------|-------------------------------------------------------|-------------|-----|

| [動作電源電圧]           |           |                                                       |             |     |

| PVCC1端子電圧          | PVCC1     | PVCC1=PVCC2=AVCC                                      | 4.5~5.5     | V   |

| PVCC2端子電圧          | PVCC2     | PVCC1=PVCC2=AVCC                                      | 4.5~5.5     | V   |

| AVCC端子電圧           | AVCC      | PVCC1=PVCC2=AVCC                                      | 4.5~5.5     | V   |

| [システム電源LSI]        |           |                                                       |             |     |

| 消費電流               | ICC       | VDCO1=VDCO2=5V<br>CSW0=5V,XLEDON=0V<br>XHRST=5V,CS=5V | 1.25~2.50   | mA  |

| シャットダウン電流          | ISHUT     | CS=0V                                                 | 0.42~0.80   | mA  |

| CS' "H" レベル入力電圧    | VCSH      |                                                       | 2.0         | V   |

| CS' "L" レベル入力電圧    | VCSL      |                                                       | 0.8         | V   |

| CS入力電流1            | ICS1      | CS=0V                                                 | -5.0~5.0    | μA  |

| CS入力電流2            | ICS2      | CS=5V                                                 | -5.0~5.0    | μA  |

| [DC/DCコンバータ部]      |           |                                                       |             |     |

| VDCO1電圧            | VDCO1     |                                                       | 1.455~1.545 | V   |

| VDCO2電圧            | VDCO2     |                                                       | 3.201~3.399 | V   |

| 発振周波数              | FOSC      |                                                       | 2.1~3.9     | MHz |

| DCSW1ローサイドスイッチオン抵抗 | RONH1     |                                                       | 0.40~0.60   | Ω   |

| DCSW1ローサイドスイッチオフ抵抗 | RONL1     |                                                       | 0.30~0.50   | Ω   |

| DCSW2ローサイドスイッチオン抵抗 | RONH2     |                                                       | 0.40~0.60   | Ω   |

| DCSW2ローサイドスイッチオフ抵抗 | RONL2     |                                                       | 0.30~0.50   | Ω   |

| ソフトスタート時間          | TSOFT     | 無負荷                                                   | 0.6~1.8     | ms  |

| [リセット部]            |           |                                                       |             |     |

| リセットオン電圧           | VRSTON1   | AVCC電圧監視                                              | 3.60~3.80   | V   |

| VRSTON2            | VDCO2電圧監視 |                                                       | 2.59~2.81   | V   |

| リセットヒステリシス幅        | VRSTHYS1  | AVCC電圧監視                                              | 140~260     | mV  |

| VRSTHYS2           | VDCO2電圧監視 |                                                       | 70~130      | mV  |

| リセット出力シングル電圧       | VRSINK    | $I_{sink}=1.0mA$                                      | 0.3         | V   |

| リセット出力カーリー電流       | IRLK      |                                                       | -5.0~5.0    | μA  |

| リセット運延時間           | TRST      |                                                       | 30~70       | ms  |

| XHRSTスレッシュホールド電圧   | VXHRST    | XRESET=0Vで判定                                          | 0.8~1.6     | V   |

| VXHRHYS            |           |                                                       | 70~330      | mV  |

| XHRST入力電流          | IXHRST    |                                                       | -5.0~5.0    | μA  |

| [LEDドライバ部]         |           |                                                       |             |     |

| LEDドライバオン抵抗        | RLED0     | XLEDON=0V                                             | 5~10        | Ω   |

| XLEDON "H" レベル入力電圧 | VLEDH     |                                                       | 2.0         | V   |

| XLEDON "L" レベル入力電圧 | VLEDL     |                                                       | 0.8         | V   |

| XLEDON入力電流1        | ILED1     | XLEDON=0V                                             | -5.0~5.0    | μA  |

| XLEDON入力電流2        | ILED2     | XLEDON=5V                                             | 33~100      | μA  |

| [カレントスイッチ部]        |           |                                                       |             |     |

| カレントスイッチドライバオン抵抗   | RCSW      | CSW0=5V                                               | 0.5~1.0     | Ω   |

| CSW0 "H" レベル入力電圧   | VCSWH     |                                                       | 2.0         | V   |

| CSW0 "L" レベル入力電圧   | VCSWL     |                                                       | 0.8         | V   |

| CSW0入力電流1          | ICSW1     | CSW0=0V                                               | -5.0~5.0    | μA  |

| CSW0入力電流2          | ICSW2     | CSW0=5V                                               | 33~100      | μA  |

【図7】

【図9】

【図8】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図19】

【図20】

【図18】

【図21】

【図22】

【図 2 3】

【図 2 4】

---

フロントページの続き

(58)調査した分野(Int.Cl. , DB名)

H 02 M 3 / 155