# ${\bf (19)}\ World\ Intellectual\ Property\ Organization$

International Bureau

(10) International Publication Number

PCT

#### (43) International Publication Date 11 June 2009 (11.06.2009)

- (51) International Patent Classification: *G06F 12/02* (2006.01)

- (21) International Application Number:

PCT/IL2008/001232

(22) International Filing Date:

17 September 2008 (17.09.2008)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

| 60/996,782 | 5 December 2007 (05.12.2007) | US |

|------------|------------------------------|----|

| 61/006,805 | 31 January 2008 (31.01.2008) | US |

| 61/064,853 | 31 March 2008 (31.03.2008)   | US |

| 61/071,465 | 30 April 2008 (30.04.2008)   | US |

| 61/129,608 | 8 July 2008 (08.07.2008)     | US |

|            |                              |    |

- (71) Applicant (for all designated States except US): DENS-BITS TECHNOLOGIES LTD. [IL/IL]; Building 30, Flr 3, Matam Industrial Park, P.O.Box 15111, 31015 Haifa (IL).

- (72) Inventor; and

- (75) Inventor/Applicant (for US only): KATZ, Michael [IL/IL]; 75 Moriah Ave., 34616 Haifa (IL).

- WO 2009/072102 A2

- (74) Agent: PEARL COHEN ZEDEK LATZER; 5 Shenkar Street, P.O. Box 12704, Herzlia 46733 (IL).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MT, NL, NO, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### Published:

without international search report and to be republished upon receipt of that report

# (54) Title: SYSTEM AND METHODS EMPLOYING MOCK THRESHOLDS TO GENERATE ACTUAL READING THRESHOLDS IN FLASH MEMORY DEVICES

(57) Abstract: A method for reading at least one page within an erase sector of a flash memory device, the method comprising computing at least one mock reading threshold; using the at least one mock reading threshold to perform at least one mock read operation of at least a portion of at least one page within the erase sector, thereby to generate a plurality of logical values; defining a set of reading thresholds based at least partly on the plurality of logical values; and reading at least one page in the erase sector using the set of reading thresholds.

# SYSTEM AND METHODS EMPLOYING MOCK THRESHOLDS TO GENERATE ACTUAL READING THRESHOLDS IN FLASH MEMORY DEVICES

## 5 REFERENCE TO CO-PENDING APPLICATIONS

10

15

20

25

30

Priority is claimed from the following co-pending applications: US Provisional Application No. 61/129,608, filed July 8, 2008 and entitled "A Method for Acquiring and Tracking Detection Thresholds in Flash Devices", US Provisional Application No. 60/996,782, filed December 5, 2007 and entitled "Systems and Methods for Using a Training Sequence in Flash Memory", US Provisional Application No. 61/064,853, filed March 31, 2008 and entitled "Flash Memory Device with Physical Cell Value Deterioration Accommodation and Methods Useful in Conjunction Therewith", US Provisional Application No. 61/006,805, filed January 31, 2008 and entitled "A Method for Extending the Life of Flash Devices" and US Provisional Application No. 61/071,465, filed April 30, 2008 and entitled "Systems and Methods for Temporarily Retiring Memory Portions".

Other co-pending applications include: US Provisional Application No. 60/960,207, filed September 20, 2007 and entitled "Systems and Methods for Coupling Detection in Flash Memory", US Provisional Application No. 61/071,467, filed April 30, 2008 and entitled "Improved Systems and Methods for Determining Logical Values of Coupled Flash Memory Cells", US Provisional Application No. 60/960,943, filed October 22, 2007 and entitled "Systems and methods to reduce errors in Solid State Disks and Large Flash Devices" and US Provisional Application No. 61/071,469, filed April 30, 2008 and entitled "Systems and Methods for Averaging Error Rates in Non-Volatile Devices and Storage Systems", US Provisional Application No. 60/996,027, filed October 25, 2007 and entitled "Systems and Methods for Coping with Variable Bit Error Rates in Flash Devices", US Provisional Application No. 61/071,466, filed April 30, 2008 and entitled "Systems and Methods for Multiple Coding Rates in Flash Devices", US Provisional Application No. 61/071,466, filed April 30, 2008 and entitled "Systems and Methods for Multiple Coding Rates in Flash Devices", US Provisional Application No. 61/006,120, filed December 19, 2007 and entitled

5

10

15

25

30

"Systems and Methods for Coping with Multi Stage Decoding in Flash Devices", US Provisional Application No. 61/071,464, filed April 30, 2008 and entitled "A Decoder Operative to Effect A Plurality of Decoding Stages Upon Flash Memory Data and Methods Useful in Conjunction Therewith", US Provisional Application No. 61/006,385, filed January 10, 2008 and entitled "A System for Error Correction Encoder and Decoder Using the Lee Metric and Adapted to Work on Multi-Level Physical Media", US Provisional Application No. 61/064,995, filed April 8, 2008 and entitled "Systems and Methods for Error Correction and Decoding on Multi-Level Physical Media", US Provisional Application No. 60/996,948, filed December 12, 2007 and entitled "Low Power BCH/RS Decoding: a Low Power Chien-Search Implementation", US Provisional Application No. 61/071,487, filed May 1, 2008 and entitled "Chien-Search System Employing a Clock-Gating Scheme to Save Power for Error Correction Decoder and other Applications", US Provisional Application No. 61/071,468, filed April 30, 2008 and entitled "A Low Power Chien-Search Based BCH/RS Recoding System for Flash Memory, Mobile Communications Devices and Other Applications", US Provisional Application No. 61/006,806, filed January 31, 2008 and entitled "Systems and Methods for using a Erasure Coding in Flash memory", US Provisional Application No. 61/071.486, filed May 1, 2008 and entitled "Systems and Methods for Handling Immediate Data Errors in Flash Memory", US Provisional Application No. 61/006,078, filed December 18, 2007 and entitled "Systems and Methods for Multi Rate Coding in 20 . Multi Level Flash Devices", US Provisional Application No. 61/064,923, filed April 30, 2008 and entitled "Apparatus For Coding At A Plurality Of Rates In Multi-Level Flash Memory Systems, And Methods Useful In Conjunction Therewith", US Provisional Application No. 61/064,760, filed March 25, 2008 and entitled "Hardware efficient implementation of rounding in fixed-point arithmetic", US Provisional Application No. 61/071,404, filed April 28, 2008 and entitled "Apparatus and Methods for Hardware-Efficient Unbiased Rounding", US Provisional Application No. 61/136,234, filed August 20, 2008 and entitled "A Method Of Reprogramming A Non-Volatile Memory Device Without Performing An Erase Operation", US Provisional Application No. 61/129,414, filed June 25, 2008 and entitled "Improved Programming Speed in Flash Devices Using

Adaptive Programming", and several other co-pending patent applications being filed concurrently (same day).

#### FIELD OF THE INVENTION

5

10

15

20

25

30

The present invention relates generally to flash memory devices.

#### BACKGROUND OF THE INVENTION

Conventional flash memory technology and related technologies are described in the following publications inter alia:

- [1] Paulo Cappelletti, Clara Golla, Piero Olivo, Enrico Zanoni, "Flash Memories", Kluwer Academic Publishers, 1999

- [2] G. Campardo, R. Micheloni, D. Novosel, "VLSI-Design of Non-Volatile Memories", Springer Berlin Heidelberg New York, 2005

- [3] G. Proakis, "Digital Communications," 3rd ed., New York: McGraw-Hill, 1995.

- [4] "4-Bit-Per-Cell NROM Reliability". Boaz Eitan, Guy Cohen, Assaf Shappir, Eli Lusky, Amichai Givant, Meir Janai, Ilan Bloom, Yan Polansky, Oleg Dadashev, Avi Lavan, Ran Sahar and Eduardo Maayan. Appears on the website of Saifun.com.

- [5] Portal, J. M. et al. "EEPROM Diagnosis Based on Threshold Voltage Embedded Measurement". Journal of Electronic Testing: Theory and Applications Volume 21, Issue 1 (January 2005)

- [6] Himeno, T.; Matsukawa, N.; Hazama, H.; Sakui, K.; Oshikiri, M.; Masuda, K.; Kanda, K.; Itoh, Y.; Miyamoto, J. "A new technique for measuring threshold voltage distribution in flash EEPROM devices." Microelectronic Test Structures, 1995. ICMTS 1995. Proceedings of the 1995 International Conference on Volume, Issue, 22-25 Mar 1995 Page(s):283 287 Digital Object Identifier 10.1109/ICMTS.1995.513988

- [7] G. Tao, A. Scarpa, J. Dijkstra, W. Stidl and F. Kuper, "Data retention prediction for modern floating gate non-volatile memories", Microelectronics Reliability, Volume 40, Issues 8-10, August-October 2000, Pages 1561-1566

[8] Esseni, D., "Trading-off programming speed and current absorption in flash memories with the ramped-gate programming technique", IEEE Transactions on Electron Devices, 47(4), April 2000.

[9] Portal, J. M. "EEPROM Memory: Threshold voltage built in self diagnosis", ITC International Test Conference, Paper 2.1.

5

The disclosures of all publications and patent documents mentioned in the specification, and of the publications and patent documents cited therein directly or indirectly, are hereby incorporated by reference.

#### SUMMARY OF THE INVENTION

5

10

15

20

25

The following terms may be construed either in accordance with any definition thereof appearing in the prior art literature or in accordance with the specification, or as follows:

Bit error rate (BER) = a parameter that a flash memory device manufacturer commits to vis a vis its customers, expressing the maximum proportion of wrongly read bits (wrongly read bits/ total number of bits) that users of the flash memory device need to expect at any time during the stipulated lifetime of the flash memory device e.g. 10 years.

Block = a set of flash memory device cells which must, due to physical limitations of the flash memory device, be erased together. Also termed erase sector, erase block.

Cell: A component of flash memory that stores one bit of information (in single-level cell devices) or n bits of information (in a multi-level device having 2 exp n levels). Typically, each cell comprises a floating-gate transistor. n may or may not be an integer. "Multi-level" means that the physical levels in the cell are, to an acceptable level of certainty, statistically partitionable into multiple distinguishable regions, plus a region corresponding to zero, such that digital values each comprising multiple bits can be represented by the cell. In contrast, in single-level cells, the physical levels in the cell are assumed to be statistically partitionable into only two regions, one corresponding to zero and one other, non-zero region, such that only one bit can be represented by a single-level cell.

Charge level: the measured voltage of a cell which reflects its electric charge.

Cycling: Repeatedly writing new data into flash memory cells and repeatedly erasing the cells between each two writing operations.

Decision regions: Regions extending between adjacent decision levels, e.g. if decision levels are 0, 2 and 4 volts respectively, the decision regions are under 0 V, 0 V - 2 V, 2V - 4 V, and over 4 V.

Demapping: basic cell-level reading function in which a digital n-tuple originally received from an outside application is derived from a physical value representing a physical state in the cell having a predetermined correspondence to the digital n-tuple.

Digital value or "logical value": n-tuple of bits represented by a cell in flash memory capable of generating 2 exp n distinguishable levels of a typically continuous physical value such as charge, where n may or may not be an integer.

Erase cycle: The relatively slow process of erasing a block of cells (erase sector), each block typically comprising more than one page, or, in certain non-flash memory devices, of erasing a single cell or the duration of so doing. An advantage of erasing cells collectively in blocks as in flash memory, rather than individually, is enhanced programming speed: Many cells and typically even many pages of cells are erased in a single erase cycle.

- Erase-write cycle: The process of erasing a block of cells (erase sector), each block typically comprising a plurality of pages, and subsequently writing new data into at least some of them. The terms "program" and "write" are used herein generally interchangeably.

- 25 Flash memory: Non-volatile computer memory including cells that are erased block by block, each block typically comprising more than one page, but are written into and read from, page by page. Includes NOR-type flash memory, NAND-type flash memory, and PRAM, e.g. Samsung PRAM, inter alia, and flash memory devices with any suitable number of levels per cell, such as but not limited to 2, 4, or 8.

15

Logical page: a portion of typically sequential data, whose amount is typically less than or equal to a predetermined amount of data defined to be a pageful of data, which has typically been defined by a host (data source/destination) or user thereof, as a page, and which is sent by the host to a flash memory device for storage and is subsequently read by the host from the flash memory device.

Mapping: basic cell-level writing function in which incoming digital n-tuple is mapped to a program level by inducing a program level in the cell, having a predetermined correspondence to the incoming logical value.

10

15

20

25

5

Physical Page = A portion, typically 512 or 2048 or 4096 bytes in size, of a flash memory e.g. a NAND or NOR flash memory device. Writing and reading is typically performed physical page by physical page, as opposed to erasing which can be performed only erase sector by erase sector. A few bytes, typically 16 - 32 for every 512 data bytes are associated with each page (typically 16, 64 or 128 per page), for storage of error correction information. A typical block may include 32 512-byte pages or 64 2048-byte pages. Alternatively, a physical page is an ordered set (e.g. sequence or array) of flash memory cells which are all written in simultaneously by each write operation, the set typically comprising a predetermined number of typically physically adjacent flash memory cells containing actual data written by and subsequently read by the host, as well as, typically error correction information and back pointers used for recognizing the true address of a page.

Precise read, soft read: Cell threshold voltages are read at a precision (number of bits) greater than the number of Mapping levels (2<sup>n</sup>). The terms precise read or soft read are interchangeable. In contrast, in "hard read", cell threshold voltages are read at a precision (number of bits) smaller than the number of Mapping levels (2<sup>n</sup> where n = number of bits per cell).

Present level, Charge level: The amount of charge in the cell. The Amount of charge currently existing in a cell, at the present time, as opposed to "program level", the amount of charge originally induced in the cell (i.e. at the end of programming).

5 Program: same as "write".

20

25

30

Program level (programmed level, programming level): amount of charge originally induced in a cell to represent a given logical value, as opposed to "present level".

Reliability: Reliability of a flash memory device may be operationalized as the probability that a worst-case logical page written and stored in that device for a predetermined long time period such as 10 years will be successfully read i.e. that sufficiently few errors, if any, will be present in the physical page/s storing each logical page such that the error code appended to the logical page will suffice to overcome those few errors.

Reprogrammability (Np): An aspect of flash memory quality. This is typically operationalized by a reprogrammability parameter, also termed herein "Np", denoting the number of times that a flash memory can be re-programmed (number of erase-write cycles that the device can withstand) before the level of errors is so high as to make an unacceptably high proportion of those errors irrecoverable given a predetermined amount of memory devoted to redundancy. Typically recoverability is investigated following a conventional aging simulation process which simulates or approximates the data degradation effect that a predetermined time period e.g. a 10 year period has on the flash memory device, in an attempt to accommodate for a period of up to 10 years between writing of data in flash memory and reading of the data therefrom.

Resolution: Number of levels in each cell, which in turn determines the number of bits the cell can store; typically a cell with 2<sup>n</sup> levels stores n bits. Low resolution (partitioning the window, W, of physical values a cell can assume into a small rather than large number of levels per cell) provides high reliability.

Retention: of original physical levels induced in the flash memory cells despite time which has elapsed and despite previous erase/write cycles; retention is typically below 100% resulting in deterioration of original physical levels into present levels.

Retention time: The amount of time that data has been stored in a flash device, typically without, or substantially without, voltage having been supplied to the flash device i.e. the time which elapses between programming of a page and reading of the same page.

Symbol: Logical value

10

Threshold level or "decision level": the voltage (e.g.) against which the charge level of a cell is measured. For example, a cell may be said to store a particular digital n-tuple D if the charge level or other physical level of the cell falls between two threshold values T.

15 Code rate: ratio of redundancy bits to data bits in flash memory.

Data cells: cells storing data provided by host as opposed to "non-data cells" which do not store host-provided data, and may, for example, store instead error correction information, management information, redundancy information, spare bits or parity bits.

20

25

30

Logical page: a set of bits defined as a page typically having a unique page address, by a host external to a flash memory device.

In the present specification, the terms "row" and "column" refer to rows of cells and columns of cells, respectively and are not references to sub-divisions of a logical page.

1

The term "MSB" is used herein to denote the bit which is programmed into a multi-level cell, storing several bits, first. The term "LSB" is used herein to denote the bit which is programmed into the multi-level cell, last. The term "CSB" is used herein to denote the bit which is programmed into a 3-level cell, storing 3 bits, second, i.e. after the MSB and before the LSB. It is appreciated that more generally, e.g. if the multi-level cell stores 4 or more levels, there are more than one CSBs and use of the term "CSB" herein,

which implies that the cell is a 3-level cell, is merely by way of example and is not intended to be limiting.

A logical page is a set of bytes which is meaningful to an application. The location of a logical page in memory is termed herein a physical page. This location may comprise certain cells in their entirety, or, more commonly, may comprise only one or some bits within certain cells. The locations of each of a logical sequence of logical pages (page 0, page 1, page 2,....) within memory is pre-determined by a suitable mapping scheme mapping logical pages into the bits of the cells of a particular erase sector (block) in flash memory.

5

10

15

20

25

30

"Successfully reconstructed " means that using error correction code, the original logical page has been reconstructed generally satisfactorily, e.g., typically, that the logical page has been read, using reading thresholds, has undergone error correction as appropriate and has successfully passed its CRC (cyclic redundancy check) criterion.

"Bit errors" are those errors found in the physical page corresponding to a logical page, which typically are corrected using ECC (error correction code) such that the page is successfully reconstructed despite these errors.

The term "reading threshold" and "detection threshold" are used generally interchangeably.

Certain embodiments of the present invention seek to provide improved flash memory apparatus.

There is thus provided, in accordance with at least one embodiment of the present invention, a method for reading at least one page within an erase sector of a flash memory device, the method comprising computing at least one mock reading threshold; using the at least one mock reading threshold to perform at least one mock read operation of at least a portion of at least one page within the erase sector, thereby to generate a plurality of logical values; defining a set of reading thresholds based at least partly on the plurality of logical values; and reading at least one page in the erase sector using the set of reading thresholds.

Further in accordance with at least one embodiment of the present invention, the defining of a set of reading thresholds based at least partly on the plurality of logical values includes estimating a mean and standard deviation of at least one physical level

over at least a portion of at least one page belonging to the erase sector of the flash memory device based on the at least one mock reading operation.

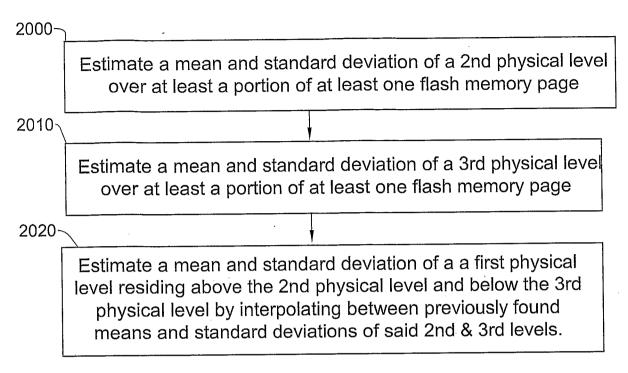

Still further in accordance with at least one embodiment of the present invention, the estimating is performed for at least a first physical level residing above a second physical level and below a third physical level and wherein estimating the mean and standard deviations of the first physical level comprises interpolating between previously found means and standard deviations of the second and third levels.

5

10

15

20

25

30

An advantage of the embodiment described above is that a significant amount of computation is saved since it is not necessary to generate a histogram for intermediate physical levels if histograms for physical levels on both sides are known. It is appreciated that alternatively or in addition to claim 3, estimating may be performed for a first physical level even if it does not reside above the second physical level and below the third physical level by extrapolating suitably between previously found means and standard deviations of the second and third levels.

Also provided, in accordance with another embodiment of the present invention, is a method for rapidly assessing functionality of erase sectors in a flash memory, the method comprising estimating a mean and standard deviation of at least one physical level over at least a portion of at least one page belonging to an erase sector of a flash memory device; wherein the estimating is performed for at least a first physical level residing above a second physical level and below a third physical level and wherein estimating the mean and standard deviations of the first physical level comprises interpolating between previously found means and standard deviations of the second and third levels.

Further in accordance with at least one embodiment of the present invention, the defining of a set of reading thresholds based at least partly on the plurality of logical values includes identifying at least one non-populous region of a predetermined size, within a distribution of physical values of a population of cells belonging to a page within the erase sector.

It is appreciated that non-populous does not mean non-populated i.e. the non-populous regions include only a small number of values but not necessarily zero values.

Still further in accordance with at least one embodiment of the present invention, at least one reading threshold in the set of reading thresholds is determined to be a central value within the non-populous region.

5

10

15

20

25

30

Also provided, in accordance with still another embodiment of the present invention, is a method for assessing effects of retention and cycling on individual erase sectors in a flash memory which has undergone retention and cycling, the method comprising receiving a first centerpoint of a rightmost lobe of a distribution of physical values within the cells of a new flash memory device and a second centerpoint of a rightmost lobe of a distribution of physical values within the cells of an entirely degraded flash memory device; generating a histogram representing distribution of physical values within the cells of an individual erase sector, over a range extending at least between the second and first centerpoints; and computing at least one statistic of a rightmost lobe of the histogram. It is appreciated that there may be only one lobe.

Further in accordance with at least one embodiment of the present invention, at least one statistic comprises at least one of a mean and a standard deviation.

Still further in accordance with at least one embodiment of the present invention, the defining comprises seeking a local maximum in a threshold voltage distribution and determining at least one reading threshold based at least partly on the local maximum.

Additionally in accordance with at least one embodiment of the present invention, the defining comprises seeking a local minimum in a threshold voltage distribution and determining at least one reading threshold based at least partly on the local minimum.

Further in accordance with at least one embodiment of the present invention, the defining comprises identification of a threshold voltage distribution of a highest program level in a probability distribution of physical values within the erase sector; and preventing misidentification of the threshold voltage distribution of the highest program level by comparing the number of cells whose threshold voltage is larger than the candidate maximizing voltage, to a threshold.

Still further in accordance with at least one embodiment of the present invention, the method also comprises guaranteeing a similar number of cells in each program level.

Additionally in accordance with at least one embodiment of the present invention, each time the computing, using, defining and reading are performed, the reading

thresholds as most recently modified are stored in a data base in association with characterization information, and the method also comprises, for at least one page in the erase sector: accessing the data base and reviewing at least some of the characterization information to determine whether the database includes reading thresholds suitable for the page; if the database does include suitable thresholds, using the suitable thresholds to read the page; and if the database does not include suitable thresholds, performing the computing, using, defining and reading steps for the page. The database is termed herein "threshold history data base".

5

10

15

20

25

It typically stores, as time goes on, a set of thresholds for each row or group of adjacent rows, but not for each erase sector but rather for each category of erase sectors. Typically, a category of erase sectors comprises a set of erase sectors which share a common range of cycling indices and a common range of retention durations. For example, the first category may comprise erase sectors which have undergone up to 100 cycles and whose retention duration is up to 1 month. The second category may comprise erase sectors which have undergone from 101 to 200 cycles and whose retention duration is up to 1 month, and so on, up to a 50th category which may comprise erase sectors which have undergone from 4901 up to 5000 cycles and whose retention duration is up to 1 month. The 51st to 100 categories may comprise erase sectors which have undergone 0-100, 101-200 etc. cycles respectively, and whose retention duration is between 1 and 2 months. The 101th to 150th categories may comprise erase sectors which have undergone 0 - 100, 101 - 200 etc. cycles respectively, and whose retention duration is between 2 and 3 months, etc. and so forth, with steps of 1 month between categories for the first year. From the first year to the tenth year, the retention duration increment between categories may be 1 year rather than a single month. The cycling index increment between categories may be uniform e.g. 100 cycles as in this example.

Further in accordance with at least one embodiment of the present invention, the characterization information includes: identification of row neighborhood, number of program/erase cycles which rows in the row neighborhood underwent, and retention period which rows in the row neighborhood endured.

Additionally in accordance with at least one embodiment of the present invention, the guaranteeing comprises scrambling of bits stored in the erase sector. Scrambling may be carried out by the scrambler/descrambler described herein.

5

10

15

20

25

30

Also provided, in accordance with yet another embodiment of the present invention, is a system for reading at least one page within an erase sector of a flash memory device, the system comprising mock threshold computation apparatus operative to compute at least one mock reading threshold; a reading threshold set generator operative to define a set of reading thresholds based at least partly on the plurality of logical values; and reading apparatus using the at least one mock reading threshold to perform at least one mock read operation of at least a portion of at least one page within the erase sector, thereby to generate a plurality of logical values and subsequently using the set of reading thresholds based at least partly on the plurality of logical values to read at least one page in the erase sector using the set of reading thresholds.

Still further provided, in accordance with still another embodiment of the present invention, is a system for rapidly assessing functionality of erase sectors in a flash memory, the system comprising flash memory physical level distribution statistic estimation apparatus estimating a mean and standard deviation of at least one physical level over at least a portion of at least one page belonging to an erase sector of a flash memory device and including interpolation apparatus, wherein the apparatus receives and operates upon at least a first physical level residing above a second physical level and below a third physical level by using the interpolation apparatus to interpolate between previously found means and standard deviations of the second and third levels.

Also provided, in accordance with another embodiment of the present invention, is a system for assessing effects of retention and cycling on individual erase sectors in a flash memory which has undergone retention and cycling, the system comprising a histogram generator operative to generate a histogram representing distribution of physical values within the cells of an individual erase sector, over a range extending at least between a first centerpoint of a rightmost lobe of a distribution of physical values within the cells of a new flash memory device and a second centerpoint of a rightmost lobe of a distribution of physical values within the cells of an entirely degraded flash

memory device; and a rightmost lobe analyzer operative to compute at least one statistic of a rightmost lobe of the histogram.

Further in accordance with at least one embodiment of the present invention, the computing comprises translating the mock reading thresholds along a physical value axis of a probability distribution of physical values within the erase sector, according to at least one characteristic of a highest program level within the probability distribution.

5

10

15

20

25

30

According to certain embodiments, an average or central value of a highest lobe in a probability density function graph of logical values read from flash memory may be found, by defining mock thresholds between maximal values identified for a new flash memory device and minimal values identified for an extremely run down (high retention, high cycle count) flash memory device. To do this, a new flash memory device may be taken up at a set up stage, and a large number of cells therein, perhaps one erase-sector full, may be programmed to their highest levels. The erase sector is read, using suitable thresholds whose intervals define a suitable resolution, to determine the location of the top edge of the highest (rightmost) lobe. An extremely run-down flash memory device is then taken up, also at the set up stage, and a large number of cells therein, perhaps one erase-sector full, may be programmed to their highest levels.

The erase sector is read, using suitable thresholds whose intervals define a suitable resolution, to determine the location of the bottom edge of the lowest (leftmost) lobe. It can then be assumed to be the case, that any flash memory device's highest lobe falls within the window between the known bottom edge of the lowest lobe of the rundown flash memory, and the known top edge of the highest lobe of the new flash memory. This is helpful, for example, when it is desired to define mock reading thresholds to identify the location of a highest lobe of a probability density function of an individual flash memory device, wherein the mock reading thresholds are to span all possible locations of the highest lobe. This can be done by distributing mock reading thresholds throughout the entire window described above.

Any suitable processor, display and input means may be used to process, display, store and accept information, including computer programs, in accordance with some or all of the teachings of the present invention, such as but not limited to a conventional personal computer processor, workstation or other programmable device or computer or

electronic computing device, either general-purpose or specifically constructed, for processing; a display screen and/or printer and/or speaker for displaying; machine-readable memory such as optical disks, CDROMs, magnetic-optical discs or other discs; RAMs, ROMs, EPROMs, EEPROMs, magnetic or optical or other cards, for storing, and keyboard or mouse for accepting. The term "process" as used above is intended to include any type of computation or manipulation or transformation of data represented as physical, e.g. electronic, phenomena which may occur or reside e.g. within registers and /or memories of a computer.

5

10

15

20

25

30

The above devices may communicate via any conventional wired or wireless digital communication means, e.g. via a wired or cellular telephone network or a computer network such as the Internet.

The apparatus of the present invention may include, according to certain embodiments of the invention, machine readable memory containing or otherwise storing a program of instructions which, when executed by the machine, implements some or all of the apparatus, methods, features and functionalities of the invention shown and described herein. Alternatively or in addition, the apparatus of the present invention may include, according to certain embodiments of the invention, a program as above which may be written in any conventional programming language, and optionally a machine for executing the program such as but not limited to a general purpose computer which may optionally be configured or activated in accordance with the teachings of the present invention.

The embodiments referred to above, and other embodiments, are described in detail in the next section.

Any trademark occurring in the text or drawings is the property of its owner and occurs herein merely to explain or illustrate one example of how an embodiment of the invention may be implemented.

Unless specifically stated otherwise, as apparent from the following discussions, it is appreciated that throughout the specification discussions, utilizing terms such as, "processing", "computing", "estimating", "selecting", "ranking", "grading", "calculating", "determining", "generating", "reassessing", "classifying", "generating", "producing", "stereo-matching", "registering", "detecting", "associating", "superimposing", "obtaining"

or the like, refer to the action and/or processes of a computer or computing system, or processor or similar electronic computing device, that manipulate and/or transform data represented as physical, such as electronic, quantities within the computing system's registers and/or memories, into other data similarly represented as physical quantities within the computing system's memories, registers or other such information storage, transmission or display devices.

10

15

20

25

5

## BRIEF DESCRIPTION OF THE DRAWINGS

Certain embodiments of the present invention are illustrated in the following drawings:

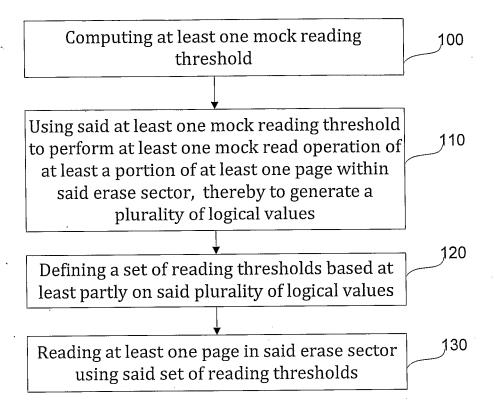

Fig. 1A is a simplified flowchart illustration of a generalized method for reading at least one page within an erase sector of a flash memory device, the method being operative in accordance with certain embodiments of the present invention;

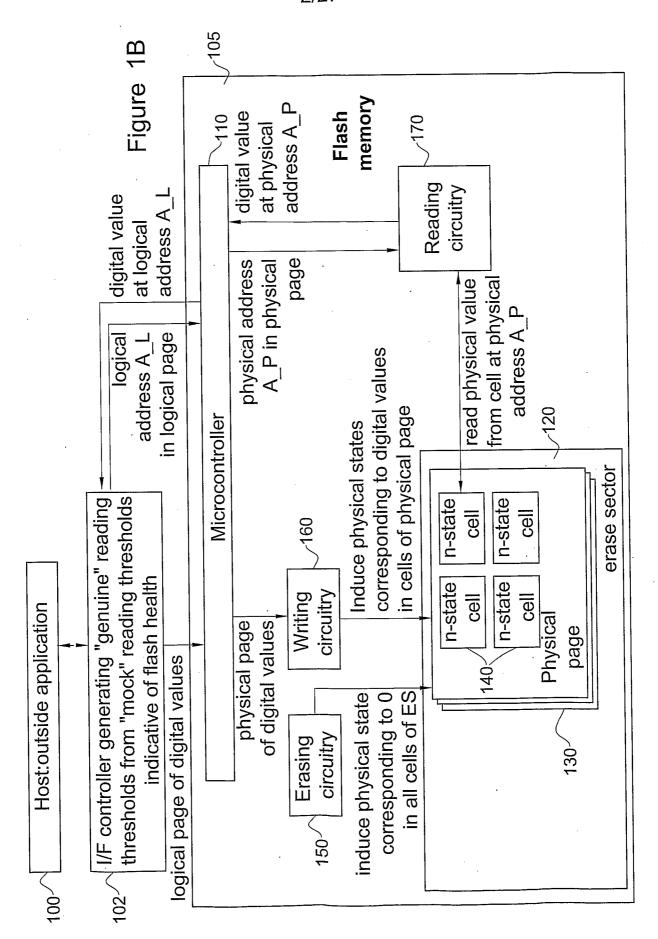

Fig. 1B is a simplified block diagram of a flash memory system constructed and operative in accordance with certain embodiments of the present invention;

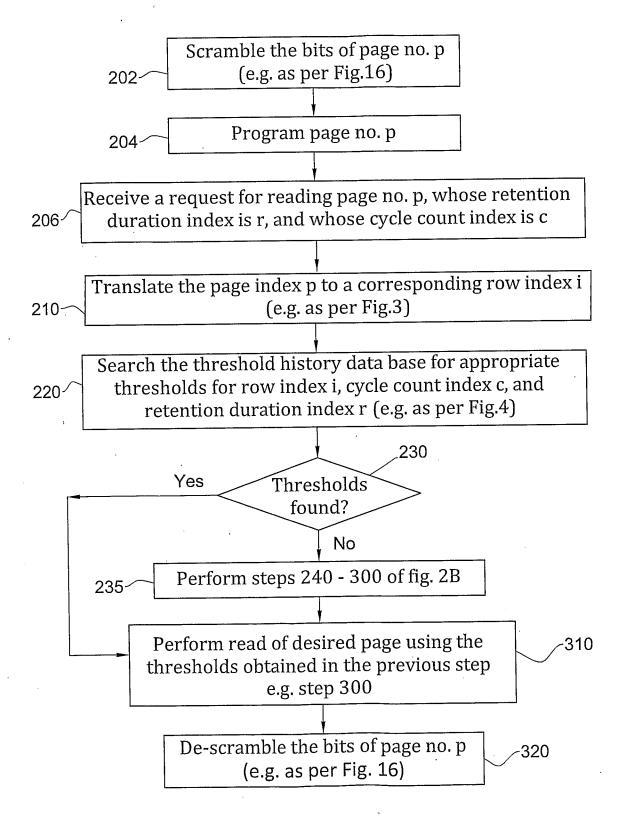

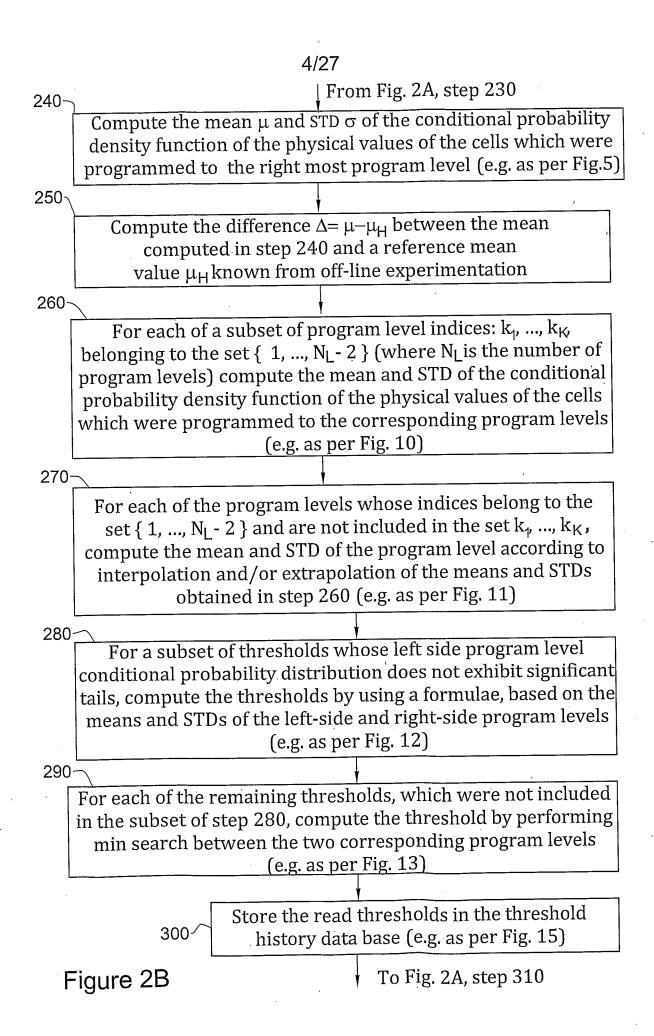

Figs. 2A – 2B, taken together, form a simplified flowchart illustration of an example method implementing the generalized method of Fig. 1A, the method of Figs. 2A – 2B being operative in accordance with certain embodiments of the present invention;

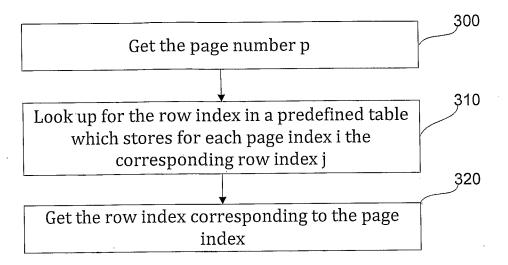

Fig. 3 is a simplified flowchart illustration of a method for performing step 210 of Fig. 2A, the method being operative in accordance with certain embodiments of the present invention;

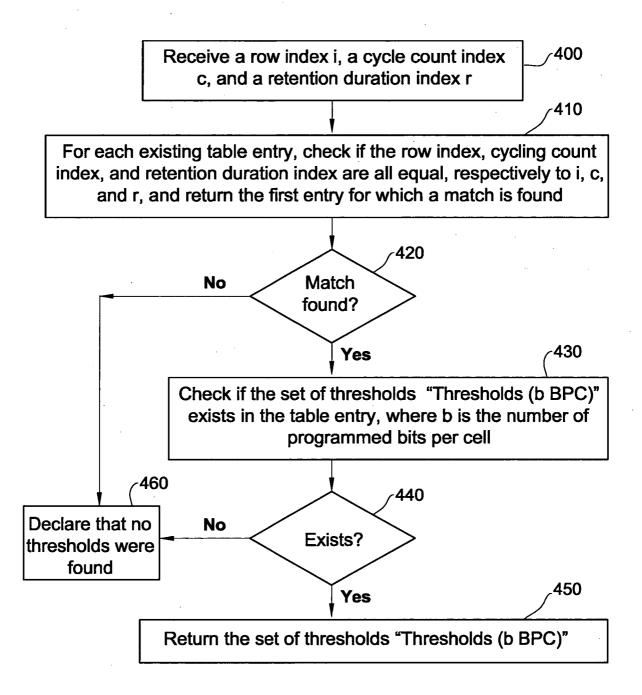

Fig. 4 is a simplified flowchart illustration of a method for performing step 220 of Fig. 2A, the method being operative in accordance with certain embodiments of the present invention;

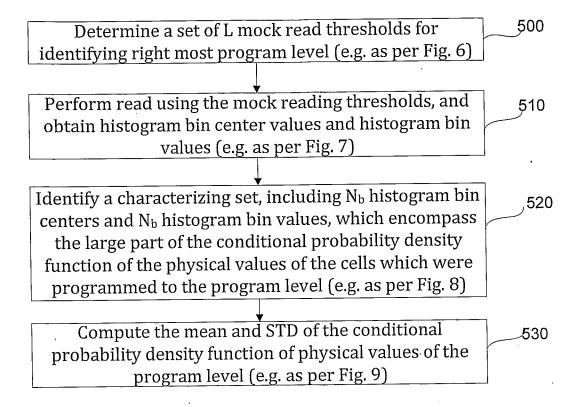

Fig. 5 is a simplified flowchart illustration of a method for performing step 240 of Fig. 2B, the method being operative in accordance with certain embodiments of the present invention;

Fig. 6 is a simplified flowchart illustration of a method for performing step 500 of Fig. 5, the method being operative in accordance with certain embodiments of the present invention;

5

10

15

25

30

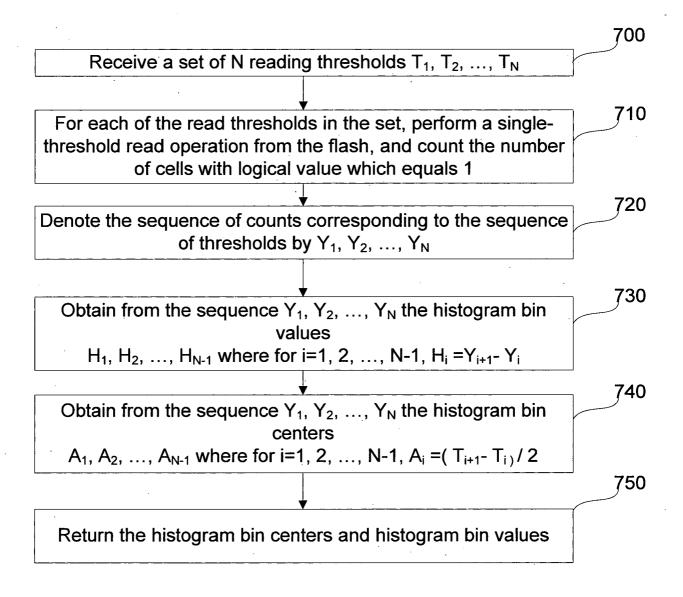

Fig. 7 is a simplified flowchart illustration of a method for performing step 510 of Fig. 5, the method being operative in accordance with certain embodiments of the present invention;

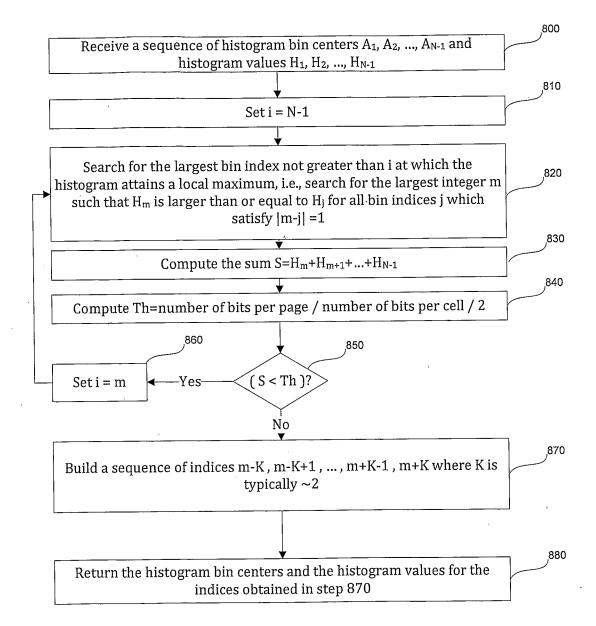

Fig. 8 is a simplified flowchart illustration of a method for performing step 520 of Fig. 5, the method being operative in accordance with certain embodiments of the present invention;

Fig. 9 is a simplified flowchart illustration of a method for performing step 530 of Fig. 5, the method being operative in accordance with certain embodiments of the present invention;

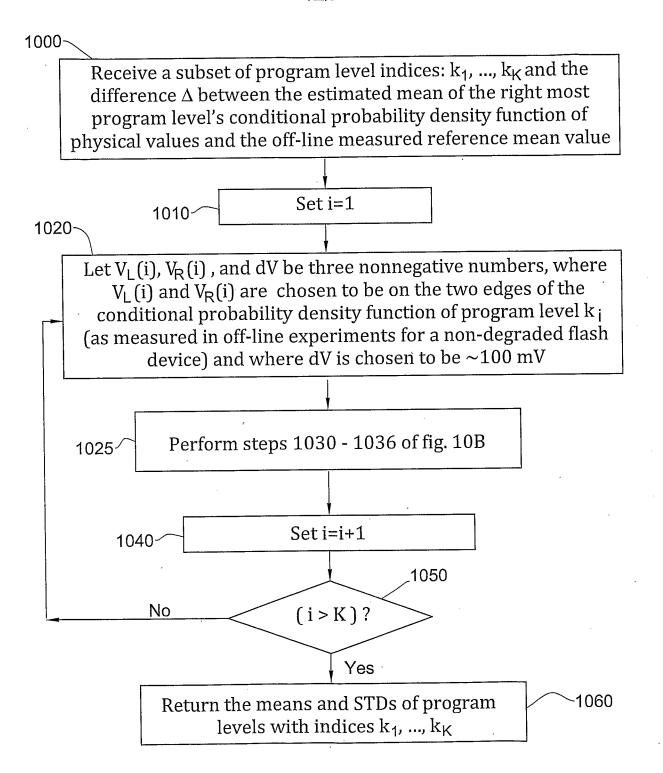

Fig. 10A - 10B, taken together, form a simplified flowchart illustration of a method for performing step 260 of Fig. 2B, the method being operative in accordance with certain embodiments of the present invention;

Fig. 11 is a simplified flowchart illustration of a method for performing step 270 of Fig. 2B, the method being operative in accordance with certain embodiments of the present invention;

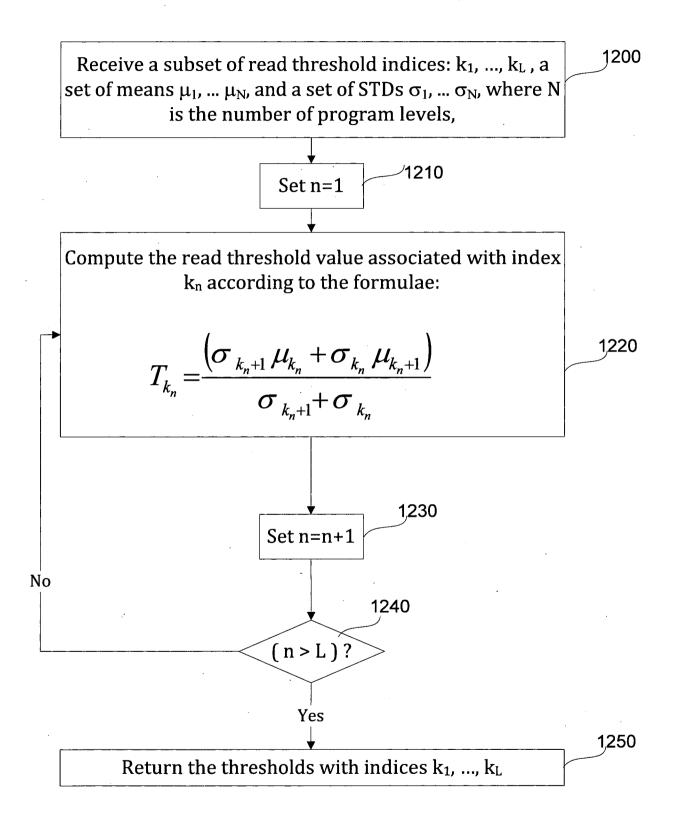

Fig. 12 is a simplified flowchart illustration of a method for performing step 280 of Fig. 2B, the method being operative in accordance with certain embodiments of the present invention;

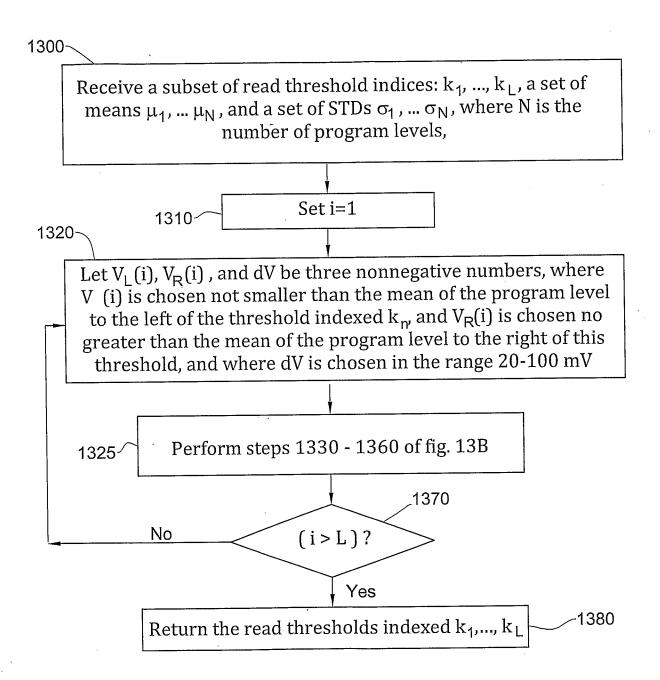

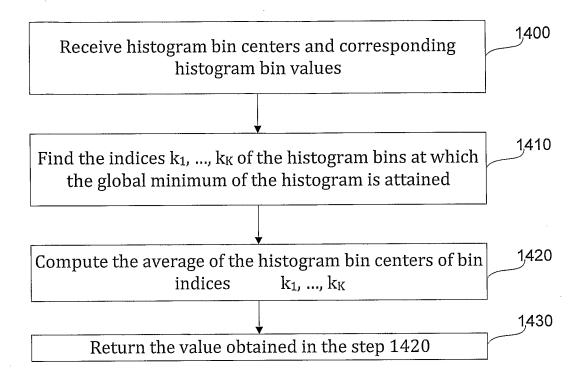

Fig. 13A – 13B, taken together, form a simplified flowchart illustration of a method for performing step 290 of Fig. 2B, the method being operative in accordance with certain embodiments of the present invention;

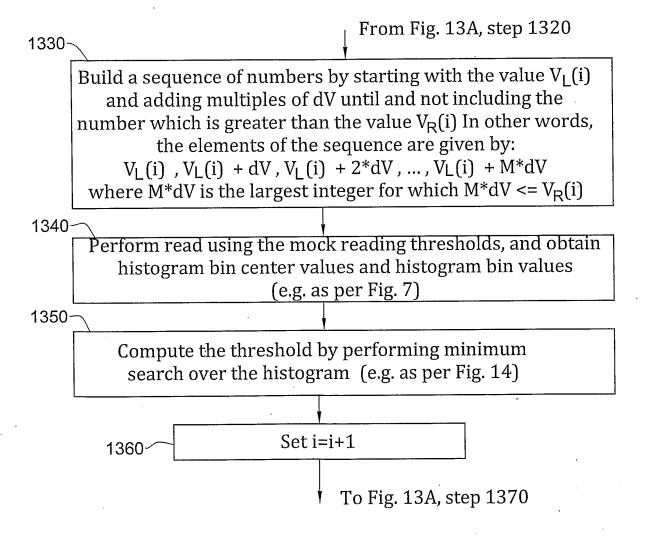

Fig. 14 is a simplified flowchart illustration of a method for performing step 1350 of Fig. 13B, the method being operative in accordance with certain embodiments of the present invention;

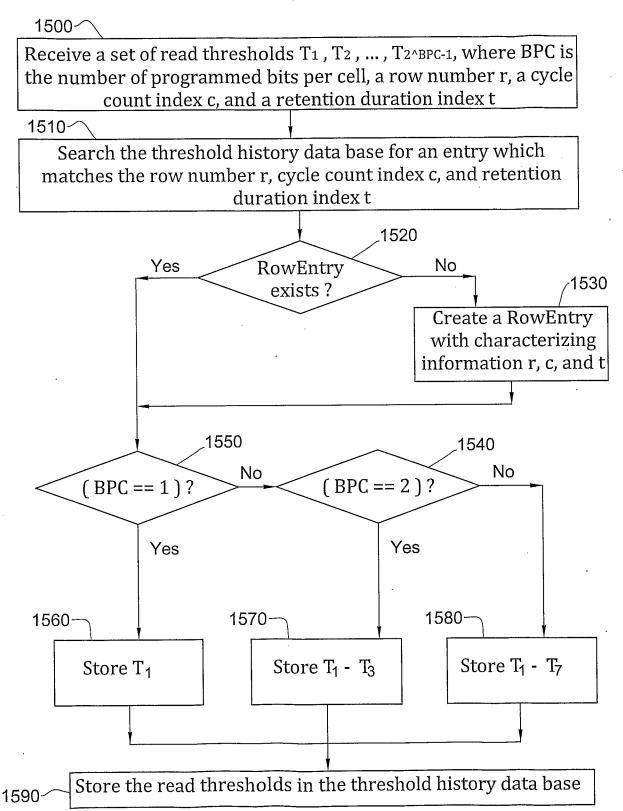

Fig. 15 is a simplified flowchart illustration of a method for performing step 300 of Fig. 2B, the method being operative in accordance with certain embodiments of the present invention;

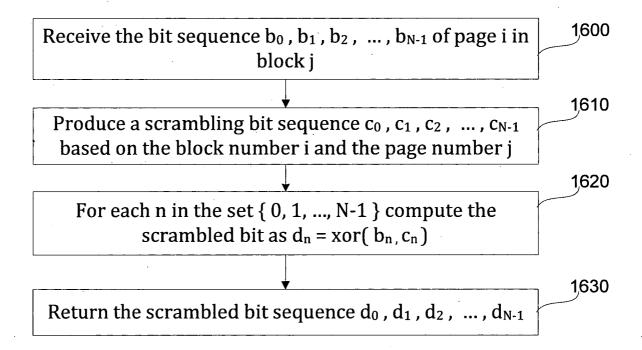

Fig. 16 is a simplified flowchart illustration of a method for performing step 202 of Fig. 2A, the method being operative in accordance with certain embodiments of the present invention;

5

10

15

20

25

30

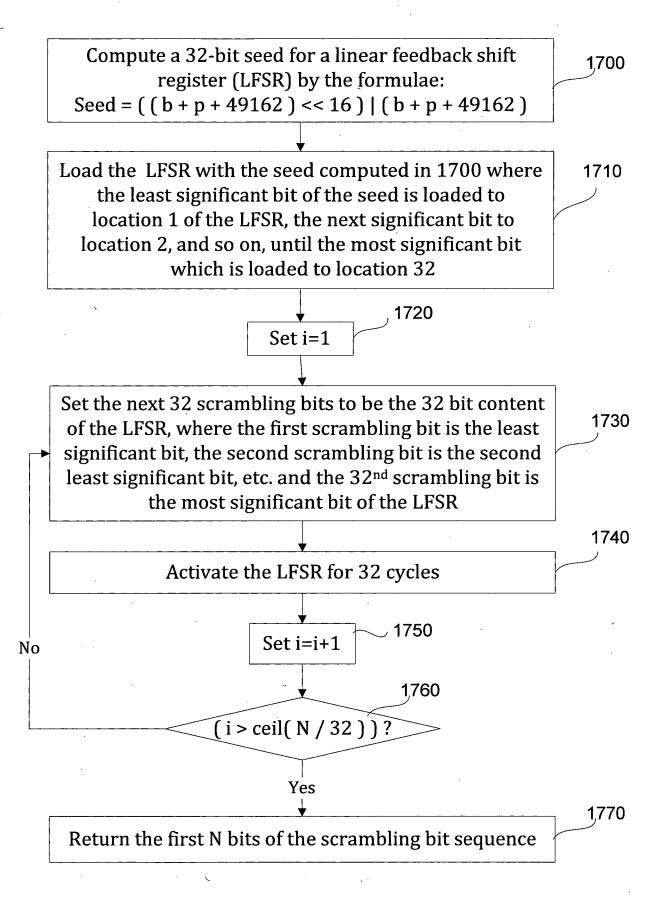

- Fig. 17 is a simplified flowchart illustration of a method for performing step 1620 of Fig. 16, the method being operative in accordance with certain embodiments of the present invention;

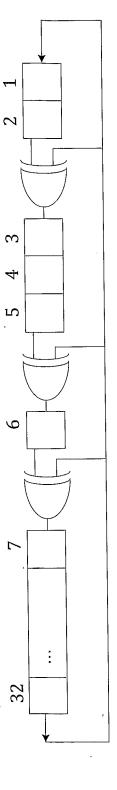

- Fig. 18 is a simplified electronic diagram of a linear feedback shift register suitable for implementing a scrambler/descrambler as described herein with reference also to Fig. 27;

- Fig. 19 (prior art) is a simplified theoretical probability density function v. voltage graph showing voltage distributions of program levels, in which the vertical axis represents theoretical physical values conditional on programmed levels;

- Fig. 20 is a graph of a threshold voltage distribution of a highest program level which is useful in understanding the highest program level mean and standard deviation fine estimation methods shown and described herein;

- Fig. 21 is a graph of a threshold voltage distribution of an intermediate program level which is useful in understanding the intermediate program level mean and standard deviation fine estimation methods shown and described herein;

- Fig. 22 is a graph of adaptive voltage intervals for estimation of means and standard deviations of intermediate program levels as shown and described herein;

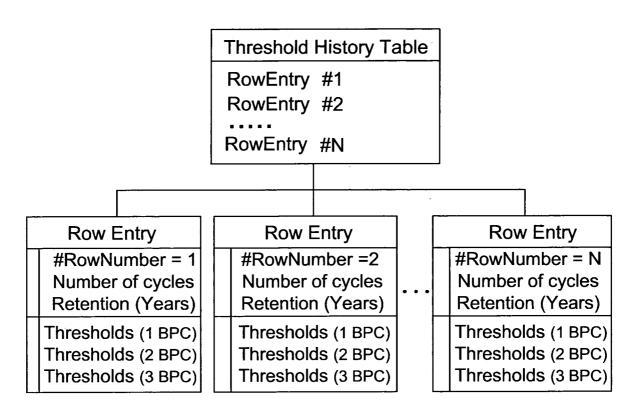

- Fig. 23 is an example of a data structure for a Threshold history table which may be searched using the method of Fig. 4 and maintained using the method of Fig. 15;

- Fig. 24 is a simplified diagram of Detection thresholds sets useful in accordance with certain embodiments of the present invention;

- Fig. 25 is a simplified flowchart illustration of a method for rapidly assessing functionality of erase sectors in a flash memory operative in accordance with certain embodiments of the present invention;

Fig. 26 is a simplified flowchart illustration of a method for assessing effects of retention and cycling on individual erase sectors in a flash memory which has undergone retention and cycling, operative in accordance with certain embodiments of the present invention; and

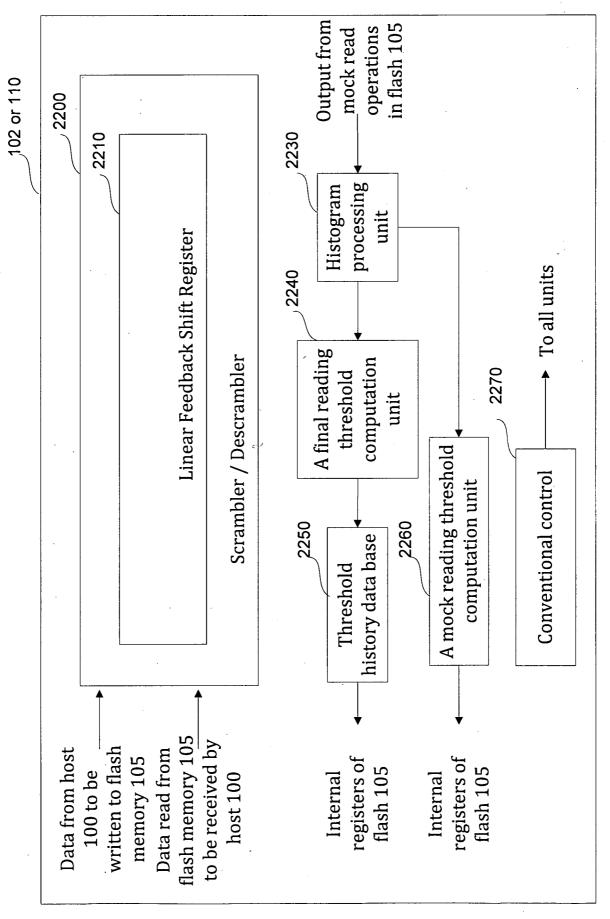

Fig. 27 is a simplified functional block diagram of the external controller of Fig. 1B, according to certain embodiments of the present invention.

# DETAILED DESCRIPTION OF CERTAIN EMBODIMENTS

5

10

15

20

25

30

Reference is now made to Fig. 1A which is a simplified generally self-explanatory flowchart illustration of a generalized method for reading at least one page within an erase sector of a flash memory device, the method being operative in accordance with certain embodiments of the present invention. The method of Fig. 1A typically includes some or all of the following steps, suitably ordered, e.g. as shown:

Step 100: computing at least one mock reading threshold. A mock threshold is a threshold which is far from being an adequate conventional reading threshold useful for reconstructing a logical value from a physical value residing in a flash memory cell. While the mock threshold is used as an input to a reading process, as though it were a true reading threshold, its utility differs. For example, mock thresholds may be used to ascertain the state of health of an erase sector at a certain point in time. Mock thresholds may be used as a reflection of the current locations and shapes of the various lobes of the probability density functions, as shown in Fig. 19, of a particular erase sector or entire flash memory device.

Step 110: using the at least one mock reading threshold to perform at least one mock read operation of at least a portion of at least one page within the erase sector, thereby to generate a plurality of logical values.

Step 120: defining a set of reading thresholds based at least partly on the plurality of logical values.

Step 130: reading at least one page in the erase sector using the set of reading thresholds.

Reference is now made to Fig. 1B which is a simplified block diagram of a flash memory system constructed and operative in accordance with certain embodiments of the present invention. As shown, the flash memory system of Fig. 1B includes a host or outside application 100 which interfaces, via an interface controller 102 operative to generate "genuine" reading thresholds from "mock" reading threshold indicative of flash memory health. The controller 102 is typically operative to perform some or all of the methods shown and described herein such as the methods of Figs. 1A and 2A – 2B, with a flash memory device 105. Fig. 27 is a simplified functional block diagram of the controller 102 according to certain embodiments of the present invention.

5

10

15

20

25

30

An internal microcontroller 110 typically manages the functional units of the flash memory device 105. The storage portion of the flash memory device includes one or more typically many erase sectors 120 each storing one or more typically many physical pages 130 each including one or more typically many cells 140 having more than one possible state such that logical values may be stored therein. Erasing circuitry 150 is provided to erase data from cells, writing circuitry 160 writes data into cells, and reading circuitry 170 reads data from cells.

Figs. 2A - 2B, taken together, form a simplified generally self-explanatory flowchart illustration of an example method implementing the generalized method of Fig. 1A, the method of Figs. 2A - 2B being operative in accordance with certain embodiments of the present invention.

Fig. 3 is a simplified generally self-explanatory flowchart illustration of a method for performing step 210 of Fig. 2A, the method being operative in accordance with certain embodiments of the present invention.

Fig. 4 is a simplified generally self-explanatory flowchart illustration of a method for performing step 220 of Fig. 2A, the method being operative in accordance with certain embodiments of the present invention. Fig. 2B provides detail of step 235 in Fig. 2A. It is appreciated that a decision as to whether or not a tail effect is present, which impacts on appropriate action which may be taken in each case, occurs in step 280. A "tail effect" is defined herein as a situation in which the right tail of the probability density function of the physical value of a cell decays much slower than the Gaussian probability density. Such a situation can be detected empirically by generating a

histogram with a fine grid over the entire voltage range, thereby effectively "taking a picture" of the probability function of the physical values. By examining this distribution it is possible to identify program levels which may exhibit excessive tails in their distribution.

Fig. 5 is a simplified generally self-explanatory flowchart illustration of a method for performing step 240 of Fig. 2B, the method being operative in accordance with certain embodiments of the present invention.

5

10

15

20

25

30

Fig. 6 is a simplified generally self-explanatory flowchart illustration of a method for performing step 500 of Fig. 5, the method being operative in accordance with certain embodiments of the present invention.

Fig. 7 is a simplified generally self-explanatory flowchart illustration of a method for performing step 510 of Fig. 5, the method being operative in accordance with certain embodiments of the present invention.

Fig. 8 is a simplified generally self-explanatory flowchart illustration of a method for performing step 520 of Fig. 5, the method being operative in accordance with certain embodiments of the present invention.

Fig. 9 is a simplified generally self-explanatory flowchart illustration of a method for performing step 530 of Fig. 5, the method being operative in accordance with certain embodiments of the present invention.

Fig. 10A - 10B, taken together, form a simplified generally self-explanatory flowchart illustration of a method for performing step 260 of Fig. 2B, the method being operative in accordance with certain embodiments of the present invention.

Fig. 11 is a simplified generally self-explanatory flowchart illustration of a method for performing step 270 of Fig. 2B, the method being operative in accordance with certain embodiments of the present invention.

Fig. 12 is a simplified generally self-explanatory flowchart illustration of a method for performing step 280 of Fig. 2B, the method being operative in accordance with certain embodiments of the present invention.

Fig. 13A - 13B, taken together, form a simplified generally self-explanatory flowchart illustration of a method for performing step 290 of Fig. 2B, the method being operative in accordance with certain embodiments of the present invention.

Fig. 14 is a simplified generally self-explanatory flowchart illustration of a method for performing step 1350 of Fig. 13B, the method being operative in accordance with certain embodiments of the present invention.

5

10

15

20

25

30

Fig. 15 is a simplified generally self-explanatory flowchart illustration of a method for performing step 300 of Fig. 2B, the method being operative in accordance with certain embodiments of the present invention. In step 1560, T1 may be stored in MSB thresholds (T1) of thresholds (1 BPC) of RowEntry (r, c, t). In step 1570, T2 may be stored in MSB thresholds (T2) of thresholds (2 BPC) of RowEntry (r, c, t). T1 and T3 may be stored in CSB thresholds (T1, T3) of thresholds (2 BPC) of RowEntry (r, c, t). In step 1580, T4 may be stored in MSB thresholds (T4) of thresholds (3 BPC) of RowEntry (r, c, t). T2 and T6 may be stored in CSB thresholds (T2, T6) of thresholds (3 BPC) of RowEntry (r, c, t). T1, T3, T5 and T7 may be stored in LSB thresholds (T1, T3, T5, T7) of thresholds (3 BPC) of RowEntry (r, c, t).

The acronyms MSB, LSB and CSB are used herein to denote most significant, least significant, and intermediately significant (e.g. in 3-bit-per-cell applications) bits respectively.

Fig. 16 is a simplified generally self-explanatory flowchart illustration of a method for performing step 202 of Fig. 2A, the method being operative in accordance with certain embodiments of the present invention.

Fig. 17 is a simplified generally self-explanatory flowchart illustration of a method for performing step 1610 of Fig. 16, the method being operative in accordance with certain embodiments of the present invention.

Fig. 18 is a simplified generally self-explanatory electronic diagram of a linear feedback shift register suitable for implementing the scrambler/descrambler of Fig. 27.

Design considerations may take into account the following: Conventional flash memory devices store information as charge in "cells", each made of either a floating gate transistor or an NROM transistor. In single-level cell (SLC) devices, each cell stores only one bit of information. Multi-level cell (MLC) devices can store more than one bit per cell by choosing between multiple levels of electrical charge to apply to the floating gates of their cells. The amount of charge (also known as charge level) is then measured by a detector, by comparing the voltage of the transistor gate (also known as charge level and

denoted  $V_T$ ) to a decision threshold voltage (also known as charge level boundary point and denoted  $V_D$ ). The amount of charge is then used to determine the programmed level (logical value) of the cell. Due to inaccuracies during the programming procedure and charge loss due to time and temperature (also known as retention), the measured levels suffer from a random distortion.

5

10

15

20

25

30

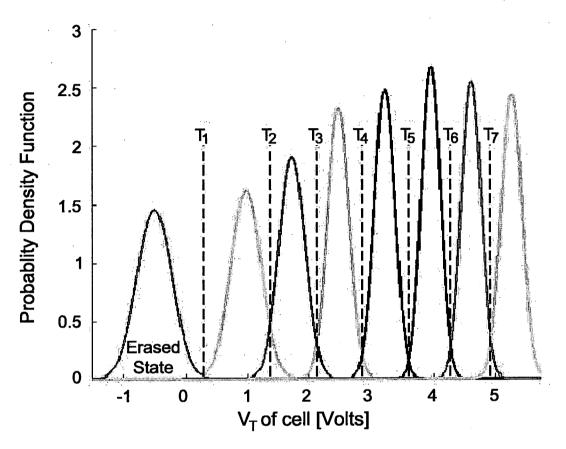

Fig. 19 illustrates an example of the eight (8) separate probability distributions of a cell which can be programmed with one of eight (8) corresponding program levels (111, 110, 100, 101, 001, 000, 010, and 011, respectively). For each distribution curve, the Y-axis represents the probability that the cell is programmed to the corresponding level, given the value of the charge level  $V_T$  (represented by the x-axis).

The cell's programmed level may be determined using several methods. One method is to apply a voltage to the cell's gate and measure if the cell conducts current. The cell has a certain threshold voltage such that if voltage above that threshold is applied to the gate, the gate will conduct. Bellow that threshold voltage the gate will not conduct current (or will conduct a small amount of current, below a certain demarcation level). As the amount of charge in the cell changes this threshold voltage, the charge may be inferred by determining at which voltage the cell starts to conduct current. Thus, the programmed level is determined by iteratively applying different voltages to the gate and measuring whether the cells conduct or not. Another method is based on the fact that when applying a voltage above the threshold voltage, the cell conducts current and the amount of current depends on the difference between the applied voltage and the threshold voltage. As the threshold voltage changes as a function of the amount of charge in the cell, the programmed level may be inferred by measuring the current going through the cell.

Thus, the programmed level may be obtained by simultaneously comparing the conducted current with a given set of fixed currents distinguishing between all programmed levels. In other words, each cell's programmed level is determined by simultaneously comparing the  $V_T$  level against several decision threshold levels (reading thresholds). For example, if there are eight (8) possible programmed levels, the cell's  $V_T$  is simultaneously compared against seven decision threshold levels which divide the voltage axis into eight (8) regions, as shown in Fig. 19.

In general, if there are L possible program levels, then L-1 decision threshold levels are employed. As the probability distributions extend beyond the decision threshold levels, there is a probability of detection error, i.e. detecting the wrong program level. In order to minimize the detection error, one wishes to set the decision threshold levels optimally. The optimal placement of the decision thresholds levels in terms of minimizing the detection error probability generally depends on the probability distribution associated with the  $V_T$  level of the cells. The statistical behavior of the cells'  $V_T$  level can be approximated by Gaussian distributions. The optimal placement of the reading threshold for the Gaussian case is a known function, as described e.g. in the above-referenced publication by Proakis, of the means and standard deviations (STDs) of the the Gaussian distributions. In other words, knowledge of good decision thresholds (assuming the Gaussian assumption is correct) is possible if the means and standard deviations of the cells'  $V_T$  distributions are known.

5

10

15

20

25

30

Since the means and standard deviations of the probability distributions change as a result of cycling and retention, it is not clear how to set the decision thresholds when attempting to read a given page storing information. Setting the decision thresholds to the optimal position corresponding to a fresh flash device might show acceptable performance only if the page was recently programmed and not retained for a significant amount of time. Similarly, setting the decision thresholds to fit a device which was cycled 1000 times and retained for 10 years might not work, i.e. cause too many detection errors, if the page in question was recently written to a non-cycled flash device.

This situation calls for a training stage in which the flash device's controller learns the "state" of the page/block and determines a set of decision thresholds which will yield preferably as little detection errors as possible when used to read the page. One method for performing training involves estimating the state of the flash device from the data bearing cells themselves in order to deduce appropriate reading thresholds without any apriori knowledge of the data stored in these cells.

The training procedures mentioned above could be performed prior to the reading of every page. In some applications, this approach might turn out expensive in terms of a system's resources. It is therefore important to find ways in which the training procedure

comes into play less frequently. One such way, which utilizes a data base of previously obtained training information is described herein.

5

10

15

20

25

30

Certain embodiments of the present invention allow generation of reading threshold values for use when reading data from cells of a flash memory device, without incurring any penalty in terms of a reduction in the number of available cells used for storing data (e.g., without using a "training-sequence"). This is done by employing a "blind" training method in which the probability distributions of the cells'  $V_T$  level is estimated based on the actual data bearing cells, whose actual content is in general unknown to the controller. Estimation of the probability distribution of each program level is done by successive read operations which are carried out over the entire page (or a large part thereof) in an appropriate voltage interval. The results of the read operations are translated into an approximate histogram of  $V_T$  levels corresponding to a specific program level, and the probability distribution is estimated based on this histogram. Certain embodiments of this invention also include some refinements which allow to trade-off complexity vs. performance, as well as to improve performance in the presence of certain types of non-Gaussian statistics.

Other embodiments of this invention include the usage of a threshold history data base which keeps a list of previously obtained reading thresholds. The data base is organized and used based on the assumption that distinct erase blocks with a similar degradation state, i.e. with a similar cycling counter and similar duration of retention, behave statistically the same. This implies that thresholds which exist in the data base and which were obtained from a certain block with certain degradation characteristics can be used to successfully read another page within another erase block which has undergone similar degradation.

According to certain embodiments, a method for evaluating the unknown degradation state of a first erase block based on certain characteristics indicative of degradation, such as but not limited to cycling index and retention duration, is provided. The first erase block is matched with a second erase block sharing the same characteristics, whose degradation state is known. If the two erase blocks share the same characteristics, the known degradation state of the second is taken to be the degradation state of the first.

For clarity, the specification and drawings at times relate specifically to a flash memory device where each cell has eight (8) possible charge levels (or program levels), thus storing 3 bits per cell. It is appreciated however that certain embodiments of this invention are also applicable to flash devices with less or more charge levels. The page to be read has typically been written to a flash device after an unknown number of program/erase cycles, and the data in the page has been retained for an unknown period of time. Denote the number of cells in the page by  $N_c$ . Denote the means of the cells'  $V_T$  level distributions by  $\mu_1, \mu_2, ..., \mu_8$ , where the index 1 corresponds to the erase level, index 2 corresponds to the program level closest to the erased state, and so on. Furthermore, denote by  $\sigma_1, \sigma_2, ..., \sigma_8$ , the standard deviations (STDs) of these distributions, respectively. Finally, denote by  $T_1, T_2, ..., T_7$ , the reading thresholds which are to be used for reading the page. An approximation to the optimal reading thresholds is given by the following formulae, e.g. as described herein in Fig. 2B, step 280 and in Fig. 12:

15

$$T_k = \frac{{}^{\sigma}k + 1^{\mu}k + {}^{\sigma}k^{\mu}k + 1}{{}^{\sigma}k + {}^{\sigma}k + 1}, k = 1, 2, ... 7.$$

5

10

20

25

Fine Estimation of the Mean and standard deviation of the Highest Program Level, according to certain embodiments of the present invention, is now described in detail.

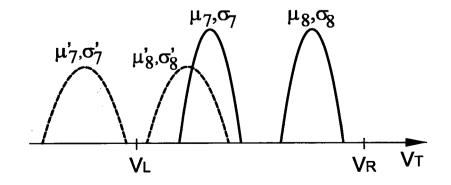

In one embodiment of the present invention, the mean and standard deviation of the probability distribution of the  $V_T$  level of the cells programmed to the highest program level are estimated e.g. as illustrated herein in Fig. 2B at step 240 and in Fig. 5. An example of the threshold voltage distribution of the two (2) highest program levels is shown in Fig. 20. The solid line corresponds to a fresh cell which underwent little (if any) program-erase cycles and whose data was retained for a very short period of time. The (Gaussian) probability distribution of the threshold voltage of these cells is determined by their means  $\mu_7$ ,  $\mu_8$  and standard deviations  $\sigma_7$ , $\sigma_8$ . The dashed line corresponds to used cells which were subjected to 1000 program-erase cycles and whose

data was retained for 10 years. The (Gaussian) probability distribution of these cells is designated by the means  $\mu'_7$ ,  $\mu'_8$  and standard deviations  $\sigma'_7$ ,  $\sigma'_8$ .

The flash device typically supports a read operation in which the threshold levels of all the cells in a given page are compared simultaneously against some fixed voltage. Specifically, if the read operation is given a voltage  $V_0$ , then each cell which conducts current after applying this voltage to its gate is read as 1, and each cell which does not conduct current is read as 0.

Several such read operations can be performed successively with a sequence of voltages which span the interval  $[V_L, V_R]$  e.g. as shown in Figs. 2A - 2B. In particular, assume that for a prescribed value dV, the sequence of read voltages is given by

$$V_L$$

,  $V_L+dV$ ,  $V_L+2dV$ ,  $V_L+3dV$ ,...,  $V_R$

e.g. as shown in Fig. 5 at step 500 and in Fig. 6.

Once these read operations are done, it is possible to obtain a sampled histogram of the threshold voltages in the voltage range. Assume that  $V_R - V_L = M * dV$ , where M is an integer, and let H(m), m = 1, 2, ..., M, be the sampled histogram of the threshold voltage, i.e. H(1) holds the number of cells whose threshold voltage lies in the interval  $[V_L, V_L + dV]$ , H(2) holds the number of cells whose threshold voltage lies in the interval  $[V_L + dV, V_L + 2 * dV)$  and so on. Finally, H(M) holds the number of cells whose threshold voltage lies in the interval  $[V_L + (M - 1) * dV, V_R]$ . Also, for future reference, denote by A(m), m=1,2, ..., M, the sequence of center points of the histogram's intervals, i.e.,  $A(m) = V_L + (m-1/2) * dV$ , e.g. as shown in Fig. 5 at step 510 and in Fig. 7.

Next, if the page in question belongs to a fresh block, it is expected that the sequence H(m) will exhibit two local maxima corresponding to the two highest program levels (see solid curve in Fig. 20. At the other extreme, if the page was cycled and its data retained, it is expected that only one maximum will be noticed, close to the left end of the voltage interval  $[V_L, V_R]$ .

In order to estimate the mean and standard deviation of the highest program level, a subset of histogram values is identified, which corresponds to the highest program level.

25

5

10

15

20

This is done by searching for the first bin from the right at which a local maximum is attained. Regardless of the state of the flash device in question, the first significant maximum from the right will always correspond to the highest program level, e.g. as shown in Fig. 5 at step 520 and in Fig. 8.

Once the maximizing bin is identified, several bins may be taken from either side of that bin and accounted for as belonging to cells in the highest program level. Denote by m\* the first bin index from the right at which the histogram posses a local maximum. Then, e.g. as shown in Fig. 5 at step 530 and in Fig. 9, the mean and standard deviation of the highest program level can be estimated as follows:

10

$$\mu = \frac{\sum_{k=m^*-N_B}^{m^*+N_B} H(k)A(k)}{\sum_{k=m^*-N_B}^{m^*+N_B} H(k)}$$

5

15

20

25

$$\sigma = \sqrt{\max \left( \frac{\sum_{k=m^{*}-N_{B}}^{m^{*}+N_{B}} H(k)(A(k)-\mu)^{2}}{\sum_{k=m^{*}-N_{B}}^{m^{*}+N_{B}} H(k)} - \frac{dV^{2}}{12}, 0 \right)},$$

where  $N_B$  is chosen on the one hand to guarantee that all the distribution mass of the highest program level is accounted for, and on the other hand to prevent penetration of cells from lower program levels into the computation. The term  $\frac{dV^2}{12}$  accounts for the quantization noise stemming from the sampling of the histogram.

Fine Estimation of the Mean and standard deviation of the Intermediate program Levels according to certain embodiments of the present invention, is now described in detail.

In one embodiment of the present invention, the means and standard deviations of the remaining program levels can be estimated as described hereinabove. To this end, one can define appropriate intervals  $[V_L^{(i)}, V_R^{(i)}]$ , i=1,2,... for each program level and repeat the procedure described herein.

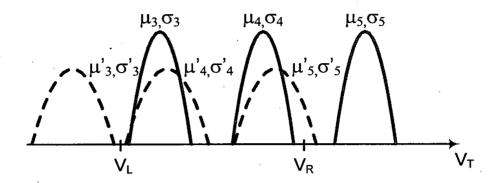

As opposed to the case of the highest program level, it is not always clear that such intervals exist which prevent ambiguity in identifying the part of the histogram which

relates to the desired program level. This situation is illustrated in Fig. 21. As shown, the threshold voltage distributions of program levels 3, 4, and 5 are depicted. The solid curves correspond to fresh devices, while the dashed curves correspond to devices which underwent substantial cycling and retention. If it is desired to estimate the mean and standard deviation of program level 4, then in order to allow estimation of the mean and standard deviation in fresh flash devices as well as in cycled and retained flash arrays, the voltage window depicted in Fig. 21 may be selected. In particular, the right edge of the interval typically contains the lobe of program level 4 in a fresh device, and the left edge of the interval typically ensures that program level 4 is captured in cycled and/or retained devices. However, given the histogram of a device whose cycle count and retention are unknown, it is not clear which local maximum corresponds to program level 4. In a fresh device, it will be the maximum on the right side of the voltage interval, and in cycled and retained devices the maximum on the left side of the voltage interval corresponds to this program level. In order to circumvent this problem, adaptive voltage windows may be defined which are determined according to the mean of the highest program level.

5

10

15

20

25

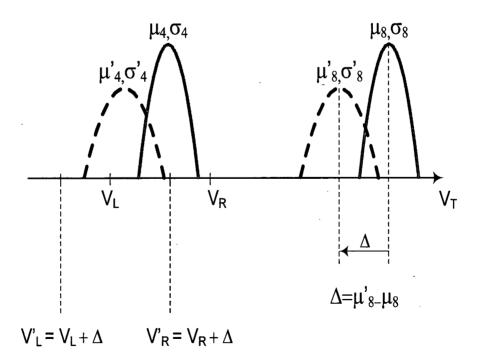

Fig. 22 depicts this procedure for the case of estimating the mean and standard deviation of program level 4. For convenience, only the lobes of program levels four (4) and eight (8) are plotted. A default search voltage interval is defined, which corresponds to the case of a fresh device (see  $V_L$ ,  $V_R$  in Fig. 22). Then, after estimating the mean of the highest program level as described herein, the difference, denoted as  $\Delta$ , is computed, between the estimated mean of the highest program level and the mean of the highest program level for a non-cycled and non-retained device. With this difference the endpoints of the search interval for program level 4 are shifted to a pair of new endpoints, namely  $V'_L$ ,  $V'_R$  as shown in Fig. 22, such that the new search interval coincides with the histogram mass of program level 4 as it behaves in the flash device. This ensures that within the voltage interval only a single maximum will be present, and it will be the one corresponding to the desired program level, e.g. as shown in Fig. 2B at steps 250 and 260, and in Fig. 10. The estimation procedure then continues in the same way as described herein.

Coarse Estimation of the Mean and standard deviation of the Intermediate Program Levels according to certain embodiments of the present invention, is now described in detail.

In some applications, fine estimation of the means and standard deviations of all the program levels with the procedure described hereinabove is prohibitively expensive in terms of the number of flash read operations employed to obtain the histograms. One way to alleviate the complexity is by using the fine estimation procedure only for a subset of the program levels.

In one embodiment, the means and standard deviations of program levels 2, 4, 6, and 8 are estimated finely as described hereinabove, and the remaining means and standard deviations are interpolated from the former. The means and standard deviations can be linearly interpolated by:

$$\mu_k = \frac{\mu_{k-1} + \mu_{k+1}}{2}, k = 3,5,7$$

15

$$\sigma_k = \frac{\sigma_{k-1} + \sigma_{k+1}}{2}, k = 3,5,7,$$

5

10

20

25

e.g. as shown in Fig. 2B at step 270 and in Fig. 11.

Methods for coping with certain types of non-Gaussian statistics according to certain embodiments of the present invention, are now described in detail.

In some situations, the Gaussian assumption regarding the probability distribution of the threshold voltage of the cells is not valid. In such cases, the formulae used to compute the decision thresholds is no longer close to optimal. It is known, as described e.g. in the above-referenced publication by Proakis, that the optimal reading thresholds should be placed precisely at the intersection point of the probability distributions corresponding to adjacent program levels. Alternatively, decision thresholds are computed, in which the intersection points are approximated by the voltage at which the histogram attains its minimal value. This can be achieved by defining new search intervals and obtaining the histogram as described hereinabove. The histogram can then be searched for the minimum, e.g. as shown in Fig. 2B at step 290 and in Fig. 13.

Methods for reducing the overhead of read operations from the flash device according to certain embodiments of the present invention, are now described in detail and are shown in Fig. 5 at step 510 and 520, and in Figs. 7 and 8. As described hereinabove, read operations are done from the flash memory device in order to build the threshold voltage histogram of a population of cells within the device. In order to reduce the overhead associated with these read operations, read operations may be performed as follows. If it is desired estimate the mean and standard deviation of the highest program level, for which an appropriate voltage search interval [ $V_L$ ,  $V_R$ ] is chosen. The process begins with the rightmost (largest) read voltage, and works its way towards the leftmost (smallest) read voltage. After the desired maximum is identified, continue reading a sufficient number of read voltages to complete  $2 * N_E + 1$  histogram bins, and then terminate the reading process and continue with the processing of the sampled histogram in order to estimate the mean and standard deviation. This approach is beneficial especially in new devices where the threshold voltage distribution of the highest program level is close to the right edge of the voltage interval [ $V_L$ ,  $V_R$ ].

5

10

15

20

25

30

Although the highest program level is used herein as an example for the possible benefit of this approach, this approach can be beneficial whenever read operations are used to estimate the means and standard deviations as described hereinabove.

Methods for ensuring uniform spreading of cells across program levels according to certain embodiments of the present invention, are now described in detail.

The accuracy of estimating the mean and standard deviation of the threshold distribution of a program level as described hereinabove depends on the number of cells which occupy this level. The more cells are programmed to a certain program level, the more accurate the mean and standard deviation estimation is. Since the data stored in the flash device is arbitrary, it may well be that the program levels of a particular page within a flash device are all the same, or that certain program levels are only scarcely occupied. This situation, unless changed, can cause inaccuracies in the estimation procedure, because the estimation might be based on too little cells. Such inaccuracies might be too high to the degree that the resulting reading thresholds will yield many detection errors and the error correcting code will fail. This situation may be circumvented by employing a scrambler on the data bits which are to be stored in the flash device and a descrambler

on the bits which are read from the flash (unit 2200 of Fig. 27). For the purposes of the present specification, a scrambler may comprise any device which receives at its input a bit sequence and produces at its output another sequence of bits such that the following two conditions are met:

1. The 1s and 0s in the output bit sequence are equally likely.

5

10

15

20

25

30

2. The original bit sequence can be easily obtained from the output sequence by employing the inverse of the scrambling operation (descrambling).

When the bit sequence to be written to the flash is guaranteed to have 1s and 0s equally likely, the distribution of cells among the program levels is guaranteed to be more or less the same. In other words, the number of cells which will be programmed to each program level will be more or less the same. The phrase "more or less" is used to stipulate that the probability that the number of cells in any particular program level is too small to ensure sufficient accuracy of estimation is small enough so as not to degrade the overall performance, e.g. as shown in Fig. 2A at steps 202 and 320, and in Fig. 16.

Methods for preventing misidentification of local maximum corresponding to desired program level according to certain embodiments of the present invention, are now described in detail.

The procedure described hereinabove for finding the lobe corresponding to the estimated program level by searching for the first maximum from the right hinges on the assumption that the histogram H(m) does not exhibit any other local maxima to the right of the desired lobe. In situations where a local maximum does exist due to some fluctuating behavior in a small set of cells, this assumption does not hold. This situation might introduce a dramatic estimation error causing the reading threshold to be wrongly placed and the entire reading process to fail. In order to prevent misidentification of the lobe corresponding to the estimated program level, the search for the maximum may be modified as follows. Upon identifying a local maximum in the histogram, the number of cells which lie to the right of this maximum is tested (Fig. 8, step 850). If this number is above some threshold Th, this maximum is assumed to be the appropriate one. Otherwise, the search for the next maximum commences. Finally, it is noted that this procedure can also be employed in situations where the search for the local maximum is done from left to right.

Methods for maintaining a threshold history table to reduce the number of training procedures according to certain embodiments of the present invention, are now described in detail and are shown e.g. in Fig. 2A at step 220, in Fig. 2B at step 300 and in Figs. 4 and 15.

The training procedures described hereinabove can be performed whenever it is difficult or impossible to determine reading thresholds which yield a sufficiently low bit error count, thus enabling the error correcting mechanism to recover the encoded data correctly. As mentioned above, performing these training procedures for each page in an erase sector might be prohibitively complex and/or might consume too much of the overall system's resources. For this reason, it is important to be able to determine appropriate reading thresholds without resorting to training.

In one embodiment of the present invention, reading thresholds of a certain page in a certain erase sector are stored in a data base and retrieved later on when reading successive pages of the same erase sector or other erase sectors. In one embodiment, a threshold history table (or data base) is structured as depicted in Fig. 23, in which BPC represents "bits per cell".

Each entry in the table comprises threshold information pertaining to a set of physical rows in the flash device. The set of rows associated with a particular row entry comprises of all the rows in the flash device sharing some common features, namely:

1. The row number within the erase sector.

5

10

15

20

25

30

- 2. The cycle count of the erase sector in which the row resides.

- 3. The retention period of the erase sector in which the row resides.