(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5946311号

(P5946311)

(45) 発行日 平成28年7月6日(2016.7.6)

(24) 登録日 平成28年6月10日(2016.6.10)

(51) Int.Cl.

H01L 33/48 (2010.01)

H01L 33/00 (2010.01)

F 1

H01L 33/48

H01L 33/00

J

請求項の数 6 (全 12 頁)

(21) 出願番号 特願2012-89929 (P2012-89929)

(22) 出願日 平成24年4月11日 (2012.4.11)

(65) 公開番号 特開2013-219263 (P2013-219263A)

(43) 公開日 平成25年10月24日 (2013.10.24)

審査請求日 平成26年11月5日 (2014.11.5)

(73) 特許権者 000001960

シチズンホールディングス株式会社

東京都西東京市田無町六丁目1番12号

(73) 特許権者 000131430

シチズン電子株式会社

山梨県富士吉田市上暮地1丁目23番1号

(74) 代理人 100126583

弁理士 宮島 明

(72) 発明者 渡辺 茂久

山梨県富士吉田市上暮地1丁目23番1号

シチズン電子株式会社内

(72) 発明者 荒井 秀和

山梨県富士吉田市上暮地1丁目23番1号

シチズン電子株式会社内

最終頁に続く

(54) 【発明の名称】 LEDモジュール

## (57) 【特許請求の範囲】

## 【請求項 1】

回路基板上に複数のLED素子と前記LED素子を駆動するドライバー回路を実装したLEDモジュールにおいて、

前記LED素子は直列接続して複数の部分LED列を形成し、さらに前記部分LED列は直列接続してLED列を形成し、

前記ドライバー回路は、ブリッジ整流回路と、前記部分LED列同士の接続部に接続するバイパス回路と、前記LED列の端部に接続する電流制限回路を含み、

前記LED素子を実装する領域は前記ドライバー回路を実装する領域の周囲に配置され、

前記ブリッジ整流回路は4個のダイオードからなり、

10

前記ダイオード同士を接続する配線の内側の領域に交流接続端子を備え、

前記ダイオード同士を接続する配線の外側の領域に前記ブリッジ回路以外のドライバー回路と前記LED列が配置され、

前記バイパス回路は、第1電流入力端子と第2電流入力端子と電流出力端子を備え、前記第1電流入力端子が前記部分LED列の接続部に接続し、前記第2電流入力端子から入力する電流により前記第1電流入力端子から入力する電流が制限され、

前記バイパス回路がディプレッション型のFETと抵抗を含み、前記第1電流入力端子に前記FETのドレインが接続し、前記第2電流入力端子に前記FETのソースと前記抵抗の一端が接続し、前記電流出力端子に前記FETのゲートと前記抵抗の他端が接続している

20

ことを特徴とする L E D モジュール。

**【請求項 2】**

回路基板上に複数の L E D 素子と前記 L E D 素子を駆動するドライバー回路を実装した L E D モジュールにおいて、

前記 L E D 素子は直列接続して複数の部分 L E D 列を形成し、さらに前記部分 L E D 列は直列接続して L E D 列を形成し、

前記ドライバー回路は、ブリッジ整流回路と、前記部分 L E D 列同士の接続部に接続するバイパス回路と、前記 L E D 列の端部に接続する電流制限回路を含み、

前記 L E D 素子を実装する領域は前記ドライバー回路を実装する領域の周囲に配置され、

前記ブリッジ整流回路は 4 個のダイオードからなり、

前記ダイオード同士を接続する配線の内側の領域に交流接続端子を備え、

前記ダイオード同士を接続する配線の外側の領域に前記ブリッジ回路以外のドライバー回路と前記 L E D 列が配置され、

前記バイパス回路は、第 1 電流入力端子と第 2 電流入力端子と電流出力端子を備え、前記第 1 電流入力端子が前記部分 L E D 列の接続部に接続し、前記第 2 電流入力端子から入力する電流により前記第 1 電流入力端子から入力する電流が制限され、

第 1 ダム材と第 2 ダム材を備え、前記第 1 ダム材が前記 L E D 列を囲み、前記第 2 ダム材が前記交流接続端子と前記ドライバー回路の間に配置され、前記第 1 ダム材と第 2 ダム材の間の領域に被覆部材を充填している

ことを特徴とする L E D モジュール。

**【請求項 3】**

前記 L E D 素子、前記 F E T、前記抵抗及び前記ブリッジ整流回路を構成するダイオードがペアチップであることを特徴とする請求項1に記載の L E D モジュール。

**【請求項 4】**

前記部分 L E D 列のうち一の部分 L E D 列が他の部分 L E D 列を環状に囲むことを特徴とする請求項1 から 3 のいずれか一項に記載の L E D モジュール。

**【請求項 5】**

前記 L E D 素子がチップサイズパッケージ L E D であることを特徴とする請求項1に記載の L E D モジュール。

**【請求項 6】**

前記部分 L E D 列のうち一の部分 L E D 列が他の部分 L E D 列を環状に囲み、前記一の部分 L E D 列に配光分布の広いチップサイズパッケージ L E D が含まれることを特徴とする請求項5に記載の L E D モジュール。

**【発明の詳細な説明】**

**【技術分野】**

**【0 0 0 1】**

本発明は、複数の L E D 素子とともに他の電子部品を回路基板に実装した L E D モジュールに関する。

**【背景技術】**

**【0 0 0 2】**

L E D 素子を使った照明器具が普及してきている。このような中で電気スタンドやランプなどの照明器具の設計手番を短くするためには光源部をモジュール化すると良い。例えば特許文献 1 の図 2 には、複数の L E D チップ ( L E D 素子 ) とともに駆動回路を同一の回路基板に実装した L E D モジュールが示されている。

**【0 0 0 3】**

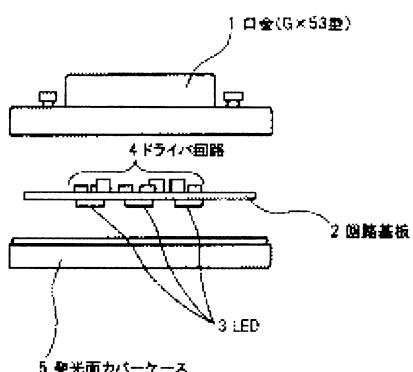

特許文献 1 の図 2 を図 6 に再掲示する。図 6 は I E C 規格の口金 ( G X 5 3 型 ) を使用する L E D ランプの断面図である。L E D モジュールは、回路基板 2 、ドライバー回路 4 、 L E D 3 ( L E D 素子 ) からなり、回路基板 2 の上面にドライバー回路 4 が実装され、回路基板 2 の下面に L E D 3 が実装されている。そしてこの L E D モジュールは口金 1 の

10

20

30

40

50

ハウジングにはめ込まれ、発光面カバークース5で抑えられる。薄型化が要請されるとときはLED3をCOB(チップオンボード)とすれば良い。なおCOBは、ペアチップ状態のLED(以下特に断らない限りLEDダイとよぶ)を回路基板2に直接的に実装するものである。

**【先行技術文献】**

**【特許文献】**

**【0004】**

**【特許文献1】特開2007-157690号公報 (図2)**

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0005】**

図6に示したLEDモジュールは、回路基板2の一方の面に駆動回路4を配置し、他方の面にLED3を配置することにより駆動回路4とLED3を一体化していた。さらに特許文献1はLED3をCOBとすることで薄型化が図れることを示唆していた。しかしながら回路基板の一方の面だけにLEDダイとドライバー回路を配置できれば、よりいっそこの薄型化が図れる。この場合、実装できる領域が狭くなるのでドライバー回路も小さくしておかなければないが、例えばドライバー回路を抵抗1個からなるようなものにしてまつては電源電圧変動に対して安定した動作を保証できなくなるように、単純化を進めると充分な性能が得られないことがある。

**【0006】**

そこで本発明は、上記課題に鑑みて為されたものであり、複数のLED素子とともに他の電子部品を回路基板に実装したLEDモジュールにおいて、ドライバー回路が小型でありながら利便性が高く充分な性能を備えさらに製造し易いLEDモジュールを提供することを目的とする。

**【課題を解決するための手段】**

**【0007】**

本発明のLEDモジュールは、回路基板上に複数のLED素子と前記LED素子を駆動するドライバー回路を実装したLEDモジュールにおいて、

前記LED素子は直列接続して複数の部分LED列を形成し、さらに前記部分LED列は直列接続してLED列を形成し、

前記ドライバー回路は、ブリッジ整流回路と、前記部分LED列同士の接続部に接続するバイパス回路と、前記LED列の端部に接続する電流制限回路を含み、

前記LED素子を実装する領域は前記ドライバー回路を実装する領域の周囲に配置され

前記ブリッジ回路は4個のダイオードからなり、

前記ダイオード同士を接続する配線の内側の領域に交流接続端子を備え、

前記ダイオード同士を接続する配線の外側の領域に前記ブリッジ回路以外のドライバー回路と前記LED列が配置される

ことを特徴とする。

前記バイパス回路は、第1電流入力端子と第2電流入力端子と電流出力端子を備え、前記第1電流入力端子が前記部分LED列の接続部に接続し、前記第2電流入力端子から入力する電流により前記第1電流入力端子から入力する電流が制限されても良い。

**【0008】**

本発明のLEDモジュールでは、交流接続端子の周囲にブリッジ整流回路とバイパス回路と電流制限回路を備えたドライバー回路が配置され、さらにその周りにLED素子が配置されている。この交流接続端子に交流電源を接続し、ブリッジ整流回路により交流電源から生成した全波整流波形でLED列を点灯させる。このLED列はLED素子が直列接続したものであり、複数の部分LED列に区分できる。部分LED列の接続部にはバイパス回路の第1電流入力端子が接続される。このときLED列を流れる電流がバイパス回路の第1電流入力端子か第2電流入力端子に流れ込む。

10

20

30

40

50

## 【0009】

ブリッジ整流回路は4個のダイオードからなる。バイパス回路は外部に対し第1電流入力端子と第2電流入力端子と電流出力端子だけを備えるよう構成する。電流制限回路は外部に対し電流入力端子と電流出力端子だけを備えるよう構成する。このときバイパス回路は第2電流入力端子から入力する電流により第1電流入力端子から入力する電流を制限する。このような構成とすることでバイパス回路及び電流制限回路は電源配線が不要となり、さらに前述のようにLED列を流れる電流がバイパス回路の第1電流入力端子か第2電流入力端子に流れ込むのでバイパス回路の制御配線も不要となる。この結果、ドライバー回路の配線が減るため、回路基板の一面に配線パターンを形成するだけでドライバー回路を作りこむことが可能となり、回路基板が製造しやすくなる。

10

## 【0010】

さらに全波整流波形の電圧が低い期間では、全波整流波形を印加する側からみて前段の部分LED列からバイパス回路の第1電流入力端子を通じて電流が流れ、前段の部分LED列が点灯し、後段の部分LED列が消灯した状態になる。全波整流波形の電圧が高くなり後段の部分LED列にも電流が流れるようになると、バイパス回路の第1電流入力端子を経由する電流がなくなり、前段の部分LED列とともに後段の部分LED列が効率よく点灯する。また全波整流波形の一周期のなかで比較的長い期間、LED列が点灯した状態を維持できるため輝度の向上やちらつきの低減が達成される。

## 【0011】

前記バイパス回路がディプレッション型のFETと抵抗を含み、前記第1電流入力端子に前記FETのドレインが接続し、前記第2電流入力端子に前記FETのソースと前記抵抗の一端が接続し、前記電流出力端子に前記FETのゲートと前記抵抗の他端が接続しても良い。

20

## 【0012】

第1ダム材と第2ダム材を備え、前記第1ダム材が前記LED列を囲み、前記第2ダム材が前記交流接続端子と前記ドライバー回路の間に配置され、前記第1ダム材と第2ダム材の間の領域に被覆部材を充填しても良い。

## 【0013】

前記LED素子、前記FET、前記抵抗及び前記ブリッジ整流回路を構成するダイオードがベアチップであっても良い。

30

## 【0014】

前記部分LED列のうち一の部分LED列が他の部分LED列を環状に囲んでも良い。

## 【0015】

前記LED素子がチップサイズパッケージLEDであっても良い。

## 【0016】

前記部分LED列のうち一の部分LED列が他の部分LED列を環状に囲み、前記一の部分LED列に配光分布の広いチップサイズパッケージLEDが含まれても良い。

## 【発明の効果】

## 【0017】

本発明のLEDモジュールでは、交流接続端子の周囲にドライバー回路が配置され、さらにその周りにLED素子が配置されている。ドライバー回路に含まれるバイパス回路と電流制限回路は電源配線や制御配線が不要なため、回路基板の一面に配線パターンを形成するだけでドライバー回路を作り込め、回路基板製造が容易になる。またブリッジ回路を実装しているので交流電源を接続するだけで全波整流波形によりLED素子を駆動できるため、利便性の高さと効率の良い駆動が達成される。さらにバイパス回路により全波整流波形の一周期のなかで比較的長い期間点灯させられるので輝度の向上やちらつきの低減といった効果も得られる。さらにバイパス回路と電流制限回路を備えているので、広い動作電圧範囲が確保され、交流電源の電圧が変動しても動作が安定する。

40

## 【0018】

以上のように本発明のLEDモジュールは、交流電源を接続するだけで良く、この交流

50

電源から得た全波整流波形で LED 素子を駆動しても非点灯期間が短いうえ、さらに回路基板の配線パターンが簡単化するため、ドライバー回路が小型でありながら利便性が高く充分な性能を備えさらに製造し易い。

**【図面の簡単な説明】**

**【0019】**

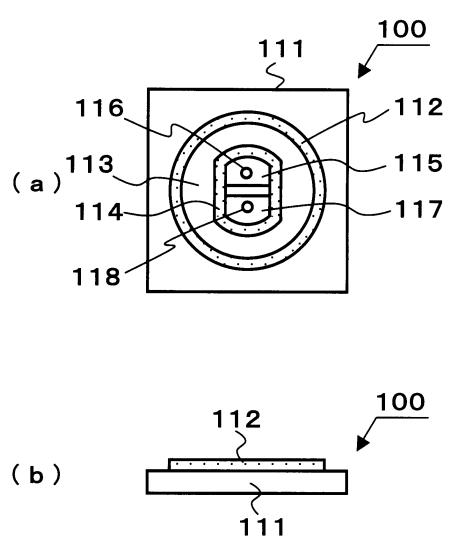

【図1】本発明の第1実施形態として示すLEDモジュールの外形図。

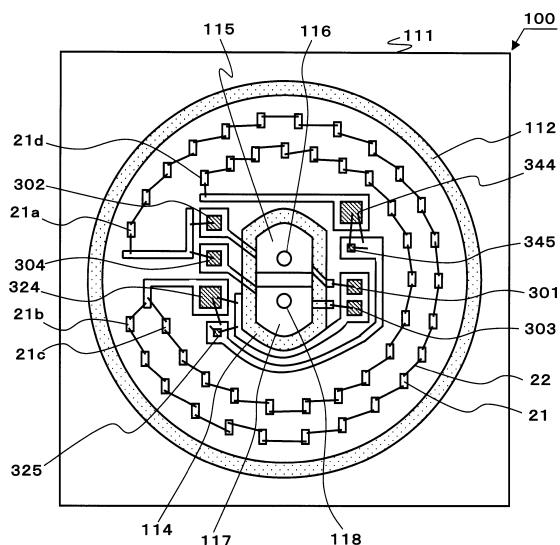

【図2】図1に示すLEDモジュールから蛍光樹脂を除いた状態の平面図。

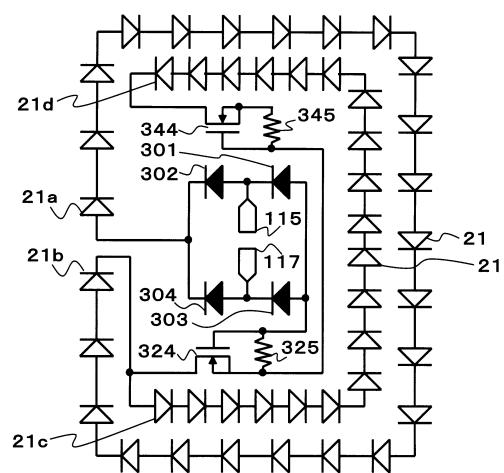

【図3】図1に示すLEDモジュールの実体的な回路図。

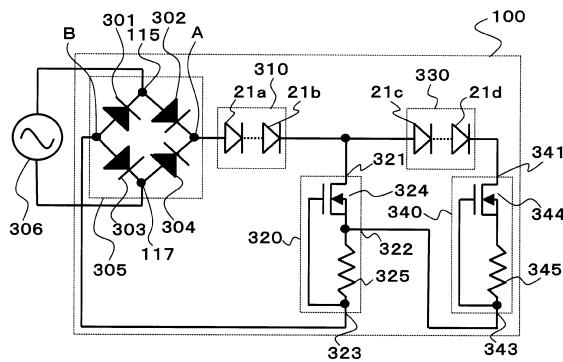

【図4】図1に示すLEDモジュールの回路図。

【図5】本発明の第2実施形態で用いるLED素子の断面図。

10

【図6】従来例として示したLEDモジュールの断面図。

**【発明を実施するための形態】**

**【0020】**

以下、添付図1～5を参照しながら本発明の好適な実施形態について詳細に説明する。なお図面の説明において、同一または相当要素には同一の符号を付し、重複する説明は省略する。また説明のため部材の縮尺は適宜変更している。さらに特許請求の範囲に記載した発明特定事項との関係をカッコ内に記載している。なおLED素子は様々な形態をとるので、ウェハーから切り出されたベアチップ状態のLED素子をLEDダイと呼び、平面サイズがLEDダイと略等しく且つLEDダイの表面又は側面を樹脂等で被覆したLED素子をチップサイズパッケージLEDと呼び区別する。

20

(第1実施形態)

**【0021】**

先ず図1によりLEDモジュール100の外観を説明する。図1はLEDモジュール100の外形図であり、(a)が平面図、(b)が正面図である。回路基板111上には円形のダム材112(第1ダム材)と、図の縦方向に延びた直線状の辺と上下部分に存在する曲線状の辺からなるダム材114(第2ダム材)がある。ダム材112とダム材114の間の領域には蛍光樹脂113(被覆部材)が充填される。ダム材114で囲まれた領域には交流接続端子115, 117があり、交流接続端子115, 117はそれぞれスルーホール116, 118を備えている。図示していないが、回路基板111の裏面には照明器具から電力供給を受けるための二つの裏面交流接続端子があり、スルーホール116, 118を介して裏面交流接続端子が交流接続端子115, 117と接続している。

30

**【0022】**

次に図2によりLEDモジュール100の電子部品の配置を説明する。図2は図1に示したLEDモジュール100から蛍光樹脂113を除いた状態の平面図である。なおダム材114の下部に存在する配線パターンも実線で示している。

**【0023】**

図2において、ダム材114の周囲には、ダイオード301, 302, 303, 304と、FET324, 344と、抵抗325, 345がある。ダイオード301, 302, 303, 304と、FET324, 344と、抵抗325, 345からドライバー回路が構成される。これらの電子部品が実装された領域を45個のLEDダイ21(以下、個別のLEDダイについては必要に応じてサフィックスをつけて区別する)が2重の環で囲んでいる。これらのLEDダイ21は直列接続し一本のLED列を構成し、このLED列の外側の環及び内側の環がそれぞれ部分LED列(図4で示す部分LED列310, 330)となる。さらにLEDダイ21が実装された領域の外側には円形のダム材112がある。

40

**【0024】**

ダイオード301, 302, 303, 304及び2個のFET324, 344はベアチップであり、導電性のペーストで配線パターン上にダイポンディングされている。このときダイオード301, 302, 303, 304の底面はアノードであり、FET324, 344の底面はドレインである。抵抗325, 355及びLEDダイ21もベアチップで

50

あり、配線パターン上にダイボンディングされているが、底面は絶縁されている。なお L E D ダイ 2 1 の底部にもダイボンディングのために島状（孤立しており他の配線パターンとは接続していない状態）の配線パターンがあるが図示していない。ダイオード 3 0 1 , 3 0 2 , 3 0 3 , 3 0 4 と F E T 3 2 4 , 3 4 4 の底部を除き、ダイオード 3 0 1 , 3 0 2 , 3 0 3 , 3 0 4 、F E T 3 2 4 , 3 4 4 、抵抗 3 2 5 , 3 4 5 は、配線パターンとワイヤ 2 2 で接続している。なお F E T 3 4 4 のソースと抵抗 3 4 5 だけは直接的にワイヤ 2 2 で接続している。L E D ダイ 2 1 も配線パターン若しくは他の L E D ダイ 2 1 とワイヤ 2 2 で接続している。なお図 2 では多くの L E D ダイ 2 1 同士を直接的にワイヤ 2 2 で接続しているが、L E D ダイ 2 1 同士の距離が離れている場合は、島状の中継用配線パターンを設けワイヤ 2 2 の長を調整しても良い。

10

#### 【 0 0 2 5 】

L E D ダイ 2 1 は  $500 \mu m \times 290 \mu m$  、F E T 3 2 4 , 3 4 4 は  $1.5 mm \times 1.5 mm$  、抵抗 3 2 5 , 3 4 5 は  $500 \mu m \times 500 \mu m$  である。回路基板 1 1 1 は熱伝導性と反射率を考慮してアルミナを使用した。配線パターンは A g 上に N i , P d , A u を積層している。ダム材 1 1 2 , 1 1 4 はシリコーン樹脂からなり、太さが  $0.7 \sim 1.0 mm$  であり、高さが  $0.5 \sim 0.7 mm$  である。図 1 に示した蛍光樹脂 1 1 3 は蛍光体を含有したシリコーン樹脂であり、厚さが  $400 \sim 800 \mu m$  程度である。なお F E T 3 2 4 , 3 4 4 の被覆材を蛍光樹脂 1 1 3 としても光による誤動作はなかった。

#### 【 0 0 2 6 】

次に図 1 , 2 を参照して L E D モジュール 1 0 0 の製造方法を説明する。まず回路基板 1 1 1 上に L E D ダイ 2 1 、ダイオード 3 0 1 ~ 3 0 4 、F E T 3 2 4 , 3 4 4 及び抵抗 3 2 5 , 3 4 5 をダイボンディングし、その後ワイヤボンディングする。次にディスペンサで硬化前のダム材 1 1 2 , 1 1 4 を配置し、ダム材 1 1 2 , 1 1 4 を約 150 °で硬化させる。最後にディスペンサでダム材 1 1 2 , 1 1 4 の間に蛍光樹脂 1 1 3 を塗布し、L E D ダイ 2 1 及び他の電子部品を被覆する。なお蛍光樹脂 1 1 3 の焼結温度は約 150 °である。

20

#### 【 0 0 2 7 】

次に L E D モジュール 1 0 0 の接続状態を図 3 により説明する。図 3 は図 2 に示した L E D モジュール 1 0 0 の実体的な回路図であり、図 2 で示した電子部品と図 3 で示した電子部品の相対的な位置関係が概ね一致するよう描いている。L E D ダイ 2 1 は直列接続しており、この L E D 列は、L E D ダイ 2 1 a から始まり、途中 L E D ダイ 2 1 b , 2 1 c を通り、L E D ダイ 2 1 d で終わっている。L E D ダイ 2 1 a から L E D ダイ 2 1 b に至る部分（図 4 で示す部分 L E D 列 3 1 0 ）の実装部は外周に沿っている。L E D ダイ 2 1 c から L E D ダイ 2 1 d に至る部分（図 4 で示す部分 L E D 列 3 3 0 ）は部分 L E D 列 3 1 0 の内側を環状に配列している。L E D ダイ 2 1 a のアノードはダイオード 3 0 2 , 3 0 4 のカソードと接続している。L E D ダイ 2 1 b のカソードは、L E D ダイ 2 1 c のアノードとともに F E T 3 2 4 のドレインに接続している。L E D ダイ 2 1 d のカソードは F E T 3 4 4 のドレインに接続している。

30

#### 【 0 0 2 8 】

ダイオード 3 0 1 , 3 0 3 のアノードは抵抗 3 2 5 と F E T 3 2 4 のゲートに接続している。ダイオード 3 0 1 とダイオード 3 0 2 の接続部及びダイオード 3 0 3 とダイオード 3 0 4 の接続部はそれぞれ交流接続端子 1 1 5 , 1 1 7 と接続している。F E T 3 4 4 のソースは抵抗 3 4 5 の一端と接続し、F E T 3 4 4 のゲートは抵抗 3 4 5 の他端と接続するとともに、抵抗 3 2 5 及び F E T 3 2 4 のソースと接続している。

40

#### 【 0 0 2 9 】

次に図 4 により L E D モジュール 1 0 0 の動作について説明する。図 4 は L E D モジュール 1 0 0 と周辺回路の回路図である。なお図 3 の回路図と図 4 に示した L E D モジュール 1 0 0 の回路図は等価であり、各電子部品は共通の符号を用いている。L E D モジュール 1 0 0 は、ブリッジ整流回路 3 0 5 、部分 L E D 列 3 1 0 、部分 L E D 列 3 3 0 、バイパス回路 3 2 0 、電流制限回路 3 4 0 からなり、図 4 では商用交流電源 3 0 6 も書き加え

50

ている。なおドライバー回路は L E D モジュール 1 0 0 から部分 L E D 列 3 1 0 , 3 3 0 を除いた部分である。ブリッジ整流回路 3 0 5 は 4 個のダイオード 3 0 1 , 3 0 2 , 3 0 3 , 3 0 4 からなり、端子 A が全波整流波形の出力端子であり、端子 B が基準電圧を与える端子となる。商用交流電源 3 0 6 はブリッジ整流回路 3 0 5 の入力端子（交流接続端子 1 1 5 , 1 1 7 ）に接続している。

#### 【 0 0 3 0 】

L E D モジュール 1 0 0 全体の L E D 列は部分 L E D 列 3 1 0 と部分 L E D 列 3 3 0 とが直列接続したものである。部分 L E D 列 3 1 0 内では L E D ダイ 2 1 a , 2 1 b を含む多数の L E D ダイ 2 1 ( 図 3 参照 ) が直列接続しており、同様に部分 L E D 列 3 3 0 内でも L E D ダイ 2 1 c , 2 1 d を含む多数の L E D ダイ 2 1 ( 図 3 参照 ) が直列接続している。10 部分 L E D 列 3 1 0 のアノードはブリッジ整流回路 3 0 5 の A 端子に接続している。部分 L E D 列 3 1 0 , 3 3 0 の接続部はバイパス回路 3 2 0 の電流入力端子 3 2 1 ( 第 1 電流入力端子 ) と接続している。部分 L E D 列 3 3 0 のカソードは電流制限回路 3 4 0 の電流入力端子 3 4 1 に接続している。

#### 【 0 0 3 1 】

バイパス回路 3 2 0 は、電流入力端子 3 2 1 ( 第 1 電流入力端子 ) 、電流入力端子 3 2 2 ( 第 2 電流入力端子 ) 、電流出力端子 3 2 3 を備えている。電流入力端子 3 2 2 は電流制限回路 3 4 0 の電流出力端子 3 4 3 と接続している。電流出力端子 3 2 3 はブリッジ整流回路 3 0 5 の B 端子に接続している。バイパス回路 3 2 0 は、ディプレッション型の F E T 3 2 4 及び抵抗 3 2 5 からなり、電流入力端子 3 2 1 に F E T 3 2 4 のドレインが接続し、電流入力端子 3 2 2 に F E T 3 2 4 のソースと抵抗 3 2 5 の一端が接続し、電流出力端子 3 2 3 に F E T 3 2 4 のゲートと抵抗 3 2 5 の他端が接続している。またバイパス回路 3 2 0 は、電流入力端子 3 2 2 から流入する電流により電流入力端子 3 2 1 から流入する電流が制限される。20

#### 【 0 0 3 2 】

電流制限回路 3 4 0 は、バイパス回路 3 2 0 と略同じ回路構成であり、相違点はバイパス回路 3 2 0 の電流入力端子 3 2 2 に相当するものがないことだけである。F E T 3 4 4 、抵抗 3 4 5 の結線もバイパス回路 3 2 0 と等しい。なお L E D ダイ 2 1 の順方向電圧降下量が 3 V 程度なので、部分 L E D 列 3 1 0 の閾値は約 7 5 V 、部分 L E D 列 3 3 0 の閾値は約 6 0 V となり、L E D モジュール 1 0 0 は実効値が 1 2 0 V となる商用交流電源 3 0 6 に対応している。また抵抗 3 4 5 は、抵抗 3 2 5 よりも値が小さく、抵抗 3 4 5 と抵抗 3 2 5 の抵抗値の比を 1 : 2 にしている。30

#### 【 0 0 3 3 】

次に図 4 により L E D モジュール 1 0 0 の点灯状況を説明する。全波整流波形の電圧が上昇し、部分 L E D 列 3 1 0 の閾値を越えると、部分 L E D 列 3 1 0 とバイパス回路 3 2 0 に電流が流れ部分 L E D 列 3 1 0 が点灯する。このとき抵抗 3 2 5 から F E T 3 2 4 のソースにフィードバックが掛かり、バイパス回路 3 2 0 は定電流動作する。

#### 【 0 0 3 4 】

さらに全波整流波形の電圧が上昇し、部分 L E D 列 3 1 0 の閾値と部分 L E D 列 3 3 0 の閾値の和よりも大きくなると、部分 L E D 列 3 3 0 及び電流制限回路 3 4 0 にも電流が流れ始める。電流入力端子 3 2 2 に入力する電流が所定値を超えると、F E T 3 2 4 はソース電圧が上昇し、ソース - ゲート間の電圧が広がるためカットオフする。このとき抵抗 3 4 5 から F E T 3 4 4 にフィードバックが掛かり、電流制限回路 3 4 0 は定電流動作する。このようにして部分 L E D 列 3 1 0 と部分 L E D 列 3 3 0 が点灯する。なお全波整流波形の電圧が下降する期間では、全波整流波形の電圧が上昇する期間の逆の過程を辿る。40

#### 【 0 0 3 5 】

L E D モジュール 1 0 0 は、部分 L E D 列 3 1 0 と部分 L E D 列 3 3 0 がそれぞれ環状に配列している ( 図 2 参照 ) ので、全波整流波形の低電圧位相でも高位相でも環状に発光するため良好な配光分布が得られる。

#### 【 0 0 3 6 】

10

20

30

40

50

また L E D モジュール 100 ではバイパス回路 320 がディプレッション型の F E T 324 と抵抗 325 からなるだけである。さらにバイパス回路 320 は、部分 L E D 列 330 を流れる電流がバイパス回路 320 の第 2 の電流入力端子 322 に入力し、第 1 の電流入力端子 321 から流れ込む電流を制限しているため、電源配線や制御配線が存在しない。このため配線を交差させることなく回路図が描ける（図 3 参照）。電流制限回路 340 も同様である。このことは回路基板 111 の表面上の配線パターンとワイヤ 22（図 2 参照）だけで各電子部品を接続できることを示している。すなわち回路基板 111（図 1, 2 参照）は、交流接続端子 115, 117 に接続するスルーホール 116, 118（図 1 参照）を除きスルーホールが不要となり製造しやすくなる。

## 【0037】

10

図 4 においてバイパス回路 320 は F E T 324 と抵抗 325 からなっていた。同様に電流制限回路 340 は F E T 344 と抵抗 345 からなっていた。周知のように、電流制限回路は 2 個の抵抗とエンハンスマント型の F E T と N P N バイポーラ型のトランジタでも構成できる。この電流制限回路は、電流入力端子（第 1 電流入力端子）に抵抗と F E T のドレインを接続し、この抵抗の他端を F E T のゲートとトランジスタのコレクタに接続する。そして他の抵抗と F E T のソースとトランジスタのベースを接続し、この抵抗の他端とトランジスタのエミッタを電流出力端子に接続する。このときトランジスタのベース等に接続する配線を第 2 電流入力端子とすると、第 2 電流入力端子に入力する電流により第 1 電流入力端子に入力する電流を制限するバイパス回路が構成できる。

## 【0038】

20

図 4 において、部分 L E D 列 310 とバイパス回路 320 からなるブロックと、部分 L E D 列 330 と電流制限回路 340 からなるブロックとが相似している。すなわち部分 L E D 列 310 とバイパス回路 320 からなるブロックをカスケード接続し、最終段のブロックに含まれるバイパス回路を電流制限回路とすることも可能である。このときも前述と同様に配線を交差させずに回路図が描けるため、交流接続端子を除き回路基板にスルーホールが不要となる。なお部分 L E D 列に含まれる L E D 素子の数及び抵抗値は使用条件により調整する必要がある。このように L E D モジュールにおいて部分 L E D 列及びバイパス回路からなるブロックを多段化すると、回路電流の変化をきめ細かく制御できるので回路電流波形が正弦波に近づき、力率や歪率が改善する。

## （第 2 実施形態）

30

## 【0039】

第 1 実施形態として示した L E D モジュール 100 では L E D ダイ 21 を回路基板 111 にダイボンディングしワイヤ 22 で配線パターン若しくは他の L E D ダイに接続していた。しかしながら L E D ダイの実装方法はダイボンディング及びワイヤボンディングに限られず、L E D ダイをフリップチップ実装しても良い。この場合、配線パターンにより L E D ダイ同士を接続することとなるので接続用のワイヤが不要になる。このためワイヤの影がなくなり L E D モジュールの発光効率が向上する。また L E D モジュール 100 では F E T 324, 344 と抵抗 325, 345 もダイボンディング及びワイヤボンディングで実装し、小型化を図ると共に L E D ダイ 21 の実装方法と共に通化させていた。しかし F E T や抵抗は表面実装用のチップ部品でも良い。同様に L E D 素子は L E D ダイに限られず表面実装用のチップ部品でも良い。そこで図 4 により第 2 実施形態として L E D ダイと略同じサイズの表面実装用 L E D 素子（チップサイズパッケージ L E D と呼ぶ、チップサイズパッケージは C S P とも呼ばれる）を用いた L E D モジュールを説明する。

40

## 【0040】

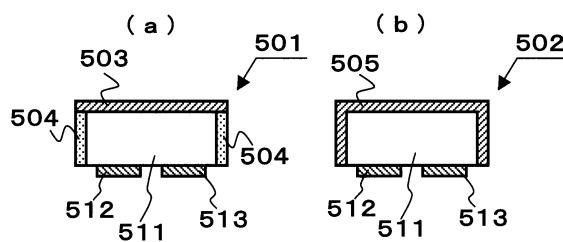

図 5 は本発明の第 2 実施形態の L E D モジュールで用いるチップサイズパッケージ L E D 501, 502（L E D 素子）の断面図である。（a）で示したチップサイズパッケージ L E D 501 では、L E D ダイ 511 の側面を反射性樹脂 504（被覆部材）が覆い、L E D ダイ 511 の上面を蛍光樹脂 503（被覆部材）が覆っている。（b）で示したチップサイズパッケージ L E D 501 では、L E D ダイ 511 の側面及び上面を蛍光樹脂 505（被覆部材）が覆っている。L E D ダイ 511 は下面に突起電極 512, 513 を備

50

え、突起電極 512, 513 がそれぞれアノードとカソードになる。なお LED ダイ 511 は、厚みが 80 ~ 120 μm でサファイアなどからなる透明絶縁基板を備え、その下面に発光層を含む半導体層を形成している。突起電極 512, 513 は、半導体層を覆う絶縁膜のスルーホールを介して半導体層と接続している。また突起電極 512, 513 はフリップチップ実装しやすいように層間絶縁膜や層間配線など半導体プロセスで良く知られた手法によりサイズや位置を調整している。

#### 【0041】

蛍光樹脂 503, 505 はシリコーン樹脂に蛍光体を混練し硬化させたもので厚さは 100 μm 程度である。反射性樹脂 504 もシリコーン樹脂にアルミナや酸化チタンなどの反射性部粒子を混練し硬化させたもので厚さは 100 μm 程度である。この結果、チップサイズパッケージ LED 501 は上方向にのみ配光分布を有するのに対し、チップサイズパッケージ LED 502 は側面からも光を放射するので広い配光分布を有する。10

#### 【0042】

第 2 実施形態における LED モジュール（図示せず）は、第 1 実施形態の LED モジュール 100 と同じ回路であり、図 2 における LED ダイ 21 の代わりにチップサイズパッケージ LED 501, 502 を配置したものとなる。なお配線パターンはフリップチップ実装用のものとなり、チップサイズパッケージ LED 501, 502 は半田リフローで配線パターンと接続する。このとき LED ダイ 21a, 21b を含む外側の部分 LED 列 310 では LED ダイ 21 をチップサイズパッケージ LED 502 ( 又はチップサイズパッケージ LED 501 とチップサイズパッケージ LED 502 が混ざったもの ) で置き換える、LED ダイ 21c, 21d を含む内側の部分 LED 列 330 では LED ダイ 21 をチップサイズパッケージ LED 501 で置き換えると良い。このようにすると LED モジュールの配光分布を広げながら発光効率の低下を防ぐことができる。また図 2 の LED モジュール 100 に対し第 2 実施形態における LED モジュールは、LED モジュール 100 におけるダム材 112 が不要となり、ダイオード、FET、抵抗を表面実装用にすることでダム材 114 も不要となる。同時に蛍光樹脂 113 ( 図 1 参照 ) も不要となる。20

#### 【符号の説明】

#### 【0043】

- 100 ... LED モジュール、30

- 111 ... 回路基板、

- 112 ... ダム材 ( 第 1 ダム材 ) 、

- 113, 503, 505 ... 蛍光樹脂 ( 被覆部材 ) 、

- 114 ... ダム材 ( 第 2 ダム材 ) 、

- 115, 117 ... 交流接続端子、

- 116, 118 ... スルーホール、

- 21, 21a ~ d ... LED ダイ ( LED 素子 ) 、

- 22 ... ワイヤ、

- 301, 302, 303, 304 ... ダイオード、

- 305 ... ブリッジ整流回路、40

- 306 ... 商用交流電源、

- 310, 330 ... 部分 LED 列、

- 320 ... バイパス回路、

- 321 ... 電流入力端子 ( 第 1 電流入力端子 ) 、

- 322 ... 電流入力端子 ( 第 2 電流入力端子 ) 、

- 323, 343 ... 電流出力端子、

- 324, 344 ... FET、

- 325, 345 ... 抵抗、

- 340 ... 電流制限回路、

- 341 ... 電流入力端子、

- 501, 502 ... チップサイズパッケージ LED ( LED 素子 ) 、50

5 0 4 ... 反射性樹脂(被覆部材)、

5 1 1 ... L E D ダイ、

5 1 2 , 5 1 3 ... 突起電極。

【図 1】

【図 2】

【図3】

【図4】

【図5】

【図6】

---

フロントページの続き

(72)発明者 秋山 貴

山梨県富士吉田市上暮地1丁目23番1号 シチズン電子株式会社内

(72)発明者 落合 雄紀

山梨県富士吉田市上暮地1丁目23番1号 シチズン電子株式会社内

審査官 高棕 健司

(56)参考文献 特開2009-218192(JP,A)

特開2011-040701(JP,A)

特開2005-117028(JP,A)

特開2003-007929(JP,A)

登録実用新案第3168487(JP,U)

(58)調査した分野(Int.Cl., DB名)

H01L 33/00 - 33/64

H05B 37/00 - 39/10