(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3974284号

(P3974284)

(45) 発行日 平成19年9月12日(2007.9.12)

(24) 登録日 平成19年6月22日(2007.6.22)

(51) Int.C1.

F 1

HO1L 23/52 (2006.01)

HO1L 21/3205 (2006.01)

HO1L 21/88

M

請求項の数 7 (全 11 頁)

(21) 出願番号 特願平11-73486

(22) 出願日 平成11年3月18日(1999.3.18)

(65) 公開番号 特開2000-269213(P2000-269213A)

(43) 公開日 平成12年9月29日(2000.9.29)

審査請求日 平成17年2月22日(2005.2.22)

(73) 特許権者 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 100058479

弁理士 鈴江 武彦

(74) 代理人 100084618

弁理士 村松 貞男

(74) 代理人 100092196

弁理士 橋本 良郎

(74) 代理人 100091351

弁理士 河野 哲

(74) 代理人 100088683

弁理士 中村 誠

(74) 代理人 100070437

弁理士 河井 将次

最終頁に続く

(54) 【発明の名称】半導体装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項1】

半導体基板上に形成された絶縁層に溝或いは孔を形成する工程と、

前記溝或いは孔が形成された絶縁層の表面に、所定の金属元素を含む第1の導電層を形成する工程と、

前記基板を酸化雰囲気に暴露することにより、前記第1の導電層の表面に前記金属元素の酸化物層を形成する工程と、

前記酸化物層の表面に、前記金属元素より酸化物の生成自由エネルギーが低いA1元素を含む第2の導電層を堆積する工程と、

前記基板を真空中でアニール処理し、前記酸化物層を前記A1元素により還元することにより、前記第1の導電層と前記第2の導電層との界面に前記A1元素の酸化物層を形成する工程と、

前記A1元素の酸化物層の形成で酸化されずに残った前記第2の導電層を除去する工程と、

前記第2の導電層の除去後に、前記絶縁層の溝或いは孔内にCu配線を埋め込み形成する工程と、

を含むことを特徴とする半導体装置の製造方法。

## 【請求項2】

前記A1元素の酸化物層を形成する工程と、前記絶縁層の溝或いは孔内に前記配線を埋め込み形成する工程との間に、

10

20

前記溝或いは孔の側面に形成される前記 A<sub>1</sub> 元素の酸化物層を残しつつ、前記溝或いは孔の底面に形成される前記 A<sub>1</sub> 元素の酸化物層を除去する工程を行うことを特徴とする請求項 1 に記載の半導体装置の製造方法。

**【請求項 3】**

前記金属元素が W, Ti, Ta 或いは Nb であり、第 1 の導電層が W, Ti, Ta 或いは Nb の窒化物であることを特徴とする請求項 1 に記載の半導体装置の製造方法。

**【請求項 4】**

半導体基板上に形成された所定元素の酸化物を含む絶縁層に溝或いは孔を形成する工程と、

前記溝或いは孔が形成された絶縁層の表面に、前記所定元素より酸化物の生成自由エネルギーが低い A<sub>1</sub> 元素を含む第 1 の導電層を形成する工程と、

前記基板を真空中でアニール処理し、前記所定元素の酸化物を前記 A<sub>1</sub> 元素により還元することにより、前記絶縁層と第 1 の導電層との界面に該 A<sub>1</sub> 元素の酸化物層を形成する工程と、

前記 A<sub>1</sub> 元素の酸化物層の形成で酸化されずに残った前記第 1 の導電層を除去する工程と、

前記第 1 の導電層の除去後に、前記絶縁層の溝或いは孔内に Cu 配線を埋め込み形成する工程と、

を含むことを特徴とする半導体装置の製造方法。

**【請求項 5】**

半導体基板上に形成された所定元素の酸化物を含む絶縁層に溝或いは孔を形成する工程と、

前記溝或いは孔が形成された絶縁層の表面に、前記所定元素より酸化物の生成自由エネルギーが低い A<sub>1</sub> 元素を含む第 1 の導電層を形成する工程と、

前記基板を真空中でアニール処理し、前記所定元素の酸化物を前記 A<sub>1</sub> 元素により還元することにより、前記絶縁層と第 1 の導電層との界面に該 A<sub>1</sub> 元素の酸化物層を形成する工程と、

前記 A<sub>1</sub> 元素の酸化物層の形成で酸化されずに残った前記第 1 の導電層を除去する工程と、

前記第 1 の導電層の除去後に、前記 A<sub>1</sub> 元素より酸化物の生成自由エネルギーが高い金属元素を含む第 2 の導電層を堆積する工程と、

前記第 2 の導電層を堆積した後に、前記絶縁層の溝或いは孔内に Cu 配線を埋め込み形成する工程と、

を含むことを特徴とする半導体装置の製造方法。

**【請求項 6】**

前記所定元素が Si であることを特徴とする請求項 4 又は 5 に記載の半導体装置の製造方法。

**【請求項 7】**

前記所定元素が Si, 前記 A<sub>1</sub> 元素より酸化物の生成自由エネルギーが高い金属元素が W, Ti, Ta 或いは Nb, 且つ第 2 の導電層が W, Ti, Ta 或いは Nb の窒化物であることを特徴とする請求項 5 に記載の半導体装置の製造方法。

**【発明の詳細な説明】**

**【0001】**

**【発明の属する技術分野】**

本発明は、配線材の拡散を抑制するバリアメタルを具備する半導体装置の製造方法に関する。

**【0002】**

**【従来の技術】**

半導体装置のバリアメタルとして用いられる TiN 層の表面を酸化雰囲気にさらすことにより、A<sub>1</sub> に対する拡散バリア性が向上することが知られている。これは、TiN の表面

10

20

30

40

50

と結晶粒界に沿って、バリア性の高い Ti 酸窒化物層が形成されるためと考えられている。

#### 【 0 0 0 3 】

例えば、Al 配線が Si 基板の拡散層と接続するコンタクトホールに、拡散バリアとして TiN 膜を堆積した後、微量の酸素を含む窒素雰囲気でアニール（スタッフィング処理）を行った上で Al 膜を堆積すると、その後の熱履歴による Al と Si の相互拡散を効果的に阻止することができる。

#### 【 0 0 0 4 】

そこで、半導体装置の Cu ダマシン配線の製造工程に対しても同様に、TiN 層の表面または粒界に Ti 酸化物 ( $TiO_x$ ,  $Ti(ON)_x$ ) を形成し、Cu の拡散を抑制する方法が提案されている。

10

#### 【 0 0 0 5 】

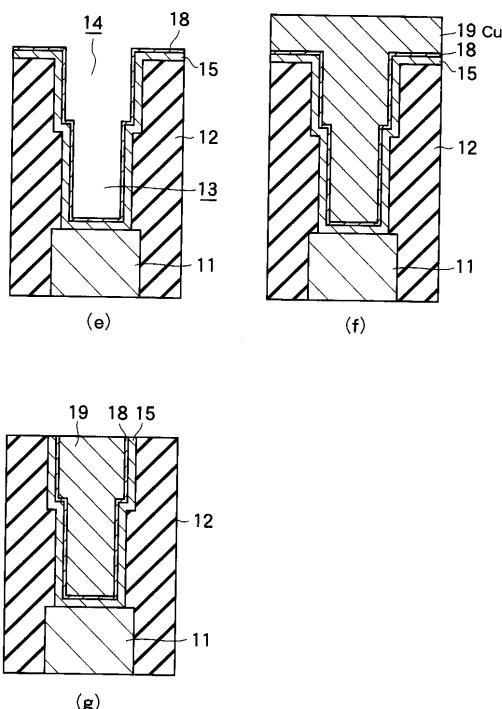

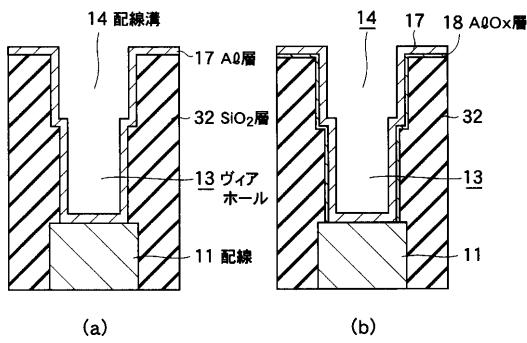

この製造プロセスを図 5 の工程断面図を用いて説明する。先ず、図 5 (a) に示すように、絶縁層 12 に形成された配線溝 14 とヴィアホール 13 に TiN 層 15 を堆積する。ヴィアホール 13 は下層の配線 11 との接続部位であり、底部は配線 11 が露出している。次いで、図 5 (b) に示すように、TiN 層 15 の表面に Ti 酸化物 ( $TiO_x$ ) 16 を形成する。Ti 酸化物 16 は、大気中暴露、酸素プラズマ処理、微量酸素を含む窒素アニール（stuffing 処理）することで形成することができる。次いで、図 5 (c) に示すように、Cu 19 を堆積し、配線溝 14 とヴィアホール 13 を Cu 19 で埋め込む。そして、図 5 (d) に示すように、CMP により絶縁層 12 上の余分な Cu 19 及び TiN 層 15 を除去し、Cu ダマシン配線 19 を形成する。

20

#### 【 0 0 0 6 】

しかしながら、以上的方法では、TiN 層の Cu 拡散に対するバリア性が十分でなく、製造プロセスの熱履歴により Cu が絶縁層中に拡散する恐れがある。Cu 膜と TiN 層の界面の Ti 酸化物の存在により、Cu 膜と TiN 層の密着強度が低下して CMP で不良が発生する問題がある。

#### 【 0 0 0 7 】

##### 【発明が解決しようとする課題】

上述したように、バリアメタル層の TiN の表面を酸化雰囲気にさらすことによって、Al に対するバリア性が向上することが知られているが、Cu 膜に対するバリア性の顕著な向上が見られないという問題点がある。また、Ti 酸化物と TiN 層との界面に Ti 酸化物が存在することによって、密着強度が不足し CMP 時に不良が発生するという問題点がある。

30

#### 【 0 0 0 8 】

本発明の目的は、配線材に対するバリア性の向上を図ると共に、CMP 時の膜剥がれによる不良の発生を抑制し得る半導体装置の製造方法を提供することにある。

#### 【 0 0 0 9 】

##### 【課題を解決するための手段】

###### 【構成】

本発明は、上記目的を達成するために以下のように構成されている。

40

#### 【 0 0 1 0 】

(1) 本発明（請求項 1）の半導体装置の製造方法は、半導体基板上に形成された絶縁層に溝或いは孔を形成する工程と、前記溝或いは孔が形成された絶縁層の表面に、所定の金属元素を含む第 1 の導電層を形成する工程と、前記基板を酸化雰囲気に暴露することにより、前記第 1 の導電層の表面に前記金属元素の酸化物層を形成する工程と、前記酸化物層の表面に、前記金属元素より酸化物の生成自由エネルギーが低い A1 元素を含む第 2 の導電層を堆積する工程と、前記基板を真空中でアニール処理し、前記酸化物層を前記 A1 元素により還元することにより、前記第 1 の導電層と前記第 2 の導電層との界面に前記 A1 元素の酸化物層を形成する工程と、前記 A1 元素の酸化物層の形成で酸化されずに残った前記第 2 の導電層を除去する工程と、前記第 2 の導電層の除去後に、前記絶縁層の溝或

50

いは孔内に C u 配線を埋め込み形成する工程とを含むことを特徴とする。

#### 【0012】

(2) 本発明(請求項4)の半導体装置の製造方法は、半導体基板上に形成された所定元素の酸化物を含む絶縁層に溝或いは孔を形成する工程と、前記溝或いは孔が形成された絶縁層の表面に、前記所定元素より酸化物の生成自由エネルギーが低いA1元素を含む第1の導電層を形成する工程と、前記基板を真空中でアニール処理し、前記所定元素の酸化物を前記A1元素により還元することにより、前記絶縁層と第1の導電層との界面に該A1元素の酸化物層を形成する工程と、前記A1元素の酸化物層の形成で酸化されずに残った前記第1の導電層を除去する工程と、前記第1の導電層の除去後に、前記絶縁層の溝或いは孔内に C u 配線を埋め込み形成する工程と、を含むことを特徴とする。10

(3) 本発明(請求項5)の半導体装置の製造方法は、半導体基板上に形成された所定元素の酸化物を含む絶縁層に溝或いは孔を形成する工程と、前記溝或いは孔が形成された絶縁層の表面に、前記所定元素より酸化物の生成自由エネルギーが低いA1元素を含む第1の導電層を形成する工程と、前記基板を真空中でアニール処理し、前記所定元素の酸化物を前記A1元素により還元することにより、前記絶縁層と第1の導電層との界面に該A1元素の酸化物層を形成する工程と、前記A1元素の酸化物層の形成で酸化されずに残った前記第1の導電層を除去する工程と、前記第1の導電層の除去後に、前記A1元素より酸化物の生成自由エネルギーが高い金属元素を含む第2の導電層を堆積する工程と、前記第2の導電層を堆積した後に、前記絶縁層の溝或いは孔内に C u 配線を埋め込み形成する工程とを含むことを特徴とする。20

#### 【0014】

##### [作用]

本発明は、上記構成によって以下の作用・効果を有する。

#### 【0015】

請求項1によれば、配線のバリアメタル層として用いられる第1の導電層の表面に、配線材に対するバリア性に優れた薄い第2の金属元素の酸化物層(例えばA1酸化物)を均一な厚みで選択的に形成することができる。抵抗が高い酸化物層は、薄く形成されるので、配線の電気抵抗の増加を抑制することができる。

#### 【0016】

また、請求項5によれば、酸素を含む絶縁層の表面に、配線材に対するバリア性に優れた薄い金属元素の酸化物層を均一な厚みで選択的に形成することができる。下層の配線に接続する絶縁層の溝或いは孔の表面には、金属酸化物の酸化物層が形成されないので、配線抵抗の増大の懼がない。30

#### 【0017】

##### 【発明の実施の形態】

先ず、本発明の実施の形態を説明する前に、本発明の背景について説明する。

#### 【0018】

前述したように、TiN層の表面を酸化雰囲気にさらすことにより、A1に対する拡散バリア性が向上することが知られている。これは、TiNの表面と結晶粒界に沿って、バリア性の高いTi酸窒化物層が形成されるためと考えられていた。しかしながら、上記のようなTiN層の表面酸化処理をCuに対して行った場合、A1に対する拡散バリア性のようないきめ細かいバリア性の向上は認められない。40

#### 【0019】

そこで、本発明者等は、表面酸化処理によりバリア性の向上が認められたA1とTiNとの界面の詳細な解析を行った。先ず、シリコン酸化膜上にTiN膜を化成スパッタ法により膜厚20nm堆積した後、酸素を微量含むN<sub>2</sub>ガスを流しながらアニールを行い、TiN膜表面の酸化処理を行って、Ti酸化膜を形成した。その後、Ti酸化膜上にA1膜をスパッタリング法により膜厚20nm堆積し、スパッタリング装置内の超高真空中で、A1膜に島状の凝集が生じるまでアニールを行った。凝集したA1のTi酸化物に対する接触角を断面SEMで測定した結果、Ti酸化物上のA1の接触角とは大きく異なり、A1

酸化物上の接触角に近いことが明らかになった。

**【0020】**

次に、AlとTiN界面での結合状態を調べるため、X線電子分光法(X-ray photoelectron spectroscopy: XPS)による深さ方向の分析を行った結果、AlとTiNとの界面付近にAl-O結合のピークが認められた。

**【0021】**

以上のことから、本発明者等は、TiNの表面酸化処理によるAlに対するバリア性の向上は、単にTiN表面にTi酸化物が形成されるためではなく、その後のAlとの界面反応によりTi酸化物の還元が起こって、界面にバリア性の高いAl酸化物が生成されるためであると考えるに至った。

10

**【0022】**

本発明者等は、各種元素の酸化物について、以下のようなCuに対するバリア性の評価を試みた。Si基板上に、基板へのCu拡散を防止するため、LPCVD法によりシリコン窒化膜を厚さ200nm堆積した後、LPCVD法によりアモルファスシリコン膜を膜厚100nm堆積した。引き続き、化成スパッタ法によりAl酸化物膜、Ta酸化物膜、Nb酸化物膜、W酸化物膜、Ti酸化物膜或いはSi酸化物膜を膜厚5nmで堆積した後、Cu膜を厚さ200nm堆積した。このようにして作成した試料を、真空中において450度4時間、16時間のアニールを行い、Cu膜から酸化物膜を通してアモルファスシリコン膜に拡散したCuにより生成されたCuシリサイドの生成率(シリサイド化率)により、酸化物膜のバリア性の評価を行った。シリサイド化率の評価結果を表1に示す。

20

**【0023】**

**【表1】**

|      | Al酸化物 | Ta酸化物 | Nb酸化物 | W酸化物 | Ti酸化物 | Si酸化物 |

|------|-------|-------|-------|------|-------|-------|

| 4時間  | ○     | △     | △     | △    | △     | ×     |

| 16時間 | ○     | ×     | ×     | ×    | ×     | ×     |

×：シリサイド生成多い

△：シリサイド生成少ない

○：シリサイド生成無し

30

**【0024】**

表1に示すように、Ta酸化物、Nb酸化物、W酸化物又はTi酸化物は、シリコン酸化膜に比べてCuに対するバリア性が高いが、Al酸化物は、それらの酸化物よりも更に優れたバリア性を持つことが確認された。

**【0025】**

また、Al酸化物は、Cuに対する密着性についても優れており、その後のプロセスで溝や孔にCu埋め込み配線を形成する際に、CMPによる膜剥がれが生じる懼れが無かった。

40

**【0026】**

次に、本発明の実施の形態を以下に図面を参照して説明する。

**【0027】**

[第1実施形態]

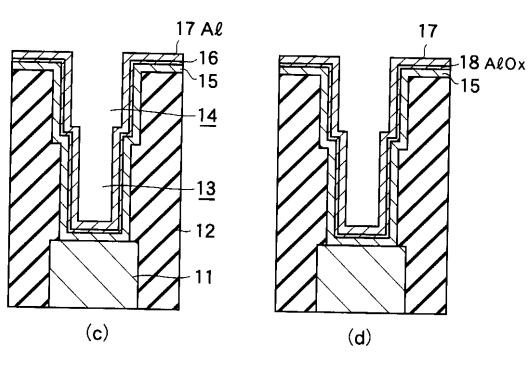

図1、図2は、本発明の第1実施形態に係わる半導体装置の製造工程を示す工程断面図である。

先ず、図1(a)に示すように、配線11を覆うように形成された絶縁層12に、配線11に接続するヴィアホール13、及びこのヴィアホール13に接続する配線溝14を形成する。なお、図1、図2において、配線11及び絶縁層12は、素子が形成された半導体

50

基板上に形成されているが、素子及び半導体基板の図示を省略している。そして、全面に膜厚 10 nm の TiN 層 15 をロング・スロー・スパッタ法により堆積する。このとき、TiN 層 15 が、ヴィアホール 13 及び配線溝 14 の内壁及び底面を被覆するような条件で形成する。

#### 【0028】

次いで、図 1 (b) に示すように、微量の酸素を含む窒素雰囲気中でアニール (stufing 处理) を 450 °C で 30 分行い、TiN 層 15 の表面に Ti 酸化物 ( $TiO_x$ ) 16 を形成する。

#### 【0029】

次いで、図 1 (c) に示すように、ロング・スロー・スパッタ法により、Ti (第 1 の金属元素) より酸化物の生成自由エネルギーが低い Al (第 2 の金属元素) を堆積することにより、Ti 酸化物 16 の表面に膜厚 100 nm の Al 层 17 を形成する。

#### 【0030】

次いで、図 1 (d) に示すように、450 °C で 15 分間真空アニールを行って、Al 层 17 と Ti 酸化物 16 とを反応させて、Al 层 17 と Ti 酸化物 16 との界面に Al 酸化物層 ( $AlO_x$ ) 18 を厚さ 1 ~ 3 nm 形成する。前述したように Al は Ti より酸化物の生成自由エネルギーが低いので、真空アニールによって Ti 酸化物が Al により還元されて Al 酸化物が生成される。Al 酸化物層 18 は、前述したように優れたバリア性を有するので、後に形成される Cu 配線の拡散を抑制することができる。

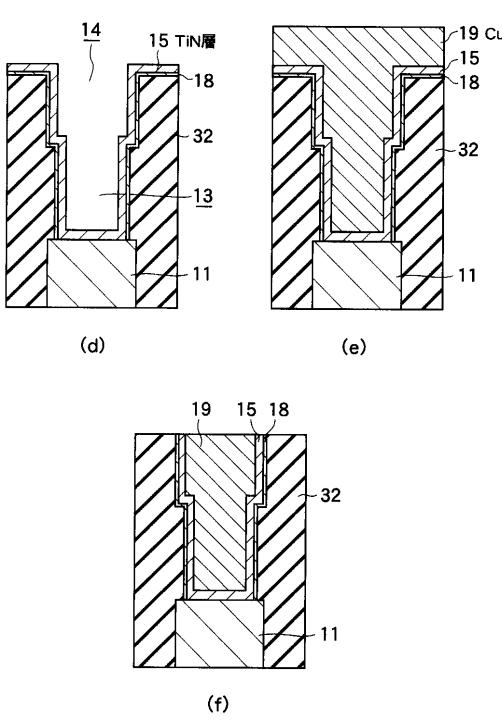

#### 【0031】

次いで、図 2 (e) に示すように、反応せずに残った Al 层 17 を、リン酸を主成分とするウェット・エッチング液により除去する。なお、Al 酸化物層 18 の抵抗が高いので、配線 11 と後に形成される Cu 配線との接触抵抗が高くなるので、異方性エッチング等を行うことによって、ヴィアホール 13 の底面の Al 酸化物層 18 を選択的に除去しても良い。なお、ヴィアホール 13 底面の Al 酸化物層 18 の除去と同時に、ヴィアホール 13 底面の TiN 層 15 を除去しても良い。

#### 【0032】

次いで、図 2 (f) に示すように、Cu をロング・スロー・スパッタ法により堆積した後、450 °C で 15 分アニールを行ってリフローし、配線溝 14 及びヴィアホール 13 を Cu 19 で埋め込む。

そして、図 2 (g) に示すように、CMP により絶縁層 12 上の余分な Cu 19、TiN 层 15 を除去し、Cu ダマシン配線 19 を形成する。この CMP 工程において、Cu 19 と TiN 层 15 との間には、Cu に対する密着性が優れた Al 酸化物層 18 が形成されているので、膜剥がれが生じず、不良の発生を抑制することができる。

#### 【0033】

本方法によれば、Cu ダマシン配線 19 と TiN 层 15 との界面に緻密で薄い AlO<sub>x</sub> を形成することができるので、TiN 层 15 の Cu に対するバリア性が向上する。また、Cu と AlO<sub>x</sub> は密着強度が高いので、CMP を良好に行うことができ、膜剥がれによる不良の発生を抑制することができる。

#### 【0034】

なお、Cu ダマシン配線 19 と配線 11 との界面には抵抗の高い Al 酸化物層 18 が形成されるが、厚さを薄く形成できるのでトンネル効果により電流が流れ、電気抵抗の増加を抑制できる。なお、電気抵抗の増加が問題となる場合は、RIE などの異方性エッチングによりヴィアホール底の Al 酸化物を選択的に除去すればよい。

#### 【0035】

##### [第 2 実施形態]

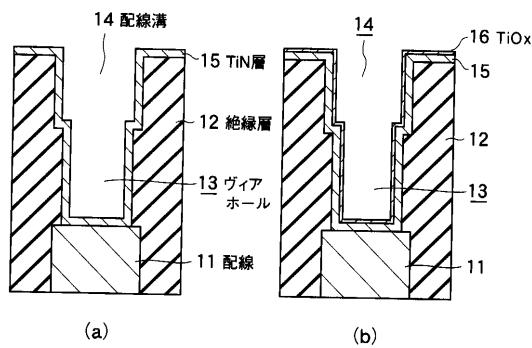

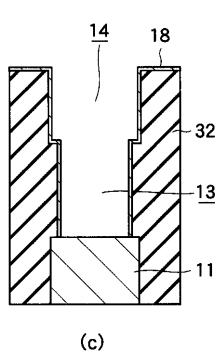

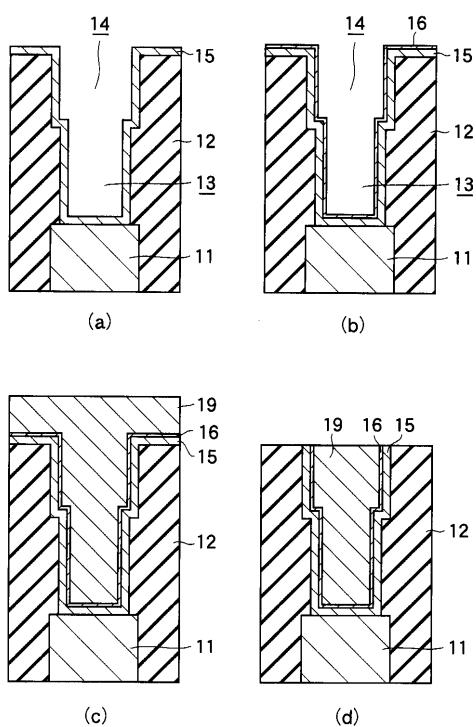

図 3, 図 4 は、本発明の第 2 実施形態に係わる半導体装置の製造方法を示す工程断面図である。

先ず、図 3 (a) に示すように、配線 11 を覆うように形成された SiO<sub>x</sub> 絶縁層 (所定元素の酸化物) 32 に、配線 11 に接続するヴィアホール 13、及びこのヴィアホール 1

10

20

30

40

50

3に接続する配線溝14を形成する。なお、図3、図4において、配線11及び $\text{SiO}_x$ 絶縁層32は、素子が形成された半導体基板上に形成されているが、素子及び半導体基板の図示を省略している。そして、全面に膜厚10nmのA1層17をロング・スロー・スペッタ法により堆積する。このとき、A1層17が、ヴィアホール13及び配線溝14の内壁及び底面を被覆するような条件で形成する。

#### 【0036】

次いで、図3(b)に示すように、真空アニールを450度15分行い、A1層17と $\text{SiO}_x$ 絶縁層32を反応させ、A1層17と $\text{SiO}_x$ 絶縁層32との界面に厚さ1~3nmのA1酸化物( $\text{AlO}_x$ )層18を形成する。A1(金属元素)はSi(所定元素)より酸化物の生成自由エネルギーが低いので、真空アニールにより、 $\text{SiO}_x$ がA1によって還元され、A1酸化物が生成される。

10

#### 【0037】

次いで、図3(c)に示すように、反応せずにA1酸化物層18上に残存するA1層17を、リン酸を主成分とするウェット・エッチング液により選択的に除去する。

次いで、図4(d)に示すように、TiN層15をロング・スロー・スペッタ法により膜厚10nm堆積する。Ti(第2の金属元素)はA1(金属元素)より酸化物の生成自由エネルギーが高いので、後に加熱されてもA1酸化物層18を還元することができない。

#### 【0038】

そして、図4(e)に示すように、大気中に暴露すること無く、Cuをロング・スロー・スペッタ法により連続して堆積した後、450度15分アニールによりリフローして、配線溝14とヴィアホール13内をCu19で埋め込む。

20

#### 【0039】

次に、図4(f)に示すように、CMPにより $\text{SiO}_x$ 絶縁層32上の余分なCu19、TiN層15を除去し、Cuダマシン配線19を形成する。

#### 【0040】

本方法によれば、 $\text{SiO}_x$ 絶縁層32とTiN層15との界面に薄いA1酸化物層18を形成されるので、TiN層15のCuダマシン配線19に対するバリア性が向上する。また、TiN層15とCu19とを連続して堆積するので密着強度が低下することなく、CMPを良好に行うことができる。Cuダマシン配線19と配線11との接続する界面にはA1酸化物が形成されないので、電気抵抗の増大の懸念がない。

30

#### 【0041】

なお、本発明は、上記実施形態に限定されるものではない。例えば、第1実施形態において、第1の金属元素及び第2の金属元素としてそれぞれA1及びTiを用いていたが、これに限るものではなく、二つの金属元素の酸化物の生成自由エネルギーが異なり、且つ第2の金属元素の酸化物の生成自由エネルギーが第1の金属元素より低い関係にあるならば任意の金属元素を用いることができる。

#### 【0042】

また、第2実施形態において、金属元素及び所定元素としてそれぞれA1及びSiを用いていたが、これに限るものではなく、二つの元素の酸化物の生成自由エネルギーが異なり、且つ金属元素の酸化物の生成自由エネルギーが所定元素より低い関係にあるならば任意の金属元素を用いることができる。

40

#### 【0043】

上記実施形態では、TiN層15の堆積方法にロング・スロー・スペッタ法を用いたが、他の堆積方法、例えばプリカーサにTDMATを用いたMOCVDのようなCVDを用いてもよい。また、Ti酸化物16の形成方法として、微量酸素を含む窒素アニール(sulfating処理)を用いたが、他の酸化処理、たとえば大気中暴露、酸素プラズマ処理を用いてもよい。また、TiN以外に、W、Ta或いはNbを少なくとも含む導電材料、例えばW、Ta或いはNbの窒化物を用いることができる。

#### 【0044】

A1層17を堆積したが、A1層の代りに、A1-Si、AlCuなどのA1合金層を堆

50

積してもよい。本実施形態では、A1層17の堆積方法としてロング・スロー・スパッタ法を用いたが、他の堆積方法、たとえばCVDを用いてもよい。また、還元反応を促進するためにA1層の堆積後にアニールを行ったが、堆積時に加熱してもよいし、A1層の堆積時に反応が十分進行する場合は特に加熱、アニールの必要はない。また、反応せずに残ったA1層の除去を行ったが、反応により残ったA1がCuと反応して配線抵抗を増加させるなどの問題が生じなければ、必ずしも除去する必要はない。

#### 【0045】

また、Cuの堆積方法としてロング・スロー・スパッタ法を用いたが、他の堆積方法、たとえばCVDまたは電解メッキまたは無電解メッキまたはそれらの成膜手法を組み合わせを用いてもよく、埋め込みを促進する必要がない場合は、加熱、アニールは不要である。

また、Cu以外の配線材を用いることができる。

10

その他、本発明は、その要旨を逸脱しない範囲で、種々変形して実施することが可能である。

#### 【0046】

##### 【発明の効果】

以上説明したように本発明によれば、配線のバリアメタル層として用いられる第1の導電層の表面に、配線材に対するバリア性に優れると共に配線材との密着性に優れる薄い酸化物層を均一な厚みで選択的に形成することができる。抵抗が高い酸化物層は、薄く形成されるので、配線の電気抵抗の増加を抑制することができる。

#### 【0047】

20

また、酸素を含む絶縁層の表面に、配線材に対するバリア性に優れる薄い金属元素の酸化物層を均一な厚みで選択的に形成することができる。下層の配線に接続する絶縁層の溝あるいは孔の表面には、金属酸化物の酸化物層が形成されないので、配線抵抗の増大の恐れがない。

##### 【図面の簡単な説明】

【図1】第1実施形態に係わる半導体装置の製造方法を示す工程断面図。

【図2】第1実施形態に係わる半導体装置の製造方法を示す工程断面図。

【図3】第2実施形態に係わる半導体装置の製造方法を示す工程断面図。

【図4】第2実施形態に係わる半導体装置の製造方法を示す工程断面図。

【図5】従来の半導体装置の製造方法を示す工程断面図。

30

##### 【符号の説明】

1 1 ... 配線

1 2 ... 絶縁層

1 3 ... ヴィアホール

1 4 ... 配線溝

1 5 ... TiN層

1 6 ... Ti酸化物

1 7 ... A1層

1 8 ... A1酸化物層

1 9 ... ダマシン配線

40

【図1】

【図2】

【図3】

【図4】

【図5】

---

フロントページの続き

(72)発明者 川ノ上 孝

神奈川県横浜市磯子区新杉田町 8 番地 株式会社東芝横浜事業所内

(72)発明者 松田 哲朗

神奈川県横浜市磯子区新杉田町 8 番地 株式会社東芝横浜事業所内

(72)発明者 金子 尚史

神奈川県横浜市磯子区新杉田町 8 番地 株式会社東芝横浜事業所内

(72)発明者 飯島 匠

神奈川県横浜市磯子区新杉田町 8 番地 株式会社東芝横浜事業所内

審査官 小野田 誠

(56)参考文献 特開平09-022907 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/3205

H01L 23/52