(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-31439

(P2004-31439A)

(43) 公開日 平成16年1月29日(2004.1.29)

(51) Int.Cl.<sup>7</sup>

H01L 21/768

H01L 21/82

F 1

H01L 21/90

H01L 21/82

テーマコード(参考)

5 F 0 3 3

5 F 0 6 4

審査請求 未請求 請求項の数 32 O L (全 35 頁)

(21) 出願番号

特願2002-181974 (P2002-181974)

(22) 出願日

平成14年6月21日 (2002. 6. 21)

(71) 出願人

503121103

株式会社ルネサステクノロジ

東京都千代田区丸の内二丁目4番1号

(74) 代理人

100080001

弁理士 筒井 大和

(72) 発明者

藤井 貴子

東京都小平市上水本町五丁目20番1号

株式会社日立製作所半導体グループ内

(72) 発明者

村上 英一

東京都小平市上水本町五丁目20番1号

株式会社日立製作所半導体グループ内

(72) 発明者

柳沢 一正

東京都小平市上水本町五丁目20番1号

株式会社日立製作所半導体グループ内

最終頁に続く

(54) 【発明の名称】半導体集積回路装置およびその製造方法

## (57) 【要約】

【課題】複数層の埋め込み配線を有する半導体集積回路装置において、埋め込み配線と底部にて接続するプラグとその埋め込み配線との界面でのストレスマイグレーションによる導通不良を防ぐ。

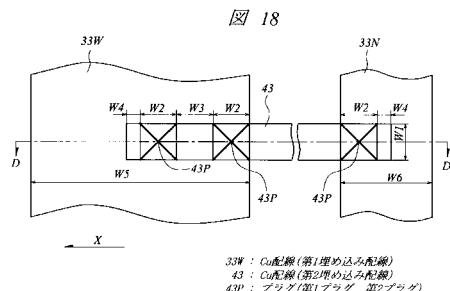

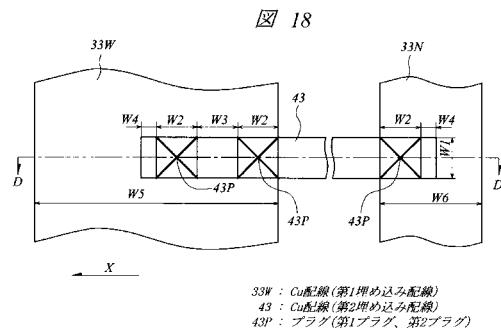

【解決手段】たとえば、Cu配線33Wの幅が約0.9  $\mu\text{m}$ 以上かつ約1.44  $\mu\text{m}$ 未満であり、Cu配線43の幅およびプラグ43Pの径が約0.18  $\mu\text{m}$ である場合において、Cu配線33W上にてCu配線33WとCu配線43とを電気的に接続するプラグ43Pを2個以上配置する。

【選択図】 図18

33W : Cu配線(第1埋め込み配線)

43 : Cu配線(第2埋め込み配線)

43P : プラグ(第1プラグ、第2プラグ)

**【特許請求の範囲】****【請求項 1】**

第1絶縁膜に形成された第1配線溝の内部に第1埋め込み配線が形成され、

前記第1絶縁膜の上層に第2絶縁膜が形成され、

前記第2絶縁膜の上層に第3絶縁膜が形成され、

前記第3絶縁膜に形成された第2配線溝の内部に第2埋め込み配線が形成され、

前記第2絶縁膜に形成された第1孔部の内部に前記第1埋め込み配線と前記第2埋め込み配線とを電気的に接続する第1プラグが形成された半導体集積回路装置であって、

前記第1プラグと前記第1埋め込み配線とが接続する第1位置は、前記第1位置から前記第1埋め込み配線の幅方向における両端部までの距離が等しくならないように配置されていることを特徴とする半導体集積回路装置。 10

**【請求項 2】**

第1絶縁膜に形成された第1配線溝の内部に第1埋め込み配線が形成され、

前記第1絶縁膜の上層に第2絶縁膜が形成され、

前記第2絶縁膜の上層に第3絶縁膜が形成され、

前記第3絶縁膜に形成された第2配線溝の内部に第2埋め込み配線が形成され、

前記第2絶縁膜に形成された第1孔部の内部に前記第1埋め込み配線と前記第2埋め込み配線とを電気的に接続する第1プラグが形成された半導体集積回路装置であって、

前記第2配線の幅は前記第1配線の幅より小さく、

前記第1プラグと前記第1埋め込み配線とが接続する第1位置は、前記第1位置から前記第1埋め込み配線の幅方向における両端部までの距離が等しくならないように配置されていることを特徴とする半導体集積回路装置。 20

**【請求項 3】**

第1絶縁膜に形成された第1配線溝および第3配線溝の内部にそれぞれ第1埋め込み配線および前記第1埋め込み配線より幅の小さい第3埋め込み配線が形成され、

前記第1絶縁膜の上層に第2絶縁膜が形成され、

前記第2絶縁膜の上層に第3絶縁膜が形成され、

前記第3絶縁膜に形成された第2配線溝の内部に前記第1埋め込み配線より幅の小さい第2埋め込み配線が形成され、

前記第2絶縁膜に形成された第1孔部および第2孔部の内部に、それぞれ前記第1埋め込み配線と前記第2埋め込み配線とを電気的に接続する第1プラグおよび前記第3埋め込み配線と前記第2埋め込み配線とを電気的に接続する第2プラグが形成された半導体集積回路装置であって、

前記第1プラグの径は、前記第2プラグの径より大きいことを特徴とする半導体集積回路装置。 30

**【請求項 4】**

第1絶縁膜に形成された第1配線溝の内部に第1埋め込み配線が形成され、

前記第1絶縁膜の上層に第2絶縁膜が形成され、

前記第2絶縁膜の上層に第3絶縁膜が形成され、

前記第3絶縁膜に形成された第2配線溝の内部に第2埋め込み配線が形成され、

前記第2絶縁膜に形成された複数の第1孔部の内部に前記第1埋め込み配線と前記第2埋め込み配線とを電気的に接続する複数の第1プラグが形成されていることを特徴とする半導体集積回路装置。 40

**【請求項 5】**

第1絶縁膜に形成された第1配線溝の内部に第1埋め込み配線が形成され、

前記第1絶縁膜の上層に第2絶縁膜が形成され、

前記第2絶縁膜の上層に第3絶縁膜が形成され、

前記第3絶縁膜に形成された第2配線溝の内部に第2埋め込み配線が形成され、

前記第2絶縁膜に形成された複数の第1孔部の内部に前記第1埋め込み配線と前記第2埋め込み配線とを電気的に接続する複数の第1プラグが形成された半導体集積回路装置であ 50

つて、

前記第2配線の幅は前記第1配線の幅より小さいことを特徴とする半導体集積回路装置。

【請求項6】

第1絶縁膜に形成された第1配線溝の内部に第1埋め込み配線が形成され、

前記第1絶縁膜の上層に第2絶縁膜が形成され、

前記第2絶縁膜の上層に第3絶縁膜が形成され、

前記第3絶縁膜に形成された第2配線溝の内部に第2埋め込み配線が形成され、

前記第2絶縁膜に形成された複数の第1孔部の内部に前記第1埋め込み配線と前記第2埋め込み配線とを電気的に接続する複数の第1プラグが形成された半導体集積回路装置であつて、

前記第1プラグと前記第1埋め込み配線とが接続する第1位置は、前記第1位置から前記第1埋め込み配線の幅方向における両端部までの距離が等しくならないように配置されていることを特徴とする半導体集積回路装置。

【請求項7】

半導体基板上に形成されたMISFETを有し、

前記半導体基板上に第1絶縁膜が形成され、

前記MISFETのゲート電極より上層の前記第1絶縁膜に第1配線溝が形成され、

前記第1配線溝の内部に前記ゲート電極と電気的に接続する第1埋め込み配線が形成され、

、

前記第1絶縁膜の上層に第2絶縁膜が形成され、

前記第2絶縁膜の上層に第3絶縁膜が形成され、

前記第3絶縁膜に形成された第2配線溝の内部に第2埋め込み配線が形成され、

前記第2絶縁膜に形成された複数の第1孔部の内部に前記第1埋め込み配線と前記第2埋め込み配線とを電気的に接続する複数の第1プラグが形成されている半導体集積回路装置。

【請求項8】

請求項1～3のいずれか1項に記載の半導体集積回路装置であつて、平面において前記第1プラグの端部は前記第1埋め込み配線の幅方向における端部と同位置に配置されていることを特徴とする半導体集積回路装置。

【請求項9】

請求項1～3のいずれか1項に記載の半導体集積回路装置であつて、前記第1プラグの径は前記第2埋め込み配線の幅と等しいことを特徴とする半導体集積回路装置。

【請求項10】

請求項4～7のいずれか1項に記載の半導体集積回路装置であつて、複数の前記第1プラグのうち少なくとも1個はその端部が前記第1埋め込み配線の幅方向における端部と同位置に配置されていることを特徴とする半導体集積回路装置。

【請求項11】

請求項4～7のいずれか1項に記載の半導体集積回路装置であつて、複数の前記第1プラグはそれぞれ等間隔で配置されていることを特徴とする半導体集積回路装置。

【請求項12】

請求項4～7のいずれか1項に記載の半導体集積回路装置であつて、複数の前記第1プラグはそれぞれ前記第1プラグの径と等しい間隔で配置されていることを特徴とする半導体集積回路装置。

【請求項13】

請求項1、2、4～7のいずれか1項に記載の半導体集積回路装置であつて、前記第1絶縁膜に形成された第3配線溝の内部に第3埋め込み配線が形成され、前記第2絶縁膜に形成された第2孔部の内部に前記第3埋め込み配線と前記第2埋め込み配線とを電気的に接続する第2プラグが形成され、前記第1プラグの径は前記第2プラグの径より大きいことを特徴とする半導体集積回路装置。

【請求項14】

10

20

30

40

50

請求項 1 ~ 7 のいずれか 1 項に記載の半導体集積回路装置であって、前記第 2 埋め込み配線の延在する方向における前記第 1 プラグの径は、前記第 1 埋め込み配線の延在する方向における前記第 1 プラグの径より 2 倍以上大きいことを特徴とする半導体集積回路装置。

【請求項 15】

請求項 1 ~ 7 のいずれか 1 項に記載の半導体集積回路装置であって、平面において、前記第 1 埋め込み配線の幅方向における中心は第 1 配線格子線上に配置され、前記第 2 埋め込み配線の幅方向における中心は第 2 配線格子線上に配置され、前記第 1 プラグの中心は前記第 1 プラグの形成時における形成位置合わせ余裕のための最小限の距離以上前記第 1 配線格子線から離間して配置されていることを特徴とする半導体集積回路装置。

【請求項 16】

請求項 1 ~ 7 のいずれか 1 項に記載の半導体集積回路装置であって、前記第 1 埋め込み配線は銅を主成分とする導電性膜から形成されていることを特徴とする半導体集積回路装置。

【請求項 17】

- ( a ) 半導体基板上に第 1 絶縁膜を形成する工程、

- ( b ) 前記第 1 絶縁膜に第 1 配線溝を形成する工程、

- ( c ) 前記第 1 配線溝に第 1 導電性膜を埋め込んで第 1 埋め込み配線を形成する工程、

- ( d ) 前記第 1 絶縁膜および前記第 1 埋め込み配線に第 2 絶縁膜を形成する工程、

- ( e ) 前記第 2 絶縁膜に前記第 1 埋め込み配線に達する第 1 孔部を形成する工程、

- ( f ) 前記第 1 孔部に第 2 導電性膜を埋め込んで前記第 1 埋め込み配線と第 1 位置で接続する第 1 プラグを形成する工程、

- ( g ) 前記第 2 絶縁膜および前記第 1 プラグ上に第 3 絶縁膜を形成する工程、

- ( h ) 前記第 3 絶縁膜に前記第 1 プラグに達する第 2 配線溝を形成する工程、

- ( i ) 前記第 2 配線溝に第 3 導電性膜を埋め込んで前記第 1 プラグと接続する第 2 埋め込み配線を形成する工程、

を含み、前記第 1 位置は前記第 1 位置から前記第 1 埋め込み配線の幅方向における両端部までの距離が等しくならないように配置することを特徴とする半導体集積回路装置の製造方法。

【請求項 18】

- ( a ) 半導体基板上に第 1 絶縁膜を形成する工程、

- ( b ) 前記第 1 絶縁膜に第 1 配線溝を形成する工程、

- ( c ) 前記第 1 配線溝に第 1 導電性膜を埋め込んで第 1 埋め込み配線を形成する工程、

- ( d ) 前記第 1 絶縁膜および前記第 1 埋め込み配線上に第 2 絶縁膜および第 3 絶縁膜を順次形成する工程、

- ( e ) 前記第 3 絶縁膜および前記第 2 絶縁膜をエッティングして、第 2 配線溝と前記第 2 配線溝の底部で開孔し前記第 1 埋め込み配線に達する第 1 孔部とを形成する工程、

- ( f ) 前記第 1 孔部および前記第 2 配線溝に第 3 導電性膜を埋め込んで、前記第 1 埋め込み配線と第 1 位置で接続する第 1 プラグと前記第 1 プラグと接続する第 2 埋め込み配線とを一体に形成する工程、

を含み、前記第 1 位置は前記第 1 位置から前記第 1 埋め込み配線の幅方向における両端部までの距離が等しくならないように配置することを特徴とする半導体集積回路装置の製造方法。

【請求項 19】

- ( a ) 半導体基板上に第 1 絶縁膜を形成する工程、

- ( b ) 前記第 1 絶縁膜に第 1 配線溝および第 3 配線溝を形成する工程、

- ( c ) 前記第 1 配線溝および前記第 3 配線溝に第 1 導電性膜を埋め込んで、それぞれ第 1 埋め込み配線および前記第 1 埋め込み配線より幅の小さい第 3 埋め込み配線を形成する工程、

- ( d ) 前記第 1 絶縁膜、前記第 1 埋め込み配線および前記第 3 埋め込み配線上に第 2 絶縁膜を形成する工程、

10

20

30

40

50

(e) 前記第2絶縁膜に前記第1埋め込み配線に達する第1孔部および前記第3埋め込み配線に達する第2孔部を形成する工程、

(f) 前記第1孔部および前記第2孔部に第2導電性膜を埋め込んで前記第1埋め込み配線と接続する第1プラグおよび前記第3埋め込み配線と接続する第2プラグを形成する工程、

(g) 前記第2絶縁膜、前記第1プラグおよび前記第2プラグ上に第3絶縁膜を形成する工程、

(h) 前記第3絶縁膜に前記第1プラグおよび前記第2プラグに達する第2配線溝を形成する工程、

(i) 前記第2配線溝に第3導電性膜を埋め込んで前記第1プラグおよび前記第2プラグと接続する第2埋め込み配線を形成する工程、 10

を含み、前記第1プラグの径は前記第2プラグの径より大きく形成することを特徴とする半導体集積回路装置の製造方法。

【請求項20】

(a) 半導体基板上に第1絶縁膜を形成する工程、

(b) 前記第1絶縁膜に第1配線溝および第3配線溝を形成する工程、

(c) 前記第1配線溝および前記第3配線溝に第1導電性膜を埋め込んで、それぞれ第1埋め込み配線および前記第1埋め込み配線より幅の小さい第3埋め込み配線を形成する工程、

(d) 前記第1絶縁膜、前記第1埋め込み配線および前記第3埋め込み配線上に第2絶縁膜をおよび第3絶縁膜を順次形成する工程、 20

(e) 前記第3絶縁膜および前記第2絶縁膜をエッチングして、第2配線溝および前記第2配線溝の底部で開孔し前記第1埋め込み配線に達する第1孔部および前記第3埋め込み配線に達する第2孔部を形成する工程、

(f) 前記第1孔部、前記第2孔部および前記第2配線溝に第3導電性膜を埋め込んで、前記第1埋め込み配線と接続する第1プラグと、前記第3埋め込み配線と接続する第2プラグと、前記第1プラグおよび前記第2プラグと接続する第2埋め込み配線とを一体に形成する工程、

を含み、前記第1プラグの径は前記第2プラグの径より大きく形成することを特徴とする半導体集積回路装置の製造方法。 30

【請求項21】

(a) 半導体基板上に第1絶縁膜を形成する工程、

(b) 前記第1絶縁膜に第1配線溝を形成する工程、

(c) 前記第1配線溝に第1導電性膜を埋め込んで第1埋め込み配線を形成する工程、

(d) 前記第1絶縁膜および前記第1埋め込み配線上に第2絶縁膜を形成する工程、

(e) 前記第2絶縁膜に前記第1埋め込み配線に達する複数の第1孔部を形成する工程、

(f) 複数の前記第1孔部に第2導電性膜を埋め込んで前記第1埋め込み配線と接続する複数の第1プラグを形成する工程、

(g) 前記第2絶縁膜および複数の前記第1プラグ上に第3絶縁膜を形成する工程、

(h) 前記第3絶縁膜に複数の前記第1プラグに達する第2配線溝を形成する工程、 40

(i) 前記第2配線溝に第3導電性膜を埋め込んで複数の前記第1プラグと接続する第2埋め込み配線を形成する工程、

を含むことを特徴とする半導体集積回路装置の製造方法。

【請求項22】

(a) 半導体基板上に第1絶縁膜を形成する工程、

(b) 前記第1絶縁膜に第1配線溝を形成する工程、

(c) 前記第1配線溝に第1導電性膜を埋め込んで第1埋め込み配線を形成する工程、

(d) 前記第1絶縁膜および前記第1埋め込み配線上に第2絶縁膜および第3絶縁膜を順次形成する工程、

(e) 前記第3絶縁膜および前記第2絶縁膜をエッチングして、第2配線溝と前記第2配 50

線溝の底部で開孔し前記第1埋め込み配線に達する複数の第1孔部とを形成する工程、

(f)複数の前記第1孔部および前記第2配線溝に第3導電性膜を埋め込んで、前記第1埋め込み配線と第1位置で接続する複数の第1プラグと複数の前記第1プラグと接続する第2埋め込み配線とを一体に形成する工程、

を含むことを特徴とする半導体集積回路装置の製造方法。

## 【請求項23】

請求項17～20のいずれか1項に記載の半導体集積回路装置の製造方法であって、平面において前記第1プラグの端部は前記第1埋め込み配線の幅方向における端部と同位置に配置することを特徴とする半導体集積回路装置の製造方法。

## 【請求項24】

請求項17～20のいずれか1項に記載の半導体集積回路装置の製造方法であって、前記第1プラグの径は前記第2埋め込み配線の幅と等しいことを特徴とする半導体集積回路装置の製造方法。

## 【請求項25】

請求項21または22に記載の半導体集積回路装置の製造方法であって、複数の前記第1プラグのうち少なくとも1個はその端部を前記第1埋め込み配線の幅方向における端部と同位置に配置することを特徴とする半導体集積回路装置の製造方法。

## 【請求項26】

請求項21または22に記載の半導体集積回路装置の製造方法であって、複数の前記第1プラグはそれぞれ等間隔で配置することを特徴とする半導体集積回路装置の製造方法。

## 【請求項27】

請求項21または22に記載の半導体集積回路装置の製造方法であって、複数の前記第1プラグはそれぞれ前記第1プラグの径と等しい間隔で配置することを特徴とする半導体集積回路装置の製造方法。

## 【請求項28】

請求項17、18、21および22のいずれか1項に記載の半導体集積回路装置の製造方法であって、前記第2埋め込み配線の延在する方向における前記第1プラグの径を前記第1埋め込み配線の延在する方向における前記第1プラグの径より2倍以上大きく形成することを特徴とする半導体集積回路装置の製造方法。

## 【請求項29】

請求項17または21に記載の半導体集積回路装置の製造方法であって、前記(b)工程は、

(b1)前記第1絶縁膜に第3配線溝を形成する工程を含み、前記(c)工程は、

(c1)前記第3配線溝に前記第1導電性膜を埋め込んで、前記第1埋め込み配線より幅の小さい第3埋め込み配線を形成する工程を含み、前記(e)工程は、(e1)前記第2絶縁膜に前記第3埋め込み配線に達する第2孔部を形成する工程を含み、前記(f)工程は、

(f1)前記第2孔部に前記第2導電性膜を埋め込んで、前記第3埋め込み配線と接続する第2プラグを形成する工程を含み、前記第2配線溝は前記第2プラグに達し、前記第1プラグの径は前記第2プラグの径より大きく形成することを特徴とする半導体集積回路装置の製造方法。

## 【請求項30】

請求項18または22に記載の半導体集積回路装置の製造方法であって、前記(b)工程は、

(b1)前記第1絶縁膜に第3配線溝を形成する工程含み、前記(c)工程は、(c1)前記第3配線溝に前記第1導電性膜を埋め込んで、前記第1埋め込み配線より幅の小さい第3埋め込み配線を形成する工程を含み、前記(e)工程は、(e1)前記第3絶縁膜および前記第2絶縁膜をエッチングして、前記第2配線溝の底部で開孔し前記第3埋め込み配線に達する第2孔部を形成する工程を含み、前記(f)工程は、

(f1)前記第2孔部および前記第2配線溝に前記第3導電性膜を埋め込んで、前記第3

10

20

30

40

50

埋め込み配線と接続する第2プラグと、前記第2プラグと接続する第2埋め込み配線とを一体に形成する工程を含み、前記第1プラグの径は前記第2プラグの径より大きく形成することを特徴とする半導体集積回路装置の製造方法。

【請求項 3 1】

請求項 1 7 ~ 2 2 のいずれか 1 項に記載の半導体集積回路装置の製造方法であって、平面において、前記第1埋め込み配線の幅方向における中心は第1配線格子線上に配置し、前記第2埋め込み配線の幅方向における中心は第2配線格子線上に配置し、前記第1プラグの中心は前記第1プラグの形成時における形成位置合わせ余裕のための最小限の距離以上前記第1配線格子線から離間して配置することを特徴とする半導体集積回路装置の製造方法。

10

【請求項 3 2】

請求項 1 7 ~ 2 2 のいずれか 1 項に記載の半導体集積回路装置の製造方法であって、前記第1導電性膜は銅を主成分とすることを特徴とする半導体集積回路装置の製造方法。

【発明の詳細な説明】

【0 0 0 1】

【発明の属する技術分野】

本発明は、半導体集積回路装置およびその製造技術に関し、特に、絶縁膜に形成した配線形成用の溝部に導電性膜を埋め込むことにより形成された配線を有する半導体集積回路装置の製造に適用して有効な技術に関するものである。

【0 0 0 2】

【従来の技術】

半導体集積回路装置の素子集積度の向上や半導体チップのサイズの縮小等に伴い、半導体集積回路装置を構成する配線の微細化および多層化が進められている。特に、多層配線構造を有するロジック系の半導体集積回路装置においては、配線遅延が半導体集積回路装置全体の信号遅延の支配的要因の 1 つとなっている。この配線を流れる信号の速度は、配線抵抗と配線容量とに比例していることから配線遅延を改善するために配線抵抗と配線容量とを低減することが重要である。

【0 0 0 3】

配線抵抗の低減に関しては、配線材料に銅系材料 (Cu (銅) または Cu 合金) を用いたダマシン (D a m a s c e n e) 法の適用が進められている。この方法は、絶縁膜に配線溝または接続孔を形成した後、半導体基板の正面に配線形成用またはプラグ形成用の導電性膜を堆積し、さらに、その配線溝または接続孔以外の領域の導電性膜を化学機械的研磨 (C M P ; C hemical M echanical P o l i s h i n g) 法によって除去することにより、配線溝内に埋め込み配線、または接続孔内にプラグを形成する方法である。この方法の場合は、特に、微細なエッティング加工が困難な銅系の導体材料からなる埋め込み配線の形成方法として適している。

30

【0 0 0 4】

また、ダマシン法の応用としてデュアルダマシン (D u a l - D a m a s c e n e) 法がある。この方法は、絶縁膜に配線形成用の溝 (以下、配線溝という) および下層配線との接続を行なうための接続孔を形成した後、半導体基板の正面に配線形成用の導電性膜を堆積し、さらに、その溝以外の領域の導電性膜を C M P によって除去することにより、配線形成用の溝内に埋め込み配線を形成し、かつ、接続孔内にプラグを形成する方法である。この方法の場合は、特に、多層配線構造を有する半導体集積回路において、工程数の削減が可能であり、配線コストの低減が可能である。

40

【0 0 0 5】

このようなダマシン法等を用いた配線形成技術については、たとえば特開平 1 0 - 1 3 5 1 5 3 号公報に記載がある。

【0 0 0 6】

また、特開 2 0 0 1 - 1 1 8 9 2 2 号公報においては、高融点金属または高融点金属窒化物をバリア導電膜とし、Cu、Cu 合金、Ag (銀) または Ag 合金を主導電層とする埋

50

め込み配線と、その埋め込み配線上に堆積された絶縁膜に形成され、埋め込み配線の上面に達する接続孔とを有する半導体装置において、その接続孔の底部は埋め込み配線の幅方向を覆う程度の大きさとし、埋め込み配線と同一の層構成の多層膜を前記接続孔に埋め込むことでプラグを形成することによって、密着性の良いプラグおよび埋め込み配線の界面にてエレクトロマイグレーション現象によって生じた空隙の拡大を阻止する技術が開示されている。

【0007】

【発明が解決しようとする課題】

本発明者らは、配線形成用の溝内に埋め込み配線を形成する技術について検討し、以下のような新たな問題点を見出した。

10

【0008】

銅系材料を用いて複数層の埋め込み配線を形成する場合には、まず下層の埋め込み配線（以降、第1埋め込み配線という）を形成した後、隣接する第1埋め込み配線間における経時絶縁破壊（TDDDB；Time Dependent Dielectric Breakdown）特性の低下を防止するために第1埋め込み配線の表面に存在する銅系材料の研磨残骸を除去した後、アンモニアプラズマを用いて表面に付着している吸着ガス、水分および有機物の除去等により表面改質し、信頼性の高い埋め込み配線を形成する。続いて、上層の埋め込み配線（以降、第2埋め込み配線という）が形成される絶縁膜へ第1埋め込み配線を形成している銅系材料が拡散して素子特性に悪影響を及ぼすのを防ぐために、たとえば銅系材料の拡散防止膜として窒化シリコン膜などのキャップ絶縁膜を第1埋め込み配線上に形成する。次いで、その窒化シリコン膜上に酸化シリコン膜などの絶縁膜を堆積し、その絶縁膜およびキャップ絶縁膜をエッチングすることによって第2埋め込み配線が形成される配線溝および第1埋め込み配線に達する接続孔を形成する。その後、その配線溝および接続孔内に銅系材料を埋め込むことによって第2埋め込み配線および第1埋め込み配線と接続するプラグを形成する。ここで、第1埋め込み配線の膜中には多くの空孔（原子の抜けた孔）が点在し、これは特にめっき膜の場合に著しく多く存在する。このような空孔の点在下において、前記第1埋め込み配線および第2埋め込み配線などが形成された半導体ウェハに対して高温放置試験（ストレスマイグレーション試験）を施すと、前記空孔は、熱による応力を緩和するようにキャップ絶縁膜の存在しない領域、すなわち前記プラグと第1埋め込み配線との界面へ移動していく（以降、この現象をストレスマイグレーションという）。これら空孔がそのプラグと第1埋め込み配線との界面に集まつて大きな空隙（ボイド）になると、プラグと第1埋め込み配線との間で導通不良となってしまう。

20

【0009】

ここで、本発明者らは、埋め込み配線形成プロセスを改善することによって埋め込み配線を形成する銅系材料内部での応力の低減、および埋め込み配線中の多くの空孔の発生の低減はある程度実現することはできたが、1箇所のプラグに対してそれに接続する第1埋め込み配線の幅が大きい場合には、ストレスマイグレーションによる導通不良が発生し得ることを新たに見出した。また、この導通不良は、特に微細化に伴いプラグが形成される接続孔の径が小さくなるに従い発生しやすくなる。埋め込み配線の膜中に形成された空孔の移動は、埋め込み配線と接続したプラグの底部を中心とした全方向から同心円状に起こっていることから、その同心円内に存在する空孔が多いほどプラグと埋め込み配線を形成する膜中における多くの空孔の成長は早くなり、導通不良を起こすまでの時間（ストレスマイグレーション寿命）も短くなると本発明者らは推測している。つまり、1箇所のプラグに対してそれに接続する第1埋め込み配線の幅が大きい場合ほど、ストレスマイグレーションによる導通不良が発生しやすいのではないかと、本発明者らは推測している。

30

【0010】

本発明の目的は、複数層の埋め込み配線を有する半導体集積回路装置において、埋め込み配線と底部にて接続するプラグとその埋め込み配線との界面でのストレスマイグレーションによる導通不良を防ぐ手段を提供することにある。

40

50

**【 0 0 1 1 】**

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

**【 0 0 1 2 】****【課題を解決するための手段】**

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

**【 0 0 1 3 】**

すなわち、本発明は、第1絶縁膜に形成された第1配線溝の内部に第1埋め込み配線が形成され、前記第1絶縁膜の上層に第2絶縁膜が形成され、前記第2絶縁膜に形成された第2配線溝の内部に第2埋め込み配線が形成され、前記第2絶縁膜に形成された第1孔部の内部に前記第1埋め込み配線と前記第2埋め込み配線とを電気的に接続する第1プラグが形成されたものであり、前記第1プラグと前記第1埋め込み配線とが接続する位置は、前記第1位置から前記第1埋め込み配線の幅方向における両端部までの距離が等しくならないように配置されているものである。10

**【 0 0 1 4 】**

また、本発明は、第1絶縁膜に形成された第1配線溝の内部に第1埋め込み配線が形成され、前記第1絶縁膜の上層に第2絶縁膜が形成され、前記第2絶縁膜に形成された第2配線溝および第3配線溝の内部にそれぞれ第2埋め込み配線および第3埋め込み配線が形成され、前記第2絶縁膜に形成された第1孔部および第2孔部の内部に、それぞれ前記第1埋め込み配線と前記第2埋め込み配線とを電気的に接続する第1プラグおよび前記第1埋め込み配線と前記第3埋め込み配線とを電気的に接続する第2プラグが形成されたものであり、前記第1プラグの径は、前記第2プラグの径より大きいものである。20

**【 0 0 1 5 】**

また、本発明は、第1絶縁膜に形成された第1配線溝の内部に第1埋め込み配線が形成され、前記第1絶縁膜の上層に第2絶縁膜が形成され、前記第2絶縁膜に形成された第2配線溝の内部に第2埋め込み配線が形成され、前記第2絶縁膜に形成された複数の第1孔部の内部に前記第1埋め込み配線と前記第2埋め込み配線とを電気的に接続する複数の第1プラグが形成されているものである。

**【 0 0 1 6 】**

また、本発明は、半導体基板上に第1絶縁膜を形成する工程と、前記第1絶縁膜に第1配線溝を形成する工程と、前記第1配線溝に第1導電性膜を埋め込んで第1埋め込み配線を形成する工程と、前記第1絶縁膜および前記第1埋め込み配線上に第2絶縁膜および第3絶縁膜を順次形成する工程と、前記第3絶縁膜および前記第2絶縁膜をエッティングして、第2配線溝と前記第2配線溝の底部で開孔し前記第1埋め込み配線に達する第1孔部とを形成する工程と、前記第1孔部および前記第2配線溝に第3導電性膜を埋め込んで、前記第1埋め込み配線と第1位置で接続する第1プラグと前記第1プラグと接続する第2埋め込み配線とを一体に形成する工程とを含み、前記第1位置は前記第1位置から前記第1埋め込み配線の幅方向における両端部までの距離が等しくならないように配置するものである。30

**【 0 0 1 7 】**

また、本発明は、半導体基板上に第1絶縁膜を形成する工程と、前記第1絶縁膜に第1配線溝を形成する工程と、前記第1配線溝に第1導電性膜を埋め込んで第1埋め込み配線を形成する工程と、前記第1絶縁膜および前記第1埋め込み配線上に第2絶縁膜および第3絶縁膜を順次形成する工程と、前記第3絶縁膜および前記第2絶縁膜をエッティングして、第2配線溝、第3配線溝、前記第2配線溝の底部で開孔し前記第1埋め込み配線に達する第1孔部および前記第3配線溝の底部で開孔し前記第1埋め込み配線に達する第2孔部を形成する工程と、前記第1孔部、前記第2孔部、前記第2配線溝および前記第3配線溝に第3導電性膜を埋め込んで、前記第1埋め込み配線と接続する第1プラグ、前記第1埋め込み配線と接続する第2プラグ、前記第1プラグと接続する第2埋め込み配線および前記40

第2プラグと接続する第3埋め込み配線を一体に形成する工程とを含み、前記第1プラグの径は前記第2プラグの径より大きく形成するものである。

【0018】

また、本発明は、以下の工程を含むものである。

- (a) 半導体基板上に第1絶縁膜を形成する工程、

- (b) 前記第1絶縁膜に第1配線溝を形成する工程、

- (c) 前記第1配線溝に第1導電性膜を埋め込んで第1埋め込み配線を形成する工程、

- (d) 前記第1絶縁膜および前記第1埋め込み配線上に第2絶縁膜および第3絶縁膜を順次形成する工程、

- (e) 前記第3絶縁膜および前記第2絶縁膜をエッチングして、第2配線溝と前記第2配線溝の底部で開孔し前記第1埋め込み配線に達する複数の第1孔部とを形成する工程、

- (f) 複数の前記第1孔部および前記第2配線溝に第3導電性膜を埋め込んで、前記第1埋め込み配線と第1位置で接続する複数の第1プラグと複数の前記第1プラグと接続する第2埋め込み配線とを一体に形成する工程。

10

【0019】

【発明の実施の形態】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一の符号を付し、その繰り返しの説明は省略する。また、以下の実施の形態の説明に用いる図面においては、各部材の構成をわかりやすくするために平面図であってもハッチングを付す場合がある。

20

【0020】

(実施の形態1)

本実施の形態1の半導体集積回路装置は、たとえばCMOS(C o m p l e m e n t a r y - M e t a l - O x i d e - S e m i c o n d u c t o r) - L S I であり、その製造方法を工程順に説明する。

20

【0021】

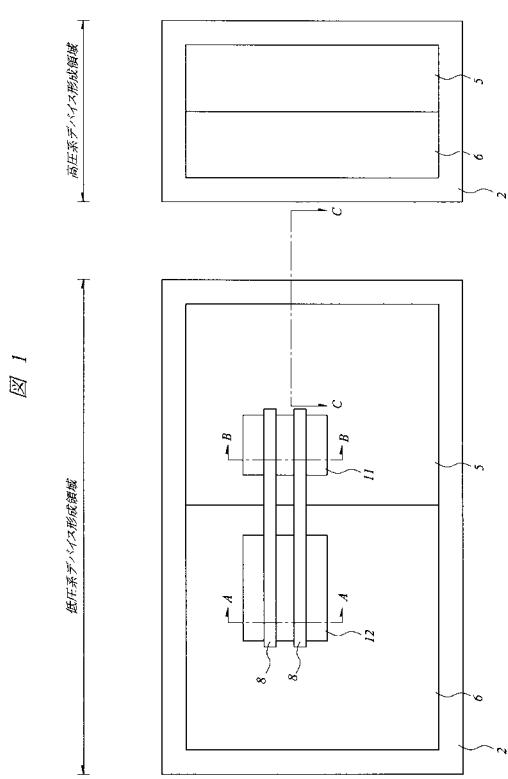

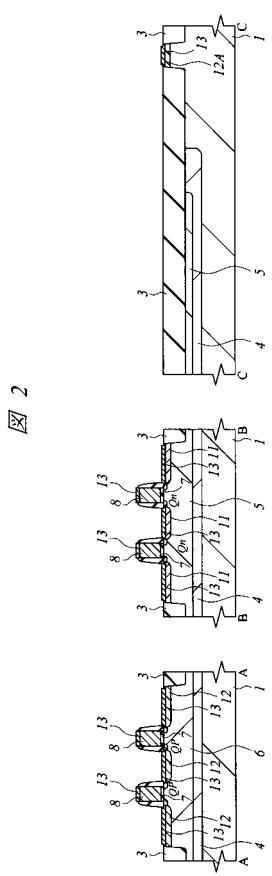

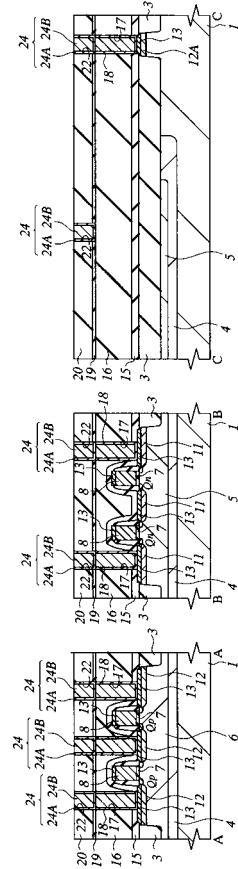

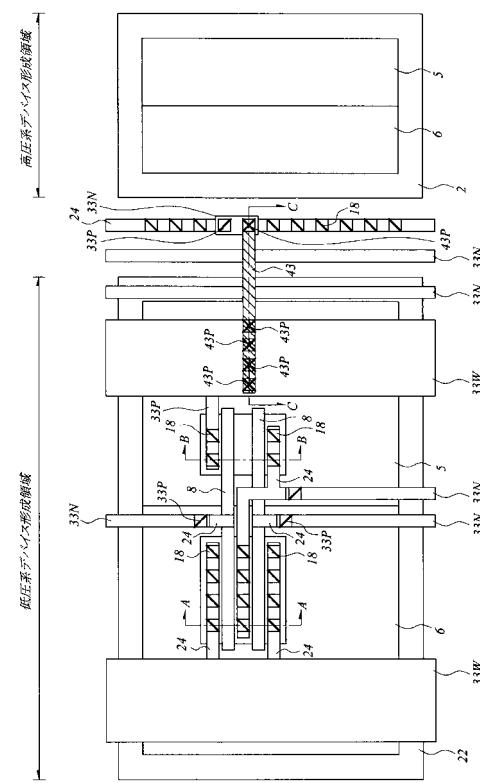

図1は本実施の形態1の半導体集積回路装置の製造方法を説明する要部平面図を示したものであり、図2は図1中に示すA - A線、B - B線およびC - C線のそれぞれに沿った断面図を示したものである。また、図1において、低圧系デバイス形成領域は相対的に高い電圧が印加される回路が形成される領域であり、高圧系デバイス形成領域は相対的に低い電圧が印加される回路が形成される領域である。

30

【0022】

まず、図1および図2に示すように、たとえば1~10cm程度の比抵抗を有するp型の単結晶シリコンからなる半導体基板1に素子分離領域3を形成する。素子分離領域3は、たとえば素子分離領域の半導体基板1をエッチングして素子分離溝を形成した後、素子分離溝の内部を含む半導体基板1上にCVD(C h e m i c a l V a p o r D e p o s i t i o n)法で絶縁膜である酸化シリコン膜を堆積し、続いて素子分離溝の外部の酸化シリコン膜を化学機械的に研磨することによって除去することにより形成される。

30

【0023】

続いて、たとえば半導体基板1にn型の導電型を有する不純物(たとえばP(リン))をイオン注入法等により導入した後、半導体基板1に熱処理を施し、そのn型不純物を拡散させることによりn型アイソレーション領域4を形成する。

40

【0024】

続いて、たとえば半導体基板1の一部にB(ホウ素)をイオン注入し、他の一部にPをイオン注入することによって、p型ウエル5およびn型ウエル6を形成した後、基板1をスチーム酸化することによって、p型ウエル5およびn型ウエル6のそれぞれの表面にMISFET(M e t a l - I n s u l a t o r - S e m i c o n d u c t o r - F i e l d - E f f e c t - T r a n s i s t o r)のゲート絶縁膜であるゲート酸化膜7を形成する。

【0025】

50

続いて、p型ウエル5およびn型ウエル6のそれぞれの上部にゲート電極8を形成する。ゲート電極8を形成するには、たとえばゲート酸化膜7の上部にCVD法で多結晶シリコン膜を堆積した後、p型ウエル5の上部の多結晶シリコン膜にPをイオン注入し、n型ウエル6の上部の多結晶シリコン膜にBをイオン注入した後、フォトレジスト膜をマスクにしたドライエッティングで多結晶シリコン膜をパターニングする。

## 【0026】

続いて、p型ウエル5にPまたはAs(ヒ素)をイオン注入することによって低不純物濃度のn<sup>-</sup>型半導体領域を形成し、n型ウエル6にBをイオン注入することによって低不純物濃度のp<sup>-</sup>型半導体領域を形成する。次いで、半導体基板1上に絶縁膜としてCVD法で窒化シリコン膜を堆積し、続いてこの窒化シリコン膜を異方的にエッティングすることによって、ゲート電極8の側壁にサイドウォールスペーサを形成した後、p型ウエル5にPまたはAsをイオン注入することによって高不純物濃度のn<sup>+</sup>型半導体領域11(ソース、ドレイン)を形成し、n型ウエル6にホウ素をイオン注入することによって高不純物濃度のp<sup>+</sup>型半導体領域12(ソース、ドレイン)およびp型引き出し層12Aを形成する。

## 【0027】

続いて、半導体基板1の表面を洗浄した後、ゲート電極8、n<sup>+</sup>型半導体領域11(ソース、ドレイン)、p<sup>+</sup>型半導体領域12(ソース、ドレイン)およびp型引き出し層12Aのそれぞれの表面にシリサイド層13を形成する。シリサイド層13は、たとえば半導体基板1上にスパッタリング法でCo(コバルト)膜を堆積し、次いで窒素ガス雰囲気中で熱処理を行って半導体基板1およびゲート電極8とCo膜とを反応させた後、未反応のCo膜をウェットエッティングで除去することにより形成される。ここまで工程で、nチャネル型MISFETQnおよびpチャネル型MISFETQpが完成する。なお、本実施の形態1では、高圧系デバイス形成領域には低圧系デバイス形成領域と同様に半導体素子および配線などが形成されるが、図1を含む平面図においては、本実施の形態1の半導体集積回路装置の要部平面構成をわかりやすくするために、高圧系デバイス形成領域におけるn型アイソレーション領域4、p型ウエル5およびn型ウエル6以外の部材の図示は省略している。

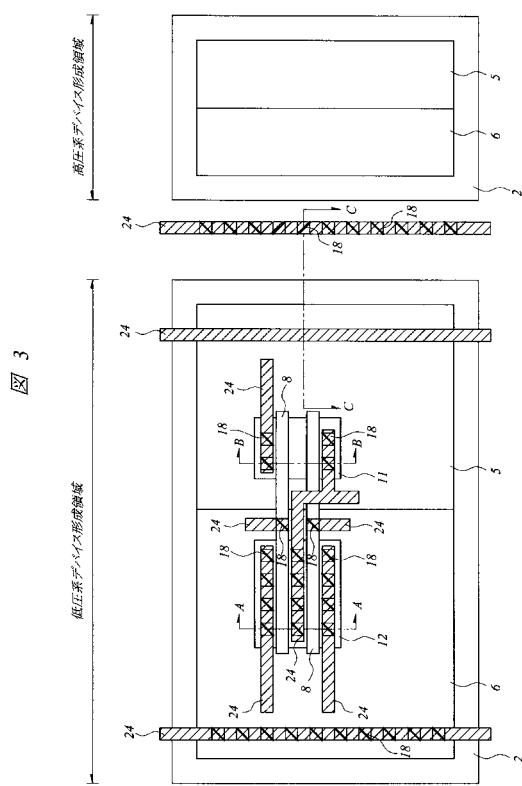

## 【0028】

次に、図3および図4に示すように、半導体基板1上にセルファーラインコンタクト用の絶縁膜として、たとえばCVD法で窒化シリコン膜15を堆積し、窒化シリコン膜15上に絶縁膜として酸化シリコン膜16を堆積する。続いてn<sup>+</sup>型半導体領域11(ソース、ドレイン)、p<sup>+</sup>型半導体領域12(ソース、ドレイン)、p型引き出し層12A、ゲート電極8A上のシリサイド層13のそれぞれの上部の酸化シリコン膜16および窒化シリコン膜15をドライエッティングしてコンタクトホール17を形成した後、コンタクトホール17の内部に導電性膜からなるプラグ18を形成する。なお、図4においては、ゲート電極8A上のシリサイド層13に達するコンタクトホール17およびその内部に形成されたプラグ18の図示は省略している。酸化シリコン膜16をエッティングするときは、下層の窒化シリコン膜15のエッティング速度を小さくするために、CF<sub>4</sub>、CHF<sub>3</sub>、C<sub>4</sub>F<sub>8</sub>などのハイドロフルオロカーボン系ガスまたはフルオロカーボン系ガスを使用する。すなわち、窒化シリコン膜15はエッティングストップ膜として機能する。また、窒化シリコン膜15をエッティングするときは、ハイドロフルオロカーボン系ガス(CHF<sub>3</sub>やCH<sub>2</sub>F<sub>2</sub>など)に酸素とArとを加えた混合ガスを使用する。プラグ18を形成するには、コンタクトホール17の内部を含む酸化シリコン膜16上にCVD法でTiN(窒化チタン)膜とW(タンゲステン)膜とを堆積し、続いて酸化シリコン膜16の上部の不要なTiN膜およびW膜を化学機械研磨(CMP)法またはエッチバック法によって除去する。なお、酸化シリコン膜16は、モノシラン(SiH<sub>4</sub>)をソースガスに用いた通常のCVD法で形成する酸化シリコン膜の他、BPSG(Boron-doped Phosphate Silicate Glass)膜、スピニ塗布法によって形成されるSOG(Spin On Glass)膜あるいはこれらの積層膜などによって構成してもよい。

10

20

30

40

50

## 【0029】

続いて、たとえば酸化シリコン膜16の上部に絶縁膜として炭化シリコン膜19を堆積した後、炭化シリコン膜19上に、たとえば炭化シリコン膜よりも誘電率の低い絶縁膜としてSiOF膜、酸化シリコン膜を順次堆積することによって層間絶縁膜20を形成する。炭化シリコン膜19は、次の工程で層間絶縁膜20に配線溝を形成する際に下層の酸化シリコン膜16がエッチングされるのを防ぐためのエッチングストップ膜として機能するもので、たとえばモノシラン(SiH<sub>4</sub>)、ジシラン(Si<sub>2</sub>H<sub>6</sub>)などのシラン系ガスと、アンモニア(NH<sub>3</sub>)または窒素との混合ガスを用いたCVD法で堆積する。SiOF膜は、たとえばSiH<sub>4</sub>とSiF<sub>4</sub>と酸素との混合ガス、またはテトラエトキシシラン((C<sub>2</sub>H<sub>5</sub>O)<sub>4</sub>Si)とSiF<sub>4</sub>と酸素との混合ガスを用いたプラズマCVD法で堆積する。SiOF膜20は、酸化シリコン(比誘電率=4.7)よりも比誘電率が小さい(約3.7)後の工程で形成されるCu配線の配線容量を低減することができる。

10

## 【0030】

続いて、たとえばフォトリソグラフィ技術によってパターニングされたフォトレジスト膜をマスクにして層間絶縁膜20、炭化シリコン膜19を順次ドライエッチングすることによって、コンタクトホール17の上部に配線溝22を形成する。次いで、そのフォトレジスト膜を除去した後、配線溝22の内部に第1層目の埋め込み配線24を形成する。埋め込み配線24は、バリアメタル膜24Aと、Cu膜あるいはW膜24Bとの積層膜で構成し、たとえば次のような方法で形成する。まず、配線溝22の内部を含む層間絶縁膜20上にバリアメタル膜24AとCu膜(またはW膜24B)とを堆積し、続いて、配線溝22の外部の不要なCu膜(またはW膜24B)とバリアメタル膜24Aとを化学機械研磨法で除去する。Cu膜を用いた場合には、Cu膜の堆積後に、たとえば非酸化性雰囲気(たとえば水素雰囲気)中で熱処理(リフロー)を施すことによって、Cu膜を配線溝22の内部に隙間なく埋め込む処理を施しても良い。

20

## 【0031】

Cu膜24Bとバリアメタル膜24Aとを研磨するには、たとえばアルミナなどの砥粒と過酸化水素水または硝酸第二鉄水溶液などの酸化剤とを主成分とし、これらを水に分散または溶解させた研磨スラリを使用する。このような化学機械研磨法による配線溝22の外部の不要なCu膜24Bおよびバリアメタル膜24Aの除去工程後にCuの研磨残骸を除去し、その後、たとえばアンモニアプラズマを用いた処理によって埋め込み配線24の表面改質する。これにより、隣接する埋め込み配線24間ににおける経時絶縁破壊特性が低下してしまうことを防ぐことができる。

30

## 【0032】

上記バリアメタル膜24Aは、たとえば埋め込み配線24中のCuが層間絶縁膜20中に拡散するのを防止する機能と共に、埋め込み配線24と層間絶縁膜20中との接着性を向上させる機能および上記Cu膜24Bをリフローする際の濡れ性を向上させる機能を有している。このような機能を持ったバリアメタル膜としては、たとえばスパッタリング法あるいはCVD法で堆積したTiN膜、WN(窒化タンゲステン)膜、TaN(窒化タンタル)、TiSiN膜、Ta(タンタル)膜などの高融点金属または高融点金属窒化物からなる膜や、これらの積層膜などが例示される。

40

## 【0033】

埋め込み配線24を構成するCu膜24Bは、スパッタリング法、CVD法、メッキ法(電解メッキ法または無電解メッキ法)のいずれかの方法で形成する。メッキ法でCu膜24Bを形成する場合は、あらかじめバリアメタル膜24Aの表面にスパッタリング法などを用いて薄いCu膜からなるシード層を形成し、次に、このシード層の表面にCu膜を成長させる。また、スパッタリング法でCu膜を形成する場合は、ロングスロースパッタリング法やコリメートスパッタリング法のような指向性の高いスパッタリング法を用いることが好ましい。Cu膜24Bは、単体のCuの他、Cuを主成分として含むCu合金で構成してもよい。

## 【0034】

50

なお、埋め込み配線 2 4 を W 膜で形成する場合には、たとえばスパッタリング法あるいは CVD 法によって形成することができ、バリアメタル膜 2 4 A としては、たとえばスパッタリング法あるいは CVD 法で形成した TiN 膜、Ti (チタン) 膜などの高融点金属膜または高融点金属窒化膜からなる膜や、これらの積層膜などを例示することができる。

【 0 0 3 5 】

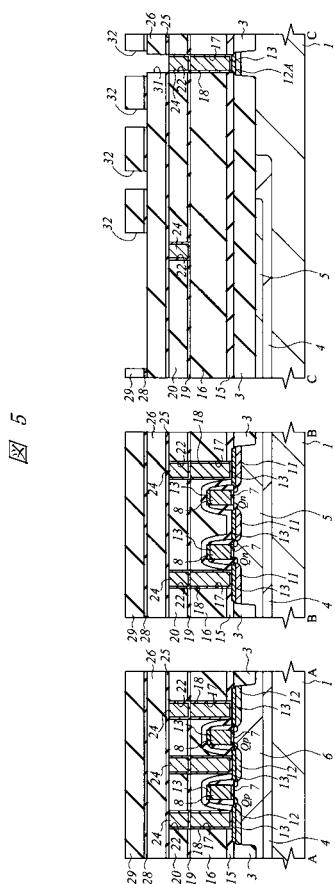

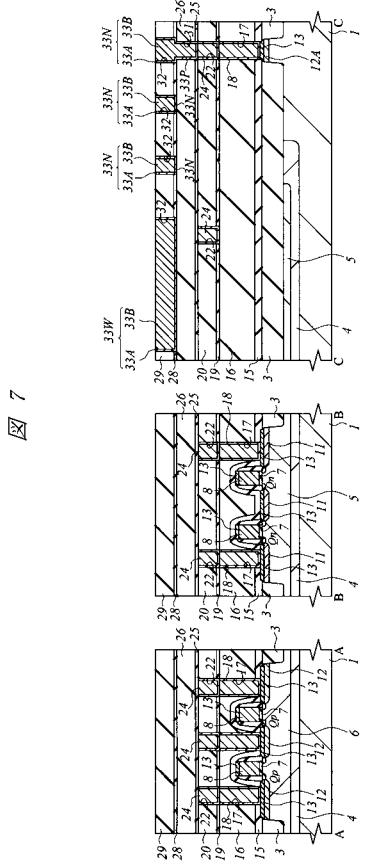

次に、図 5 に示すように、たとえば埋め込み配線 2 4 の上部に CVD 法で絶縁膜として炭化シリコン膜 2 5 を堆積した後、炭化シリコン膜 2 5 上に絶縁膜として SiOF 膜、酸化シリコン膜を CVD 法で順次堆積することによって層間絶縁膜 2 6 を形成する。炭化シリコン膜 2 5 は、埋め込み配線 2 4 中の Cu が層間絶縁膜 2 6 中に拡散するのを防止する拡散バリア層として機能するものである。続いて、たとえば層間絶縁膜 2 6 の上部に絶縁膜として CVD 法で炭化シリコン膜 (第 1 絶縁膜) 2 8 を堆積した後、炭化シリコン膜 2 8 上に絶縁膜として SiOF 膜、酸化シリコン膜を CVD 法で順次堆積することによって層間絶縁膜 (第 1 絶縁膜) 2 9 を形成する。次いで、その層間絶縁膜 2 9 上に絶縁膜として CVD 法により窒化シリコン膜 (図示は省略) を堆積する。炭化シリコン膜 2 8 および層間絶縁膜 2 9 上に堆積された窒化シリコン膜は、次の工程で配線溝 (3 2) を形成する際のエッティングストップ層として機能するものである。

【 0 0 3 6 】

続いて、たとえばフォトリソグラフィ技術によってパターニングされたフォトレジスト膜をマスクに用いたドライエッティングで配線溝形成領域における層間絶縁膜 2 9 上の窒化シリコン膜を除去する。次いで、そのフォトレジスト膜を除去した後、新たにパターニングされたフォトレジスト膜をマスクに用いたドライエッティングで配線溝形成領域の一部における層間絶縁膜 2 9 上の窒化シリコン膜、層間絶縁膜 2 9 、炭化シリコン膜 2 8 および層間絶縁膜 2 6 を除去し、炭化シリコン膜 2 5 の表面でエッティングを停止する。続いて、上記フォトレジスト膜を除去した後、層間絶縁膜 2 9 上の窒化シリコン膜をマスクに用いたドライエッティングで配線溝形成領域の層間絶縁膜 2 9 を除去する。次いで、層間絶縁膜 2 9 上の窒化シリコン膜、炭化シリコン膜 2 8 および炭化シリコン膜 2 5 をドライエッティングすることによって、埋め込み配線 2 4 の上部に接続孔 3 1 および配線溝 (第 1 配線溝、第 3 配線溝) 3 2 を形成する。

【 0 0 3 7 】

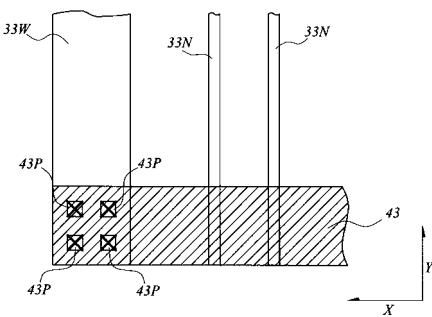

次に、図 6 および図 7 に示すように、配線溝 3 2 の内部にバリアメタル膜 3 3 A および Cu 膜 (第 1 導電性膜) 3 3 B からなる第 2 層目の埋め込み配線である Cu 配線 (第 3 埋め込み配線) 3 3 N および Cu 配線 (第 1 埋め込み配線) 3 3 W を形成する。また、この時、接続孔 3 1 内にはバリアメタル膜 3 3 A および Cu 膜 3 3 B からなるプラグ 3 3 P が Cu 配線 3 3 N 、 3 3 W と一体に形成される。第 2 層目の Cu 配線 3 3 N 、 3 3 W は、前述した第 1 層目の埋め込み配線 2 4 を形成する Cu 膜 2 4 B の形成方法 (図 4 参照) に準じて形成すればよい。本実施の形態 1 においては、Cu 配線 3 3 W は、Cu 配線 3 3 N に対して相対的に大きな配線幅で形成されるものである。また、本実施の形態 1 において、Cu 配線 3 3 N はプラグ 3 3 P 、埋め込み配線 2 4 、プラグ 1 8 および p 型引き出し層 1 2 A を介して半導体基板 1 の電位へ電気的に接続され、Cu 配線 3 3 W は、基準 (接地) 電位 (図示は省略) へ電気的に接続される。

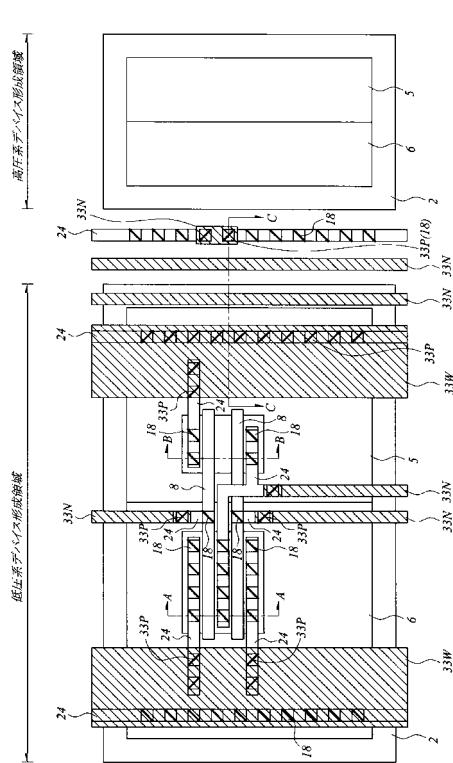

【 0 0 3 8 】

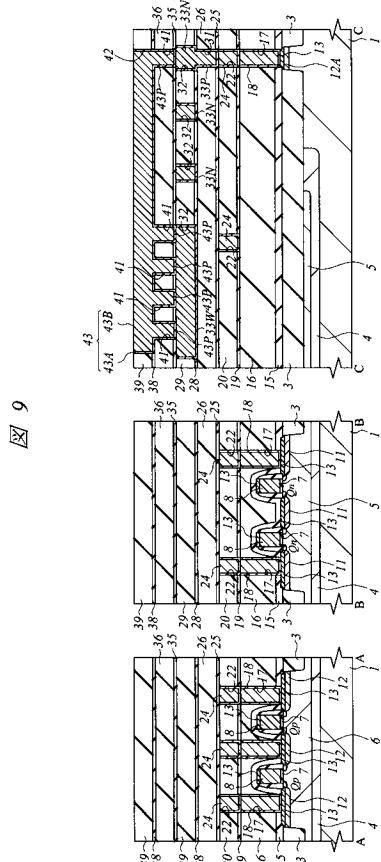

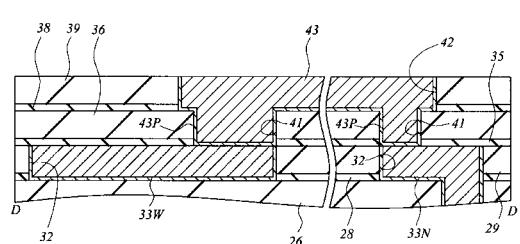

次に、図 8 および図 9 に示すように、Cu 配線 3 3 N 、 3 3 W の上部に、たとえば上記炭化シリコン膜 2 5 、層間絶縁膜 2 6 、炭化シリコン膜 2 8 および層間絶縁膜 2 9 と同様の炭化シリコン膜 (第 2 絶縁膜) 3 5 、層間絶縁膜 (第 2 絶縁膜) 3 6 、炭化シリコン膜 (第 3 絶縁膜) 3 8 および層間絶縁膜 (第 3 絶縁膜) 3 9 を順次堆積する。続いて、たとえば層間絶縁膜 3 9 上に窒化シリコン膜を堆積した後、上記接続孔 3 1 および配線溝 3 2 を形成した工程と同様の工程により Cu 配線 3 3 N 、 3 3 W の上部に接続孔 (第 1 孔部) 4 1 および配線溝 (第 2 配線溝) 4 2 を形成する。次いで、配線溝 4 2 の内部にバリアメタル膜 4 3 A および Cu 膜 (第 3 導電性膜) 4 3 B からなる第 3 層目の埋め込み配線である Cu 配線 (第 2 埋め込み配線) 4 3 を形成する。また、この時、接続孔 4 1 内にはバ

10

20

30

40

50

リニアメタル膜43AおよびCu膜43Bからなるプラグ(第1プラグ、第2プラグ)43PがCu配線43と一緒に形成される。第3層目のCu配線43は、前述した第1層目の埋め込み配線24を形成するCu膜24Bの形成方法(図4参照)に準じて形成すればよい。このCu配線43を介することによって、Cu配線33NとCu配線33Wとは電気的に接続される。

#### 【0039】

上記したように、本実施の形態1においては、プラグ43PとCu配線43と一緒に形成する場合について例示したが、層間絶縁膜36を堆積した工程に続いて、層間絶縁膜36および炭化シリコン膜35をエッチングすることによって接続孔41を形成し、その接続孔41内にバリアメタル膜およびCu膜(第2導電性膜)からなるプラグ43Pを形成した後、炭化シリコン膜38および層間絶縁膜39を順次堆積し、層間絶縁膜39および炭化シリコン膜38をエッチングすることによって配線溝42を形成し、その配線溝42内にバリアメタル膜およびCu膜(第3導電性膜)からなるCu配線43を形成してもよい。このような場合においても、プラグ43PおよびCu配線43は、前述した第1層目の埋め込み配線24を形成するCu膜24Bの形成方法(図4参照)に準じて形成すればよい。

#### 【0040】

なお、図示はしないが、たとえば第3層目の埋め込み配線であるCu配線43の上部には、Cu配線43と同様にしてCuを主導電層とする第4層目の埋め込み配線および第5層目の埋め込み配線が形成される。また、たとえば高集積化のため、第1層目～第3層目の信号配線の配線幅は、第4層目および第5層目の信号配線の配線幅よりも細く形成される。これにより第4層目のCu配線と第5層目のCu配線とを電気的に接続するプラグの口径は、第2層目のCu配線と第3層目のCu配線とを電気的に接続するプラグ43Pの口径よりも大きく形成される。

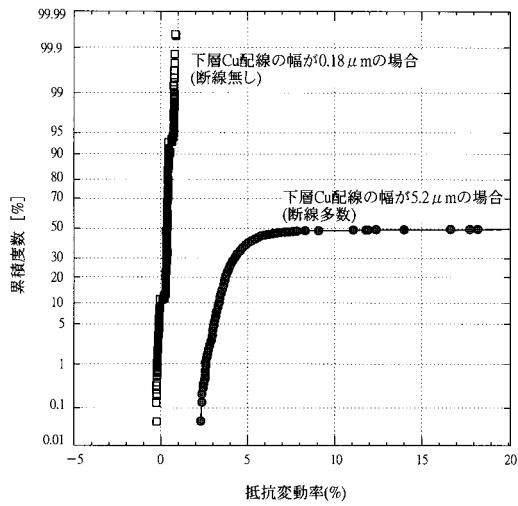

#### 【0041】

上記埋め込み配線24およびCu配線33N、33W、43の膜中には、多くの空孔(原子の抜けた孔)が点在している。このような空孔は、ストレスマイグレーションによってその表面に接続するプラグとの界面へ移動してくる。本発明者らは、上記埋め込み配線24およびCu配線33N、33W、43などが形成された半導体基板1に対して高温放置試験(ストレスマイグレーション試験)を施し、Cu配線33WおよびCu配線43を例に取り、Cu配線33WとCu配線43との間の抵抗変動率および抵抗変動率の測定点の累積度数を調べた。図10は、その抵抗変動率と累積不良率との関係を示したものである。この時、Cu配線43の配線幅は約0.18μmであり、Cu配線33WとCu配線43との間のプラグ43Pは1つのみである。Cu配線33Wの表面に存在する空孔の量は、その配線幅(配線の表面積)に比例することから、図10に示すように、下層のCu配線33Wの幅が上層のCu配線43と同程度(約0.18μm)である場合に、これらの配線をプラグ43P(口径は、約0.18μm)で接続する場合に対して、Cu配線33Wの幅がCu配線43よりも大きい(たとえば約5.2μm)場合には、抵抗変動率の測定点の累積度数の増加量に対して抵抗変動率の増加量が大幅に大きくなる。すなわち、Cu配線33Wの幅がCu配線43よりも大きい場合には、Cu配線33Wの膜中に点在する空孔がストレスマイグレーションによってCu配線33Wとプラグ43Pとの界面に集まって大きな空隙(ボイド)になり、Cu配線33WとCu配線43との間で導通不良(断線)が発生しやすいことを示している。また、ここでは下層のCu配線33Wの幅が上層のCu配線43と同程度の場合と比較して、Cu配線33Wの幅が上層のCu配線43の幅よりも広い場合としているが、これは特にこの条件に限られるものではない。すなわち、Cu配線33Wの幅がプラグ43Pの口径と同程度(約0.18μm)であり、上層のCu配線43の幅(約5.2μm)よりも狭い場合、またはプラグ43P(口径は約0.18μm)に対してCu配線33Wの幅および上層のCu配線43の幅が広い場合(約5.2μm)についても同様に抵抗変動率の測定点の累積度数の増加量に対して抵抗変動率の増加量が大幅に大きくなる傾向があり、特にプラグ43Pの口径に対して下層のCu

10

20

30

40

50

配線 3 3 W の幅が広い場合に顕著である。つまり、プラグ 4 3 P の口径に対して上層または下層の配線幅が広い場合においては、プラグ 4 3 P の底面部に空隙（ボイド）が集まりやすくなり、導通不良（断線）の発生を促す要因となることを示している。

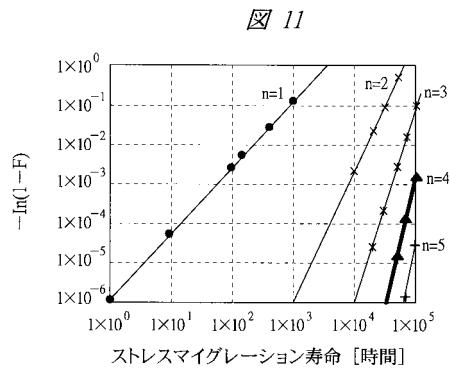

#### 【0042】

プラグ 4 3 P の径を Cu 配線 4 3 の幅とほぼ同一とし、Cu 配線 3 3 W と Cu 配線 4 3 との間のプラグ 4 3 P における故障（導通不良）の発生が完全に独立事象であるとした場合には、確率の積の法則から、そのプラグ 4 3 P が n 個である場合の故障確率は、そのプラグが 1 個である場合の故障確率の n 乗となる。そのため、プラグ 4 3 P が n 個である場合の累積不良率（故障確率）をプラグ 4 3 P の個数 n と経過時間 t の関数 F で表すと、 $F(n, 1; t) = F(1, 1; t)^n$  と表すことができる。また、本実施の形態 1 の半導体集積回路装置が形成された半導体チップ内に前述したような Cu 配線 3 3 W および Cu 配線 4 3 の組み合わせが N 個存在する場合には、関数 F にその組み合わせ数 N をパラメータとして加えることができ、その半導体チップの累積不良率とすることができます。すなわち、 $1 - F(n, N; t) = \{1 - F(n, 1; t)\}^N$  となることから、 $1 - F(n, N; t) = \{1 - F(1, 1; t)\}^N$  と表すことができる。図 11 は、この式をもとに求めた、N が 500 である場合の Cu 配線 3 3 W と Cu 配線 4 3 との間ににおけるストレスマイグレーションによる導通不良発生までの寿命（ストレスマイグレーション寿命という）と関数 F との関係を示したものであり、n が 1 ~ 4 である場合のそれぞれについて示している。図 11 中において、n が 1 である場合と n が 2 である場合とを関数 F が  $1 \times 10^{-3}$  となるところで比較すると、n が 2 である場合のストレスマイグレーション寿命は、n が 1 である場合のストレスマイグレーション寿命から約  $1 \times 10^2$  倍向上している。また、n が 1 である場合と n が 4 である場合とを関数 F が  $1 \times 10^{-3}$  となるところで比較すると、n が 4 である場合のストレスマイグレーション寿命は、n が 1 である場合のストレスマイグレーション寿命から約  $1 \times 10^3$  倍向上しており、約 10 年（87600 時間）を実現することができる。

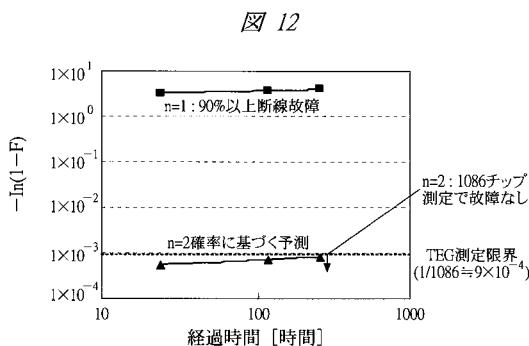

#### 【0043】

また、図 12 は、上記 n が 1 であり N が 20000 である場合の経過時間に対する累積不良率の実測値および上記の式をもとに求めた、n が 2 である場合の経過時間と関数 F との関係を示したものである。この時、1 枚の半導体ウェハ（半導体基板 1）から、本実施の形態 1 の半導体集積回路装置が形成された半導体チップが 1086 個取得できるものとし、TEG（Test Element Group）を用いた検査で測定できる  $-1n$  ( $1 - F$ ) の最小値は、 $1 / 1086$  ( $9 \times 10^{-4}$ ) としている。図 12 に示すように、n が 1 である場合に、たとえば Cu 配線 3 3 W および Cu 配線 4 3 の組み合わせのうちの約 90% 以上においてストレスマイグレーションによる導通不良が発生していたとしても、n を 2 とすることによって、1 枚の半導体ウェハ内においては Cu 配線 3 3 W と Cu 配線 4 3 との間でのストレスマイグレーションによる導通不良発生の抑制が可能となる。

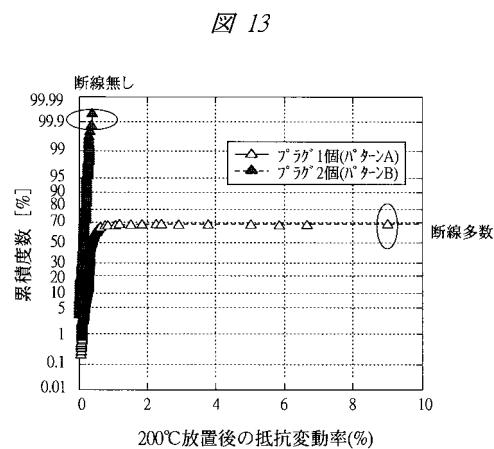

#### 【0044】

図 13 は、正面（素子形成面）上に複数の上記 Cu 配線 3 3 W、4 3 およびプラグ 4 3 P などが形成された半導体基板 1 に対して、約 200 の加熱を施すストレスマイグレーション試験を行った後における Cu 配線 3 3 W と Cu 配線 4 3 との間の抵抗変動率と、抵抗変動率の測定点の累積度数との関係を示したものであり、Cu 配線 3 3 W と Cu 配線 4 3 との間にプラグ 4 3 P が 1 個配置された場合と 2 個配置された場合とのそれぞれについて示している。ここで、上記した Cu 配線 3 3 W および Cu 配線 4 3 の組み合わせ数 N は、20000 であるとする。また、図 13 ~ 図 17 中では、プラグ 4 3 P について 2 通りの形成パターン（パターン A、B）で形成した際の結果を示している。図 13 に示すように、Cu 配線 3 3 W と Cu 配線 4 3 との間にプラグ 4 3 P が 1 個配置された場合（パターン A）には、抵抗変動率の測定点の累積度数の増加に対して Cu 配線 3 3 W と Cu 配線 4 3 との間の抵抗変動率が大きく増加している。これは、Cu 配線 3 3 W と Cu 配線 4 3 との間で導通不良（断線）が多数発生していることを示しているものである。一方、Cu 配線 3 3 W と Cu 配線 4 3 との間にプラグ 4 3 P が 2 個配置された場合（パターン B）には、

10

20

30

40

50

抵抗変動率の測定点の累積度数の増加に対して Cu 配線 3 3 W と Cu 配線 4 3 との間の抵抗変動率の変化は、プラグ 4 3 P が 1 個の場合に比べて大幅に小さい。これは、Cu 配線 3 3 W と Cu 配線 4 3 との間で導通不良（断線）がほとんど発生していないことを示しているものである。すなわち、ストレスマイグレーション試験の結果からも、Cu 配線 3 3 W と Cu 配線 4 3 との間に複数個のプラグ 4 3 P を配置することにより、Cu 配線 3 3 W と Cu 配線 4 3 との間での導通不良（断線）を抑制できることがわかる。

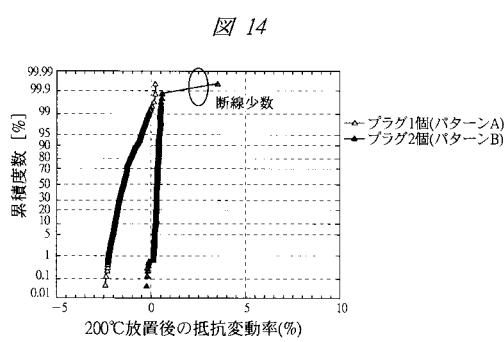

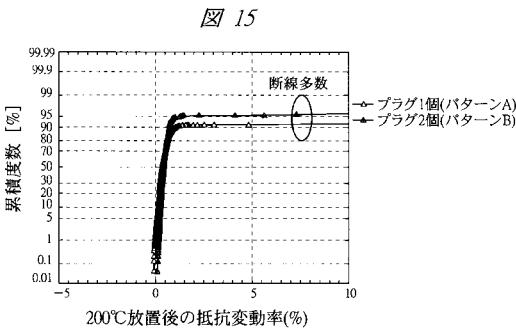

#### 【 0 0 4 5 】

図 14 および図 15 は、主面上に複数の上記 Cu 配線 3 3 W、4 3 およびプラグ 4 3 P などが形成された半導体基板 1 に対して、約 200 の加熱を施すストレスマイグレーション試験を行った後における Cu 配線 3 3 W と Cu 配線 4 3 との間の抵抗変動率と、抵抗変動率の測定点の累積度数との関係を示したものであり、Cu 配線 3 3 W と Cu 配線 4 3 との間にプラグ 4 3 P が 1 個配置された場合（パターン A）と 2 個配置された場合（パターン B）とのそれぞれについて示している。この時、Cu 配線 3 3 W の幅は約 5.2 μm であり、Cu 配線 4 3 の幅は 0.18 μm であり、上記した Cu 配線 3 3 W および Cu 配線 4 3 の組み合わせ数 N は 1200 である。また、図 14 は、Cu 配線 3 3 W の幅方向（Cu 配線 3 3 W が延在する方向に直行する方向）の端部から約 0.09 μm のところにプラグ 4 3 P を配置した場合（パターン A）（プラグ 4 3 P が 2 個の場合には、Cu 配線 3 3 W の幅方向の端部に近いプラグ 4 3 P までの距離が約 0.09 μm の場合（パターン B））の結果について示したものである。一方、図 15 は、Cu 配線 3 3 W の幅方向の端部から約 2.6 μm のところにプラグ 4 3 P を配置した場合（パターン A）（プラグ 4 3 P が 2 個の場合には、Cu 配線 3 3 W の幅方向の端部に近いプラグ 4 3 P までの距離が約 2.6 μm の場合（パターン B））の結果について示したものである。図 15 に示すように、Cu 配線 3 3 W の幅方向の端部から約 2.6 μm のところにプラグ 4 3 P を配置した場合には、抵抗変動率の測定点の累積度数の増加に対して Cu 配線 3 3 W と Cu 配線 4 3 との間の抵抗変動率が大きく増加している。これは、Cu 配線 3 3 W と Cu 配線 4 3 との間で導通不良（断線）が多数発生していることを示しているものである。一方、図 14 に示すように、Cu 配線 3 3 W の幅方向の端部から約 0.09 μm のところにプラグ 4 3 P を配置した場合には、図 15 に示した場合に比べて抵抗変動率の測定点の累積度数の増加に対する Cu 配線 3 3 W と Cu 配線 4 3 との間の抵抗変動率の増加量は大幅に小さくなっている。すなわち、図 14 および図 15 に示した結果より、プラグ 4 3 P の配置位置が、配線幅方向において Cu 配線 3 3 W の端部から離れ中央部に近づくに従って、Cu 配線 3 3 W と Cu 配線 4 3 との間でのストレスマイグレーションによる導通不良が増加することがわかる。

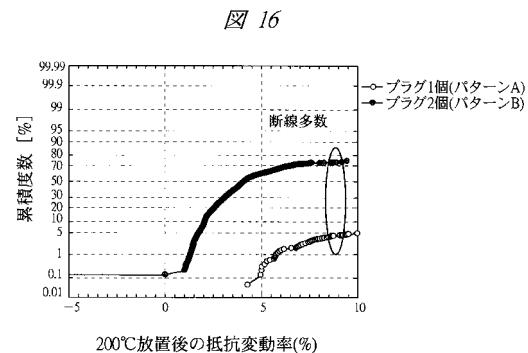

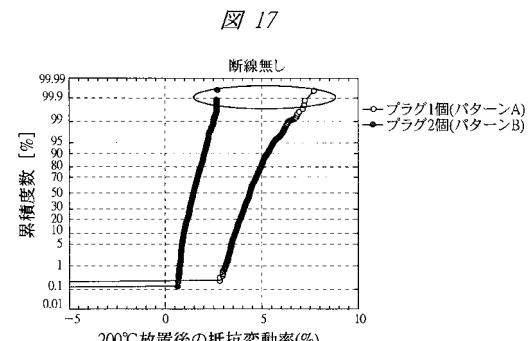

#### 【 0 0 4 6 】

図 16 および図 17 は、主面上に複数の上記 Cu 配線 3 3 W、4 3 およびプラグ 4 3 P などが形成された半導体基板 1 に対して、約 200 の加熱を施すストレスマイグレーション試験を行った後における Cu 配線 3 3 W と Cu 配線 4 3 との間の抵抗変動率と、抵抗変動率の測定点の累積度数との関係を示したものであり、Cu 配線 3 3 W と Cu 配線 4 3 との間にプラグ 4 3 P が 1 個配置された場合（パターン A）と 2 個配置された場合（パターン B）とのそれぞれについて示している。この時、Cu 配線 3 3 W の幅は約 5.2 μm であり、Cu 配線 4 3 の幅は 0.18 μm であり、上記した Cu 配線 3 3 W および Cu 配線 4 3 の組み合わせ数 N は 1200 である。また、図 16 はプラグ 4 3 P の径を約 0.18 μm とした場合の結果について示したものであり、図 17 はプラグ 4 3 P の径を約 0.36 μm とした場合の結果について示したものである。図 16 に示すように、プラグ 4 3 P の径を約 0.18 μm とした場合には、抵抗変動率の測定点の累積度数の増加に対して Cu 配線 3 3 W と Cu 配線 4 3 との間の抵抗変動率が大きく増加している。これは、Cu 配線 3 3 W と Cu 配線 4 3 との間で導通不良（断線）が多数発生していることを示しているものである。一方、図 17 に示すように、プラグ 4 3 P の径を約 0.36 μm とした場合には、プラグ 4 3 P の径を約 0.18 μm とした場合に比べて抵抗変動率の測定点の累積度数の増加に対する Cu 配線 3 3 W と Cu 配線 4 3 との間の抵抗変動率の増加量は大幅に

10

20

30

40

50

小さくなっている。すなわち、図16および図17に示した結果より、プラグ43Pの径が大きくなるに従って、プラグ43PとCu配線33Wとの接触面積が増大するので、Cu配線33WとCu配線43との間ににおいてストレスマイグレーションによる導通不良に対する耐性が強くなることがわかる。すなわち、プラグ43Pの径が約0.36μmより小さくなるに従い、ストレスマイグレーションによる導通不良が発生しやすくなる。

#### 【0047】

本実施の形態1においては、図10～図17を用いて説明した各要素を考慮して、Cu配線33WとCu配線43とを接続するプラグ43Pの配置方法について以下のような規定をする。なお、以下の規定中においては、特に断りのない限りCu配線43の幅は約0.18μmであり、プラグ43Pの径も約0.18μmであるものとする。

10

#### 【0048】

たとえば、Cu配線33W (Cu配線33Nも含む)の幅が約0.9μm以下である場合には、プラグ43Pは1個のみ配置する。前述したように、プラグ43Pの径に対してCu配線33Wの幅が大きくなるに従って、ストレスマイグレーションによる導通不良が発生しやすくなるものであるから、Cu配線33Wの幅が所定の値より小さい場合には、そのような導通不良の恐れも少ないことから、プラグ43Pの配置数は1個のみとするものである。また、ストレスマイグレーションによる導通不良の原因となる空孔はCu配線33Wの膜中に多く存在し、プラグ43PとCu配線33Wとの界面を中心として全方向から集まつてくるものであるから、プラグ43Pは、可能な限りCu配線33Wの幅方向における端部に近い位置 (第1位置) で目外れのないようにCu配線33Wと接続するよう配置する。これにより、そのプラグ43Pの配置位置においては、Cu配線33Wの幅方向における端部からの空隙の集中を防ぐことができるので、図14および図15を用いて前述したように、Cu配線33WとCu配線43との間でストレスマイグレーションによる導通不良が発生することを抑制することができる。

20

#### 【0049】

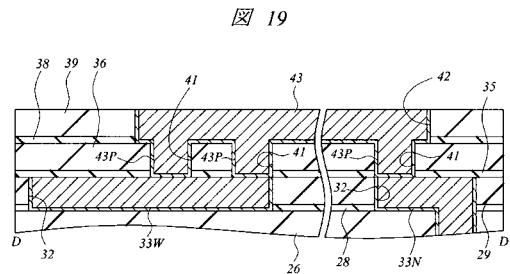

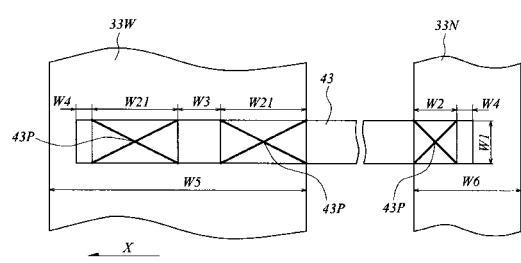

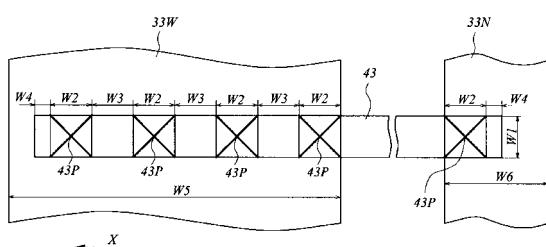

たとえば、Cu配線33Wの幅が約0.9μm以上かつ約1.44μm未満である場合には、図18および図19に示すように、Cu配線33W上にプラグ43Pは2個以上配置する。なお、図18および図19は、プラグ43Pを2個配置した場合について図示したものであり、図19は、図18中のD-D線に沿った断面を示したものである。また、図18中において、W1はCu配線43の幅を示し、W2はプラグ43Pの径を示し、W3は隣接するプラグ43P間の距離を示し、W4はCu配線43の延在する方向 (Xで示す方向) におけるプラグ43PのCu配線43の端部からの配置余裕距離を示し、W5はCu配線33Wの幅を示し、W6はCu配線33Nの幅を示すものである。また、たとえばW3はプラグ43Pの径と同様の約0.18μmとし、W4は約0.06μmとする。本実施の形態1において、Cu配線33Wの幅が約0.9μm以上であり約1.44μmより小さい場合には、Cu配線33Wと接続するプラグ43Pを2個以上配置しても、本実施の形態1の半導体集積回路装置を形成するセルの大きさに与える影響は小さい。そのため、2個以上のCu配線33Wと接続するプラグ43Pを容易に配置することができる。図13を用いて前述したように、Cu配線33Wの幅が大きくなり、Cu配線33WとCu配線43との間でストレスマイグレーションによる導通不良 (断線) が発生しやすくなることが懸念される場合でも、Cu配線33WとCu配線43との間に2個以上のプラグ43Pを配置することによって、ストレスマイグレーションによる導通不良の原因となる空隙の集合を複数のプラグ43Pの配置箇所へ分散させることができるので、そのような導通不良の発生を防ぐことができる。すなわち、Cu配線33WとCu配線43との間で導通不良を起こすまでの時間 (ストレスマイグレーション寿命) を延ばすことができる。

30

#### 【0050】

また、ストレスマイグレーションによる導通不良の原因となる空孔は、プラグ43PとCu配線33Wとの界面を中心としてCu配線33Wの膜中の全方向から集まつくるものであるから、プラグ43Pのうちの1個は、可能な限りCu配線33Wの幅方向 (Xで示す方向) における端部に近い位置で目外れのないようにCu配線33Wと接続するよう

40

50

配置する。すなわち、プラグ43Pの口径の中心を、Cu配線33Wの配線幅方向の中心部から合わせ余裕の1/2以上配線幅方向にずらして配置する。これにより、そのプラグ43Pの配置位置においては、Cu配線33Wの幅方向における端部からの空孔の集中を防ぐことができるので、図14および図15を用いて前述したように、Cu配線33WとCu配線43との間でストレスマイグレーションによる導通不良が発生することを抑制することができる。

#### 【0051】

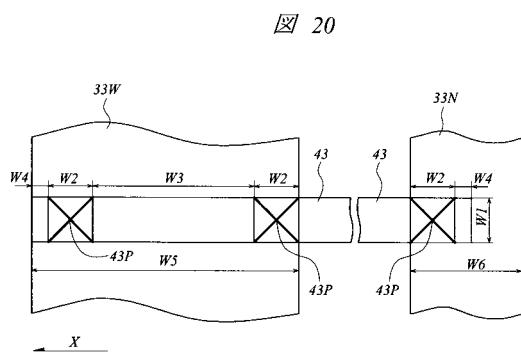

また、図20に示すように、プラグ43Pの両方を可能な限りCu配線33Wの配線幅方向(Xで示す方向)における両端部に近い位置で目外れのないようにCu配線33Wと接続するように配置する。すなわち、両方のプラグ43Pのそれぞれの口径の中心をCu配線33Wの配線幅方向の中心部から合わせ余裕の1/2以上配線幅方向にずらして配置する。これにより、両方のプラグ43Pの配置位置においては、Cu配線33Wの配線幅方向における端部からの空孔の集中を防ぐことができるので、図14および図15を用いて前述したように、Cu配線33WとCu配線43との間でストレスマイグレーションによる導通不良が発生することを抑制することができる。

#### 【0052】

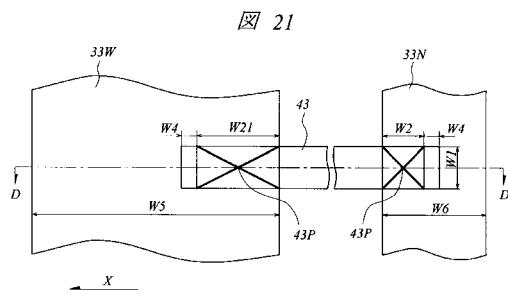

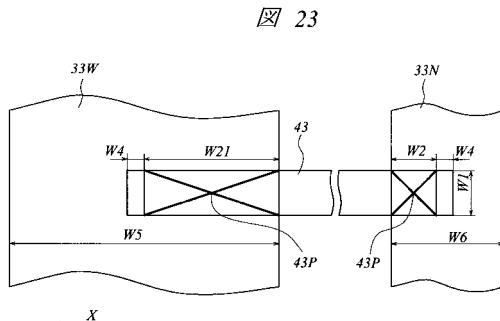

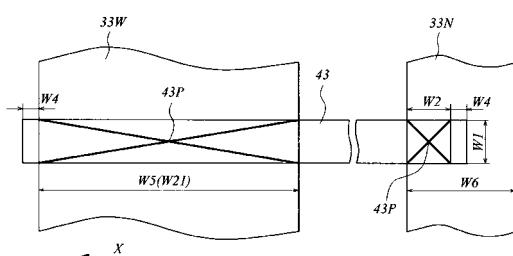

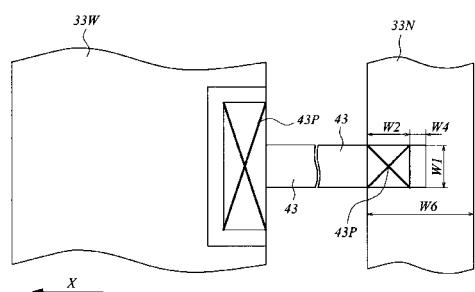

図18および図19で図示したような2個のプラグ43PをCu配線33W上に配置する代わりに、図21および図22に示すように、Cu配線33W上に配置するプラグ43Pは1個とし、そのプラグ43PのCu配線43の延在する方向(Xで示す方向)での径W21を拡大してもよい。この時、W21については、Cu配線43の幅W1の約2倍(約0.36μm)とすることを例示できる。このように径を大きくしたプラグ43Pを配置することにより、プラグ43PとCu配線33Wとが接する面積を拡大できるので、図16および図17を用いて前述したように、プラグ43PとCu配線33Wとの界面にストレスマイグレーションによって空孔が集中した場合でも、Cu配線33WとCu配線43との間におけるストレスマイグレーションによる導通不良に対する耐性を強くすることができる。それにより、Cu配線33WとCu配線43との間でストレスマイグレーションによる導通不良が発生することを抑制することができる。図18および図19中においては、W21をW1の約2倍とした場合について例示したが、W21をさらに大きく設計してもよく、たとえば約3倍以上としてもよい(図23参照)。

#### 【0053】

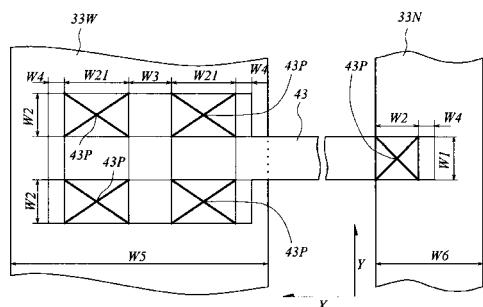

また、図24に示すように、Cu配線33W上において図21～図23に示したようなCu配線43の延在する方向(Xで示す方向)での径W21が拡大したプラグ43PをCu配線43の延在する方向で複数個配置できる場合には、そのようにしてもよい。なお、図23においては、プラグ43Pを2個配置した場合について図示してある。この時、隣接するプラグ43P間の距離は、図18および図19を用いて説明した場合と同様に約0.18μmとすることを例示できる。このように、Cu配線43の延在する方向(Xで示す方向)での径W21が拡大したプラグ43PをCu配線43の延在する方向で複数個配置ことにより、Cu配線33WとCu配線43との間におけるストレスマイグレーションによる導通不良に対する耐性を、図21～図23に示した場合よりさらに強くすることができる。

#### 【0054】

また、図25に示すように、Cu配線33W上においてCu配線43の幅を広げ、Cu配線43の延在する方向(Xで示す方向)での径W21が拡大したプラグ43PをCu配線43の延在する方向で複数個配置したもの(図23参照)を、さらにCu配線33Wの延在する方向(Yで示す方向)においても複数個配置してもよい。このようにXで示す方向およびYで示す方向のそれぞれについてプラグ43Pを複数個配置する場合には、プラグ43Pの配置位置の設計を手動で行うものとする。なお、図25においては、Xで示す方向およびYで示す方向のそれぞれについて、プラグ43Pを2個ずつ配置した場合について図示してある。このようなプラグ43Pの配置手段を用いることにより、Cu配線33WとCu配線43との間におけるストレスマイグレーションによる導通不良に対する耐性

10

20

30

40

50

を、図24に示した場合よりさらに強くすることができる。

【0055】

また、図26に示すように、Cu配線43がCu配線33Wを跨ぐように延在するようにパターニングし、Cu配線43の延在する方向(Xで示す方向)でのプラグ43Pの径W21をCu配線33Wの幅W5と同程度にまで拡大してもよい。このようなプラグ43PをCu配線33W上に配置することにより、Cu配線33WとCu配線43との間におけるストレスマイグレーションによる導通不良に対する耐性を、図21～図23に示した場合よりさらに強くすることができる。

【0056】

なお、本実施の形態1において、Cu配線33W(Cu配線33Nも含む)の幅が約0.9μm以下である場合には、プラグ43Pの配置数は1個のみとしているが、これに限定されるものではなく、Cu配線33W(Cu配線33Nも含む)の幅が約0.6μm以上かつ0.9μm未満では、図18および図19に示すようにCu配線33W上にプラグ43Pを2個配置してもよいし、図21～図23に示すように、Cu配線33W上に配置するプラグ43Pは1個とし、そのプラグ43PのCu配線43の延在する方向(Xで示す方向)での径W21を拡大してもよい。

【0057】

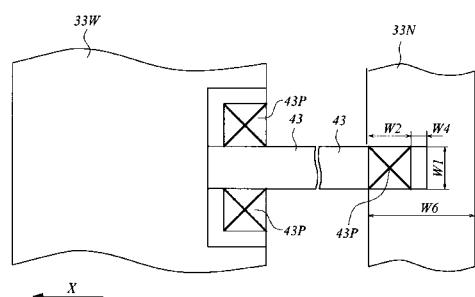

また、Cu配線33W(Cu配線33Nも含む)の幅が約0.6μm未満では、図27に示すようにCu配線33W上にプラグ43PをCu配線33Wの延在する方向(Xで示す方向に垂直な方向)に2個以上配置してもよいし、図28に示すようにCu配線33W上に配置するプラグ43Pは1個とし、そのプラグ43PのCu配線33Wの延在する方向(Xで示す方向に垂直な方向)での径W21を拡大してもよい。なお、Cu配線33W上を延在するCu配線43を、Cu配線33Wの延在する方向にさらに延在して設け、3個以上複数のプラグ43Pを配置してもよいし、プラグ43Pは1個とし、そのプラグ43PのCu配線43の延在する方向(Xで示す方向)での径W21を拡大してもよい。それにより、Cu配線33W(Cu配線33Nも含む)の幅が約0.9μm以下である場合においても、Cu配線33WとCu配線43との間でストレスマイグレーションによる導通不良が発生することを抑制することができる。

【0058】

Cu配線33Wの幅が約1.44μm以上である場合には、たとえば図29に示すように、Cu配線33W上にプラグ43Pは4個以上配置する。なお、図29は、プラグ43Pを4個配置した場合について図示したものである。本実施の形態1において、Cu配線33Wの幅が約1.44μm以上である場合には、Cu配線33Wと接続するプラグ43Pを4個以上配置しても、本実施の形態1の半導体集積回路装置を形成するセルの大きさに与える影響は小さい。そのため、4個以上のCu配線33Wと接続するプラグ43Pを容易に配置することができる。このように、下層のCu配線33Wの幅が大きくなった場合には、それに合わせてCu配線33Wと接続するプラグ43Pの配置数を増やすことにより、図18および図19を用いて前述した場合と同様の効果を得ることができる。

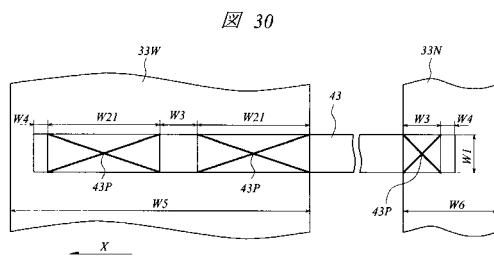

【0059】

また、図30に示すように、Cu配線33Wの幅が約1.44μm以上である場合にも、図21～図23を用いて前述したようなCu配線43の延在する方向(Xで示す方向)での径W21が拡大したプラグ43PをCu配線43の延在する方向で複数個配置してもよい。それにより、Cu配線33Wの幅が約1.44μm以上である場合にも、図21～図23を用いて前述した場合と同様の効果を得ることができる。

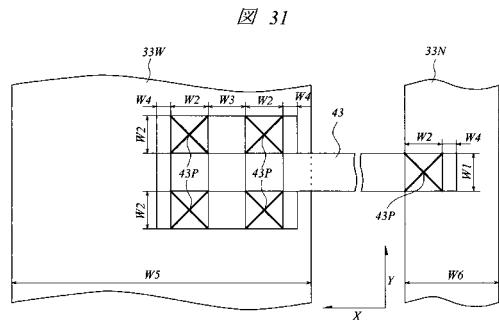

【0060】

Cu配線33Wの幅が約1.44μm以上である場合には、4個以上のプラグ43PをCu配線33W上にてCu配線43の延在する方向(Xで示す方向)に沿って一列に配置する以外の手段を用いてもよい。たとえば、図31に示すように、Cu配線33W上においてCu配線43の幅を広げ、Cu配線43の延在する方向およびCu配線33Wの延在する方向(Xで示す方向)のそれぞれにおいてプラグ43Pを複数個配置するものである。

10

20

30

40

50

なお、図31においては、Xで示す方向およびYで示す方向のそれぞれについて、プラグ43Pを2個ずつ配置した場合について図示してある。この時、Xで示す方向における隣接するプラグ43P間の距離W3はプラグ43Pの径と同程度とし、Yで示す方向における隣接するプラグ43P間の距離はCu配線33N上におけるCu配線43の幅と同程度とすることを例示できる。このようにプラグ43Pを配置することによっても、図29に示した場合と同様の効果を得ることができる。

#### 【0061】

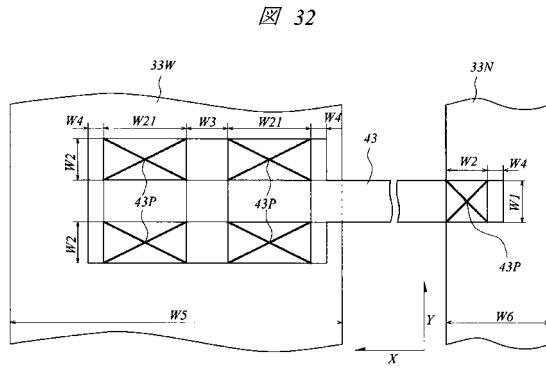

また、Cu配線33Wの幅が約1.44μm以上である場合においても、図25を用いて前述した場合と同様のプラグ43Pの配置手段を用いることができる（図32参照）。それにより、Cu配線33WとCu配線43との間におけるストレスマイグレーションによる導通不良に対する耐性を、図30に示した場合よりさらに強くすることができる。

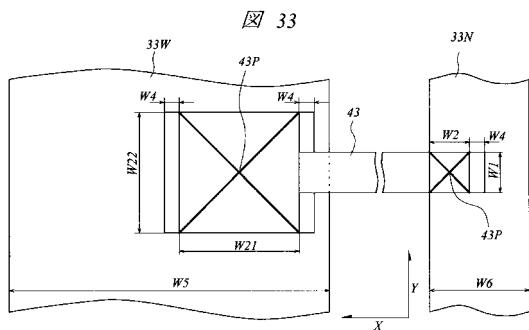

#### 【0062】

また、Cu配線33Wの幅が約1.44μm以上である場合においては、図33に示すように、Cu配線33W上においてCu配線43の幅を広げ、Cu配線43の延在する方向（Xで示す方向）での径W21およびCu配線33Wの延在する方向（Yで示す方向）での径W22が拡大したプラグ43PをCu配線33W上に配置してもよい。この時、W21およびW22は、Cu配線33N上に配置されたプラグ43Pの径W2の約2倍以上とすることを例示できる。このようにプラグ43Pを配置することによっても、図29～図32を用いて前述した場合と同様の効果を得ることができる。

#### 【0063】

また、本発明者らが行った実験によれば、本実施の形態1におけるCu配線33WとCu配線43とを接続するプラグ43Pの配置方法は、プラグ43Pの底部の径が0.2μm程度以下である場合に特に有効であることがわかった。

#### 【0064】

ここで、本実施の形態1に示す図21、23、24、25、26、30、32、33のような接続孔の形状において、実際にこのような大きな径を形成する場合には、エッチングされる層（ここでは層間絶縁膜36）とエッチングストップとなる層（ここでは炭窒化シリコン膜35）との間で選択比が小さくなる恐れがある。すなわち、図26に示されるような径がW5とW2の接続孔を同時に形成する場合、W2の接続孔が開口する前にW5の接続孔が開口され、その後W2の接続孔が開口するまでエッチングを続けるとオーバーエッチとなり、W5の接続孔下、またはその周辺までもエッチングしてしまうという問題が発生する。このエッチングの選択比はエッチングされる層36、エッチングストップ層35の材料やドライエッティングの条件にも起因するため、一般的に径の大きさのみでは定義できないが、この選択比は5以上が必要であり、この選択比が満たされる範囲で接続孔の径を大きくするならば、ストレスマイグレーションによる導通不良に対する耐性を高めるのに有効な手段であることは前述した通りである。

#### 【0065】

なお、図示は省略するが、図7および図8を用いて説明した工程の後、前述した工程を繰り返し、第3層目のCu配線43の上部に単層または複数層のCu配線を形成することにより、本実施の形態1の半導体集積回路装置を製造する。

#### 【0066】

なお、特に限定はされないが、第3層目のCu配線よりも上層のCu配線層において、それらの配線層間を接続するプラグの口径が0.5μm以上の場合、配線層間を接続するプラグは、電流密度等が許す範囲内等他の事情により複数個プラグを設ける必要がある場合以外は一つで構成される。

#### 【0067】

また、特に限定はされないが、後述するように、たとえば第2および第3層目のCu配線において、高集積化のために信号配線は約0.18μmの配線幅で形成され、約0.18μm以上の太い配線幅を有する配線としては、基準電圧（V<sub>SS</sub>）または電源電圧（V<sub>D</sub>）を供給する電源配線がある。

10

20

30

40

50

## 【0068】

(実施の形態2)

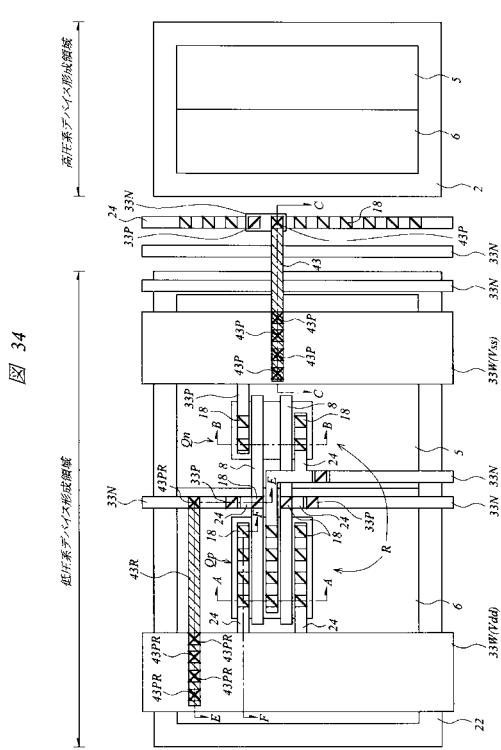

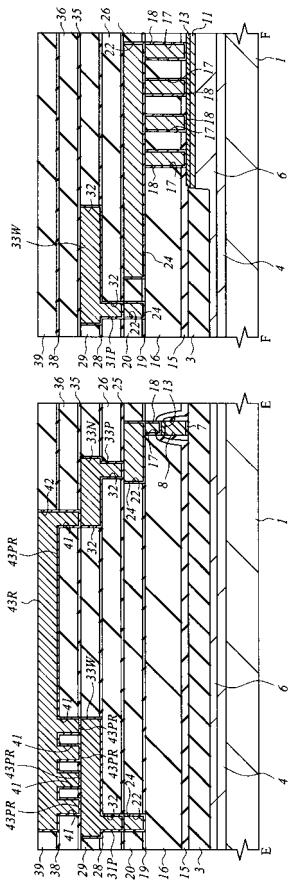

図34は本実施の形態2の半導体集積回路装置の製造工程中の要部平面図であり、図35は図34中に示すE-E線およびF-F線のそれぞれに沿った断面図を示したものである。

## 【0069】

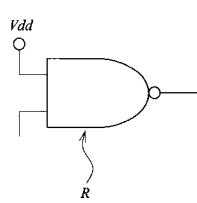

本実施の形態2の半導体集積回路装置の製造工程は、修正用の回路Rを有すること以外前記実施の形態1の半導体集積回路装置の製造工程とほぼ同様であるが、図34および図35に示すように、プラグ43PおよびCu配線43を形成する工程時にプラグ(第1プラグ)43PRおよびCu配線(第2埋め込み配線)43Rも形成するものである。本実施の形態2においては、たとえば本実施の形態2の半導体集積回路装置を製造し回路動作のテストを行う一連の製造工程にて回路設計上の欠陥が発生した場合に、回路接続を修正するために修正用の回路Rが予め半導体集積回路装置に形成されている。すなわち、回路動作のテスト後にマスクパターンを変更し、配線に対して切断・接続処理することによってその欠陥によって不良となつた回路(配線)を半導体集積回路装置から電気的に切り離したり、回路接続を修正するため修正用の回路Rを電気的に接続できるように、第3層目のCu配線43Rについては予め冗長な設計がなされている。また、そのような切断・接続処理を考慮して、Cu配線43Rはできるだけ上層の配線として形成することが好ましく、第3層目の埋め込み配線であるCu配線43Rを用いている。たとえば、図34および図36に例示するように、修正用の回路Rは、使用しないときはフロー・ティングになるのを避ける目的で、修正用の回路Rの入力(MISFETQn、Qpのゲート電極)は、Cu配線43RによりCu配線33W(電源配線(Vdd))に電気的に接続され、電位が固定されている。

## 【0070】

Cu配線43Rは、プラグ43PRを介してCu配線33Wと電気的に接続している。ここで、本実施の形態2においては、Cu配線33Wは基準電位(Vss)または電源電位(Vdd)をMISFETQp、Qnまたはp型ウェル5およびn型ウェル6に供給する電源配線を形成する。そのため、Cu配線33Wと電気的に接続しているCu配線43Rの電位は固定される。それにより、たとえば本実施の形態2の半導体集積回路装置のスタートティング時において、Cu配線43Rに大電流が流れてしまうことを防ぐことができるので、Cu配線43Rを可能な限り細い幅で形成することが可能となる。すなわち、Cu配線43Rの幅はCu配線33Wの幅に比べて相対的に狭くなることから、本実施の形態2におけるCu配線33WとCu配線43Rとを接続するプラグ43PRの配置方法については、前記実施の形態1において図18～図33を用いて説明したCu配線33WとCu配線43とを接続するプラグ43Pの配置方法と同様の規定を行う。それにより、本実施の形態2においても、前記実施の形態1と同様に、Cu配線33WとCu配線43Rとの間ににおけるストレスマイグレーションによる導通不良(断線)の発生を抑制することが可能となる。

## 【0071】

(実施の形態3)

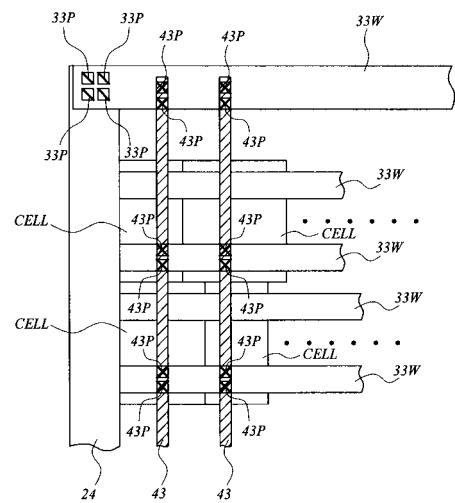

図37は本実施の形態3の半導体集積回路装置の製造工程中の要部平面図である。

## 【0072】

本実施の形態3の半導体集積回路装置の製造工程は、前記実施の形態1および2の半導体集積回路装置の製造工程とほぼ同様である。本実施の形態3においては、たとえば本実施の形態3の半導体集積回路装置を形成するセルCELLの配列上に配置され基準(接地)電位へ電気的に接続されている電源幹線である複数のCu配線33Wにおいて電位差が生じてしまうことを防ぐために、Cu配線33Wの上層に配置されたCu配線43を用いてそれら複数のCu配線33Wを電気的に接続する。すなわち、Cu配線43を複数のCu配線33Wの補助電源配線として用いるものである。

## 【0073】

10

20

30

40

50

上記したように、本実施の形態3における上記Cu配線43は補助電源配線である。また、本実施の形態3の半導体集積回路装置が形成された半導体チップの面積を小さくする目的から、Cu配線43を含む配線の配置密度を増加させる必要がある。そのため、補助電源配線となるCu配線43は、可能な限り細い幅で形成することになる。すなわち、Cu配線43の幅はCu配線33Wの幅に比べて相対的に狭くなることから、本実施の形態3におけるCu配線33WとCu配線43とを接続するプラグ43Pの配置方法については、前記実施の形態1において図18～図33を用いて説明したCu配線33WとCu配線43とを接続するプラグ43Pの配置方法と同様の規定を行う。それにより、本実施の形態3においても、前記実施の形態1と同様に、Cu配線33WとCu配線43との間におけるストレスマイグレーションによる導通不良（断線）の発生を抑制することが可能となる。10

#### 【0074】

上記のような本実施の形態3においても、前記実施の形態1および前記実施の形態2と同様の効果を得ることができる。

#### 【0075】

##### （実施の形態4）

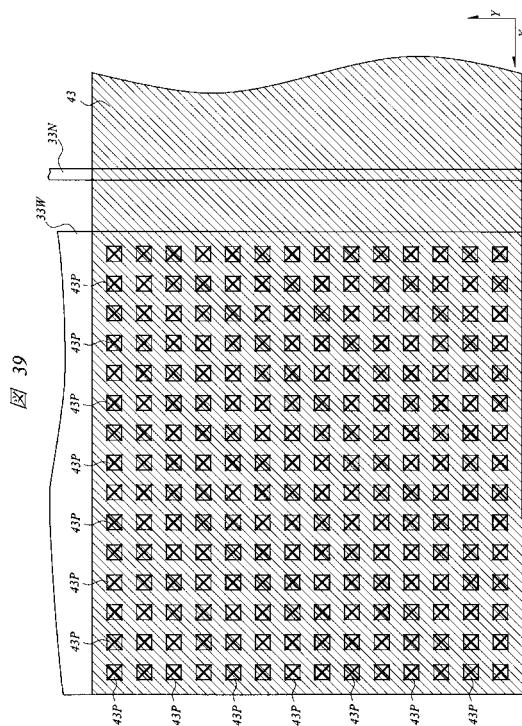

図38は本実施の形態4の半導体集積回路装置の製造工程中の要部平面図である。

#### 【0076】

本実施の形態4の半導体集積回路装置の製造工程は、前記実施の形態1～3の半導体集積回路装置の製造工程とほぼ同様である。本実施の形態4においては、たとえば前記実施の形態1の場合に比べて相対的に大きな電流をCu配線43に導通させる目的で、Cu配線43の幅を前記実施の形態1にて示したCu配線43（図8および図9参照）の幅より相対的に大きく形成するものである。ここで、本実施の形態4において、Cu配線33W、43の幅は、約3μmとする。このような場合、Cu配線33WとCu配線43とを電気的に接続するプラグ43Pは、平面においてが重なる領域にて可能な限り狭い間隔で配置可能な個数分個配置する。たとえば、径が約0.6μmのプラグ43PをCu配線43の延在する方向（Xで示す方向）およびCu配線33Wの延在する方向（Yで示す方向）のそれぞれについて2個ずつ配置するものである。Cu配線33WとCu配線43との間に、Cu配線33WおよびCu配線43の幅に対して相対的に小さい径を有するプラグ43Pを1個のみしか配置しない場合には、Cu配線33WとCu配線43との間におけるストレスマイグレーションによる導通不良（断線）の発生が懸念されるが、上記のような本実施の形態4のプラグ43Pの配置手段を用いることにより、そのような不具合を防ぐことが可能となる。20

#### 【0077】

また、図39に示すように、Cu配線33Wが電源幹線である場合には、Cu配線33WおよびCu配線43の幅を図38に示した場合よりもさらに大きく形成する。この時、そのCu配線33WおよびCu配線43の幅は、約17μmとすることを例示できる。このような場合、プラグ43Pを図38を用いて説明した場合よりもさらに多数個配置するものである。たとえば、径が約0.6μmのプラグ43PをCu配線43の延在する方向（Xで示す方向）およびCu配線33Wの延在する方向（Yで示す方向）のそれぞれについて15個ずつ配置するものである。このように、Cu配線33WおよびCu配線43の幅が大きくなった場合でも、それに合わせてCu配線33WとCu配線43とを電気的に接続するプラグ43Pの配置個数を増やすことにより、Cu配線33WとCu配線43との間におけるストレスマイグレーションによる導通不良（断線）の発生を抑制することができる。30

#### 【0078】

上記のような本実施の形態4においても、前記実施の形態1～3と同様の効果を得ることができる。

#### 【0079】

##### （実施の形態5）

10

20

30

40

50

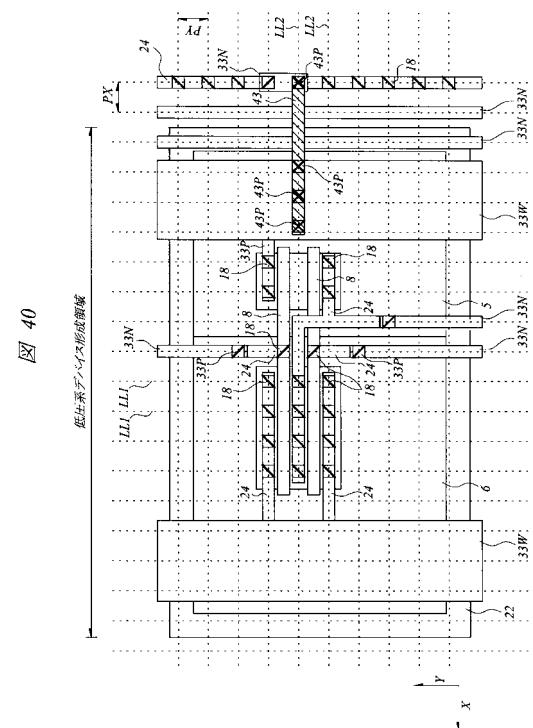

図40は本実施の形態5の半導体集積回路装置の製造工程中の要部平面図である。

【0080】

本実施の形態5の半導体集積回路装置の製造工程は、前記実施の形態1～4の半導体集積回路装置の製造工程とほぼ同様である。また、本実施の形態5においては、各配線およびプラグのレイアウト設計をコンピュータにより自動的に行うものである。たとえば、図40中に示すY方向に延在し間隔P<sub>X</sub>で配列された複数の配線格子線（第1配線格子線）L<sub>LL1</sub>とX方向に延在し間隔P<sub>Y</sub>で配列された複数の配線格子線（第2配線格子線）L<sub>LL2</sub>とが設定され、Cu配線33W、33Nはその幅方向の中心が配線格子線L<sub>LL1</sub>上に配置されるように設計され、Cu配線43はその幅方向の中心が配線格子線L<sub>LL2</sub>上に配置されるように設計されるものである。この時、コンピュータを用いてプラグ43Pの配置位置を自動的に設定すると、プラグ43Pは、その中心が配線格子線L<sub>LL1</sub>と配線格子線L<sub>LL2</sub>との交点に配置されることになるが、本実施の形態4では、Cu配線33Nに比べて相対的に幅の大きいCu配線33W上に配置されるプラグ43Pの配置位置の設定については、コンピュータによる自動設定を行わずに手動で行うものとする。すなわち、プラグ43Pの中心が配線格子線L<sub>LL1</sub>上に配置されないようにプラグ43Pの配置位置を設定するものである。この時、プラグ43Pの中心と配線格子線L<sub>LL1</sub>とを、プラグ43Pの形成位置合わせ余裕となる必要最小限の距離以上（たとえばプラグ43Pの径の1/2程度以上）離間させ、平面においてプラグ43Pの配置位置をCu配線33Wの幅方向における端部へ近づける。また、プラグ43Pは、可能な限りCu配線33Wの幅方向における端部に近い位置で目外れのないようにCu配線33Wと接続するように配置する。ストレスマイグレーションによる導通不良の原因となる空孔はCu配線33Wの膜中に多く存在し、プラグ43PとCu配線33Wとの界面を中心として全方向から集まってくるものであるが、このようなプラグ43Pの配置位置においては、Cu配線33Wの幅方向における端部からの空孔の集中を防ぐことができる。それにより、Cu配線33WとCu配線43との間でストレスマイグレーションによる導通不良が発生することを抑制することができる。

【0081】

上記のような本実施の形態5においても、前記実施の形態1～4と同様の効果を得ることができる。

【0082】

以上、本発明者によってなされた発明を発明の実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることは言うまでもない。

【0083】

前記実施の形態1～5のそれぞれを、他の実施の形態1～5の一つまたは2以上の複数と組み合わせてもよい。

【0084】

前記実施の形態においては、本発明をCMOS-LSIにおける埋め込み配線（Cu配線）および埋め込み配線間を接続するプラグの製造工程に適用した場合について例示したが、CMOS-LSI以外にもSRAM（Static Random Access Memory）における埋め込み配線および埋め込み配線間を接続するプラグの製造工程に適用してもよい。

【0085】

上記実施の形態によって得られる効果を簡単に説明すれば以下の通りである。

（1）絶縁膜をエッティングして形成した配線溝にCuを主成分とする導電性膜を埋め込んでなる埋め込み配線を複数層に渡って形成する際に、下層の埋め込み配線（第1埋め込み配線）と上層の埋め込み配線（第2埋め込み配線）とを電気的に接続するプラグ（第1プラグ）を複数個配置することにより、1個のプラグと下層の埋め込み配線との界面にストレスマイグレーションによる空孔の集中を防ぐことができるので、下層の埋め込み配線と上層の埋め込み配線との間での導通不良を防ぐことができる。

10

20

30

40

50

(2) 絶縁膜をエッチングして形成した配線溝にCuを主成分とする導電性膜を埋め込んでなる埋め込み配線を複数層に渡って形成する際に、下層の埋め込み配線（第1埋め込み配線）と上層の埋め込み配線（第2埋め込み配線）とを電気的に接続するプラグ（第1プラグ）の径を拡大し、プラグと下層の配線とが接する面積を拡大することにより、プラグと下層の埋め込み配線との界面にストレスマイグレーションによって空孔が集中した場合でも、下層の埋め込み配線と上層の埋め込み配線との間での導通不良を防ぐことができる。

(3) 絶縁膜をエッチングして形成した配線溝にCuを主成分とする導電性膜を埋め込んでなる埋め込み配線を複数層に渡って形成する際に、下層の埋め込み配線（第1埋め込み配線）と上層の埋め込み配線（第2埋め込み配線）とを電気的に接続するプラグ（第1プラグ）を下層の埋め込み配線の端部に近い位置で下層の埋め込み配線と接続させることによって、ストレスマイグレーションによってプラグと下層の埋め込み配線との界面に集中する空孔の量を低減できるので、下層の埋め込み配線と上層の埋め込み配線との間での導通不良を防ぐことができる。10

#### 【0086】

#### 【発明の効果】

本願によって開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下の通りである。

#### 【0087】

埋め込み配線と底部にて接続するプラグとその埋め込み配線との界面でのストレスマイグレーションによる導通不良を防ぐことができる。20

#### 【図面の簡単な説明】

【図1】本発明の実施の形態1である半導体集積回路装置の製造方法を説明する要部平面図である。

【図2】本発明の実施の形態1である半導体集積回路装置の製造方法を説明する要部断面図である。

【図3】図1に続く半導体集積回路装置の製造工程中の要部平面図である。

【図4】図2に続く半導体集積回路装置の製造工程中の要部断面図である。

【図5】図4に続く半導体集積回路装置の製造工程中の要部断面図である。

【図6】本発明の実施の形態1である半導体集積回路装置の製造工程中の要部平面図である。30

【図7】本発明の実施の形態1である半導体集積回路装置の製造工程中の要部断面図である。

【図8】図6に続く半導体集積回路装置の製造工程中の要部平面図である。

【図9】図7に続く半導体集積回路装置の製造工程中の要部断面図である。

【図10】本発明者らが実験により求めた上層配線と下層配線との間の抵抗変動率と抵抗変動率の測定点の累積度数との関係を下層配線の幅毎に示した説明図である。

【図11】本発明者らが計算により求めた上層配線と下層配線との間のストレスマイグレーション寿命と累積不良率との関係を上層配線と下層配線との間のプラグの数毎に示した説明図である。

【図12】本発明者らが計算により求めた上層配線と下層配線との間の累積不良率と経過時間との関係を示した説明図である。

【図13】本発明者らが高温放置試験により求めた上層配線と下層配線との間の抵抗変動率と抵抗変動率の測定点の累積度数との関係を上層配線と下層配線との間のプラグの数毎に示した説明図である。

【図14】本発明者らが高温放置試験により求めた、上層配線と下層配線との間のプラグの配置位置に起因する上層配線と下層配線との間の抵抗変動率と抵抗変動率の測定点の累積度数との関係を示した説明図である。

【図15】本発明者らが高温放置試験により求めた、上層配線と下層配線との間のプラグの配置位置に起因する上層配線と下層配線との間の抵抗変動率と抵抗変動率の測定点の累4050

積度数との関係を示した説明図である。

【図16】本発明者らが高温放置試験により求めた、上層配線と下層配線との間のプラグの径に起因する上層配線と下層配線との間の抵抗変動率と抵抗変動率の測定点の累積度数との関係を示した説明図である。

【図17】本発明者らが高温放置試験により求めた、上層配線と下層配線との間のプラグの径に起因する上層配線と下層配線との間の抵抗変動率と抵抗変動率の測定点の累積度数との関係を示した説明図である。

【図18】本発明の実施の形態1である半導体集積回路装置の製造工程中の要部平面図である。

【図19】図18中のD-D線に沿った断面図である。

10

【図20】本発明の実施の形態1である半導体集積回路装置の製造工程中の要部平面図である。

【図21】本発明の実施の形態1である半導体集積回路装置の製造工程中の要部平面図である。

【図22】図21中のD-D線に沿った断面図である。

【図23】本発明の実施の形態1である半導体集積回路装置の製造工程中の要部平面図である。

【図24】本発明の実施の形態1である半導体集積回路装置の製造工程中の要部平面図である。

【図25】本発明の実施の形態1である半導体集積回路装置の製造工程中の要部平面図である。

20

【図26】本発明の実施の形態1である半導体集積回路装置の製造工程中の要部平面図である。

【図27】本発明の実施の形態1である半導体集積回路装置の製造工程中の要部平面図である。

【図28】本発明の実施の形態1である半導体集積回路装置の製造工程中の要部平面図である。

【図29】本発明の実施の形態1である半導体集積回路装置の製造工程中の要部平面図である。

【図30】本発明の実施の形態1である半導体集積回路装置の製造工程中の要部平面図である。

30

【図31】本発明の実施の形態1である半導体集積回路装置の製造工程中の要部平面図である。

【図32】本発明の実施の形態1である半導体集積回路装置の製造工程中の要部平面図である。

【図33】本発明の実施の形態1である半導体集積回路装置の製造工程中の要部平面図である。

【図34】本発明の実施の形態2である半導体集積回路装置の製造工程中の要部平面図である。

【図35】本発明の実施の形態2である半導体集積回路装置の製造工程中の要部断面図である。

40

【図36】本発明の実施の形態2である半導体集積回路装置の要部等価回路図である。

【図37】本発明の実施の形態3である半導体集積回路装置の製造工程中の要部平面図である。

【図38】本発明の実施の形態4である半導体集積回路装置の製造工程中の要部平面図である。

【図39】本発明の実施の形態4である半導体集積回路装置の製造工程中の要部平面図である。

【図40】本発明の実施の形態5である半導体集積回路装置の製造工程中の要部平面図である。

50

## 【符号の説明】

|      |                                 |    |

|------|---------------------------------|----|

| 1    | 半導体基板                           |    |

| 3    | 素子分離領域                          |    |

| 4    | n型アイソレーション領域                    |    |

| 5    | p型ウエル                           |    |

| 6    | n型ウエル                           |    |

| 7    | ゲート酸化膜                          |    |

| 8    | ゲート電極                           |    |

| 11   | n <sup>+</sup> 型半導体領域(ソース、ドレイン) |    |

| 12   | p <sup>+</sup> 型半導体領域(ソース、ドレイン) | 10 |

| 12A  | p型引き出し層                         |    |

| 13   | シリサイド層                          |    |

| 15   | 窒化シリコン膜                         |    |

| 16   | 酸化シリコン膜                         |    |

| 17   | コンタクトホール                        |    |

| 18   | プラグ                             |    |

| 19   | 炭化シリコン膜                         |    |

| 20   | 層間絶縁膜                           |    |

| 22   | 配線溝                             |    |

| 24   | 埋め込み配線                          | 20 |

| 24A  | バリアメタル膜                         |    |

| 24B  | W膜                              |    |

| 25   | 炭窒化シリコン膜                        |    |

| 26   | 層間絶縁膜                           |    |

| 28   | 炭化シリコン膜(第1絶縁膜)                  |    |

| 29   | 層間絶縁膜(第1絶縁膜)                    |    |

| 31   | 接続孔(第1孔部)                       |    |

| 32   | 配線溝(第1配線溝、第3配線溝)                |    |

| 33A  | バリアメタル膜                         |    |

| 33B  | Cu膜(第1導電性膜)                     | 30 |

| 33P  | プラグ                             |    |

| 33N  | Cu配線(第3埋め込み配線)                  |    |

| 33W  | Cu配線(第1埋め込み配線)                  |    |

| 35   | 炭窒化シリコン膜(第2絶縁膜)                 |    |

| 36   | 層間絶縁膜(第2絶縁膜)                    |    |

| 38   | 炭化シリコン膜(第3絶縁膜)                  |    |

| 39   | 層間絶縁膜(第3絶縁膜)                    |    |

| 41   | 接続孔(第1孔部)                       |    |

| 42   | 配線溝(第2配線溝)                      |    |

| 43   | Cu配線(第2埋め込み配線)                  | 40 |

| 43A  | バリアメタル膜                         |    |

| 43B  | Cu膜(第3導電性膜)                     |    |

| 43P  | プラグ(第1プラグ、第2プラグ)                |    |

| 43PR | プラグ(第1プラグ)                      |    |

| 43R  | Cu配線(第2埋め込み配線)                  |    |

| CELL | セル                              |    |

| LL1  | 配線格子線(第1配線格子線)                  |    |

| LL2  | 配線格子線(第2配線格子線)                  |    |

| Qn   | nチャネル型MISFET                    |    |

| Qp   | pチャネル型MISFET                    | 50 |

## R 修正用の回路

【 図 1 】

【 図 2 】

【図3】

図3

【図4】

図4

【図5】

図5

【図6】

図6

【 図 7 】

〔 囮 9 〕

【 义 8 】

【 図 1 0 】

☒ 10

【図 1 1】

【図 1 2】

【図 1 4】

【図 1 5】

【図 1 3】

【図 1 6】

【図 1 7】

【図18】

【図20】

【図19】

【図21】

【図23】

【図22】

【図24】

図24

【図26】

図26

【図25】

図25

【図27】

図27

【図29】

図29

【図28】

図28

【図30】

【 図 3 1 】

### 【図34】

### 【図32】

【 図 3 3 】

【 図 3 5 】

【図36】

図36

【図37】

図37

【図39】

【図38】

図38

【図40】

## フロントページの続き

(72)発明者 竹内 幹

東京都小平市上水本町五丁目 20 番 1 号 株式会社日立製作所半導体グループ内

(72)発明者 青木 英雄

東京都青梅市新町六丁目 16 番地の 3 株式会社日立製作所デバイス開発センタ内

(72)発明者 山口 日出

東京都青梅市新町六丁目 16 番地の 3 株式会社日立製作所デバイス開発センタ内

(72)発明者 大島 隆文

東京都青梅市新町六丁目 16 番地の 3 株式会社日立製作所デバイス開発センタ内

(72)発明者 津国 和之

東京都小平市上水本町五丁目 20 番 1 号 株式会社日立製作所半導体グループ内

F ターム(参考) 5F033 HH11 HH12 HH18 HH19 HH21 HH27 HH32 HH33 HH34 JJ01

JJ11 JJ12 JJ18 JJ19 JJ21 JJ27 JJ32 JJ33 JJ34 KK04

KK11 KK12 KK18 KK19 KK21 KK25 KK27 KK32 KK33 KK34

LL04 MM01 MM02 MM07 MM12 MM13 NN06 NN07 NN33 NN34

PP06 PP15 PP21 PP22 PP27 PP28 PP33 QQ08 QQ09 QQ10

QQ11 QQ19 QQ25 QQ31 QQ37 QQ48 QQ58 QQ59 QQ65 QQ70

QQ73 QQ75 RR01 RR04 RR06 RR09 RR11 RR15 SS02 SS03

SS11 SS15 SS21 TT02 TT08 UU04 VV12 XX00 XX06 XX14

XX24 XX28 XX37

5F064 BB02 BB13 CC12 EE09 EE12 EE17 EE22 EE26 EE27 EE32

EE41 EE52 HH06