# (19) United States

# (12) Patent Application Publication (10) Pub. No.: US 2005/0026369 A1 Noble et al.

Feb. 3, 2005 (43) Pub. Date:

### (54) METHOD AND APPARATUS ON (110) SURFACES OF SILICON STRUCTURES WITH CONDUCTION IN THE DIRECTION

(75) Inventors: Wendell P. Noble, Milton, VT (US); Leonard Forbes, Corvallis, OR (US); Alan R. Reinberg, Westport, CT (US)

> Correspondence Address: SCHWEGMAN, LUNDBERG, WOESSNER & KLUTH, P.A. P.O. BOX 2938 MINNEAPOLIS, MN 55402 (US)

(73) Assignee: Micron Technology, Inc.

10/930,213 (21) Appl. No.:

(22) Filed: Aug. 31, 2004

#### Related U.S. Application Data

(62) Division of application No. 10/463,261, filed on Jun. 17, 2003, which is a division of application No. 09/850,764, filed on May 8, 2001, now Pat. No. 6,580,154, which is a division of application No. 09/386,181, filed on Aug. 31, 1999, now Pat. No. 6,245,615.

#### Publication Classification

- (51) **Int. Cl.**<sup>7</sup> ...... **H01L** 29/94; H01L 21/336

- (57)**ABSTRACT**

Improved methods and structures are provided that are lateral to surfaces with a (110) crystal plane orientation such that an electrical current of such structures is conducted in the <110> direction. Advantageously, improvements in hole carrier mobility of approximately 50% can be obtained by orienting the structure's channel in a (110) plane such that the electrical current flow is in the <110> direction. Moreover, these improved methods and structures can be used in conjunction with existing fabrication and processing techniques with minimal or no added complexity.

FIG. 1 (PRIOR ART)

FIG. 2 (PRIOR ART)

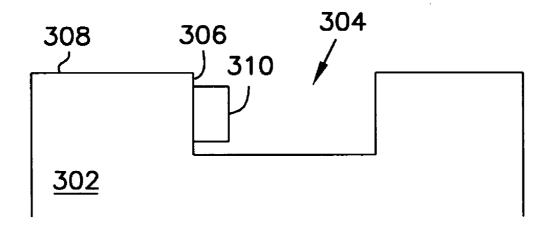

FIG. 3A

FIG. 3B

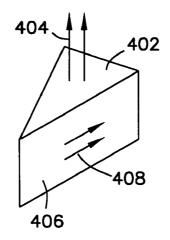

FIG. 4

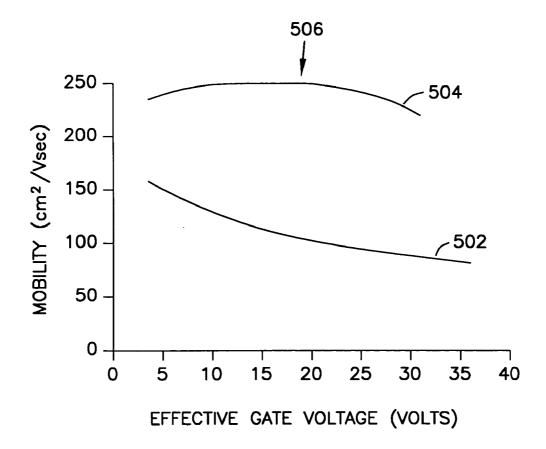

FIG. 5

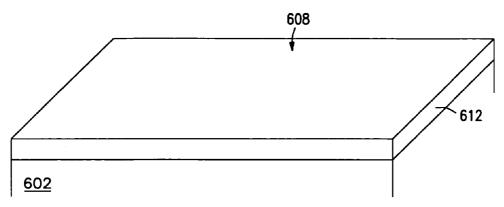

FIG. 6A

604a 608 612 604b 602 634 606 610 634

FIG. 6C

FIG. 7A

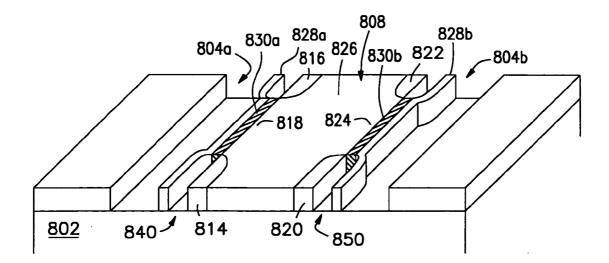

FIG. 8A

FIG. 9

FIG. 10

FIG. 11

# METHOD AND APPARATUS ON (110) SURFACES OF SILICON STRUCTURES WITH CONDUCTION IN THE DIRECTION

#### RELATED APPLICATIONS

[0001] This application is a Divisional of U.S. Ser. No. 10/463,261, filed Jun. 17, 2003, which application is a Divisional of U.S. Ser. No. 09/850,764, filed May 8, 2001, which is a Divisional of U.S. Ser. No. 09/386,181 filed Aug. 31, 1999, now U.S. Pat. No. 6,245,615. This application is related to co-pending and co-filed application Ser. No. 09/386,185, attorney docket number 303.604US1, filed on Aug. 31, 1999, entitled "Multiple Oxide Thicknesses for Merged Memory and Logic Applications" by inventors Leonard Forbes and Wendell P. Noble, now U.S. Pat. No. 6,383,871, which is hereby incorporated by reference. This application is further related to co-pending and co-filed application Ser. No. 09/386,313, attorney docket number M4065.180/P180, filed on Aug. 31, 1999, entitled "Vertical Sub-Micron CMOS Transistors on (110), (111), (311), (511), and Higher Order Surfaces of Bulk, SOI and Thin Film Structures and Method of Forming Same," by inventors Leonard Forbes, Wendell P. Noble and Alan R. Reinberg, which is hereby incorporated by reference. This application is also related to co-pending and co-filed application Ser. No. 09/386,315, attorney docket number M4065.0204/P204, filed on Aug. 31, 1999, entitled "Method for Fabricating CMOS Transistors Having Matching Characteristics and Apparatus Formed Thereby," by inventors Leonard Forbes and Wendell P. Noble, which is hereby incorporated by reference.

#### FIELD OF THE INVENTION

[0002] The present invention relates to integrated circuits, and more particularly, to a method, a structure and a system for providing semiconductor devices on (110) surfaces with conduction in the <110> direction.

## BACKGROUND OF THE INVENTION

[0003] In general, the standard silicon wafer crystal orientation for VLSI (Very Large Scale Integration) is the (100) orientation. This surface orientation was chosen over the previously used (111) crystal orientation because of its comparatively low surface state density on thermally oxidized surfaces. In particular, a (111) crystal orientation has a surface state charge density of approximately 5×10<sup>11</sup> e/centimeters<sup>2</sup> (cm<sup>2</sup>) in comparison with a (100) crystal orientation which has a surface state charge density of approximately 9×10<sup>10</sup> e/cm<sup>2</sup>.

[0004] Surface state density was a particularly important consideration for n-channel Metal Oxide Semiconductor (NMOS) technologies because the higher this surface state density level the more difficult the controlling of active and parasitic device threshold voltages for devices using such technologies. For (110) surfaces, the surface state charge density is approximately 2×10<sup>11</sup> e/cm² which is approximately twice the density level for (100) surfaces. In present day technology, this difference in density levels translates into less than 0.09 volts offset in active device threshold voltage and is readily compensated by a surface threshold voltage ion implant. A further benefit to a lower surface state charge density for NMOS devices is that the electron mobility in inversion layers is greater on the (100) surface than on other lower order planes.

[0005] However, for modern day complimentary metal oxide semiconductor (CMOS) technology involving submicron devices, a different set of trade-offs are involved. For such short channel devices, the NMOS devices operate largely in velocity saturation resulting in a source to drain current which is independent of crystal orientation.

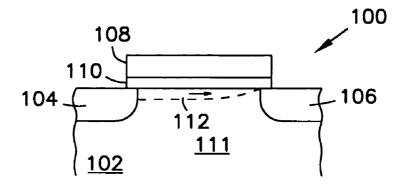

[0006] In contrast as illustrated in FIGS. 1 and 2, p-channel Metal Oxide Semiconductor (PMOS) devices are less likely to operate in velocity saturation, and therefore are more dependent on the choice of crystal orientation around inversion layer hole mobility. In particular, FIG. 1 includes a transistor 100, which can be either an NMOS or PMOS transistor. Transistor 100 is comprised of a silicon wafer 102, a source region 104, a drain region 106, a gate 108, an oxide layer 110, a body region 111 and a channel region 112 between the source region 104 and the drain region 106. As is well-known in the art, a voltage differential between the source region 104 and the drain region 106 induces an electric field across the channel region 112. A gate potential applied to the gate 108 can create an inversion layer in the body region 111 allowing the channel region 112 to form between the source region 104 and the drain region 106. This electric field is expressed in terms of the voltage differential between the source region 104 and the drain region 106 per the length of the channel region 112.

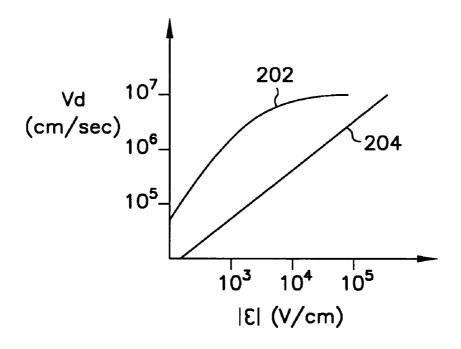

[0007] FIG. 2 illustrates a graph of the drift velocity for carriers (i.e., either holes or electrons) across the channel region 112, expressed in cm/second (sec), versus an average source-to-drain electric field, expressed in volts/cm. In particular, a plot 202 is the graphical plot of the drift velocity of electrons in the channel of an NMOS versus the electric field generated by the voltage differential between the source region 104 and the drain region 106. Additionally, a plot 204 is the graphical plot of the drift velocity of holes in the channel of a PMOS versus the electric field generated by the voltage differential between the source region 104 and the drain region 106. As illustrated, the plot 202 reaches velocity saturation at approximately  $10^4$  V/cm (i.e., the point in which the graphical plot flattens). In contrast in the graph of FIG. 2, the plot 204 has not reached the point of velocity saturation, even at 10<sup>5</sup> V/cm. Thus, a PMOS device that uses holes as carriers is more dependent on the choice of crystal orientation for inversion hole mobility.

[0008] Currently, surfaces with a (110) crystal plane orientation have been explored in the planar bulk and Silicon On Insulator (SOI) technologies by using (110) substrate wafers or causing the recrystallization of the surface of a substrate wafer to have a (110) crystal orientation. However, these structures and methods require re-tooling of crystal growth mechanisms used in conjunction with the standard (100) crystalline plane orientation and/or otherwise introduce costly, additional processing steps and procedures.

[0009] Thus, there is a need for structures and methods which improve carrier mobility in semiconductor devices and which do so without the introduction of costly additional processing steps or which require any re-tooling of standard crystal growth mechanisms. For these and other reasons there is a need for the present invention.

## SUMMARY OF THE INVENTION

[0010] The above-mentioned problems and limitations associated with carrier mobility in semiconductor devices

and other problems are addressed by the present invention and will be understood by reading and studying the following specification. Structures and methods are described which accord improved benefits.

[0011] Improved methods and structures are provided that are lateral to surfaces with a (110) crystal plane orientation in which an electrical current of such structures is in a <110> direction. Advantageously, improvements in carrier mobility of approximately 50% can be obtained by orienting the structure's channel in a (110) plane such that the electrical current flow is in the <110> direction. Moreover, these improved methods and structures can be used in conjunction with existing fabrication and processing techniques with minimal or no added complexity.

[0012] Embodiments of a method of forming an integrated circuit include forming a trench in a silicon wafer. A trench wall of the trench has a (110) crystal plane orientation. A semiconductor device is also formed lateral to the trench wall such that the semiconductor device is capable of conducting an electrical current in a <110> direction.

[0013] One method of the present invention provides for forming an integrated circuit. Another method includes forming an integrated circuit including an array of MOS-FETs while another method includes forming an integrated circuit including a number of lateral transistors. Another method includes forming a semiconductor device. Moreover, other embodiments provide for forming MOSFET devices (e.g., PMOS and NMOS devices). The present invention also includes structures as well as systems incorporating such structures all formed according to the methods provided in this application.

[0014] These and other embodiments, aspects, advantages, and features of the present invention will be set forth in part in the description which follows, and in part will become apparent to those skilled in the art by reference to the following description of the invention and referenced drawings or by practice of the invention. The aspects, advantages, and features of the invention are realized and attained by means of the instrumentalities, procedures, and combinations particularly pointed out in the appended claims.

#### BRIEF DESCRIPTION OF THE DRAWINGS

[0015] FIG. 1 is a cross-sectional view of a MOSFET device.

[0016] FIG. 2 is a graph that illustrates a drift velocity of carriers of a MOSFET device vs. average source-to-drain electric field for the MOSFET device.

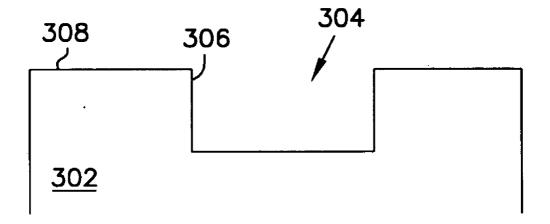

[0017] FIGS. 3A-3B illustrate an embodiment of a process of fabrication of conduction regions on a silicon wafer according to the teachings of the present invention.

[0018] FIG. 4 is a silicon structure illustrating embodiments of crystal plane orientations of surfaces and electrical current flow directions.

[0019] FIG. 5 is a graph that illustrates inversion layer hole mobility vs. effective gate voltage.

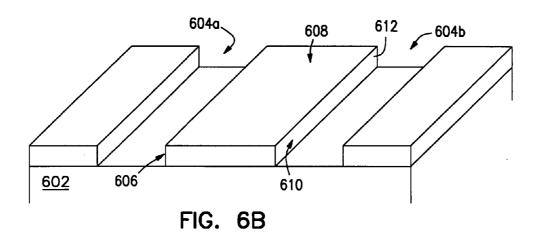

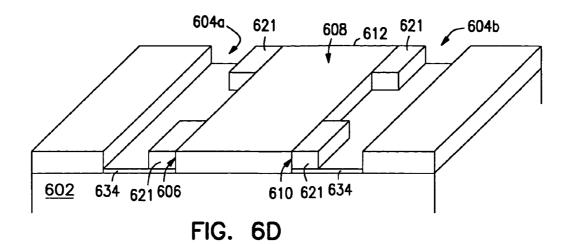

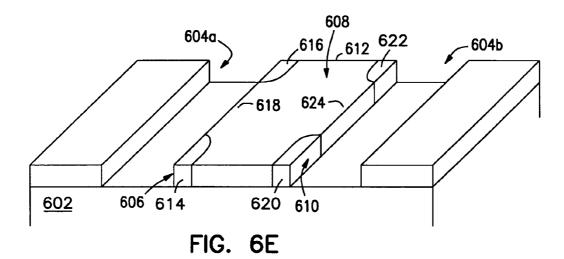

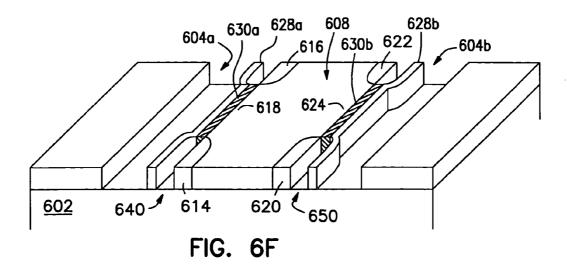

[0020] FIGS. 6A-6F illustrate an embodiment of a process of fabrication of conduction regions on a silicon wafer according to the teachings of the present invention.

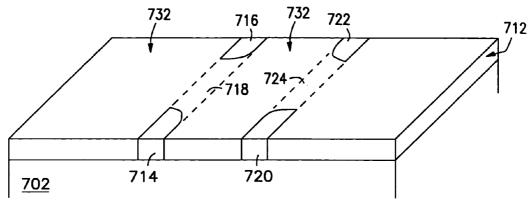

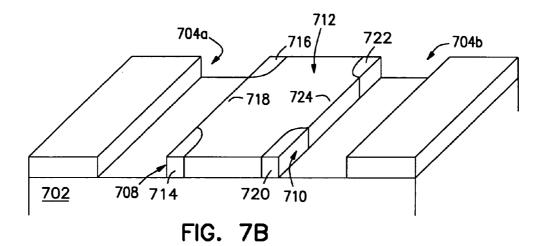

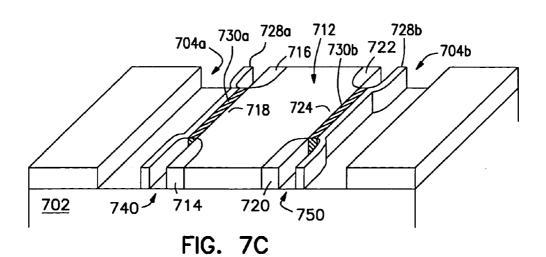

[0021] FIGS. 7A-7C illustrate another embodiment of a process of fabrication of conduction regions on a silicon wafer according to the teachings of the present invention.

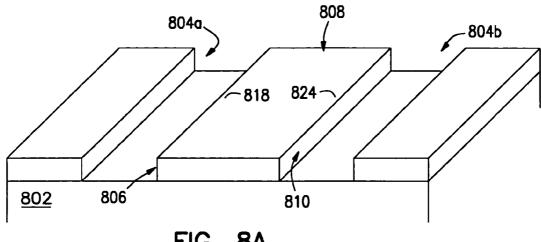

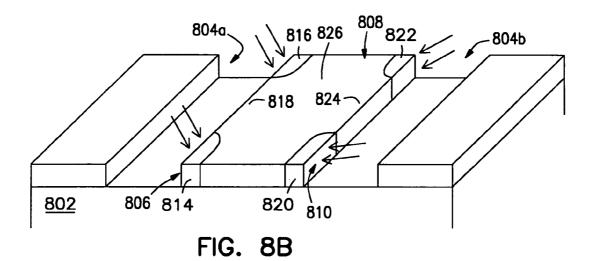

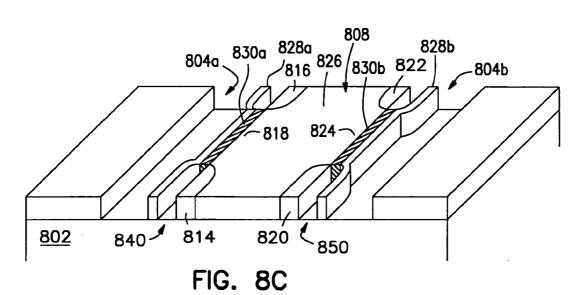

[0022] FIGS. 8A-8C illustrate another embodiment of a process of fabrication of conduction regions on a silicon wafer according to the teachings of the present invention.

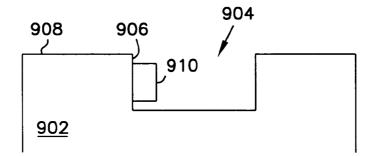

[0023] FIG. 9 is a cross-sectional view of an embodiment of an integrated circuit according to the teachings of the present invention.

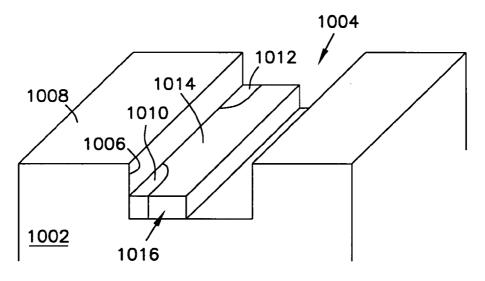

[0024] FIG. 10 is a cross-sectional view of an embodiment of a semiconductor device according to the teachings of the present invention.

[0025] FIG. 11 is a block diagram which illustrates an embodiment of a system according to teachings of the present invention.

#### DETAILED DESCRIPTION

[0026] In the following detailed description of the invention, reference is made to the accompanying drawings which form a part hereof, and in which is shown, by way of illustration, specific embodiments in which the invention may be practiced. In the drawings, like numerals describe substantially similar components throughout the several views. These embodiments are described in sufficient detail to enable those skilled in the art to practice the invention. Other embodiments may be utilized and structural, logical, and electrical changes may be made without departing from the scope of the present invention.

[0027] The terms wafer and substrate used in the following description include any structure having an exposed surface with which to form the integrated circuit (IC) structure of the invention. The term substrate is understood to include semiconductor wafers. The term substrate is also used to refer to semiconductor structures during processing, and may include other layers that have been fabricated thereupon. Both wafer and substrate include doped and undoped semiconductors, epitaxial semiconductor layers supported by a base semiconductor or insulator, as well as other semiconductor structures well known to one skilled in the art. The term conductor is understood to include semiconductors, and the term insulator is defined to include any material that is less electrically conductive than the materials referred to as conductors. The following detailed description is, therefore, not to be taken in a limiting sense, and the scope of the present invention is defined only by the appended claims, along with the full scope of equivalents to which such claims are entitled.

[0028] In particular, an illustrative embodiment of the present invention includes a method of forming an integrated circuit. The method includes forming a trench in a silicon wafer. A trench wall of the trench has a (110) crystal plane orientation. Additionally, a semiconductor device is formed lateral to the trench wall. Moreover, the semiconductor device is capable of conducting an electrical current in a <110> direction.

[0029] Another embodiment of the present invention includes a method of forming a semiconductor device. This method includes forming a first conductive region of a first type in a trench of a silicon wafer. In particular, the first conductive region of the first type is lateral to a trench wall

of the trench with the trench wall having a (110) crystal plane orientation. Moreover, a second conductive region of the first type is formed in the trench. The second conductive region of the first type is formed lateral to the trench wall. The method also includes forming a conductive region of a second type in the trench. In particular, this conductive region of the second type is lateral to the trench wall and between the first and second conductive regions of the first type. Additionally, an electrical current is capable of flowing between the first and the second conductive regions of the first type in a <110> direction.

[0030] An alternative method embodiment of the present invention includes forming an integrated circuit which includes a number of lateral transistors. The method includes forming a trench in a silicon wafer, which has a top surface having a (100) crystal plane orientation. Additionally, the trench has a trench wall with a (110) crystal plane orientation. The method also includes forming a first conductive region in a first portion of the trench. In particular, this first conductive region is lateral to the trench wall. Moreover, a second conductive region is formed in a second portion of the trench such that this second conductive region is lateral to the trench wall. The method also includes forming a third conductive region in a third portion of the trench. This third conductive region is lateral to the trench wall and between the first and second conductive regions. Moreover, an electrical current is capable of flowing between the first conductive region and the second conductive region in a <110>

[0031] Another method embodiment of the present invention includes forming a p-channel Metal Oxide Semiconductor Field Effect Transistor (p-MOSFET) device. This method includes forming a trench in a silicon wafer such that the trench includes a trench wall having a (110) crystal plane orientation. Additionally, a first conductive p-type region is formed in the trench of the silicon wafer. In particular, this first conductive p-type region is lateral to the trench wall of the trench. The method also includes forming a second conductive p-type region in the trench such that the second conductive p-type region is lateral to the trench wall. Further a conductive n-type region is formed in the trench. This conductive n-type region is formed lateral to the trench wall and between the first and second conductive p-type regions. Additionally, the p-MOSFET device is configured for conducting an electrical current between the first and the second conductive p-type regions in a direction lateral to the trench

[0032] An additional method embodiment of the present invention includes forming an integrated circuit including an array of Metal Oxide Semiconductor Field Effect Transistors (MOSFETs). The method includes forming a number of trenches in a silicon wafer such that the number of trenches have a trench wall in a (110) crystalline plane orientation. The method also includes forming a number of spaced MOSFETs in each trench. The formation of the number of spaced MOSFETs includes forming a first conductive p-type region in the trench of the silicon wafer such that the first conductive p-type region is lateral to the trench wall of the trench. Further, a second conductive p-type region is formed in the trench such that the second conductive p-type region is lateral to the trench wall. The formation of the number of spaced MOSFETs also includes forming a conductive n-type region in the trench such that the conductive n-type region is lateral to the trench wall and between the first and the second conductive p-type regions. Additionally, an electrical current is capable of flowing between the first and the second p-type regions in a <110> direction.

[0033] An apparatus embodiment of the present invention includes an integrated circuit. The integrated circuit includes a trench wall in a silicon wafer in which the trench wall has a (110) crystal plane orientation. The integrated circuit also includes a semiconductor device lateral to the trench wall. Moreover, the semiconductor device is configured to conduct an electrical current in the <110> direction.

[0034] Another apparatus embodiment of the present invention includes a semiconductor device. The semiconductor device includes a first conductive region of a first type in a trench of a silicon wafer. This first conductive region of the first type is lateral to a trench wall of the trench, and the trench wall has a (110) crystal plane orientation. The semiconductor device also includes a second conductive region of the first type in the trench. This second conductive region of the first type is lateral to the trench wall. Additionally, the semiconductor device includes a conductive region of a second type in the trench. This conductive region of the second type is lateral to the trench wall and between the first and second conductive regions of the first type. Moreover, the semiconductor device is designed to conduct an electrical current between the first and second conductive regions of the first type in a <110> direction.

[0035] An alternative apparatus embodiment of the present invention includes a dynamic random access memory (DRAM). The DRAM includes an array of lateral transistors formed on a trench wall of a trench in a silicon wafer such that the silicon wafer has a top surface in a (100) crystal plane orientation and the trench wall has a (110) crystal plane orientation. Additionally, each lateral transistor includes a first conductive region in a first portion of the trench wall. Each lateral transistor also includes a second conductive region in a second portion of the trench wall. Further, each lateral transistor includes a third conductive region in a third portion of the trench wall, such that the third conductive region is between the first and second conductive regions. Additionally, each lateral transistor is configured to conduct an electrical current between the first conductive regions and the second conductive region in a <110> direction. The DRAM also includes a wordline coupled to a gate of each lateral transistor formed on the trench wall of the trench of the silicon wafer.

[0036] Another apparatus embodiment of the present invention includes a p-channel Metal Oxide Semiconductor Field Effect Transistor (p-MOSFET) device. The p-MOS-FET device includes a first conductive p-type region in a trench of a silicon wafer. This first conductive p-type region is lateral to a trench wall of the trench with the trench wall having a (110) crystal plane orientation. The p-MOSFET device also includes a second conductive p-type region in the trench in which the second conductive p-type region is lateral to the trench wall. Additionally, the p-MOSFET device includes a conductive n-type region in the trench. This conductive n-type region is lateral to the trench wall and between the first and second conductive p-type regions. Moreover, an electrical current is capable of flowing between the first and second conductive p-type regions in a direction lateral to the trench wall.

[0037] Another apparatus embodiment of the present invention includes an array of Metal Oxide Semiconductor Field Effect Transistors (MOSFETs). The array of MOS-FETs includes a number of trenches formed in a silicon wafer. The array of MOSFETs also includes a number of spaced MOSFETs in each trench. Each MOSFET includes a first conductive p-type region in a trench of the silicon wafer such that the first conductive p-type region is lateral to a trench wall of the trench. The trench wall has a (110) crystal plane orientation. Each MOSFET also includes a second conductive p-type region in the trench such that the second conductive p-type region is lateral to the trench wall. Further, each MOSFET includes a conductive n-type region in the trench such that the conductive n-type region is lateral to the trench wall and between the first and second conductive p-type regions. Additionally, an electrical current is capable of flowing between the first and second conductive p-type regions in a <110> direction.

[0038] An alternative apparatus embodiment of the present invention includes an electronic system. This electronic system includes a processor. This electronic system also includes an integrated circuit coupled to the processor. In particular, the integrated circuit is formed on a silicon wafer. The silicon wafer includes a trench wall that has a (110) crystal plane orientation. The silicon wafer also includes a semiconductor device lateral to the trench wall. The semiconductor device is capable of conducting an electrical current in a <110> direction.

[0039] Another apparatus embodiment of the present invention includes an electronic system. The electronic system includes a processor as well as a semiconductor device coupled to the processor. The semiconductor device includes a first conductive region of a first type in a trench of a silicon wafer. In particular, the first conductive region of the first type is lateral to a trench wall of the trench, and the trench wall has a (110) crystal plane orientation. The semiconductor device also includes a second conductive region of the first type in the trench. This second conductive region of the first type is lateral to the trench wall. Additionally, the semiconductor device includes a conductive region of a second type in the trench. In particular, the conductive region of the second type is lateral to the trench wall and between the first and second conductive regions of the first type. Moreover, an electrical current is capable of flowing between the first and second conductive regions of the first type in a <110> direction.

[0040] An alternative apparatus embodiment of the present invention includes an electronic system. The electronic system includes a processor as well as a memory coupled to the processor. The memory includes an array of lateral transistors formed on a trench wall of a trench in a silicon wafer. The silicon wafer has a top surface with a (100) crystal plane orientation, and the trench wall has a (110) crystal plane orientation. Additionally, each lateral transistor in the array of lateral transistors includes a first conductive region in a first portion of the trench in which the first conductive region is lateral to the trench wall. Moreover, each lateral transistor includes a second conductive region in a second portion of the trench. In particular, this second conductive region is lateral to the trench wall. Each lateral transistor also includes a third conductive region in a third portion of the trench. This third conductive region is lateral to the trench wall and between the first and second conductive regions. Moreover, an electrical current is capable of flowing between the first conductive region and the second conductive region in a <110> direction.

[0041] FIGS. 3A-3B illustrate an embodiment of a process of fabrication of conduction regions on a silicon wafer according to the teachings of the present invention. The sequence can be followed as a method of forming an integrated circuit, as a method of forming a semiconductor device, as a method of forming an integrated circuit that includes a number of lateral transistors and as a method of forming a MOSFET device.

[0042] FIG. 3A shows the structure after the first sequence of processing. A trench 304 is formed in a silicon wafer 302 using photolithography and etching techniques. One of ordinary skill in the art will understand the manner in which photolithography and etching techniques can be used to form a trench in a silicon wafer. According to the teachings of the present invention, the trench 304 is specifically formed such that a trench wall 306 of the trench 304 has a (110) crystal plane orientation. In one embodiment, the silicon wafer 302 has a top surface 308 that has a (100) crystal plane. However, it is important to appreciate that the top surface 308 may have other specific crystal plane orientations (e.g., (111) crystal plane orientation). In one embodiment, the silicon wafer 302 includes a bulk silicon material. In an alternative embodiment, the silicon wafer 302 includes a Silicon On Insulator (SOI) material.

[0043] FIG. 3B shows the structure after the next sequence of processing. A semiconductor device 310 is formed in the trench 304 using standard photolithography, etching, ion implantation and other processing techniques. In particular, the semiconductor device 310 is formed lateral to the trench wall 306. Moreover, in one embodiment, the semiconductor device 310 is formed in the trench 304 such that it is capable of conducting an electrical current in a <110> direction. In one embodiment, the electrical current is capable of conducting an electrical current lateral to the trench wall 306. In one embodiment, the semiconductor device 310 is a MOSFET device. In one such embodiment, the semiconductor device 310 is a PMOS device. In another such embodiment, the semiconductor device 310 is an NMOS device.

[0044] FIG. 4 illustrates one embodiment wherein an electrical current flow in a <110> direction. In particular, FIG. 4 is a silicon structure having a top surface 402. According to the teachings of the present invention, the top surface 402 has a (100) crystal plane orientation. FIG. 4 also illustrates a direction 404 coming from the top surface 402, which is essentially perpendicular to such surface. Electrical current flow in direction 404 is in a <100> direction. Additionally, the silicon structure of FIG. 4 has a side surface 406, which has a (110) crystal plane orientation. FIG. 4 also illustrates a direction 408, which runs essentially parallel to the side surface 406 and the top surface 402. Electrical current flow in direction 408 is in a <110> direction.

[0045] As illustrated in FIG. 5, the room temperature hole mobility for a PMOS device and the resultant electrical current in the PMOS device formed according to the teachings of the present invention is approximately two and a half times faster than a conventional planar device formed on a surface with a (100) crystal plane orientation. Because

circuit performance is typically limited by the electrical current through PMOS devices, advantageously, a corresponding increase in performance for most logic applications generally occurs due to this increase in the speed of electrical current through PMOS devices.

[0046] In particular, the graph of FIG. 5 illustrates inversion layer hole mobility, expressed in velocity in centimeters per second divided by the field in V per centimeter, e.g. (cm<sup>2</sup>/Vsec), versus effective gate voltage, e.g. -(V<sub>G</sub>-V<sub>T</sub>), expressed in volts (V), at a temperature of approximately 297° Kelvin (° K.). FIG. 5 includes a plot 502 and a plot 504. The plot 502 is the graphical plot of hole mobility versus a gate voltage for a MOSFET device on a silicon surface conducting in the <100> direction. The plot 504 is the graphical plot of hole mobility versus a gate voltage for a MOSFET device on a silicon surface having a (110) crystalline plane orientation and conducting in the <110> direction. As illustrated in a region of normal operation 506, the plot 504 has a hole mobility of approximately 250 cm <sup>2</sup>/V\*sec. In contrast, as illustrated in the region of normal operation 506, the plot 502 only has a hole mobility of approximately 100 cm<sup>2</sup>/V\*sec. Thus, according to the teachings of the present invention, the formation and orientation of circuit devices lateral to surfaces having a (110) crystalline plane orientation in which the electrical current of such devices is flowing in the <110> direction allows for increases in the overall performance of such devices as well as of circuits which contain such devices.

[0047] FIGS. 6A-6F illustrate a preferred embodiment of a process of fabrication of conduction regions on a silicon wafer according to the teachings of the present invention. The sequence can be followed as a method of forming an integrated circuit, as a method of forming a semiconductor device, as a method of forming an integrated circuit that includes a number of lateral transistors and as a method of forming a MOSFET device.

[0048] FIG. 6A shows the structure after the first sequence of processing. A doped silicon layer 612 is grown on silicon wafer 602. In one embodiment, the silicon wafer 602 has a top surface 608 that has a (100) crystal plane orientation. However, it is important to appreciate that the top surface 608 may have other crystal plane orientations (e.g., (111) crystal plane orientation). In one embodiment, the silicon wafer 602 includes a bulk silicon material. In an alternative embodiment, the silicon wafer 602 includes a Silicon On Insulator (SOI) material. In one embodiment, the doped silicon layer 612 includes an n-type. In an alternative embodiment, the doped silicon layer 612 includes a p-type.

[0049] FIG. 6B shows the structure after the next sequence of processing. Trenches 604a-b are formed in the doped silicon layer 612, using conventional photolithography and etching techniques. In particular, the trenches 604a-b are specifically formed such that a first and a second trench wall 606 and 610 of the trenches 604a-b, respectively, have a (110) crystal plane orientation.

[0050] FIG. 6C shows the structure after the next sequence of processing. A thin silicon nitride  $(Si_3Ni_4)$  layer 634 is deposited by any suitable method, such as chemical vapor deposition (CVD), over the entire surface. The thin silicon nitride layer 634 is selectively etched to leave a thin layer on the bottom of trenches 604a-b.

[0051] FIG. 6D shows the structure after the next sequence of processing. A heavily doped glass layer 621,

which is of a different type than the type of the doped silicon layer 612, is deposited across the entire surface. In one such embodiment, the doped silicon layer 612 is an n-type semiconductor material, and the heavily doped glass layer 621 contains p-type dopant. In another such embodiment, the doped silicon layer 612 is a p-type semiconductor material, and the heavily doped glass layer 621 contains n-type dopant. The heavily doped glass layer 621 is deposited by any suitable means, such as by CVD. The heavily doped glass layer 621 is then selectively etched to leave specific portions of the trenches 604a-b, as shown in FIG. 6D

[0052] FIG. 6E shows the structure after the next sequence of processing. The structure undergoes an anneal, such as a rapid thermal anneal (RTA), in order to drive the dopant species from the heavily doped glass layer 621 into the lateral walls of doped silicon layer 612. Accordingly, a first conductive region 614 or first conductive region of a first type 614 is formed in the doped silicon layer 612. A second conductive region 616 or second conductive region of a first type 616 is also formed in the doped silicon layer 612. In particular, the second conductive region 616 is formed in reference to the first conductive region 618 or a conductive region of a second type 618, in between the first conductive region 614 and the second conductive region 616 within the doped silicon layer 612.

[0053] Further, a fourth conductive region 620 and a fifth conductive region 622 are formed in the doped silicon layer 612. In particular, the fifth conductive region 622 is formed in reference to the fourth conductive region 620 to cause the formation of a sixth conductive region 624 in between the fourth conductive region 620 and the fifth conductive region 622 within the doped silicon layer 612.

[0054] In one embodiment, the third and sixth conductive regions 618 and 624 include an n-type semiconductor material. In another embodiment, the third and sixth conductive regions 616 and 624 include a p-type. In one embodiment, the third and sixth conductive regions 618 and 624 are of a different type conductive material in comparison with the first, second, fourth and fifth conductive regions 614, 616, 620 and 622.

[0055] Additionally, an electrical current is capable of flowing between the first conductive region 614 and the second conductive region 616 through the third conductive region 618 in a <110> direction, e.g. parallel to the top surface 608 of the silicon wafer 602. In one embodiment, the electrical current is capable of flowing between the first conductive region 614 and the second conductive region 616 through the third conductive region 618 lateral to the first trench wall 606.

[0056] Further, an electrical current is capable of flowing between the fourth conductive region 620 and the fifth conductive region 622 through the sixth conductive region 624 in a <110> direction, e.g. parallel to the top surface 608 of the silicon wafer 602. In one embodiment, the electrical current is capable of flowing between the fourth conductive region 620 and the fifth conductive region 622 through the sixth conductive region 624 lateral to the second trench wall 610.

[0057] FIG. 6F shows the structure after the next sequence of processing. In particular, word lines 628a and

628b along with corresponding gate oxides 630a and 630b are formed lateral to the trench walls 606 and 610 of silicon wafer 602, using standard photolithography and deposition techniques. In one embodiment, word lines 628a and 628b include gates formed lateral to the gate oxides, 630a and 630b respectively. In one embodiment, word lines 628a and 628b are conductive lines constructed from a polysilicon. In one embodiment, the configuration illustrated in FIG. 6F includes two access transistors used in conjunction with a DRAM.

[0058] In one embodiment, the third and sixth conductive regions 618 and 624 are body regions of a transistor capable of forming a channel when a voltage potential is applied to the gates of such transistor. While only lateral transistors 640 and 650 are shown in FIG. 6F, one skilled in the art will recognize the repeatable structure shown and that any number of lateral transistors can be formed from the above described process and used in an array, hence, the details of a longer array are not disclosed in the present application.

[0059] FIGS. 7A-7C illustrate another embodiment of a process of fabrication of conduction regions on a silicon wafer according to the teachings of the present invention. The sequence can be followed as a method of forming an integrated circuit, as a method of forming a semiconductor device, as a method of forming an integrated circuit that includes a number of lateral transistors and as a method of forming a MOSFET device.

[0060] FIG. 7A shows the structure after the first sequence of processing. A doped silicon layer 712 is grown on a silicon wafer 702. In one embodiment, the silicon wafer 702 has a top surface 732 that has a (100) crystal plane orientation. However, it is important to appreciate that the top surface 732 may have other crystal plane orientations (e.g., (111) crystal plane orientation). In one embodiment, the silicon wafer 702 includes a bulk silicon material. In an alternative embodiment, the silicon wafer 702 includes a Silicon On Insulator (SOI) material.

[0061] In one embodiment, the doped silicon layer 712 includes an n-type. In an alternative embodiment, the doped silicon layer 712 includes a p-type. Additionally, a first conductive region 714 or first conductive region of a first type 714 is formed in the doped silicon layer 712, using, for example, ion implantation techniques. A second conductive region 716 or second conductive region of a first type 716 is also formed in the doped silicon layer 712. The second conductive region 716 can also be formed using, for example, ion implantation techniques. In particular, the second conductive region 716 is formed in reference to the first conductive region 714 to cause the formation of a third conductive region 718 or a conductive region 714 and the second conductive region 716 within the doped silicon layer 712.

[0062] Further, a fourth conductive region 720 and a fifth conductive region 722 are formed in the doped silicon layer 712, using, for example, ion implantation techniques. In particular, the fifth conductive region 722 is formed in reference to the fourth conductive region 720 to cause the formation of a sixth conductive region 724 in between the fourth conductive region 720 and the fifth conductive region 722 within the doped silicon layer 712.

[0063] In one embodiment, the first, second, fourth and fifth conductive regions 714, 716, 720 and 722 include an

n-type. In another embodiment, the first, second, fourth and fifth conductive regions 714, 716, 720 and 722 include a p-type. In one embodiment, the first and fourth conductive regions 714 and 720 are source regions and the second and fifth conductive regions 716 and 722 are drain regions of a transistor.

[0064] FIG. 7B shows the structure after the next sequence of processing. Trenches 704a-b are etched in the silicon wafer 702 using conventional photolithography and etching techniques. In particular, the trenches 704a-b are specifically etched such that a first and a second trench wall 708 and 710 of trenches 704a-b, respectively, have a (110) crystal plane orientation. Moreover, the first and the second trench walls 708 and 710 are specifically etched in the first, second and third conductive regions and the fourth, fifth and sixth conductive regions, respectively, of the silicon wafer 702.

[0065] Additionally, an electrical current is capable of flowing between the first conductive region 714 and the second conductive region 716 through the third conductive region 718 in a <110> direction, e.g. parallel to the top surface 708 of the silicon wafer 702. In one embodiment, the electrical current is capable of flowing between the first conductive region 714 and the second conductive region 716 through the third conductive region 718 lateral to the first trench wall 708.

[0066] Further, an electrical current is capable of flowing between the fourth conductive region 720 and the fifth conductive region 722 through the sixth conductive region 724 in a <110> direction, e.g. parallel to the top surface 708 of the silicon wafer 702. In one embodiment, the electrical current is capable of flowing between the fourth conductive region 720 and the fifth conductive region 722 through the sixth conductive region 724 lateral to the second trench wall 710.

[0067] FIG. 7C shows the structure after the next sequence of processing. In particular, word lines 728a and 728b along with corresponding gate oxides 730a and 730b are formed lateral to the trench walls 708 and 710 of silicon wafer 702, using standard photolithography and deposition techniques. In one embodiment, word lines 728a and 728b include gates formed lateral to the gate oxides, 730a and 730b respectively. In one embodiment, word lines 728a and 728b are conductive lines constructed from a polysilicon. In one embodiment, the configuration illustrated in FIG. 7C includes two access transistors used in conjunction with a DRAM.

[0068] In one embodiment, the third and sixth conductive regions 718 and 724 are body regions of a transistor capable of forming a channel when a voltage potential is applied to the gates of such transistor. In one embodiment, the third and sixth conductive regions 718 and 724 include an n-type semiconductor material. In another embodiment, the third and sixth conductive regions 716 and 724 include a p-type. In one embodiment, the third and sixth conductive regions 718 and 724 are of a different type conductive material in comparison with the first, second, fourth and fifth conductive regions 714, 716, 720 and 722.

[0069] While only lateral transistors 740 and 750 are shown in FIG. 7C, one skilled in the art will recognize the repeatable structure shown and that any number of lateral

transistors can be formed from the above described process and used in an array, hence, the details of a longer array are not disclosed in the present application.

[0070] FIGS. 8A-8C illustrate another embodiment of a process of fabrication of conduction regions on a silicon wafer according to the teachings of the present invention. The sequence can be followed as a method of forming an integrated circuit, as a method of forming a semiconductor device, as a method of forming an integrated circuit that includes a number of lateral transistors and as a method of forming a MOSFET device.

[0071] FIG. 8A shows the structure after the first sequence of processing. Trenches 804a-b are formed in a silicon wafer 802, using conventional photolithography and etching techniques. In particular, the trenches 804a-b are specifically formed such that a first and a second trench wall 806 and 810 of the trenches 804a-b, respectively, have a (110) crystal plane orientation. In one embodiment, the silicon wafer 802 has a top surface 808 that has a (100) crystal plane orientation. However, it is important to appreciate that the top surface 808 may have other crystal plane orientations (e.g., (111) crystal plane orientation). In one embodiment, the silicon wafer 802 includes a bulk silicon material. In an alternative embodiment, the silicon wafer 802 includes a Silicon On Insulator (SOI) material.

[0072] FIG. 8B shows the structure after the next sequence of processing. In particular, regions in the trench walls 806 and 810 are doped using, for example, angled ion implantation, as shown. The doped regions include (1) a first conductive region 814 or a first conductive region of a first type 814, (2) a second conductive region 816 or a second conductive region 6 a first type 816, (3) a fourth conductive region 820, (4) a fifth conductive region 822, and (5) a remaining region 826 of the top surface 808. The remaining region 826 includes a third conductive region 818 or a conductive region of a second type 818 and a sixth conductive region 824.

[0073] The doped regions are formed such that the second conductive region 816 is formed in reference to the first conductive region 814 to cause the formation of the third conductive region 818 in between the first conductive region 814 and the second conductive region 816. Additionally, the fifth conductive region 822 is formed in reference to the fourth conductive region 820 to cause the formation of the sixth conductive region 824 in between the fourth conductive region 820 and the fifth conductive region 822.

[0074] In one embodiment, the remaining region 826, which includes the third conductive region 818 and sixth conductive region 824, is a different type conductive material in comparison with the first, second, fourth and fifth conductive regions 814, 816, 820 and 822, respectively. In one such embodiment, the remaining region 826 is an n-type, while the first, second, fourth and fifth conductive regions 814, 816, 820 and 822, respectively, are a p-type. In another such embodiment, the remaining region 826 is a p-type, and the first, second, fourth and fifth conductive regions 814, 816, 820 and 822, respectively, are an n-type. In one embodiment, the first and fourth conductive regions 814 and 820 are source regions and the second and fifth conductive regions 816 and 822 are drain regions of a transistor. In one embodiment, the third and sixth conductive

regions 818 and 824 are body regions of a transistor capable of forming a channel when a voltage potential is applied to the gates of such transistor.

[0075] Additionally, an electrical current is capable of flowing between the first conductive region 814 and the second conductive region 816 through the third conductive region 818 in a <110> direction, e.g. parallel to the top surface 808 of the silicon wafer 802. In one embodiment, the electrical current is capable of flowing between the first conductive region 814 and the second conductive region 816 through the third conductive region 818 lateral to the first trench wall 806, which has a (110) crystal plane orientation.

[0076] Further, an electrical current is capable of flowing between the fourth conductive region 820 and the fifth conductive region 822 through the sixth conductive region 824 in a <110> direction, e.g. parallel to the top surface 808 of the silicon wafer 802. In one embodiment, the electrical current is capable of flowing between the fourth conductive region 820 and the fifth conductive region 822 through the sixth conductive region 824 lateral to the second trench wall 810, which has a (110) crystal plane orientation.

[0077] FIG. 8C shows the structure after the next sequence of processing. In particular, word lines 828a and 828b along with corresponding gate oxides 830a and 830b are formed lateral to the trench walls 806 and 810 of silicon wafer 802, using standard photolithography and deposition techniques. In one embodiment, word lines 828a and 828b include gates formed lateral to the gate oxides, 830a and 830b respectively. In one embodiment, word lines 828a and 828b are conductive lines constructed from a polysilicon. In one embodiment, the configuration illustrated in FIG. 8C includes two access transistors used in conjunction with a DRAM.

[0078] While only lateral transistors 840 and 850 are shown in FIG. 8C, one skilled in the art will recognize the repeatable structure shown and that any number of lateral transistors can be formed from the above described process and used in an array, hence, the details of a longer array are not disclosed in the present application.

[0079] FIG. 9 is a cross-sectional view of an embodiment of an integrated circuit according to the teachings of the present invention. The integrated circuit of FIG. 9 is constructed in a similar manner according to any one of the methods presented in this application. The integrated circuit includes a trench wall 906 of a trench 904 in a silicon wafer 902. According to the teachings of the present invention, the trench wall 906 has a (110) crystal plane orientation. In one embodiment, the silicon wafer 902 has a top surface 908 that has a (100) crystal plane orientation. However, it is important to appreciate that the top surface 908 may have other crystal plane orientations (e.g., (111) crystal plane orientation). In one embodiment, the silicon wafer 902 includes a bulk silicon material. In an alternative embodiment, the silicon wafer 902 includes a Silicon On Insulator (SOI) material.

[0080] The integrated circuit of FIG. 9 also includes a semiconductor device 910 which is lateral to the trench wall 906. Specifically, according to the teachings of the present invention, the semiconductor device 910 is designed for or configured for conducting an electrical current in the <110> direction. In one embodiment, the semiconductor device 910

is a MOSFET device. In one such embodiment, the semiconductor device 910 is a p-MOSFET device. In another such embodiment, the semiconductor device 910 is a n-MOSFET device.

[0081] FIG. 10 is a cross-sectional view of an embodiment of a device according to the teachings of the present invention. The device of FIG. 10 is constructed in a similar manner according to any one of the methods presented in this application. Additionally, in one embodiment, the device of FIG. 10 is a semiconductor device. In one embodiment, the device of FIG. 10 is a MOSFET device. In one such embodiment, the device is an n-MOSFET device. In another embodiment, the device is a p-MOSFET device. In another embodiment, the device is a portion of a dynamic random access memory (DRAM) having an array of transistors. In one embodiment, the device is a portion of an array of MOSFETs. In another embodiment, the device of FIG. 10 is a portion of an integrated circuit.

[0082] While only one device 1016 is shown in FIG. 10, one skilled in the art will recognize the repeatable structure shown and that any number of similar devices can be formed from the above described process and used as a portion of a DRAM, in an array, or portion of an integrated circuit. Hence, the details of a longer array are not disclosed in the present application.

[0083] The device includes a first conductive region 1010 in a trench 1004 of a silicon wafer 1002. The first conductive region 1010 is of a first type and is lateral to a trench wall 1006 of the trench 1004. Additionally, the trench wall 1006 has a (110) crystal plane orientation. In one embodiment, the first type is an n-type. In another embodiment, the first type is a p-type. In one embodiment, the silicon wafer 1002 has a top surface 1008, which has a (100) crystal plane orientation

[0084] The device of FIG. 10 also includes a second conductive region 1012 in the trench 1004. The second conductive region 1012 is of the first type and is lateral to the trench wall 1006. Additionally, the device of FIG. 10 includes a third conductive region 1014 in the trench 1004. The third conductive region 1014 is of a second type and is lateral to the trench wall 1006. An electrical current is also capable of flowing between the first conductive region 1010 and the second conductive region 1012 in a <110> direction. In one embodiment, the third conductive region 1014 is a body region of a MOSFET device.

[0085] FIG. 11 is a block diagram which illustrates an embodiment of a system 1100 according to teachings of the present invention. The system 1100 includes an integrated circuit 1110 which can include a memory, e.g. a DRAM. The integrated circuit 1110 includes the embodiments of a device in a trench of a semiconductor wafer according to the structures and methods described above in this application. In particular, the device is lateral to a trench wall of the trench such that the trench wall has a (110) crystal plane orientation and an electrical current is capable of flowing in the device in a <110> direction, all according to the teachings of the present invention. Additionally, the system 1100 includes a processor 1120 that is operatively coupled to the integrated circuit 1110. The processor 1120 is coupled to the integrated circuit 1110 through a bus 1130. In one embodiment, the processor 1120 and the integrated circuit 1110 are on the same semiconductor chip.

#### Conclusion

[0086] Thus, improved methods and structures are provided that are lateral to surfaces with a (110) crystal plane orientation such that an electrical current of such structures is in a <110> direction. Advantageously, improvements in hole carrier mobility of approximately 50% can be obtained by orienting the structure's channel in a (110) plane such that the electrical current flow is in the <110> direction. Moreover, these improved methods and structures can be used in conjunction with existing fabrication and processing techniques with minimal or no added complexity.

[0087] Although specific embodiments have been illustrated and described herein, it will be appreciated by those of ordinary skill in the art that any arrangement which is calculated to achieve the same purpose may be substituted for the specific embodiment shown. This application is intended to cover any adaptations or variations of the present invention. It is to be understood that the above description is intended to be illustrative, and not restrictive. Combinations of the above embodiments, and other embodiments will be apparent to those of skill in the art upon reviewing the above description. The scope of the invention includes any other applications in which the above structures and fabrication methods are used. The scope of the invention should be determined with reference to the appended claims, along with the full scope of equivalents to which such claims are entitled.

What is claimed is:

- 1. A semiconductor device, comprising:

- a first conductive n-type region in a trench of a silicon wafer such that the first conductive n-type region is lateral to a trench wall of the trench, wherein the trench wall has a (110) crystal plane orientation;

- a second conductive n-type region in the trench such that the second conductive n-type region is lateral to the trench wall; and

- a conductive p-type region in the trench such that the conductive p-type region is lateral to the trench wall and located between the first and second conductive n-type regions, wherein the semiconductor device is designed to conduct an electrical current between the first and second conductive p-type regions in a direction parallel to a top surface of the silicon wafer.

- 2. The semiconductor device of claim 1, wherein the silicon wafer has a top surface having a (100) crystal plane orientation.

- 3. A semiconductor device, comprising:

- a number of trenches formed in a silicon wafer; and

- a number of spaced MOSFETs in each trench, wherein each MOSFET includes:

- a first conductive p-type region in a trench of the silicon wafer such that the first conductive p-type region is lateral to a trench wall of the trench, wherein the trench wall has a (110) crystal plane orientation;

- a second conductive p-type region in the trench such that the second conductive p-type region is lateral to the trench wall; and

- a conductive n-type region in the trench such that the conductive n-type region is lateral to the trench wall

- and between the first and second conductive p-type regions, wherein an electrical current is capable of flowing between the first and second conductive p-type regions in a <110> direction.

- **4.** The semiconductor device of claim 3, wherein the silicon wafer includes a bulk silicon material.

- 5. The semiconductor device of claim 3, wherein the silicon wafer has a top surface with a (100) crystal plane orientation.

- 6. The semiconductor device of claim 3, wherein each MOSFET includes a gate which opposes the conductive n-type region.

- 7. The semiconductor device of claim 6, wherein each MOSFET includes a gate oxide separating the gate and the conductive n-type region.

- **8**. The semiconductor device of claim 7, further including a wordline coupling together the gates on each MOSFET in each trench.

- 9. An electronic system comprising:

- a processor; and

- an integrated circuit coupled to the processor, wherein the integrated circuit is formed on a silicon wafer, and wherein the silicon wafer includes:

- a trench wall having a (110) crystal plane orientation; and

- a semiconductor device lateral to the trench wall, wherein the semiconductor device is capable of conducting an electrical current in a <110> direction.

- 10. The electronic system of claim 9, wherein the processor and the integrated circuit are formed on the same silicon wafer

- 11. The electronic system of claim 9, wherein a top surface of the silicon wafer has a (100) crystal plane orientation.

- 12. The electronic system of claim 9, wherein the silicon wafer includes a bulk silicon material.

- 13. The electronic system of claim 9, wherein the semiconductor device includes a p-channel Metal Oxide Semiconductor Field Effect Transistor (p-MOSFET) device.

- 14. An electronic system comprising:

- a processor; and

- a semiconductor device coupled to the processor, the semiconductor device including:

- a first conductive region of a first type in a trench of a silicon wafer such that the first conductive region of the first type is lateral to a trench wall of the trench, wherein the trench wall has a (110) crystal plane orientation;

- a second conductive region of the first type in the trench such that the second conductive region of the first type is lateral to the trench wall; and

- a third conductive region of a second type in the trench such that the third conductive region of the second type is lateral to the trench wall and between the first and second conductive regions of the first type, wherein an electrical current is capable of flowing between the first and second conductive regions of the first type in a <110> direction.

- 15. The electronic system of claim 14, wherein the third conductive region of the second type includes a channel of a Metal Oxide Semiconductor Field Effect Transistor (MOSFET) device.

- 16. The electronic system of claim 14, wherein the first type is an n-type.

- 17. The electronic system of claim 14, wherein the second type is an p-type.

- 18. The electronic system of claim 14, wherein the silicon wafer has a top surface having a (100) crystal plane orientation.

- 19. A semiconductor device, comprising:

- a layer of conductive material of a first type;

- at least one trench formed in the layer of conductive material, the at least one trench including a trench wall; and

- at least one semiconductor device formed laterally to the trench wall, the at least one semiconductor device comprising:

- a first conductive region of a second type formed laterally to the trench wall;

- a second conductive region of the second type formed laterally to the trench wall; and

- a third conductive region of the layer of conductive material disposed laterally to the trench wall and separating the first and second conductive regions to provide a channel to conduct electrical current between the first and second conductive regions.

- **20**. The semiconductor device of claim 19, wherein the first and second conductive regions are formed by at least one of rapid thermal annealing, ion implantation, angled ion implantation, and chemical vapor deposition.

- 21. The semiconductor device of claim 19, wherein the at least one semiconductor device is one of an n-channel semiconductor device or a p-channel semiconductor device.

- 22. A semiconductor device, comprising:

- a substrate;

- a layer of conductive material of a first type formed on the substrate;

- at least one trench formed in the layer of conductive material and including trench walls substantially perpendicular to a plane of the substrate; and

- at least one semiconductor device formed laterally to at least one of the trench walls, the at least one semiconductor device comprising:

- a first conductive region of a second type formed laterally to the at least one trench wall;

- a second conductive region of the second type formed laterally to the at least one trench wall; and

- a third conductive region of the layer of conductive material disposed laterally to the at least one trench wall and separating the first and second conductive regions to permit electrical current to be conducted between the first and second conductive regions.

- 23. A semiconductor device, comprising:

- a layer of conductive material of a first type;

- at least one trench formed in the layer of conductive material, the at least one trench including a trench wall having a (110) crystal plane orientation; and

- at least one semiconductor device formed laterally to the trench wall, the at least one semiconductor device comprising:

- a first conductive region of a second type formed laterally to the trench wall;

- a second conductive region of the second type formed laterally to the trench wall; and

- a third conductive region of the layer of conductive material disposed laterally to the trench wall and separating the first and second conductive regions to permit electrical current to be conducted in a <110> direction between the first and second conductive regions.

- 24. A semiconductor device, comprising:

- a substrate;

- a layer of conductive material of a first type formed on the substrate;

- at least one trench formed in the layer of conductive material and including a trench wall substantially perpendicular to a top surface of the substrate and including a (110) crystal plane orientation; and

- at least one semiconductor device formed in a plane defined by the trench wall, the at least one semiconductor device comprising:

- a first conductive region of a second type formed in the plane of the trench wall;

- a second conductive region of the second type formed in the plane of the trench wall; and

- a third conductive region of the layer of conductive material disposed in the plane of the trench wall and separating the first and second conductive regions to permit electrical current to be conducted in a <110> direction.

- 25. A semiconductor device, comprising:

- a layer of conductive material of a first type;

- a plurality of trenches formed in the layer of conductive material, each trench including a trench wall;

- at least one semiconductor device formed laterally to the trench wall, the at least one semiconductor device comprising:

- a first conductive region of a second type formed laterally to the trench wall;

- a second conductive region of the second type formed laterally to the trench wall; and

- a third conductive region of the layer of conductive material disposed laterally to the trench wall and separating the first and second conductive regions to provide a channel to conduct electrical current between the first and second conductive regions.

- 26. A semiconductor device, comprising:

- an array of memory elements, each memory element comprising:

- a first conductive region of a first type formed laterally in a trench wall;

- a second conductive region of the first type formed laterally to the trench wall; and

- a third conductive region of a second type disposed laterally to the trench wall and separating the first and second conductive regions to provide a channel to conduct electrical current between the first and second conductive regions; and

- a wordline coupled to each memory element.

- 27. A semiconductor device, comprising:

- a first conductive region of a first type formed laterally in a trench wall;

- a second conductive region of the first type formed laterally to the trench wall; and

- a third conductive region of a second type disposed laterally to the trench wall and separating the first and second conductive regions to provide a channel to conduct electrical current between the first and second conductive regions.

- 28. A semiconductor device, comprising:

- a first conductive region of a first type formed laterally to a trench wall having a (110) crystal plane orientation;

- a second conductive region of the first type formed laterally to the trench wall; and

- a third conductive region of a second type disposed laterally to the trench wall and separating the first and second conductive regions to permit electrical current to be conducted in a <110> direction between the first and second conductive regions.

- 29. A semiconductor device, comprising:

- a layer of conductive material of a first type formed on a substrate;

- at least one trench formed in the layer of conductive material and including a trench wall substantially perpendicular to a top surface of the substrate and including a (110) crystal plane orientation;

- a first conductive region of a second type formed in a plane of the trench wall;

- a second conductive region of the second type formed in the plane of the trench wall; and

- a third conductive region of the layer of conductive material disposed in the plane of the trench wall and separating the first and second conductive regions to permit electrical current to be conducted in a <110> direction

- **30**. An electronic system, comprising:

- a processor; and

- a semiconductor device coupled to the processor, wherein the semiconductor device comprises:

- a first conductive region of a first type formed laterally in a trench wall;

- a second conductive region of the first type formed laterally to the trench wall; and

- a third conductive region of a second type disposed laterally to the trench wall and separating the first and second conductive regions to provide a channel to conduct electrical current between the first and second conductive regions.

- **31**. An electronic system, comprising:

- a processor; and

- a semiconductor device coupled to the processor, wherein the semiconductor device comprises:

- a first conductive region of a first type formed laterally to a trench wall having a (110) crystal plane orientation;

- a second conductive region of the first type formed laterally to the trench wall; and

- a third conductive region of a second type disposed laterally to the trench wall and separating the first and second conductive regions to permit electrical current to be conducted in a <110> direction between the first and second conductive regions.

- 32. An electronic system, comprising:

- a processor; and

- a memory device coupled to the processor, the memory device comprising:

- a layer of conductive material of a first type;

- at least one trench formed in the layer of conductive material, the at least one trench including a trench wall;

- at least one memory element formed laterally to the at least one trench wall, the at least one memory element comprising:

- a first conductive region of a second type formed laterally to the trench wall;

- a second conductive region of the second type formed laterally to the trench wall; and

- a third conductive region of the layer of conductive material disposed laterally to the trench wall and separating the first and second conductive regions to

- provide a channel to conduct electrical current between the first and second conductive regions.

- 33. An electronic system, comprising:

- a processor; and

- a memory device coupled to the processor, the memory device including an array of memory elements, each memory element comprising:

- a first conductive region of a first type formed laterally to a trench wall having a (110) crystal plane orientation:

- a second conductive region of the first type formed laterally to the trench wall; and

- a third conductive region of a second type disposed laterally to the trench wall and separating the first and second conductive regions to permit electrical current to be conducted in a <110> direction between the first and second conductive regions.

- 34. An electronic system, comprising:

- a processor; and

- a memory device couple to the processor, the memory device comprising:

- an array of memory element, each memory element comprising:

- a layer of conductive material of a first type formed on a substrate;

- at least one trench formed in the layer of conductive material and including a trench wall substantially perpendicular to a top surface of the substrate and including a (110) crystal plane orientation;

- a first conductive region of a second type formed in a plane of the trench wall;

- a second conductive region of the second type formed in the plane of the trench wall; and

- a third conductive region of the layer of conductive material disposed in the plane of the trench wall and separating the first and second conductive regions to permit electrical current to be conducted in a <110> direction.

\* \* \* \* \*