(12)

## Patentschrift

(21) Aktenzeichen: 10 2014 218 389.8

(22) Anmelddatum: 12.09.2014

(43) Offenlegungstag: 30.04.2015

(45) Veröffentlichungstag

der Patenterteilung: 17.06.2021

(51) Int Cl.: H01L 23/16 (2006.01)

H01L 23/42 (2006.01)

H01L 23/48 (2006.01)

H01L 21/52 (2006.01)

H01L 25/07 (2006.01)

Innerhalb von neun Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten (§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 1 Patentkostengesetz).

(30) Unionspriorität:

**2013-226731** 31.10.2013 JP

(73) Patentinhaber:

**Mitsubishi Electric Corporation, Tokyo, JP**

(74) Vertreter:

**Prüfer & Partner mbB Patentanwälte

Rechtsanwälte, 81479 München, DE**

(72) Erfinder:

**Otsuki, Takami c/o Mitsubishi Electric Corp.,

Tokyo, JP; Yoneyama, Rei c/o Mitsubishi Electric

Corp., Tokyo, JP; Yamashita, Akihiko c/o Wave

Technology Inc., Kawanishi-shi, Hyogo, JP;

Kimura, Yoshitaka c/o Mitsubishi Electric Corp.,

Tokyo, JP**

(56) Ermittelter Stand der Technik:

|    |               |   |

|----|---------------|---|

| JP | H01- 281 760  | A |

| JP | 2013- 161 961 | A |

| JP | 2000- 31 358  | A |

(54) Bezeichnung: **Halbleitermodul**

(57) Hauptanspruch: Halbleitermodul (1, 1A) mit:

einer Basisplatte (3), die eine vordere Fläche (3a) hat, die

mit einem Positionierdrahtfügeabschnitt (20, 20a, 20b, 20c,

20d) versehen ist;

einem Isoliersubstrat (8), das mit einem Aufnahmearnschnitt

(21, 21a, 21b, 21c, 21d, 22, 22a, 22b, 22c, 22d, 23, 23a,

23b, 23c, 23d) versehen ist, der den Positionierdrahtfügeab-

schnitt (20, 20a, 20b, 20c, 20d) an einer Seite einer hinteren

Fläche (8b) unterbringt, die der Basisplatte (3) zugewandt

ist, und das an der Basisplatte (3) befestigt ist, indem es hin-

sichtlich der Basisplatte (3) durch den Aufnahmearnschnitt

(21, 21a, 21b, 21c, 21d, 22, 22a, 22b, 22c, 22d, 23, 23a,

23b, 23c, 23d) positioniert ist, der den Positionierdrahtfü-

geabschnitt (20, 20a, 20b, 20c, 20d) unterbringt; und

einem Halbleiterchip (10), der an einer Seite einer vorderen

Fläche (8a) des Isoliersubstrats (8), die der hinteren Fläche

(8b) abgewandt ist, angeordnet ist, wobei

der Aufnahmearnschnitt (21, 21a, 21b, 21c, 21d, 22, 22a,

22b, 22c, 22d, 23, 23a, 23b, 23c, 23d) ein Lochabschnitt (21,

21a, 21b, 21c, 21d) ist, der in einer Musterlage (9) vorgese-

hen ist, die an der hinteren Fläche (8b) des Isoliersubstrats

(8) ausgebildet ist, und

das Isoliersubstrat (8) hinsichtlich der Basisplatte (3) durch

den Positionierdrahtfügeabschnitt (20, 20a, 20b, 20c, 20d)

positioniert ist, der in den Lochabschnitt (21, 21a, 21b, 21c,

21d) eingefügt ist.

**Beschreibung**

**[0001]** Die vorliegende Erfindung bezieht sich auf ein Halbleitermodul.

**[0002]** Bei einem Leistungshalbleitermodul sind ein Isoliersubstrat, ein Halbleiterchip und dergleichen durch eine Lötfügestelle an einer Metallbasisplatte angebracht. Zum Beispiel schlagen die JP 2000-31 358 A und die JP H01- 281 760 A bei einem Halbleitermodul, bei dem ein Isoliersubstrat mit einem Schaltungslayout, das unter Verwendung von Kupferfolie ausgebildet wird, an einer Metallbasisplatte angebracht ist, Techniken zum Bereitstellen von konvexen und konkaven Abschnitten an vorbestimmten Positionen an der Metallbasisplatte zum Positionieren des Isoliersubstrats vor.

**[0003]** Ferner offenbart JP 2013-161 961 A ein Halbleitermodul - Herstellungsverfahren, bei dem Positionierdrähte auf der Basisplatte gebondet sind und das Positionieren eines Keramiksubstrats in Bezug auf die Basisplatte in horizontaler Richtung durch Anlegen von Seitenflächen einer unteren Metallschicht, die unter dem Keramiksubstrat angeordnet ist, an die Positionierungsdrähte durchgeführt wird.

**[0004]** Bei den Halbleitermodulen, die in der JP 2000- 31 358 A und der JP H01- 281 760 A vorgeschlagen werden, ist es erforderlich, eine zusätzliche Verarbeitung an der Basisplatte durchzuführen, um die konvexen und konkaven Abschnitte in der Basisplatte bereitzustellen, was die Mannstunden erhöht und die Herstellungseffizienz reduziert. Falls des Weiteren die konvexen und konkaven Abschnitte unter Verwendung einer Gussform oder dergleichen vorgesehen werden, ist es außerdem erforderlich, das Design der Gussform selbst zu ändern, wenn die Orte zum Ausbilden der konvexen und konkaven Abschnitte sowie die Anzahl der konvexen und konkaven Abschnitte geändert werden, und somit ist es schwierig, die Gussform für die Produktion einer großen Vielfalt von Produkten in kleinen Mengen zu nutzen.

**[0005]** Die vorliegende Erfindung wurde angesichts des vorstehend geschilderten Problems geschaffen, und es ist die Aufgabe der vorliegenden Erfindung, ein Halbleitermodul vorzusehen, bei dem die Reduzierung der Herstellungseffizienz unterdrückt wird und ein Isoliersubstrat hinsichtlich einer Basisplatte mit einem hohen Genauigkeitsgrad positioniert wird.

**[0006]** Die obengenannte Aufgabe der vorliegenden Erfindung ist durch ein Halbleitermodul gemäß Anspruch 1 oder 3 erzielt.

**[0007]** Gemäß dem Halbleitermodul der vorliegenden Erfindung kann ein Halbleitermodul vorgesehen werden, bei dem eine Reduzierung der Herstellungs-

effizienz unterdrückt wird und ein Isoliersubstrat hinsichtlich einer Basisplatte mit einem hohen Genauigkeitsgrad positioniert wird.

**[0008]** Diese sowie weitere Merkmale, Aspekte und Vorteile der vorliegenden Erfindung werden aus der folgenden, detaillierten Beschreibung der vorliegenden Erfindung im Zusammenhang mit den beigefügten Zeichnungen ersichtlich.

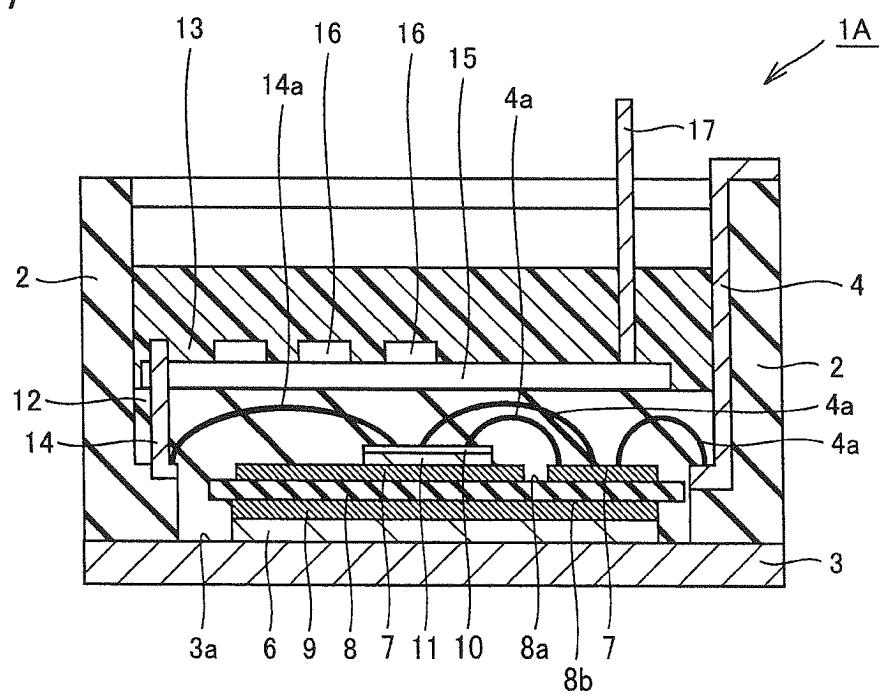

**Fig. 1** zeigt eine schematische Querschnittsansicht einer Struktur eines Halbleitermoduls gemäß Ausführungsbeispiel 1.

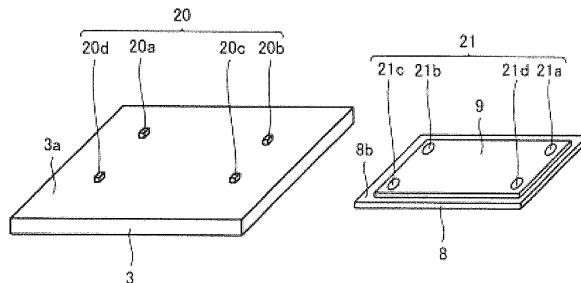

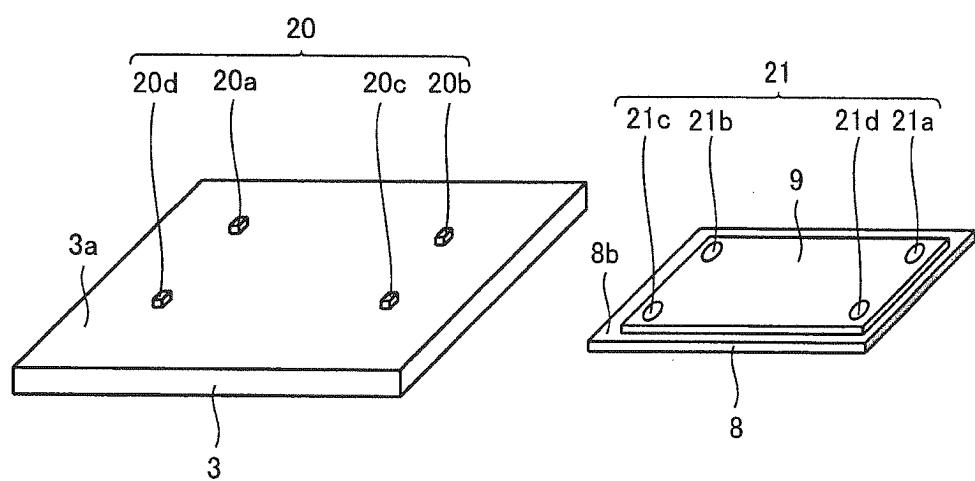

**Fig. 2** zeigt eine schematische, perspektivische Ansicht zum Darstellen der Struktur des Halbleitermoduls gemäß Ausführungsbeispiel 1.

**Fig. 3** zeigt eine schematische, perspektivische Ansicht zum Darstellen einer Struktur einer ersten Abwandlung des Halbleitermoduls gemäß Ausführungsbeispiel 1.

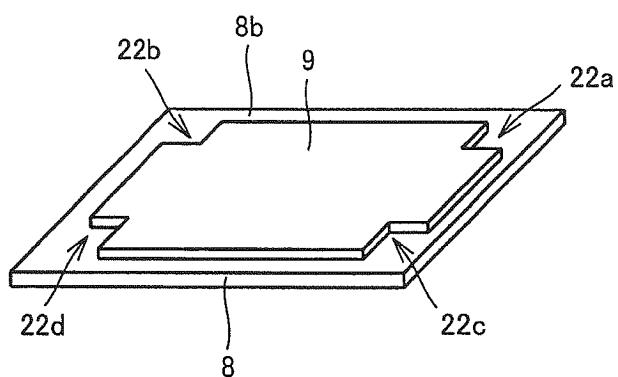

**Fig. 4** zeigt eine schematische, perspektivische Ansicht zum Darstellen einer Struktur einer zweiten Abwandlung des Halbleitermoduls gemäß Ausführungsbeispiel 1.

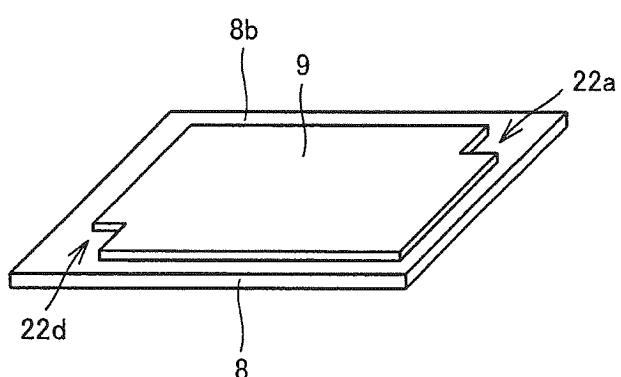

**Fig. 5** zeigt eine schematische, perspektivische Ansicht zum Darstellen einer Struktur einer dritten Abwandlung des Halbleitermoduls gemäß Ausführungsbeispiel 1.

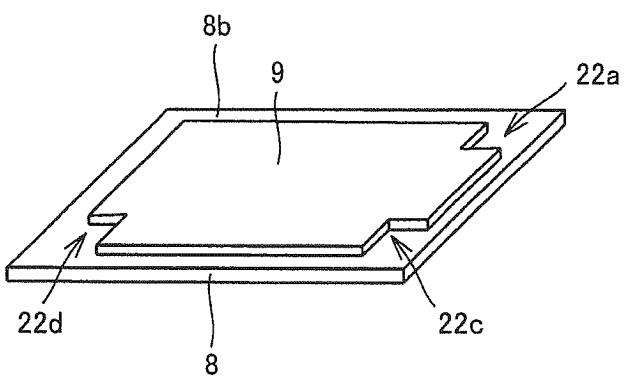

**Fig. 6** zeigt eine schematische, perspektivische Ansicht zum Darstellen einer Struktur einer vierten Abwandlung des Halbleitermoduls gemäß Ausführungsbeispiel 1.

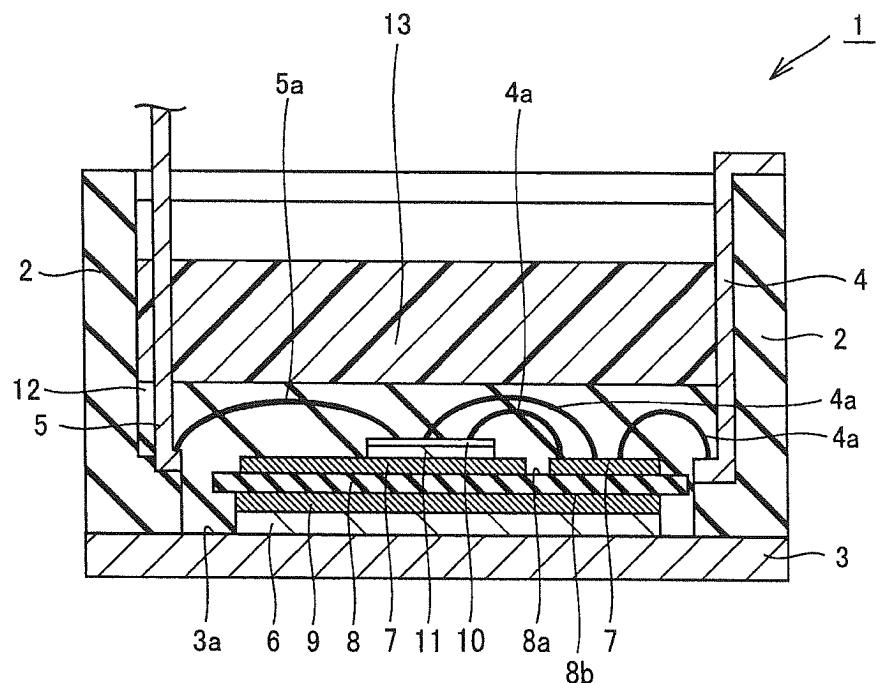

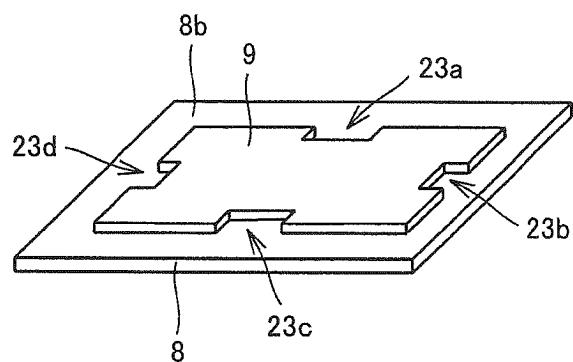

**Fig. 7** zeigt eine schematische Querschnittsansicht einer Struktur eines Halbleitermoduls gemäß Ausführungsbeispiel 2.

**[0009]** Nachfolgend werden Ausführungsbeispiele der vorliegenden Erfindung unter Bezugnahme auf die Zeichnungen beschrieben. In den nachfolgenden Zeichnungen werden identische oder entsprechende Teile durch dieselben Bezugszeichen bezeichnet, und deren Beschreibung wird nicht wiederholt.

(Ausführungsbeispiel 1)

**[0010]** Zunächst wird Ausführungsbeispiel 1 als ein Ausführungsbeispiel der vorliegenden Erfindung beschrieben. Zu Beginn wird eine Struktur eines Halbleitermoduls gemäß dem gegenwärtigen Ausführungsbeispiel beschrieben. Unter Bezugnahme auf **Fig. 1** hat ein Leistungsmodul 1 als das Halbleitermodul gemäß dem gegenwärtigen Ausführungsbeispiel hauptsächlich ein Gehäuse 2, eine Basisplatte 3, einen Leistungsanschluss 4, einen Signalanschluss 5, Leistungsdrähte 4a und einen Signaldraht 5a (Fügedrähte), ein Isoliersubstrat 8, einen Halbleiterchip 10, Sili-kongel 12 und einen Dichtungskunststoff 13.

**[0011]** Das Gehäuse **2** ist an einer vorderen Fläche **3a** der Basisplatte **3** angeordnet und bildet zusammen mit der Basisplatte **3** einen Innenraum zum Unterbringen des Halbleiterchips **10**. Der Leistungsanschluss **4** besteht aus Metall und erstreckt sich derart, dass er entlang einer Innenfläche des Gehäuses **2** gebogen ist, um sich dem Halbleiterchip **10** anzunähern. Der Leistungsanschluss **4** ist über einen Leistungsdraht **4a** mit einer Musterlage **7** verbunden, die an einer vorderen Fläche **8a** des Isoliersubstrats **8** ausgebildet ist.

**[0012]** Der Signalanschluss **5** besteht aus Metall und erstreckt sich derart entlang der Innenfläche des Gehäuses **2**, dass er sich dem Halbleiterchip **10** annähert. Der Signalanschluss **5** ist so angeordnet, dass er dem Leistungsanschluss **4** zugewandt ist und den Halbleiterchip **10** zwischen sich selbst und dem Leistungsanschluss **4** in dem Innenraum des Gehäuses **2** einfasst. Der Signalanschluss **5** ist über einen Signaldraht **5a** mit dem Halbleiterchip **10** verbunden.

**[0013]** Das Isoliersubstrat **8** hat eine vordere Fläche **8a** und eine hintere Fläche **8b**, und Musterlagen **7, 9** sind an der vorderen Fläche **8a** bzw. der hinteren Fläche **8b** ausgebildet. Die Musterlagen **7, 9** bestehen zum Beispiel aus einer Kupferfolie oder dergleichen, und sie haben eine Dicke, die gleich oder größer als 0,1 mm und gleich oder kleiner als 0,5 mm ist. Das Isoliersubstrat **8** ist an der Basisplatte **3** durch eine Lötlage **6** befestigt, während es hinsichtlich der Basisplatte **3** positioniert ist. Die Lötlage **6** hat zum Beispiel eine Dicke, die gleich oder größer als 0,1 mm und gleich oder kleiner als 0,5 mm ist. Ein Mechanismus zum Positionieren des Isoliersubstrats **8** hinsichtlich der Basisplatte **3** wird später beschrieben.

**[0014]** Der Halbleiterchip **10** ist an einer Seite der vorderen Fläche **8a** des Isoliersubstrats **8** angeordnet und an dem Isoliersubstrat **8** durch eine Lötlage **11** befestigt. Der Halbleiterchip **10** ist eine Halbleitervorrichtung, wie zum Beispiel ein MOSFET (Metal-Oxide-Semiconductor-Field-Effect-Transistor), ein IGBT (Insulated-Gate-Bipolar-Transistor), eine Diode oder dergleichen. Auch wenn nur ein einziger Halbleiterchip **10** an dem Isoliersubstrat **8** in der **Fig. 1** befestigt ist, können viele Halbleitervorrichtungen gemäß der vorstehenden Beschreibung nebeneinander an dem Isoliersubstrat **8** platziert und befestigt werden.

**[0015]** Das Silikongel **12** ist in dem Innenraum des Gehäuses **2** gepackt und deckt den Halbleiterchip **10** ab. Der Dichtungskunststoff **13** ist an dem Silikongel **12** angeordnet. Somit ist der Halbleiterchip **10** durch das Silikongel **12** und den Dichtungskunststoff **13** in dem Innenraum des Gehäuses **2** abgedichtet.

**[0016]** Als nächstes wird der Mechanismus zum Positionieren des Isoliersubstrats **8** hinsichtlich der Basisplatte **3** unter Bezugnahme auf die **Fig. 1** und

**Fig. 2** beschrieben. **Fig. 2** zeigt einen Zustand, bei dem die Basisplatte **3** und das Isoliersubstrat **8** in dem Leistungsmodul **1** (**Fig. 1**) als Explosionsbild dargestellt sind. Unter Bezugnahme auf die **Fig. 2** sind viele Positionierdrahtfügeabschnitte **20** (20a bis 20d) an der vorderen Fläche **3a** der Basisplatte **3** vorgesehen. Die Positionierdrahtfügeabschnitte **20** werden an der Basisplatte **3** durch dasselbe Verfahren zum Befestigen der Leistungsdrähte **4a**, des Signaldrahts **5a** (**Fig. 1**) und dergleichen an dem Halbleiterchip **10** und den Anschlüssen befestigt. Insbesondere werden die Positionierdrahtfügeabschnitte **20** an der vorderen Fläche **3a** durch Aufbringen von Wärme, Ultraschall, Druck oder dergleichen an Drähten vorgesehen, die an der vorderen Fläche **3a** der Basisplatte **3** platziert sind.

**[0017]** Die Positionierdrahtfügeabschnitte **20** bestehen aus einem Metall wie die Leistungsdrähte **4a** und der Signaldraht **5a**, und sie bestehen aus einem Metallmaterial, wie zum Beispiel Aluminium, Kupfer oder dergleichen. Die Positionierdrahtfügeabschnitte **20** haben jeweils einen Durchmesser, der zum Beispiel gleich oder größer als 0,1 mm und gleich oder kleiner als 1,0 mm ist. Auch wenn die Positionierdrahtfügeabschnitte **20** jeweils an vier Ecken eines Rechtecks angeordnet sein können, wie dies in der **Fig. 2** dargestellt ist, sind ihre Anzahl und das Verfahren ihrer Anordnung nicht besonders beschränkt.

**[0018]** Viele Lochabschnitte **21a** bis **21d** (Aufnahmabschnitte) zum Unterbringen der jeweiligen Positionierdrahtfügeabschnitte **20a** bis **20d** sind in der Musterlage **9** vorgesehen, die an der hinteren Fläche **8b** (jene Fläche, die der Basisplatte **3** zugewandt ist) des Isoliersubstrats **8** ausgebildet ist. Insbesondere können die Positionierdrahtfügeabschnitte **20a** bis **20d** in jeweilige Lochabschnitte **21a** bis **21d** eingefügt werden, und dadurch wird das Isoliersubstrat **8** hinsichtlich der Basisplatte **3** positioniert.

**[0019]** Auch wenn die Lochabschnitte **21** an Eckenausbildungen (vier Ecken) eines Rechtecks vorgesehen sein können, das eine Außenumfangsform der Musterlage **9** bildet, wie dies in der **Fig. 2** gezeigt ist, sind die Positionen der Lochabschnitte **21** nicht darauf beschränkt, und sie können in geeigneter Weise in Abhängigkeit von der Anzahl der Positionierdrahtfügeabschnitte **20** und des Verfahrens ihrer Anordnung ausgewählt werden. Zum Beispiel können die Lochabschnitte **21** an Abschnitten vorgesehen sein, die an den Seiten des Rechtecks angrenzen.

**[0020]** Das vorstehend beschriebene Leistungsmodul **1** kann gemäß der nachfolgenden Beschreibung hergestellt werden. Unter Bezugnahme auf die **Fig. 1** werden zunächst das Isoliersubstrat **8**, das die darin ausgebildeten Musterlagen **7, 9** hat, und der Halbleiterchip **10** an der vorderen Fläche **3a** an der Basisplatte **3** durch Löten befestigt. Als nächstes wer-

den der Halbleiterchip **10** und die Musterlage **7** mit dem Leistungsanschluss **4**, dem Signalanschluss **5** und dergleichen über die Leistungsdrähte **4a** und den Signaldraht **5a** verbunden. Nachfolgend werden das Silikongel **12** und der Dichtungskunststoff **13** sequentiell aufgebracht, um den Halbleiterchip **10** abzudichten. Dadurch wird das vorstehend beschriebene Leistungsmodul **1** erhalten.

**[0021]** Als nächstes werden die Merkmale des Leistungsmoduls **1** gemäß dem gegenwärtigen Ausführungsbeispiel beschrieben, und dessen Funktion und Wirkung werden ebenfalls beschrieben. Das Leistungsmodul **1** weist Folgendes auf: die Basisplatte **3** mit der vorderen Fläche **3a**, die mit dem Positionierdrahtfügeabschnitt **20** versehen ist; das Isoliersubstrat **8**, das mit dem Lochabschnitt **21** (Aufnahmeabschnitt) versehen ist, der an einer Seite der hinteren Fläche **8b**, die der Basisplatte **3** zugewandt ist, den Positionierdrahtfügeabschnitt **20** unterbringt, und das an der Basisplatte **3** befestigt ist, indem es hinsichtlich der Basisplatte **3** durch den Lochabschnitt **21** positioniert ist, der den Positionierdrahtfügeabschnitt **20** unterbringt; und den Halbleiterchip **10**, der an einer Seite der vorderen Fläche **8a** des Isoliersubstrats **8**, die von der hinteren Fläche **8b** abgewandt ist, angeordnet ist.

**[0022]** In dem vorgestehend beschriebenen Leistungsmodul **1** kann das Isoliersubstrat **8** an der Basisplatte **3** befestigt werden, indem es hinsichtlich der Basisplatte **3** durch den Positionierdrahtfügeabschnitt **20** positioniert wird, der in dem Lochabschnitt **21** untergebracht ist. Dies vereinfacht des Weiteren die Arbeitsschritte und verbessert die Herstellungseffizienz, wenn dies mit einem Fall verglichen wird, bei dem die Basisplatte selbst verarbeitet wird, um konvexe und konkave Abschnitte oder dergleichen zu bilden, und die konvexen und konkaven Abschnitte zum Positionieren des Isoliersubstrats **8** verwendet werden. Des Weiteren kann der Positionierdrahtfügeabschnitt **20** unter Verwendung derselben Einrichtung hergestellt werden, die zum Verbinden der Leistungsdrähte **4a** und des Signaldrahts **5a** verwendet wird, und die Ankerposition und die Art des Drahts kann in einfacher Weise für die entsprechende Art geändert werden. Da darüber hinaus die Ausbildung eines Resists zum Positionieren des Isoliersubstrats an der Basisplatte weggelassen werden kann, kann die Basisplatte standardisiert werden.

**[0023]** Bei dem vorstehend beschriebenen Leistungsmodul **1** sind viele Positionierdrahtfügeabschnitte **20a** bis **20d** an der vorderen Fläche **3a** der Basisplatte **3** vorgesehen. Zusätzlich sind die vielen Lochabschnitte **21a** bis **21d** (Aufnahmeabschnitte) zum Unterbringen der jeweiligen vielen Positionierdrahtfügeabschnitte **20a** bis **20d** an der Seite der hinteren Fläche **8b** des Isoliersubstrats **8** vorgesehen. Dadurch kann das Isoliersubstrat **8** hinsichtlich der

Basisplatte **3** mit einem höheren Genauigkeitsgrad positioniert werden.

**[0024]** Bei dem vorstehend beschriebenen Leistungsmodul **1** ist der Lochabschnitt **21** (Aufnahmeabschnitt) in der Musterlage **9** vorgesehen, die an der hinteren Fläche **8b** des Isoliersubstrats **8** ausgebildet ist. Das Isoliersubstrat **8** wird hinsichtlich der Basisplatte **3** durch den Positionierdrahtfügeabschnitt **20** positioniert, indem dieser in den Lochabschnitt **21** eingefügt wird. Dadurch kann das Isoliersubstrat **8** hinsichtlich der Basisplatte **3** mit einem noch höheren Genauigkeitsgrad positioniert werden.

(Erste Abwandlung)

**[0025]** Als nächstes wird eine erste Abwandlung des Leistungsmoduls **1** gemäß dem gegenwärtigen Ausführungsbeispiel beschrieben. Die **Fig. 3** zeigt eine Struktur des Isoliersubstrats **8** und der Musterlage **9** bei der gegenwärtigen Abwandlung. Unter Bezugnahme auf die **Fig. 3** sind bei der gegenwärtigen Abwandlung viele Ausschnittabschnitte **22a** bis **22d** (Aufnahmeabschnitte) an Endabschnitten der Musterlage **9** ausgebildet, die an der hinteren Fläche **8b** des Isoliersubstrats **8** ausgebildet ist. Insbesondere hat die Musterlage **9** eine Außenumfangsform in der Gestalt eines Rechtecks, und die Ausschnittabschnitte **22a** bis **22d** sind jeweils an vier Eckenabschnitten des Rechtecks ausgebildet. Das Isoliersubstrat **8** ist so konfiguriert, dass es hinsichtlich der Basisplatte **3** positioniert wird, indem Positionierdrahtfügeabschnitte **20a** bis **20d** (**Fig. 2**) an den jeweiligen Ausschnittabschnitten **22a** bis **22d** angeordnet werden. Dadurch wird die Musterlage **9** noch einfacher verarbeitet, und somit kann die Produktivität noch weiter verbessert werden.

(Zweite Abwandlung)

**[0026]** Als nächstes wird eine zweite Abwandlung des Leistungsmoduls **1** gemäß dem gegenwärtigen Ausführungsbeispiel beschrieben. Die **Fig. 4** zeigt eine Struktur des Isoliersubstrats **8** und der Musterlage **9** bei der gegenwärtigen Abwandlung. Unter Bezugnahme auf die **Fig. 4** sind bei der gegenwärtigen Abwandlung Ausschnittabschnitte **22a**, **22d** ausgebildet, die Abschnitte sind, die durch Ausschneiden von zwei gegenüberliegenden Eckenabschnitten des Rechtecks ausgebildet sind, das die Außenumfangsform der Musterlage **9** bildet. Das Isoliersubstrat **8** ist so konfiguriert, dass es hinsichtlich der Basisplatte **3** positioniert wird, indem Positionierdrahtfügeabschnitte **20a**, **20d** (**Fig. 2**) an den jeweiligen Ausschnittabschnitten **22a**, **22d** angeordnet werden. Dadurch ist die Form der Musterlage **9** noch weiter vereinfacht, und die Produktivität ist weiter verbessert. Zusätzlich kann die Genauigkeit beim Positionieren des Isoliersubstrats **8** hinsichtlich der Basisplatte **3** weiter verbessert werden, indem die Ausschnittabschnitte **22a**

bis **22d** an zwei gegenüberliegenden Eckenabschnitten (die beiden Eckenabschnitte, die voneinander am weitesten entfernt sind) des Rechtecks ausgebildet sind.

### (Dritte Abwandlung)

**[0027]** Als nächstes wird eine dritte Abwandlung des Leistungsmoduls **1** gemäß dem gegenwärtigen Ausführungsbeispiel beschrieben. Die **Fig. 5** zeigt eine Struktur des Isoliersubstrats **8** und der Musterlage **9** bei der gegenwärtigen Abwandlung. Unter Bezugnahme auf die **Fig. 5** ist bei der gegenwärtigen Abwandlung des Weiteren zusätzlich zu den Ausschnittabschnitten **22a, 22d**, die durch Ausschneiden von zwei gegenüberliegenden Eckenabschnitten des Rechtecks ausgebildet sind, das die Außenumfangsform der Musterlage **9** bildet, ein Ausschnittabschnitt **22c** ausgebildet, der ein Abschnitt ist, der durch Ausschneiden von einem Eckenabschnitt gebildet ist, der sich von den beiden Eckenabschnitten unterscheidet. Das Isoliersubstrat **8** ist so konfiguriert, dass es hinsichtlich der Basisplatte **3** durch die Positionierdrahtfügeabschnitte **20a, 20c, 20d** (**Fig. 2**) positioniert wird, die sich an den jeweiligen Ausschnittabschnitten **22a, 22c, 22d** befinden. Dadurch wird eine Neigung des Isoliersubstrats **8** hinsichtlich der Basisplatte **3** unterdrückt, und die Genauigkeit beim Positionieren des Isoliersubstrats **8** hinsichtlich der Basisplatte **3** ist weiter verbessert.

### (Vierte Abwandlung)

**[0028]** Als nächstes wird eine vierte Abwandlung des Leistungsmoduls **1** gemäß dem gegenwärtigen Ausführungsbeispiel beschrieben. Die **Fig. 6** zeigt eine Struktur des Isoliersubstrats **8** und der Musterlage **9** bei der gegenwärtigen Abwandlung. Unter Bezugnahme auf die **Fig. 6** sind bei der gegenwärtigen Abwandlung Ausschnittabschnitte **23a** bis **23d** ausgebildet, die Abschnitte sind, die durch Ausschneiden der Seiten des Rechtecks gebildet sind, das die Außenumfangsform der Musterlage **9** bildet. Das Isoliersubstrat **8** ist so konfiguriert, dass es hinsichtlich der Basisplatte **3** durch die Positionierdrahtfügeabschnitte **20** positioniert wird, die sich an den jeweiligen Ausschnittabschnitten **23a** bis **23d** befinden. Dadurch können zwei oder mehrere Fügestellen in den jeweiligen Positionierdrahtfügeabschnitten **20** vorgesehen werden, die sich an den jeweiligen Ausschnittabschnitten **23a** bis **23d** befinden. Infolgedessen können Stellen vorgesehen werden, an denen die Drahtform durch das Fügen nicht geändert wird, und ein Abstand entsprechend dem Drahdurchmesser zwischen der Basisplatte **3** und dem Isoliersubstrat **8** kann noch zuverlässiger gewährleistet werden.

### (Ausführungsbeispiel 2)

**[0029]** Als nächstes wird ein Ausführungsbeispiel **2** als ein anderes Ausführungsbeispiel der vorliegenden Erfindung beschrieben. Ein Halbleitermodul gemäß dem gegenwärtigen Ausführungsbeispiel hat grundsätzlich dieselbe Konfiguration und zeigt dieselbe Wirkung wie das Halbleitermodul gemäß Ausführungsbeispiel **1**. Jedoch unterscheidet sich das Halbleitermodul gemäß dem gegenwärtigen Ausführungsbeispiel von dem Halbleitermodul gemäß Ausführungsbeispiel **1**, indem es des Weiteren eine Steuerschaltung zum Antreiben des Halbleiterchips aufweist.

**[0030]** Unter Bezugnahme auf die **Fig. 7** hat ein Leistungsmodul **1A** als das Halbleitermodul gemäß dem gegenwärtigen Ausführungsbeispiel des Weiteren eine Steuerschaltung, die aus einem Relaisanschluss **14**, einem gedruckten Substrat **15**, vielen SMT-Komponenten (Surface-Mount-Technology-Komponenten) **16** und einer Schnittstelle **17** zusätzlich zu der Konfiguration des Leistungsmoduls **1** gemäß Ausführungsbeispiel **1** (**Fig. 1**) besteht. Diese Steuerschaltung kann den Halbleiterchip **10** antreiben.

**[0031]** Der Relaisanschluss **14** erstreckt sich so, dass er sich dem Halbleiterchip **10** annähert, und er ist mit dem Halbleiterchip **10** durch einen Steuerdraht **14a** verbunden. Das gedruckte Substrat **15** ist an dem Silikongel **12** angeordnet, und die vielen SMT-Komponenten **16** sind so angeordnet, dass sie an einer vorderen Fläche des gedruckten Substrats **15** nebeneinander platziert sind. Die Schnittstelle **17** hat einen Endabschnitt, der mit dem gedruckten Substrat **15** verbunden ist, und der andere Endabschnitt erstreckt sich zu der Außenseite des Gehäuses **2**. So mit ist das Leistungsmodul **1A** gemäß dem gegenwärtigen Ausführungsbeispiel ein intelligentes Leistungsmodul (IPM), das die Steuerschaltung zum Antreiben des Halbleiterchips **10** aufweist.

**[0032]** Das Halbleitermodul gemäß der vorliegenden Erfindung ist in vorteilhafter Weise insbesondere auf ein Halbleitermodul anwendbar, das eine Reduzierung der Herstellungseffizienz unterdrückt und ein Isoliersubstrat hinsichtlich einer Basisplatte mit einem hohen Genauigkeitsgrad positioniert.

### Patentansprüche

1. Halbleitermodul (1, 1A) mit:

einer Basisplatte (3), die eine vordere Fläche (3a) hat, die mit einem Positionierdrahtfügeabschnitt (20, 20a, 20b, 20c, 20d) versehen ist;

einem Isoliersubstrat (8), das mit einem Aufnahmeabschnitt (21, 21a, 21b, 21c, 21d, 22, 22a, 22b, 22c, 22d, 23, 23a, 23b, 23c, 23d) versehen ist, der den Positionierdrahtfügeabschnitt (20, 20a, 20b, 20c, 20d)

an einer Seite einer hinteren Fläche (8b) unterbringt, die der Basisplatte (3) zugewandt ist, und das an der Basisplatte (3) befestigt ist, indem es hinsichtlich der Basisplatte (3) durch den Aufnahmeabschnitt (21, 21a, 21b, 21c, 21d, 22, 22a, 22b, 22c, 22d, 23, 23a, 23b, 23c, 23d) positioniert ist, der den Positionierdrahtfügeabschnitt (20, 20a, 20b, 20c, 20d) unterbringt; und einem Halbleiterchip (10), der an einer Seite einer vorderen Fläche (8a) des Isoliersubstrats (8), die der hinteren Fläche (8b) abgewandt ist, angeordnet ist, wobei der Aufnahmeabschnitt (21, 21a, 21b, 21c, 21d, 22, 22a, 22b, 22c, 22d, 23, 23a, 23b, 23c, 23d) ein Lochabschnitt (21, 21a, 21b, 21c, 21d) ist, der in einer Musterlage (9) vorgesehen ist, die an der hinteren Fläche (8b) des Isoliersubstrats (8) ausgebildet ist, und das Isoliersubstrat (8) hinsichtlich der Basisplatte (3) durch den Positionierdrahtfügeabschnitt (20, 20a, 20b, 20c, 20d) positioniert ist, der in den Lochabschnitt (21, 21a, 21b, 21c, 21d) eingefügt ist.

2. Halbleitermodul (1, 1A) gemäß Anspruch 1, wobei der Lochabschnitt (21, 21a, 21b, 21c, 21d) an einem Eckenabschnitt eines Rechtecks vorgesehen ist, das eine Außenenumfangsform der Musterlage (9) bildet, oder an einem Abschnitt angrenzend an einer Seite des Rechtecks.

3. Halbleitermodul (1, 1A) mit: einer Basisplatte (3), die eine vordere Fläche (3a) hat, die mit einem Positionierdrahtfügeabschnitt (20, 20a, 20b, 20c, 20d) versehen ist; einem Isoliersubstrat (8), das mit einem Aufnahmeabschnitt (21, 21a, 21b, 21c, 21d, 22, 22a, 22b, 22c, 22d, 23, 23a, 23b, 23c, 23d) versehen ist, der den Positionierdrahtfügeabschnitt (20, 20a, 20b, 20c, 20d) an einer Seite einer hinteren Fläche (8b) unterbringt, die der Basisplatte (3) zugewandt ist, und das an der Basisplatte (3) befestigt ist, indem es hinsichtlich der Basisplatte (3) durch den Aufnahmeabschnitt (21, 21a, 21b, 21c, 21d, 22, 22a, 22b, 22c, 22d, 23, 23a, 23b, 23c, 23d) positioniert ist, der den Positionierdrahtfügeabschnitt (20, 20a, 20b, 20c, 20d) unterbringt; und einem Halbleiterchip (10), der an einer Seite einer vorderen Fläche (8a) des Isoliersubstrats (8), die der hinteren Fläche (8b) abgewandt ist, angeordnet ist, wobei der Aufnahmeabschnitt (21, 21a, 21b, 21c, 21d, 22, 22a, 22b, 22c, 22d, 23, 23a, 23b, 23c, 23d) ein Ausschnittabschnitt (22, 22a, 22b, 22c, 22d, 23, 23a, 23b, 23c, 23d) ist, der an einem Endabschnitt einer Musterlage (9) vorgesehen ist, die an der hinteren Fläche (8b) des Isoliersubstrats (8) ausgebildet ist, und das Isoliersubstrat (8) hinsichtlich der Basisplatte (3) durch den Positionierdrahtfügeabschnitt (20, 20a, 20b, 20c, 20d) positioniert ist, der sich an dem Aus-

schnittabschnitt (22, 22a, 22b, 22c, 22d, 23, 23a, 23b, 23c, 23d) befindet.

4. Halbleitermodul (1, 1A) gemäß Anspruch 3, wobei der Ausschnittabschnitt (22, 22a, 22b, 22c, 22d, 23, 23a, 23b, 23c, 23d) einen Abschnitt (22a, 22d) aufweist, der durch Ausschneiden von jeweils zwei gegenüberliegenden Eckenabschnitten eines Rechtecks ausgebildet ist, das eine Außenenumfangsform der Musterlage (9) bildet.

5. Halbleitermodul (1, 1A) gemäß Anspruch 4, wobei der Ausschnittabschnitt (22, 22a, 22b, 22c, 22d, 23, 23a, 23b, 23c, 23d) des Weiteren einen Abschnitt (22c) aufweist, der durch Ausschneiden von einem Eckenabschnitt ausgebildet ist, der sich von den beiden Eckenabschnitten unterscheidet.

6. Halbleitermodul (1, 1A) gemäß Anspruch 3, wobei der Ausschnittabschnitt (22, 22a, 22b, 22c, 22d, 23, 23a, 23b, 23c, 23d) des Weiteren einen Abschnitt (23, 23a, 23b, 23c, 23d) aufweist, der durch Ausschneiden einer Seite eines Rechtecks ausgebildet ist, das eine Außenenumfangsform der Musterlage (9) bildet.

7. Halbleitermodul (1, 1A) gemäß einem der Ansprüche 1 bis 6, des Weiteren mit einer Steuerschaltung (14, 15, 16, 17) zum Antreiben des Halbleiterchips (10).

8. Halbleitermodul (1, 1A), gemäß einem der Ansprüche 1 bis 7, wobei viele der Positionierdrahtfügeabschnitte (20, 20a, 20b, 20c, 20d) an der vorderen Fläche (3a) der Basisplatte (3) vorgesehen sind, und viele der Aufnahmeabschnitte (21, 21a, 21b, 21c, 21d, 22, 22a, 22b, 22c, 22d, 23, 23a, 23b, 23c, 23d), die die vielen, jeweiligen Positionierdrahtfügeabschnitte (20, 20a, 20b, 20c, 20d) unterbringen, an der Seite der hinteren Fläche (8b) des Isoliersubstrats (8) vorgesehen sind.

Es folgen 3 Seiten Zeichnungen

## Anhängende Zeichnungen

FIG.1

FIG.2

FIG.3

FIG.4

FIG.5

FIG.6

FIG.7