(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7204454号**

**(P7204454)**

(45)発行日 令和5年1月16日(2023.1.16)

(24)登録日 令和5年1月5日(2023.1.5)

(51)国際特許分類

|                         |     |              |         |

|-------------------------|-----|--------------|---------|

| H 01 L 29/78 (2006.01)  | F I | H 01 L 29/78 | 6 5 2 G |

| H 01 L 29/12 (2006.01)  |     | H 01 L 29/78 | 6 5 2 T |

| H 01 L 21/336 (2006.01) |     | H 01 L 29/78 | 6 5 3 A |

|                         |     | H 01 L 29/78 | 6 5 2 J |

|                         |     | H 01 L 29/78 | 6 5 8 E |

請求項の数 7 (全17頁) 最終頁に続く

(21)出願番号 特願2018-225629(P2018-225629)

(22)出願日 平成30年11月30日(2018.11.30)

(65)公開番号 特開2020-88343(P2020-88343A)

(43)公開日 令和2年6月4日(2020.6.4)

審査請求日 令和3年7月12日(2021.7.12)

(73)特許権者 000003609

株式会社豊田中央研究所

愛知県長久手市横道41番地の1

(73)特許権者 000004260

株式会社デンソー

愛知県刈谷市昭和町1丁目1番地

(74)代理人 110000110

弁理士法人 快友国際特許事務所

朽木 克博

(72)発明者 愛知県長久手市横道41番地の1 株式

会社豊田中央研究所内

山下 侑佑

(72)発明者 愛知県長久手市横道41番地の1 株式

会社豊田中央研究所内

副島 成雅

最終頁に続く

(54)【発明の名称】 半導体装置

**(57)【特許請求の範囲】****【請求項1】**

化合物半導体を有する縦型の半導体装置であって、

負荷短絡時に大電流が流れることに応じて発熱する前記化合物半導体の特定領域が、前記化合物半導体よりも線膨張係数が小さい特定材料を含み、

前記化合物半導体は、

基板と、

前記基板の上に設けられている第1導電型のドリフト領域と、

前記ドリフト領域の上に設けられており、互いに離間している第2導電型の一対のボディ領域であって、前記化合物半導体の上面に露出している前記一対のボディ領域と、

前記ドリフト領域の上であり、かつ、前記一対のボディ領域の間に設けられている前記第1導電型のJ F E T領域であって、前記一対のボディ領域のそれぞれに接触しており、前記化合物半導体の上面に露出している前記J F E T領域と、

を備え、

前記半導体装置は、さらに、

ゲート絶縁膜を介して、前記化合物半導体の上面に設けられているゲート電極であって、前記ゲート絶縁膜を介して、前記一対のボディ領域の一部、及び、前記J F E T領域に対向する前記ゲート電極を備え、

前記特定領域は、前記半導体装置を前記化合物半導体の上面の垂直上方から見たときに、前記一対のボディ領域の間に設けられており、

前記特定領域は、前記ドリフト領域内に設けられており、

前記特定領域の下端は、前記ドリフト領域の下端よりも上方に位置している、半導体装置。

【請求項 2】

前記特定領域は、前記一対のボディ領域の下面よりも下方側であり、かつ、前記半導体装置を前記化合物半導体の上面の垂直上方から見たときに、前記一対のボディ領域の間に設けられており、前記一対のボディ領域の下方に設けられていない、請求項1に記載の半導体装置。

【請求項 3】

前記ドリフト領域は、前記基板の上に設けられている第1ドリフト領域と、前記第1ドリフト領域の上に設けられている第2ドリフト領域と、を備えており、

10

前記一対のボディ領域及び前記J F E T領域は、前記第2ドリフト領域の上に設けられており、

前記特定領域は、前記第1ドリフト領域に設けられており、

前記特定領域の上端は、前記第1ドリフト領域と前記第2ドリフト領域との間の界面と一致する、請求項1又は2に記載の半導体装置。

【請求項 4】

複数の前記特定領域を備え、

前記半導体装置を前記化合物半導体の上面の垂直上方から見たときに、前記複数の特定領域のそれぞれが離間している、請求項1～3のいずれか一項に記載の半導体装置。

【請求項 5】

前記特定材料は、導電性のSi、導電性のC、又は、導電性を有する多結晶のSiCである、請求項1～4のいずれか一項に記載の半導体装置。

20

【請求項 6】

前記特定材料は、絶縁体であるSiO<sub>2</sub>又は空気である、請求項1～5のいずれか一項に記載の半導体装置。

【請求項 7】

前記化合物半導体は、SiC又はGaNである、請求項1～6のいずれか一項に記載の半導体装置。

【発明の詳細な説明】

【技術分野】

30

【0001】

本明細書が開示する技術は、半導体装置に関する。

【背景技術】

【0002】

特許文献1には、化合物半導体を有する縦型の半導体装置が開示されている。化合物半導体は、基板と、エピタキシャル層と、を備える。エピタキシャル層は、一対のウェル領域と、J F E T領域と、を備える。一対のウェル領域は、基板の上方に設けられており、化合物半導体の上面に露出している。J F E T層は、基板の上方であって、一対のウェル領域の間に設けられている。J F E T層は、一対のウェル領域のそれぞれに接しており、化合物半導体の上面に露出している。特許文献1の半導体装置では、一対のウェル領域の間の幅、即ち、J F E T領域の幅を狭くすることによって、負荷短絡時に半導体装置を流れる電流量を抑制している。

40

【先行技術文献】

【特許文献】

【0003】

【文献】特開2012-33731号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

特許文献1の半導体装置では、電流経路であるJ F E T領域の幅が狭いために、負荷短

50

絡時に、化合物半導体の特定領域に電流が集中する。この場合、特定領域が自己発熱し、特定領域が局所的に熱膨張する。特定領域が局所的に熱膨張することによって、半導体装置に熱応力が作用し、半導体装置に異常が発生し得る。本明細書は、負荷短絡時における信頼性の高い半導体装置を提供することを目的とする。

**【課題を解決するための手段】**

**【0005】**

本明細書が開示する化合物半導体を有する縦型の半導体装置は、負荷短絡時に大電流が流れることに応じて発熱する前記化合物半導体の特定領域が、前記化合物半導体よりも線膨張係数が小さい特定材料を含む。

**【0006】**

上記の構成によると、特定領域が、化合物半導体よりも線膨張係数が小さい特定材料を含んでいる。このため、特定領域が、化合物半導体よりも線膨張係数が小さい特定材料を含まない場合と比較して、特定領域が熱膨張することを抑制することができる。従って、負荷短絡時に、特定領域が熱膨張することによって、半導体装置に作用する熱応力を低減することができ、半導体装置に異常が発生することを抑制することができる。従って、半導体装置の信頼性を向上させることができる。

**【0007】**

上記の化合物半導体は、基板と、基板の上に設けられている第1導電型のドリフト領域と、ドリフト領域の上に設けられており、互いに離間している第2導電型の一対のボディ領域であって、化合物半導体の上面に露出している一対のボディ領域と、ドリフト領域の上であり、かつ、一対のボディ領域の間に設けられている第1導電型のJ F E T領域であって、一対のボディ領域のそれぞれに接触しており、化合物半導体の上面に露出しているJ F E T領域と、を備えていてもよい。半導体装置は、さらに、ゲート絶縁膜を介して、化合物半導体の上面に設けられているゲート電極であって、ゲート絶縁膜を介して、一対のボディ領域の一部、及び、J F E T領域に対向するゲート電極を備え、特定領域は、半導体装置を化合物半導体の上面の垂直上方から見たときに、一対のボディ領域の間に設けられていてもよい。効果の詳細は実施例で説明する。

**【0008】**

特定領域は、一対のボディ領域の下面よりも下方側であり、かつ、半導体装置を化合物半導体の上面の垂直上方から見たときに、一対のボディ領域の間に設けられていてもよい。効果の詳細は実施例で説明する。

**【0009】**

上記の化合物半導体は、基板と、基板の上に設けられている第1導電型のドリフト領域と、ドリフト領域の上に設けられている第2導電型のボディ領域であって、ボディ領域の一部は、化合物半導体の上面に露出するボディ領域と、ボディ領域の上に設けられており、化合物半導体の上面に露出する第1導電型のソース領域と、化合物半導体の上面から、ソース領域、及び、ボディ領域を貫通して、ドリフト領域に到達するトレンチと、を備えてよい。半導体装置は、さらに、トレンチ内に設けられているトレンチゲートを備え、特定領域は、トレンチの底面よりも下方側であり、かつ、半導体装置を化合物半導体の上面の垂直上方から見たときに、トレンチが形成されている範囲内に設けられていてもよい。効果の詳細は実施例で説明する。

**【0010】**

上記の半導体装置は、複数の特定領域を備え、半導体装置を化合物半導体の上面の垂直上方から見たときに、複数の特定領域のそれぞれが離間していてもよい。効果の詳細は実施例で説明する。

**【0011】**

特定材料は、導電性のS i、導電性のC、又は、導電性を有する多結晶のS i cであってもよい。効果の詳細は実施例で説明する。

**【0012】**

特定材料は、絶縁体であるS i O<sub>2</sub>又は空気であってもよい。効果の詳細は実施例で説

10

20

30

40

50

明する。

**【0013】**

化合物半導体は、SiC又はGaNであってもよい。効果の詳細は実施例で説明する。

**【図面の簡単な説明】**

**【0014】**

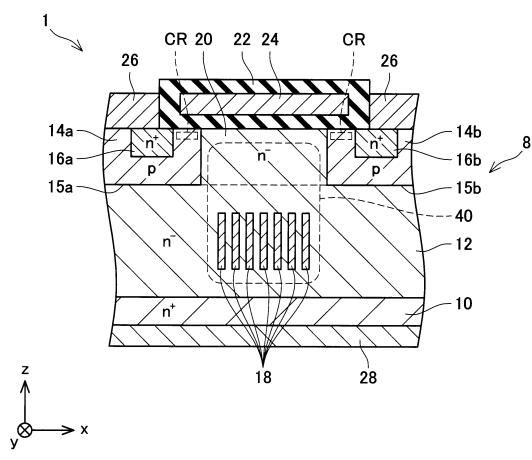

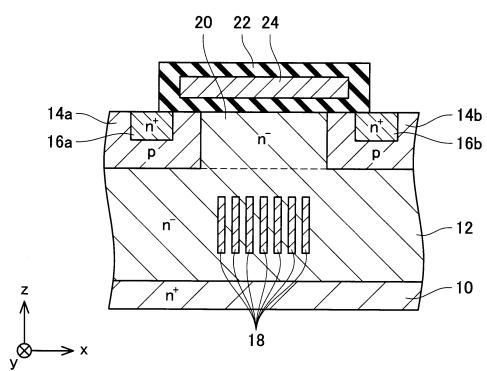

**【図1】**第1実施例の半導体装置の要部断面図である。

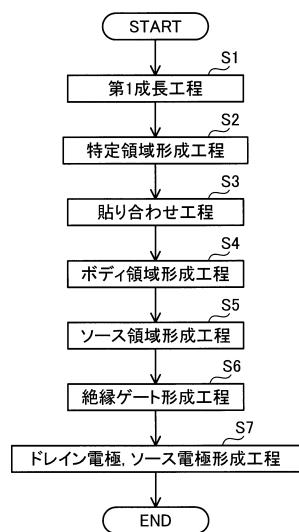

**【図2】**第1実施例の半導体装置の製造方法を示すフローチャートである。

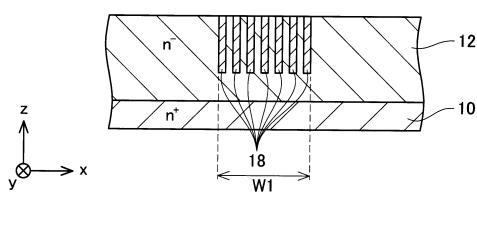

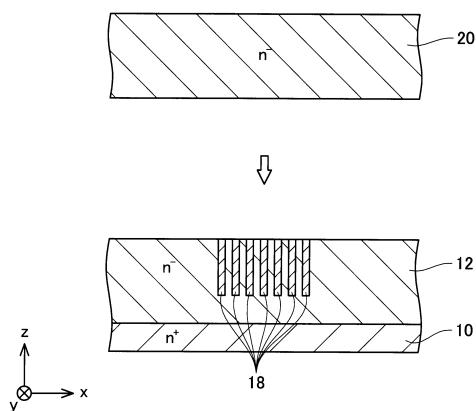

**【図3】**第1実施例の半導体装置の製造工程を示す図である(1)。

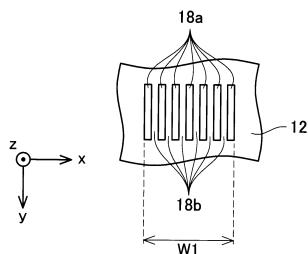

**【図4】**図3の半導体装置を垂直上方から見た図である。

**【図5】**第1実施例の半導体装置の製造工程を示す図である(2)。

10

**【図6】**第1実施例の半導体装置の製造工程を示す図である(3)。

**【図7】**第1実施例の半導体装置の製造工程を示す図である(4)。

**【図8】**第1実施例の半導体装置の製造工程を示す図である(5)。

**【図9】**第1実施例の半導体装置の製造工程を示す図である(6)。

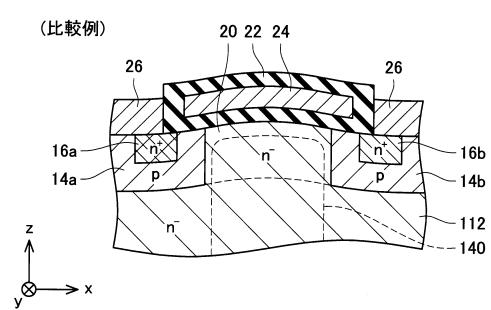

**【図10】**比較例の半導体装置において、負荷短絡時の半導体装置を示す図である。

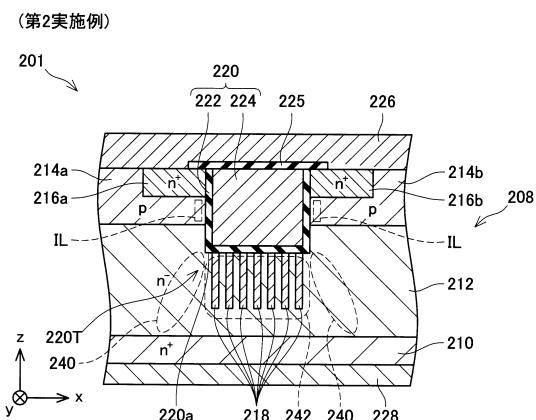

**【図11】**第2実施例の半導体装置の要部断面図である。

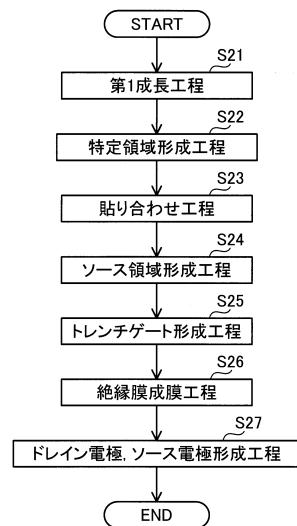

**【図12】**第2実施例の半導体装置の製造方法を示すフローチャートである。

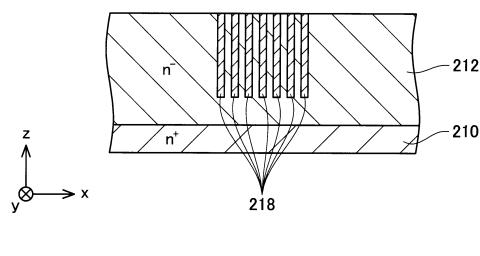

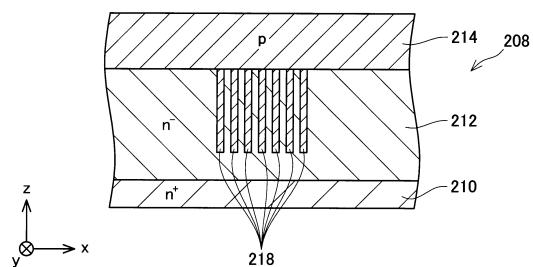

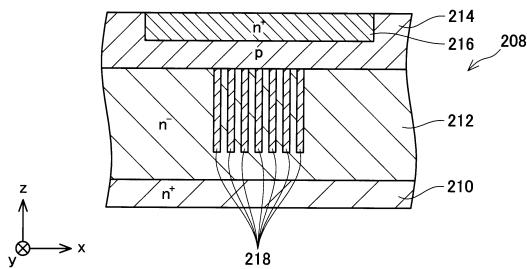

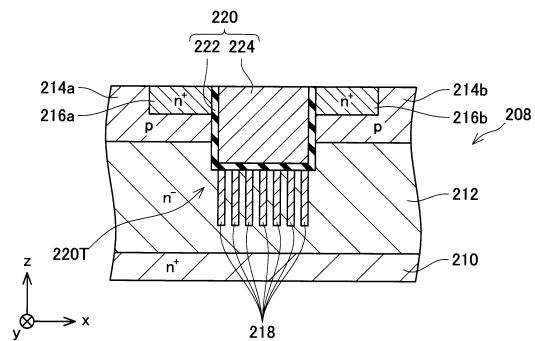

**【図13】**第2実施例の半導体装置の製造工程を示す図である(1)。

**【図14】**第2実施例の半導体装置の製造工程を示す図である(2)。

20

**【図15】**第2実施例の半導体装置の製造工程を示す図である(3)。

**【図16】**第2実施例の半導体装置の製造工程を示す図である(4)。

**【図17】**第2実施例の半導体装置の製造工程を示す図である(5)。

**【図18】**第3実施例の半導体装置の要部断面図である。

**【図19】**第4実施例の半導体装置の要部断面図である。

**【図20】**第5実施例の半導体装置の要部断面図である。

**【発明を実施するための形態】**

**【0015】**

(第1実施例)

図1の要部断面図に示されるように、半導体装置1は、縦型のMOSFETである。半導体装置1は、プレーナゲート構造を有する。半導体装置1は、化合物半導体8、ゲート絶縁膜22、ゲート電極24、ソース電極26、及び、ドレイン電極28を備えている。

30

**【0016】**

化合物半導体8は、基板10、n<sup>-</sup>型のドリフト領域12、p型の一対のボディ領域14a、14b、n<sup>+</sup>型のソース領域16a、16b、複数の特定領域18、及び、n<sup>-</sup>型のJFET(Junction Field Effect Transistor)領域20を備えている。

**【0017】**

基板10は、n型不純物を高濃度に含むSiCの単結晶基板である。基板10の裏面全体にドレイン電極28がオーミック接觸している。基板10は、ドリフト領域12がエピタキシャル成長するための下地板である。

**【0018】**

ドリフト領域12は、基板10の上に半導体物質をエピタキシャル成長させた層である。ドリフト領域12は、基板10よりもn型不純物を低濃度に含む。

40

**【0019】**

p型の一対のボディ領域14a、14bは、ドリフト領域12の上に設けられており、互いに離間している。なお、一対のボディ領域14a、14bを以下では、「ボディ領域14」と総称する場合がある。ボディ領域14の一部は、化合物半導体8の上面に露出している。ボディ領域14のうち、後述するソース領域16とJFET領域20に挟まれた部分は、チャネル領域CRと呼ばれることがある。

**【0020】**

JFET領域20は、ドリフト領域12の上であり、かつ、一対のボディ領域14a、

50

14bの間に設けられている。J F E T 領域 20 は、一対のボディ領域 14a、14b のそれぞれに接触しており、化合物半導体 8 の上面に露出している。J F E T 領域 20 は、ドリフト領域 12 と連続しており、ドリフト領域 12 と一体である。説明の都合上、図 1 では、破線で J F E T 領域 20 をドリフト領域 12 から区別している。J F E T 領域 20 は、ドリフト領域 12 と同じ組成である。

#### 【 0 0 2 1 】

$n^+$  型の一対のソース領域 16a、16b のそれぞれは、一対のボディ領域 14a、14b に囲まれており、化合物半導体 8 の上面に露出している。一対のソース領域 16a、16b は、ボディ領域 14a、14b によって、ドリフト領域 12 及び J F E T 領域 20 から隔てられている。なお、以下では、一対のソース領域 16a、16b を「ソース領域 16」と総称する場合がある。ソース領域 16 にソース電極 26 がオーミック接觸している。なお、ボディ領域 14 の表層でソース領域 16 に接するように p 型の半導体領域であるコンタクト領域が設けられることがあるが、図 1 では、コンタクト領域の図示は省略した。コンタクト領域は、p 型不純物をボディ領域 14 よりも高濃度に含む。

10

#### 【 0 0 2 2 】

ゲート電極 24 は、ゲート絶縁膜 22 を介して、化合物半導体 8 の上面に設けられている。ゲート電極 24 は、ポリシリコンからなる。ゲート電極 24 は、ゲート絶縁膜 22 を介して、一対のボディ領域 14a、14b の一部、一対のソース領域 16a、16b の一部、及び、J F E T 領域 20 と対向するように配置されている。ゲート電極 24 は、半導体装置 1 を垂直上方 (z 軸上方) から見たときに、一端が一方のボディ領域 14a と重なり、他端が他方のボディ領域 14b と重なるように配置されている。基板 10 と平行な平板状のゲート電極 24 を有しているので、半導体装置 1 は、プレーナゲート型と呼ばれる。

20

#### 【 0 0 2 3 】

複数の特定領域 18 は、化合物半導体 8 のドリフト領域 12 に設けられている。複数の特定領域 18 は、ドリフト領域 12 を構成する単結晶の SiC よりも線膨張係数が小さい特定材料からなる。SiC の線膨張係数は、 $4.5 \times 10^{-6} / K$  である。本実施例において、特定材料は、導電性の Si である。Si の線膨張係数は、 $3.9 \times 10^{-6} / K$  であり、SiC の線膨張係数よりも小さい。複数の特定領域 18 は、ボディ領域 14a、14b の下面 15a、15b よりも下方側に設けられており、かつ、半導体装置 1 を垂直上方から見たときに、一対のボディ領域 14 の間に設けられている。また、半導体装置 1 を垂直上方から見たときに、複数の特定領域 18 のそれぞれが離間している。

30

#### 【 0 0 2 4 】

半導体装置 1 の動作について説明する。半導体装置 1 は、ドレイン電極 28 にソース電極 26 よりも高い電圧が印加され、かつ、ゲート電極 24 に閾値電圧よりも高い電圧が印加されると、オン状態となる。オン状態では、チャネル領域 CR のゲート絶縁膜 22 の近傍に n 型の反転層が形成され、ドレイン電極 28 とソース電極 26 の間が導通する。一方、半導体装置 1 は、ドレイン電極 28 にソース電極 26 よりも高い電圧が印加され、かつ、ゲート電極 24 に閾値電圧以下の電圧が印加されると、反転層が消失し、オフ状態となる。このように、半導体装置 1 は、ゲート電極 24 に印加する電圧に基づいてオンとオフが切り換えられるスイッチング素子として機能する。

40

#### 【 0 0 2 5 】

##### ( 複数の特定領域 18 の効果 )

負荷短絡によってドレイン電極 28 に高い電圧が印加されると、ドレイン電極 28 からソース電極 26 に大電流が流れる。具体的には、ドレイン電極 28、基板 10、ドリフト領域 12、J F E T 領域 20、ボディ領域 14 の反転層、ソース領域 16、ソース電極 26 という順番で電流が流れる。このような状況において、図 1 に示す電流集中領域 40 に大電流が流れる。具体的には、電流集中領域 40 は、J F E T 領域 20 の一部、及び、ドリフト領域 12 のうち J F E T 領域 20 の下方の領域である。電流集中領域 40 は、大電流が流れることによって発熱する。

#### 【 0 0 2 6 】

50

本実施例の半導体装置 1 の効果について説明する前に、図 10 を参照して、比較例の半導体装置について説明する。比較例の半導体装置は、ドリフト領域 112 に複数の特定領域 18 が設けられていない点を除いて、本実施例の半導体装置 1 と同様の構造を有する。従って、比較例の半導体装置においても、負荷短絡が発生すると、電流集中領域 140 に大電流が流れる。比較例の半導体装置は、複数の特定領域 18 を有さない。即ち、電流集中領域 140 全体が、SiC で構成されている。このため、電流集中領域 140 における線膨張係数は、複数の特定領域 18 が形成されている場合よりも、大きい。このため、図 10 に示すように、負荷短絡が発生すると、電流集中領域 140 に大電流が集中し、電流集中領域 140 が発熱する。このため、ドリフト領域 112 及び J F E T 領域 20 の一部が熱膨張し、その結果、比較例の半導体装置に大きな熱応力が作用する。この熱応力によって、ゲート絶縁膜 22 等が変形し、ゲート絶縁膜 22 等に亀裂等が発生し得る。ゲート絶縁膜 22 等に亀裂が発生すると、比較例の半導体装置に異常が発生する。

#### 【0027】

一方、図 1 に示すように、本実施例の半導体装置 1 では、電流集中領域 40 に、複数の特定領域 18 が形成されている。上述のように、複数の特定領域 18 の線膨張係数は、SiC の線膨張係数よりも小さい。このため、電流集中領域 40 に大電流が流れ、電流集中領域 40 が発熱しても、複数の特定領域 18 が熱膨張することを抑制することができる。複数の特定領域 18 の熱膨張が抑制されることによって、半導体装置 1 に作用する熱応力を低減することができる。即ち、比較例の半導体装置と比較して、負荷短絡時におけるゲート絶縁膜 22 等の変形量を低減することができる。この結果、半導体装置 1 に異常が発生することを抑制することができ、半導体装置 1 の信頼性を向上させることができる。

#### 【0028】

##### (半導体装置 1 の製造方法)

次に、図 2 ~ 図 9 を参照して、半導体装置 1 の製造方法を説明する。図 2 のフローチャートのステップ S1において、SiC を材料とする n 型の基板 10 の主面上に、周知のエピタキシャル成長技術を用いて n 型のドリフト領域 12 を堆積させる（第 1 成長工程）。エピタキシャル成長技術の一例は、有機金属化合物気相成長法（MOCVD 法）である。

#### 【0029】

ステップ S2において、ドリフト領域 12 に、複数の特定領域 18 を形成する（特定領域形成工程）（図 3 参照）。具体的には、周知のフォトリソグラフィー技術及びドライエッチング加工を用いて、ドリフト領域 12 上に、複数の特定領域 18 が開口しているマスクを加工する。次いで、ドライエッチングを利用して、開口が形成されている領域のドリフト領域 12 を除去して、複数の特定領域 18 に対応する複数のスリット 18a を形成する（図 4 参照）。複数のスリット 18a は、幅 W1 の範囲内において、間隔 18b を隔てて形成される。次いで、ドリフト領域 12 上のマスクを除去した後に、化学気相堆積法（CVD 法）を用いて、複数のスリット 18a 内に Si を堆積させる。次いで、周知の CMP（chemical mechanical polishing）技術を用いて、ドリフト領域 12 の上面を研磨する。

#### 【0030】

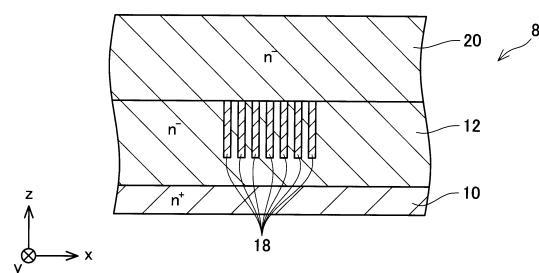

ステップ S3において、図 5 に示すように、ドリフト領域 12 の上面に、n 型の半導体基板 20 を貼り合わせる（貼り合わせ工程）。これにより、図 6 の化合物半導体 8 が形成される。なお、変形例では、周知のエピタキシャル成長技術を用いて、ドリフト領域 12 上に、n 型の半導体領域を成長させてよい。

#### 【0031】

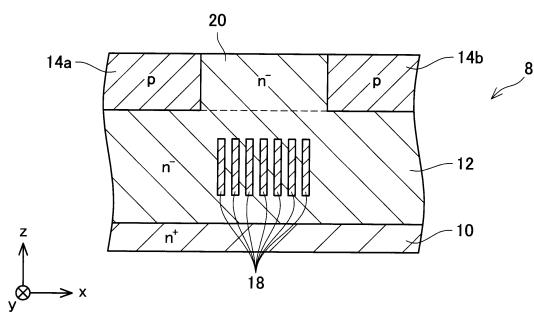

ステップ S4において、化合物半導体 8 に、ボディ領域 14 を形成する（ボディ領域形成工程）。具体的には、周知のフォトリソグラフィー技術及びドライエッチング加工を用いて、化合物半導体 8 上に、ボディ領域 14 が開口しているマスクを加工する。次いで、マスクを介して p 型の不純物イオンを注入する。これにより、化合物半導体 8 に、一対のボディ領域 14a、14b が形成される。そして、一対のボディ領域 14a、14b の間に残った領域が J F E T 領域 20 となる（図 7 参照）。なお、変形例では、ステップ S3

において、ドリフト領域 12 上に p 型の半導体領域を堆積させ、ステップ S4 において、JFET 領域 20 に n 型の不純物を注入してもよい。

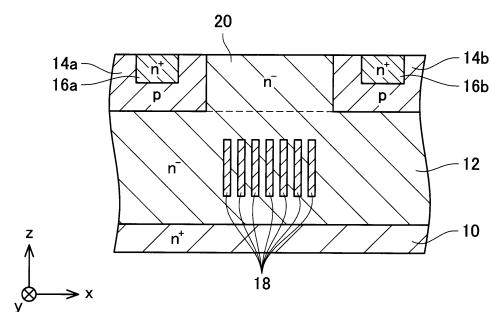

#### 【0032】

ステップ S5 において、化合物半導体 8 に、ソース領域 16 を形成する（ソース領域形成工程）。具体的には、周知のフォトリソグラフィー技術及びドライエッチング加工を用いて、化合物半導体 8 上に、ソース領域 16 が開口しているマスクを加工する。次いで、マスクを介して n 型の不純物イオンを注入する。これにより、化合物半導体 8 に、ソース領域 16 が形成される（図 8 参照）。

#### 【0033】

ステップ S6 において、化合物半導体 8 上に、ゲート絶縁膜 22 及びゲート電極 24 を形成する（ゲート電極形成工程）。まず、周知のフォトリソグラフィー技術及びドライエッチング加工を用いて、化合物半導体 8 上に、ゲート絶縁膜 22 が形成される領域が開口しているマスクを加工する。次いで、CVD 法又は原子層堆積法（ALD 法）を用いて、化合物半導体 8 上に、シリコン酸化膜を成膜する。次いで、シリコン酸化膜上にゲート電極 24 を形成する。具体的には、シリコン酸化膜上に、ポリシリコンを堆積する。次いで、ゲート電極 24 以外の領域に形成されているポリシリコンを除去する。これにより、ゲート電極 24 が形成される。次いで、シリコン酸化膜及びゲート電極 24 上に、さらに、シリコン酸化膜を成膜する。これにより、ゲート絶縁膜 22 が形成される（図 9 参照）。

10

#### 【0034】

ステップ S7 において、化合物半導体 8 上にソース電極 26 を形成し、化合物半導体 8 の下面にドレイン電極 28 を形成する（ドレイン電極、ソース電極形成工程）。これにより、図 1 に示す半導体装置 1 が完成する。

20

#### 【0035】

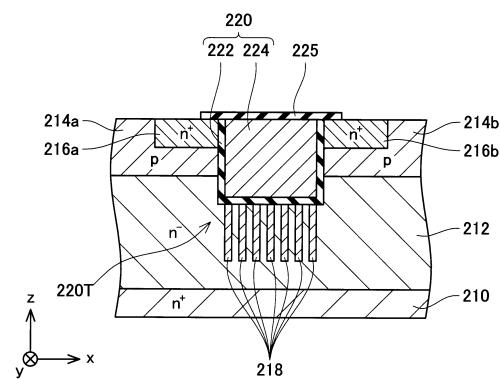

##### （第 2 実施例）

図 11 に、第 2 実施例の半導体装置 201 の要部断面図を示す。半導体装置 201 は、縦型の MOSFET であり、トレンチゲート型である。半導体装置 201 は、化合物半導体 208、トレンチゲート 220、絶縁膜 225、ソース電極 226、及び、ドレイン電極 228 を備えている。

#### 【0036】

化合物半導体 208 は、基板 210、n<sup>-</sup>型のドリフト領域 212、p 型の一対のボディ領域 214a、214b、n<sup>+</sup>型のソース領域 216a、216b、及び、複数の特定領域 218 を備えている。基板 210 は、SiC の単結晶基板である。ドリフト領域 212 は、基板 210 の上に設けられている。一対のボディ領域 214a、214b は、ドリフト領域 212 の上に設けられており、一対のボディ領域 214a、214b の一部は、化合物半導体 8 の上面に露出している。なお、一対のボディ領域 214a、214b を以下では、「ボディ領域 214」と総称する場合がある。n<sup>+</sup>型の一対のソース領域 216a、216b のそれぞれは、一対のボディ領域 214a、214b の上に設けられており、化合物半導体 208 の上面に露出している。

30

#### 【0037】

化合物半導体 208 の表層部には、トレンチゲート 220 が形成されている。トレンチゲート 220 は、トレンチ 220T 内に設けられている。トレンチ 220T は、ソース領域 216、及び、ボディ領域 214 を貫通してドリフト領域 212 の一部に到達している。トレンチゲート 220 は、ゲート電極 224、及び、シリコン酸化膜からなるゲート絶縁膜 222 を有している。

40

#### 【0038】

化合物半導体 8 の上面には、ソース電極 226 が形成されている。ゲート電極 224、ソース電極 226 は、絶縁膜 225 によって絶縁されている。

#### 【0039】

半導体装置 201 の動作について説明する。半導体装置 201 は、ドレイン電極 228 にソース電極 226 よりも高い電圧が印加され、かつ、ゲート電極 224 に閾値電圧より

50

も高い電圧が印加されると、オン状態となる。オン状態では、トレンチゲート 220 の側面に接するボディ領域 214 に反転層 IL (図 1 参照) が形成され、ドレイン電極 228 とソース電極 226 の間が導通する。一方、半導体装置 201 は、ドレイン電極 228 にソース電極 226 よりも高い電圧が印加され、かつ、ゲート電極 224 に閾値電圧以下の電圧が印加されると、反転層 IL が消失し、オフ状態となる。このように、半導体装置 201 は、ゲート電極 224 に印加する電圧に基づいてオンとオフが切り替えられるスイッチング素子として機能する。

#### 【0040】

##### (複数の特定領域 218 の効果)

負荷短絡によってドレイン電極 228 に高い電圧が印加されると、ドレイン電極 228 からソース電極 226 に大電流が流れる。具体的には、ドレイン電極 228、基板 210、ドリフト領域 212、ボディ領域 214 の反転層 IL、ソース領域 216、ソース電極 226 という順番で電流が流れる。このような状況において、図 11 に示す電流集中領域 240 に大電流が流れる。具体的には、電流集中領域 240 は、トレンチ 220T の下端よりも下方であり、かつ、半導体装置 201 を垂直上方から見たときに、トレンチ 220T よりも外側の領域である。電流集中領域 240 は、大電流が流れることによって、発熱する。上述のように、ドリフト領域 212 は SiC からなる。SiC の熱伝導率は、シリコン酸化膜、ポリシリコン等よりも小さい。このため、電流集中領域 240 の発熱による熱は、ドリフト領域 212 (SiC) 内を伝導する。電流集中領域 240 の上方には、熱伝導率が小さい材料が設けられていない。このため、半導体装置 201 を垂直上方から見たときに、トレンチ 220T の外側に拡散された熱は、半導体装置 201 の上方に放熱される。一方、トレンチ 220T には、熱伝導率が小さい材料からなるゲート電極 224 及びゲート絶縁膜 222 が形成されている。このため、半導体装置 201 を垂直上方から見たときに、トレンチ 220T の内側に拡散された熱は、半導体装置 201 の上方に放熱されない。このため、トレンチ 220T の下方が発熱し、発熱領域 242 となる。

#### 【0041】

本実施例の半導体装置 201 の効果について説明する前に、比較例の半導体装置について説明する。比較例の半導体装置は、ドリフト領域に複数の特定領域 218 が設けられていない点を除いて、本実施例の半導体装置 201 と同様の構造を有する。従って、比較例の半導体装置においても、負荷短絡が発生すると、電流集中領域 240 に大電流が流れ、その内側の発熱領域が発熱する。比較例の半導体装置は、複数の特定領域 218 を有さない。即ち、発熱領域全体が、SiC で構成されている。このため、発熱領域における線膨張係数は、複数の特定領域 218 が形成されている場合よりも大きい。このため、負荷短絡が発生すると、電流集中領域が発熱する。このため、ドリフト領域の一部が熱膨張し、その結果、比較例の半導体装置に大きな熱応力が作用する。この熱応力によって、ゲート絶縁膜等が変形する。ゲート絶縁膜が変形し、ゲート絶縁膜等に亀裂等が発生し得る。ゲート絶縁膜等に亀裂が発生すると、比較例の半導体装置に異常が発生する。

#### 【0042】

一方、図 11 に示すように、本実施例の半導体装置 201 では、発熱領域 242 に、複数の特定領域 218 が形成されている。上述のように、複数の特定領域 218 の線膨張係数は、SiC の線膨張係数よりも小さい。このため、電流集中領域 240 に大電流が流れ、発熱領域 242 が発熱しても、複数の特定領域 218 が熱膨張することを抑制することができる。複数の特定領域 218 の熱膨張が抑制されることによって、半導体装置 201 に作用する熱応力を低減することができる。即ち、比較例の半導体装置と比較して、負荷短絡時におけるゲート絶縁膜 222 等の変形量を低減することができる。この結果、半導体装置 201 に異常が発生することを抑制することができ、半導体装置 201 の信頼性を向上させることができる。

#### 【0043】

##### (半導体装置 201 の製造方法)

次に、図 12 ~ 図 17 を参照して、半導体装置 201 の製造方法を説明する。図 12 の

10

20

30

40

50

フローチャートのステップ S 2 1、S 2 2 は、それぞれ、第 1 実施例における図 2 のフローチャートのステップ S 1、S 2 と同様である。これにより、図 1 3 に示すように、ドリフト領域 2 1 2 に複数の特定領域 2 1 8 が形成される。

#### 【 0 0 4 4 】

ステップ S 2 3 は、ドリフト領域 2 1 2 上に p 型の半導体基板が貼り合わされる点を除いて、第 1 実施例における図 2 のフローチャートのステップ S 3 と同様である。これにより、化合物半導体 2 0 8 に、ボディ領域 2 1 4 が形成される（図 1 4 参照）。

#### 【 0 0 4 5 】

ステップ S 2 4 において、化合物半導体 2 0 8 に、ソース領域 2 1 6 を形成する（ソース領域形成工程）。具体的には、周知のフォトリソグラフィー技術及びドライエッチング加工を用いて、化合物半導体 2 0 8 上に、ソース領域 2 1 6 が開口しているマスクを加工する。次いで、マスクを介して n 型の不純物イオンを注入する。これにより、化合物半導体 2 0 8 に、ソース領域 2 1 6 が形成される（図 1 5 参照）。

10

#### 【 0 0 4 6 】

ステップ S 2 5 において、トレンチゲート 2 2 0 を形成する（トレンチゲート形成工程）。具体的には、フォトリソグラフィー技術を用いて、化合物半導体 2 0 8 上に、トレンチ領域が開口しているマスクを加工する。次いで、ドライエッチング加工を用いて、ソース領域 2 1 6 、及び、ボディ領域 2 1 4 を貫通してドリフト領域 2 1 2 の一部に到達するトレンチ 2 2 0 T を形成する。これにより、一対のボディ領域 2 1 4 a、2 1 4 b 、及び、一対のソース領域 2 1 6 a、2 1 6 b が形成される。次いで、化合物半導体 2 0 8 上に、ゲート絶縁膜 2 2 2 を成膜する。次いで、ゲート絶縁膜 2 2 2 上にポリシリコン層を堆積する。これにより、トレンチゲート 2 2 0 が完成する（図 1 6 参照）。

20

#### 【 0 0 4 7 】

ステップ S 2 6 において、化合物半導体 2 0 8 の上、及び、トレンチゲート 2 2 0 の上に、絶縁膜 2 2 5 を成膜する（絶縁膜成膜工程）（図 1 7 参照）。

#### 【 0 0 4 8 】

ステップ S 2 7 において、化合物半導体 8 の上面側にソース電極 2 2 6 を形成し、化合物半導体 8 の下面側にドレイン電極 2 2 8 を形成する（ソース電極、ドレイン電極形成工程）。これにより、図 1 1 に示す半導体装置 2 0 1 が完成する。

30

#### 【 0 0 4 9 】

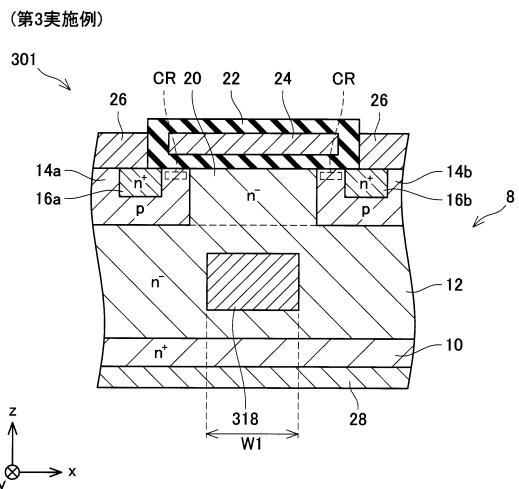

##### （第 3 実施例）

図 1 8 に、第 3 実施例の半導体装置 3 0 1 の要部断面図を示す。第 3 実施例の半導体装置 3 0 1 は、特定領域 3 1 8 の構造を除いて、第 1 実施例の半導体装置 1 と同様の構造を有する。以下では、実施例間で共通する構造については、同じ符号を付して、その説明を省略する。

#### 【 0 0 5 0 】

本実施例では、ドリフト領域 3 1 2 に、1 個の特定領域 3 1 8 が形成されている。なお、半導体装置 3 0 1 の製造方法において、図 2 のステップ S 3 と同様に、ドリフト領域 1 2 の上面に、n 型の SiC 基板を貼り合わせる工程が行われる。本実施例の特定領域 3 1 8 の幅 W 1 は、第 1 実施例の複数の特定領域 1 8 のうちの 1 個の特定領域 1 8 の幅よりも大きい。仮に、図 2 のステップ S 3 の代わりに、周知のエピタキシャル成長技術を用いて、ドリフト領域 1 2 上に、n 型の半導体領域を成長させる工程が行われると、結晶面に成長するため、特定領域 3 1 8 の上方を n 型の半導体領域で塞ぐことができない。即ち、特定領域 3 1 8 の上方に、n 型の半導体領域を形成させることができない。本実施例の場合、半導体装置 3 0 1 の製造方法において、ドリフト領域 1 2 の上面に、n 型の SiC 基板を貼り合わせるために、特定領域 3 1 8 上にも、n 型の半導体領域を形成することができる。また、1 個の特定領域 3 1 8 によっても、第 1 実施例と同様の効果を奏することができる。

40

#### 【 0 0 5 1 】

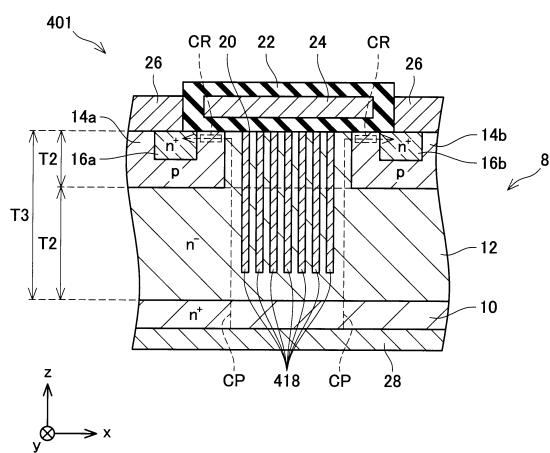

##### （第 4 実施例）

50

図19に、第4実施例の半導体装置401の要部断面図を示す。第4実施例の半導体装置401は、特定領域418の構造を除いて、第1実施例の半導体装置1と同様の構造を有する。

#### 【0052】

本実施例では、複数の特定領域418は、化合物半導体8の上面から、JFET領域20を貫通してドリフト領域12の一部に到達している。なお、複数の特定領域418は、半導体装置401がオン状態であるときに、ドレイン電極28からソース電極26に電流が流される電流経路CP上に設けられていない。従って、ドレイン電極28からソース電極26に流れる電流の経路は、複数の特定領域418によって阻害されない。

#### 【0053】

続いて、半導体装置401の製造方法について説明する。まず、図2のステップS1と同様に、SiCを材料とするn型の基板10の主面上に、周知のエピタキシャル成長技術を用いてn型の半導体領域を堆積させる。なお、本実施例においては、基板10上のn型の半導体領域の厚みが、ドリフト領域12の厚みT1及びJFET領域の厚みT2の合計の厚みT3となるように、n型の半導体領域の厚みを調整する。そして、図2のステップS2と同様に、化合物半導体8に、複数の特定領域418を形成する。その後、図2のステップS4～S7と同様の工程が行われることで、図19の半導体装置401が完成する。このように、半導体装置401の場合、図2のステップS3の工程を省略することができる。従って、半導体装置401を容易に製造することができる。また、複数の特定領域418によっても、第1実施例と同様の効果を奏すことができる。

10

#### 【0054】

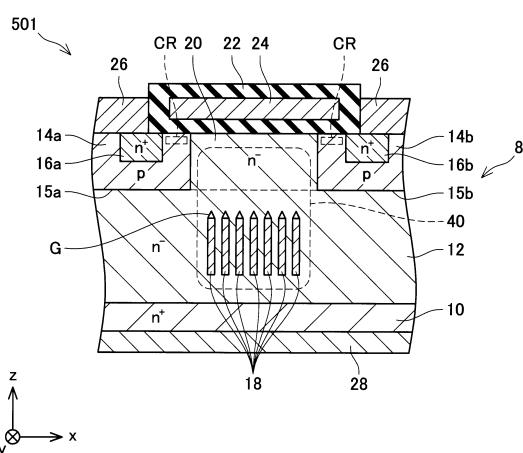

##### (第5実施例)

図20に、第5実施例の半導体装置501の要部断面図を示す。第5実施例の半導体装置501は、複数の特定領域18上にギャップGが形成されている点を除いて、第1実施例の半導体装置1と同様の構造を有する。なお、図20では、見易くするために、左端の特定領域18上のギャップにのみ符号が付されている。

20

#### 【0055】

本実施例の半導体装置501の製造方法は、第1実施例の半導体装置1の製造方法と異なる。具体的には、本実施例では、図2のフローチャートのステップS3において、周知のエピタキシャル成長技術を用いて、ドリフト領域12上に、n型の半導体領域を成長させる点が、第1の実施例の半導体装置1の製造方法と異なる。n型の半導体領域を成長させる工程において、複数の特定領域18は成長しないが、複数の特定領域18の間の間隔18bのSiCは成長する。n型の半導体領域を成長させる工程において、SiCは、上方方向だけではなく、左右方向(x軸方向)及び前後方向(y軸方向)にも広がりながら成長する。図4に示すように、複数の特定領域18の間の間隔18bは、比較的に小さい。このために、上方方向、左右方向、及び、前後方向に広がりながら成長するSiCが特定領域18の上方で結合する。これにより、複数の特定領域18上にギャップGが形成される。従って、複数の特定領域18の間の間隔18bが比較的に小さくすることで、エピタキシャル成長技術を用いて図20の半導体装置を製造することができる。

30

#### 【0056】

以上、本発明の具体例を詳細に説明したが、これらは例示に過ぎず、特許請求の範囲を限定するものではない。特許請求の範囲に記載の技術には、以上に例示した具体例を様々に変形、変更したものが含まれる。

40

#### 【0057】

(第1変形例)特定領域を構成する特定材料は、SiCに限定されない。特定材料は、導電性のCであってもよい。導電性のCとは、グラファイトである。グラファイトの線膨張係数は、 $4.2 \times 10^{-6} / K$ である。また、特定材料は、導電性を有する多結晶のSiCであってもよい。多結晶のSiCの線膨張係数は、 $4.2 \times 10^{-6} / K$ である。

#### 【0058】

また、特定材料は、絶縁体であるSiO<sub>2</sub>であってもよいし、空気(エアギャップ)で

50

あってもよい。SiO<sub>2</sub>又は空気を特定材料として利用することで、電界集中を緩和することができる。

【0059】

(第2変形例)半導体装置の基板は、GaNの単結晶基板であってもよい。なお、GaNの線膨張係数は、5.5×10<sup>-6</sup>/Kである。本変形例では、特定材料の線膨張係数は、5.5×10<sup>-6</sup>/Kよりも小さければよい。

【0060】

本明細書または図面に説明した技術要素は、単独あるいは各種の組合せによって技術的有用性を發揮するものであり、出願時請求項記載の組合せに限定されるものではない。また、本明細書または図面に例示した技術は複数目的を同時に達成し得るものであり、そのうちの一つの目的を達成すること自体で技術的有用性を持つものである。

10

【符号の説明】

【0061】

1：半導体装置、8：化合物半導体、10：基板、12：ドリフト領域、14：ボディ領域、15：下面、16：ソース領域、18：特定領域、18a：スリット、20：JFE T領域、20a：半導体領域、22：ゲート絶縁膜、24：ゲート電極、26：ソース電極、28：ドレイン電極、40：電流集中領域、112：ドリフト領域、140：電流集中領域、201：半導体装置、208：化合物半導体、210：基板、212：ドリフト領域、214：ボディ領域、216：ソース領域、218：特定領域、220：トレンチゲート、220T：トレンチ、222：ゲート絶縁膜、224：ゲート電極、225：絶縁膜、226：ソース電極、228：ドレイン電極、240：電流集中領域、242：発熱領域

20

30

40

50

【図面】

【図 1】

【図 2】

10

【図 3】

【図 4】

20

30

40

50

【図 5】

【図 6】

10

【図 7】

【図 8】

20

【図 9】

【図 10】

30

40

50

【図 1 1】

【図 1 2】

10

【図 1 3】

【図 1 4】

20

30

40

50

【図 15】

【図 16】

10

【図 17】

【図 18】

20

30

40

50

【図 19】

(第4実施例)

【図 20】

(第5実施例)

10

20

30

40

50

---

フロントページの続き

(51)国際特許分類

F I

H 0 1 L      2 9 / 7 8      6 5 8 K

愛知県長久手市横道 4 1 番地の 1 株式会社豊田中央研究所内

(72)発明者 渡辺 行彦

愛知県長久手市横道 4 1 番地の 1 株式会社豊田中央研究所内

(72)発明者 片岡 恵太

愛知県長久手市横道 4 1 番地の 1 株式会社豊田中央研究所内

(72)発明者 斎藤 順

愛知県豊田市トヨタ町 1 番地 トヨタ自動車株式会社内

(72)発明者 浦上 泰

愛知県刈谷市昭和町 1 丁目 1 番地 株式会社デンソー内

審査官 石塚 健太郎

(56)参考文献 特開 2 0 0 7 - 2 8 8 1 7 2 ( J P , A )

特開 2 0 0 9 - 1 6 4 5 5 8 ( J P , A )

特開 2 0 1 7 - 0 4 1 6 1 3 ( J P , A )

特開 2 0 1 2 - 1 9 0 9 8 2 ( J P , A )

(58)調査した分野 (Int.Cl., DB名)

H 0 1 L      2 9 / 7 8

H 0 1 L      2 9 / 1 2

H 0 1 L      2 1 / 3 3 6