(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4731816号

(P4731816)

(45) 発行日 平成23年7月27日(2011.7.27)

(24) 登録日 平成23年4月28日(2011.4.28)

|               |                             |

|---------------|-----------------------------|

| (51) Int.Cl.  | F 1                         |

| HO 1 L 29/78  | (2006.01) HO 1 L 29/78 301W |

| HO 1 L 29/06  | (2006.01) HO 1 L 29/78 652P |

| HO 1 L 29/739 | (2006.01) HO 1 L 29/78 655F |

| HO 1 L 29/861 | (2006.01) HO 1 L 29/06 301F |

|               | HO 1 L 29/91 D              |

請求項の数 9 (全 34 頁)

(21) 出願番号 特願2004-16663 (P2004-16663)

(22) 出願日 平成16年1月26日 (2004.1.26)

(65) 公開番号 特開2005-209983 (P2005-209983A)

(43) 公開日 平成17年8月4日 (2005.8.4)

審査請求日 平成18年5月26日 (2006.5.26)

(73) 特許権者 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目7番3号

(74) 代理人 100088672

弁理士 吉竹 英俊

(74) 代理人 100088845

弁理士 有田 貴弘

(72) 発明者 帰手 一成

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

審査官 川村 裕二

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1導電型の第1半導体領域と、

前記第1半導体領域を挟むように形成された第2導電型の第2半導体領域および前記第1半導体領域よりも不純物濃度が高い第1導電型の第3半導体領域と、

前記第1半導体領域上に形成された第1絶縁膜と、

前記第1絶縁膜上に形成され、前記第1半導体領域上方に、前記第3半導体領域から前記第2半導体領域へ向かう第1方向に並べて配設された複数個の第1フローティングフィールドプレートと、

前記第1フローティングフィールドプレート上に形成された第2絶縁膜と、

前記第2絶縁膜上に形成され、前記第1半導体領域上方に、前記第1方向に並べて配設された複数個の第2フローティングフィールドプレートと、

前記第2フローティングフィールドプレート上に形成された第3絶縁膜と、

前記第3絶縁膜上に形成され、前記第1半導体領域上方に、前記第1方向に並べて配設された複数個の第3フローティングフィールドプレートとを備え、

前記第1絶縁膜の厚さをaとし、前記第1フローティングフィールドプレートと前記第2フローティングフィールドプレートとの間の前記厚さの方向である第2方向の距離をbとし、前記第2フローティングフィールドプレートと前記第3フローティングフィールドプレートとの間の前記第2方向の距離をcとしたとき、

a > b 且つ a > c である

10

20

ことを特徴とする半導体装置。

【請求項 2】

請求項 1 に記載の半導体装置であって、

前記第 3 半導体領域上に形成された電極をさらに有し、

前記電極は、前記第 1 絶縁膜上に延びる第 1 電極部および前記第 2 絶縁膜上に延びる第 2 電極部を有し、

前記第 2 電極部における前記第 1 絶縁膜上方を前記第 1 方向に延びた部分の長さは、前記第 1 電極部における前記第 1 絶縁膜上を前記第 1 方向に延びた部分の長さよりも長いことを特徴とする半導体装置。

【請求項 3】

10

請求項 2 記載の半導体装置であって、

前記第 1 電極部における前記第 1 絶縁膜上を前記第 1 方向に延びた部分の長さを d とし、前記第 2 電極部における前記第 1 絶縁膜上方を前記第 1 方向に延びた部分の長さが、前記長さ d よりもさらに長さ e だけ長いとしたとき、

$d > e$  である

ことを特徴とする半導体装置。

【請求項 4】

20

第 1 導電型の第 1 半導体領域と、

前記第 1 半導体領域を挟むように形成された第 2 導電型の第 2 半導体領域および前記第 1 半導体領域よりも不純物濃度が高い第 1 導電型の第 3 半導体領域と、

前記第 1 半導体領域上に形成された第 1 絶縁膜と、

前記第 1 絶縁膜上に形成され、前記第 1 半導体領域上方に、前記第 3 半導体領域から前記第 2 半導体領域へ向かう第 1 方向に並べて配設された複数個の第 1 フローティングフィールドプレートと、

前記第 1 フローティングフィールドプレート上に形成された第 2 絶縁膜と、

前記第 2 絶縁膜上に形成され、前記第 1 半導体領域上方に、前記第 1 方向に並べて配設された複数個の第 2 フローティングフィールドプレートと、

前記第 2 フローティングフィールドプレート上に形成された第 3 絶縁膜と、

前記第 3 絶縁膜上に形成され、前記第 1 半導体領域上方に、前記第 1 方向に並べて配設された複数個の第 3 フローティングフィールドプレートとを備える半導体装置であって、

前記第 1 絶縁膜の厚さを a とし、前記第 1 フローティングフィールドプレートと前記第 2 フローティングフィールドプレートとの間の前記厚さの方向である第 2 方向の距離を b とし、前記第 2 フローティングフィールドプレートと前記第 3 フローティングフィールドプレートとの間の前記第 2 方向の距離を c としたとき、

$c < a$ 、且つ、 $c < b$  である

ことを特徴とする半導体装置。

30

【請求項 5】

請求項 1 から請求項 4 のいずれかに記載の半導体装置であって、

前記第 2 半導体領域は、トランジスタのチャネル領域として機能し、

前記第 3 半導体領域は、前記トランジスタのドレインとして機能する

ことを特徴とする半導体装置。

40

【請求項 6】

請求項 1 から請求項 4 のいずれかに記載の半導体装置であって、

前記第 2 半導体領域は、ダイオードのアノードとして機能し、

前記第 3 半導体領域は、前記ダイオードのカソードとして機能する

ことを特徴とする半導体装置。

【請求項 7】

請求項 1 から請求項 4 のいずれかに記載の半導体装置であって、

前記第 3 半導体領域は、チップの外周部のチャネルストップとして機能する

ことを特徴とする半導体装置。

50

**【請求項 8】**

請求項 1 から請求項 7 のいずれかに記載の半導体装置であって、

前記第1半導体領域の下側に接する第2導電型の第4半導体領域をさらに有する

ことを特徴とする半導体装置。

**【請求項 9】**

請求項 8 に記載の半導体装置であって、

前記第1半導体領域と前記第4半導体領域との間の第1p n接合に、前記第1半導体領域と前記第2半導体領域との間の第2p n接合の降伏電圧よりも低い逆方向電圧が印加されることによって、前記第2半導体領域と前記第3半導体領域との間で、空乏層が、前記第1p n接合から前記第1半導体領域の上面にまで拡がるように、前記第1半導体領域の不純物濃度が低く且つ厚さが薄い

ことを特徴とする半導体装置。

10

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は半導体装置に関し、特に、高耐圧半導体装置における耐電圧（以下「耐圧」）の安定性向上および高耐電圧化を図るための技術に関する。

**【背景技術】****【0002】**

例えば、ハーフブリッジ型のインバータのように、高圧側および低圧側の2つのパワースイッチングデバイス（MOSFETやIGBT等）を駆動する場合には、高圧側のパワースイッチングデバイスを駆動するハイサイド（高電位島）の駆動回路と、低圧側のパワースイッチングデバイスを駆動するローサイドの駆動回路とを有するパワーデバイス駆動装置が使用される。ハイサイドの回路は、接地電位に対して電位的に浮いた状態で動作するので、そのようなパワーデバイス駆動装置には、駆動信号をハイサイドの駆動回路に伝達するための、いわゆるレベルシフト回路が備えられている。一般的なレベルシフト回路は、駆動信号により駆動されるMOSFETなどの高耐圧スイッチング素子と、それに直列に接続したレベルシフト抵抗とにより構成される（後述の図2参照）。そして、該レベルシフト抵抗に生じる電圧降下が、ハイサイドの駆動信号として駆動回路へと伝達される。パワーデバイス駆動装置の破損やレベルシフト回路での誤信号の発生を防止するために、当該高耐圧スイッチング素子には安定した高耐圧性が望まれる。

20

**【0003】**

ダイオードなどの高耐圧スイッチング素子の耐電圧の安定性向上および高耐圧化のための技術としては、例えば、半導体基板上に絶縁膜を介して複数のフローティング状態のフィールドプレート（以下、単に「フローティングフィールドプレート」と称する）を形成して基板表面における電界分布を均一にしたり（例えば特許文献1）、半導体素子構造としてRESURF構造（例えば特許文献2）を用いることによって基板中の空乏化を促進させる手法が知られている。

30

**【0004】**

【特許文献1】特開平10-341018号公報

40

【特許文献2】米国特許4292642号公報

**【発明の開示】****【発明が解決しようとする課題】****【0005】**

遮断状態（OFF状態）の高耐圧半導体装置に高電圧が印加されると、当該高耐圧半導体装置はその電圧を保持する。このとき当該装置が形成された半導体基板内に局部的な電界集中（電界のピーク）が生じていると、その部分におけるp/n接合部の降伏現象や絶縁膜の破壊が発生しやすくなり、耐圧特性の劣化を招く。例えば、高耐圧半導体装置がRESURF構造を有するnチャネル型MOSFETの場合、半導体基板上部に形成されるn<sup>-</sup>層とその下のp<sup>-</sup>基板との接合深さにおけるドレイン側n層の近傍や、電極およびフィ

50

ールドプレートの端部の下方における半導体基板表面などには、電界のピークが生じやすい（詳細は後述する）。

#### 【0006】

また、高耐圧半導体装置の実使用時には、その上面は、オーバーコート絶縁膜や組立て用のエポキシ樹脂により覆われる。例えば遮断状態のMOSFETのドレイン-ソース間に高電圧が印加され、そのとき内部に電界のピークが発生すると、その影響によりオーバーコート絶縁膜や組立て用エポキシ樹脂が分極してしまう。その分極により生じた電荷は、高電圧の印加が終わった後も、ある時間保持される。そして次にドレイン-ソース間に高電圧が印加されたときに、その電荷の影響により、局所的に（特にシリコン基板表面近傍）空乏層の拡がりが抑制されてしまう。空乏層の拡がりが抑制された箇所では、電界のピークはより高くなる。そのピークがシリコン表面で降伏臨界電界に到達してしまうと、耐圧低下や耐圧変動、場合によっては半導体装置の破壊を引き起こしてしまう。

#### 【0007】

本発明は以上のような問題を解決するためになされたものであり、半導体装置が形成される基板内の電界集中を緩和することによって、耐電圧の安定性向上および高耐圧化を図ることを目的とする。

#### 【課題を解決するための手段】

#### 【0008】

本発明の第1の局面としての半導体装置は、第1導電型の第1半導体領域と、前記第1半導体領域を挟むように形成された第2導電型の第2半導体領域および前記第1半導体領域よりも不純物濃度が高い第1導電型の第3半導体領域と、前記第1半導体領域上に形成された第1絶縁膜と、前記第1絶縁膜上に形成され、前記第1半導体領域上方に、前記第3半導体領域から前記第2半導体領域へ向かう第1方向に並べて配設された複数個の第1フローティングフィールドプレートと、前記第1フローティングフィールドプレート上に形成された第2絶縁膜と、前記第2絶縁膜上に形成され、前記第1半導体領域上方に、前記第1方向に並べて配設された複数個の第2フローティングフィールドプレート、前記第2フローティングフィールドプレート上に形成された第3絶縁膜と、前記第3絶縁膜上に形成され、前記第1半導体領域上方に、前記第1方向に並べて配設された複数個の第3フローティングフィールドプレートとを備え、前記第1絶縁膜の厚さをaとし、前記第1フローティングフィールドプレートと前記第2フローティングフィールドプレートとの間の前記厚さの方向である第2方向の距離をbとし、前記第2フローティングフィールドプレートと前記第3フローティングフィールドプレートとの間の前記第2方向の距離をcとしたとき、a > b且つa > cであるものである。

#### 【0009】

本発明の第2の局面としての半導体装置は、第1導電型の第1半導体領域と、前記第1半導体領域を挟むように形成された第2導電型の第2半導体領域および前記第1半導体領域よりも不純物濃度が高い第1導電型の第3半導体領域と、前記第1半導体領域上に形成された第1絶縁膜と、前記第1絶縁膜上に形成され、前記第1半導体領域上方に、前記第3半導体領域から前記第2半導体領域へ向かう第1方向に並べて配設された複数個の第1フローティングフィールドプレートと、前記第1フローティングフィールドプレート上に形成された第2絶縁膜と、前記第2絶縁膜上に形成され、前記第1半導体領域上方に、前記第1方向に並べて配設された複数個の第2フローティングフィールドプレートとを備える半導体装置であって、個々の前記第1フローティングフィールドプレートの前記第1方向の幅をiとし、個々の前記第1フローティングフィールドプレート間の前記第1方向の距離をjとしたとき、i = jであるものである。

#### 【0010】

本発明の第3の局面としての半導体装置は、第1導電型の第1半導体領域と、前記第1半導体領域を挟むように形成された第2導電型の第2半導体領域および前記第1半導体領域よりも不純物濃度が高い第1導電型の第3半導体領域と、前記第1半導体領域上に形成された第1絶縁膜と、前記第1絶縁膜上に形成され、前記第1半導体領域上方に、前記第

10

20

30

40

50

3 半導体領域から前記第2半導体領域へ向かう第1方向に並べて配設された複数個の第1フローティングフィールドプレートと、前記第1フローティングフィールドプレート上に形成された第2絶縁膜と、前記第2絶縁膜上に形成され、前記第1半導体領域上方に、前記第1方向に並べて配設された複数個の第2フローティングフィールドプレートと、前記第2フローティングフィールドプレート上に形成された第3絶縁膜と、前記第3絶縁膜上に形成され、前記第1半導体領域上方に、前記第1方向に並べて配設された複数個の第3フローティングフィールドプレートとを備える半導体装置であって、前記第1絶縁膜の厚さをaとし、前記第1フローティングフィールドプレートと前記第2フローティングフィールドプレートとの間の前記厚さの方向である第2方向の距離をbとし、前記第2フローティングフィールドプレートと前記第3フローティングフィールドプレートとの間の前記第2方向の距離をcとしたとき、 $c < a$ 、且つ、 $c < b$ であるものである。 10

【0011】

本発明の第4の局面としての半導体装置は、第1導電型の第1半導体領域と、前記第1半導体領域を挟むように形成された第2導電型の第2半導体領域および前記第1半導体領域よりも不純物濃度が高い第1導電型の第3半導体領域と、前記第1半導体領域上に形成された第1絶縁膜と、前記第1絶縁膜上に形成され、前記第1半導体領域上方に、前記第3半導体領域から前記第2半導体領域へ向かう第1方向に並べて配設された複数個の第1フローティングフィールドプレートと、前記第1フローティングフィールドプレート上に形成された第2絶縁膜と、前記第2絶縁膜上に形成され、前記第1半導体領域上方に、前記第1方向に並べて配設された複数個の第2フローティングフィールドプレートとを備える半導体装置であって、個々の前記第1フローティングフィールドプレートにおいて前記第2絶縁膜を介して1つの前記第2フローティングフィールドプレートと重なる部分の前記第1方向の幅をgとし、個々の前記第2フローティングフィールドプレート間の前記第1方向の距離をhとしたとき、 $g > h$ であるものである。 20

【0012】

本発明の第5の局面としての半導体装置は、第1導電型の第1半導体領域と、前記第1半導体領域を挟むように形成された第2導電型の第2半導体領域および前記第1半導体領域よりも不純物濃度が高い第1導電型の第3半導体領域と、前記第3半導体領域上に形成された電極と、前記第1半導体領域上に形成された第1絶縁膜と、前記第1絶縁膜上に形成された第2絶縁膜と、前記第2絶縁膜上に形成され、前記第1半導体領域上方に、前記第3半導体領域から前記第2半導体領域へ向かう第1方向に並べて配設された複数個の第2フローティングフィールドプレートと、前記第2フローティングフィールドプレート上に形成された第3絶縁膜と、前記第3絶縁膜上に形成され、前記第1半導体領域上方に、前記第1方向に並べて配設された複数個の第3フローティングフィールドプレートとを備える半導体装置であって、前記電極は、前記第1絶縁膜上に前記第1方向に延びる第1電極部を有するものである。 30

【0013】

本発明の第6の局面としての半導体装置は、第1導電型の第1半導体領域と、前記第1半導体領域を挟むように形成された第2導電型の第2半導体領域および前記第1半導体領域よりも不純物濃度が高い第1導電型の第3半導体領域と、前記第3半導体領域上に形成された電極と、前記第1半導体領域上に形成された第1絶縁膜と、前記第1絶縁膜上に形成された第2絶縁膜と、前記第2絶縁膜上に形成され、前記第1半導体領域上方に、前記第3半導体領域から前記第2半導体領域へ向かう第1方向に並べて配設された複数個の第2フローティングフィールドプレートと、前記第2フローティングフィールドプレート上に形成された第3絶縁膜と、前記第3絶縁膜上に形成され、前記第1半導体領域上方に、前記第1方向に並べて配設された複数個の第3フローティングフィールドプレートとを備える半導体装置であって、前記電極は、前記第1絶縁膜上に延びる第1電極部および前記第2絶縁膜上に延びる第2電極部を有し、前記第2電極部における前記第1絶縁膜上方を前記第1方向に延びた部分の長さは、前記第1電極部における前記第1絶縁膜上を前記第1方向に延びた部分の長さよりも長いものである。 40 50

## 【0014】

本発明の第7の局面としての半導体装置は、第1導電型の第1半導体領域と、前記第1半導体領域を挟むように形成された第2導電型の第2半導体領域および前記第1半導体領域よりも不純物濃度が高い第1導電型の第3半導体領域と、前記第3半導体領域上に形成された電極と、前記第1半導体領域上に形成された第1絶縁膜と、前記第1絶縁膜上に形成され、前記第1半導体領域上方に、前記第3半導体領域から前記第2半導体領域へ向かう第1方向に並べて配設された複数個の第1フローティングフィールドプレートと、前記第1フローティングフィールドプレート上に形成された第2絶縁膜と、前記第2絶縁膜上に形成され、前記第1半導体領域上方に、前記第1方向に並べて配設された複数個の第2フローティングフィールドプレートとを備える半導体装置であって、前記電極は、前記第1絶縁膜上に延びる第1電極部および前記第2絶縁膜上に延びる第2電極部を有し、前記第1電極部における前記第1絶縁膜上を前記第1方向に延びた部分の長さをdとしたとき、前記第2電極部における前記第1絶縁膜上方を前記第1方向に延びた部分の長さは、前記長さdよりもさらに長さeだけ長く、 $d > e$ であるものである。10

## 【発明の効果】

## 【0015】

第1の局面の半導体装置によれば、第1半導体領域上面における電界集中が緩和される。従って、降伏臨界電界点の電界強度に対するマージンが大きくなり、デバイスの耐圧低下や耐圧特性の不安定の問題は抑えられる。その結果、当該デバイスは、安定して高耐圧を維持することができる。20

## 【0016】

第2の局面の半導体装置によれば、個々の第1フローティングフィールドプレートの幅iと、個々の第1フローティングフィールドプレート間の距離jとが等しいので、第1半導体領域上面における電位分布が均一になり、第1半導体領域上面における電界集中が緩和される。従って、降伏臨界電界点の電界強度に対するマージンが大きくなり、当該装置の耐圧低下や耐圧特性の不安定の問題は抑えられる。その結果、当該装置は、安定して高耐圧を維持することができる。

## 【0017】

第3の局面の半導体装置によれば、第2フローティングフィールドプレートと第3フローティングフィールドプレートとの間の距離cが小さいので、第2フローティングフィールドプレートと第3フローティングフィールドプレートとで形成されるコンデンサにおいて高い容量結合効果が得られ、第3絶縁膜の分極化が促進される。それによって、従来空乏相が拡がり難かった各第1フローティングフィールドプレート間の下方の第1半導体領域上部における空乏層が拡がりやすくなり、その部分での電界集中が緩和される。従って、降伏臨界電界点の電界強度に対するマージンが大きくなり、当該装置の耐圧低下や耐圧特性の不安定の問題は抑えられる。その結果、当該装置は、安定して高耐圧を維持することができる。30

## 【0018】

第4の局面の半導体装置によれば、個々の第1フローティングフィールドプレートにおいて1つの第2フローティングフィールドプレートと重なる部分の幅gが大きいので、第1フローティングフィールドプレートと第2フローティングフィールドプレートとで形成されるコンデンサにおいて高い容量結合効果が得られ、第2絶縁膜の分極化が促進される。それによって、従来空乏相が拡がり難かった各第1フローティングフィールドプレート間の下方の第1半導体領域上部における空乏層が拡がりやすくなり、その部分での電界集中が緩和される。従って、降伏臨界電界点の電界強度に対するマージンが大きくなり、当該装置の耐圧低下や耐圧特性の不安定の問題は抑えられる。その結果、当該装置は、安定して高耐圧を維持することができる。40

## 【0019】

第5の局面の半導体装置によれば、第3半導体領域上に形成された電極が、第1絶縁膜上に第1方向に延びる第1電極部を有しているので、第1半導体領域上面における第3半50

導体領域付近の電界集中が緩和される。装置の降伏臨界電界点は、第3半導体領域付近にあることが多く、その近傍の電界集中が緩和されるので、当該装置の耐圧低下や耐圧特性の不安定の問題は抑えられる。その結果、当該装置は、安定して高耐圧を維持することができる。

【0020】

第6の局面の半導体装置によれば、第2電極部における第1絶縁膜上方を第1方向に延びた部分の長さは、第1電極部における第1絶縁膜上を第1方向に延びた部分の長さよりも長いので、第1半導体領域上面における第3半導体領域付近の電界集中が緩和される。装置の降伏臨界電界点は、第3半導体領域付近にあることが多く、その近傍の電界集中が緩和されるので、当該装置の耐圧低下や耐圧特性の不安定の問題は抑えられる。その結果 10、当該装置は、安定して高耐圧を維持することができる。

【0021】

第7の局面の半導体装置によれば、第1電極部における第1絶縁膜上を第1方向に延びた部分の長さをdとしたとき、第2電極部における第1絶縁膜上方を第1方向に延びた部分の長さは、長さdよりもさらに長さeだけ長く、この長さdと長さeとの関係はd>eであるので、第1半導体領域上面における最も第3半導体領域側の電界ピークは、従来構造のものよりも当該第3半導体領域から遠くになる。その結果、第1半導体領域上面における第3半導体領域付近の電界集中が緩和される。装置の降伏臨界電界点は、第3半導体領域付近にあることが多く、その近傍の電界集中が緩和されるので、当該装置の耐圧低下や耐圧特性の不安定の問題は抑えられる。その結果、当該装置は、安定して高耐圧を維持することができる。 20

【発明を実施するための最良の形態】

【0022】

<実施の形態1>

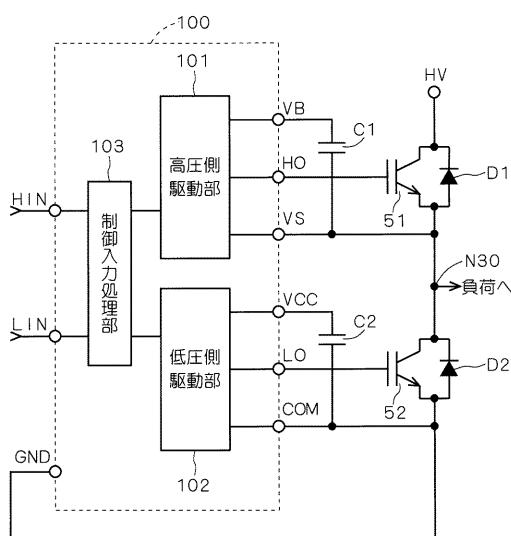

図1は、本発明が適用可能な半導体装置の一例を説明するための図であり、一般的なパワーデバイスおよびパワーデバイス駆動装置を示す図である。パワースイッチングデバイスであるnチャネル型IGBT（絶縁ゲート型バイポーラトランジスタ）51, 52は、主電源である高電圧HVをスイッチングする。ノードN30には負荷が接続されており、IGBT51, 52のそれぞれには、該負荷による逆起電圧から保護するためのフリーホイールダイオードD1, D2が接続されている。 30

【0023】

IGBT51, 52を駆動するパワーデバイス駆動装置100は、高圧側IGBT51を制御する高圧側制御入力HINおよび低圧側IGBT52を制御する低圧側制御入力LINに従い動作する。パワーデバイス駆動装置100はさらに、高圧側IGBT51を駆動する高圧側駆動部101、低圧側IGBT52を駆動する低圧側駆動部102、制御入力処理部103を有している。

【0024】

制御入力処理部103は、例えばIGBT51, 52が同時にオン状態になりIGBT51, 52に貫通電流が流れ、負荷に電流が流れないというような、好ましくない状態を回避するための信号処理等を行う。高圧側駆動部101の高圧側駆動信号出力HOは、IGBT51の制御端子に接続される。低圧側駆動部102の低圧側駆動信号出力LOは、IGBT52の制御端子に接続される。 40

【0025】

低圧側駆動部102の電源となる低圧側固定供給電圧VCCは、低圧側固定供給電源（図示せず）より供給される。高圧側浮遊オフセット電圧VSは、高圧側駆動部101の基準電位となる。また、高圧側駆動部101に電源となる高圧側浮遊供給絶対電圧VBは、高圧側浮遊電源（図示せず）により供給される。共通接地COM、高圧側浮遊オフセット電圧VSはそれぞれIGBT51, 52のエミッタ端子に接続される。

【0026】

また、高圧側浮遊供給絶対電圧VB - 高圧側浮遊オフセット電圧VS間および、共通接 50

地 C O M - 低圧側固定供給電圧 V C C 間には、高圧側駆動部 1 0 1 および低圧側駆動部 1 0 2 に供給される電源電圧を、I G B T 5 1 , 5 2 の動作に伴う電位変動に追随させるために、コンデンサ C 1 、C 2 が接続されている。

【 0 0 2 7 】

以上のような構成により、制御入力 H I N 、L I N に基づく I G B T 5 1 , 5 2 の主電源 H V のスイッチングを行うパワーデバイスが構成される。

【 0 0 2 8 】

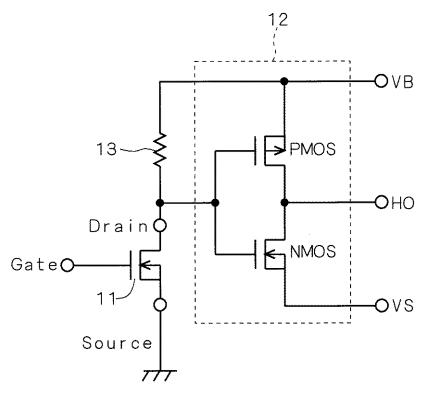

高圧側駆動部 1 0 1 は、回路の接地電位に対して電位的に浮いた状態で動作するので、高圧側回路へ駆動信号を伝達するための、いわゆるレベルシフト回路を有する構成となっている。図 2 は、高耐圧駆動部 1 0 1 の主要部の回路図である。この図において、図 1 に示したものと同様の要素には、同一符号を付してある。高耐圧 M O S F E T ( 以下、「 H V - M O S 」 ) 1 1 は、高耐圧スイッチング素子である。高圧側駆動信号出力用 C M O S 1 2 は、p M O S トランジスタと n M O S トランジスタとからなり、高圧側駆動信号を出力する。レベルシフト抵抗 1 3 は、高圧側駆動信号出力用 C M O S 1 2 のゲート電位を設定するためのプルアップ抵抗に相当する役割を果たしている。

【 0 0 2 9 】

H V - M O S 1 1 は、高圧側制御入力 H I N に従ってスイッチングし、高圧側駆動信号出力用 C M O S 1 2 のゲート電位を変化させる。それによって高圧側駆動信号出力用 C M O S 1 2 は、高圧側浮遊供給絶対電圧 V B - 高圧側浮遊オフセット電圧 V S 間の電圧をスイッチングして、高圧側駆動信号出力 H O に駆動信号を出力し、I G B T 5 1 を駆動させる。

【 0 0 3 0 】

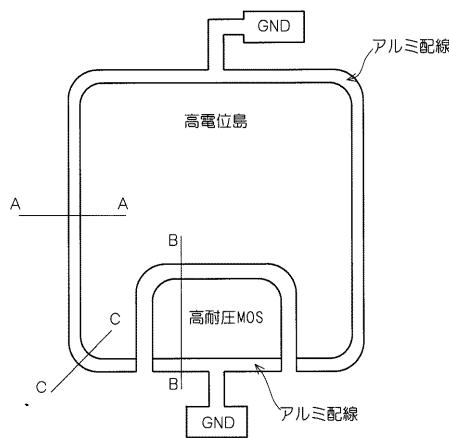

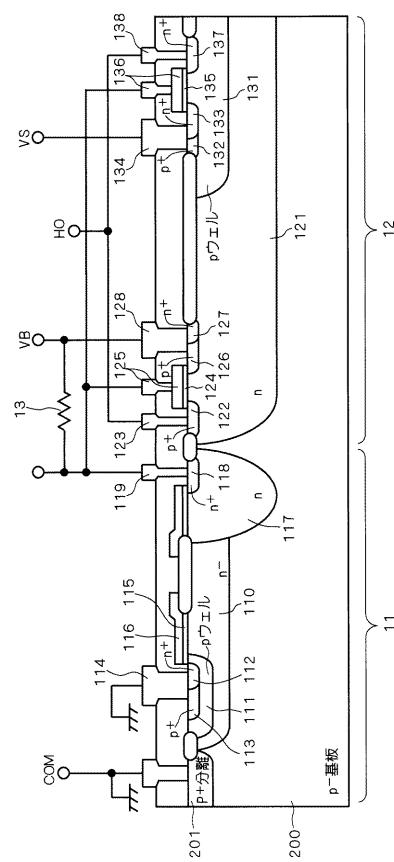

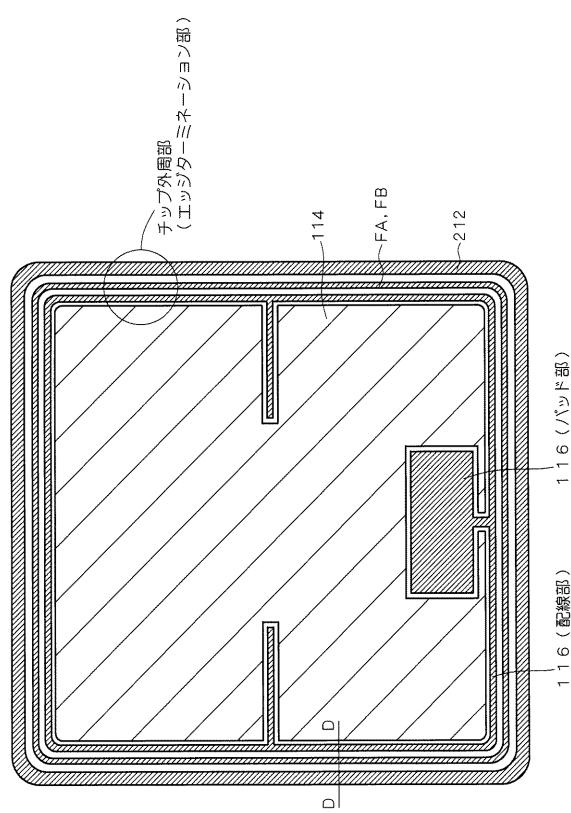

図 3 は、パワーデバイス駆動装置 1 0 0 における高電位島に設けられるレイアウトを示す概略平面図である。高圧側駆動信号出力用 C M O S 1 2 およびレベルシフト抵抗 1 3 から成る高圧側駆動回路は高電位島と称される領域内に形成されている。高圧側駆動部 1 0 1 のレイアウトを示す概略平面図である。同図のアルミ配線は接地電位 G N D にコンタクトされている。図 4 は、図 2 に示した高耐圧駆動部 1 0 1 の主要部の概略断面図であり、図 3 の B - B 断面に対応している。図 4 において、図 1 および図 2 に示したものと同様の要素には同符号を付してある。

【 0 0 3 1 】

p + 分離 2 0 1 の底部はシリコン基板 ( p - 基板 ) の p - 領域 2 0 0 に達しており、当該 p + 分離 2 0 1 および p - 領域 2 0 0 の電位は回路上最も低い電位 ( 接地電位 G N D または共通接地 C O M 電位 ) となっている。H V - M O S 1 1 が形成される領域には、それぞれ基板の上面に達するように、第 1 半導体領域としての n - 層 1 1 0 、第 2 半導体領域としての p ウェル 1 1 1 、n - 層 1 1 0 よりも不純物濃度が高い第 3 半導体領域としての n 領域 1 1 7 および n + ドレイン領域 1 1 8 が形成される。p ウェル 1 1 1 は、n - 層 1 1 0 の内部に該 n - 層 1 1 0 に接するように形成されている。n 領域 1 1 7 は、p ウェル 1 1 1 に対し n - 層 1 1 0 を挟んだ位置に形成されている。即ち、n - 層 1 1 0 を挟むように、その一側に p ウェル 1 1 1 が、他側に n 領域 1 1 7 がそれぞれ配設される。

【 0 0 3 2 】

p ウェル 1 1 1 の内部には、さらに n + ソース領域 1 1 2 および p + 領域 1 1 3 が形成され、その上に接続するように H V - M O S 1 1 のソース電極 1 1 4 が形成される。n + ソース領域 1 1 2 と n - 層 1 1 0 との間の p ウェル 1 1 1 上には、ゲート絶縁膜 1 1 5 を介してゲート電極 1 1 6 が形成される。即ち、p ウェル 1 1 1 は H V - M O S 1 1 のチャネル領域として機能する。H V - M O S 1 1 のドレイン電極 1 1 9 は、n + ドレイン領域 1 1 8 の上に接続するように形成される。

【 0 0 3 3 】

高圧側駆動信号出力用 C M O S 1 2 の p M O S トランジスタが形成される n 層 1 2 1 内には、p + ドレイン領域 1 2 2 、n + 領域 1 2 7 および p + ソース領域 1 2 6 が形成される。p + ドレイン領域 1 2 2 の上にはドレイン電極 1 2 3 が形成され、p + ソース領域 1 2 6

10

20

30

40

50

および $n^+$ 領域127の上にはソース電極128が形成され、 $p^+$ ドレイン領域122と $p^+$ ソース領域126の間の $n$ 層121上には、ゲート絶縁膜124を介してゲート電極125が形成される。一方、高圧側駆動信号出力用CMOS12のnMOSトランジスタが形成される $p$ ウェル131内には、 $p^+$ 領域132、 $n^+$ ソース領域133および $n^+$ ドレイン領域137が形成される。 $p^+$ 領域132および $n^+$ ソース領域133の上にはソース電極134が形成され、 $n^+$ ドレイン領域137の上にはドレイン電極138が形成され、 $n^+$ ソース領域133と $n^+$ ドレイン領域137の間の $p$ ウェル131上には、ゲート絶縁膜135を介してゲート電極136が形成される。

【0034】

そして、HV-MOS11のドレイン電極119は、高圧側駆動信号出力用CMOS12のpMOSトランジスタおよびnMOSトランジスタのゲート電極125、136に接続し、またレベルシフト抵抗13を介してpMOSトランジスタのソース電極128および高圧側浮遊供給絶対電圧VBに接続する。

【0035】

図5は、パワーデバイス駆動装置100における高圧側駆動部101の他の（図4とは別の）概略断面図であり、図3のA-AあるいはC-C断面に対応している。同図において、図4に示したものと同様の要素には同符号を付してある。図5に示す領域14は、高圧側駆動部101に接続される高耐圧ダイオード（図1、図2では不図示）を示している。

【0036】

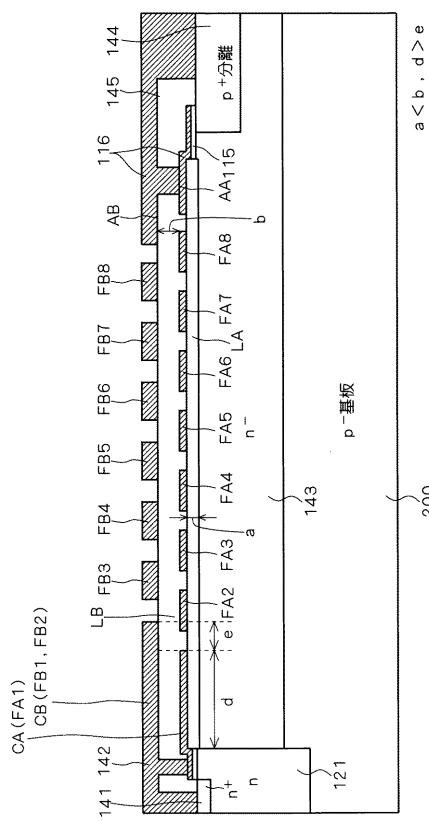

高耐圧ダイオード（以下「HV-ダイオード」）14は、上記のHV-MOS11に類似した構造を有しており、それぞれ基板の上面に達するように、第1半導体領域としての $n^-$ 層143、第2半導体領域としての $p^+$ 分離144、 $n^-$ 層143よりも不純物濃度が高い第3半導体領域としての $n$ 層121および $n^+$ カソード領域141から構成される。 $p^+$ 分離144は $n^-$ 層143の一側に接しており、 $n$ 層121は $n^-$ 層143の他側に接している。即ち、 $p^+$ 分離144と $n$ 層121とは、 $n^-$ 層143を挟むように形成されている。 $p^+$ 分離144は、HV-ダイオード14のアノードとして機能するので、以下、「 $p^+$ アノード領域144」と称する。HV-ダイオード14のカソード電極142は $n^+$ カソード領域141の上に接続するように形成され、アノード電極145は、 $p^+$ アノード領域144の上に接続するように形成される。 $p^+$ アノード領域144は $p^-$ 領域200に達している。 $p^+$ アノード領域144上にはアノード電極145が形成されており、 $p^-$ 領域200の電位は回路上最も低い電位（GND又はCOM電位）となっている。HV-ダイオード14は、高圧側浮遊供給絶対電圧VBとGND又はCOMとの間の電圧を保持している。

【0037】

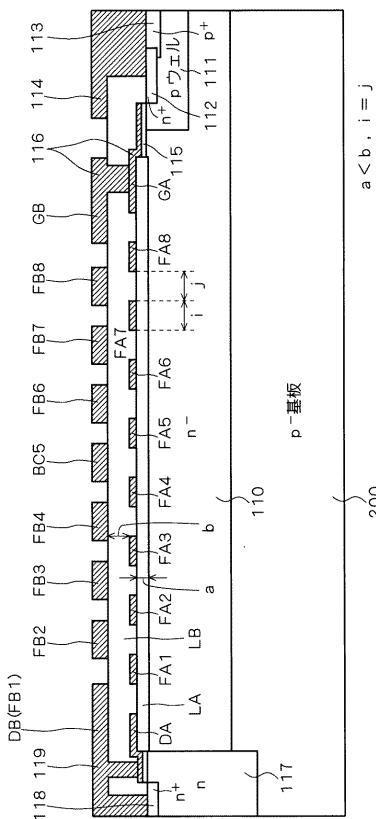

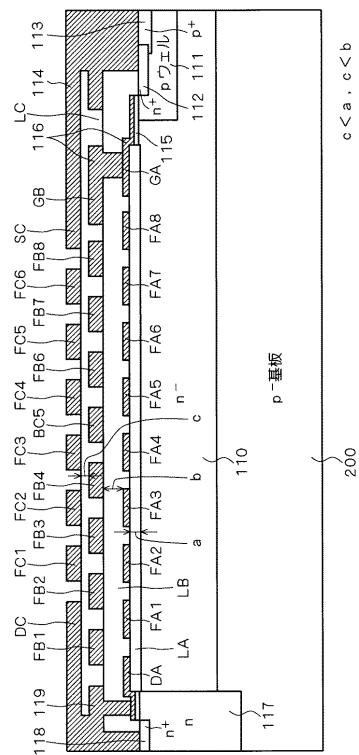

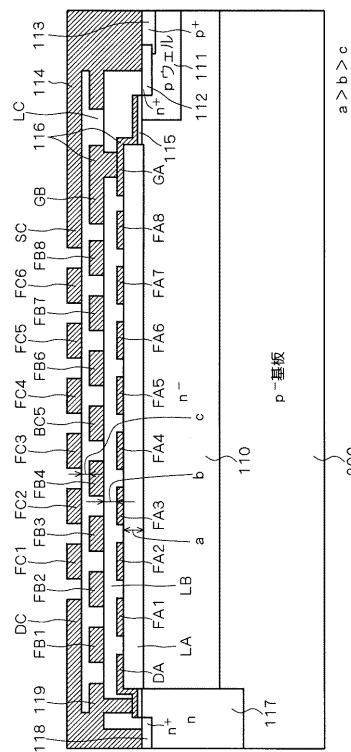

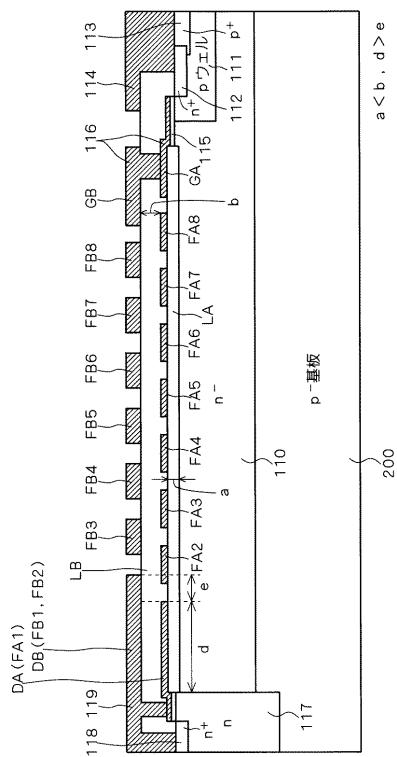

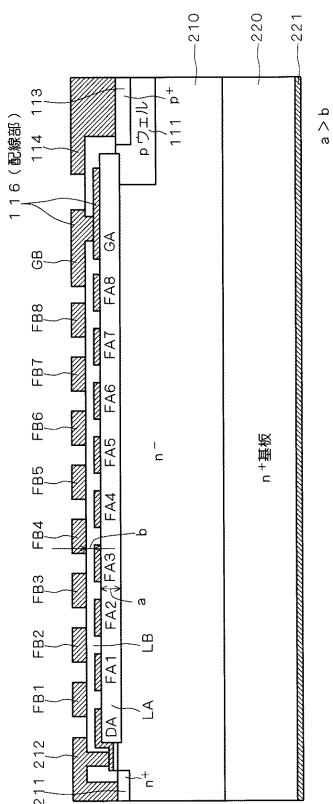

図6は、実施の形態1に係るHV-MOSの構成を示す図であり、図4におけるHV-MOS11の拡大図である。図4に示したものと同様の要素には同符号を付してある。但し、この図においては、以降の説明の便宜を図るために、図4とは左右を逆にして描いている。

【0038】

$n^-$ 層110の上には第1絶縁膜LAが形成される。第1絶縁膜LAの上面には、 $n^-$ 層110の上方に、複数個の第1フローティングフィールドプレートFA（FA1～FA8）が形成される。さらに、第1フローティングフィールドプレートFAの上には、第2絶縁膜LBが形成される。第2絶縁膜LBの上面には、 $n^-$ 層110の上方に、複数個の第2フローティングフィールドプレートFB（FB1～FB8）が形成される。

【0039】

ここで、本明細書においては、第3半導体領域（ここでは $n$ 領域117）から第2半導体領域（ここでは $n^+$ ソース領域112）へ向かう方向を「第1方向」と称し、第1絶縁膜LA、第2絶縁膜LBの厚さ方向を「第2方向」と称する（図6の矢印参照）。第1フローティングフィールドプレートFA1～FA8は、第1方向に並んで配設されており、

10

20

30

40

50

第2フローティングフィールドプレートF B 1～F B 8も、同じく第1方向に並んで配設されている。

【0040】

また、ドレイン電極119は、第1絶縁膜L A上に延びる部位D Aを有しており、この部分は通常の（フローティング状態ではない）フィールドプレートとして機能している。以下、当該部位を「第1ドレイン電極部D A」と称する。一方、ゲート電極116は、第1絶縁膜L A上に延びる部位G Aおよび第2絶縁膜L B上に延びる部位G Bを有しており、この部分も通常のフィールドプレートとして機能している。以下、両者をそれぞれ「第1ゲート電極部G A」とおよび「第2ゲート電極部G B」と称する。

【0041】

第1フローティングフィールドプレートF Aおよび第2フローティングフィールドプレートF Bは、フィールドプレート効果によって、n<sup>-</sup>層110内の空乏層の拡がりを促進させる。個々の第1フローティングフィールドプレートF Aおよび第2フローティングフィールドプレートF Bは、第2絶縁膜L Bを介して互いに容量結合して複数のコンデンサ（キャパシタ）を形成している。また、最ドレイン側の第2フローティングフィールドプレートF B 1は、第2絶縁膜L Bを介して第1ドレイン電極部D Aとの間でコンデンサを形成し、最ゲート側の第1絶縁膜L A 8は、第2絶縁膜L Bを介して第2ゲート電極部G Bとの間でコンデンサを形成している。これら多数のコンデンサは、HV-MOSの遮断時にはドレイン電極119-ソース電極114間に印加される高電圧を分担して保持し、それによって、各々の第1フローティングフィールドプレートF Aおよび第2フローティングフィールドプレートF Bの電位が定まる。それによって、フィールドプレート効果により空乏層の拡がりが促進され過ぎるのを抑制している。

【0042】

例えば、第1フローティングフィールドプレートF Aが連続した1枚のものであったと仮定すると、空乏層の拡がりが促進され過ぎ、ドレイン近くのシリコン基板表面で電界集中が生じ、HV-MOSの高耐圧化が困難となる。そこで本実施の形態では、第1フローティングフィールドプレートF Aおよび第2フローティングフィールドプレートF Bをそれぞれ複数個、第1方向に並べて配設することで、空乏層の拡がり過ぎを抑制し、HV-MOSの高耐圧化を図っている。

【0043】

また、図6のHV-MOSには、いわゆるRESURF構造を適用してさらなる高耐圧化を図っている。即ち、n<sup>-</sup>層110とp<sup>-</sup>領域200（第4半導体領域）との間のpn接合（以下「第1pn接合」）に、n<sup>-</sup>層110とpウェル111との間のpn接合（以下「第2pn接合」）の降伏電圧よりも低い逆方向電圧が印加されることによって、n領域117とpウェル111との間のn<sup>-</sup>層110内で、空乏層が、第1pn接合から基板の上面にまで拡がる程度に、n<sup>-</sup>層110は不純物濃度が低く、且つ、厚さが薄くなっている。

【0044】

本実施の形態では、第1絶縁膜L Aの厚さをaとし、第1フローティングフィールドプレートF Aと第2フローティングフィールドプレートF Bとの間の第2方向（第2絶縁膜L Bの厚さ方向）の距離をbとしたとき、a>bとなるように、従来の構造よりも第1絶縁膜L Aを厚く、第2絶縁膜L Bを薄くしている。

【0045】

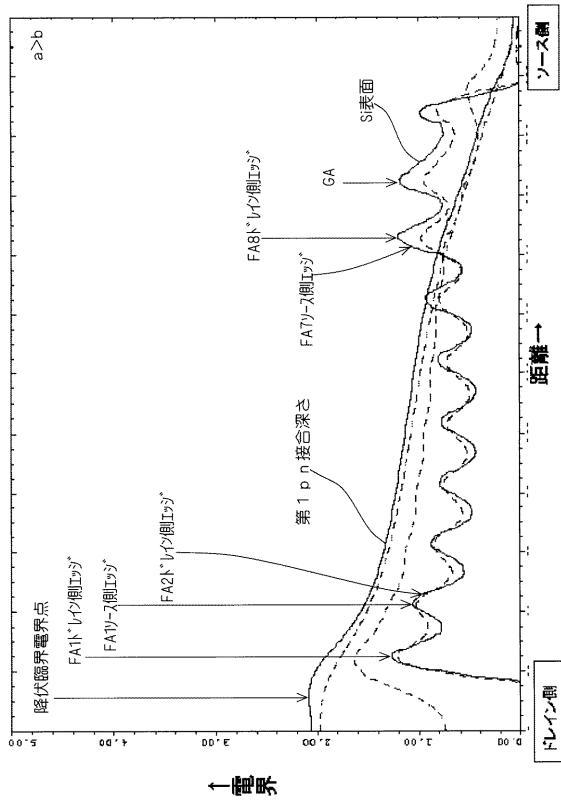

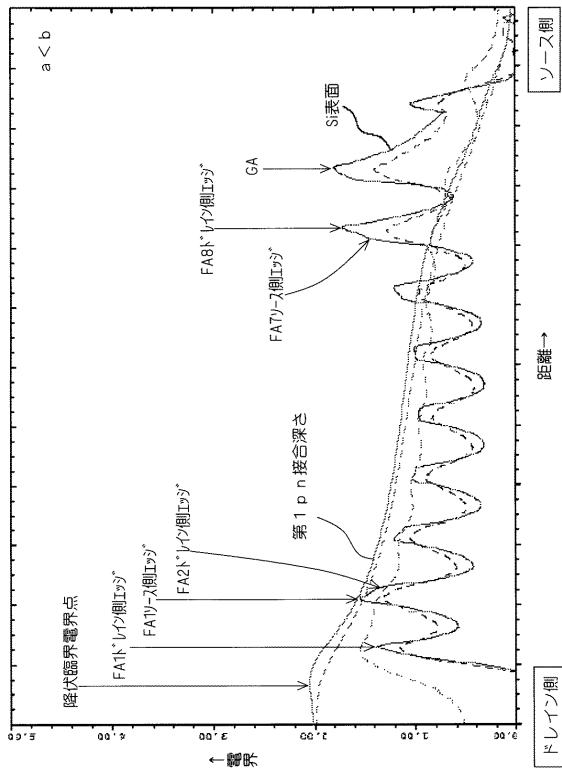

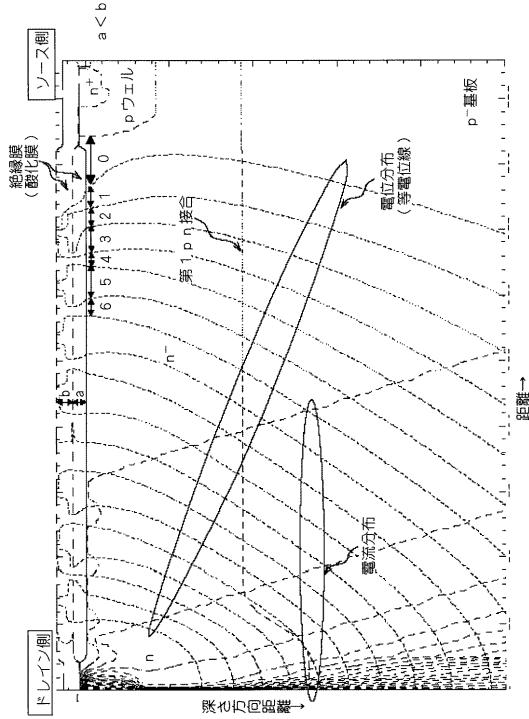

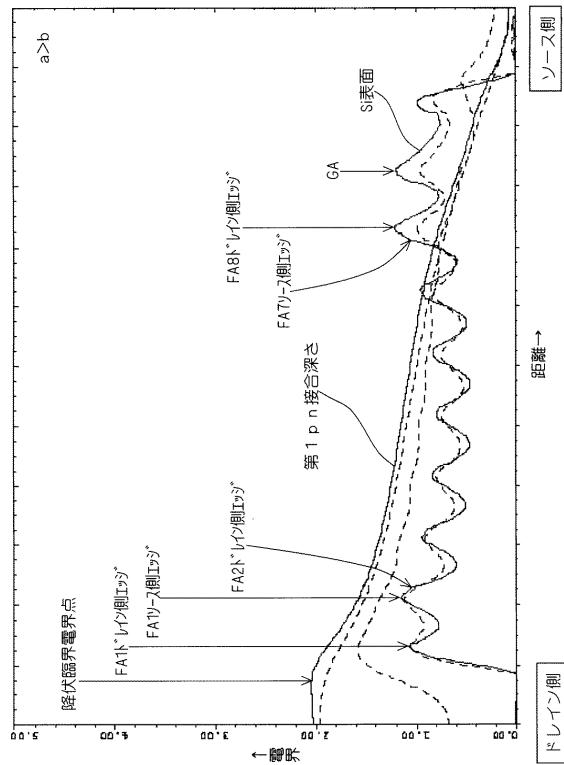

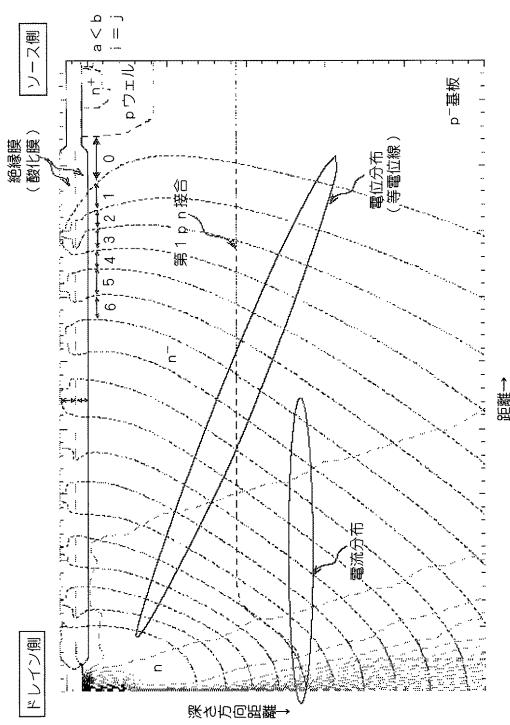

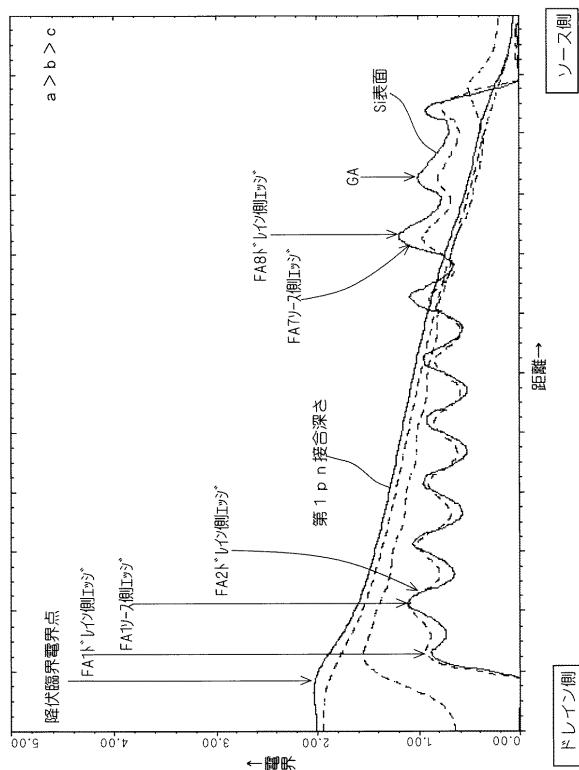

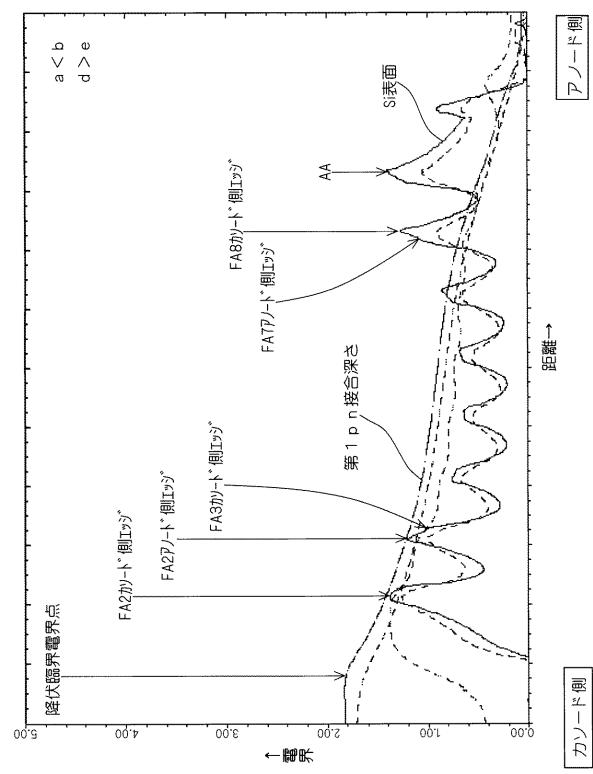

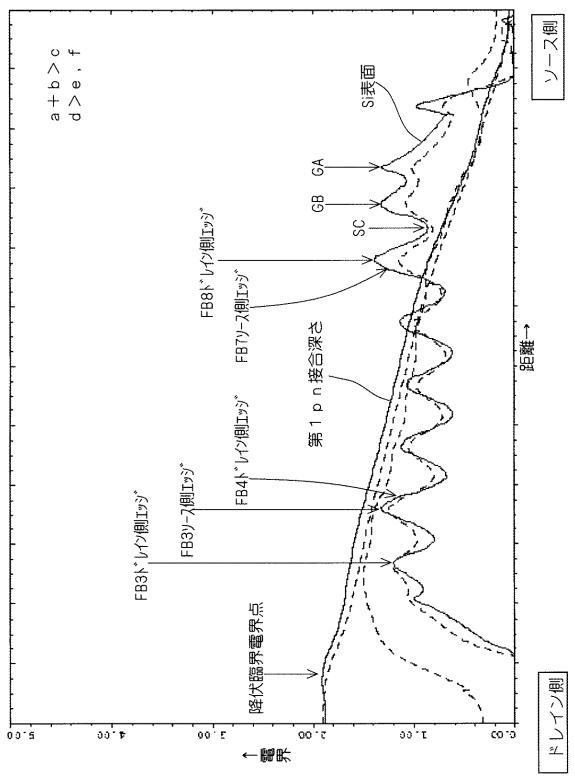

図7は、図6のHV-MOSにおいて、ゲート電極116-ソース電極114間に短絡して当該HV-MOSを遮断状態にし、ドレイン電極119-ソース電極114間に高電圧を印加したときの当該HV-MOS内部の電界分布を示す図である。同図では、シリコン基板表面（Si表面）から、n領域117とp<sup>-</sup>領域200との間のpn接合深さにかけての電界分布を示している。特に実線は、シリコン基板表面の電界分布と、n<sup>-</sup>層110とp<sup>-</sup>領域200との間の第1pn接合深さの電界分布とを示している。一方、図8は、従来のHV-MOS（図6においてa<bであり、且つ、ドレイン電極119と第2フ

10

20

30

40

50

ローティングフィールドプレート F B 1 とが接続しているもの)における、図 7 と同様の電界分布を示す図である。

【 0 0 4 6 】

図 7, 図 8 から分かるように、電界強度が最も高い箇所は、第 1 p n 接合深さにおけるドレイン近傍の部分である。従って、H V - M O S の耐電圧値を決定付ける箇所である降伏臨界電界点はその部分になる。一方、シリコン基板表面では、第 1 ゲート電極部 G A の先端の下方および第 1 フローティングフィールドプレート F A 1 ~ F A 8 それぞれのドレイン側エッジの下方あるいはソース側エッジの下方において、電界ピーク(電界集中)が観察される。

【 0 0 4 7 】

図 8 のように、従来構造の H V - M O S では、シリコン基板表面における電界ピークが比較的大きく、降伏臨界電界点における電界強度との差(マージン)は僅かである。従って、実使用時に H V - M O S 上に形成されるオーバーコート絶縁膜やエポキシ樹脂の分極の影響によって、シリコン基板表面の電界ピークが降伏臨界電界点の電界強度を越え易く、耐圧低下や耐圧特性の不安定の問題が懸念される。

10

【 0 0 4 8 】

それに対し、図 7 に示す本実施の形態では、シリコン基板表面における電界ピークが比較的小さいことが分かる。つまり、電界集中が緩和されていることが分かる。従って、降伏臨界電界点の電界強度に対するマージンが大きくなり、シリコン基板表面の電界ピークが降伏臨界電界点の電界強度を越え難くなるので、耐圧低下や耐圧特性の不安定の問題は抑えられる。その結果、H V - M O S は、安定して高耐圧を維持することができる。

20

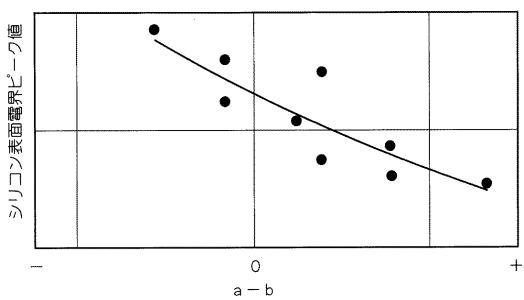

【 0 0 4 9 】

図 9 は、a - b とシリコン基板表面の電界ピーク値との関係を示す図である。a - b の値が大きくなるほど電界ピーク値は、小さくなることが分かる。つまり、厚さ a を大きくし、距離 b を小さくして a - b の値をより大きくすることにより、降伏臨界電界点の電界強度に対するマージンは大きくなるり、上記の効果を大きくすることができる。

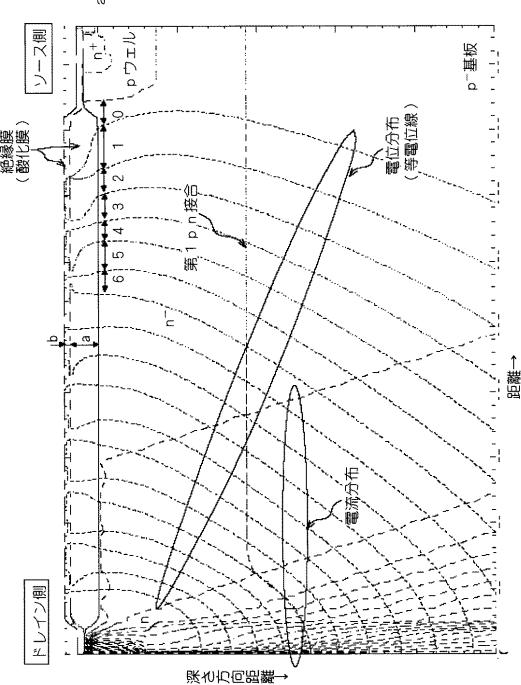

【 0 0 5 0 】

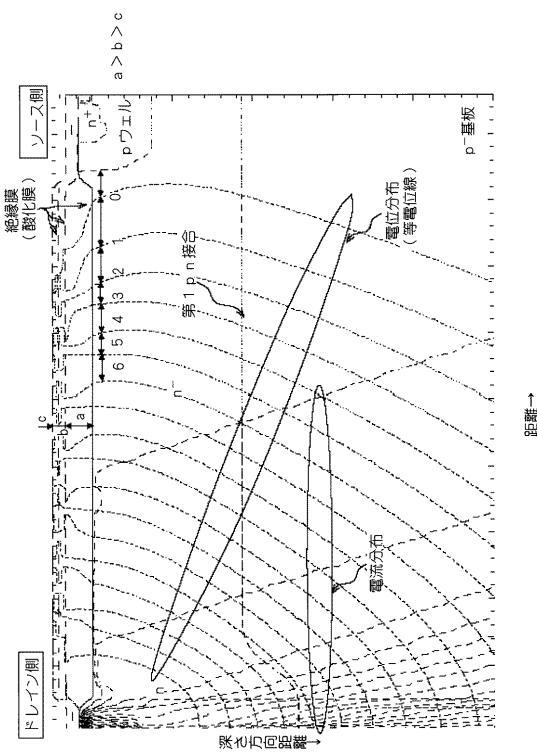

さらに、図 10 は、図 6 の H V - M O S の遮断状態において、ドレイン電極 119 - ソース電極 114 間に高電圧を印加した場合における当該 H V - M O S 内の電位分布および電流分布を示す図である。電位分布は等電位線で示しており、その形状は、ソース側からドレイン側に空乏層の拡がりの形に対応している。一方、図 11 は、従来の H V - M O S (即ち、図 6 において a < b であるもの)における、図 10 と同様の電位分布および電流分布を示している。

30

【 0 0 5 1 】

図 10 および図 11 における参考番号 0 ~ 6 は、シリコン基板表面( n 層 110 と第 1 絶縁膜 L A との界面)における等電位線の間隔を示している。本実施の形態に係る H V - M O S では、第 1 絶縁膜 L A の厚さ a が大きいため図 10 のように等電位線の歪みが第 1 絶縁膜 L A 内で緩和されるので、従来の図 11 に比較して間隔 0 ~ 6 の大きさが均等になっている。このことは、本実施の形態の H V - M O S では、従来構造のものよりもシリコン基板表面近傍における空乏層の拡がりが均一であることを示している。空乏層の拡がりが均一になれば電界集中は生じにくくなるので、本実施の形態の H V - M O S においては、シリコン基板表面での電界ピークの大きさは低く抑えられる。このように図 10 の電位分布からも、図 7 を用いて説明した効果が観察できる。

40

【 0 0 5 2 】

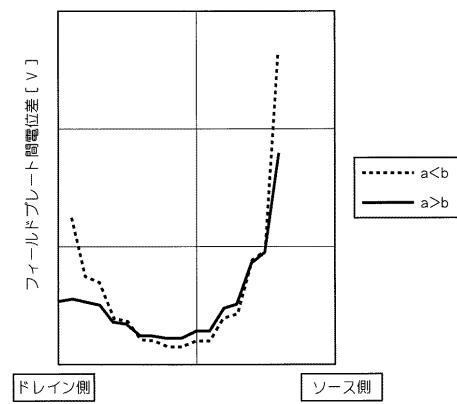

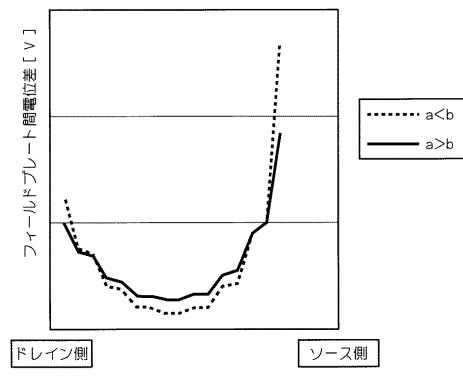

また図 12 は、遮断状態の H V - M O S のソース - ドレイン間に高電圧を印加したときの、第 1 フローティングフィールドプレート F A、第 2 フローティングフィールドプレート F B、第 1 ドレイン電極部 D A、第 1 ゲート電極部 G A、第 2 ゲート電極部 G B の間に形成される各コンデンサが保持する電位差の、ドレイン - ソース間分布を示している。図 12 において、実線のグラフは本実施の形態に係る図 6 の H V - M O S における分布のグラフであり、点線は従来の H V - M O S (図 6 において a < b であり、且つドレイン電極

50

119と第2フローティングフィールドプレートF B 1とが接続しているもの)における分布のグラフである。従来構造のH V - M O Sでは、ソース側およびドレイン側に近いコンデンサに特に高い電圧が保持される傾向があり、その部分での第2絶縁膜L Bの絶縁破壊が懸念されていた。図12に示すように、本実施の形態のH V - M O Sではその傾向は小さくなり、各コンデンサが保持する電位差のばらつきが小さくなつた。つまり、本実施の形態によれば、第2絶縁膜L Bの絶縁破壊が生じにくくなるという効果も得られ、それによってもH V - M O Sの高耐圧化に寄与できる。

#### 【0053】

また、本実施の形態のH V - M O Sでは、従来構造よりも第1フローティングフィールドプレートF Aと第2フローティングフィールドプレートF Bとの間の厚さ方向(第2方向)の距離bを小さくしているため、各コンデンサの容量値は大きくなる。従って、各コンデンサにおける容量結合効果は高くなるので、第2絶縁膜L Bの分極化が促進される。従来構造では、n<sup>-</sup>層110上部の空乏層は、各第1フローティングフィールドプレートF Aの下方では拡がりやすいものの、各第1フローティングフィールドプレートF Aの間の下方では拡がり難い傾向にあった。しかし、本実施の形態では、各コンデンサにおける高い容量結合効果によって第2絶縁膜L Bが分極化され、その影響により、各第1フローティングフィールドプレートF Aの間の下方でも空乏層が拡がり易くなるという効果も得られ、それによってもH V - M O Sの高耐圧化に寄与できる。

#### 【0054】

上で示したように、本発明はR E S U R F構造を有する半導体装置に適用することが可能である。それにより、従来のR E S U R F構造よりも更なる高耐圧化を図ることができる。また、n<sup>-</sup>層110を不純物濃度が互いに異なる多層構造にした、いわゆるマルチR E S U R F構造(例えば、米国特許第4422089号)に適用することも可能である。

#### 【0055】

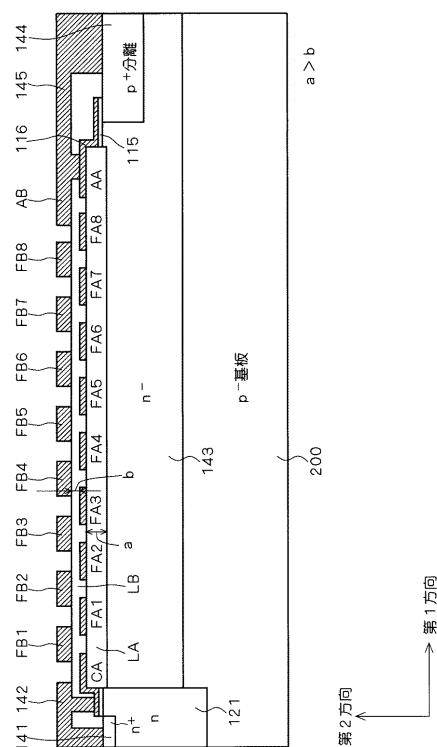

また以上の説明では、本発明をM O S F E Tに適用した例を示したが、本発明の適用はそれに限定されるものではなく、例えばダイオードやI G B Tなどにも広く適用することが可能である。図13は、実施の形態1を高耐圧ダイオード(H V - ダイオード)に適用した例を示す図であり、図5におけるH V - ダイオード14の拡大図である。図5および図6に示したものと同様の要素には同符号を付してあるので、ここでの詳細な説明は省略する。なお、この図においても、以降の説明の便宜を図るために、図5とは左右を逆にして描いている。

#### 【0056】

カソード電極142は、第1絶縁膜L A上に延びる部位C Aを有しており、この部分は通常のフィールドプレートとして機能する。以下、当該部位を「第1カソード電極部C A」と称する。アノード電極145は、第1絶縁膜L A上に延びる部位A Aおよび第2絶縁膜L B上に延びる部位A Bを有しており、これら部分は通常のフィールドプレートとして機能する。以下、それぞれ「第1アノード電極部A A」および「第2アノード電極部A B」と称する。

#### 【0057】

また、上記したようにH V - ダイオード14においては、n<sup>-</sup>層143が第1半導体領域、p<sup>+</sup>アノード領域144が第2半導体領域、n層121が第3半導体領域として機能するので、この場合の「第1方向」はn層121からp<sup>+</sup>アノード領域144へ向かう方向である(図13の矢印参照)。

#### 【0058】

このH V - ダイオード14にも、いわゆるR E S U R F構造を適用している。即ち、n<sup>-</sup>層143とp<sup>+</sup>領域200(第4半導体領域)との間の第1p n接合に、n<sup>-</sup>層143とp<sup>+</sup>アノード領域144の間の第2p n接合の降伏電圧よりも低い逆方向電圧が印加されることによって、n層121とp<sup>+</sup>アノード領域144との間のn<sup>-</sup>層143内で、空乏層が、第1p n接合から基板の上面にまで拡がる程度に、n<sup>-</sup>層143は不純物濃度が低く、且つ、厚さが薄くなっている。

10

20

30

40

50

## 【0059】

図13のHV-ダイオードでも、第1絶縁膜LAの厚さをaとし、第1フローティングフィールドプレートFAと第2フローティングフィールドプレートFBとの間の第2方向の距離をbとしたとき、a>bとなるように、従来構造よりも第1絶縁膜LAを厚く、第2絶縁膜LBを薄く形成している。a>bであるHV-ダイオードでも、シリコン基板表面の電界ピークが低くなつて電界集中が緩和され、耐圧低下や耐圧特性の不安定の問題は抑えられるなど、上での説明と同様の効果を得ることができる。

## 【0060】

＜実施の形態2＞

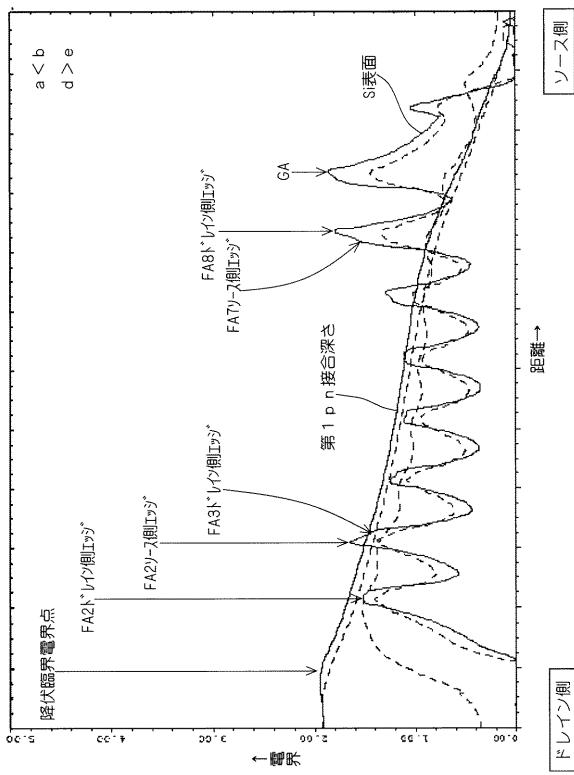

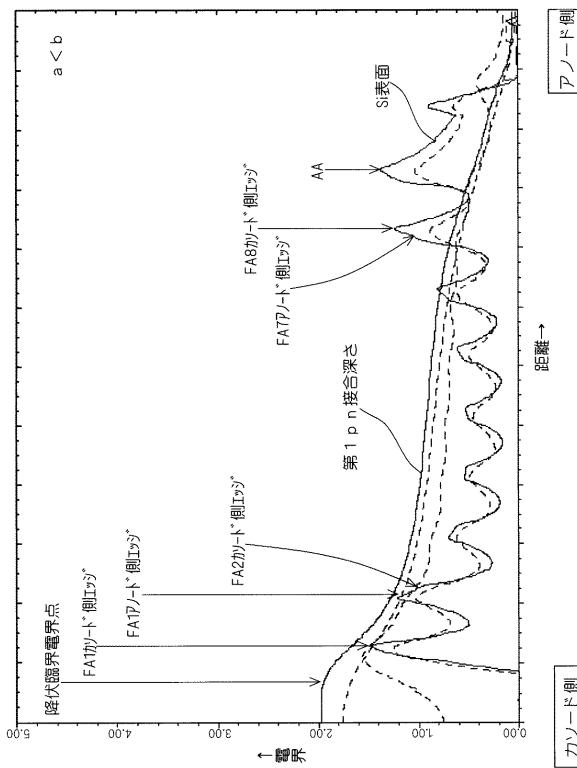

図14は、実施の形態2に係るHV-MOSの構成を示す図である。実施の形態1において図6に示したHV-MOSと異なる点は、ドレン電極119が、第2絶縁膜LB上に延びる部位DBを有していることである。この部位DBは通常の（フローティング状態ではない）フィールドプレートとして機能しており、以下「第2ドレン電極部DB」と称する。

10

## 【0061】

図14に示すように、第2ドレン電極部DBにおける第1絶縁膜LA上方を第1方向（n領域117からn<sup>+</sup>ソース領域112に向かう方向）に延びた部分の長さは、第1ドレン電極部DAにおける第1絶縁膜LA上を第1方向に延びた部分の長さよりも長い。つまり、第2ドレン電極部DBは、第2絶縁膜LBを介して第1ドレン電極部DAの上方を覆っている。そして、第2ドレン電極部DBは、その一部が第1フローティングフィールドプレートFA1の一部と第2絶縁膜LBを介して重なっている。即ち、図14に示しているように、当該第2ドレン電極部DBは、図6のドレン電極119に第2フローティングフィールドプレートFB1を接続したものであると言つてもできる。

20

## 【0062】

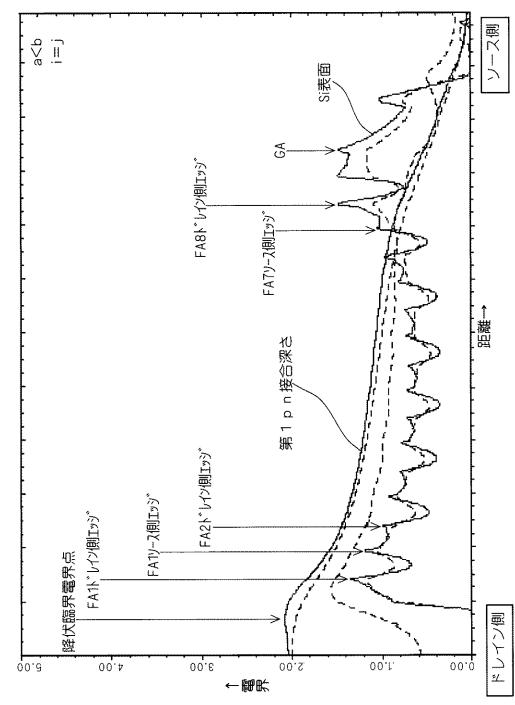

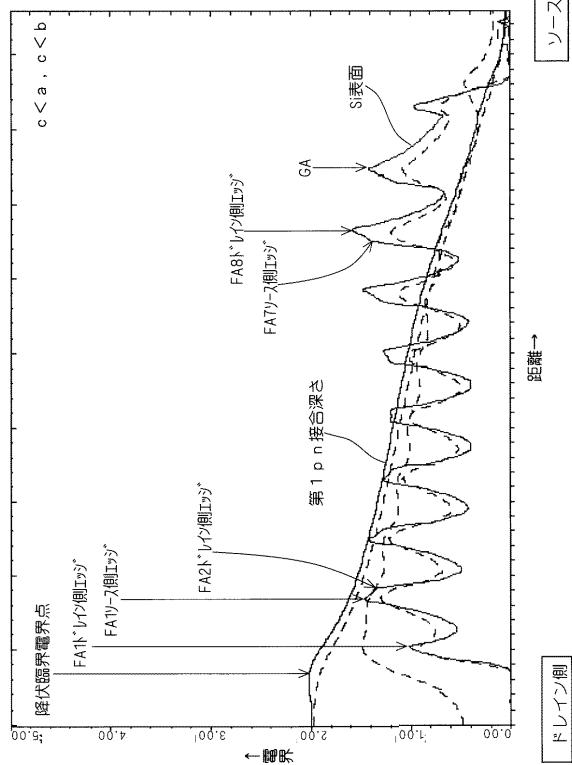

図15は、図14のHV-MOSにおいて、ゲート電極116-ソース電極114間に短絡して当該HV-MOSを遮断状態にし、ドレン電極119-ソース電極114間に高電圧を印加したときの該HV-MOS内部の電界分布を示す図である。同図では、シリコン基板表面（Si表面）から、n領域117とp<sup>-</sup>領域200との間のpn接合深さにかけての電界分布を示している。特に実線は、シリコン基板表面の電界分布と、n<sup>-</sup>層110とp<sup>-</sup>領域200との間の第1pn接合深さの電界分布とを示している。

30

## 【0063】

図15と実施の形態1で示した図7とを比較して分かるように、本実施の形態によれば、シリコン基板表面における、最ドレン側の第1フローティングフィールドプレートFA1のエッジ部下方の電界ピークが緩和される。その影響により、降伏臨界電界点（ドレン側のn領域117の第1pn接合深さの部分）の近傍の電界強度が低くなるので、HV-MOSは高耐圧化される。つまり本実施の形態によれば、実施の形態1よりもさらなる高耐圧化が可能となる。

## 【0064】

また図16は、遮断状態のHV-MOSのソース-ドレン間に高電圧を印加したときの、第1フローティングフィールドプレートFA、第2フローティングフィールドプレートFB、第1ドレン電極部DA、第1ゲート電極部GA、第2ゲート電極部GBの間に形成される各コンデンサが保持する電位差の、ドレン-ソース間分布を示している。図16において、実線のグラフは本実施の形態に係る図14のHV-MOSにおける分布のグラフであり、点線は従来のHV-MOS（図14において、a<bのもの）における分布のグラフである。本実施の形態でも、実施の形態1と同様に各コンデンサが保持する電位差のばらつきが小さくなることが分かる。つまり、本実施の形態においても、第2絶縁膜LBの絶縁破壊が生じにくくなり、HV-MOSの高耐圧化に寄与できる。

40

## 【0065】

＜実施の形態3＞

図17は、実施の形態3に係るHV-MOSの構成を示す図である。この図においては

50

、図6および図14に示したものと同様の要素には同一符号を付してあるので、それらの詳細な説明は省略する。

【0066】

本実施の形態では、個々の第1フローティングフィールドプレートFAの幅と、第1フローティングフィールドプレートFA同士の間隔を等しくしている。つまり、個々の第1フローティングフィールドプレートFAの第1方向(  $n$  領域117から $n^+$ ソース領域112に向かう方向)の幅をi、個々の第1フローティングフィールドプレート間の第1方向の距離をjとしたとき、 $i = j$ である。また、図17の例では、厚さa(第1絶縁膜LAの厚さ)と、距離b(第1フローティングフィールドプレートFAと第2フローティングフィールドプレートFB間ににおける第2方向の距離)との関係は、従来構造と同じ $a < b$ としている。上記以外の点は、実施の形態2で示した図14と同様である。

10

【0067】

図18は、図17のHV-MOSにおいて、ゲート電極116-ソース電極114間に短絡して当該HV-MOSを遮断状態にし、ドレイン電極119-ソース電極114間に高電圧を印加したときのHV-MOS内部の電界分布を示す図である。同図では、シリコン基板表面(  $S_i$  表面)から、 $n$  領域117と $p^-$ 領域200との間の $p-n$ 接合深さにかけての電界分布を示している。特に実線は、シリコン基板表面の電界分布と、 $n^-$ 層110と $p^-$ 領域200との間の第1 $p-n$ 接合深さの電界分布とを示している。従来構造のHV-MOSにおける電界分布を示す図8と比較して分かるように、本実施の形態の図18では、シリコン基板表面の電界ピークが低くなっていることが分かる。従って、降伏臨界電界点の電界強度に対するマージンが大きくなり、シリコン基板表面の電界ピークが降伏臨界電界点の電界強度を越え難くなるので、耐圧低下や耐圧特性の不安定の問題は抑えられる。その結果、HV-MOSは、安定して高耐圧を維持することができる。

20

【0068】

図19は、図17のHV-MOSの遮断状態において、ドレイン電極119-ソース電極114間に高電圧を印加したときの当該HV-MOS内部の電位分布および電流分布を示す図である。図19においても電位分布は等電位線で示しており、参照番号0~6はシリコン基板表面(  $n^-$ 層110と第1絶縁膜LAとの界面)における等電位線の間隔を示している。本実施の形態では、個々の第1フローティングフィールドプレートFAの幅と、第1フローティングフィールドプレートFA同士の幅を等しくしているので、従来の図11に比較して、間隔0~6が均等になっている。つまり、本実施の形態のHV-MOSでは、従来構造のものよりもシリコン基板表面近傍における空乏層の拡がりが均一であり、その部分での電界ピークの大きさは低く抑えられる。このように図19の電位分布からも、上記効果が観察できる。

30

【0069】

なお、図17では、厚さaと距離bとの関係を $a < b$ としたが、実施の形態1を適用して $a > b$ としてもよい。その場合は、実施の形態1で説明した効果も得ることができ、更なる高耐圧化が可能となる。

40

【0070】

また本実施の形態でも、本発明をMOSFETに適用した例を示したが、本発明の適用はそれに限定されるものではなく、例えばダイオードやIGBTなどにも広く適用することが可能である。

【0071】

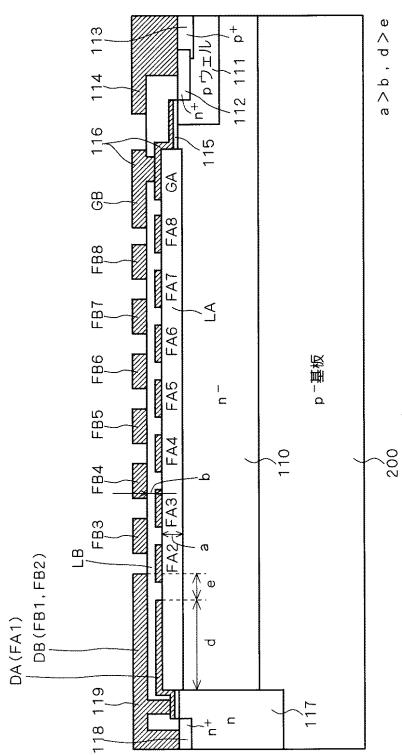

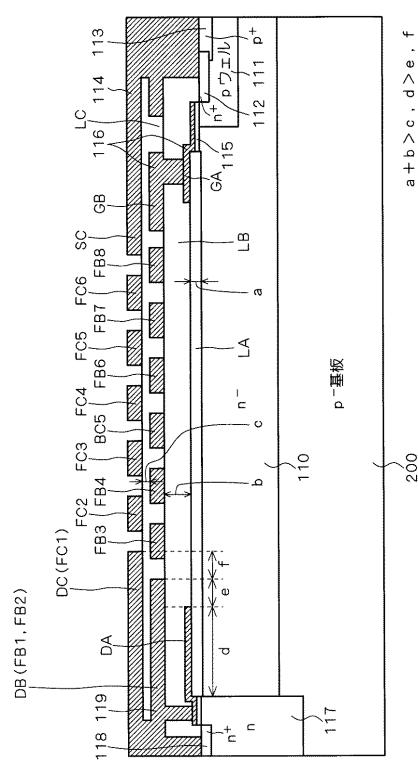

<実施の形態4>

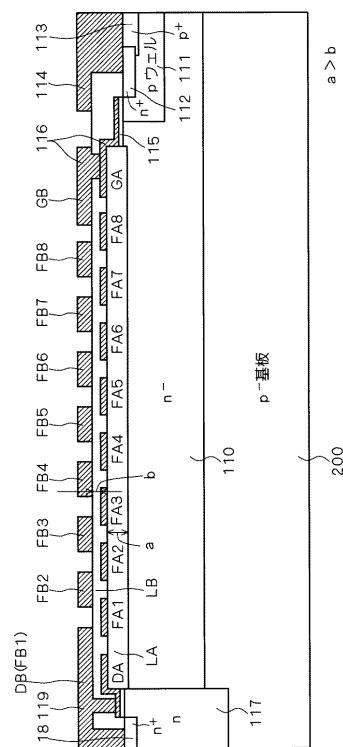

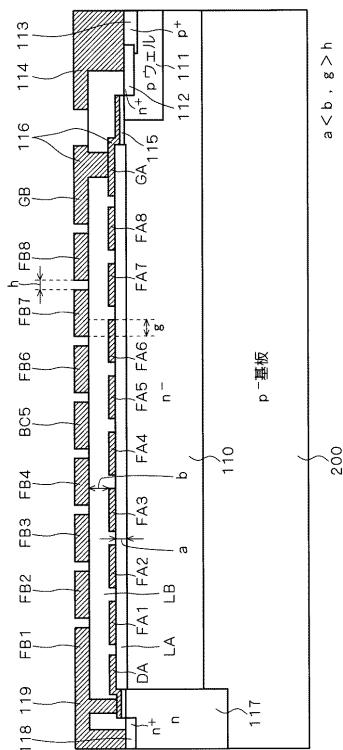

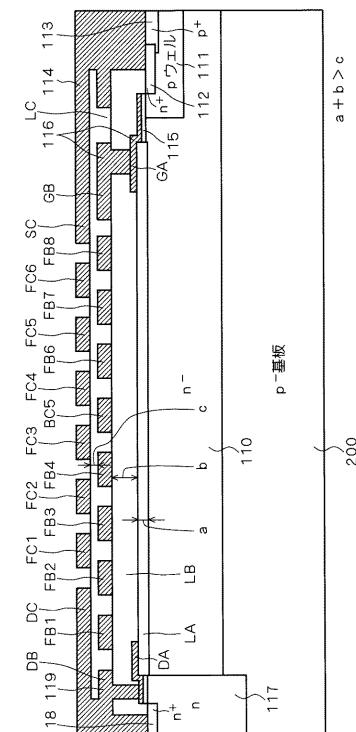

図20は、実施の形態4に係るHV-MOSの構成を示す図である。この図においては、図6および図14に示したものと同様の要素には同一符号を付してあるので、それらの詳細な説明は省略する。

【0072】

本実施の形態に係るHV-MOSは、図6のHV-MOSの構成に加え、第2フローティ

50

イングフィールドプレート F B 上に形成された第 3 絶縁膜 L C および、その上に形成された複数個の第 3 フローティングフィールドプレート F C ( F C 1 ~ F C 6 ) を有している。第 3 フローティングフィールドプレート F C は、 $n^-$ 層 110 の上方に、第 1 方向 ( $n^-$  領域 117 から  $n^+$  ソース領域 112 に向かう方向) に並べて配設されている。そして、第 1 絶縁膜 L A の厚さを a とし、第 1 フローティングフィールドプレート F A と第 2 フローティングフィールドプレート F B との間の第 2 方向 (第 1 絶縁膜 L A、第 2 絶縁膜 L B、第 3 絶縁膜 L C の厚さ方向) の距離を b とし、第 2 フローティングフィールドプレート F B と第 3 フローティングフィールドプレート F C との間の第 2 方向の距離を c とすると、 $c < a$  且つ  $c < b$  となるように、距離 c を小さくしている (第 3 絶縁膜 L C を薄くしている)。図 20 の例では、厚さ a と距離 b との関係は、従来構造と同じ  $a < b$  としている。

10

### 【 0073 】

また、ドレイン電極 119 は、第 3 絶縁膜 L C 上に延びる部位 D C を有しており、この部分は通常の (フローティング状態ではない) フィールドプレートとして機能している。以下、当該部位を「第 3 ドレイン電極部 D C」と称する。一方、ソース電極 114 は第 3 絶縁膜 L C 上に延びる部位 S C を有しており、この部分も通常のフィールドプレートとして機能している。以下、当該部位を「ソース電極部 S C」と称する。

### 【 0074 】

図 21 は、図 20 の H V - M O S において、ゲート電極 116 - ソース電極 114 間を短絡して H V - M O S を遮断状態にし、ドレイン電極 119 - ソース電極 114 間に高電圧を印加したときの H V - M O S 内部の電界分布を示す図である。同図では、シリコン基板表面 ( S i 表面) から、 $n^-$  領域 117 と  $p^-$  領域 200 との間の  $p^-n$  接合深さにかけての電界分布を示している。特に実線は、シリコン基板表面の電界分布と、 $n^-$  層 110 と  $p^-$  領域 200 との間の第 1  $p^-n$  接合深さの電界分布とを示している。従来構造の H V - M O S における電界分布を示す図 8 と比較して分かるように、図 21 ではシリコン基板表面の電界ピークが低くなっていることが分かる。従って、降伏臨界電界点の電界強度に対するマージンが大きくなり、シリコン基板表面の電界ピークが降伏臨界電界点の電界強度を越え難くなるので、耐圧低下や耐圧特性の不安定の問題は抑えられる。その結果、H V - M O S は、安定して高耐圧を維持することができる。

20

### 【 0075 】

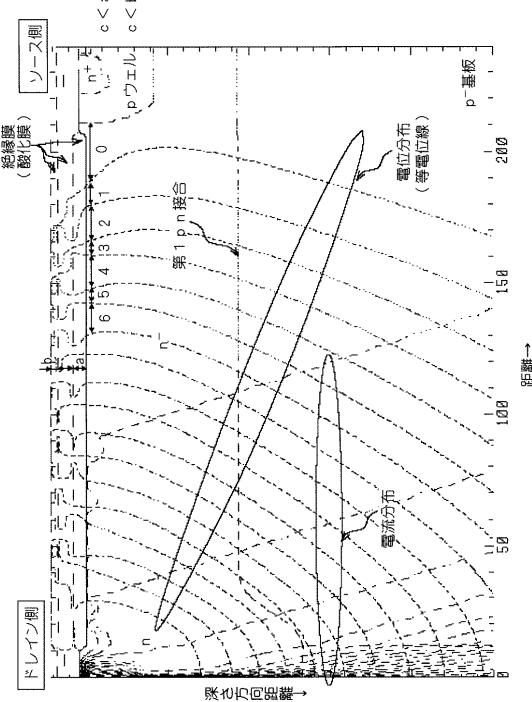

図 22 は、図 20 の H V - M O S の遮断状態において、ドレイン電極 119 - ソース電極 114 間に高電圧を印加したときの電位分布および電流分布を示す図である。図 22 においても、電位分布は等電位線で示しており、参照番号 0 ~ 6 は、シリコン基板表面 ( $n^-$  層 110 と第 1 絶縁膜 L A との界面) における等電位線の間隔を示している。従来の図 11 に比較して、シリコン基板表面の等電位線がドレイン側へシフトしており、シリコン基板表面で空乏層が拡がり易いことがわかる。これは、シリコン基板表面の電界ピークが低くなることを示している。このように図 22 の電位分布からも、上記効果が観察できる。

30

### 【 0076 】

また、本実施の形態の H V - M O S では、上記距離 c を小さくしているため、第 2 フローティングフィールドプレート F B、第 3 フローティングフィールドプレート F C、第 3 ドレイン電極部 D C、ソース電極部 S C により形成される各コンデンサの容量値は大きくなる。従って、それらのコンデンサにおける容量結合効果は高くなるので、第 3 絶縁膜 L C の分極化が促進される。その影響により、従来空乏層が拡がり難かった各第 1 フローティングフィールドプレート F A の間の下方でも、空乏層が拡がり易くなるという効果も得られ、それによっても H V - M O S の高耐圧化に寄与できる。

40

### 【 0077 】

なお、図 20 では、厚さ a と距離 b との関係を  $a < b$  としたが、実施の形態 1 を適用して図 23 のように  $a > b$  としてもよい。その場合は、実施の形態 1 で説明した効果も得ることができ、更なる高耐圧化が可能となる。

50

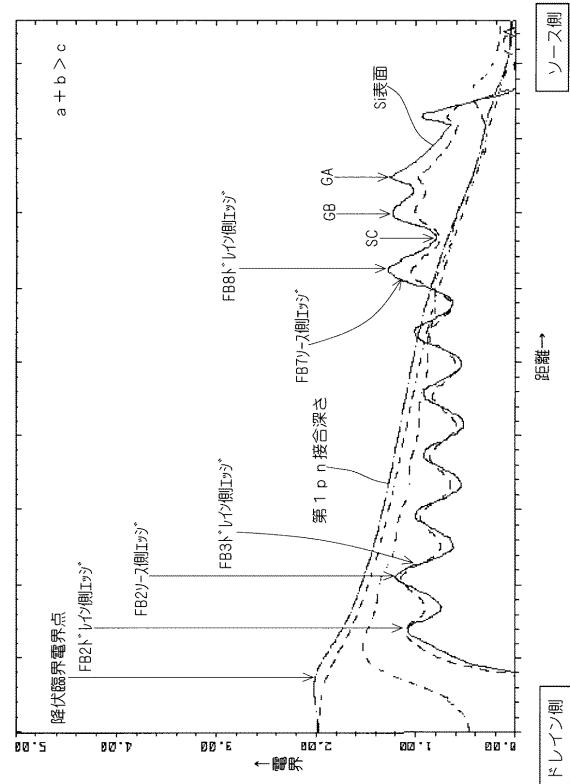

## 【0078】

図24は、図23のHV-MOSにおいて、ゲート電極116-ソース電極114間に短絡してHV-MOSを遮断状態にし、ドレイン電極119-ソース電極114間に高電圧を印加したときのHV-MOS内部の電界分布を示す図である。同図では、シリコン基板表面(Si表面)から、n領域117とp領域200との間のpn接合深さにかけての電界分布を示している。特に実線は、シリコン基板表面の電界分布と、n層110とp領域200との間の第1pn接合深さの電界分布とを示している。図21よりもさらに、シリコン基板表面の電界ピークが低くなっていることが分かる。

## 【0079】

また図25は、図23のHV-MOSの遮断状態において、ドレイン電極119-ソース電極114間に高電圧を印加した場合におけるHV-MOS内の電位分布および電流分布を示す図である。電位分布は等電位線で示しており、参考番号0~6は、シリコン基板表面における等電位線の間隔を示している。図23のHV-MOSでは、第1絶縁膜LAの厚さaが大きいため、等電位線の歪みが第1絶縁膜LA内で緩和されるので、図22よりも間隔0~6が均等になっている。そのため、シリコン基板表面での電界ピークの大きさも低く抑えられることが分かる。

## 【0080】

このように、実施の形態1を適用することによって、更なる高耐圧化が可能となる。また以上の説明では、本発明をMOSFETに適用した例を示したが、本発明の適用はそれに限定されるものではなく、例えばダイオードやIGBTなどにも広く適用することが可能である。

## 【0081】

## &lt;実施の形態5&gt;

図26は、実施の形態5に係るHV-MOSの構成を示す図である。この図においては、図6および図14に示したものと同様の要素には同一符号を付してあるので、それらの詳細な説明は省略する。

## 【0082】

本実施の形態では、従来構造よりも第1フローティングフィールドプレートFAおよび第2フローティングフィールドプレートFBの幅を広くしている。即ち、個々の第1フローティングフィールドプレートFAにおいて第2絶縁膜LBを介して1つの第2フローティングフィールドプレートFBと重なる部分の第1方向の幅をgとし、個々の第2フローティングフィールドプレートFB間の第1方向の距離をhとすると、 $g > h$ となるようにしている(図26参照)。

## 【0083】

また、図26の例では、厚さa(第1絶縁膜LAの厚さ)と、距離b(第1フローティングフィールドプレートFAと第2フローティングフィールドプレートFB間における第2方向の距離)との関係は、従来構造と同じ $a < b$ としている。

## 【0084】

上記以外の点は、実施の形態2で示した図14と同様である。

## 【0085】

本実施の形態によれば、第1フローティングフィールドプレートFAと第2フローティングフィールドプレートFBとが重なる部分の幅が広いため、第1フローティングフィールドプレートFAと第2フローティングフィールドプレートとで形成される各コンデンサの容量値が、従来構造に比べて大きくなる。従って、各コンデンサにおける容量結合効果は高くなるので、第2絶縁膜LBの分極化が促進される。それにより、各第1フローティングフィールドプレートFAの間の下方でも空乏層が拡がり易くなるという効果が得られ、HV-MOSの高耐圧化に寄与できる。

## 【0086】

また、各コンデンサにおける容量結合効果は高くなることによって、各コンデンサが保

10

20

30

40

50

持する電位差のソースドレイン間でのばらつきが小さくなり、第2絶縁膜L Bの絶縁破壊が生じにくくなるという効果も得られる。

【0087】

また本実施の形態でも、本発明をMOSFETに適用した例を示したが、本発明の適用はそれに限定されるものではなく、例えばダイオードやIGBTなどにも広く適用することが可能である。

【0088】

<実施の形態6>

図27は、実施の形態6に係るHV-MOSの構成を示す図である。この図においては、図20に示したものと同様の要素には同一符号を付してあるので、それらの詳細な説明は省略する。

10

【0089】

図27のHV-MOSは、図20の構造から、第1フローティングフィールドプレートFAを無くしたものである。第1絶縁膜LAおよび第2絶縁膜LBの厚さをそれぞれa, bとし、第2フローティングフィールドプレートFBと第3フローティングフィールドプレートFCとの間の第2方向を距離をcとしたとき、 $a + b > c$ となるようになっている。つまり、図27の第2フローティングフィールドプレートFBおよび第3フローティングフィールドプレートFCは、それぞれ実施の形態1(図6)の第1フローティングフィールドプレートFAおよび第2フローティングフィールドプレートFBと同様に機能している。従ってHV-MOSは、実施の形態1と同様に、安定して高耐圧を維持することができる。

20

【0090】

また、ドレイン電極119は、第1絶縁膜LA上に延びる第1ドレイン電極部DAを有している。当該第1ドレイン電極部DAは、その一部が第2絶縁膜LBを介して第2フローティングフィールドプレートFB1の一部と重なるように、第1絶縁膜LA上を第1方向に延びている。さらに、第3ドレイン電極部DCにおける第1絶縁膜LA上方を第1方向に延びた部分の長さは、第1ドレイン電極部DAにおける第1絶縁膜LA上を第1方向に延びた部分の長さよりも長く、且つ、第2ドレイン電極部DBにおける第1絶縁膜LA上方を第1方向に延びた部分の長さよりも長い。即ち、第3ドレイン電極部DCは、第1ドレイン電極部DAおよび第2ドレイン電極部DBの上方を覆っている。

30

【0091】

図28は、図27のHV-MOSにおいて、ゲート電極116-ソース電極114間に短絡してHV-MOSを遮断状態にし、ドレイン電極119-ソース電極114間に高電圧を印加したときの当該HV-MOS内部の電界分布を示す図である。同図では、シリコン基板表面(Si表面)から、n領域117とp<sup>+</sup>領域200との間のpn接合深さにかけての電界分布を示している。特に実線は、シリコン基板表面の電界分布と、n<sup>-</sup>層110とp<sup>+</sup>領域200との間の第1pn接合深さの電界分布とを示している。実施の形態1と同様に、シリコン基板表面の電界ピークが低くなっていることが分かる。

30

【0092】

また、シリコン基板表面における最ドレイン側の電界ピークは、第2フローティングフィールドプレートFB2のドレイン側のエッジ下であり、第2フローティングフィールドプレートFB1のエッジ下にはピークは現れない。これは、通常のフィールドプレートとして機能する第1ドレイン電極部DAが、第2フローティングフィールドプレートFB1の一部と重なる位置まで延びているためである。また、第3ドレイン電極部DCが、第1ドレイン電極部DAおよび第2ドレイン電極部DBの上方を覆うように、第1絶縁膜LA上方に長く延びているので、シリコン基板表面におけるドレイン電極付近の電界集中はさらに緩和される。従って、降伏臨界電界点(ドレイン側のn領域117の第1pn接合深さの部分)の近傍の電界強度が低くなるので、HV-MOSの耐電圧値は高くなる。つまり本実施の形態によれば、実施の形態1よりもさらなる高耐圧化が可能となる。

40

50

## 【0093】

図29は、本実施の形態に実施の形態2を適用した変形例を示す図である。即ち、図27の構造と異なる点は、ドレイン電極119が、第2絶縁膜LB上に延びる第2ドレイン電極部DBを有していることである。図29に示すように、第2ドレイン電極部DBにおける第1絶縁膜LA上方を第1方向に延びた部分の長さは、第1ドレイン電極部DAにおける第1絶縁膜LA上を第1方向に延びた部分の長さよりも長い。つまり、第2ドレイン電極部DBは、第2絶縁膜LBを介して第1ドレイン電極部DAの上方を覆っている。図29に示しているように、当該第2ドレイン電極部DBは、図27のドレイン電極119と第2フローティングフィールドプレートFB1を接続したものであると言うこともできる。

10

## 【0094】

図30は、図29のHV-MOSにおいて、ゲート電極116-ソース電極114間を短絡して当該HV-MOSを遮断状態にし、ドレイン電極119-ソース電極114間に高電圧を印加したときの当該HV-MOS内部の電界分布を示す図である。図30でも図28と同様に、シリコン基板表面における最ドレイン側の電界ピークは、第2フローティングフィールドプレートFB2のドレイン側のエッジ下であり、第2フローティングフィールドプレートFB1のエッジ下にはピークは現れない。よって、降伏臨界電界点の近傍の電界強度が低くなるので、HV-MOSの耐電圧値は高くなる。つまりこの変形例によれば、実施の形態2よりもさらなる高耐圧化が可能となる。

## 【0095】

20

また本実施の形態でも、本発明をMOSFETに適用した例を示したが、本発明の適用はそれに限定されるものではなく、例えばダイオードやIGBTなどにも広く適用することが可能である。

## 【0096】

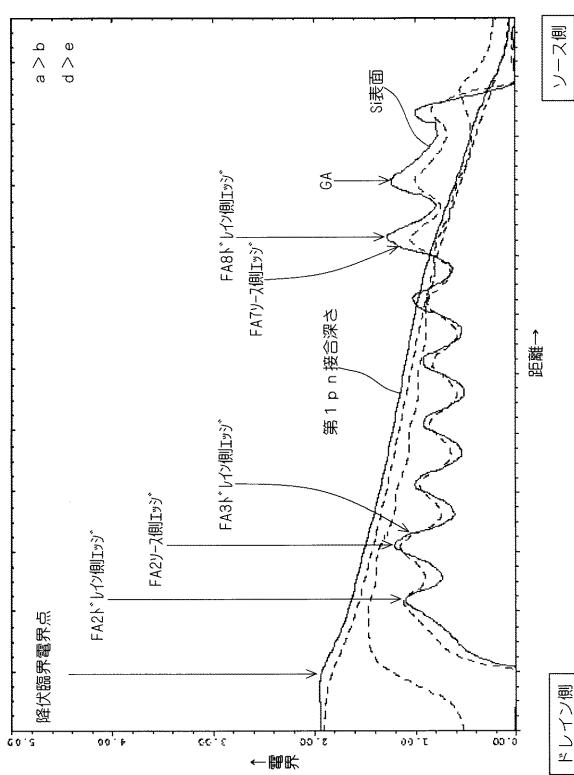

## &lt;実施の形態7&gt;

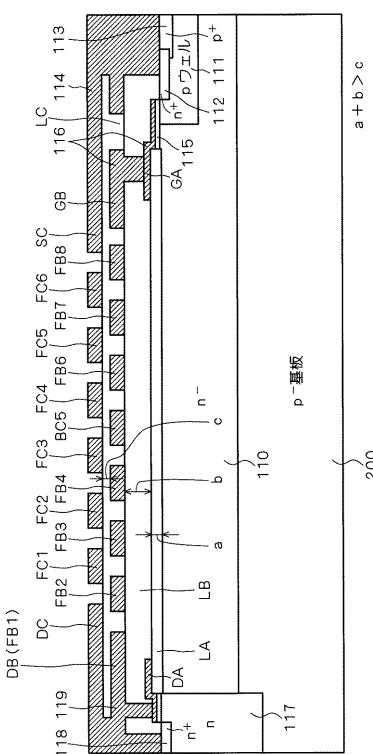

図31は、実施の形態7に係るHV-MOSの構成を示す図である。この図においては、図6および図14に示したものと同様の要素には同一符号を付してあるので、それらの詳細な説明は省略する。

## 【0097】

本実施の形態に係るHV-MOSにおいて、ドレイン電極119は第1絶縁膜LA上に延びる第1ドレイン電極部DA、第2絶縁膜LB上に延びる第2ドレイン電極部DBを有している。そして従来の構造よりも、第1ドレイン電極部DAおよび第2ドレイン電極部DBを長く延ばしている。図31に示しているように、第1ドレイン電極部DAにおける第1絶縁膜LA上方を第1方向に延びた部分の長さをdとすると、第2ドレイン電極部DBにおける第1絶縁膜LA上方を第1方向に延びた部分の長さは、長さdよりもさらに長さeだけ長い。このとき、 $d > e$ となるように長さdを充分大きくしている。また図31の例では、第1絶縁膜LAの厚さaと、第1フローティングフィールドプレートFAと第2フローティングフィールドプレートFBとの間の第2方向の距離bとの関係は、従来構造と同じ $a < b$ としている。図31に示しているように、当該第1ドレイン電極部DAは、図6のドレイン電極119を第1フローティングフィールドプレートFA1に接続したものであり、当該第2ドレイン電極部DBは、図6のドレイン電極119に第2フローティングフィールドプレートFB1, FB2を接続したものであると言うこともできる。

30

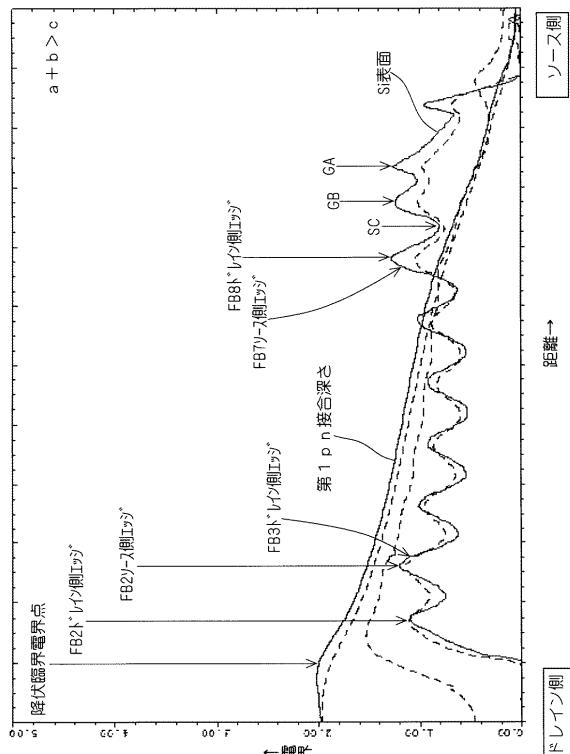

## 【0098】

40

図32は、図31のHV-MOSにおいて、ゲート電極116-ソース電極114間を短絡して当該HV-MOSを遮断状態にし、ドレイン電極119-ソース電極114間に高電圧を印加したときのHV-MOS内部の電界分布を示す図である。同図では、シリコン基板表面(Si表面)から、n領域117とp<sup>-</sup>領域200との間のpn接合深さにかけての電界分布を示している。特に実線は、シリコン基板表面の電界分布と、n<sup>-</sup>層110とp<sup>-</sup>領域200との間の第1pn接合深さの電界分布とを示している。シリコン基板表面における最ドレイン側の電界ピークは、第1フローティングフィールドプレートFA

50

2のドレイン側のエッジ下である。

【0099】

例えば、図7等と比較して分かるように、本実施の形態によれば、最ドレイン側の電界ピークが降伏臨界電界点（ドレイン側のn領域117の第1pn接合深さの部分）から遠ざかることになる。よって、降伏臨界電界点の近傍の電界強度が低くなり、HV-MOSの耐電圧値は高くなる。

【0100】

なお、図31では、厚さaと距離bとの関係をa < bとしたが、実施の形態1を適用して図33のようにa > bとしてもよい。図34は、図33のHV-MOSにおいて、ゲート電極116-ソース電極114間に短絡して該HV-MOSを遮断状態にし、ドレイン電極119-ソース電極114間に高電圧を印加したときの該HV-MOS内部の電界分布を示す図である。同図では、シリコン基板表面（Si表面）から、n領域117とp<sup>-</sup>領域200との間のpn接合深さにかけての電界分布を示している。特に実線は、シリコン基板表面の電界分布と、n<sup>-</sup>層110とp<sup>-</sup>領域200との間の第1pn接合深さの電界分布とを示している。全体的に、図32よりもシリコン基板表面の電界ピークが低くなつて電界集中が緩和されていることが分かる。従って、実施の形態1を適用すれば、更なる高耐圧化が可能となる。

【0101】

また本発明の適用はMOSFETに限定されるものではなく、例えばダイオードやIGBTなどにも広く適用することが可能である。図35は、本実施の形態を高耐圧ダイオード（HV-ダイオード）に適用した例を示す図であり、図5におけるHV-ダイオード14の拡大図である。図5および図13に示したものと同様の要素には同符号を付してあるので、ここでの詳細な説明は省略する。なお、この図においても、以降の説明の便宜を図るために、図5とは左右を逆にして描いている。図35のHV-ダイオードは、従来のHV-ダイオード（実施の形態1で示した図13においてa < bのもの）の構造に対し、第1カソード電極部CAおよび第2カソード電極部CBを、図31の第1ドレイン電極部DAおよび第2ドレイン電極部DBと同様に長く延ばしたものである。

【0102】

図36は、図35のHV-ダイオードにおいて、カソード電極142-アノード電極145間に逆方向電圧を印加したときの、当該HV-ダイオード内の電界分布を示す図である。同図では、シリコン基板表面（Si表面）から、n層121とp<sup>-</sup>領域200との間のpn接合深さにかけての電界分布を示している。特に実線は、シリコン基板表面の電界分布と、n<sup>-</sup>層143とp<sup>-</sup>領域200との間の第1pn接合深さの電界分布とを示している。また、この図は、図3のC-C断面（即ち、高電位島のコーナー部）における電界分布を示している。シリコン基板表面における最カソード側の電界ピークは、第1フローティングフィールドプレートFA2のカソード側のエッジ下であり、降伏臨界電界点（カソード側のn層121の第1pn接合深さの部分）の近傍の電界強度が低くなる。

【0103】

一方、図37は、従来のHV-ダイオード（実施の形態1で示した図13においてa < bのもの）における、図36と同様の電界分布を示す図である。この図も、図3のC-C断面（高電位島のコーナー部）における電界分布を示している。シリコン基板表面における最カソード側の電界ピークは、図35には無かった第2フローティングフィールドプレートFB1のドレイン側のエッジ下である。

【0104】

図36と図37と比較して分かるように、本実施の形態によれば、最カソード側の電界ピークが降伏臨界電界点から遠ざかることになる。よって、降伏臨界電界点の近傍の電界強度は、図35のHV-ダイオードの場合よりも高くなる。従って、本実施の形態を適用した図35のHV-ダイオードの方が、高い耐電圧を得ることができる。

【0105】

一般に高電位島のコーナー部ではその形状の影響で、特にHV-ダイオードのカソード

10

20

30

40

50

側（H V - M O S の場合はドレイン側）のシリコン基板表面における電界ピークが高くなる傾向にある。例えば図37でも、シリコン基板表面での最カソード側の電界ピークが、最アノード側の電界ピークよりも大きくなっていることが観察される。そのため従来は、コーナー部に形成されたH V - ダイオードやH V - M O S における降伏臨界電界点の近傍の電界強度が高くなることに起因する耐圧の低下が懸念されていた。本実施の形態によれば、H V - ダイオードやH V - M O S の降伏臨界電界点の近傍の電界強度を低く抑えることができるので、コーナー部のH V - ダイオードやH V - M O S への適用は特に有効である。

#### 【0106】

＜実施の形態8＞

10

実施の形態8では、実施の形態6に実施の形態7を適用した例を示す。図38は、本実施の形態に係るH V - M O S の構成を示す図である。この図においては、図6および図29に示したものと同様の要素には同一符号を付してあるので、それらの詳細な説明は省略する。

#### 【0107】

本実施の形態に係るH V - M O S は、図29の構造に対して、第1ドレイン電極部D A、第2ドレイン電極部D B、第3ドレイン電極部D Cのそれぞれを長く延ばしている。図38に示すように、第1ドレイン電極部D Aにおける第1絶縁膜L A上を第1方向に延びた部分の長さをd とすると、第2ドレイン電極部D Bにおける第1絶縁膜L A上方を第1方向に延びた部分の長さは、長さd よりもさらに長さe だけ長い。そして、第3ドレイン電極部D Cにおける第1絶縁膜L A上方を第1方向に延びた部分の長さは、長さd + e よりもさらに長さf だけ長い。このときd > e 且つd > f となるように、長さd を充分大きくしている。

20

#### 【0108】

図38に示しているように、当該第2ドレイン電極部D Bは、図29のドレイン電極119を第2フローティングフィールドプレートF B 1, F B 2に接続したものであり、また当該第3ドレイン電極部D Cは、図29のドレイン電極119に第3フローティングフィールドプレートF C 1を接続したものであると言うこともできる。

#### 【0109】

図39は、図38のH V - M O S において、ゲート電極116 - ソース電極114間に短絡してH V - M O S を遮断状態にし、ドレイン電極119 - ソース電極114間に高電圧を印加したときのH V - M O S 内部の電界分布を示す図である。同図では、シリコン基板表面（Si表面）から、n領域117とp領域200との間のpn接合深さにかけての電界分布を示している。特に実線は、シリコン基板表面の電界分布と、n層110とp層200との間の第1pn接合深さの電界分布とを示している。シリコン基板表面における最ドレイン側の電界ピークは、第2フローティングフィールドプレートF B 3のドレイン側のエッジ下である。図30と比較して分かるように、本実施の形態でも実施の形態7と同様に、最ドレイン側の電界ピークが降伏臨界電界点（ドレイン側のn領域117の第1pn接合深さの部分）から遠ざかることになる。よって、降伏臨界電界点の近傍の電界強度が低くなり、H V - M O S の耐電圧値は高くなる。

30

#### 【0110】

上述したように、高電位島のコーナー部では、特にH V - ダイオードのカソード側（H V - M O S の場合はドレイン側）のシリコン基板表面における電界ピークが高くなる傾向にあり、それによる耐圧低下が懸念されていた。本実施の形態によれば、H V - ダイオードやH V - M O S の降伏臨界電界点の近傍の電界強度を低く抑えることができるので、高電位島のコーナー部のH V - ダイオードへの適用は特に有効である。

40

#### 【0111】

＜変形例＞

以上の各実施の形態では、本発明を、R E S U R F 構造を適用した横型のデバイスに適用したが、本発明は縦型のデバイスに対しても適用可能である。ここでは、縦型のデバイ

50

スに上記実施の形態1を適用した変形例を示す。

【0112】

図40は、縦型のHV-MOSのチップ上面図であり、図41はそのチップ外周部（エッジターミネーション部）のD-D線に沿った拡大断面図である。図40と図41とで、同一の要素には同一符号を付してある。また、両図において図6と同様の機能を有する要素にも、それらと同一符号を付してある。

【0113】

図40に示すように、縦型のHV-MOSでは、チップ上面にソース電極114およびゲート電極116が配設され、裏面側にドレイン電極（不図示）が配設される。チップ上面の外周部には、チャネルストップ層211（図41参照）が形成され、その上に電極212（「チャネルストップ電極」と称する）。

【0114】

縦型のHV-MOSでは、実施の形態1～8で説明した縦型のHV-MOSとは異なり第1半導体領域であるn-層210は、n<sup>+</sup>基板220上に形成される。即ち、n-層210の下にはp<sup>+</sup>領域（第4半導体領域）は形成されない。n<sup>+</sup>基板211はHV-MOSのドレインとして機能し、ドレイン電極221がn<sup>+</sup>基板211の裏面側に形成される。n-層210内には、第2半導体領域としてのpウェル111が形成され、その内部にp<sup>+</sup>領域113が形成される。pウェル111の上方には、第1絶縁膜LAを介してゲート電極116が形成され、pウェル111およびp<sup>+</sup>領域113の上部にはソース電極114が形成される。そして、n-層210のチップ外周部に第3半導体領域としてのチャネルストップ層211が形成され、その上にチャネルストップ電極212が形成される。pウェル111とチャネルストップ層211は、n-層210を挟むように形成されている。

【0115】

ゲート電極116の配線部とチャネルストップ電極212との間のn-層210の上方には、第1絶縁膜LAを介して複数の第1フローティングフィールドプレートFAが形成される。さらに、第1フローティングフィールドプレートFAの上には第2絶縁膜LBが形成され、第2絶縁膜LBの上には複数の第2フローティングフィールドプレートFBが形成される。図41に示すように、第1フローティングフィールドプレートFAおよび第2フローティングフィールドプレートFBはそれぞれ、第3半導体領域（チャネルストップ層211）から第2半導体領域（pウェル111）に向かう第1方向に並んで配設される（図40では、第1フローティングフィールドプレートFA、第2フローティングフィールドプレートFBを簡略化して描いている）。

【0116】

本変形例では、実施の形態1と同様に、第1絶縁膜LAの厚さをa、第1フローティングフィールドプレートFAと第2フローティングフィールドプレートFBとの間の第2方向（第1絶縁膜LAおよび第2絶縁膜LBの厚さ方向）の距離をbとしたとき、a>bとなるように、従来の構造よりも第1絶縁膜LAを厚く、第2絶縁膜LBを薄くしている。

【0117】

このように、縦型のHV-MOSに実施の形態1を適用することによって、当該HV-MOS遮断時における、第1絶縁膜LAとn-層210との界面における電界集中は緩和される。従って、当該HV-MOSはチップ外周部において、安定して高耐圧を維持することができ、縦型のHV-MOS高耐圧化を図ることができる。

【0118】

なお、ここでは本発明を縦型のHV-MOSに適用した例を示したが、その他、IGBTやダイオードなど、縦型パワーデバイス全般に適用可能であり、同様の効果を得ることができる。また、本変形例では、実施の形態1を適用したケースのみを示したが、他の実施の形態を適用してもよいことは言うまでもない。

【図面の簡単な説明】

【0119】

【図1】パワーデバイスおよびパワーデバイス駆動装置を示す図である。

10

20

30

40

50

【図2】パワーデバイス駆動装置における高圧側駆動部の主要部の回路図である。

【図3】パワーデバイス駆動装置における高圧側駆動部のレイアウトを示す概略平面図である。

【図4】パワーデバイス駆動装置における高圧側駆動部の主要部の概略断面図である。

【図5】パワーデバイス駆動装置における高圧側駆動部の主要部の概略断面図である。

【図6】実施の形態1に係るH V - M O Sの構成を示す図である。

【図7】実施の形態1に係るH V - M O Sの遮断状態におけるドレイン - ソース間の電界分布を示す図である。

【図8】従来のH V - M O Sの遮断状態におけるドレイン - ソース間の電界分布を示す図である。

【図9】実施の形態1の効果を説明するための図である。

【図10】実施の形態1に係るH V - M O Sの遮断状態におけるドレイン - ソース間の電位分布および電流分布を示す図である。

【図11】従来のH V - M O Sの遮断状態におけるドレイン - ソース間の電位分布および電流分布を示す図である。

【図12】実施の形態1の効果を説明するための図である。

【図13】実施の形態1に係る発明を高耐圧ダイーオードに適用した例を示す図である。

【図14】実施の形態2に係るH V - M O Sの構成を示す図である。

【図15】実施の形態2に係るH V - M O Sの遮断状態におけるドレイン - ソース間の電界分布を示す図である。

【図16】実施の形態2の効果を説明するための図である。

【図17】実施の形態3に係るH V - M O Sの構成を示す図である。

【図18】実施の形態3に係るH V - M O Sの遮断状態におけるドレイン - ソース間の電界分布を示す図である。

【図19】実施の形態3に係るH V - M O Sの遮断状態におけるドレイン - ソース間の電位分布および電流分布を示す図である。

【図20】実施の形態4に係るH V - M O Sの構成を示す図である。

【図21】実施の形態4に係るH V - M O Sの遮断状態におけるドレイン - ソース間の電界分布を示す図である。

【図22】実施の形態4に係るH V - M O Sの遮断状態におけるドレイン - ソース間の電位分布および電流分布を示す図である。

【図23】実施の形態4の変形例を示す図である。

【図24】実施の形態4の変形例であるH V - M O Sの遮断状態におけるドレイン - ソース間の電界分布を示す図である。

【図25】実施の形態4の変形例であるH V - M O Sの遮断状態におけるドレイン - ソース間の電位分布および電流分布を示す図である。

【図26】実施の形態5に係るH V - M O Sの構成を示す図である。

【図27】実施の形態6に係るH V - M O Sの構成を示す図である。

【図28】実施の形態6に係るH V - M O Sの遮断状態におけるドレイン - ソース間の電界分布を示す図である。

【図29】実施の形態6の変形例を示す図である。

【図30】実施の形態6の変形例であるH V - M O Sの遮断状態におけるドレイン - ソース間の電界分布を示す図である。

【図31】実施の形態7に係るH V - M O Sの構成を示す図である。

【図32】実施の形態7に係るH V - M O Sの遮断状態におけるドレイン - ソース間の電界分布を示す図である。

【図33】実施の形態7の変形例を示す図である。

【図34】実施の形態7の変形例であるH V - M O Sの遮断状態におけるドレイン - ソース間の電界分布を示す図である。

【図35】実施の形態7に係る発明を高耐圧ダイーオードに適用した例を示す図である。

10

20

30

40

50

【図36】実施の形態7に係る高耐圧ダイオードの遮断状態におけるドレイン-ソース間の電界分布を示す図である。

【図37】実施の形態7に係る高耐圧ダイオードの遮断状態におけるドレイン-ソース間の電界分布を示す図である。

【図38】実施の形態8に係るH V - M O Sの構成を示す図である。

【図39】実施の形態8に係るH V - M O Sの遮断状態におけるドレイン-ソース間の電界分布を示す図である。

【図40】本発明の実施の形態の変形例を説明するための図である。

【図41】本発明の実施の形態の変形例を説明するための図である。

【符号の説明】

10

【0120】

110 n<sup>-</sup>層、111 pウェル、112 n<sup>+</sup>ソース領域、113 p<sup>+</sup>領域、114 ソース電極、115 ゲート絶縁膜、116 ゲート電極、117 n領域、118 n<sup>+</sup>ドレイン領域、119 ドレイン電極、121 n層、141 n<sup>+</sup>カソード領域、142 カソード電極、143 n<sup>-</sup>層、144 p<sup>+</sup>アノード領域、145 アノード電極、200 p<sup>-</sup>領域、201 p<sup>+</sup>分離、212 チャネルストップ電極、211 チャネルストップ層、210 n<sup>-</sup>層、LA 第1絶縁膜、LB 第2絶縁膜、LC 第3絶縁膜、FA 第1フローティングフィールドプレート、FB 第2フローティングフィールドプレート、FC 第3フローティングフィールドプレート、DA 第1ドレイン電極部、DB 第2ドレイン電極部、DC 第3ドレイン電極部、CA 第1カソード電極部、CB 第2カソード電極部。

20

【図1】

100:パワーデバイス駆動装置

【図2】

11:高耐圧MOS

12:高圧側駆動信号出力用CMOS

13:レベルシフト抵抗

【図3】

【図4】

【 义 7 】

【 四 8 】

【図9】

【図10】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

【図15】

【図16】

----- a<b

—— a>b

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

### 【図23】

【 図 2 4 】

【図25】

【 図 2 6 】

【図27】

【図28】

【図29】

【図30】

【図31】

【 図 3 2 】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

【図39】

【図40】

### 【図4-1】

---

フロントページの続き

(56)参考文献 特開昭56-169369(JP,A)

特開2002-353444(JP,A)

特開2000-022175(JP,A)

特開平10-163482(JP,A)

特開2001-196578(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 29/78

H01L 29/06

H01L 29/739

H01L 29/861