## (12)发明专利

(10)授权公告号 CN 105577153 B

(45)授权公告日 2020.05.26

(21)申请号 201510660762.9

H03K 17/567(2006.01)

(22)申请日 2015.10.14

## (56)对比文件

(65)同一申请的已公布的文献号

US 2008212247 A1, 2008.09.04,

申请公布号 CN 105577153 A

CN 103166615 A, 2013.06.19,

(43)申请公布日 2016.05.11

US 2006114633 A1, 2006.06.01,

## (30)优先权数据

CN 102377419 A, 2012.03.14,

2014-222433 2014.10.31 JP

CN 102779820 A, 2012.11.14,

(73)专利权人 富士电机株式会社

JP 2012253202 A, 2012.12.20,

地址 日本神奈川县川崎市

CN 103703566 A, 2014.04.02,

(72)发明人 内藤达也 大月正人

CN 1242604 A, 2000.01.26,

(74)专利代理机构 北京铭硕知识产权代理有限公司 11286

CN 202103639 U, 2012.01.04,

代理人 金玉兰 王颖

US 2008084642 A1, 2008.04.10,

(51)Int.Cl.

CN 102684661 A, 2012.09.19,

H03K 17/12(2006.01)

US 2011242866 A1, 2011.10.06,

审查员 杨苏倩

权利要求书2页 说明书8页 附图7页

## (54)发明名称

半导体装置

## (57)摘要

提供半导体装置，其保护具有同一芯片上形成且并联的IGBT与MOSFET的功率半导体元件，使其免于随检出过电流时断开控制的异常高压损害。是将IGBT(11)与SJMOSFET(12)并联时使其栅极端子独立而分别控制IGBT(11)和SJMOSFET(12)。在此接通控制IGBT(11)和SJMOSFET(12)时外部电路发生短路等而被施加高电压且大电流流过时，运算放大器(24)以检出IGBT(11)的过电流而控制栅极信号以限制IGBT(11)中流动的电流。然后运算放大器(24)根据被恒定电流源(25)的放电降低的电容器(26)的基准电压，限制IGBT(11)流动的电流，软关断IGBT(11)。

1.一种半导体装置,其特征在于,具备:

IGBT;

MOSFET,其与所述IGBT在同一芯片上形成,耐压比所述IGBT低,漏极和源极分别与所述IGBT的集电极和发射极连接;以及

控制IC,其将第一控制信号输出到作为第一栅极的所述IGBT的栅极,将第二控制信号输出到作为第二栅极的所述MOSFET的栅极,并且所述控制IC具有过电流检测电路和强制关断电路,所述过电流检测电路检测所述IGBT的过电流,所述强制关断电路强制地使所述第一控制信号成为断开信号,

在所述控制IC中,在通过所述第一控制信号和所述第二控制信号对所述IGBT和所述MOSFET进行导通控制期间,所述过电流检测电路检测出了过电流时,所述强制关断电路强制地使所述第一控制信号成为断开信号,

所述强制关断电路为相对于所述第一控制信号使所述IGBT软关断的软关断电路,

所述软关断电路具有:门闩电路,其在所述过电流检测电路检测出所述IGBT的过电流时保持过电流检测状态;斜坡电压生成电路,其在所述门闩电路保持所述过电流检测状态之后输出电压值连续变化的斜坡电压;以及软关断控制电路,其跟随所述斜坡电压使所述第一控制信号的值向断开的方向变化。

2.根据权利要求1所述的半导体装置,其特征在于,所述控制IC具有检测所述MOSFET的过电流的第二过电流检测电路、以及强制地使所述第二控制信号成为断开信号的第二强制关断电路,在所述强制关断电路强制地使所述第一控制信号成为断开信号之后,所述第二过电流检测电路检测出了所述MOSFET的过电流时,所述第二强制关断电路强制地使所述第二控制信号成为断开信号。

3.根据权利要求1所述的半导体装置,其特征在于,所述强制关断电路具有延迟电路,所述延迟电路用于在经过了保证所述IGBT的破坏耐受量的时间内的预定时间之后,使所述第一控制信号成为断开信号。

4.根据权利要求3所述的半导体装置,其特征在于,所述控制IC具有检测所述MOSFET的过电流的第二过电流检测电路、以及强制地使所述第二控制信号成为断开信号的第二强制关断电路,在所述强制关断电路强制地使所述第一控制信号成为断开信号之后,所述第二过电流检测电路检测出了所述MOSFET的过电流时,所述第二强制关断电路强制地使所述第二控制信号成为断开信号。

5.根据权利要求1至4中任一项所述的半导体装置,其特征在于,所述MOSFET是超接合型MOSFET。

6.一种半导体装置,其特征在于,具备:

IGBT;

MOSFET,其与所述IGBT在同一芯片上形成,耐压比所述IGBT低,漏极和源极分别与所述IGBT的集电极和发射极连接;以及

控制IC,其将第一控制信号输出到作为第一栅极的所述IGBT的栅极,将第二控制信号输出到作为第二栅极的所述MOSFET的栅极,并且所述控制IC具有过电流检测电路和强制关断电路,所述过电流检测电路检测所述IGBT的过电流,所述强制关断电路强制地使所述第一控制信号成为断开信号,

在所述控制IC中，在通过所述第一控制信号和所述第二控制信号对所述IGBT和所述MOSFET进行导通控制期间，所述过电流检测电路检测出了过电流时，所述强制关断电路强制地使所述第一控制信号成为断开信号，

所述控制IC具有：检测所述IGBT的集电极与发射极之间的过电压的过电压检测电路、检测所述MOSFET的过电流的第二过电流检测电路、以及强制地使所述第二控制信号成为断开信号的第二强制关断电路，在所述强制关断电路强制地使所述第一控制信号成为断开信号之后，所述过电压检测电路检测出了过电压，并且所述第二过电流检测电路检测出了所述MOSFET的过电流时，所述第二强制关断电路强制地使所述第二控制信号成为断开信号。

7. 根据权利要求6所述的半导体装置，其特征在于，所述MOSFET是超接合型MOSFET。

## 半导体装置

### 技术领域

[0001] 本发明涉及半导体装置,特别是涉及具备IGBT(Insulated Gate Bipolar Transistor,绝缘栅双极型晶体管)、MOSFET(Metal Oxide Semiconductor Field Effect Transistor,金属氧化物半导体场效应晶体管)和控制IC(Integrated Circuit,集成电路)的半导体装置。

### 背景技术

[0002] 在电源装置、电动机控制等的逆变电路中,作为功率半导体元件,通常使用IGBT或MOSFET。IGBT具有在高耐压和大电流的区域通态电阻小的特性,另一方面,MOSFET具有在中耐压/低耐压和小电流的区域通态电阻小的特性。因此,已知有如下半导体装置,该半导体装置利用IGBT和MOSFET的特性,具有在从低耐压至高耐压以及从小电流至大电流的范围内减小通态电阻的特性(例如,参照专利文献1、专利文献2)。

[0003] 使用了由功率半导体元件与控制IC集成在同一封装件所构成的半导体装置作为IPM(Intelligent Power Module,智能功率模块),控制IC内置有驱动该功率半导体元件的驱动电路和保护电路。

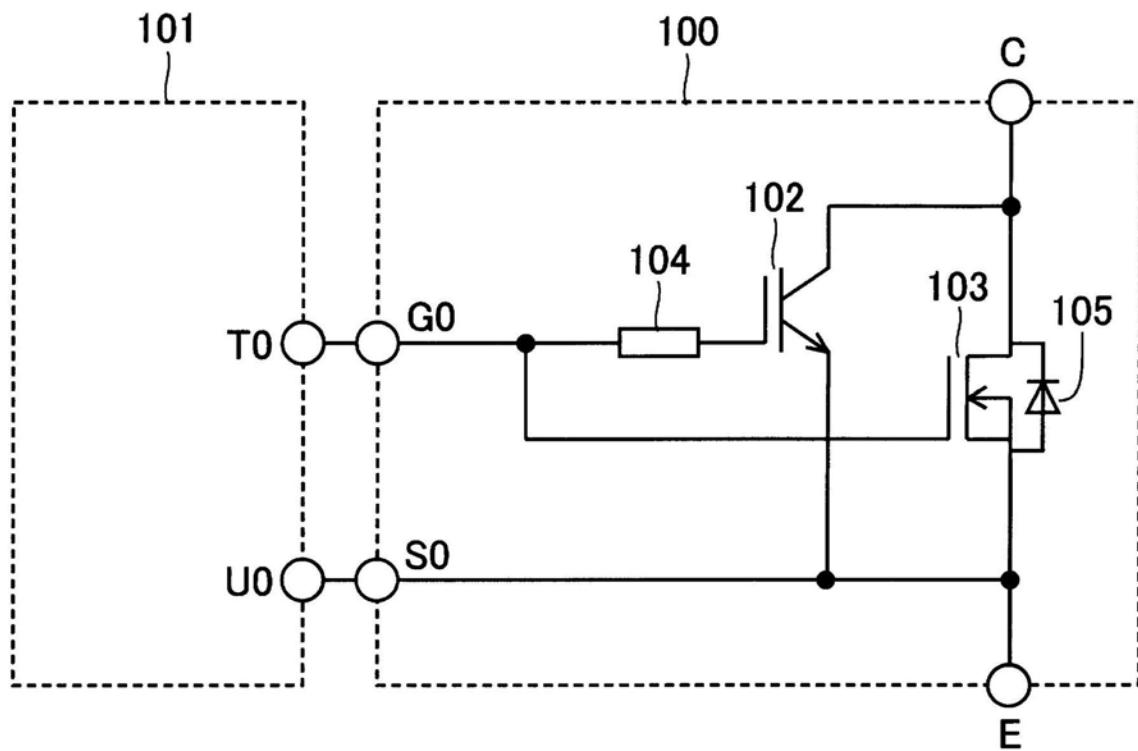

[0004] 图7是示出以往的具备IGBT和MOSFET的半导体装置的一个示例的电路图。

[0005] 该半导体装置具备功率半导体元件100和控制IC 101。对功率半导体元件100而言,IGBT 102与MOSFET 103并联连接。即,IGBT 102的发射极和MOSFET 103的源极与功率半导体元件100的端子E和端子S0连接,IGBT 102的集电极和MOSFET 103的漏极与功率半导体元件100的端子C连接。另外,IGBT 102的栅极通过电阻104与功率半导体元件100的端子G0连接,MOSFET 103的栅极直接与功率半导体元件100的端子G0连接。需要说明的是,反并联连接到MOSFET 103的二极管105是形成于MOSFET 103的体二极管,并用作使来自功率半导体元件100的端子E的电流回流的续流二极管。功率半导体元件100的端子S0和端子G0分别与控制IC101的端子U0和端子T0连接。

[0006] 通过使IGBT 102与MOSFET 103并联连接,功率半导体元件100利用MOSFET 103的特性,减小在低电流区域的通态电阻,由此能够减小稳态损耗。另一方面,在大电流区域,成为IGBT 102的特性,能够防止元件损坏。

[0007] 而且,将高阻值的电阻104连接到IGBT 102的栅极,并且,当功率半导体元件100接通时,以首先接通MOSFET 103,然后接通IGBT 102的方式来降低反馈电容从而减小传导损耗。

[0008] 另外,虽然未特别地图示,但是控制IC 101具备过电流保护电路。该过电流保护电路例如在端子U0监测流经IGBT 102的发射极的电流,当流经发射极的电流超过预定的阈值时,强制降低端子T0的电位从而使IGBT 102和MOSFET 103断开。

[0009] 对如上构成的半导体装置而言,例如,准备结构相同的另外的半导体装置,并且串联连接各个功率半导体元件从而作为图腾柱电路,由此能够构成半桥逆变电路。在这样的逆变电路中,通过对高侧桥臂或低侧桥臂的功率半导体元件进行接通或断开控制,例如能

够将直流电压转换为交流电压。

- [0010] 现有技术文献

- [0011] 专利文献

- [0012] 专利文献1:日本特开平4-354156号公报(图2、图5)

- [0013] 专利文献2:日本特开2014-130909号公报(图5)

## 发明内容

- [0014] 技术问题

[0015] 例如,在用于低侧桥臂的半导体装置中,在对功率半导体元件进行接通控制的期间,高侧桥臂的半导体装置发生了短路事故的情况下,控制IC检测到功率半导体元件的过电流并断开功率半导体元件。由此,对功率半导体元件而言,存在因集电极电流的急剧的下降导致集电极电压上升,IGBT和MOSFET达到它们的耐压的情况。另外,当检测出过电流时,IGBT和MOSFET基本同时断开,因此,在被施加高电压的状态下因大电流流动元件被破坏为止的短路保证时间受到短路保证时间短的IGBT的特性制约,成为短路耐受量低的半导体装置。

[0016] 本发明是为了解决这种问题而完成的,其目的在于,提供一种能够保护功率半导体元件免于随着检测到过电流时的断开控制的异常高压损害的半导体装置。

- [0017] 技术方案

[0018] 在本发明中为了解决上述课题,提供一种半导体装置,半导体装置形成为使在同一芯片上形成的IGBT和MOSFET并联连接而构成,并使它们的栅极端子分别独立地构成。该半导体装置具备:IGBT;MOSFET,耐压比该IGBT低,漏极和源极分别连接到IGBT的集电极和发射极;以及控制IC,其将第一控制信号发送到作为第一栅极的IGBT的栅极,将第二控制信号发送到作为第二栅极的MOSFET的栅极,并且控制IC具有过电流检测电路和强制关断电路,上述电流检测电路检测IGBT的过电流,上述强制关断电路强制地使第一控制信号成为断开信号。当在通过上述第一控制信号和上述第二控制信号对上述IGBT和上述MOSFET进行接通控制期间,上述过电流检测电路检测出了过电流时,该控制IC的强制关断电路强制地使第一控制信号成为断开信号。

- [0019] 有益效果

[0020] 上述构成的半导体装置具有以下优点:对并联连接的IGBT和MOSFET的栅极进行独立地控制,在检测IGBT的过电流时首先断开IGBT,由此能够兼顾高通道密度化和短路耐受量提高。

## 附图说明

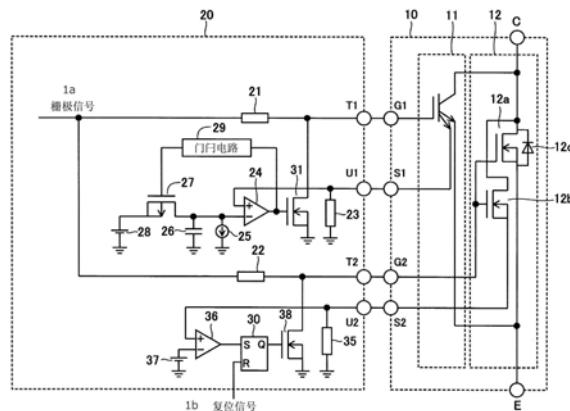

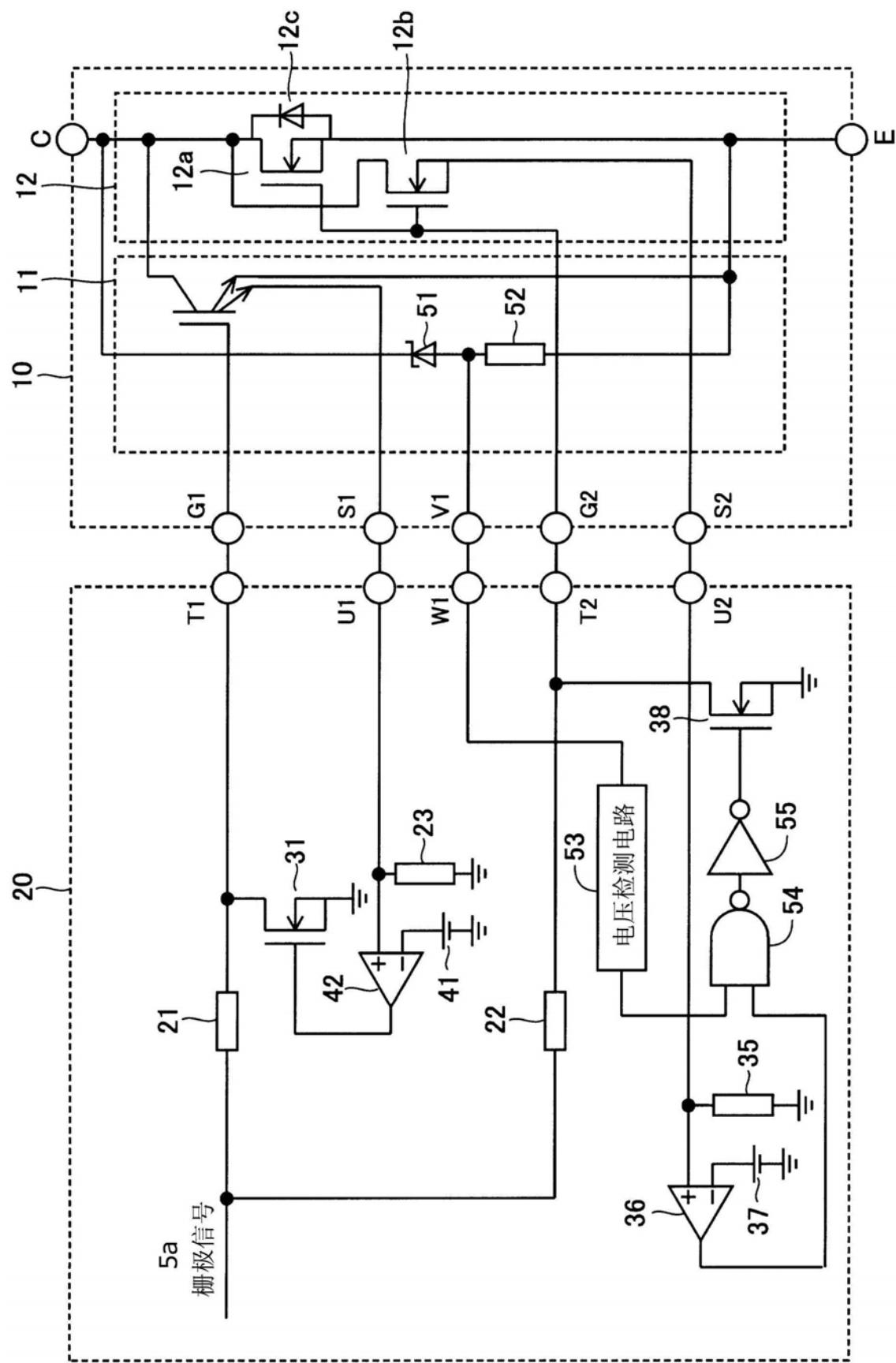

- [0021] 图1是示出第一实施方式的半导体装置的图。

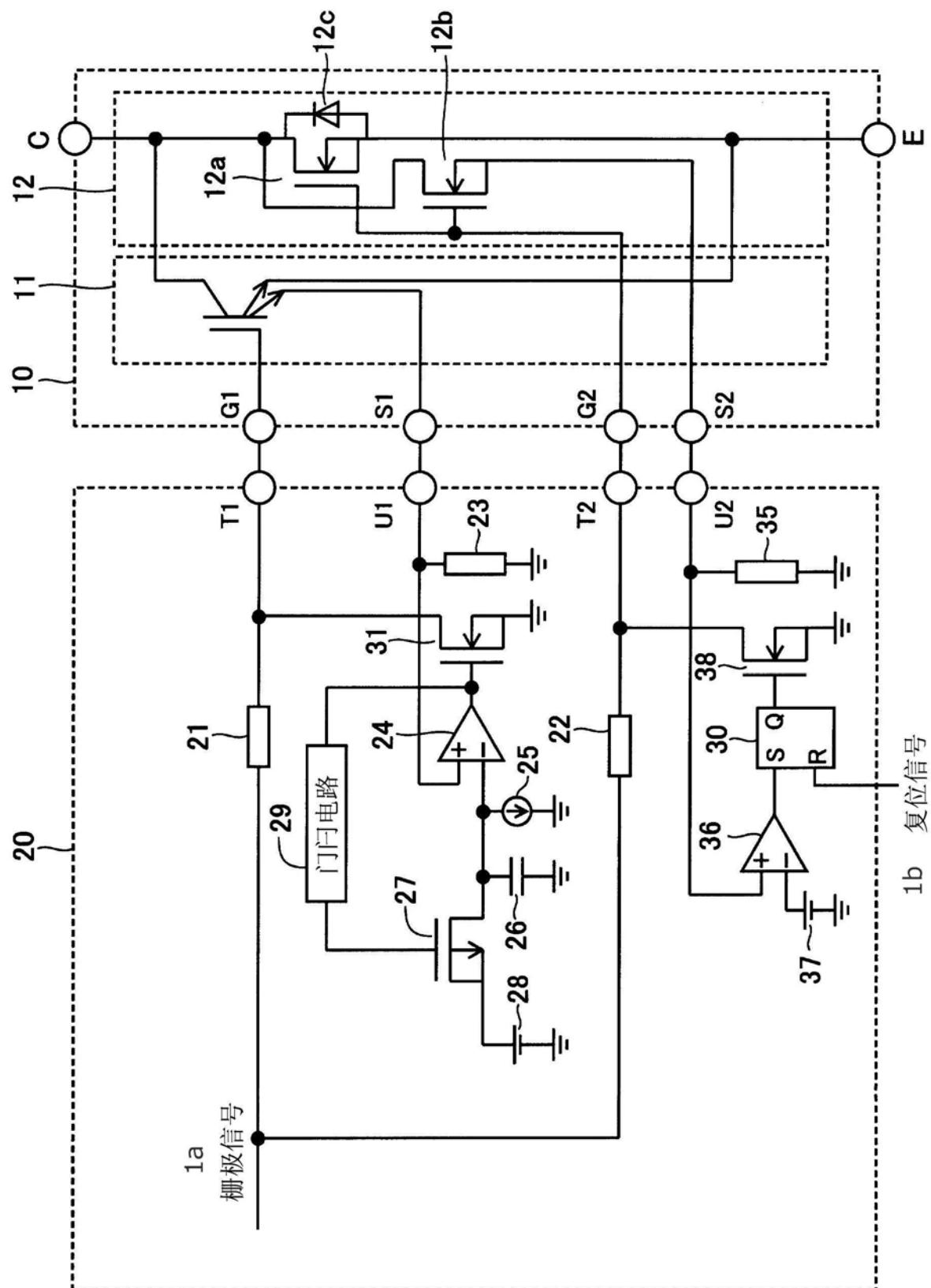

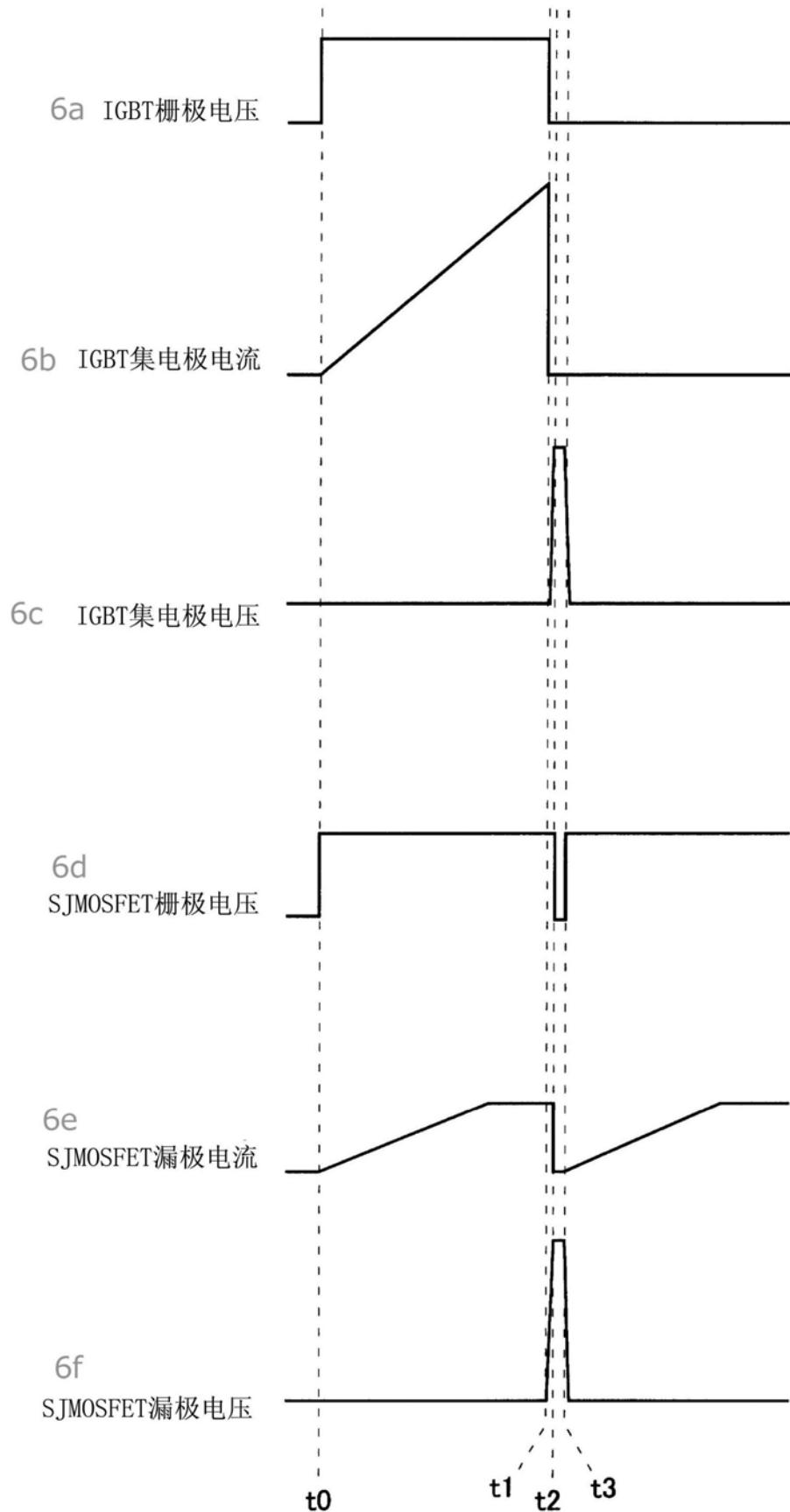

- [0022] 图2是示出第一实施方式的半导体装置的主要部分波形的时序图。

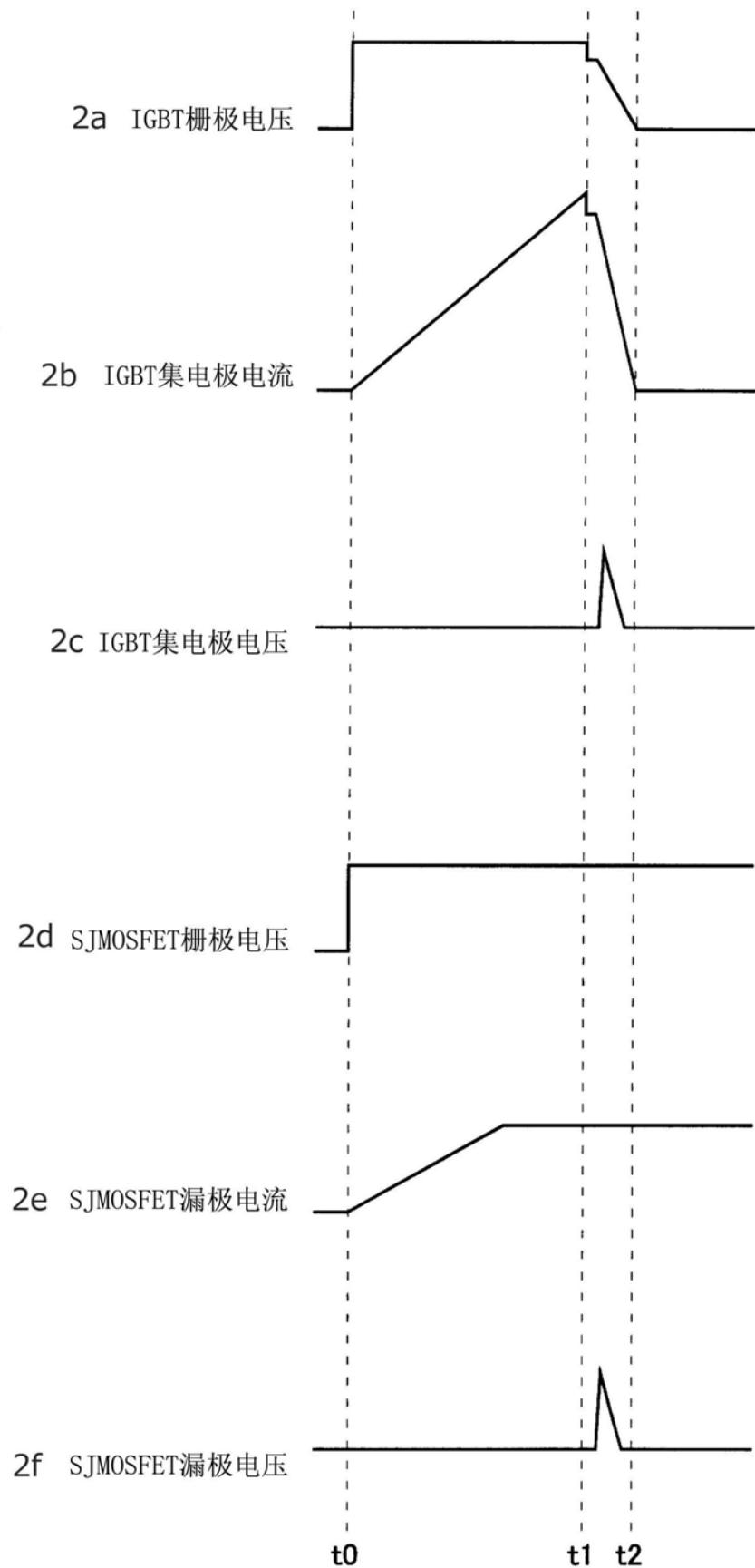

- [0023] 图3是示出第二实施方式的半导体装置的图。

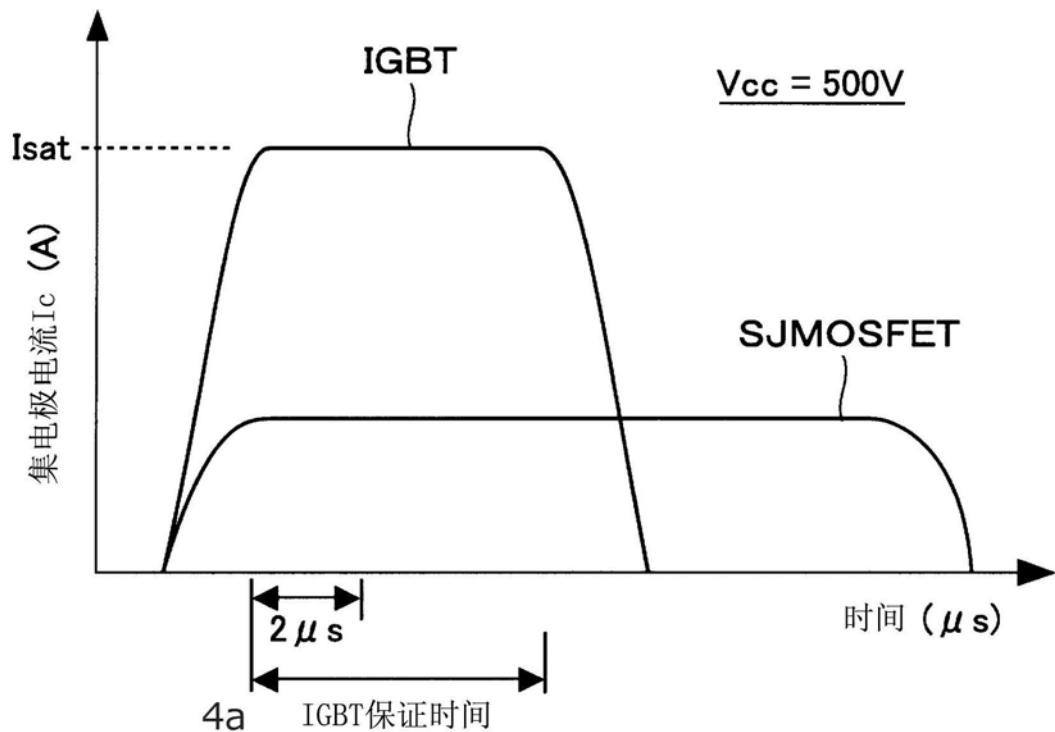

- [0024] 图4是示出第二实施方式的半导体装置的短路耐受量的图。

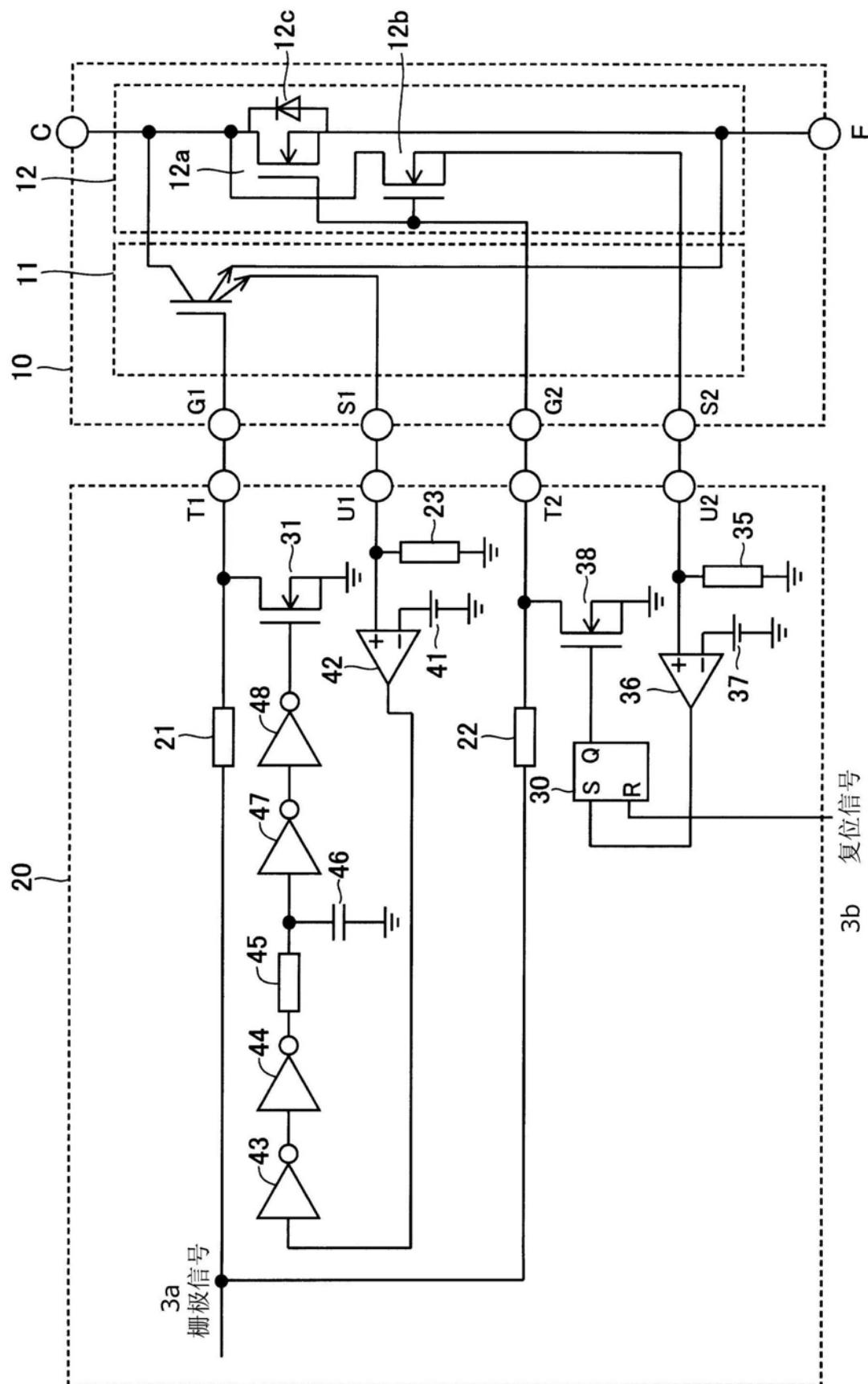

- [0025] 图5是示出第三实施方式的半导体装置的图。

- [0026] 图6是示出第三实施方式的半导体装置的主要部分波形的时序图。

- [0027] 图7是示出以往的具备IGBT和MOSFET的半导体装置的一个示例的电路图。

- [0028] 符号说明

- [0029] 10 功率半导体元件

- [0030] 11 IGBT

- [0031] 12 SJMOSFET

- [0032] 20 控制IC

- [0033] 21、22、23 电阻

- [0034] 24 运算放大器

- [0035] 25 恒定电流源

- [0036] 26 电容器

- [0037] 27 晶体管

- [0038] 28 电压源

- [0039] 29 门闩电路

- [0040] 30 RS触发器

- [0041] 31 晶体管

- [0042] 35 电阻

- [0043] 36 比较器

- [0044] 37 基准电压源

- [0045] 38 晶体管

- [0046] 41 基准电压源

- [0047] 42 比较器

- [0048] 43、44 逆变电路

- [0049] 45 电阻

- [0050] 46 电容器

- [0051] 47、48 逆变电路

- [0052] 51 齐纳二极管

- [0053] 52 电阻

- [0054] 53 电压检测电路

- [0055] 54 NAND电路

- [0056] 55 逆变电路

### 具体实施方式

[0057] 以下,参照附图对本发明的实施方式进行详细说明。需要说明的是,在各实施方式中,作为MOSFET,采用了与现有的MOSFET相比能够进一步降低传导损耗和开关损耗的超接合型MOSFET(Super Junction MOSFET:SJMOSFET)的结构进行说明,但MOSFET也可以不是超接合型而是通常的MOSFET。另外,对各实施方式而言,在不矛盾的范围内能够部分地组合多个实施方式来实施。

[0058] <第一实施方式>

[0059] 图1是示出第一实施方式的半导体装置的图,图2是示出第一实施方式的半导体装

置的主要部分波形的时序图。

[0060] 第一实施方式的半导体装置具备功率半导体元件10和控制IC 20。功率半导体元件10是在同一芯片上并联连接IGBT 11和SJMOSFET 12而形成的。在此，IGBT 11具备供主电流流过的主元件和检测该主元件的电流的电流感测元件。需要说明的是，在图1中利用一个IGBT标记来表示主元件与电流感测元件，并且仅区分发射极端子，表示主元件的发射极端子与电流感测元件的发射极端子的这两个。另外，在SJMOSFET 12中也以如下状态构成，即，使检测主元件12a的电流的电流感测元件12b与供主电流流过的该主元件12a并联连接。

[0061] 在该功率半导体元件10中，IGBT 11的发射极和SJMOSFET 12的源极一起连接到功率半导体元件10的端子E。另外，IGBT 11的集电极和SJMOSFET 12的漏极一起连接到功率半导体元件10的端子C。IGBT 11的电流感测元件的发射极端子连接到端子S1，SJMOSFET 12的电流感测元件12b的源极连接到端子S2。

[0062] IGBT 11和SJMOSFET 12的栅极独立设置而成，IGBT 11的栅极连接到功率半导体元件10的端子G1，SJMOSFET 12的栅极连接到功率半导体元件10的端子G2。需要说明的是，SJMOSFET 12内置有体二极管12c，当IGBT 11和SJMOSFET 12断开时，其用作使来自功率半导体元件10的端子E的电流回流的续流二极管。

[0063] 控制IC 20具有端子T1、T2和端子U1、U2，分别连接到功率半导体元件10的端子G1、G2和端子S1、S2。在该控制IC 20中，使功率半导体元件10接通或断开的栅极信号通过电阻21作为第一控制信号被发送到端子T1，另外，还通过电阻22作为第二控制信号被发送到端子T2。

[0064] 控制IC 20具有电阻23，该电阻23的一个端子连接到端子U1，电阻23的另一个端子接地。另外，电阻23的一个端子连接到运算放大器24的非反转输入端子。运算放大器24的反转输入端子连接到恒定电流源25和电容器26的一个端子以及晶体管27的漏极。恒定电流源25和电容器26的另一个端子接地。晶体管27的源极连接到电压源28的正极端子，电压源28的负极端子接地。运算放大器24的输出端子连接到门闩电路29的输入端子，门闩电路29的输出端子连接到晶体管27的栅极。另外，运算放大器24的输出端子连接到晶体管31的栅极。该晶体管31的漏极连接到端子T1，源极接地。

[0065] 在此，电阻23和运算放大器24构成对流经IGBT 11的电流进行监测并检测过电流的过电流检测电路。由门闩电路29控制的晶体管27、电压源28、恒定电流源25和电容器26构成斜坡电压生成电路。而且，运算放大器24和晶体管31构成软关断控制电路，软关断控制电路使被供给到端子T1的第一控制信号的值跟随斜坡电压而向断开的方向变化。

[0066] 另外，控制IC 20具有电阻35，该电阻35的一个端子连接到端子U2，电阻35的另一个端子接地。另外，电阻35的一个端子连接到比较器36的非反转输入端子。比较器36的反转输入端子连接到基准电压源37的正极端子，基准电压源37的负极端子接地。比较器36的输出端子连接到RS触发器30的置位输入端子(set input terminal) S，RS触发器30的输出端子Q连接到晶体管38的栅极。晶体管38的漏极连接到端子T2，源极接地。

[0067] 在此，电阻35、比较器36和基准电压源37构成对流经SJMOSFET 12的电流进行监测并检测过电流的过电流检测电路。通过RS触发器30与比较器36连接的晶体管38构成强制地使发送到端子T2的第二控制信号成为断开信号的强制关断电路。

[0068] 在以上的构成的半导体装置中，在通常工作时，控制IC 20将生成的栅极信号分别

作为第一控制信号和第二控制信号发送到端子T1、T2。在功率半导体元件10中,利用发送到端子G1的第一控制信号使IGBT 11接通或断开,利用施加到端子G2的第二控制信号使SJMOSFET 12接通或断开。当对功率半导体元件10进行接通控制时,流经IGBT 11和SJMOSFET 12的电流在额定电流的范围内,因此没有检测出IGBT 11和SJMOSFET 12的过电流。

[0069] 这时,因流经IGBT 11的电流感测元件的电流在电阻23中流动所产生的端子电压(以下,称为感测电压)比电容器26的充电电压(以下,称为基准电压)低,因此运算放大器24输出低电平的电压信号。由此,晶体管31断开,因此不会对发送到端子T1的第一控制信号造成任何影响。需要说明的是,这时,门闩电路29从运算放大器24接收低电平的电压信号并输出低电平的电压信号,使晶体管27接通,因此使从电压源28供给的电流对电容器26充电。由于通过恒定电流源25放电的电流比从电压源28供给到电容器26的电流小,因此电容器26的电压被维持为高电平的电压。

[0070] 检测SJMOSFET 12的过电流的比较器36也是一样的,通过电阻35检测的感测电压比基准电压源37的基准电压小。因此,比较器36输出低电平的电压信号。RS触发器30保持复位状态,从而将低电平的电压信号发送到该输出端子Q,由此,对晶体管38进行关断控制,因此不会对发送到端子T2的第二控制信号造成任何影响。

[0071] 在此,例如,对在串联连接到功率半导体元件10的端子C的高侧桥臂的其它功率半导体元件发生短路事故时的该半导体装置的工作进行说明。首先,如图2所示,在时刻t0将作为IGBT栅极电压的第一控制信号发送到功率半导体元件10的端子G1,将作为SJMOSFET栅极电压的第二控制信号发送到端子G2。由此,IGBT集电极电流增大,SJMOSFET漏极电流增大。

[0072] 如果该IGBT集电极电流增大,且在时刻t1电阻23的感测电压超过电容器26的基准电压,则运算放大器24的输出成为高电平的电压信号,使晶体管31接通。由此,为了在晶体管31中使电流流经电阻21,下拉IGBT栅极电压,减小IGBT集电极电流。然后,IGBT集电极电流以使感测电压=基准电压的方式维持平衡。

[0073] 另一方面,通过使运算放大器24的输出端子变为高电平,来使门闩电路29工作而保持其检测状态。这时,门闩电路29输出高电平的电压信号,使晶体管27断开。由此,电容器26的基准电压因恒定电流源25的恒定电流的放电而降低,成为从高电平逐渐降低的斜坡电压。如果基准电压降低,则感测电压跟随该基准电压也下降,IGBT集电极电流也逐渐下降。在时刻t2,IGBT栅极电压和IGBT集电极电流降低到0。

[0074] 如此,当检测出了IGBT 11的过电流时,控制IC 20以强制地使IGBT栅极电压逐渐降低来减小IGBT集电极电流的方式进行软关断控制。由此,大幅度抑制由断开IGBT11所引起的IGBT集电极电压(SJMOSFET漏极电压)的上升,因此能够避免SJMOSFET 12因高电压的施加所导致的损坏。

[0075] 需要说明的是,对于JMOSFET12的过电流检测电路而言,与IGBT 11的过电流检测电路独立地进行工作。通过该SJMOSFET 12的过电流检测电路,SJMOSFET 12的电流感测元件12b的源极电流流经电阻35,如果这时的感测电压超过基准电压源37的电压,则比较器36输出高电平的电压信号。由此,设定RS触发器30,将高电平的电压信号发送到其输出端子Q,对晶体管38进行接通控制,下拉发送到端子T2的第二控制信号,使SJMOSFET 12断开。消除

SJMOSFET 12的过电流检测电路的过电流的主要因素后,将复位信号发送到RS触发器30的复位输入端子R,由此恢复到过电流检测待机状态。

[0076] <第二实施方式>

[0077] 图3是示出第二实施方式的半导体装置的图,图4是示出第二实施方式的半导体装置的短路耐受量的图。需要说明的是,在图3中,对与示出在图1中的构成要素相同或等同的构成要素标注相同的符号。

[0078] 在第二实施方式的半导体装置中,控制IC 20具备过电流检测电路,过电流检测电路具有IGBT 11的过电流检测用的电阻23以及将该电阻23检测出的感测电压与基准电压源41的基准电压进行比较的比较器42。比较器42的输出端子通过逆变电路43、44连接到电阻45的一个端子。电阻45的另一个端子连接到电容器46的一个端子,电容器46的另一个端子接地。另外,电阻45的另一个端子通过逆变电路47、48连接到晶体管31的栅极。该晶体管31的漏极连接到电阻21和端子T1,源极接地。具有进行波形整形的逆变电路43、44和逆变电路47、48、以及电阻45、电容器46的电路构成使过电流检测信号延迟预定时间的延迟电路。

[0079] 另外,对控制IC20而言,关于SJMOSFET 12的过电流检测电路和强制地使第二控制信号成为断开信号的强制关断电路与第一实施方式的相同。

[0080] 在以上的构成的半导体装置中,通常工作时,比较器42不检测IGBT 11的过电流,因此比较器42的输出端子输出低电平的电压信号。该低电平的电压信号通过两级逆变电路43、44而变为低电平的电压信号,因此电容器46的端子电压成为低电平的电压信号。由此,经历了逆变电路47、48的信号成为低电平的电压信号,因此晶体管31处于断开状态。

[0081] 在此,当功率半导体元件10处于接通状态时,若比较器42检测出IGBT 11的过电流后,则比较器42的输出端子成为高电平的电压信号。该高电平的电压信号经过两级逆变电路43、44而成为高电平的电压信号,因此电容器46通过电阻45被充电。在预定时间之后,如果该电容器46的充电电压超过逆变电路47的阈值,则逆变电路47输出低电平的电压信号,逆变电路48输出高电平的电压信号。由此,晶体管31接通,下拉作为发送到端子T1的第一控制信号的栅极电压,使IGBT 11断开。

[0082] 这时,SJMOSFET 12的栅极电压(第二控制信号)保持原状,因此SJMOSFET 12仍然处于接通状态。SJMOSFET 12的漏极电流的一部分从SJMOSFET 12的电流感测元件12b的源极流过控制IC 20的电阻35。如果在该电阻35中流动的电流增大、感测电压上升,并且该感测电压超过基准电压源37的基准电压,则比较器36将高电平的电压信号发送到其输出端子。由此,设定RS触发器30,将高电平的电压信号发送到其输出端子Q,对晶体管38进行接通控制,下拉施加到端子T2的栅极电压,使SJMOSFET 12断开。

[0083] 通过由电阻45和电容器46的值所求出的时间常数来确定从比较器42检测出IGBT 11的过电流至IGBT 11断开为止的预定时间。如图4中所示例的那样,例如在当施加了500伏特的IGBT集电极电压时能够使饱和集电极电流 $I_{sat}$ 持续流动的短路时间即保证损坏耐受量的时间为几微秒的情况下,该预定时间设为2微秒左右。

[0084] 在该半导体装置中,将IGBT 11先断开来降低IGBT 11的负荷,另一方面,饱和电流比IGBT 11低且能够相应地延长短路时间的SJMOSFET 12花费时间来消耗电感器等负荷中蓄积的残留能量。由此,即使在串联连接到功率半导体元件10的半导体装置短路而导致IGBT 11被施加高电压而使大电流流过的情况下,也能够使其在保证其破坏耐受量的时间

内断开,由此防止损坏。另外,由于保证破坏耐受量的时间内使IGBT 11断开,相应地能够设计为增加通道密度来提高饱和电流,承受更高的电流。

[0085] 在此,通过相对于IGBT 11和SJMOSFET 12的栅极容量分别适当地选择电阻21、22的值来分别适当地设定时间常数,来确定断开IGBT 11的时间、断开SJMOSFET 12的时间。

[0086] <第三实施方式>

[0087] 图5是示出第三实施方式的半导体装置的图,图6是示出第三实施方式的半导体装置的主要部分波形的时序图。需要说明的是,在图5中,对于与在图1和图3示出的构成要素相同或等同的构成要素标注相同的符号。

[0088] 在该第三实施方式的半导体装置中,控制IC 20具备:检测IGBT 11的过电流并进行保护的电路以及检测SJMOSFET 12的过电压和过电流并进行保护的电路。

[0089] 即,控制IC 20具备:IGBT 11的过电流检测用的电阻23、将该电阻23检测的感测电压与基准电压源41的基准电压进行比较的比较器42、以及下拉施加到端子T1的栅极电压的晶体管31。由此,如果检测出IGBT 11的过电流,则控制IC 20立刻断开IGBT 11。

[0090] 在该半导体装置中,在功率半导体元件10的芯片上形成有齐纳二极管51与电阻52的串联连接电路。对齐纳二极管51而言,其阴极连接到功率半导体元件10的端子C,阳极连接到电阻52的一个端子和功率半导体元件10的端子V1,电阻52的另一个端子连接到功率半导体元件10的端子E。由此,如果功率半导体元件10的端子E与端子C之间的电压高于齐纳二极管51的齐纳电压,则利用通过雪崩破坏现象引起电流剧烈流动,来检测功率半导体元件10的过电压。

[0091] 为了检测功率半导体元件10的过电压,控制IC 20具有端子W1,使该端子W1连接到功率半导体元件10的端子V1。在控制IC 20的内部,端子W1连接到电压检测电路53。该电压检测电路53对因在齐纳二极管51中电流剧烈流动而引起的电阻52产生的电压下降的变化进行监控。

[0092] 该电压检测电路53的输出端子连接到NAND电路54的一个输入端子,NAND电路54的另一个输入端子连接到检测SJMOSFET 12的过电流的比较器36的输出端子。NAND电路54的输出端子通过逆变电路55连接到晶体管38的栅极。晶体管38的漏极连接到端子T2,源极接地。

[0093] 根据以上构成的半导体装置,首先,如图6所示,在时刻t0通过使IGBT栅极电压和SJMOSFET栅极电压成为高电平的电压信号而分别接通IGBT 11和SJMOSFET 12。

[0094] 在时刻t1,控制IC 20的比较器42检测出了IGBT 11的过电流的情况下,比较器42立刻接通晶体管31,使IGBT栅极电压成为低电平的电压信号。由此,IGBT 11断开,防止IGBT 11的损坏。

[0095] 通过断开IGBT 11使得IGBT集电极电压骤升,在时刻t2,通过齐纳二极管51、电阻52和电压检测电路53检测出该电压。这时,比较器36检测SJMOSFET 12的过电流,因此NAND电路54的两个输入端子接收到高电平的电压信号。因此,NAND电路54的输出端子成为低电平的电压信号,因此逆变电路55的输出端子成为高电平的电压信号。由此,对晶体管38进行接通控制,下拉施加到端子T2的栅极电压,使SJMOSFET 12断开。如此,在SJMOSFET 12中有大电流流过且被施加了高电压的情况下,断开SJMOSFET 12,由此能够防止SJMOSFET 12的损坏。需要说明的是,在SJMOSFET 12中有大电流流过或被施加了高电压中的任意一种情况

下,SJMOSFET 12不被损坏,因此不进行SJMOSFET 12的断开控制。

[0096] 如果SJMOSFET 12的断开控制之后,抑制IGBT集电极电压的骤增并降低IGBT集电极电压(时刻t3),则电压检测电路53不检测功率半导体元件10的过电压,因此使输出端子成为低电平的电压信号。由此,NAND电路54的输出端子成为高电平,逆变电路55的输出端子成为低电平的电压信号,晶体管38断开。其结果是,SJMOSFET栅极电压重新变为高电平的电压信号,SJMOSFET 12再次接通,消耗在IGBT 11断开后存在的能量。

[0097] 以上,在本发明中对其优选实施方式进行了说明,但本发明不限定于该特定的实施方式,只要在不脱离本发明的精神的范围内,可以进行各种变更。

图1

图2

图3

图4

图5

图6

图7