**(19) 대한민국특허청(KR)**

**(12) 공개특허공보(A)**

(51) . Int. Cl.

*G06K 19/07* (2006.01)

*H02M 7/06* (2006.01)

*H02M 7/217* (2006.01)

*G06K 17/00* (2006.01)

(11) 공개번호 10-2007-0006693

(43) 공개일자 2007년01월11일

(21) 출원번호 10-2006-7014269

(22) 출원일자 2006년07월14일

심사청구일자 없음

번역문 제출일자 2006년07월14일

(87) 국제공개번호 WO 2005/062241

(86) 국제출원번호 PCT/US2004/036344

국제공개일자 2005년07월07일

국제출원일자 2004년11월01일

(30) 우선권주장 10/738,082 2003년12월17일 미국(US)

(71) 출원인 쓰리엠 이노베이티브 프로퍼티즈 컴파니

미국 55133-3427 미네소타주 세인트 폴 피.오.박스 33427 쓰리엠 센터

(72) 발명자 보드, 폴 에프.

미국 55133-3427 미네소타주 세인트 폴 포스트 오피스 박스 33427

해제, 마이클 에이.

미국 55133-3427 미네소타주 세인트 폴 포스트 오피스 박스 33427

테이스, 스티븐 디.

미국 55133-3427 미네소타주 세인트 폴 포스트 오피스 박스 33427

(74) 대리인 주성민

백만기

이중희

전체 청구항 수 : 총 26 항

(54) 로직 게이트 및 부분 정류 스테이지를 갖는 전기 회로

(57) 요약

로직 회로는 부분적으로 정류된 교류(ac) 파형에 의해 전력을 공급받는다. 파형은, 깨끗한 근본적인 dc 전력 신호를 제공하지 않는다는 면에서, 부분적으로 정류된 것이다. 대신에, 실질적인 ac 성분을 포함하는 파형의 전력을 로직 회로에 공급하는 것이 가능하다. 부분적으로 정류된 ac 파형은 비정질 또는 다결정 유기 반도체, 무기 반도체 또는 이들의 조합에 기초한 박막 트랜지스터들을 포함하는 로직 회로에 인가될 수 있다.

대표도

도 1

## 특허청구의 범위

### 청구항 1.

전자 회로에 있어서,

로직 게이트를 형성하도록 구성된 제1 트랜지스터 및 제2 트랜지스터;

ac 전력 파형을 생성하기 위한 교류(ac)원; 및

상기 ac 전력 파형으로부터 부분적으로 정류된 ac 전력 파형을 생성하여, 이 부분적으로 정류된 ac 전력 파형의 전력을 상기 로직 게이트에 직접 공급하는 부분 정류 스테이지(a partial rectification stage)

를 포함하며, 상기 부분적으로 정류된 ac 전력 파형은 ac 성분 및 직류(dc)성분을 포함하며, 상기 dc 성분은 상기 회로에 전력을 제공하기에는 불충분한 전자 회로.

### 청구항 2.

제1항에 있어서, 상기 부분 정류 스테이지는 출력 필터링 커패시터를 포함하는 전자 회로.

### 청구항 3.

제1항에 있어서, 상기 부분 정류 스테이지는 출력 필터링 커패시터를 포함하지 않는 전자 회로.

### 청구항 4.

제1항에 있어서, 상기 부분 정류 스테이지는, 상기 부분적으로 정류된 ac 전력 파형으로서 근본적인 직류(primarily dc) 전력 신호를 생성하기 위해 불충분한 용량성 필터링을 갖는 반파 정류기(half-wave rectifier)를 포함하는 전자 회로.

### 청구항 5.

제1항에 있어서, 상기 부분 정류 스테이지는 트랜지스터 기반 정류기를 포함하는 전자 회로.

### 청구항 6.

제1항에 있어서, 상기 부분 정류 스테이지는 다이오드 기반 정류기를 포함하는 전자 회로.

### 청구항 7.

제1항에 있어서, 상기 로직 게이트는 인버터, NOR 게이트 및 NAND 게이트 중 하나를 포함하는 전자 회로.

### 청구항 8.

제1항에 있어서, 상기 로직 게이트는 아날로그 증폭기를 형성하는 전자 회로.

### 청구항 9.

제1항에 있어서, 표시 소자를 더 포함하며, 상기 로직 게이트는 상기 표시 소자를 구동하도록 결합되어 있는 전자 회로.

### 청구항 10.

제1항에 있어서, 상기 회로는 일련의 인버터 스테이지들을 포함하며, 상기 일련의 인버터 스테이지들은 링 오실레이터의 적어도 일부를 형성하도록 결합되어 있는 전자 회로.

### 청구항 11.

제10항에 있어서,

복수의 데이터 라인; 및

상기 링 오실레이터에 의해 생성된 클럭 신호에 응답하여 상기 데이터 라인으로부터의 데이터를 선택적으로 출력하는 복수의 로직 게이트

를 더 포함하는 전자 회로.

### 청구항 12.

제1항에 있어서, 상기 트랜ジ스터들 중 적어도 하나는 유기 박막 트랜ジ스터인 전자 회로.

### 청구항 13.

제1항에 있어서, 상기 트랜ジ스터들 중 적어도 하나의 반도체 재료는 펜타센(pentacene), 산화 아연, 폴리실리콘 또는 비정질 실리콘 중 하나인 전자 회로.

### 청구항 14.

제1항에 있어서, 상기 제1 트랜ジ스터는 n 채널 트랜ジ스터이고, 상기 제2 트랜ジ스터는 p 채널 트랜ジ스터인 전자 회로.

### 청구항 15.

제1항에 있어서, 상기 로직 게이트는 RFID(radio frequency identification) 태그의 일부를 형성하는 전자 회로.

### 청구항 16.

제1항에 있어서, 상기 트랜ジ스터들 중 적어도 하나는 무기 박막 트랜ジ스터인 전자 회로.

### 청구항 17.

적어도 제1 트랜지스터와 제2 트랜지스터로 형성된 로직 게이트에, 교류(ac) 전원으로부터 생성된 부분적으로 정류된 ac 파형의 전력을 직접적으로 공급하는 방법으로서, 상기 부분적으로 정류된 ac 전력 파형은 ac 성분 및 직류(dc) 성분을 포함하고, 상기 dc 성분은 상기 로직 게이트에 전력을 제공하기에 불충분한 방법.

### 청구항 18.

제17항에 있어서, 상기 로직 게이트에 전력을 인가하기 전에, 상기 부분적으로 정류된 ac 전력 파형을 커패시터에 의해 필터링하는 것을 더 포함하는 방법.

### 청구항 19.

제17항에 있어서, 부분 정류 스테이지에 의해, 상기 ac 전원에 의해 생성된 ac 전력 파형을 부분적으로 정류하여, 상기 부분적으로 정류된 ac 전력 파형을 생성하는 것을 더 포함하는 방법.

### 청구항 20.

제19항에 있어서, 상기 부분 정류 스테이지는, 상기 부분적으로 정류된 ac 전력 파형으로서 근본적인 직류(primarily dc) 전력 신호를 생성하기 위해 불충분한 용량성 필터링을 갖는 반파 정류기를 포함하는 방법.

### 청구항 21.

제19항에 있어서, 상기 부분 정류 스테이지는 트랜지스터 기반 정류기를 포함하는 방법.

### 청구항 22.

제21항에 있어서, 상기 부분 정류 스테이지는 다이오드 기반 정류기를 포함하는 방법.

### 청구항 23.

제17항에 있어서, 상기 트랜지스터들 중 적어도 하나는 유기 박막 트랜지스터인 방법.

### 청구항 24.

제17항에 있어서, 상기 트랜지스터들 중 적어도 하나는 무기 박막 트랜지스터인 방법.

### 청구항 25.

RFID(radio frequency identification) 태그에 있어서,

로직 게이트를 형성하도록 구성된 제1 및 제2 트랜지스터, RF 에너지를 교류(ac) 전력 파형으로 변환하는 RF 주파수(radio frequency) 컨버터, 상기 ac 전력 파형으로부터 부분적으로 정류된 ac 전력 파형을 생성하여, 상기 부분적으로 정류된 ac 전력 파형의 전력을 상기 로직 게이트에 직접 공급하는 부분 정류 스테이지, 및 정보를 이송하는 변조기

를 포함하며, 상기 부분적으로 정류된 ac 전력 파형은 ac 성분과 dc 성분을 포함하며, 상기 dc 성분은 상기 로직 게이트에 전력을 제공하기에 불충분한 RFID 태그.

## 청구항 26.

RFID(radio frequency identification) 시스템에 있어서,

- a) 제25항의 RFID 태그; 및

- b) 상기 RF 컨버터에 의해 변환하기 위해 상기 RFID 태그에 RF 에너지를 전송하고, 상기 변조기에 의해 이송되는 정보를 판독하는 RFID 판독기

를 포함하는 RFID 시스템.

## 명세서

### 기술분야

본 발명은 로직 회로에 관한 것으로, 특히 로직 회로에 전력을 공급(powering)하는 기술에 관한 것이다.

### 배경기술

집적 회로, 평면 패널 디스플레이, 스마트 카드, 및 RFID(radio frequency identification) 태그를 포함하는 각종 모던 전자 디바이스의 로직 회로를 형성하기 위해, 트랜지스터, 다이오드 등을 포함하는 박막 회로 디바이스들이 광범위하게 사용된다. 박막 회로 디바이스들은, 각종의 도체, 반도체 및 절연층들을 피착, 마스킹, 및 에칭하여 박막 스택을 형성함으로써 형성된다.

통상, 박막 트랜지스터(TFT)는 비정질 실리콘 또는 카드뮴 셀레나이드 등의 무기 반도체 재료에 기초한다. 최근, 유기 반도체 재료를 이용하여 박막 트랜지스터 회로를 형성하는 것에 관한 상당한 연구 개발 노력이 있어왔다.

유기 반도체 재료는, 낮은 처리 온도를 포함한 트랜지스터 제조를 위한 많은 제조 이점을 제공한다. 특히, 유기 반도체 재료는, 얇은 유리, 폴리메릭(ploymeric) 또는 페이퍼 기초(paper-based) 기판 등의 가요성 기판 상의 유기 박막 트랜지스터(OTFT)의 제조를 허용한다.

또한, 유기 반도체 재료는 프린팅, 엠보싱 또는 쉐도우 마스킹 등의 저가의 제조 기술을 이용하여 형성될 수 있다. 계속된 연구와 개발로, OTFT의 성능 특성이 향상되었지만, 디바이스 성능 및 안정성은 과제로 남아있다.

### <요약>

일반적으로, 본 발명은 부분적으로 정류된 교류(ac) 파형에 의해 전력을 공급받는 로직 회로에 관한 것이다. 그 파형은, 깨끗한 근본적인 dc(primarily dc) 전력 파형을 제공하지 않는다는 면에서 부분적으로 정류된 것이다. 대신에, 로직 회로에, 실질적인 ac 성분을 포함하는 파형의 전력을 공급하는 것이 가능하다. 사실상, dc 성분은, 그 자신만으로는, 회로에 전력을 공급하기에 충분하지는 않다. 본 발명은, 비정질 또는 다결정 유기 반도체, 무기 반도체 또는 이들의 조합에 기초한 박막 트랜지스터를 통합한 로직 회로에 적용될 수 있다.

향상된 안정도는, OTFT 회로를 이용하여 인버터, 오실레이터, 로직 게이트, 레지스터 및 다른 트랜지스터 기반 로직 회로를 포함한 각종 박막 트랜지스터 기반 로직 회로 디바이스를 형성하는 것을 허용할 수 있다. 이러한 로직 회로 디바이스는,

집적 회로, 평면 패널 디스플레이, 스마트 카드 및 RFID 태그를 포함한 각종 어플리케이션에서 그 유용성을 찾을 수 있다. 일부 어플리케이션의 경우, 부분적으로 정류된 ac 파형의 전력을 로직 회로에 공급함으로써 전파(full wave) ac-dc 정류 스테이지에 대한 필요성을 없게 할 수 있다.

부분 정류 스테이지는, 필터링 커패시터에 대한 필요성 없이, 다이오드, 트랜지스터 등에 의해 실현될 수 있다. 이러한 방식으로, 본 발명은 부분적으로 정류된 ac 전력 파형에 의해 전력을 공급받는 로직 회로를 갖는 컴포넌트의 제조 시간, 소요 경비(expense), 가격(cost), 복잡도 및 사이즈를 저감시킬 수 있다. 부분적인 정류에 의해 ac 및 dc 성분이 둘 다 존재한다. ac 부분은 꽤 클 수 있고, dc 부분은 작을 수 있다. 이 경우, dc 부분은 그 자체로만은 로직 회로에 전력을 공급하기에 불충분할 수 있다. 전형적으로, 로직 회로는 로직 회로를 구성하는 트랜지스터의 임계 전압을 초과하는 전압을 필요로 한다. dc 전력에 의해 구동되는 회로에서는, dc 전압이 임계 전압보다 작으면, 회로는 동작하지 않을 것이다. ac 전력을 제공함으로써, ac 성분이 충분히 크고, 여전히 회로에 전력을 공급하고 있으면, dc 성분을 임계 전압보다 작게 할 수 있다.

부분적으로 정류된 ac 전력 파형은 로직 게이트 회로에 직접적으로 전력을 제공한다. 특히, ac 전원 및 부분 정류 스테이지는, 로직 게이트에 dc 전력을 인가하는 대신, 하나 이상의 개별의 로직 게이트들에 부분적으로 정류된 ac 전력 파형을 인가한다.

부분 정류 스테이지는, 부분적으로 정류된 ac 전력 파형으로서 근본적인 직류(dc) 전력 신호를 생성하기 위해 불충분한 용량성 필터링을 갖는 반파(half-wave) 또는 전파(full-wave) 정류기를 포함한다. 이런 방식으로, 전파 또는 반파 정류 스테이지에 통상적으로 제공되는 대형의 필터링 커패시터가 제거되거나 사이즈가 감소되어, 회로의 전체적인 사이즈가 감소될 수 있다.

부분적으로 정류된 ac 전력 파형에 의해 전력을 공급받는 로직 회로는 각종 전자 디바이스에 사용될 수 있다. 예를 들어, 이러한 로직 회로는 나어필드 전자기 무선 주파수 커플링(near-field electromagnetic radio frequency coupling)에 의해 ac 파형이 유도되는 무선 주파수(RFID) 태그에 관한 어플리케이션에 특히 유용할 수 있다. ac 파형은 RFID 태그를 갖는 전자 로직 회로의 일부 또는 전부에 전력을 공급하도록 부분적으로 정류될 수 있다.

일 실시예에서는, 본 발명은 로직 게이트를 형성하도록 구성된 제1 트랜지스터 및 제2 트랜지스터, ac 전력 파형을 생성하기 위한 교류(ac)원, 및 ac 전력 파형으로부터 부분적으로 정류된 ac 전력 파형을 생성하여 부분적으로 정류된 ac 전력 파형의 전력을 로직 게이트에 전력을 직접적으로 공급하기 위한 부분 정류 스테이지를 포함하는 전자 회로를 제공한다. 로직 게이트는 전달 지연(propagation delay)을 특징으로 한다. ac 파형은 전달 지연보다 작은 주기를 갖고, 양호하게는 전달 지연의 1/5보다 작은 주기를 갖는다.

또 다른 실시예에서는, 본 발명은 적어도 제1 트랜지스터 및 제2 트랜지스터에 의해 형성된 로직 게이트에, 교류(ac) 전원으로부터 생성된 부분적으로 정류된 교류(ac) 전력 파형의 전력을 직접적으로 공급하는 것을 포함하는 방법을 제공한다.

부가된 실시예에서는, 본 발명은, 적어도 제1 트랜지스터 및 제2 트랜지스터에 의해 형성된 로직 게이트, ac 전력 파형을 제공하기 위한 무선 주파수(RF) 에너지 커플링 디바이스, 및 ac 전력 파형으로부터 부분적으로 정류된 ac 전력 파형을 생성하여, 부분적으로 정류된 ac 전력 파형의 전력을 로직 게이트에 직접적으로 제공하는 부분 정류 스테이지를 포함하는 RFID(a radio frequency identification) 태그를 제공한다.

다른 실시예에서는, 본 발명은 로직 게이트를 형성하도록 구성된 제1 및 제2 트랜지스터, RF 에너지를 교류(ac) 전력 파형으로 변환하기 위한 무선 주파수(RF) 컨버터, ac 전력 파형으로부터 부분적으로 정류된 ac 전력 파형을 생성하여, 부분적으로 정류된 ac 전력 파형의 전력을 로직 게이트에 직접적으로 공급하는 부분 정류 스테이지, 및 정보를 전달하는 변조기를 포함하는 RFID 태그, 및 RF 컨버터에 의한 변환을 위해 RF 에너지를 RFID 태그로 전송하고, 변조기에 의해 전달되는 정보를 판독하는 RFID 판독기(reader)를 포함하는 RFID 시스템을 제공한다.

본 발명은 많은 장점을 제공할 수 있다. 예를 들면, 부분적으로 정류된 ac 전력 파형을 이용하여 로직 회로에 직접적으로 전력을 제공함으로써, 회로에 dc 전력을 전달하기 위해 많은 어플리케이션에 공통적으로 요구되는 전파 정류기 또는 반파 컴포넌트의 필터링 커패시터에 대한 필요성을 제거할 수 있다. 따라서, 부분적으로 정류된 ac 전력을 이용함으로써, 박막 트랜지스터 회로를 구비하는 컴포넌트의 제조 시간, 소요경비, 가격, 복잡도 및 사이즈를 저감시킬 수 있다.

RFID 태그의 경우, 특례로서, ac 전력을 공급받는 박막 회로를 이용하면, 다이오드 또는 트랜지스터 브릿지, 및 대용량 필터링 커패시터를 포함한 ac-dc 정류기 스테이지와 통상 관련된 많은 컴포넌트들의 사이즈를 제거하거나 감소시킴으로써

태그의 가격 및 사이즈가 상당히 저감될 수 있다. 정류기 스테이지의 복잡도를 저감시킴으로써, 부분적으로 정류된 ac 파형의 전력을 공급받는 박막 로직 회로에 의해 RFID 태그의 설계 및 제조에 있어서 상당한 비용 절감 및 사이즈 감소를 가져올 수 있다.

이러한 실시예 및 다른 실시예들에 대한 부가적인 상세가 첨부된 도면 및 이하의 설명에 개시되어 있다. 다른 특징, 목적 및 장점들은, 설명 및 도면으로부터 그리고 특히 청구범위로부터 명확해질 것이다.

### 도면의 간단한 설명

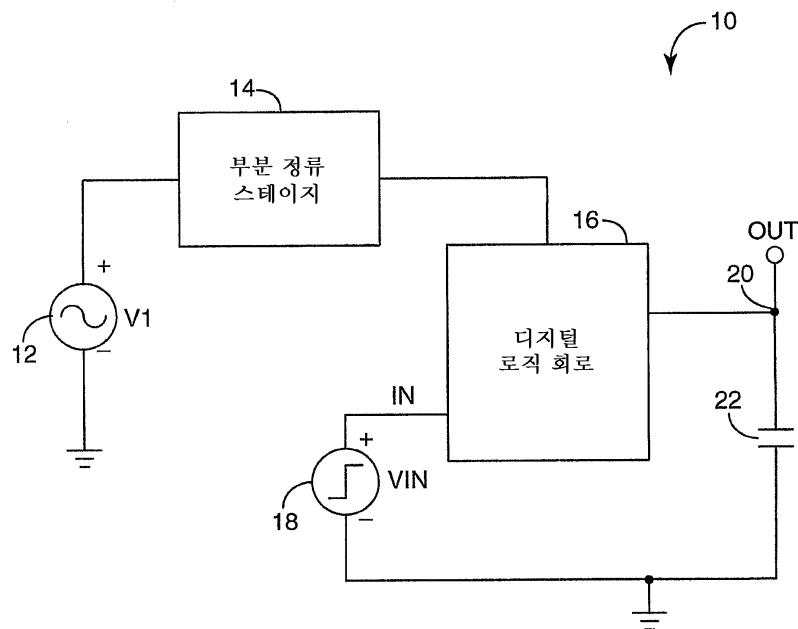

도 1은 부분적으로 정류된 ac 파형에 의해 전력을 공급받는 디지털 로직 회로를 도시하는 회로도.

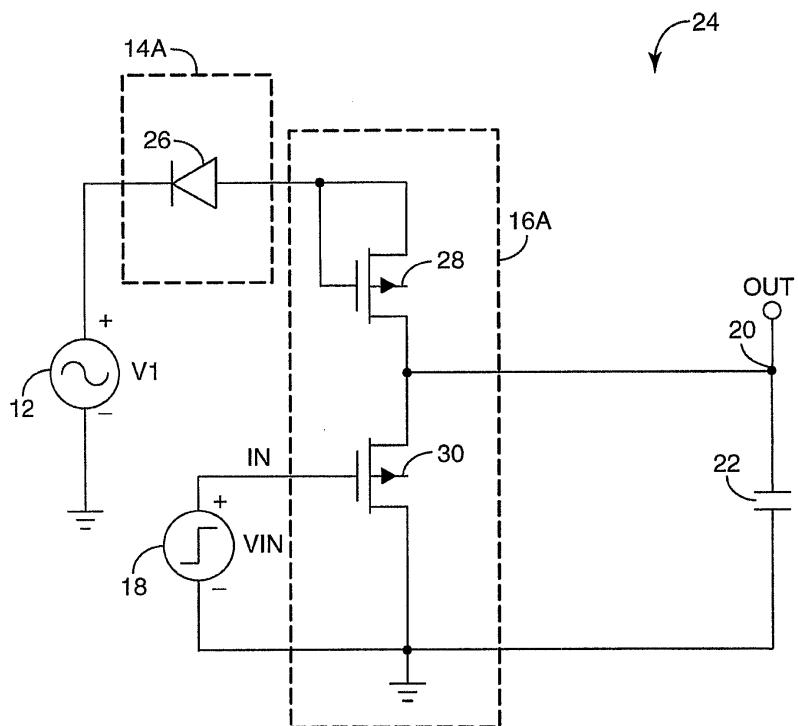

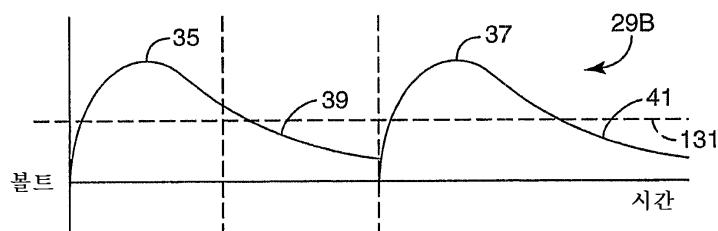

도 2는 반파 다이오드 기반 부분 정류 스테이지에 의해 생성된 부분적으로 정류된 ac 파형에 의해 전력을 공급받는 인버터 회로를 도시하는 회로도.

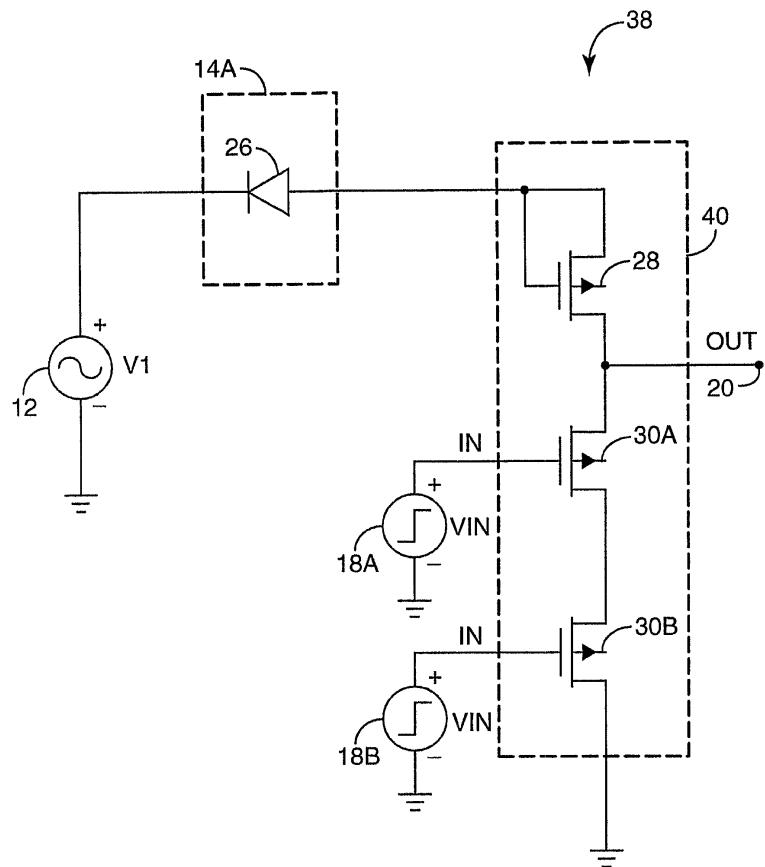

도 3은 반파 트랜지스터 기반 부분 정류 스테이지에 의해 생성된 부분적으로 정류된 ac 파형에 의해 전력을 공급받는 인버터 회로를 도시하는 회로도.

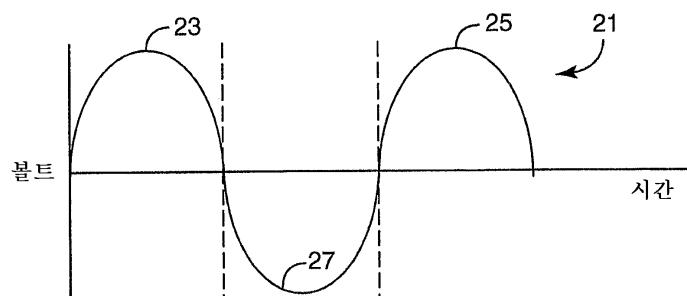

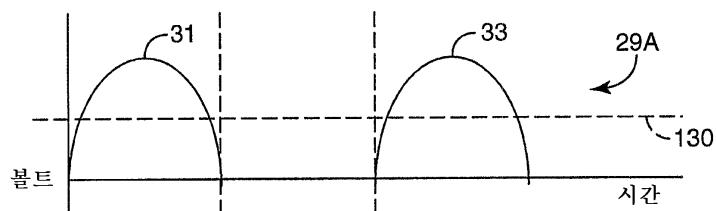

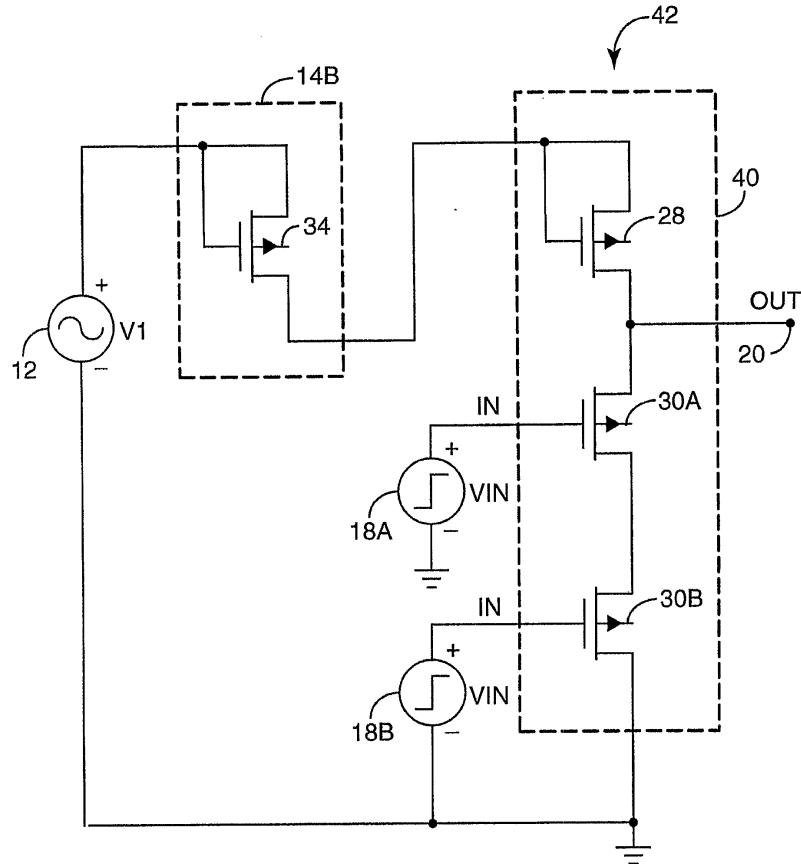

도 4A, 도 4B 및 도 4C는 ac 전력 파형 및 예시적인 부분적으로 정류된 ac 전력 파형을 개념적으로 도시하는 그레프.

도 5는 반파 다이오드 기반 부분 정류 스테이지에 의해 생성된 부분적으로 정류된 ac 파형에 의해 전력을 공급받는 NAND 게이트 회로를 도시하는 회로도.

도 6은 반파 트랜지스터 기반 부분 정류 스테이지에 의해 생성된 부분적으로 정류된 ac 파형에 의해 전력을 공급받는 NAND 게이트 회로를 도시하는 회로도.

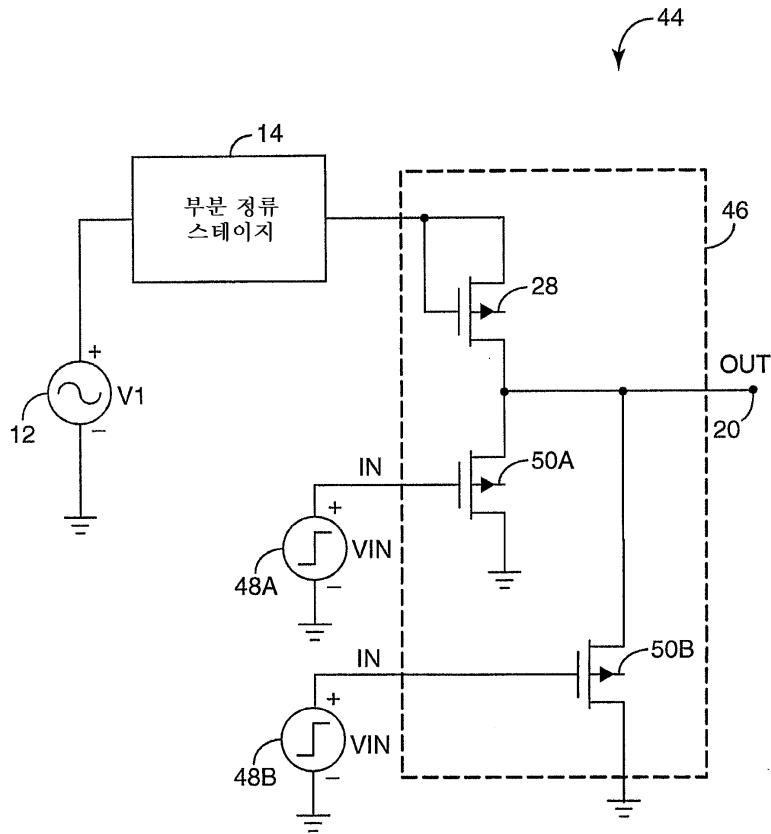

도 7은 부분적으로 정류된 ac 파형에 의해 전력을 공급받는 NOR 게이트 회로의 회로도.

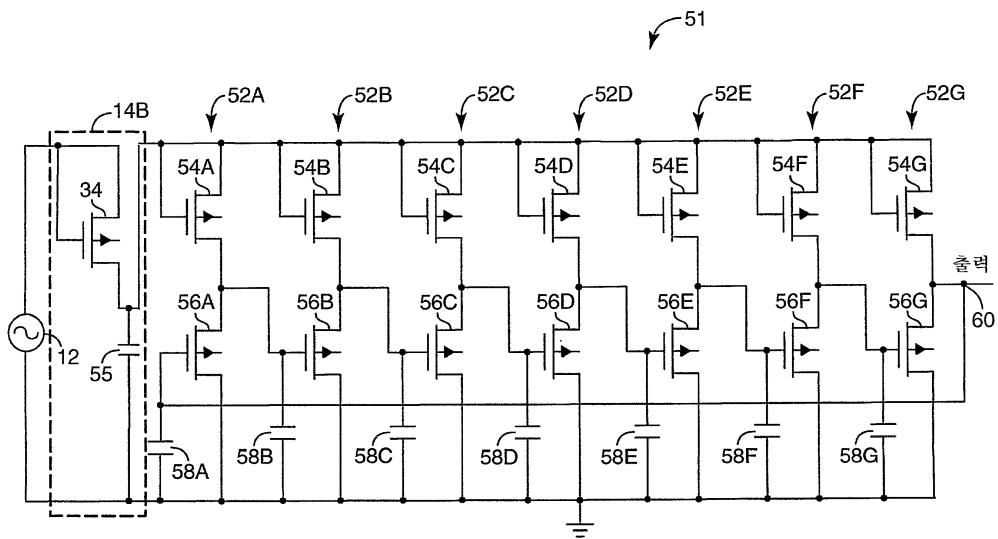

도 8은 필터링 커패시터를 갖는 반파 트랜지스터 기반 정류기 스테이지에 의해 생성된 부분적으로 정류된 ac 파형에 의해 전력을 공급받는 박막 트랜지스터 기반 링 오실레이터 회로를 도시하는 회로도.

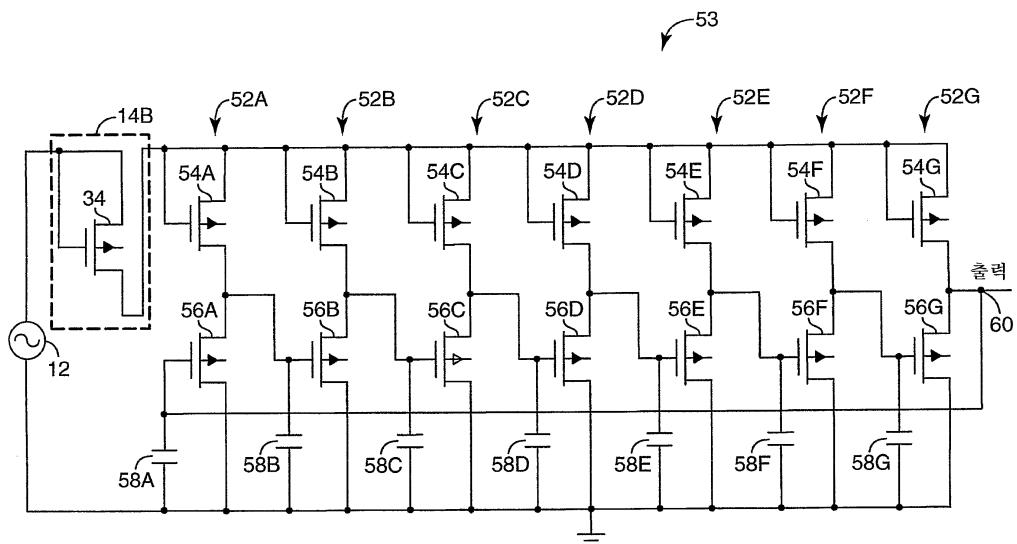

도 9는 필터링 커패시터가 없는, 반파 트랜지스터 기반 정류기 스테이지에 의해 생성된 부분적으로 정류된 ac 파형에 의해 전력을 공급되는 박막 트랜지스터 기반 링 오실레이터 회로를 도시하는 회로도.

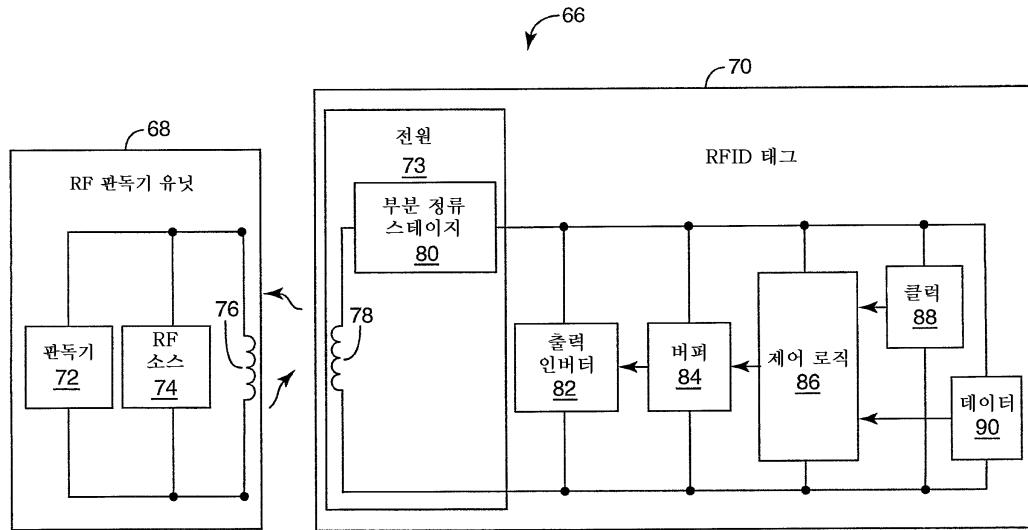

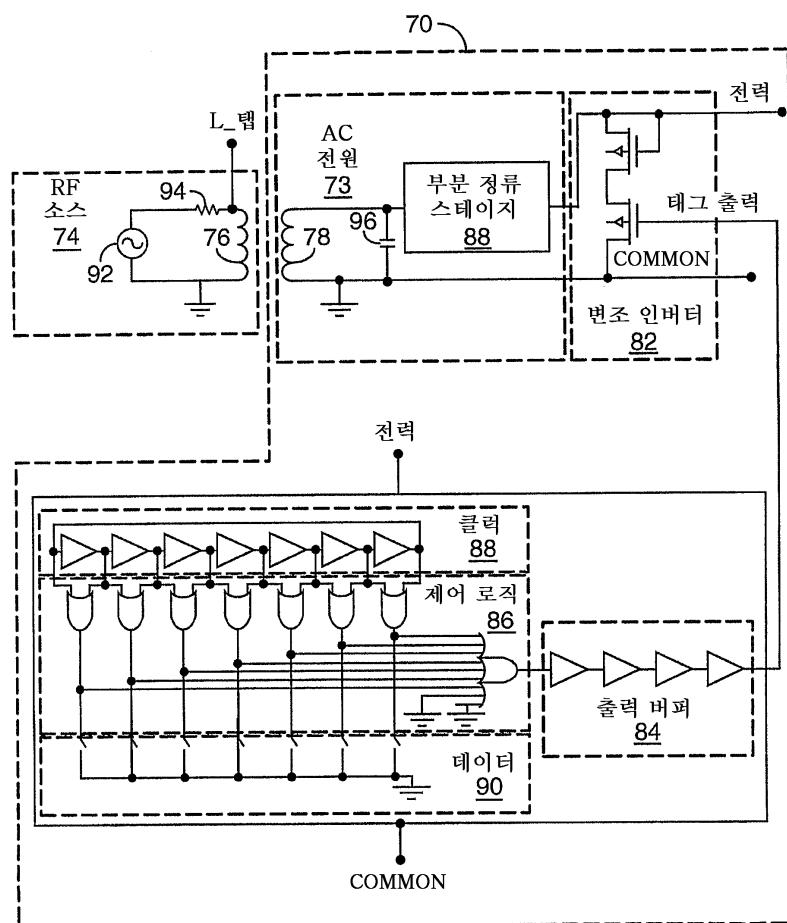

도 10은 RFID 태그/판독기 시스템에서의 ac 전력을 공급받는 박막 트랜지스터 회로의 어플리케이션을 도시하는 블록도.

도 11은 도 10의 RFID 태그/판독기 시스템을 또한 도시하는 회로도.

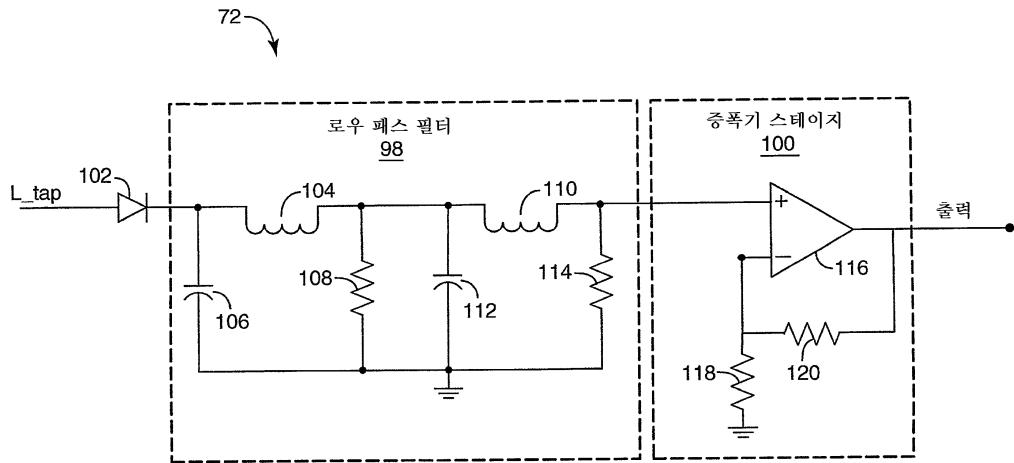

도 12는 도 10의 RFID 태그/판독기 시스템과 관련된 판독기를 또한 도시하는 회로도.

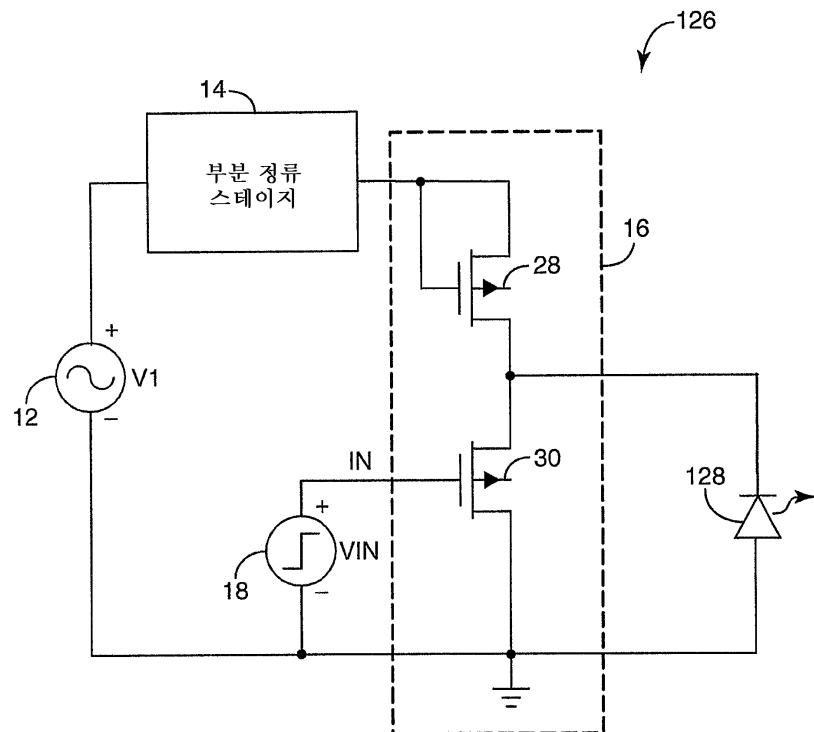

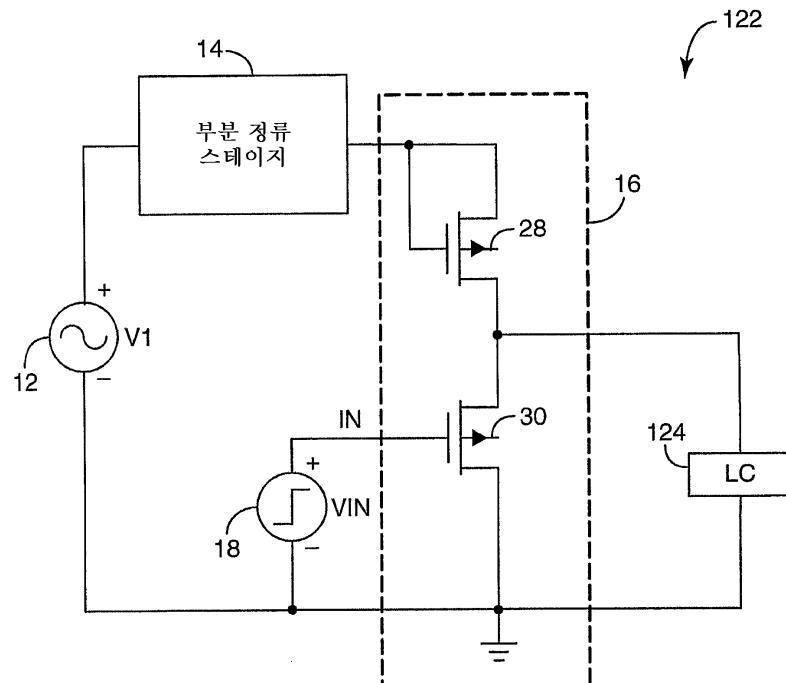

도 13은 액정 표시 소자를 구동하도록 부분적으로 정류된 ac 파형에 의해 전력을 공급받는 인버터 회로를 도시하는 회로도.

도 14는 LED(a light emitting diode)를 구동하도록 부분적으로 정류된 ac 파형에 의해 전력을 공급받는 인버터 회로를 도시하는 회로도.

### 실시예

도 1은 부분적으로 정류된 ac 파형에 의해 전력을 공급받는 회로(10)를 도시하는 회로도이다. 도 1에 도시된 바와 같이, ac 파워 서플라이(12)는 부분 정류 스테이지(14)에 ac 전력 파형을 전달한다. 부분 정류 스테이지(14)는 디지털 로직 회로(16)에 전력을 공급하기 위해 ac 전력 파형을 부분적으로 정류시킨다. 신호원(18)은 로직 신호로 디지털 로직 회로(16)를 구동시킨다. 디지털 로직 회로(16)는 출력(20)에 출력 로직 신호를 생성한다. 커패시터(22)는 출력(20)과 그라운드 사이에 결합될 수 있다.

부분 정류 스테이지(14)에 의해 디지털 로직 회로(16)에 인가된 파형은, 종래에 디지털 로직 회로에 전력을 공급하는데 사용되었던 것과 같은, 깨끗한, 근본적인 dc 전력 신호를 제공하지 않는다는 면에서, 부분적으로 정류된 것이다. 대신에, 본 발명에 따르면, 실질적인 ac 성분을 포함하는 파형의 전력을 디지털 로직 회로(16)에 제공하는 것이 가능하다.

부분적으로 정류된 파형은, 예를 들면 비정질 또는 다결정 유기 반도체, 무기 반도체 또는 그 조합에 기초한 박막 트랜지스터를 포함하는 디지털 로직 회로(16)에 인가될 수 있다. 디지털 로직 회로(16)에 전력을 공급하는데 있어 부분적으로 정류된 ac 전력 파형을 이용함으로써, 각종 어플리케이션의 만족할만한 디바이스의 성능을 지원할 수 있다. 예를 들면, OTFT 회로가 부분적으로 정류된 ac 전력 파형에 의해 전력을 공급받는 경우, OTFT 회로는 dc 전력 신호 없이도 만족할만한 성능 특성을 나타낼 수 있다.

깨끗한 dc 전력 신호 없는 만족할만한 성능은, 전파 정류 회로에 대한 필요성이 없는 TFT 회로를 이용하여, 인버터, 오실레이터, 로직 게이트, 레지스터 또는 임의의 다른 트랜지스터 기반 로직 회로를 포함하는 각종의 박막 트랜지스터 기반 로직 회로 디바이스를 형성하도록 허용한다. 이러한 로직 회로 디바이스는, 접적 회로, 평면형 패널 디스플레이, 스마트 카드, 및 RFID 태그를 포함하는 각종 어플리케이션에서 그 유용성을 찾을 수 있다.

도 2는 반파 다이오드 기반 부분 정류 스테이지(14A)에 의해 생성된 부분적으로 정류된 ac 파형에 의해 전력을 공급받는 인버터 회로(16A)를 도시하는 회로도이다. 도 2에 도시된 바와 같이, 다이오드(26)는 ac 전원(12)에 의해 생성된 ac 파형의 네거티브-고잉 하프 사이클만을 통과시키는 역할을 하여, 부분 정류 스테이지(14A)로서 기능을 한다. 이 예에서, 인버터 회로(16A)는 부하 트랜지스터(28) 및 드라이브 트랜지스터(30)를 포함한다. 각 트랜지스터(28, 30)는 박막 전계 효과 트랜지스터(FET)일 수 있고, 비정질 또는 다결정 무기 또는 유기 반도체 재료 또는 이들의 조합에 기초할 수 있다. 커패시터(22)는 출력(20)과 그라운드 사이에 결합될 수 있다.

OTFT를 형성하기 위한 유용한 유기 반도체 재료는 아센류(acenes) 및 그 치환된 유도체를 포함한다. 아센류의 특정한 예로서, 안트라센, 나프탈렌, 테트라센, 웬타센, 및 치환된 웬타센(양호하게는, 플루오르 웬타센을 포함하는 웬타센 또는 치환된 웬타센)이 있다. 다른 예로서, 반도체 폴리머, 폐릴렌, 폴러렌, 프탈로시아민, 올리고시오펜, 폴리시오펜, 폴리페닐비닐렌, 폴리아세틸렌, 메탈로프탈오시아민 및 치환된 유도체가 있다. 2003년 7월 15일자 출원된 공동 계류중인 출원 USSN 10/620027호에, 유용한 비스-(2-아세닐) 아세틸렌 반도체 재료가 개시되어 있다. 공동 계류중인 출원 USSN 10/641730호에, 유용한 아센-시오펜(acene-thiophene) 반도체 재료가 개시되어 있다. 박막 트랜지스터를 형성하기 위한 유용한 무기 반도체 재료는, 비정질 실리콘, 다결정, 텘루리움, 산화 아연, 아연 셀레나이드, 황화 아연, 황화 카드뮴 및 카드뮴 셀레나이드를 포함한다.

다른 것으로서, 디지털 로직 회로(16A)는, 유기 및 무기 반도체 재료의 조합에 의해 형성되어, 예컨대 CMOS (complementary metal oxide semiconductor) 인버터 회로를 형성할 수 있다. 예를 들어, 일부 어플리케이션에서는, 인버터 회로(16A)는 NMOS(n-channel metal oxide semiconductor) 무기 전계 효과 트랜지스터(FET) 및 PMOS(p-channel metal oxide semiconductor) 유기 전계 효과 트랜지스터(FET)에 의해 형성될 수 있다. OTFT를 사용하는 경우, 트랜지스터(28, 30)는 저가 제조 기술을 이용한 제조에 특히 적응될 수 있으며, 일부 어플리케이션의 경우 가요성 기판 상에 형성될 수 있다.

ac 전원(12)은 ac 전력 파형을 다이오드(26)에 직접 인가하는데, 이 다이오드(26)는 일련의 교류 하프 사이클의 ac 파형의 형태로 부분적으로 정류된 파형을 인버터 회로(16A)에 인가한다. 일부 실시예들에서는, 다이오드(26)의 캐소드와 그라운드 사이에 필터링 커패시터가 제공될 수 있다. 그러나, 필터링 커패시터는 완전하게 정류된 실질적으로 dc인 파형을 생성하기에 충분치 않은 용량을 가질 수 있다. 오히려, 다이오드(26)는 인버터(16A)에 직접적으로 인가되는 부분적으로 정류된 ac 파형만을 생성한다.

이런 방식으로, 인버터(16A)는 dc 전력 파형 대신에 부분적으로 정류된 ac 전력 파형만을 수신한다. 환연하면, 인버터(16A)는 부분적으로 정류된 ac 전력 파형에 응답하여 동작한다. 따라서, 인버터가 dc 전력 신호가 아니라, 여전히 부분적으로 정류된 ac 전력 파형만을 동작 전력으로서 수신한다면, ac 전원(12)과 다이오드(26) 그리고 인버터(16A) 사이에 개재 회로(intervening circuit)가 존재할 수 있다. 도 1의 예에서는, 부하 트랜지스터(28)의 공통 게이트와 드레인 접속과, 구동 트랜지스터(30)의 소스에 결합된 그라운드 접속 양단에 부분적으로 정류된 ac 전력 파형이 직접적으로 인가된다.

도 3은 반파 트랜지스터 기반 부분 정류 스테이지(14B)에 의해 생성되는 부분적으로 정류된 ac 파형에 의해 전력을 공급받는 인버터 회로(16A)를 도시하는 회로도이다. 도 3에 도시된 바와 같이, 부분 정류 스테이지(14B)는 트랜지스터(34)를 포함한다. 트랜지스터(34)의 게이트 및 드레인은 ac 파워 서플라이(12)의 포지티브 단자에 공통 결합된다. 트랜지스터

(34)의 소스는 부분 정류 스테이지(14B)의 출력 노드를 생성하도록 결합된다. 부분 정류 스테이지(14B)의 출력 노드는 인버터 회로(16A)의 부하 트랜지스터(28)의 게이트와 드레인 양쪽에 결합된다. 따라서, 도 3의 회로는 도 2의 회로에 실질적으로 대응하나, 트랜지스터 기반 부분 정류 스테이지(14B)를 포함한다. 트랜지스터(34)는 박막 전계 효과 트랜지스터(FET)일 수 있고, 비정질 또는 다결정 무기 또는 유기 반도체 재료 또는 이들의 조합에 기초할 수 있다.

다시, 도 2 및 도 3의 인버터(16A) 등의 박막 트랜지스터 기반 로직 회로에 전력을 공급하는데 있어 부분적으로 정류된 파형을 사용하면, 각종 어플리케이션의 만족할 만한 디바이스 성능을 지원할 수 있으며, 회로의 장기 안정성을 향상시킨다. 예를 들어, 인버터(16A)가 부분적으로 정류된 ac 파형에 의해 전력을 공급 받으면, 인버터는 dc 전력을 공급받는 인버터에 비해 만족할만한 성능 특징을 보여줄 수 있다. 또한, 부분적으로 정류된 ac 파형에 의한 인버터(16A)의 동작은 ac-dc 전파 정류 스테이지에 대한 필요성을 없앤다.

도 3에 도시된 바와 같이, 부하 트랜지스터(28)의 게이트 및 드레인은 부분 정류 스테이지(14B)에 의해 생성되는 부분적으로 정류된 ac 파형을 수신하도록 결합된다. 특히, 부하 트랜지스터(28)의 게이트 및 드레인은 둘 다 트랜지스터(34)의 소스에 결합된다. 구동 트랜지스터(30)의 드레인은 부하 트랜지스터(28)의 소스에 결합되고, 구동 트랜지스터의 소스는 그라운드에 결합된다. 신호원(18)은 구동 트랜지스터(30)의 게이트를 구동시키기 위해, 로직 신호를 생성한다.

이에 대한 응답으로, 인버터(16A)는 부하 커패시터(22) 양단의 출력일 수 있는 반전된 출력(20)을 생성한다. 부하 커패시터(22)는 반전된 출력(20)에 존재하는 ac 전압의 일부를 필터링하는 역할을 할 수 있고, 더 깨끗한 출력 로직 신호를 제공한다. 필터링량은 부하 커패시터(22)의 용량과 ac 전력의 주파수에 의존한다. 부하 커패시터(22)는, 인버터(16A)가 하나 이상의 추가의 로직 게이트들에 결합되는 경우에, 출력(20)에 결합된 로직 게이트 내에서 게이트/소스 오버랩에 의해 생성되는 입력 용량에 의해 형성될 수 있다.

게이트/소스 오버랩은 부하 커패시터(22)의 원하는 용량 레벨을 생성하기 위해, 후속 로직 게이트의 구동 트랜지스터의 제조 동안에 제어될 수 있다. 대안적으로, 부하 커패시터(22)는, 특히 출력(20)이 또 다른 로직 게이트를 구동시키지 않는다면, 독립적으로 형성될 수 있다.

일부 실시예들에서는, 부하 트랜지스터(28)는 구동 트랜지스터(30)의 게이트 폭 대 게이트 길이 비보다 크거나 같은 게이트 폭 대 길이 비를 가질 수 있다. 이 경우, 회로의 직류(dc) 전력 공급은, 이득이 감소되기 때문에, NMOS 또는 PMOS 설계를 위한 로직 게이트의 동작의 열화를 초래할 수 있다. 이러한 설계에 기초한 NMOS 또는 PMOS 링 오실레이터는 안정적이지 않다. 부하 트랜지스터(28)의 게이트 폭 대 게이트 길이 비를 구동 트랜지스터(30)의 게이트 폭 대 게이트 길이 비보다 더 크거나 같은 경우에 의해 전체 회로 면적이 감소된다는 부가적인 혜택이 있다.

주목할 만한 것은, 반전된 출력(20)이 부하 커패시터(22)에 의해 필터링될 수 있다고 해도, 인버터(16A)에 인가되는 입력 전력 파형은 통상 아니다. 특히, 부분 정류 스테이지(14B)에 의해 생성되는 부분적으로 정류된 ac 파형은 인버터(16A)에 대한 근본적인 dc 신호를 생성하기에 충분한 정도로 필터링되지 않는다. 오히려, 부분 정류 스테이지(14B)에 의해 생성되는 부분적으로 정류된 파형은 실질적인 ac 성분을 포함한다.

일부 실시예들에서는, 비교적으로 작은 필터링 커패시터가 트랜지스터(34)의 소스와 그라운드 사이에 결합될 수 있으나, 용량은, ac 파워 서플라이(12)에 의해 생성되는 ac 전력 파형의 비정류 부분으로 인해, 통상 부분적으로 정류된 파형의 변동을 완전하게 필터링하기에는 충분치 않다. 특히, ac 파워 서플라이(12)에 의해 생성되는 비정류 네거티브 하프 사이클과 일치하는 부분적으로 정류된 파형의 부분들은 여전히 부분적으로 정류된 파형에 상당한 변동을 제공할 것이다. 이런 방식으로, 전파 또는 반파 정류 스테이지에 통상적으로 제공되는 대형 커패시터가 제거되거나 그 사이즈가 감소되어, 회로 또는 전자 디바이스의 전체 사이즈가 감소될 수 있다.

도 4A, 도 4B 및 도 4C는 ac 전력 파형 및 예시적인 부분적으로 정류된 ac 전력 파형을 개념적으로 도시하는 그레프이다. 도 4A는 ac 파워 서플라이(12)에 의해 생성되는 ac 전력 파형(21)을 도시한다. 도 4A에 도시된 바와 같이, ac 전력 파형은 실질적으로 정현파이고, 포지티브 하프 사이클(23, 25)과 네거티브 하프 사이클(27)을 포함한다. 본 발명에 따르면, 부분 정류 스테이지(14)는 ac 전력 파형(21)을 부분적으로 정류하여, 예컨대, 도 4B 또는 도 4C에 도시된 바와 같은, 부분적으로 정류된 ac 파형을 생성한다.

도 4B의 예에서는, 부분 정류 스테이지(14)가 충분한 용량성 필터링이 없이, 본래 반파 정류에 의해서 부분적으로 정류된 ac 전력 파형(29A)을 생성하여, 근본적인 dc 신호를 생성한다. 대신에, 부분적으로 정류된 ac 전력 파형(29A)은 포지티브 하프 사이클(31) 및 포지티브 하프 사이클(33)을 포함하나, 임의의 네거티브 하프 사이클을 제거하여 기준 전압 레벨로 떨

어진다. 이에 따라서, 도 4B의 예에 따르면, 부분 정류 스테이지(14)는 실질적으로 용량성 필터링을 포함하지 않을 수 있다. 그 결과, 부분적으로 정류된 파형(29A)은, 본질적으로, 하프 사이클(31, 33) 내에, ac 전력 파형(21)의 포지티브 하프 사이클(23, 25)의 파형 특성을 유지한다. 라인(130)은 평균 dc 전압을 나타내고, 회로에 전력을 공급하기에는 불충분하다.

도 4C의 예에서는, 부분 정류 스테이지(14)는 포지티브 하프 사이클(35, 37)을 갖는 부분적으로 정류된 ac 전력 파형(29B)을 생성한다. 또한, 부분 정류 스테이지(14)는 각각의 하프 사이클(35, 37)에 후속하는 테일 익스포넨셜 테일 오프(exponential tail off)(39, 41)를 생성하는 제한된 용량성 필터링량을 포함할 수 있다. 하프 사이클(35 및 37)의 피크는 회로에 전력을 공급하기에 충분한 전압을 나타낸다. 일부 실시예들에서는, 용량성 필터링이 부분 정류 스테이지((14)의 출력과 그라운드 사이에 배치된 커페시터에 의해 제공될 수 있다. 도 4C에 도시된 바와 같이, 용량은 근본적인 dc 전력 신호를 생성하기에는 불충분하다. 오히려, 부분적으로 정류된 파형(29B)은 ac 파워 서플라이(12)에 의해 생성되는 원래의 ac 파워 서플라이 파형(21)(도 4A)의 실질적인 ac 성분을 유지할 수 있다. 라인(131)은 평균 dc 전압을 나타내며, 회로에 전력을 공급하기에는 불충분하다.

일부 어플리케이션의 경우, 부분적으로 정류된 ac 파형의 전력을 로직 회로(16)에 공급하면, 회로에 전력을 공급하는데 충분한 dc 성분을 생성하는 전파 또는 반파 ac-dc 정류 스테이지가 필요 없게 된다. 대신에, 전원은 비교적 단순한 부분 정류 스테이지(14)를 포함할 수 있다. 도 2 및 도 3에 도시된 바와 같이, 부분 정류 스테이지(14)는, 대형 필터링 커페시터에 대한 필요 없이, 다이오드, 트랜지스터 등에 의해 실현될 수 있다. 이런 방식으로, 본 발명은 부분적으로 정류된 ac 전력 파형에 의해 전력을 공급받는 로직 회로를 갖는 컴포넌트의 제조 시간, 소요 경비(expense), 가격(cost) 및 사이즈를 저감할 수 있다.

부분적으로 정류된 ac 전력 파형에 의해 전력을 공급받는 로직 회로는 각종의 전자 디바이스에 사용될 수 있다. 일 예로서, 이러한 로직 회로는, ac 파형이 무선 주파수 커플링에 의해 유도되는 무선 주파수(RFID) 태그에 관한 어플리케이션에 특히 유용할 수 있다. ac 파형은 RFID 태그가 갖는 전자 로직 회로의 일부 또는 전부에 전력을 제공하도록 부분적으로 정류될 수 있다. 반파 정류기에 자주 사용되는 어느 정도 크기가 되는 커페시터를 포함하여, 전파 또는 반파 정류기에 통상 요구되는 회로를 제거함으로써, RFID 태그의 사이즈가 상당히 줄어들 수 있다. 다른 종류의 전자 디바이스에서도 유사한 사이즈 감소가 얻어질 수 있다.

도 5는 반파 다이오드 기반 부분 정류 스테이지(14A)에 의해 생성되는 부분적으로 정류된 ac 파형에 의해 전력을 공급받는 박막 트랜지스터 기반 NAND 게이트 회로(38)를 도시하는 회로도이다. 도 5에 도시된 바와 같이, NAND 게이트(40)는 부하 트랜지스터(28) 및 구동 트랜지스터(30A, 30B)를 포함한다. 부하 트랜지스터(28)의 게이트 및 드레인은 다이오드(26)를 포함하는 부분 정류 스테이지(14A)의 출력에 결합된다.

제1 구동 트랜지스터(30A)의 드레인은 부하 트랜지스터(28)의 소스에 결합된다. 제2 구동 트랜지스터(30B)의 드레인은 제1 구동 트랜지스터(30A)의 소스에 결합된다. 제2 구동 트랜지스터(30B)의 소스는 그라운드에 결합된다. 제1 및 제2 신호원(18A, 18B)은 구동 트랜지스터(30A, 30B)의 게이트들을 각각 구동시킨다. 이에 응답하여, 트랜지스터(28, 30A, 30B)는, 논리적 NAND 출력(20)을 생성하는 NAND 게이트(40)를 형성한다.

도 5의 NAND 회로(40)는 다이오드(26)에 의해 생성되는 부분적으로 정류된 ac 전력 파형에 응답하여 동작한다. 특히, 부분적으로 정류된 ac 전력 파형은 NAND 게이트(40)에 직접적으로 결합된다. 일부 실시예들에서는, 부하 커페시터는 출력(20) 양단에 결합될 수 있다. 부하 커페시터는 독립적으로 형성되거나 NAND 게이트(40)의 출력(20)에 의해 구동되는 로직 게이트의 입력 용량에 의해 실현될 수 있다. 또한, 결과적인 용량이 근본적인 dc 전력 신호를 생성하기에 불충분하다면, 다이오드(26)의 캐소드와 그라운드 사이에 필터링 커페시터가 배치될 수 있다.

도 6은 반파 트랜지스터 기반 부분 정류 스테이지(14B)에 의해 생성되는 부분적으로 정류된 ac 파형에 의해 전력을 공급받는 NAND 게이트 회로(42)를 도시하는 회로도이다. NAND 게이트 회로(42)는 NAND 게이트(40)를 포함하며, 도 5의 NAND 회로(38)에 실질적으로 대응하나, 트랜지스터(34)를 갖는 트랜지스터 기반 부분 정류 스테이지(14B)를 포함한다.

트랜지스터 기반 부분 정류 스테이지(14B)는 도 3의 부분 정류 스테이지(14B)와 동일할 수 있다. 도 5의 예에서와 같이, 부하 커페시터는 도 6의 회로(42)의 출력(20) 양단에 결합될 수 있다. 또한, 결과적인 용량이 근본적인 dc 전력 신호를 생성하기에 불충분하다면, 부분 정류 스테이지(14B)의 출력과 그라운드 사이에 필터링 커페시터가 배치될 수 있다.

도 7은 부분적으로 정류된 ac 파형에 의해 전력을 공급받는 NOR 게이트(46)를 갖는 박막 트랜지스터 기반 NOR 게이트 회로(44)를 도시하는 회로도이다. 도 7은 부분 정류 스테이지(14)에 의해 생성되는 부분적으로 정류된 ac 파형으로 동작

하는 박막 트랜지스터 기반 로직 회로의 또 다른 예를 나타낸다. 도 7에 도시된 바와 같이, 트랜지스터(28, 50A, 50B)는 NOR 게이트(46)를 형성한다. 제1 및 제2 구동 트랜지스터(50A, 50B)의 드레인들은 부하 트랜지스터(28)의 소스 및 출력(20)에 결합된다.

제1 및 제2 구동 트랜지스터들(50A, 50B)의 소스들은 그라운드에 결합된다. 제1 및 제2 신호원(48A, 48B)은 구동 트랜지스터(50A, 50B)의 게이트들을 각각 구동시킨다. 이에 응답하여, NOR 게이트(46)는 논리적인 NOR 출력(20)을 생성시킨다. NOR 회로(46)는, 부분 정류 스테이지(14)에 의해 전달되는 부분적으로 정류된 ac 전력 파형에 응답하여 동작한다. 일부 실시예들에서는, 부하 커패시터가 논리적인 NOR 출력(20)의 양단에 결합될 수 있다. 다시, 부하 커패시터는 독립적으로 형성되거나 NOR 회로(44)의 출력(20)에 의해 구동되는 로직 게이트의 입력 용량에 의해 실현될 수 있다.

도 8 및 도 9는 ac 전력을 공급받는 박막 트랜지스터 기반 링 오실레이터 회로(51, 53)를 각각 도시하는 회로도이다. 링 오실레이터 회로(51 및 53)는 가요성 기판 상에 형성될 수 있는 OTFT에 기초한, 예컨대 인버터 스테이지를 포함하는 부분적으로 정류된 ac 전력 파형에 의해 전력을 공급받는 로직 게이트들을 이용하여 구현될 수 있는 또 다른 회로의 예이다. 도 8 및 도 9에 도시된 바와 같이, 링 오실레이터 회로(51 및 53)는 직렬로 배치된 홀수의 인버터 스테이지를 포함한다. 도 8 및 도 9의 예에서, 링 오실레이터 회로(51 및 53)는, 부하 트랜지스터(54A-54G) 및 구동 트랜지스터(56A-56G)를 각각 갖는 7개의 인버터 스테이지(52A-52G)를 각각 포함한다.

링 오실레이터 회로(51 및 53) 내의 각각의 트랜지스터(54 및 56)는 부분적으로 정류된 ac 파형에 의해 전력을 공급받는 박막 전계 효과 트랜지스터이다. 예를 들어, ac 전원(12)은 부분 정류 스테이지(14B)에 ac 전력을 전달한다. 도 8 및 도 9의 예에서, 부분 정류 스테이지(14B)는, 다이오드 기반 부분 정류 스테이지 또는 다른 구성이 이용될 수 있지만, 트랜지스터 기반 부분 정류 스테이지이다. 부분 정류 스테이지(14B) 내의 트랜지스터(34)의 소스는 제1 인버터 스테이지(52A)의 부하 트랜지스터(54A)의 공통 게이트-드레인 노드를 구동시키도록 결합된다. 도 8의 예에서, 필터링 커패시터(55)는 부분 정류 스테이지(14B)의 출력과 그라운드 사이의 링 오실레이터 회로(51A)에 선택적으로 제공될 수 있다. 도 9에서, 필터링 커패시터(55)는 링 오실레이터 회로(51B)에 제공되지 않는다.

도 8 및 도 9의 예에서, 각각의 인버터 스테이지(52A-G)는 각각의 부하 커패시터(58A-58G) 양단에 선택적으로 결합된 출력을 갖는다. 예를 들어, 인버터 스테이지(52A)의 출력은 부하 커패시터(58B)의 양단에 결합되고, 인버터 스테이지(52G)의 출력은 부하 커패시터(58A)의 양단에 결합될 수 있다. 다른 실시예에서는, 부하 커패시터(58)는 생략될 수 있다. 각각의 커패시터(58)는 각각의 인버터 스테이지의 출력에 의해 구동되는 후속 인버터 스테이지(52)의 구동 트랜지스터(56) 내의 게이트/소스 오버랩에 의해 생성되는 입력 용량에 의해 형성될 수 있다.

최종 인버터 스테이지(52G)의 출력(60)은 제1 인버터 스테이지(52A) 내의 구동 트랜지스터(56A)의 게이트에 결합되어, 피드백을 제공한다. 도 8 및 도 9의 링 오실레이터 회로(51, 53)는 부분 정류 스테이지(14B)에 의해 전달되는 부분적으로 정류된 ac 파워 서플라이 파형에 응답하여 동작한다. 동작 중에, 링 오실레이터 회로(51)는 클럭 신호를 제공한다. 예를 들어, 링 오실레이터 회로(51, 53) 내의 각 인버터 스테이지(52)의 출력을 탭핑하여 원하는 위상을 갖는 클럭 신호를 제공할 수 있다.

일반적으로, 링 오실레이터(51, 53)에 의해 생성된 출력 파형은 인버터 스테이지(52)의 수에 의존하는 주파수와, 개별의 인버터 스테이지에 의해 생성되는 전달 지연을 가질 것이다. 전달 지연은 링 오실레이터(51, 53)에 인가되는 부분적으로 정류된 ac 파형의 전압파, 반도체 재료의 이동도에 역으로 관련되며, 인버터 스테이지(52)에 존재하는 임의의 적용 가능한 기생 또는 외부 용량에 비례한다.

높은 ac 파워 서플라이 주파수에 의해, 링 오실레이터 회로(51, 53) 등의 박막 트랜지스터 회로의 동작이 가능할 수 있다. 회로(51, 53)에 실질적으로 따르는 기능 링 오실레이터 회로는, 예를 들면, 수백 kHz에서 6MHz 또는 그 이상의 정도의 ac 파워 서플라이 주파수로 동작할 수 있다. 반도체 이동도가 증가함에 따라, 10MHz보다 큰 ac 파워 서플라이 주파수로, 여기서 설명하는 바와 같은 부분적으로 정류된 ac 전력 파형에 의해 전력을 공급받는 링 오실레이터 회로의 이용을 예상하는 것이 적당할 수 있다.

도 10은 RFID 태그/판독기 시스템(66) 내의 부분적으로 정류된 ac 전력 파형에 의해 전력을 공급받는 박막 트랜지스터 기반 회로의 어플리케이션을 도시하는 블록도이다. ac 전력 공급 박막 트랜지스터 기반 회로의 사용은, 설명하는 바와 같이, 여러 가지 이유로 RFID 태그에서 특히 바람직할 수 있다. 도 10에 도시된 바와 같이, RFID 태그 시스템(66)은 판독기 유닛(68) 및 RFID 태그(70)를 포함할 수 있다.

판독기 유닛(68)은 무선 주파수(RF) 소스(74) 및 판독기(72)를 포함할 수 있다. RF 소스(74)는 RFID 태그(70)에 RF 에너지를 전송하여 전력원을 제공한다. 이런 방식으로 RFID 태그(70)는 배터리와 같은 독립된 파워 서플라이를 가지고 있을 필요가 없다. 대신에 RFID 태그(70)는 판독기 유닛(68)과 RFID 태그 간의 와이어리스 에어 인터페이스 양단에서 전력이 공급된다. 판독기 유닛(68)이, 사실상, RF 에너지를 송수신하는 안테나로서 역할을 하는 인덕터(76)를 포함한다.

또한 도 10에 도시된 바와 같이, RFID 태그(70)는 ac 전원(73)을 포함할 수 있다. 설명하는 바와 같이, ac 전원(73)은 판독기 유닛(68)에 의해 전송되는 RF 에너지를 RFID 태그(70)의 박막 트랜지스터 회로에 전달하기 위한 ac 전력으로 변환하는 역할을 할 수 있다. RFID 태그(70)는 수신기로서 역할을 하는 인덕터(78)를 통해 판독기 유닛(68)으로부터 RF 에너지를 수신할 수 있다.

인덕터(78)는 판독기 유닛(68)에 의해 전송되는 RF 에너지로부터 흡수되는 RF 에너지에 기초한 ac 전력 파형을 ac 전원(73)에 제공하도록 무선 주파수(RF) 에너지 커플링 디바이스로서 역할을 한다. 커패시터(미도시)는, 원한다면, 인덕터(78)와 병렬로 제공될 수 있다.

부분 정류 스테이지(80)는 인덕터(78)로부터 ac 파형을 수신하고, 부분적으로 정류된 ac 파형을 생성하여, RFID 태그(70) 내의 디지털 로직 회로에 전력을 공급한다. RFID 태그(70)는 또한 변조 출력 인버터(82), 출력 버퍼 회로(84), 제어 로직(86), 클럭 회로(88) 및 데이터 회로(90)를 더 포함하며, 그 중 하나 이상은 박막 트랜지스터 회로의 구성에 의해 형성될 수 있다.

클럭(88)은 제어 로직 회로(86)를 구동하여 데이터 회로(90)로부터의 데이터를 출력하며, 식별 코드가 있는 복수의 데이터 라인을 포함할 수 있다. 출력 버퍼(84)는 제어 로직(86)으로부터의 출력을 버퍼링한다. 다음으로, 변조 인버터(82)는 인덕터(76, 78)를 통해 판독기 유닛(68)에 의한 해석을 위해 버퍼링된 출력을 변조한다. 예를 들어, 변조 인버터(82)는 인덕터(78) 양단에 인가되는 신호를 변조함으로써 정보를 이송한다.

도 11은 도 10의 RFID 태그/판독기 시스템(66)을 또한 도시하는 회로도이다. 도 11에 도시된 바와 같이, RF 소스(74)는 인덕터(76)를 통해 ac 출력 신호를 전송하는 ac 생성기(92)를 포함할 수 있다. 일부 어플리케이션에서는, ac 생성기(92)는 약 125 kHz의 주파수에서 약 0 내지 5 amps의 출력을 갖는 정현파 전류원의 형태를 취할 수 있다.

인덕터(76 및 78)는 RF 소스와 RFID 태그(70) 사이의 RF 에너지의 전자기 결합을 위한 트랜스포머를 형성한다. 저항기

$$f = \frac{1}{2\pi\sqrt{LC}}$$

(94)는 전류를 제한하도록 선택된다. 커패시터(96)는 전원(73) 내에 인덕터(78)와 병렬 배치되어, 다른 전원의 주파수를 조절(govern)하는 병렬 공진 탱크를 형성한다.

여기서, L은 인덕터(78)의 인덕턴스이고, C는 커패시터(96)의 용량이다.

50μH의 인덕턴스와 32nF의 용량을 가지고, 인덕터(78) 및 커패시터(96)는 약 125KHz의 공진 주파수를 생성한다. 따라서, 본 예에서는, 전원(73)의 출력이 약 125kHz의 주파수를 갖는 정현파 파형이다. 인덕터(78)에 의해 생성된 이 파형은 부분 정류 스테이지(80)에 의해 부분적으로 정류되어, 전원(73)의 출력으로서 부분적으로 정류된 ac 전력 파형을 생성한다. 그 다음, 부분적으로 정류된 ac 전력 파형이, 단자 POWER 및 COMMON으로 도 11에 표시된 클럭 회로(88), 제어 로직(86), 데이터 라인(90), 출력 버퍼(84), 및 변조 인버터(82)에 인가된다.

도 11은 n 비트 식별 코드를 갖는 RFID 태그(70)를 도시한다. 설명을 쉽게 하기 위해, RFID 태그(70)는 데이터 라인(70)에 의해 특정된 7 비트 식별 코드를 갖는다. 많은 어플리케이션에서, RFID 태그(70)는 훨씬 더 큰 식별 코드, 예컨대, 31비트, 63비트 또는 127비트 코드를 가질 수 있다. 일부 실시예들에서는, 선택된 데이터 라인(90)들이 스타트 비트 식별, 데이터 스트림 동기화 및 에러 점검에 사용되는 정보를 가질 수 있다. 도 11의 예에서는, 클럭 회로(88)는 피드백 루프에 배열된 7 개의 일련의 인버터 스테이지들에 의해 형성된 링 오실레이터이다.

도 11의 링 오실레이터는 도 8 및 도 9의 링 오실레이터(51 또는 53)와 유사할 수 있다. 2개의 연속한 인버터들의 출력들은 제어 로직(86)에 제공된 각각의 NOR 게이트에 인가된다. 이런 방식으로, 7개의 NOR 게이트를 이용하여 링 오실레이터에 의해 생성되는 각각의 클럭 사이클 내의 7개의 웨일스 시퀀스를 생성한다. 제어 로직(86) 내의 NOR 게이트들의 수는 변할 수 있다. 다시, 이 구성은, 원리적으로는, 더 큰 비트 수, 예컨대 n=31, 63 또는 127로 연장될 수 있다.

데이터 라인(90)과 직렬로 도시된 스위치들은 일단이 각각의 NOR 게이트 출력에 접속된다. 스위치가 닫히면, 각각의 데이터 라인은 NOR 게이트 출력을 그라운드에 결합시키고, 스위치가 열리면, NOR 게이트 출력이 제어 로직(86) 내의 7-입력 OR 게이트로의 입력들 중의 하나로서 결합된다.

도 11의 예에서는, (왼쪽에서 오른쪽으로) 제2 및 제4 데이터 라인의 스위치가 닫혀 있다. 그 결과, 데이터 라인(90)은 7비트 식별 코드 "1010111"을 저장한다. 스위치는, 예를 들면, NOR 게이트 출력에서 그라운드까지 연장되는 메탈 라인으로부터 만들어질 수 있다. 그라운드에의 전기 접속은 오픈 스위치를 생성하기 위한 제조 중에 의도적으로 깨지거나 접속될 수 있어, 고유의 식별 코드를 RFID 태그(70)의 데이터 라인(90)으로 인코드한다. 전기 접속은, 예를 들면, 레이저 에칭, 기계적 스크라이빙 또는 전기적 퓨징 등과 같은 각종 제조 기술에 의해 절단될 수 있다.

제어 로직(86) 내의 7-입력 OR 게이트의 출력은 출력 버퍼(84)의 버퍼 증폭기들의 캐스케이드에 인가되어, 로직 회로의 출력 임피던스를 변조 인버터(82)의 입력 임피던스에 일치시키는 것을 돋는다. 출력 버퍼(84)의 버퍼 증폭기들의 출력은 변조 인버터(76)의 입력에 인가된다. 구체적으로, 신호 TAG OUTPUT은 변조 인버터(82)와 관련된 구동 트랜지스터의 게이트에 인가된다. 그런 다음, 변조 인버터(82)는 인덕터(78) 및 커패시터(96)에 의해 형성된 텡크의 Q를 변조하여, 반송파 신호의 진폭 변조를 제공한다. 이런 방식으로, 수신된 버퍼 출력이 판독기 유닛(68)에 이송되어, 판독기(72)가 식별 코드를 판독할 수 있게 된다. 특히, 판독기(72)는 인덕터(76)를 통해 L<sub>tap</sub>에서 수신된 신호를 처리한다.

도 12는 도 10의 RFID 태그/판독기 시스템(68)과 관련된 판독기(72)를 또한 도시하는 회로도이다. 판독기(72)는, L<sub>tap</sub>을 통해, 클럭 회로(88)의 주파수에 따라 1kHz 정도일 수 있는, TAG OUTPUT 신호에 의해 변조된, 예컨대 125kHz의 반송파 신호를 포함하는 신호를 수신한다. 저접합 용량 신호 다이오드(102)는 신호를 복조하는데 이용된다. 로우 패스 필터부(98)는 반송파 주파수를 제거하고, 인덕터(104), 커패시터(106), 저항기(108), 인덕터(110), 커패시터(112) 및 저항기(114)를 포함할 수 있다. 증폭기 스테이지(100)는 비반전 구성의 증폭기(116)를 포함하며, 저항기(118) 및 피드백 저항기(120)가 반전 입력에 결합된다.

도 13은 액정(LC) 표시 소자(124)를 구동시키기 위해 부분적으로 정류된 ac 전력 파형에 의해 전력을 공급받는 박막 트랜지스터 기반 인버터 회로(122)를 도시하는 회로도이다. 도 13의 예에서는, 인버터 회로(122)는 실질적으로 도 2 및 도 3의 인버터 회로(16A)에 따른다. 그러나, 인버터(16)의 출력은 액정 표시 소자(124)를 구동한다. 특히, 액정 표시 소자(124)의 한 전극은 부하 트랜지스터(28)의 소스 및 구동 트랜지스터(30)의 드레인에 결합된다. 액정 표시 소자(124)의 다른 전극은 그라운드에 결합된다. 도 13에 도시된 바와 같이, 인버터 회로(16)는 부분 정류 스테이지(14)에 의해 전력을 공급받고, 따라서 부하 트랜지스터(28)의 공통 게이트/드레인 접속에서, 부분적으로 정류된 ac 전력 파형을 수신한다. 풀 LCD(full LCD)를 구동하기 위해, 인버터(16)와 유사한 인버터가 LCD의 각 엘리먼트에 제공될 수 있다.

도 14는 LED(light emitting diode)(128)를 구동시키는 ac 전력을 공급받는 박막 트랜지스터 기반 인버터 회로(126)를 도시하는 회로도이다. 인버터 회로(16)는 실질적으로 도 2 및 도 3의 인버터 회로(16A)에 따른다, LDE(128)를 구동시킨다. LED(128)의 캐소드는 부하 트랜지스터(28)의 소스 및 구동 트랜지스터(1308)의 드레인에 결합되며, LED의 애노드는 그라운드에 결합된다.

본 발명은 많은 장점을 제공할 수 있다. 예를 들어, 부분적으로 정류된 ac 파형에 의해 전력을 공급받는 로직 회로, 및 특히 OTFT 기반 로직 회로는 dc 전력을 공급받는 박막 트랜지스터 회로에 비해 만족할만한 성능을 보여줄 수 있다. 링 오실레이터이 경우, 예를 들면, 부분적으로 정류된 ac 파형에 의해 전력을 공급받는 박막 트랜지스터 회로가 dc 전력을 공급받는 박막 트랜지스터 회로에 비해 만족할만한 발진 진폭을 유지할 수 있다.

장점으로서, 로직 회로에 전력을 공급하는 데 있어 부분적으로 정류된 ac 전력 파형을 이용하면, 회로에 dc 전력을 전달하기 위한 많은 어플리케이션에서 요구되는 필터링 커패시터를 갖는 전파 정류기 커포넌트 또는 반파 정류기 커포넌트에 대한 필요성을 없앨 수 있다. 따라서, 종래의 정류기 커포넌트에 대한 필요성을 없앰으로써, 부분적으로 정류된 ac 전력을 사용하여 박막 트랜지스터 회로를 구비한 커포넌트의 제조 시간, 소요 경비, 복잡도, 사이즈를 감소시킬 수 있다.

특정한 예로서, RFID 태그의 경우, ac 전력을 공급받는 박막 회로를 이용하면, 다이오드 또는 트랜지스터 브릿지를 포함하는 ac-dc 정류기 스테이지와 관련된 전형적인 커포넌트 및 대형 필터링 커패시터를 없앰으로써 태그의 가격 및 사이즈를 상당히 줄일 수 있다. 정류기 스테이지의 복잡도를 감소시킴으로써, 부분적으로 정류된 ac 파형에 의해 전력을 공급받는 박막 로직 회로는, RFID 태그의 설계 및 제조에 있어 상당한 가격 및 사이즈 절감을 가져올 수 있다.

부분적으로 정류된 ac 파형에 의해 전력을 공급받는 로직 회로 형성에 있어 유용한 박막 트랜지스터는, 여기에 설명하는 바와 같이, 다양한 형태를 취할 수 있으며, 다양한 제조 프로세스를 이용하여 제조될 수 있다. 예를 들어, 박막 트랜지스터는 유기 반도체 재료, 무기 반도체 재료 또는 이들의 조합을 포함할 수 있다. 일부 어플리케이션에서는, 유기 및 무기 반도체 재료를 이용하여 CMOS 박막 트랜지스터 회로를 형성할 수 있다.

여기에서 설명하는 부분적으로 정류된 ac 파형에 의해 전력을 공급받는 로직 회로를 형성하는데 유용한 박막 트랜지스터들은, 제한 없이, 미국 특허 6,433,359, 6,768,132 및 6,616,609; 2003년 11월 6일자로 공개된 미국 특허 공보 2003/0207505, 2003년 6월 5일자로 공개된 2003/0102471 A1, 2003년 8월 14일자로 공개된 2003/0150384 A1 및 2003/0152691 A1에 기재되어 있는 기술에 따라 제조된 박막 트랜지스터를 포함할 수 있다.

본 발명의 사상 및 범주 내에서 벗어나지 않고 다양한 변형이 만들어질 수 있다. 예를 들면, 부분 정류 스테이지의 특정한 예를 설명하였지만, 다른 부분 정류 스테이지를 제공하여 유사한 부분적인 정류 결과를 얻을 수 있다. 또한, 각종 로직 회로는 로직 회로에 전력을 제공하기 위한 부분적으로 정류된 파형을 이용하는 것으로부터 혜택을 받을 수 있다. 따라서, 여기에 설명하는 예들은 본 발명의 범주를 제한하는 것으로서 취급되서는 않된다. 이러한 실시예들 및 다른 실시예들은 다음의 특허 청구범위의 범주 내에 있다.

### 도면의 간단한 설명

도 1은 부분적으로 정류된 ac 파형에 의해 전력을 공급받는 디지털 로직 회로를 도시하는 회로도.

도 2는 반파 다이오드 기반 부분 정류 스테이지에 의해 생성된 부분적으로 정류된 ac 파형에 의해 전력을 공급받는 인버터 회로를 도시하는 회로도.

도 3은 반파 트랜지스터 기반 부분 정류 스테이지에 의해 생성된 부분적으로 정류된 ac 파형에 의해 전력을 공급받는 인버터 회로를 도시하는 회로도.

도 4A, 도 4B 및 도 4C는 ac 전력 파형 및 예시적인 부분적으로 정류된 ac 전력 파형을 개념적으로 도시하는 그레프.

도 5는 반파 다이오드 기반 부분 정류 스테이지에 의해 생성된 부분적으로 정류된 ac 파형에 의해 전력을 공급받는 NAND 게이트 회로를 도시하는 회로도.

도 6은 반파 트랜지스터 기반 부분 정류 스테이지에 의해 생성된 부분적으로 정류된 ac 파형에 의해 전력을 공급받는 NAND 게이트 회로를 도시하는 회로도.

도 7은 부분적으로 정류된 ac 파형에 의해 전력을 공급받는 NOR 게이트 회로의 회로도.

도 8은 필터링 커패시터를 갖는 반파 트랜지스터 기반 정류기 스테이지에 의해 생성된 부분적으로 정류된 ac 파형에 의해 전력을 공급받는 박막 트랜지스터 기반 링 오실레이터 회로를 도시하는 회로도.

도 9는 필터링 커패시터가 없는, 반파 트랜지스터 기반 정류기 스테이지에 의해 생성된 부분적으로 정류된 ac 파형에 의해 전력을 공급되는 박막 트랜지스터 기반 링 오실레이터 회로를 도시하는 회로도.

도 10은 RFID 태그/판독기 시스템에서의 ac 전력을 공급받는 박막 트랜지스터 회로의 어플리케이션을 도시하는 블록도.

도 11은 도 10의 RFID 태그/판독기 시스템을 또한 도시하는 회로도.

도 12는 도 10의 RFID 태그/판독기 시스템과 관련된 판독기를 또한 도시하는 회로도.

도 13은 액정 표시 소자를 구동하도록 부분적으로 정류된 ac 파형에 의해 전력을 공급받는 인버터 회로를 도시하는 회로도.

도 14는 LED(a light emitting diode)를 구동하도록 부분적으로 정류된 ac 파형에 의해 전력을 공급받는 인버터 회로를 도시하는 회로도.

도면

도면1

도면2

도면3

도면4A

도면4B

도면4C

도면5

도면6

도면7

도면8

도면9

도면10

도면11

도면12

도면13

도면14