(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2016년09월30일

(11) 등록번호 10-1661787

(24) 등록일자 2016년09월26일

- (51) 국제특허분류(Int. Cl.)

*HO4N 5/765* (2016.01) *HO4N 7/173* (2011.01)

(21) 출원번호 10-2011-7022982

(22) 출원일자(국제) 2011년02월02일

심사청구일자 2015년01월27일

(85) 번역문제출일자 2011년09월30일

(65) 공개번호 10-2012-0130121

(43) 공개일자 2012년11월29일

(86) 국제출원번호 PCT/JP2011/052180

(87) 국제공개번호 WO 2011/099407

국제공개일자 2011년08월18일

(30) 우선권주장

JP-P-2010-029545 2010년02월12일 일본(JP)

(뒷면에 계속)

## (56) 선행기술조사문헌

JP2000235545 A\*

JP2003511757 A\*

US20090178097 A1\*

JP2006309771 A

\*는 심사관에 의하여 인용된 문헌

- (73) 특허권자

소니 주식회사

일본국 도쿄도 미나토구 코난 1-7-1

(72) 발명자

타오 아카히코

일본국 도쿄도 미나토구 코난 1-7-1 소니 주식회사

사내

사이트 타케히코

일본국 도쿄도 미나토구 코난 1-7-1 소니 주식회사

사내

(뒷면에 계속)

(74) 대리인

최달용

전체 청구항 수 : 총 21 항

심사관 : 이병우

## (54) 발명의 명칭 전자 기기 및 접속 외부 기기의 디지털 인터페이스 판별 방법

**(57) 요약****과제**

접속 외부 기기의 디지털 I/F를 회로로 판별하고, 데이터 전송부의 동작을 접속 외부 기기의 디지털 I/F에 맞도록 전환 가능하게 한다.

(뒷면에 계속)

**대표도**

해결 수단

싱크 기기(120)의 제어부(123)는, 판별부(124)를 포함하고 있다. 이 판별부(124)는, 이 싱크 기기(120)에 소스 기기(110)가 접속되어 있는지, 소스 기기(110)의 데이터 송신부(112)의 디지털 I/F가 HDMI 규격인지 신규격인지 등을 판별한다. 제어부(123)는, 데이터 수신부(122)가 HDMI 규격 및 신규격의 쌍방의 디지털 I/F에 대응하고 있는 경우, 판별부(124)의 판별 결과에 의거하여, 소스 기기(110)의 데이터 송신부(112)의 디지털 I/F에 대응한 동작을 행하도록, 데이터 수신부(122)의 동작을 전환한다. HDMI 및 신규격의 디지털 I/F로 동작하는 외부 기기 를 접속하기 위한 커넥터부를 겸용할 수 있고, 비용면, 스페이스면에서 유리하게 된다.

(72) 발명자

**하야시 토시히데**일본국 도쿄도 미나토구 코난 1-7-1 소니 주식회사

내**이치무라 켄**일본국 도쿄도 미나토구 코난 1-7-1 소니 주식회사

내

(30) 우선권주장

JP-P-2010-044778 2010년03월01일 일본(JP)

JP-P-2010-067089 2010년03월23일 일본(JP)

## 명세서

### 청구범위

#### 청구항 1

복수의 핀을 갖는 커넥터부를 구비하고,

제1의 디지털 인터페이스로 동작하는 외부 기기가 상기 커넥터부에 접속될 때에는 상기 복수의 핀 중 제1의 수의 핀이 사용되고, 제2의 디지털 인터페이스로 동작하는 외부 기기가 접속될 때에는 상기 복수의 핀 중 상기 제1의 수보다 적은 제2의 수의 핀이 사용되고,

상기 복수의 핀 중, 상기 제2의 디지털 인터페이스로 동작하는 외부 기기가 상기 커넥터부에 접속될 때에는 사용되지 않는 소정의 핀의 전압 또는 전류의 상태에 의거하여, 상기 커넥터부에 접속되어 있는 외부 기기의 디지털 인터페이스가 상기 제1의 디지털 인터페이스인지 상기 제2의 디지털 인터페이스인지 판별하는 디지털 인터페이스 판별부와,

상기 커넥터부에 접속되는 데이터 전송부가, 상기 디지털 인터페이스 판별부에서 판별된 디지털 인터페이스로 동작하도록 전환 제어하는 제어부를 또한 구비하고,

상기 디지털 인터페이스 판별부는,

상기 제1의 디지털 인터페이스로 동작하는 외부 기기가 접속되는 경우에 차동 신호가 입력되고, 상기 제2의 디지털 인터페이스로 동작하는 외부 기기가 접속되는 경우에 차동 신호가 입력되지 않는 한 쌍의 핀에 주목하고,

상기 제2의 디지털 인터페이스로 동작하는 외부 기기가 접속되는 경우에 상기 한 쌍의 핀이 단락 또는 제1의 저항을 통하여 접속되고, 상기 한 쌍의 핀의 한쪽의 핀은 제2의 저항을 통하여 소정 전압으로 풀업되고, 상기 한 쌍의 핀의 다른 쪽의 핀은 접지된 상태에서, 상기 한쪽의 핀의 전압을, 상기 소정 전압을 상기 제1의 저항 및 상기 제2의 저항으로 분압하여 얻어지는 전압보다도 높은 전압과 비교한 결과에 의거하여, 상기 커넥터부에 접속되어 있는 외부 기기의 디지털 인터페이스가 상기 제1의 디지털 인터페이스인지 상기 제2의 디지털 인터페이스인지를 판별하는 것을 특징으로 하는 전자 기기.

#### 청구항 2

제1항에 있어서,

상기 제2의 디지털 인터페이스로 동작하는 외부 기기가 접속되는 경우에 상기 한 쌍의 핀이 단락 또는 상기 제1의 저항을 통하여 접속되는 상태는, 상기 외부 기기를 상기 커넥터부에 접속하기 위한 케이블의 플러그 내에서 행하여지는 것을 특징으로 하는 전자 기기.

#### 청구항 3

제1항에 있어서,

상기 커넥터부에의 케이블의 접속을 판별하는 접속 판별부를 또한 구비하고,

상기 디지털 인터페이스 판별부는, 상기 접속 판별부에서 상기 커넥터부에 상기 케이블이 접속된 것이 판별된 후에, 상기 커넥터부에 접속되어 있는 외부 기기의 디지털 인터페이스가 상기 제1의 디지털 인터페이스인지 상기 제2의 디지털 인터페이스인지를 판별하는 것을 특징으로 하는 전자 기기.

#### 청구항 4

복수의 핀을 갖는 커넥터부를 구비하고,

제1의 디지털 인터페이스로 동작하는 외부 기기가 상기 커넥터부에 접속될 때에는 상기 복수의 핀 중 제1의 수의 핀이 사용되고, 제2의 디지털 인터페이스로 동작하는 외부 기기가 접속될 때에는 상기 복수의 핀 중 상기 제1의 수보다 적은 제2의 수의 핀이 사용되고,

상기 복수의 핀 중, 상기 제2의 디지털 인터페이스로 동작하는 외부 기기가 상기 커넥터부에 접속될 때에는 사

용되지 않는 소정의 핀의 전압 또는 전류의 상태에 의거하여, 상기 커넥터부에 접속되어 있는 외부 기기의 디지털 인터페이스가 상기 제1의 디지털 인터페이스인지 상기 제2의 디지털 인터페이스인지를 판별하는 디지털 인터페이스 판별부와,

상기 커넥터부에 접속되는 데이터 전송부가, 상기 디지털 인터페이스 판별부에서 판별된 디지털 인터페이스로 동작하도록 전환 제어하는 제어부를 또한 구비하고,

상기 디지털 인터페이스 판별부는,

상기 제1의 디지털 인터페이스로 동작하는 외부 기기가 접속되는 경우에 사용되고, 상기 제2의 디지털 인터페이스로 동작하는 외부 기기가 접속되는 경우에 사용되지 않는 한 쌍의 핀에 주목하고,

상기 제2의 디지털 인터페이스로 동작하는 외부 기기가 접속되는 경우에, 상기 한 쌍의 핀이 단락 또는 저항을 통하여 접속되고,

상기 한 쌍의 핀의 한쪽의 핀은 저항을 통하여 소정 전압으로 풀업되고,

상기 한 쌍의 핀의 다른 쪽의 핀의 전류 또는 전압의 상태를 검출하는 제1의 검출부를 가지며,

상기 제1의 디지털 인터페이스로 동작하는 외부 기기가 접속되는 경우, 그 외부 기기로부터 전원이 공급되는 전원 핀에 주목하고,

상기 전원 핀의 전압 상태를 검출하는 제2의 검출부를 또한 가지며,

상기 제1의 검출부 및 상기 제2의 검출부의 검출 결과에 의거하여, 상기 커넥터부에 접속되어 있는 외부 기기의 디지털 인터페이스가 상기 제1의 디지털 인터페이스인지 상기 제2의 디지털 인터페이스인지를 판별하는 것을 특징으로 하는 전자 기기.

## 청구항 5

제4항에 있어서,

상기 디지털 인터페이스 판별부는,

상기 제2의 검출부에서 상기 전원 핀의 전압 상태가 상기 전원의 전압인 것이 검출될 때,

상기 커넥터부에 접속되어 있는 외부 기기의 디지털 인터페이스가 상기 제1의 디지털 인터페이스라고 판별하는 것을 특징으로 하는 전자 기기.

## 청구항 6

제4항에 있어서,

상기 디지털 인터페이스 판별부는,

상기 제2의 검출부에서 상기 전원 핀의 전압 상태가 상기 전원의 전압이 아닌 것이 검출되고, 또한,

상기 제1의 검출부에서 상기 한 쌍의 핀의 다른 쪽의 핀을 통하여 전류가 흐르고 있는 것, 또는 상기 한 쌍의 핀의 다른 쪽의 핀의 전압이 소정 전압에 있는 것이 검출될 때,

상기 커넥터부에 접속되어 있는 외부 기기의 디지털 인터페이스가 상기 제2의 디지털 인터페이스라고 판별하는 것을 특징으로 하는 전자 기기.

## 청구항 7

제4항에 있어서,

상기 디지털 인터페이스 판별부에서 상기 커넥터부에 접속되어 있는 외부 기기의 디지털 인터페이스가 상기 제2의 디지털 인터페이스라고 판별될 때, 상기 전원 핀을 통하여 상기 외부 기기에 전원을 공급하는 전원 공급부를 또한 구비하는 것을 특징으로 하는 전자 기기.

## 청구항 8

제4항에 있어서,

상기 제2의 디지털 인터페이스로 동작하는 외부 기기가 접속되는 경우에 상기 한 쌍의 핀이 단락 또는 저항을 통하여 접속되는 상태는, 상기 외부 기기를 상기 커넥터부에 접속하기 위한 케이블의 플러그 내에서 행하여지는 것을 특징으로 하는 기재된 전자 기기.

### 청구항 9

제4항에 있어서,

상기 제1의 디지털 인터페이스는 HDMI이고,

상기 한 쌍의 핀의 한쪽의 핀은 SCL용의 핀이고, 상기 한 쌍의 핀의 다른 쪽의 핀은 SDA용의 핀인 것을 특징으로 하는 전자 기기.

### 청구항 10

복수의 핀을 갖는 커넥터부를 구비하고,

제1의 디지털 인터페이스로 동작하는 외부 기기가 상기 커넥터부에 접속될 때에는 상기 복수의 핀 중 제1의 수의 핀이 사용되고, 제2의 디지털 인터페이스로 동작하는 외부 기기가 접속될 때에는 상기 복수의 핀 중 상기 제1의 수보다 적은 제2의 수의 핀이 사용되고,

상기 복수의 핀 중, 상기 제2의 디지털 인터페이스로 동작하는 외부 기기가 상기 커넥터부에 접속될 때에는 사용되지 않는 소정의 핀의 전압 또는 전류의 상태에 의거하여, 상기 커넥터부에 접속되어 있는 외부 기기의 디지털 인터페이스가 상기 제1의 디지털 인터페이스인지 상기 제2의 디지털 인터페이스인지지를 판별하는 디지털 인터페이스 판별부와,

상기 커넥터부에 접속되는 데이터 전송부가, 상기 디지털 인터페이스 판별부에서 판별된 디지털 인터페이스로 동작하도록 전환 제어하는 제어부를 또한 구비하고,

상기 디지털 인터페이스 판별부는,

상기 제1의 디지털 인터페이스로 동작하는 외부 기기가 접속되는 경우에 사용되고, 상기 제2의 디지털 인터페이스로 동작하는 외부 기기가 접속되는 경우에 사용되지 않는 한 쌍의 핀에 주목하고,

상기 제2의 디지털 인터페이스로 동작하는 외부 기기가 접속되는 경우에, 상기 한 쌍의 핀의 한쪽의 핀 및 다른 쪽의 핀은, 그 한쪽의 핀으로부터 그 다른 쪽의 핀에 일방향으로 신호를 흘리는 전자 소자를 통하여 접속되고,

상기 한 쌍의 핀의 상기 한쪽의 핀에 제1의 신호를 공급하는 제1의 신호 공급부와,

상기 한 쌍의 핀의 상기 다른 쪽의 핀에 제2의 신호를 공급하는 제2의 신호 공급부와,

상기 제1의 신호 공급부로부터 상기 한 쌍의 핀의 상기 한쪽의 핀에 상기 제1의 신호가 공급되는 기간에, 상기 한 쌍의 핀의 상기 다른 쪽의 핀으로부터 상기 제1의 신호를 검출하는 제1의 신호 검출부와,

상기 제2의 신호 공급부로부터 상기 한 쌍의 핀의 상기 다른 쪽의 핀에 상기 제2의 신호가 공급되는 기간에, 상기 한 쌍의 핀의 상기 한쪽의 핀으로부터 상기 제2의 신호를 검출하는 제2의 신호 검출부를 가지며,

상기 제1의 신호 검출부 및 상기 제2의 신호 검출부의 검출 결과에 의거하여, 상기 커넥터부에 접속되어 있는 외부 기기의 디지털 인터페이스가 상기 제2의 디지털 인터페이스인지의 여부를 판별하는 것을 특징으로 하는 전자 기기.

### 청구항 11

제10항에 있어서,

상기 디지털 인터페이스 판별부는,

상기 제1의 신호 검출부에서 상기 제1의 신호가 검출되고, 상기 제2의 신호 검출부에서 상기 제2의 신호가 검출되지 않을 때, 상기 커넥터부에 접속되어 있는 외부 기기의 디지털 인터페이스가 상기 제2의 디지털 인터페이스라고 판별하는 것을 특징으로 하는 전자 기기.

### 청구항 12

제11항에 있어서,

상기 디지털 인터페이스 판별부는,

상기 제1의 디지털 인터페이스로 동작하는 외부 기기가 접속되는 경우, 그 외부 기기로부터 전원이 공급되는 전원 핀에 주목하고,

상기 전원 핀의 전압 상태를 검출하는 전압 검출부를 또한 가지며,

상기 전압 검출부에서 상기 전원 핀의 전압 상태가 상기 전원의 전압인 것이 검출될 때,

상기 커넥터부에 접속되어 있는 외부 기기의 디지털 인터페이스가 상기 제1의 디지털 인터페이스라고 판별하는 것을 특징으로 하는 전자 기기.

### 청구항 13

제10항에 있어서,

상기 제1의 신호 및 상기 제2의 신호는 펄스 신호인 것을 특징으로 하는 전자 기기.

### 청구항 14

제13항에 있어서,

상기 제1의 신호 공급부는,

상기 한 쌍의 핀의 상기 한쪽의 핀을 소정 전압이 공급되는 단자에 접속하는 제1의 저항 소자와, 상기 한쪽의 핀을 접지 단자에 접속하는 제1의 스위칭 소자와, 그 제1의 스위칭 소자를 구동하는 펄스 신호를 발생하는 제1의 펄스 발생기를 가지며,

상기 제2의 신호 공급부는,

상기 한 쌍의 핀의 상기 다른 쪽의 핀을 소정 전압이 공급되는 단자에 접속하는 제2의 저항 소자와, 상기 다른 쪽의 핀을 접지 단자에 접속하는 제2의 스위칭 소자와, 그 제2의 스위칭 소자를 구동하는 펄스 신호를 발생하는 제2의 펄스 발생기를 갖는 것을 특징으로 하는 전자 기기.

### 청구항 15

제14항에 있어서,

상기 제1의 스위칭 소자 및 상기 제2의 스위칭 소자는, 전계효과 트랜지스터인 것을 특징으로 하는 전자 기기.

### 청구항 16

제12항에 있어서,

상기 디지털 인터페이스 판별부에서 상기 커넥터부에 접속되어 있는 외부 기기의 디지털 인터페이스가 상기 제2의 디지털 인터페이스라고 판별될 때, 상기 전원 핀을 통하여 상기 외부 기기에 전원을 공급하는 전원 공급부를 또한 구비하는 것을 특징으로 하는 전자 기기.

### 청구항 17

제10항에 있어서,

상기 제2의 디지털 인터페이스로 동작하는 외부 기기가 접속되는 경우에 상기 한 쌍의 핀이 상기 전자 소자를 통하여 접속되는 상태는, 상기 외부 기기를 상기 커넥터부에 접속하기 위한 케이블의 플러그 내에서 행하여지는 것을 특징으로 하는 전자 기기.

### 청구항 18

제10항에 있어서,

상기 제1의 디지털 인터페이스는 HDMI이고,

상기 한 쌍의 핀의 한쪽의 핀은 SCL용의 핀이고, 상기 한 쌍의 핀의 다른 쪽의 핀은 SDA용의 핀인 것을 특징으

로 하는 전자 기기.

### 청구항 19

제1항에 있어서,

상기 전자 소자는, 다이오드인 것을 특징으로 하는 전자 기기.

### 청구항 20

제1항에 있어서,

상기 제1의 디지털 인터페이스는, HDMI인 것을 특징으로 하는 전자 기기.

### 청구항 21

복수의 핀을 갖는 커넥터부를 구비하고,

제1의 디지털 인터페이스로 동작하는 외부 기기가 상기 커넥터부에 접속될 때에는 상기 복수의 핀 중 제1의 수의 핀이 사용되고, 제2의 디지털 인터페이스로 동작하는 외부 기기가 접속될 때에는 상기 복수의 핀 중 상기 제1의 수보다 적은 제2의 수의 핀이 사용되는 전자 기기에 있어서의 접속 외부 기기의 전송 모드 판별 방법으로서,

상기 복수의 핀 중, 상기 제2의 디지털 인터페이스로 동작하는 외부 기기가 상기 커넥터부에 접속될 때에는 사용되지 않는 소정의 핀의 전압 상태 또는 전류 상태에 의거하여, 상기 커넥터부에 접속되어 있는 외부 기기의 디지털 인터페이스가 상기 제1의 디지털 인터페이스인지 상기 제2의 디지털 인터페이스인지를 판별하는 판별 스텝을 가지며,

상기 판별 스텝에서는,

상기 제1의 디지털 인터페이스로 동작하는 외부 기기가 접속되는 경우에 차동 신호가 입력되고, 상기 제2의 디지털 인터페이스로 동작하는 외부 기기가 접속되는 경우에 차동 신호가 입력되지 않는 한 쌍의 핀에 주목하고,

상기 제2의 디지털 인터페이스로 동작하는 외부 기기가 접속되는 경우에 상기 한 쌍의 핀이 단락 또는 제1의 저항을 통하여 접속되고, 상기 한 쌍의 핀의 한쪽의 핀은 제2의 저항을 통하여 소정 전압으로 풀업되고, 상기 한 쌍의 핀의 다른 쪽의 핀은 접지된 상태에서, 상기 한쪽의 핀의 전압을, 상기 소정 전압을 상기 제1의 저항 및 상기 제2의 저항으로 분압하여 얻어지는 전압보다도 높은 전압과 비교한 결과에 의거하여, 상기 커넥터부에 접속되어 있는 외부 기기의 디지털 인터페이스가 상기 제1의 디지털 인터페이스인지 상기 제2의 디지털 인터페이스인지를 판별하는 것을 특징으로 하는 접속 외부 기기의 디지털 인터페이스 판별 방법.

### 청구항 22

삭제

### 청구항 23

삭제

### 청구항 24

삭제

### 청구항 25

삭제

### 청구항 26

삭제

### 청구항 27

삭제

청구항 28

삭제

청구항 29

삭제

청구항 30

삭제

청구항 31

삭제

청구항 32

삭제

## 발명의 설명

### 기술 분야

[0001]

본 발명은, 전자 기기 및 접속 외부 기기의 디지털 인터페이스 판별 방법에 관한 것으로, 특히, 접속 외부 기기의 디지털 인터페이스를 판별하여 데이터 전송부의 동작을 제어하는 전자 기기 등에 관한 것이다.

### 배경 기술

[0002]

근래, 예를 들면, 소스 기기로부터 싱크 기기에 화상 및 음성의 데이터를 고속으로 전송하는 통신 인터페이스로서, HDMI(High Definition Multimedia Interface) 등의 인터페이스가 보급되고 있다. 소스 기기는, 예를 들면, 게임기, DVD(Digital Versatile Disc) 레코더나, 셋톱 박스, 그 밖의 AV 소스(Audio Visual source)이다. 싱크 기기는, 예를 들면, 텔레비전 수신기, 프로젝터, 그 밖의 디스플레이이다. 예를 들면, 비특허 문헌 1에는, HDMI 규격의 상세에 관한 기재가 있다.

### 선행기술문헌

#### 비특허문헌

[0003]

(비)특허문헌 0001) 비특허 문헌 1 : High-Definition Multimedia Interface Specification Version 1.4, June 5 2009

### 발명의 내용

#### 해결하려는 과제

[0004]

HDMI 규격은, 주로 고정 기기 사이의 접속을 상정하고 있다. 그 때문에, 커넥터의 핀 수도 19핀으로 많고, 커넥터 외형 치수도 크고, 휴대 기기에서는 불리하다. 그래서, 적은 핀 수로 커넥터를 소형화하고, 또한 HDMI와 동등한 베이스랜드 비디오 전송을 행하는 규격이 검토되기 시작했다.

[0005]

한편, 텔레비전 수신기 등의 싱크 기기에서는, 신규격의 커넥터를 추가하는 것은, 유저의 편리성을 손상시키고, 또한 스페이스면, 비용면에서 불리하다. 널리 보급된 디지털 A/V 입력 포트인 HDMI 리셉터를 신규격에서도 겸용할 수 있다면 사정이 좋다. 즉, 종래의 HDMI 리셉터를 겸용하고, 회로만으로 대응하고 싶다는 요망이 있다.

[0006]

본 발명의 목적은, 접속 외부 기기의 디지털 인터페이스를 판별하고, 데이터 전송부의 동작을 접속 외부 기기의 디지털 인터페이스에 맞도록 전환 가능하게 하는 것에 있다.

## 과제의 해결 수단

- [0007] 본 발명의 개념은,

- [0008] 복수의 핀을 갖는 커넥터부를 구비하고,

- [0009] 제1의 디지털 인터페이스로 동작하는 외부 기기가 상기 커넥터부에 접속될 때에는 상기 복수의 핀 중 제1의 수(數)의 핀이 사용되고, 제2의 디지털 인터페이스로 동작하는 외부 기기가 접속될 때에는 상기 복수의 핀 중 상기 제1의 수보다 적은 제2의 수의 핀이 사용되고,

- [0010] 상기 복수의 핀 중, 상기 제2의 디지털 인터페이스로 동작하는 외부 기기가 상기 커넥터부에 접속될 때에는 사용되지 않는 소정의 핀의 전압 또는 전류의 상태에 의거하여, 상기 커넥터부에 접속되어 있는 외부 기기의 전송모드가 상기 제1의 디지털 인터페이스인지 상기 제2의 디지털 인터페이스인지지를 판별하는 디지털 인터페이스 판별부와,

- [0011] 상기 커넥터부에 접속되는 데이터 전송부가, 상기 디지털 인터페이스 판별부에서 판별된 디지털 인터페이스로 동작하도록 전환 제어하는 제어부를 또한 구비하는 전자 기기에 있다.

- [0012] 본 발명에서, 전자 기기는 복수의 핀을 갖는 커넥터부(리셉터클)를 구비하고 있다. 제1의 디지털 인터페이스로 동작하는 외부 기기가 커넥터부에 접속될 때에는, 복수의 핀 중 제1의 수의 핀이 사용된다. 또한, 제2의 디지털 인터페이스로 동작하는 외부 기기가 접속될 때에는, 복수의 핀 중 제1의 수보다 적은 제2의 수의 핀이 사용된다. 예를 들면, 커넥터부가 HDMI 리셉터클인 경우, 핀 수는 19핀이다.

- [0013] 예를 들면, 제1의 디지털 인터페이스가 HDMI이고, 이 HDMI로 동작하는 외부 기기가 접속되는 경우에는, 19핀의 전부가 사용된다. 예를 들면, 제2의 디지털 인터페이스는, HDMI에 대해, TMDS 클록의 주파수를 높이고, TMDS 채널 수를 적게하는 등등을 행한 신규격의 디지털 인터페이스이다. 이 제2의 디지털 인터페이스로 동작하는 외부 기기가 접속될 때, 예를 들면, HDMI 리셉터클의 19핀 중, 사용되지 않는 핀이 나온다.

- [0014] 디지털 인터페이스 판별부에 의해, 커넥터부에 접속되어 있는 외부 기기의 디지털 인터페이스가 제1의 디지털 인터페이스인지 제2의 디지털 인터페이스인지가 판별된다. 이 경우, 커넥터부의 복수의 핀 중, 제2의 디지털 인터페이스가 접속될 때에는 사용되지 않는 소정의 핀의 전압 또는 전류의 상태에 의거하여, 판별된다.

- [0015] 그리고, 동작 제어부에 의해, 커넥터부에 접속되는 데이터 전송부가, 디지털 인터페이스 판별부에서 판별된 디지털 인터페이스로 동작하도록 전환 제어된다. 즉, 커넥터부에 접속되어 있는 외부 기기의 디지털 인터페이스가 제1의 디지털 인터페이스일 때, 데이터 전송부의 동작은 제1의 디지털 인터페이스에 맞도록 된다. 한편, 커넥터부에 접속되어 있는 외부 기기의 디지털 인터페이스가 제2의 디지털 인터페이스일 때, 데이터 전송부의 동작은 제2의 디지털 인터페이스에 맞도록 된다.

- [0016] 본 발명에서는, 접속 외부 기기의 디지털 인터페이스가 디지털 인터페이스 판별부에서 판별되고, 데이터 전송부의 동작이 접속 외부 기기의 디지털 인터페이스에 맞도록 전환된다. 그 때문에, 제1의 디지털 인터페이스로 동작하는 외부 기기를 접속하기 위한 커넥터부와, 제2의 디지털 인터페이스로 동작하는 외부 기기를 접속하기 위한 커넥터부를 겸용할 수 있고, 비용면, 스페이스면에서 유리하게 된다.

- [0017] 본 발명에서, 예를 들면, 디지털 인터페이스 판별부는, 제1의 디지털 인터페이스로 동작하는 외부 기기가 접속되는 경우에 차동 신호가 입력되고, 제2의 디지털 인터페이스로 동작하는 외부 기기가 접속되는 경우에 차동 신호가 입력되지 않는 한 쌍의 핀의 전압 상태에 의거하여, 커넥터부에 접속되어 있는 외부 기기의 디지털 인터페이스를 판별하도록 된다. 이 경우, 싱크 기기측에서, 소스 기기의 디지털 인터페이스를 판별할 수 있다.

- [0018] 여기서, 예를 들면, 제1의 디지털 인터페이스로 동작하는 외부 기기가 접속되는 경우 및 제2의 디지털 인터페이스로 동작하는 외부 기기가 접속되는 경우의 어느 경우에도 차동 신호가 입력되는 한 쌍의 핀의 전압 상태에 의거하여, 커넥터부에 케이블을 통하여 외부 기기가 접속되어 있는지의 여부를 판별하는 접속 판별부를 또한 구비하도록 되어도 좋다.

- [0019] 또한, 본 발명에서, 예를 들면, 디지털 인터페이스 판별부는, 제1의 디지털 인터페이스로 동작하는 외부 기기가 접속되는 경우에 차동 신호를 출력하고, 제2의 디지털 인터페이스로 동작하는 외부 기기가 접속되는 경우에 차동 신호를 출력하지 않는 한 쌍의 핀의 전압 상태에 의거하여, 커넥터부에 접속되어 있는 외부 기기의 디지털 인터페이스가 제1의 디지털 인터페이스인지 제2의 디지털 인터페이스인지지를 판별하도록 된다. 이 경우, 소스 기기측에서, 싱크 기기의 디지털 인터페이스를 판별할 수 있다.

- [0020] 여기서, 예를 들면, 제1의 디지털 인터페이스로 동작하는 외부 기기가 접속되는 경우 및 제2의 디지털 인터페이스로 동작하는 외부 기기가 접속되는 경우의 어느 경우에도 차동 신호를 출력하는 한 쌍의 핀의 전압 상태에 의거하여, 커넥터부에 케이블을 통하여 외부 기기가 접속되어 있는지의 여부를 판별하는 접속 판별부를 또한 구비하여도 좋다.

- [0021] 또한, 본 발명에서, 예를 들면, 디지털 인터페이스 판별부는, 제1의 디지털 인터페이스로 동작하는 외부 기기가 접속되는 경우에, 이 외부 기기로부터 전원이 공급되는 핀과 이 핀에 다이오드 및 저항을 통하여 접속되어 있는 핀의 전압 상태에 의거하여, 커넥터부에 접속되어 있는 외부 기기의 디지털 인터페이스가 제1의 디지털 인터페이스인지 제2의 디지털 인터페이스인지를 판별하게 된다.

- [0022] 또한, 본 발명에서, 예를 들면, 디지털 인터페이스 판별부는, 제1의 디지털 인터페이스로 동작하는 외부 기기가 접속되는 경우에 접지되고, 제2의 디지털 인터페이스로 동작하는 외부 기기가 접속되는 경우에 접지 전압보다 높은 전압이 인가되던지 전기적으로 둘 뜯 상태가 되고, 또한 저항을 통하여 접지 전압보다 높은 전압으로 풀업된 핀의 전압 상태에 의거하여, 커넥터부에 접속되어 있는 외부 기기의 디지털 인터페이스가 제1의 디지털 인터페이스인지 제2의 디지털 인터페이스인지를 판별하도록 된다.

- [0023] 또한, 본 발명에서, 예를 들면, 디지털 인터페이스 판별부는, 제1의 디지털 인터페이스로 동작하는 외부 기기가 접속되는 경우에 접지되고, 제2의 디지털 인터페이스로 동작하는 외부 기기가 접속되는 경우에 제1의 저항을 통하여 접지되고, 또한 제2의 저항을 통하여 접지 전압보다 높은 소정 전압으로 풀업된 핀의 전압을, 소정 전압을 제1의 저항 및 제2의 저항으로 분압하여 얻어지는 전압의 상측 및 하측의 전압과 비교한 결과에 의거하여, 커넥터부에 접속되어 있는 외부 기기의 디지털 인터페이스가 제1의 디지털 인터페이스인지 제2의 디지털 인터페이스인지를 판별하도록 된다.

- [0024] 또한, 본 발명에서, 예를 들면, 디지털 인터페이스 판별부는, 제1의 디지털 인터페이스로 동작하는 외부 기기가 접속되는 경우에 접지되고, 제2의 디지털 인터페이스로 동작하는 외부 기기가 접속되는 경우에 소정 전압이 제1의 저항 및 제2의 저항으로 분압되어서 얻어진 전압이 인가되고, 또한 제3의 저항을 통하여 소정 전압으로 풀업된 핀의 전압을, 소정 전압을 제1의 저항 및 제3의 저항의 병렬 저항과 제2의 저항으로 분압하여 얻어지는 전압의 상측 및 하측의 전압과 비교한 결과에 의거하여, 커넥터부에 접속되어 있는 외부 기기의 디지털 인터페이스가 제1의 디지털 인터페이스인지 제2의 디지털 인터페이스인지를 판별하도록 된다.

- [0025] 또한, 본 발명에서, 예를 들면, 디지털 인터페이스 판별부는, 제1의 디지털 인터페이스로 동작하는 외부 기기가 접속되는 경우에 차동 신호가 입력되고, 제2의 디지털 인터페이스로 동작하는 외부 기기가 접속되는 경우에 차동 신호가 입력되지 않는 한 쌍의 핀에 주목하고, 제2의 디지털 인터페이스로 동작하는 외부 기기가 접속되는 경우에 한 쌍의 핀이 단락 또는 제1의 저항을 통하여 접속되고, 한 쌍의 핀의 한쪽의 핀은 제2의 저항을 통하여 소정 전압으로 풀업되고, 한 쌍의 핀의 다른 쪽의 핀은 접지된 상태에서, 한쪽의 핀의 전압을, 소정 전압을 제1의 저항 및 제2의 저항으로 분압하여 얻어지는 전압보다도 높은 전압과 비교한 결과에 의거하여, 커넥터부에 접속되어 있는 외부 기기의 디지털 인터페이스가 제1의 디지털 인터페이스인지 제2의 디지털 인터페이스인지를 판별하도록 된다.

- [0026] 여기서, 예를 들면, 제2의 디지털 인터페이스로 동작하는 외부 기기가 접속되는 경우에 한 쌍의 핀이 단락 또는 상기 제1의 저항을 통하여 접속되는 상태는, 외부 기기를 커넥터부에 접속하기 위한 케이블의 플러그 내에서 행하여진다. 또한, 커넥터부에의 케이블의 접속을 판별하는 접속 판별부를 또한 구비하고, 디지털 인터페이스 판별부는, 접속 판별부에서 커넥터부에 케이블이 접속된 것이 판별된 후에, 커넥터부에 접속되어 있는 외부 기기의 디지털 인터페이스가 제1의 디지털 인터페이스인지 제2의 디지털 인터페이스인지를 판별하도록 되어도 좋다.

- [0027] 또한, 본 발명에서, 예를 들면, 디지털 인터페이스 판별부는, 제1의 디지털 인터페이스로 동작하는 외부 기기가 접속되는 경우에 사용되고, 제2의 디지털 인터페이스로 동작하는 외부 기기가 접속되는 경우에 사용되지 않는 한 쌍의 핀에 주목하고, 제2의 디지털 인터페이스로 동작하는 외부 기기가 접속되는 경우에, 한 쌍의 핀이 단락 또는 저항을 통하여 접속되고, 이 한 쌍의 핀의 한쪽의 핀은 저항을 통하여 소정 전압으로 풀업되고, 이 한 쌍의 핀의 다른 쪽의 핀의 전류 또는 전압의 상태를 검출하는 제1의 검출부를 가지며, 제1의 디지털 인터페이스로 동작하는 외부 기기가 접속되는 경우, 이 외부 기기로부터 전원이 공급되는 전원 핀에 주목하고, 이 전원 핀의 전압 상태를 검출하는 제2의 검출부를 또한 가지며, 제1의 검출부 및 제2의 검출부의 검출 결과에 의거하여, 커넥터부에 접속되어 있는 외부 기기의 디지털 인터페이스가 제1의 디지털 인터페이스인지 제2의 디지털 인터페이스인지를 판별하도록 된다.

- [0028] 여기서, 예를 들면, 제2의 디지털 인터페이스로 동작하는 외부 기기가 접속되는 경우에 한 쌍의 핀이 단락 또는 저항을 통하여 접속되는 상태는, 외부 기기를 커넥터부에 접속하기 위한 케이블의 플러그 내에서 행하여진다. 또한, 예를 들면, 제1의 디지털 인터페이스는 HDMI이고, 한 쌍의 핀의 한쪽의 핀은 SCL용의 핀이고, 한 쌍의 핀의 다른 쪽의 핀은 SDA용의 핀이다.

- [0029] 이 경우, 예를 들면, 디지털 인터페이스 판별부는, 제2의 검출부에서 전원 핀의 전압 상태가 전원의 전압인 것이 검출될 때, 커넥터부에 접속되어 있는 외부 기기의 디지털 인터페이스가 제1의 디지털 인터페이스라고 판별하도록 된다.

- [0030] 또한, 이 경우, 예를 들면, 디지털 인터페이스 판별부는, 제2의 검출부에서 전원 핀의 전압 상태가 전원의 전압이 아닌 것이 검출되고, 또한, 제1의 검출부에서 한 쌍의 핀의 다른 쪽의 핀을 통하여 전류가 흐르고 있는 것, 또는 한 쌍의 핀의 다른 쪽의 핀의 전압이 소정 전압에 있는 것이 검출될 때, 커넥터부에 접속되어 있는 외부 기기의 디지털 인터페이스가 제2의 디지털 인터페이스라고 판별하도록 된다.

- [0031] 또한, 본 발명에서, 예를 들면, 디지털 인터페이스 판별부에서 커넥터부에 접속되어 있는 외부 기기의 디지털 인터페이스가 제2의 디지털 인터페이스라고 판별될 때, 전원 핀을 통하여 외부 기기에 전원을 공급하는 전원 공급부를 또한 구비하도록 된다.

- [0032] 이 경우, 예를 들면, 디지털 인터페이스가 제2의 디지털 인터페이스인 외부 기기가 배터리 구동의 전자 기기로서, 이 배터리가 완전히 방전되어 있는 경우에도, 이 외부 기기의 디지털 인터페이스가 제2의 디지털 인터페이스인 것이 판별 가능해진다. 그 때문에, 상술한 전원 공급부에 의해 외부 기기에 전원을 공급하여, 충전하는 것이 가능해진다.

- [0033] 또한, 본 발명에서, 예를 들면, 디지털 인터페이스 판별부는, 제1의 디지털 인터페이스로 동작하는 외부 기기가 접속되는 경우에 사용되고, 제2의 디지털 인터페이스로 동작하는 외부 기기가 접속되는 경우에 사용되지 않는 한 쌍의 핀에 주목하고, 제2의 디지털 인터페이스로 동작하는 외부 기기가 접속되는 경우에, 한 쌍의 핀의 한쪽의 핀 및 다른 쪽의 핀은, 한쪽의 핀으로부터 다른 쪽의 핀에 일방향으로 신호를 흘리는 전자 소자를 통하여 접속되고, 한 쌍의 핀의 한쪽의 핀에 제1의 신호를 공급하는 제1의 신호 공급부와, 한 쌍의 핀의 다른 쪽의 핀에 제2의 신호를 공급하는 제2의 신호 공급부와, 제1의 신호 공급부로부터 한 쌍의 핀의 한쪽의 핀에 제1의 신호가 공급되는 기간에, 한 쌍의 핀의 다른 쪽의 핀으로부터 제1의 신호를 검출하는 제1의 신호 검출부와, 제2의 신호 공급부로부터 한 쌍의 핀의 다른 쪽의 핀에 제2의 신호가 공급되는 기간에, 한 쌍의 핀의 한쪽의 핀으로부터 제2의 신호를 검출하는 제2의 신호 검출부를 가지며, 제1의 신호 검출부 및 제2의 신호 검출부의 검출 결과에 의거하여, 커넥터부에 접속되어 있는 외부 기기의 디지털 인터페이스가 제2의 디지털 인터페이스인지의 여부를 판별하도록 된다.

- [0034] 여기서, 예를 들면, 제2의 디지털 인터페이스로 동작하는 외부 기기가 접속되는 경우에 한 쌍의 핀이 전자 소자로 접속되는 상태는, 외부 기기를 커넥터부에 접속하기 위한 케이블의 플러그 내에서 행하여진다. 또한, 예를 들면, 제1의 디지털 인터페이스는 HDMI이고, 한 쌍의 핀의 한쪽의 핀은 SCL용의 핀이고, 한 쌍의 핀의 다른 쪽의 핀은 SDA용의 핀이다. 또한, 예를 들면, 전자 소자는, 다이오드이다.

- [0035] 또한, 본 발명에서, 예를 들면, 디지털 인터페이스 판별부는, 제1의 신호 검출부에서 제1의 신호가 검출되고, 제2의 신호 검출부에서 제2의 신호가 검출되지 않을 때, 커넥터부에 접속되어 있는 외부 기기의 디지털 인터페이스가 제2의 디지털 인터페이스라고 판별하도록 된다.

- [0036] 또한, 본 발명에서, 예를 들면, 디지털 인터페이스 판별부는, 제1의 디지털 인터페이스로 동작하는 외부 기기가 접속되는 경우, 이 외부 기기로부터 전원이 공급되는 전원 핀에 주목하고, 이 전원 핀의 전압 상태를 검출하는 전압 검출부를 또한 가지며, 전압 검출부에서 전원 핀의 전압 상태가 전원의 전압인 것이 검출될 때, 커넥터부에 접속되어 있는 외부 기기의 디지털 인터페이스가 제1의 디지털 인터페이스라고 판별하도록 된다.

- [0037] 또한, 본 발명에서, 예를 들면, 제1의 신호 및 제2의 신호는 펄스 신호가 된다. 이 경우, 예를 들면, 제1의 신호 공급부는, 한 쌍의 핀의 한쪽의 핀을 소정 전압이 공급되는 단자에 접속하는 제1의 저항 소자와, 이 한쪽의 핀을 접지 단자에 접속하는 제1의 스위칭 소자와, 이 제1의 스위칭 소자를 구동하는 펄스 신호를 발생하는 제1의 펄스 발생기를 가지며, 제2의 신호 공급부는, 한 쌍의 핀의 다른 쪽의 핀을 소정 전압이 공급되는 단자에 접속하는 제2의 저항 소자와, 이 다른 쪽의 핀을 접지 단자에 접속하는 제2의 스위칭 소자와, 이 제2의 스위칭 소자를 구동하는 펄스 신호를 발생하는 제2의 펄스 발생기를 갖도록 된다. 예를 들면, 스위칭 소자는, 전계효과트랜지스터가 된다.

## 발명의 효과

[0038]

본 발명에 의하면, 접속 외부 기기의 디지털 인터페이스가 판별되고, 데이터 전송부의 동작이 접속 외부 기기의 디지털 인터페이스에 맞도록 전환되기 때문에, 제1, 제2의 디지털 인터페이스로 동작하는 외부 기기를 접속하기 위한 커넥터부를 겸용할 수 있고, 비용면, 스페이스면에서 유리하게 된다.

## 도면의 간단한 설명

[0039]

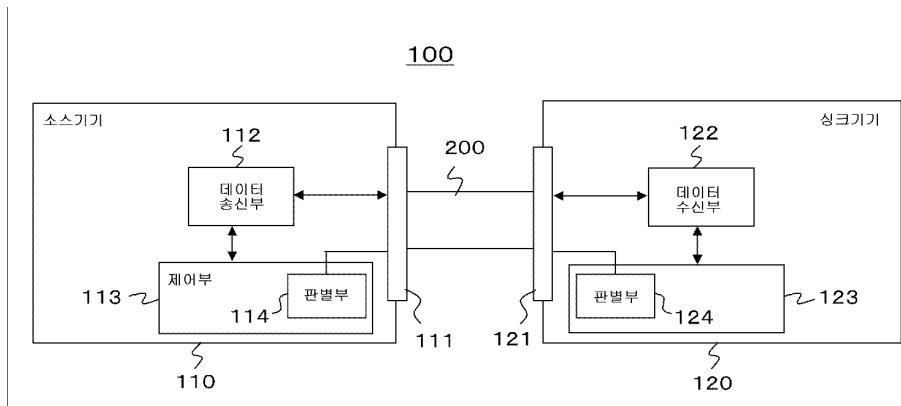

도 1은 본 발명의 실시의 형태로서의 AV 시스템의 구성례를 도시하는 블록도.

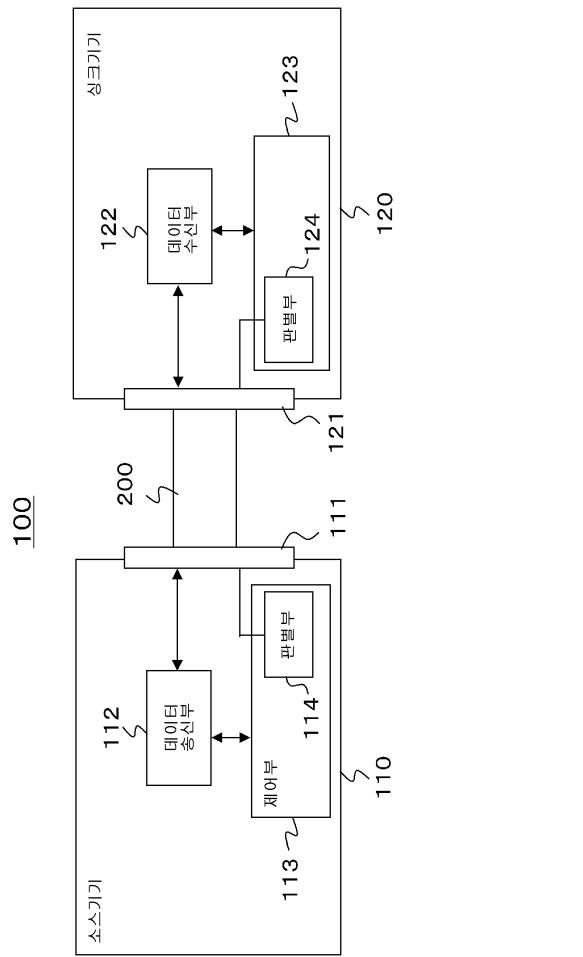

도 2는 AV 시스템에서의, 소스 기기의 데이터 송신부와, 싱크 기기의 데이터 수신부의 구성례를 도시하는 도면 (HDMI 규격의 디지털 인터페이스인 경우).

도 3은 HDMI의 TMDS 채널로 전송되는 TMDS 전송 데이터 구조의 한 예를 도시하는 도면.

도 4는 HDMI 기기에 마련되는 HDMI 단자의 핀 배열(타입 A)을 도시하는 도면.

도 5는 AV 시스템에서의, 소스 기기의 데이터 송신부와, 싱크 기기의 데이터 수신부의 구성례를 도시하는 도면 (신규격의 디지털 인터페이스인 경우).

도 6은 AV 시스템에서의, 소스 기기의 데이터 송신부와, 싱크 기기의 데이터 수신부의 구성례를 도시하는 도면 (다른 신규격의 디지털 인터페이스인 경우).

도 7은 제어부의 제어 순서를 도시하는 플로우 차트.

도 8은 TMDS 차동 신호 페어의 모식도.

도 9는 TMDS 차동 신호가, 상한 전압(V\_high), 하한 전압(V\_low), 진폭(Vswing)으로서, 이 범위 내에서 동작하는 것을 도시하는 도면.

도 10은 디지털 인터페이스 판단용의 액티브 범위 검출 회로의 구체적인 회로예를 도시하는 도면.

도 11은 소스 기기 접속 판단용의 액티브 범위 검출 회로의 구체적인 회로예를 도시하는 도면.

도 12는 소스 기기가 HDMI 기기인 경우, 소스 기기로부터 싱크 기기에 전원 라인으로 +5V의 전원이 공급되는 것을 도시하는 도면.

도 13은 소스 기기가 신규격 기기인 경우, 19핀은 HDMI 규격으로 인가되는 전압(최저 +4.7V)을 하회하는 전압, 예를 들면 0V로 설정되는 것을 도시하는 도면.

도 14는 소스 기기가 HDMI 기기인 경우, 소스 기기에서, DDC-GND 라인이 접속되는 17핀이 접지되는 것을 도시하는 도면.

도 15는 소스 기기가 신규격 기기인 경우, 소스 기기에서, DDC-GND 라인이 접속되는 17핀에는 Vcc(예를 들면 +5V)가 인가되던지, 또는 이 17핀은 미접속, 즉 전기적으로 둘뜬 상태가 되는 것을 도시하는 도면.

도 16은 소스 기기가 HDMI 기기인 경우, 소스 기기에서, DDC-GND 라인이 접속되는 17핀은 접지되는 것을 도시하는 도면.

도 17은 소스 기기가 신규격 기기인 경우, 소스 기기에서, DDC-GND 라인이 접속되는 17핀은 저항(R2)을 통하여 접지되는 것을 도시하는 도면.

도 18은 소스 기기가 HDMI 기기인 경우, 소스 기기에서, DDC-GND 라인이 접속되는 17핀은 접지되는 것 등을 도시하는 도면.

도 19는 소스 기기가 신규격 기기인 경우, 소스 기기에서, Vcc(예를 들면, +5V)가 저항(R1과 R2)으로 분압되어서 얻어진 전압이 17핀에 인가되는 것 등을 도시하는 도면.

도 20은 싱크 기기가 HDMI 기기인 경우, 싱크 기기에서, DDC-GND 라인이 접속되는 17핀은 접지되는 것 등을 도시하는 도면.

도 21은 신규격에서의 Type-A 플러그 내부의 처리예를 설명하기 위한 도면.

도 22는 싱크 기기의 제어부 내의 판별부에 마련되는 케이블 검출 회로의 구성례를 도시하는 도면.

도 23은 TMDS 차동 폐어 모식도에, 케이블 검출 회로를 삽입한 경우의 회로예를 도시하는 도면.

도 24는 케이블 미삽입시에 케이블 검출 회로의 전압 콤파레이터에 입력하는 전압을 도시하는 도면.

도 25는 PIN(1)(TMDS Data2+), PIN(3)(TMDS Data2-)의 사이를 저항기(RT)(50Ω)로 연결한 신규격 케이블이 삽입된 경우에 전압 콤파레이터에 입력하는 전압을 도시하는 도면.

도 26은 PIN(1)(TMDS Data2+), PIN(3)(TMDS Data2-)의 사이를 도선으로 쇼트시킨 신규격 케이블이 삽입된 경우에 전압 콤파레이터에 입력하는 전압을 도시하는 도면.

도 27은 HDMI 케이블 삽입시(HDMI 소스 기기는 없음)에 전압 콤파레이터에 입력하는 전압을 도시하는 도면.

도 28은 HDMI 케이블 삽입시(HDMI Source 기기 있음)에 전압 콤파레이터에 입력하는 전압을 도시하는 도면.

도 29는 리셉터를 내부 메카 스위치를 설명하기 위한 도면.

도 30은 리셉터를 내부 메카 스위치에 의한 검출 방법을 사용한 경우에 있어서의, 싱크 기기의 제어부의 제어 순서를 도시하는 플로우 차트.

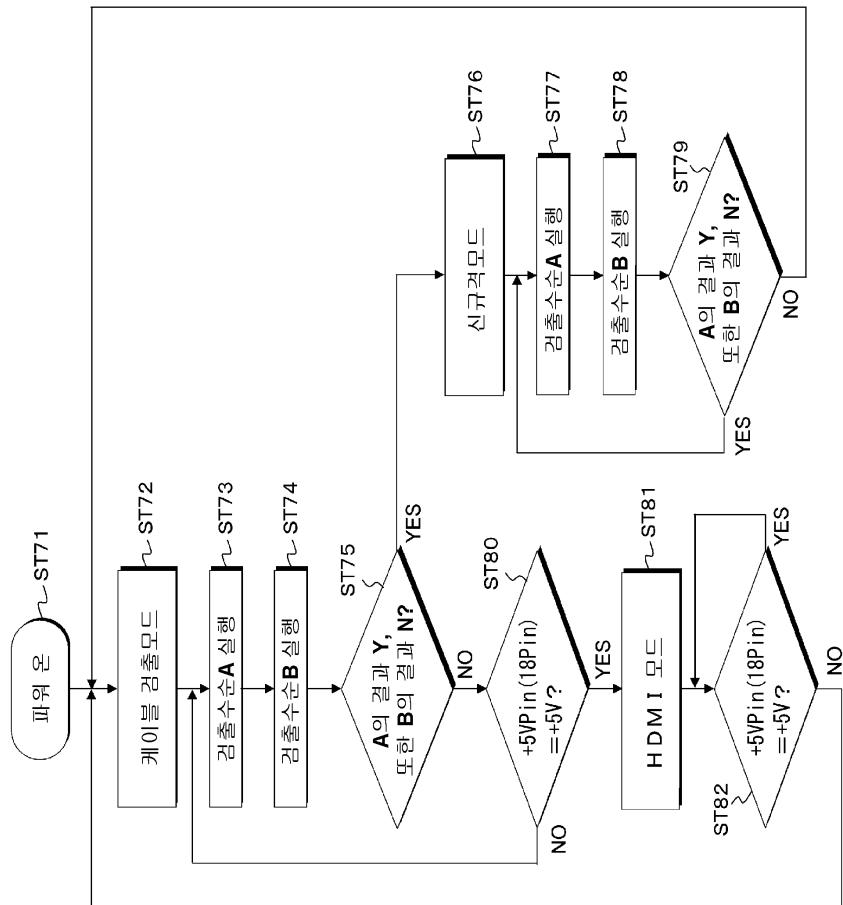

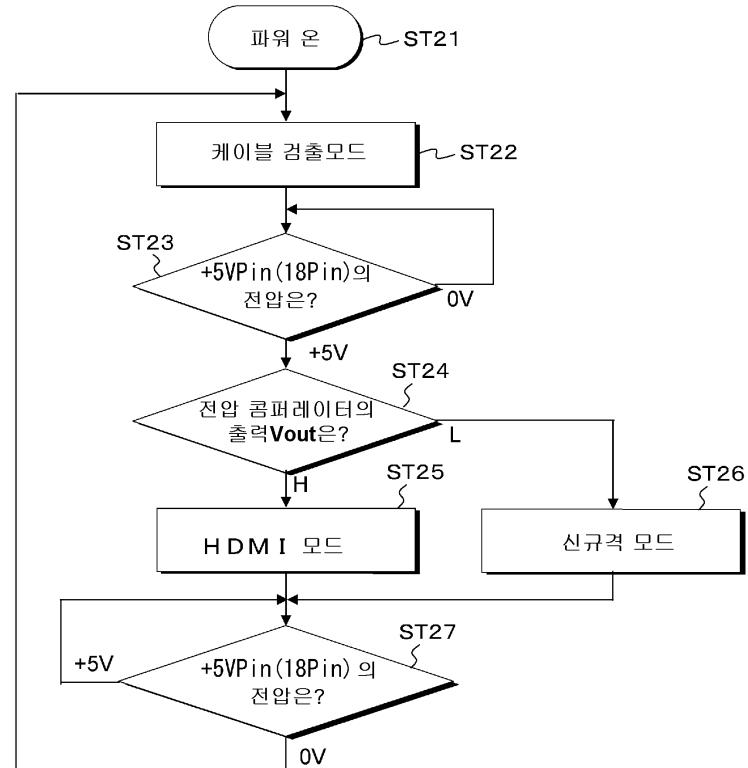

도 31은 +5V핀(18핀)의 전압을 감시하는 검출 방법을 사용한 경우에 있어서의, 싱크 기기의 제어부의 다른 제어 순서를 도시하는 플로우 차트.

도 32는 +5V핀(18핀)의 전압을 감시하는 검출 방법을 사용한 경우에 있어서의, 싱크 기기의 제어부의 다른 제어 순서를 도시하는 플로우 차트.

도 33은 신규격에 의거한 케이블선 배치를 도시하는 도면.

도 34는 신규격 케이블의 케이블선 배치를 도시하는 도면.

도 35는 싱크 기기의 제어부 내의 판별부 내의 구성을 개략적으로 도시하는 도면.

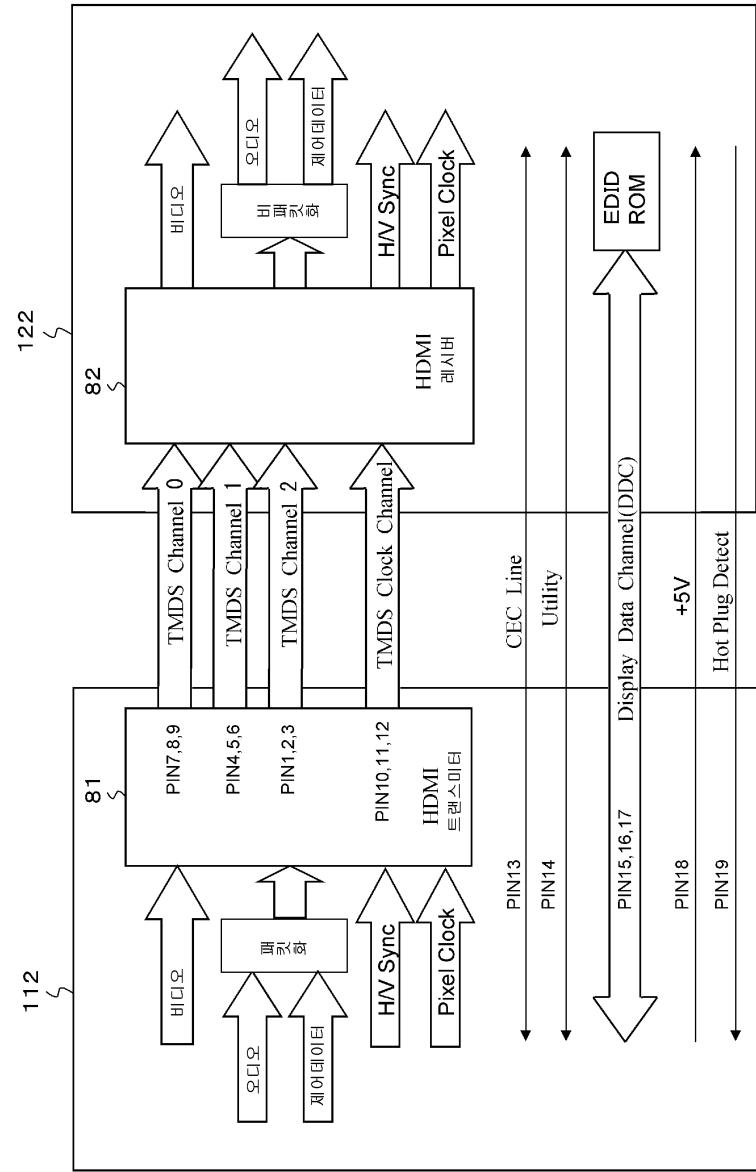

도 36은 싱크 기기의 제어부의 제어 순서를 도시하는 플로우 차트.

도 37은 신규격 케이블의 케이블선 배치를 도시하는 도면.

도 38은 싱크 기기의 제어부 내의 판별부 내의 구성을 개략적으로 도시하는 도면.

도 39는 「(1) 케이블 미접속인 경우」에 검출 순서(A, B)를 실행한 때의 검출 결과를 설명하기 위한 접속상태도.

도 40은 「(2) 신규격 케이블이 접속된 경우」에 검출 순서(A, B)를 실행한 때의 검출 결과를 설명하기 위한 접속상태도.

도 41은 「(3) 신규격 케이블+신규격 소스 기기가 접속된 경우」에 검출 순서(A, B)를 실행한 때의 검출 결과를 설명하기 위한 접속상태도.

도 42는 「(4) HDMI 케이블이 접속된 경우」에 검출 순서(A, B)를 실행한 때의 검출 결과를 설명하기 위한 접속상태도.

도 43은 「(5) HDMI 케이블+HDMI 소스 기기가 접속된 경우」에 검출 순서(A, B)를 실행한 때의 검출 결과를 설명하기 위한 접속상태도.

도 44는 각 경우의 검출 순서(A), 검출 순서(B)에서의 검출 결과(out3, out2)의 일람을 도시하는 도면.

도 45는 싱크 기기의 제어부의 제어 순서를 도시하는 플로우 차트.

### 발명을 실시하기 위한 구체적인 내용

[0040] 이하, 발명을 실시하기 위한 형태(이하, 실시의 형태라고 한다)에 관해 설명한다. 또한, 설명은 이하의 순서로 행한다.

[0041] 1. 실시의 형태

[0042] 2. 변형례

[0043] <1. 실시의 형태>

## [0044] [AV 시스템의 구성]

도 1은, 실시의 형태로서의 AV(Audio and Visual) 시스템(100)의 구성례를 도시하고 있다. 이 AV 시스템(100)은, 소스 기기와 싱크 기기가 접속되어 구성되어 있다. 소스 기기(110)는, 예를 들면, 게임기, 디스크 플레이어, 셋톱 박스, 디지털 카메라, 휴대 전화 등의 AV 소스이다. 싱크 기기(120)는, 예를 들면, 텔레비전 수신기, 프로젝터 등이다.

[0046] 소스 기기(110) 및 싱크 기기(120)는, 케이블(200)을 통하여 접속되어 있다. 소스 기기(110)에는, 데이터 송신부(112)가 접속된 커넥터부(111)가 마련되어 있다. 싱크 기기(120)에는, 데이터 수신부(122)가 접속된 커넥터부(121)가 마련되어 있다. 케이블(200)의 일단은 소스 기기(110)의 커넥터부(111)에 접속되고, 이 케이블(200)의 타단은 싱크 기기(120)의 커넥터부(121)에 접속된다.

[0047] 소스 기기(110)는, 제어부(113)를 갖고 있다. 이 제어부(113)는, 소스 기기(110)의 전체를 제어한다. 소스 기기(110)의 데이터 송신부(112)는, HDMI 규격의 디지털 인터페이스에만 대응하고 있는 경우, 신규격의 디지털 인터페이스에만 대응하고 있는 경우, 또는 그 쌍방에 대응하고 있는 경우가 있다. 데이터 송신부(112)가 쌍방의 디지털 인터페이스에 대응하고 있는 경우, 어느 한 디지털 인터페이스의 동작을 행하도록, 제어부(113)에 의해 선택적으로 전환된다.

[0048] 이 소스 기기(110)의 제어부(113)는, 판별부(114)를 포함하고 있다. 이 판별부(114)는, 이 소스 기기(110)에 싱크 기기(120)가 접속되어 있는지, 싱크 기기(120)의 데이터 수신부(122)의 디지털 인터페이스가 HDMI 규격인지 신규격인지 등을 회로를 이용하여 판별한다. 제어부(113)는, 데이터 송신부(112)가 HDMI 규격 및 신규격의 쌍방의 디지털 인터페이스에 대응하고 있는 경우, 판별부(114)의 판별 결과에 의거하여, 싱크 기기(120)의 데이터 수신부(122)의 디지털 인터페이스에 대응한 동작을 행하도록, 데이터 송신부(112)의 동작을 전환한다.

[0049] 싱크 기기(120)는, 제어부(123)를 갖고 있다. 이 제어부(123)는, 싱크 기기(120)의 전체를 제어한다. 싱크 기기(120)의 데이터 수신부(122)는, HDMI 규격의 디지털 인터페이스에만 대응하고 있는 경우, 신규격의 디지털 인터페이스에만 대응하고 있는 경우, 또는 그 쌍방에 대응하고 있는 경우가 있다. 데이터 수신부(122)가 쌍방의 디지털 인터페이스에 대응하고 있는 경우, 어느 한 디지털 인터페이스의 동작을 행하도록, 제어부(123)에 의해 선택적으로 전환된다.

[0050] 이 싱크 기기(120)의 제어부(123)는, 판별부(124)를 포함하고 있다. 이 판별부(124)는, 이 싱크 기기(120)에 소스 기기(110)가 접속되어 있는지, 소스 기기(110)의 데이터 송신부(112)의 디지털 인터페이스가 HDMI 규격인지 신규격인지 등을 회로를 이용하여 판별한다. 제어부(123)는, 데이터 수신부(122)가 HDMI 규격 및 신규격의 쌍방의 디지털 인터페이스에 대응하고 있는 경우, 판별부(124)의 판별 결과에 의거하여, 소스 기기(110)의 데이터 송신부(112)의 디지털 인터페이스에 대응한 동작을 행하도록, 데이터 수신부(122)의 동작을 전환한다.

## [데이터 송신부, 데이터 수신부의 구성례]

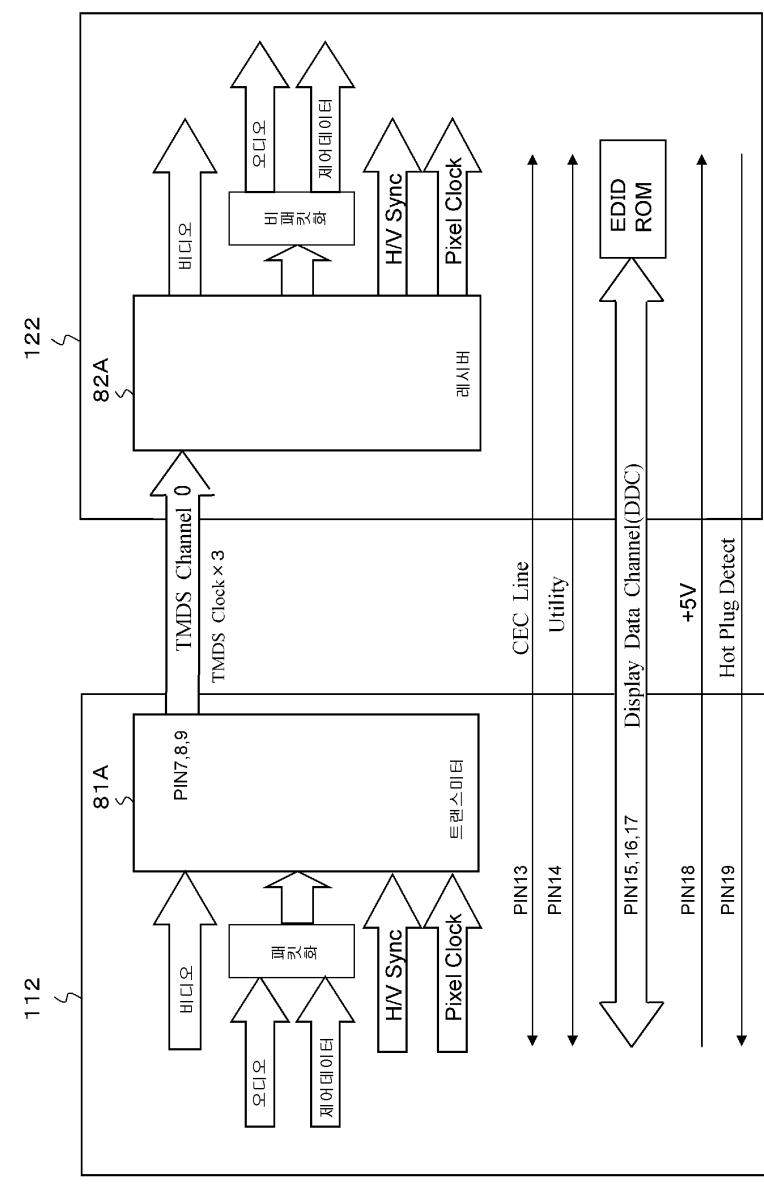

[0052] 도 2는, 도 1의 AV 시스템(100)에서의, 소스 기기(110)의 데이터 송신부(112)와, 싱크 기기(120)의 데이터 수신부(122)의 구성례를 도시하고 있다. 이 구성례는, 데이터 송신부(112) 및 데이터 수신부(122)의 디지털 인터페이스가, HDMI 규격의 디지털 인터페이스인 경우를 도시하고 있다.

[0053] 데이터 송신부(112)는, 유효 화상 구간(이하, 적절히, 액티브 비디오 구간이라고도 한다)에서, 비압축의 1화면 분의 화상의 화소 데이터에 대응하는 차동 신호를, 복수의 채널로, 데이터 수신부(122)에 일방향으로 송신한다. 여기서, 유효 화상 구간은, 하나의 수직 동기 신호로부터 다음의 수직 동기 신호까지의 구간에서, 수평 귀선 구간 및 수직 귀선 구간을 제외한 구간이다. 또한, 데이터 송신부(112)는, 수평 귀선 구간 또는 수직 귀선 구간에서, 적어도 화상에 부수되는 음성 데이터나 제어 데이터, 그 밖의 보조 데이터 등에 대응하는 차동 신호를, 복수의 채널로, 데이터 수신부(122)에 일방향으로 송신한다.

[0054] 데이터 송신부(112)와 데이터 수신부(122)로 이루어지는 HDMI 시스템의 전송 채널에는, 이하의 전송 채널이 있다. 즉, 데이터 송신부(112)로부터 데이터 수신부(122)에 대해, 화소 데이터 및 음성 데이터를, 픽셀 클록에 동기하여, 일방향으로 시리얼 전송하기 위한 전송 채널로서의, 3개의 TMDS 채널(#0 내지 #2)이 있다. 또한, TMDS 클록을 전송하는 전송 채널로서의, TMDS 클록 채널이 있다.

[0055] 데이터 송신부(112)는, HDMI 트랜스미터(81)를 갖는다. 이 HDMI 트랜스미터(81)는, 예를 들면, 비압축의 화상의 화소 데이터를 대응하는 차동 신호로 변환하고, 복수의 채널인 3개의 TMDS 채널(#0, #1, #2)로, HDMI 케이블을 통하여 접속되어 있는 데이터 수신부(122)에, 일방향으로 시리얼 전송한다.

- [0056] 또한, HDMI 트랜스미터(81)는, 비압축의 화상에 부수되는 음성 데이터, 나아가서는, 필요한 제어 데이터 그 밖의 보조 데이터 등을, 대응하는 차동 신호로 변환하고, 3개의 TMDS 채널(#0, #1, #2)로 데이터 수신부(122)에, 일방향으로 시리얼 전송한다.

- [0057] 또한, HDMI 트랜스미터(81)는, 3개의 TMDS 채널(#0, #1, #2)로 송신하는 화소 데이터에 동기한 TMDS 클록을, TMDS 클록 채널로, HDMI 케이블을 통하여 접속되어 있는 데이터 송신부(122)에 송신한다. 여기서, 하나의 TMDS 채널(#i)(i=0, 1, 2)에서는, TMDS 클록의 1클록의 사이에, 10비트의 화소 데이터가 송신된다.

- [0058] 데이터 수신부(122)는, 액티브 비디오 구간에서, 복수의 채널로, 데이터 송신부(122)로부터 일방향으로 송신되어 오는, 화소 데이터에 대응하는 차동 신호를 수신한다. 또한, 이 데이터 수신부(122)는, 수평 귀선 구간 또는 수직 귀선 구간에서, 복수의 채널로, 데이터 송신부(112)로부터 일방향으로 송신되어 오는, 음성 데이터나 제어 데이터에 대응하는 차동 신호를 수신한다.

- [0059] 즉, 데이터 수신부(122)는, HDMI 레시버(82)를 갖는다. 이 HDMI 레시버(82)는, TMDS 채널(#0, #1, #2)로, 데이터 송신부(112)로부터 일방향으로 송신되어 오는, 화소 데이터에 대응하는 차동 신호와, 음성 데이터나 제어 데이터에 대응하는 차동 신호를 수신한다. 이 경우, 데이터 송신부(112)로부터 TMDS 클록 채널로 송신되어 오는 픽셀 클록(TMDS 클록)에 동기하여 수신한다.

- [0060] HDMI 시스템의 전송 채널에는, 상술한 TMDS 채널(#0 내지 #2) 및 TMDS 클록 채널 외에, DDC(Display Data Channel)나 CEC 라인이라고 불리는 전송 채널이 있다. DDC는, HDMI 케이블에 포함되는 도시하지 않은 2개의 신호선으로 이루어진다. DDC는, 데이터 송신부(112)가, 데이터 수신부(122)로부터, E-EDID(Enhanced Extended Display Identification Data)를 판독하기 위해 사용된다.

- [0061] 즉, 데이터 수신부(122)는, HDMI 레시버(81) 외에, 자신의 성능(Configuration/capability)에 관한 성능 정보인 E-EDID를 기억하고 있는, EDID ROM(Read Only Memory)을 갖고 있다. 데이터 송신부(112)는, 예를 들면, 제어부(113)로부터의 요구에 응하여, HDMI 케이블을 통하여 접속되어 있는 데이터 수신부(122)로부터, E-EDID를, DDC를 통하여 판독한다.

- [0062] 데이터 송신부(112)는, 판독한 E-EDID를 제어부(113)에 보낸다. 제어부(113)는, 이 E-EDID를, 도시하지 않은 플래시 ROM 또는 DRAM에 격납한다. 제어부(113)는, E-EDID에 의거하여, 데이터 수신부(122)의 성능의 설정을 인식할 수 있다. 예를 들면, 제어부(113)는, 데이터 수신부(122)를 갖는 싱크 기기(120)가 입체 화상 데이터의 취급이 가능하였는지의 여부, 가능한 경우는 또한 어떠한 TMDS 전송 데이터 구조에 대응 가능하든지 등을 인식한다.

- [0063] CEC 라인은, HDMI 케이블에 포함되는 도시하지 않은 1개의 신호선으로 이루어지고, 데이터 송신부(112)와 데이터 수신부(122)의 사이에서, 제어용의 데이터의 쌍방향 통신을 행하기 위해 사용된다. 이 CEC 라인은, 제어 데이터 라인을 구성하고 있다.

- [0064] 또한, HDMI 케이블에는, HPD(Hot Plug Detect)라고 불리는 핀에 접속되는 라인(HPD 라인)이 포함되어 있다. 소스 기기는, 이 HPD 라인을 이용하여, 싱크 기기의 접속을 검출할 수 있다. 또한, 이 HPD 라인은 쌍방향 통신로를 구성하는 HEAC-라인으로서도 사용된다. 또한, HDMI 케이블에는, 소스 기기로부터 싱크 기기에 전원을 공급하기 위해 사용되는 전원 라인(+5V Power Line)이 포함되어 있다. 또한, HDMI 케이블에는, 유털리티 라인이 포함되어 있다. 이 유털리티 라인은 쌍방향 통신로를 구성한 HEAC+라인으로서도 사용된다.

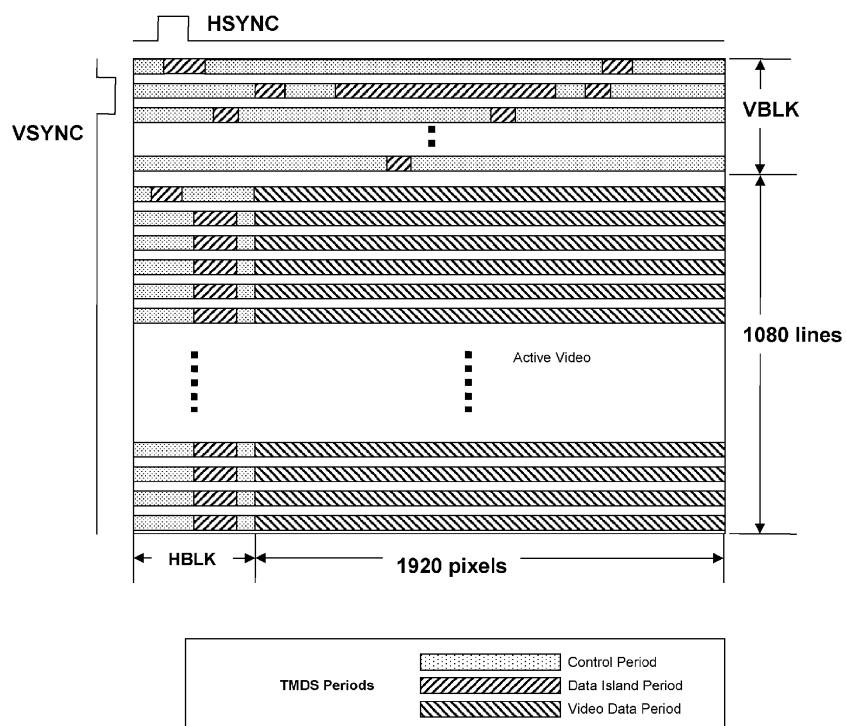

- [0065] 도 3은, TMDS 전송 데이터의 구조예를 도시하고 있다. 이 도 3은, TMDS 채널(#0, #1, #2)에서, 가로×세로가 1920픽셀×1080라인의 화상 데이터가 전송되는 경우의, 각종의 전송 데이터의 구간을 나타내고 있다.

- [0066] HDMI의 3개의 TMDS 채널(#0, #1, #2)로 전송 데이터가 전송되는 비디오 필드(Video Field)에는, 전송 데이터의 종류에 응하여, 3종류의 구간이 존재한다. 이 3종류의 구간은, 비디오 데이터 구간(Video Data period), 데이터 아일랜드 구간(Data Island period), 및 컨트롤 구간(Control period)이다.

- [0067] 여기서, 비디오 필드 구간은, 어느 수직 동기 신호의 상승 에지(active edge)로부터 다음의 수직 동기 신호의 상승 에지까지의 구간이다. 이 비디오 필드 구간은, 수평 블랭킹 기간(horizontal blanking), 수직 블랭킹 기간(vertical blanking), 및, 액티브 비디오 구간(Active Video)으로 나누어진다. 이 액티브 비디오 구간은, 비디오 필드 구간에서, 수평 블랭킹 기간 및 수직 블랭킹 기간을 제외한 구간이다.

- [0068] 비디오 데이터 구간은, 액티브 비디오 구간에 할당된다. 이 비디오 데이터 구간에서는, 비압축의 1화면분의 화상 데이터를 구성하는 1920픽셀(화소)×1080라인 분의 유효 화소(Active pixel)의 데이터가 전송된다.

- [0069] 데이터 아일랜드 구간 및 컨트롤 구간은, 수평 블랭킹 기간 및 수직 블랭킹 기간에 할당된다. 이 데이터 아일랜드 구간 및 컨트롤 구간에서는, 보조 데이터(Auxiliary data)가 전송된다. 즉, 데이터 아일랜드 구간은, 수평 블랭킹 기간과 수직 블랭킹 기간의 일부분에 할당되어 있다. 이 데이터 아일랜드 구간에서는, 보조 데이터 중, 제어에 관계되지 않는 데이터인, 예를 들면, 음성 데이터의 패킷 등이 전송된다.

- [0070] 컨트롤 구간은, 수평 블랭킹 기간과 수직 블랭킹 기간의 다른 부분에 할당되어 있다. 이 컨트롤 구간에서는, 보조 데이터 중의, 제어에 관계되는 데이터인, 예를 들면, 수직 동기 신호 및 수평 동기 신호, 제어 패킷 등이 전송된다.

- [0071] 도 4는, HDMI 리셉터클의 핀 배열의 한 예를 도시하고 있다. 도 4에 도시하는 핀 배열은 타입 A(type-A)라고 불리고 있다. TMDS 채널(#i)의 차동 신호인 TMDS Data#i+와 TMDS Data#i-는 차동선인 2개의 라인에 의해 전송된다. 이 2개의 라인은, TMDS Data#i+가 할당되어 있는 핀(핀 번호가 1, 4, 7의 핀)과, TMDS Data#i-가 할당되어 있는 핀(핀 번호가 3, 6, 9의 핀)에 접속된다.

- [0072] 또한, 제어용의 데이터인 CEC 신호가 전송되는 CEC 라인은, 핀 번호가 13인 핀에 접속된다. 또한, E-EDID 등의 SDA(Serial Data) 신호가 전송되는 라인은, 핀 번호가 16인 핀에 접속된다. SDA 신호의 송수신시의 동기에 사용되는 클록 신호인 SCL(Serial Clock) 신호가 전송되는 라인은, 핀 번호가 15인 핀에 접속된다. 상술한 DDC는, SDA 신호가 전송되는 라인 및 SCL 신호가 전송되는 라인에 의해 구성된다.

- [0073] 또한, 상술한 바와 같이 소스 기기가 싱크 기기의 접속을 검출하기 위한 HPD 라인(HEAC-라인)은, 핀 번호가 19인 핀에 접속된다. 또한, 유털리티 라인(HEAC+라인)은, 핀 번호가 14인 핀에 접속된다. 또한, 상술한 바와 같이 전원을 공급하기 위한 전원 라인은, 핀 번호가 18인 핀에 접속된다.

- [0074] 도 5는, 도 1의 AV 시스템(100)에서의, 소스 기기(110)의 데이터 송신부(112)와, 싱크 기기(120)의 데이터 수신부(122)의 구성례를 도시하고 있다. 이 구성례는, 데이터 송신부(112) 및 데이터 수신부(122)의 디지털 인터페이스가, 신규격의 디지털 인터페이스인 경우를 도시하고 있다. 이 도 5에서, 도 2와 대응하는 부분에는 동일 부호를 붙여서 나타내고, 적절히, 그 상세 설명을 생략한다.

- [0075] 데이터 송신부(112)는, 유효 화상 구간(이하, 적절히, 액티브 비디오 구간이라고도 한다)에서, 비압축의 1화면 분의 화상의 화소 데이터에 대응하는 차동 신호를, 복수의 채널로, 데이터 수신부(122)에 일방향으로 송신한다. 여기서, 유효 화상 구간은, 하나의 수직 동기 신호로부터 다음의 수직 동기 신호까지의 구간에서, 수평 귀선 구간 및 수직 귀선 구간을 제외한 구간이다. 또한, 데이터 송신부(112)는, 수평 귀선 구간 또는 수직 귀선 구간에서, 적어도 화상에 부수되는 음성 데이터나 제어 데이터, 그 밖의 보조 데이터 등에 대응하는 차동 신호를, 하나의 TMDS 채널(#0)로, 데이터 수신부(122)에 일방향으로 송신한다.

- [0076] 이 경우, TMDS 클록은, HDMI 규격(도 2 참조)의 경우의 3배가 됨으로써, TMDS 채널(#0)만으로의 전송을 가능하게 하고 있다. 또한, TMDS 클록 자신도, TMDS 채널(#0)에 커먼 모드로 삽입함으로써, TMDS 클록 채널도 불필요하게 하고 있다. 그 때문에, 이 신규격의 디지털 인터페이스에서는, HDMI 리셉터클(A 타입)의 각 핀 중, HDMI 규격의 디지털 인터페이스인 경우에 TMDS 채널(#1), TMDS 채널(#2), TMDS 클록 채널에서 사용되고 있는 9개의 핀(PIN(1-6, 10-12))은, 미사용이 된다.

- [0077] 데이터 송신부(112)는, 트랜스미터(81A)를 갖는다. 이 트랜스미터(81A)는, 예를 들면, 비압축의 화상의 화소 데이터를 대응하는 차동 신호로 변환하고, 하나의 TMDS 채널(#0)로, HDMI 케이블 또는 신규격 케이블을 통하여 접속되어 있는 데이터 수신부(122)에, 일방향으로 시리얼 전송한다.

- [0078] 또한, 트랜스미터(81A)는, 비압축의 화상에 부수되는 음성 데이터, 나아가서는, 필요한 제어 데이터 그 밖의 보조 데이터 등을, 대응하는 차동 신호로 변환하고, 하나의 TMDS 채널(#0)로 데이터 수신부(122)에, 일방향으로 시리얼 전송한다.

- [0079] 데이터 수신부(122)는, 액티브 비디오 구간에서, 하나의 채널(#0)로, 데이터 송신부(112)로부터 일방향으로 송신되어 오는, 화소 데이터에 대응하는 차동 신호를 수신한다. 또한, 이 데이터 수신부(122)는, 수평 귀선 구간 또는 수직 귀선 구간에서, 하나의 채널(#0)로, 데이터 송신부(112)로부터 일방향으로 송신되어 오는, 음성 데이터나 제어 데이터에 대응하는 차동 신호를 수신한다.

- [0080] 즉, 데이터 수신부(122)는, 레시버(82A)를 갖는다. 이 레시버(82A)는, TMDS 채널(#0)로, 데이터 송신부(112)로부터 일방향으로 송신되어 오는, 화소 데이터에 대응하는 차동 신호와, 음성 데이터나 제어 데이터에 대응하는 차동 신호를 수신한다.

- [0081] 도 5에 도시하는 신규격의 경우에 있어서의 데이터 송신부(112)와 데이터 수신부(122)의 구성례의 기타는, 도 2에 도시하는 HDMI 규격의 경우에 있어서의 데이터 송신부(112)와 데이터 수신부(122)의 구성례와 마찬가지이기 때문에, 그 상세 설명은 생략한다.

- [0082] 도 6은, 도 1의 AV 시스템(100)에서의, 소스 기기(110)의 데이터 송신부(112)와, 싱크 기기(120)의 데이터 수신부(122)의 구성례를 도시하고 있다. 이 구성례도, 데이터 송신부(112) 및 데이터 수신부(122)의 디지털 인터페이스가, 신규격의 디지털 인터페이스인 경우를 도시하고 있다. 이 도 6에서, 도 5와 대응하는 부분에는 동일 부호를 붙여서 나타내고, 적절히, 그 상세 설명을 생략한다.

- [0083] 이 도 6에 도시하는 구성례의 경우, 도 5의 구성례와 마찬가지로, 데이터 송신부(112)는, 수평 귀선 구간 또는 수직 귀선 구간에서, 적어도 화상에 부수되는 음성 데이터나 제어 데이터, 그 밖의 보조 데이터 등에 대응하는 차동 신호를, 하나의 TMDS 채널(#0)로, 데이터 수신부(122)에 일방향으로 송신한다.

- [0084] 이 경우, TMDS 클록은, HDMI 규격(도 2 참조)의 경우의 3배가 됨으로써, TMDS 채널(#0)만으로의 전송을 가능하게 하고 있다. 또한, TMDS 클록 자신도, TMDS 채널(#0)에 커먼 모드로 삽입함으로써, TMDS 클록 채널도 불필요하게 하고 있다. 이 경우, HDMI 리셉터클의 PIN(1, 2)의 2핀이 사용된다.

- [0085] 또한, 이 도 6의 구성례에서는, CEC, DDC, HPD의 라인으로서, 1개의 컨트롤 라인(Control Line)이 사용된다. 또한, 전원 라인(+5V Power Line)은 생략된다. 또한, USB와 같이 휴대 소스 기기 충전용으로 VBUS 라인(VBUS Line)이 추가되고, 또한, 공통으로 그라운드 라인(Ground Line)이 마련된다.

- [0086] 컨트롤 라인은, 핀 번호가 3인 핀에 접속된다. 또한, VBUS 라인은, 핀 번호가 4인 핀에 접속된다. 또한, 그라운드 라인은, 핀 번호가 5인 핀에 접속된다. 그 때문에, 이 도 6에 도시하는 신규격의 디지털 인터페이스에서는, HDMI 리셉터클(A 타입)의 각 핀 중, PIN(6 - 19)의 14핀이 미사용이 된다.

- [0087] 도 1에 도시하는 AV 시스템(100)에서, 싱크 기기(120)의 데이터 수신부(122)는, HDMI 규격 및 신규격의 쌍방의 디지털 인터페이스에 대응 가능한 경우, 소스 기기(110)의 데이터 송신부(112)의 디지털 인터페이스에 맞춘 동작을 행하도록 제어된다. 즉, 제어부(123)는, 파워 온 후에, 커넥터부(121)에 케이블(200)이 접속되어 있을 때, 소스 기기(110)의 데이터 송신부(112)의 디지털 인터페이스가 HDMI 규격인지 신규격인지를 판별하고, 그 판별 결과에 응하여 데이터 수신부(122)의 동작을 제어한다.

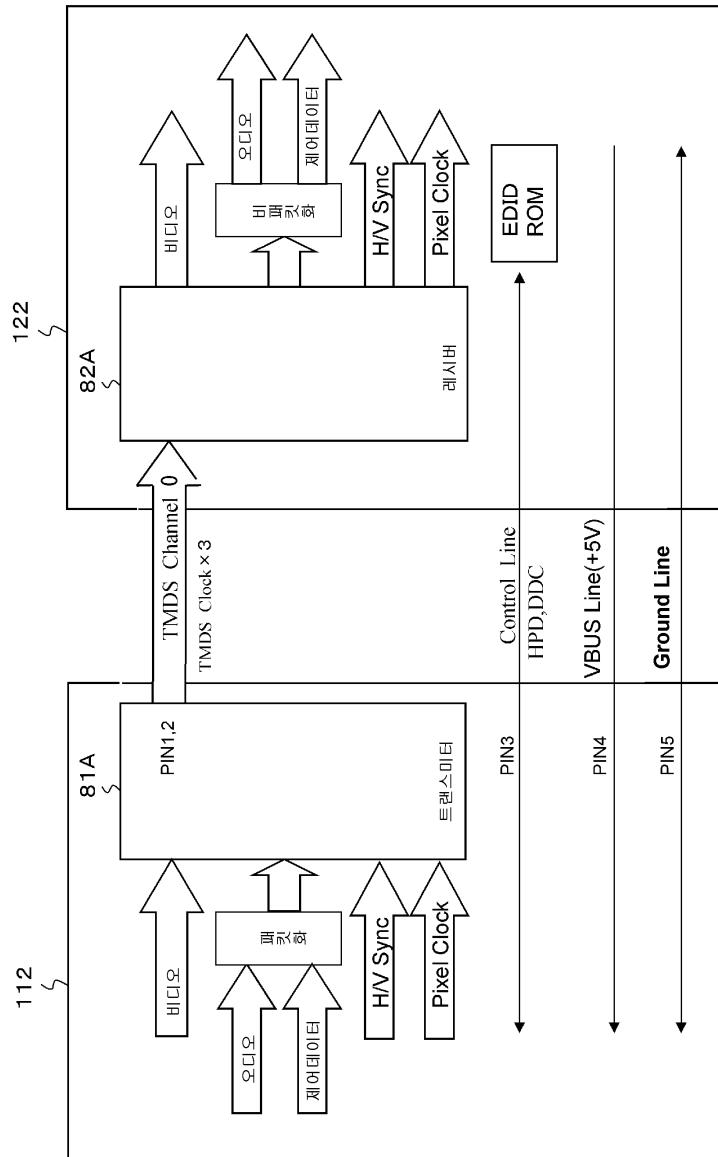

- [0088] 도 7의 플로우 차트는, 제어부(123)의 제어 순서를 도시하고 있다. 우선, 제어부(123)는, 스텝 ST1에서, 파워 온으로 처리를 시작하고, 그 후에, 스텝 ST2의 케이블 검출 모드의 처리로 이동한다. 이 케이블 검출 모드에서 는, 커넥터부(121)의 18핀의 전압, 케이블 접속을 검출하는 센서의 출력 등으로부터, 케이블(200)의 커넥터부(121)에의 접속을 검출한다.

- [0089] 다음에, 제어부(123)는, 스텝 ST3에서, 스텝 ST2의 검출 결과에 의거하여, 케이블(200)이 커넥터부(121)에 접속되었는지의 여부를 판단한다. 커넥터부(121)에 케이블(200)이 접속되어 있을 때, 제어부(123)는, 스텝 ST4의 처리로 이동한다. 이 스텝 ST4에서, 제어부(123)는, 판별부(124)의 판별 결과에 의거하여, 소스 기기(110)의 데이터 송신부(112)의 디지털 인터페이스가 HDMI 규격인지 신규격인지를 판별한다.

- [0090] HDMI 규격일 때, 제어부(123)는, 스텝 ST5에서, 데이터 수신부(122)를, HDMI 규격의 디지털 인터페이스에 맞춘 동작 모드(HDMI 모드)로 제어한다. 또한, 신규격일 때, 제어부(123)는, 스텝 ST6에서, 데이터 수신부(122)를, 신규격의 디지털 인터페이스에 맞춘 동작 모드(신규격 모드)로 제어한다. 제어부(123)는, 스텝 ST5 또는 스텝 ST6의 처리의 후, 스텝 ST7에서, 케이블(200)의 인발이 있었는지의 여부를 판별하고, 케이블(200)의 인발이 없는 한, 데이터 수신부(122)의 동작 모드를 그대로 유지한다. 한편, 데이터의 인발이 있는 때는, 곧바로, 스텝 ST2로 되돌아온다.

- [0091] 또한, 도 1에 도시하는 AV 시스템(100)에서, 소스 기기(110)의 데이터 송신부(112)는, HDMI 규격 및 신규격의 쌍방의 디지털 인터페이스에 대응 가능한 경우, 싱크 기기(120)의 데이터 수신부(122)의 디지털 인터페이스에 맞춘 동작을 행하도록 제어된다. 즉, 제어부(113)는, 파워 온 후에, 커넥터부(111)에 케이블(200)이 접속되어 있을 때, 싱크 기기(120)의 데이터 수신부(122)의 디지털 인터페이스가 HDMI 규격인지 신규격인지를 판별하고, 그 판별 결과에 응하여 데이터 송신부(112)의 동작을 제어한다. 이 제어부(113)의 제어 순서는, 상세 설명은 생략하지만, 상술한 싱크 기기(120)의 제어부(123)의 제어 순서와 마찬가지이다(도 7 참조).

- [0092] [판별부의 구성례]

- [0093] 다음에, 싱크 기기(120)의 제어부(123) 내의 판별부(124), 소스 기기(110)의 제어부(113) 내의 판별부(114)의

구성례를 설명한다.

[0094] [제1의 구성례]

이 구성례는, TMDS 차동 신호선만으로 판별하는 예이다. 복수의 TMDS 차동 신호 페어 중, 1페어만이 액티브한 신호 페어인 것을 검출한다. 예를 들면, 도 5의 구성례로 도시한 바와 같이, HDMI 규격에서는 3개의 TMDS 채널(#0 내지 #2)이 사용되지만, 신규격(도 5 참조)에서는 하나의 TMDS 채널(#0)만이 사용된다. 그 때문에, 신규격에서는, TMDS 채널(#1, #2) 및 TMDS 클록 채널은 미사용이 된다.

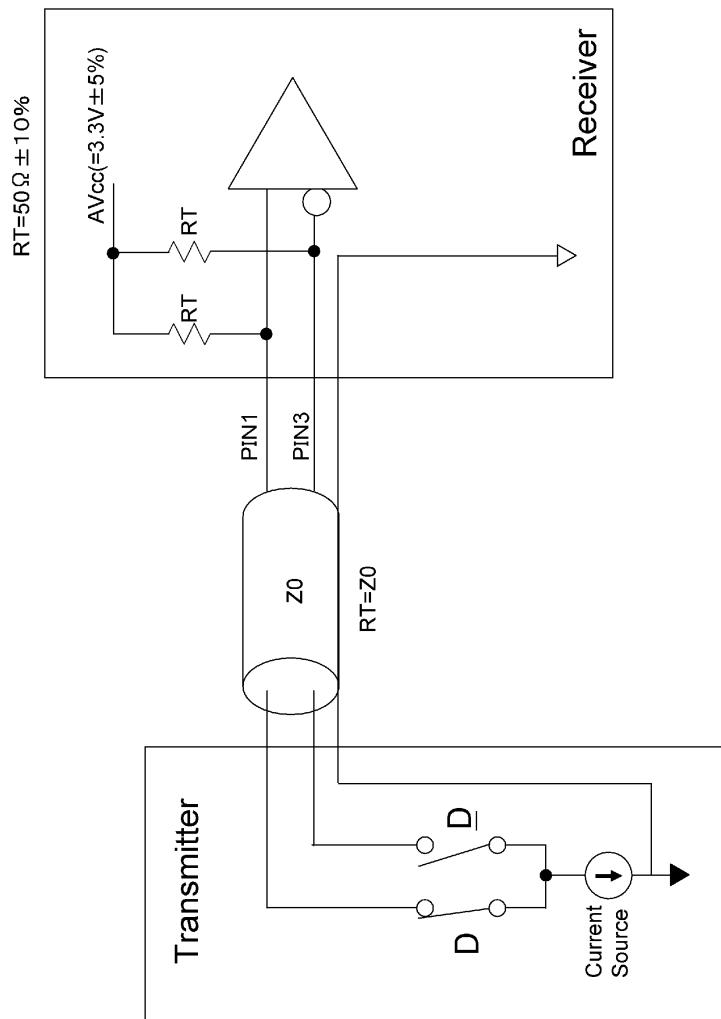

[0096] 이 구성례에서는, 소스 기기(110)의 데이터 송신부(112)가 HDMI 규격의 디지털 인터페이스로 동작하는 경우에 차동 신호가 입력되고, 또한, 소스 기기(110)의 송신부(112)가 신규격(도 5 참조)의 디지털 인터페이스로 동작하는 경우에 차동 신호가 입력되지 않는 한 쌍의 핀, 예를 들면 PIN(1, 3)에 대해, 액티브 범위 검출 회로가 마련된다. 이 액티브 범위 검출 회로의 검출 결과에 의해, 소스 기기(110)의 데이터 송신부(112)의 디지털 인터페이스가 HDMI 규격인지 신규격인지의 판단이 가능해진다.

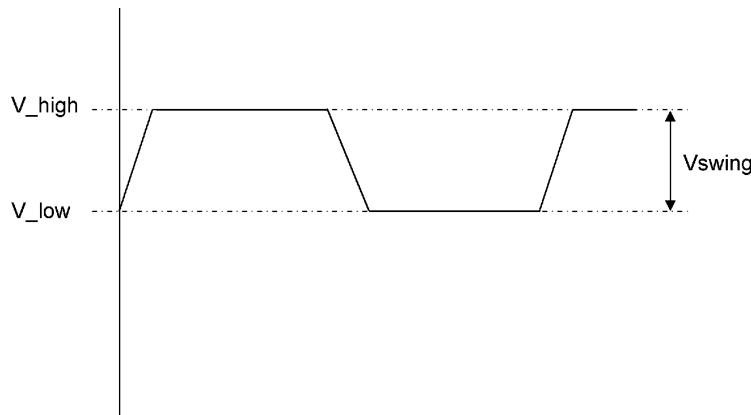

[0097] 도 8은, TMDS 차동 신호 페어의 모식도를 도시하고 있다. 이 도 8에서, TMDS 차동 신호는, 도 9에 도시하는 바와 같이, 상한 전압(V\_high), 하한 전압(V\_low), 진폭(Vswing)으로서, 이 범위 내에서 동작한다. 액티브 범위 검출 회로는, 차동 신호 페어의 어느 것이나 TMDS의 규정 전압 범위 내라면, 「H」를 출력하고, 차동 신호 페어 중 어느 한편, 또는 양쪽이 TMDS의 규정 전압 범위 외라면, 「L」을 출력하는 회로이다.

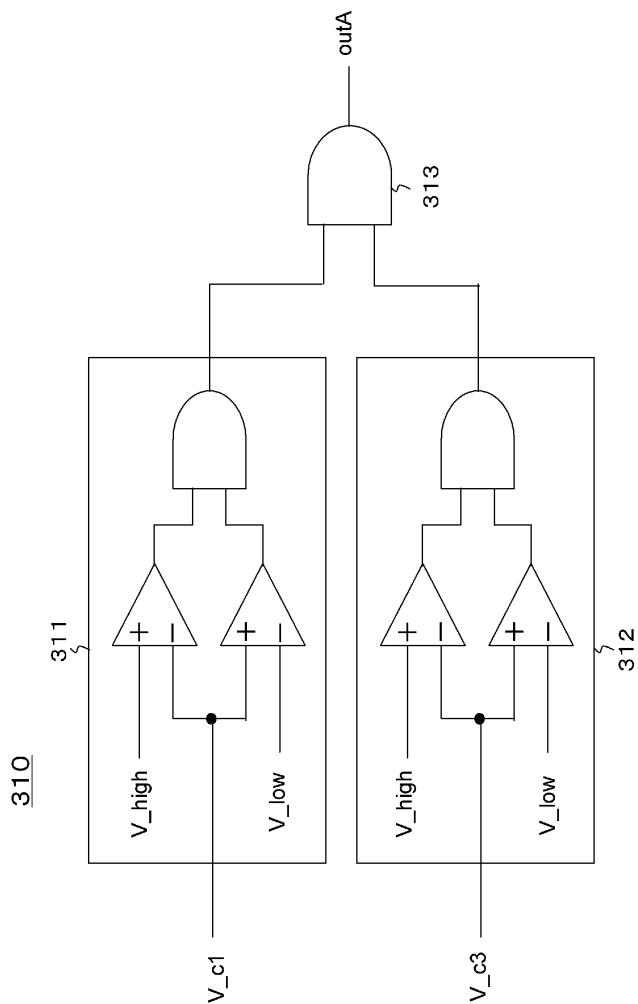

[0098] 도 10은, 디지털 인터페이스 판단용의 액티브 범위 검출 회로(310)의 구체적인 회로예를 도시하고 있다. 이 회로예는, 2개의 원드 콤파레이터(311, 312)와, 1개의 앤드 회로(313)에 의해 구성된다. 원드 콤파레이터(311, 312)는, TMDS의 상한 전압을 V\_high, 하한 전압을 V\_low로 하고, 차동 신호 페어의 1개를 V\_c에 접속하면,  $V_{high} > V_c > V_{low}$ 의 지정 범위 내라면, 앤드 회로 출력은 「H」가 된다. 원드 콤파레이터(311)에는, PIN(1)의 전압(V\_c1)이 입력되고, 원드 콤파레이터(312)에는, PIN(3)의 전압(V\_c3)이 입력된다. 그리고, 원드 콤파레이터(311, 312)의 출력이 앤드 회로(313)에 입력되고, 이 앤드 회로(313)의 출력이 액티브 범위 검출 회로(310)의 출력(outA)이 된다.

[0099] 또한, 이 구성례에서는, 소스 기기(110)의 데이터 송신부(112)가 HDMI 규격의 디지털 인터페이스로 동작하는 경우 및 소스 기기(110)의 송신부(112)가 신규격(도 5 참조)의 디지털 인터페이스로 동작하는 경우의 어느 경우에도 차동 신호가 입력되는 한 쌍의 핀, 예를 들면 PIN(7, 9)에 대해, 액티브 범위 검출 회로가 마련된다. 이 액티브 범위 검출 회로의 검출 결과에 의해, 소스 기기(110)가 케이블(200)을 통하여 접속되어 있는지의 여부의 판단이 가능해진다.

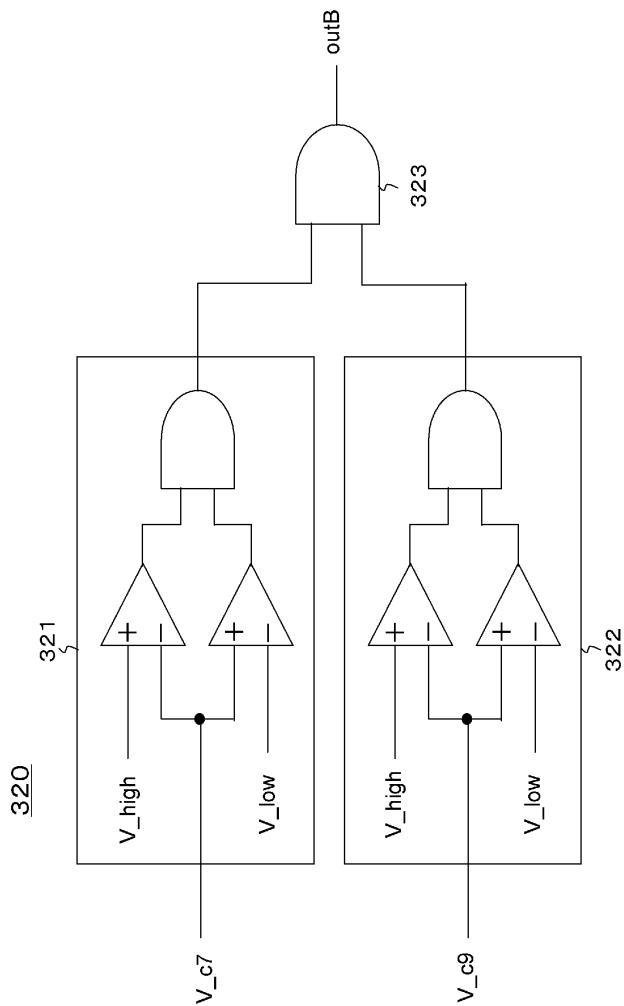

[0100] 도 11은, 소스 기기 접속 판단용의 액티브 범위 검출 회로(320)의 구체적인 회로예를 도시하고 있다. 이 회로예는, 2개의 원드 콤파레이터(321, 322)와, 1개의 앤드 회로(323)에 의해 구성된다. 원드 콤파레이터(321, 322)는, TMDS의 상한 전압을 V\_high, 하한 전압을 V\_low로 하고, 차동 신호 페어의 1개를 V\_c에 접속하면,  $V_{high} > V_c > V_{low}$ 의 지정 범위 내라면, 앤드 회로 출력은 「H」가 된다. 원드 콤파레이터(321)에는, PIN(7)의 전압(V\_c7)이 입력되고, 원드 콤파레이터(322)에는, PIN(9)의 전압(V\_c9)이 입력된다. 그리고, 원드 콤파레이터(321, 322)의 출력이 앤드 회로(323)에 입력되고, 이 앤드 회로(323)의 출력이 액티브 범위 검출 회로(320)의 출력(outB)이 된다.

[0101] 도 10, 도 11에 도시하는 액티브 범위 검출 회로(310, 320)의 출력(outA, outB)은 이하와 같이 된다. 즉, 소스 기기(110)가 접속되어 있고, 이 소스 기기(110)의 데이터 송신부(112)의 디지털 인터페이스가 HDMI 규격인 경우에는, outA=「H」, outB=「H」가 된다. 또한, 소스 기기(110)가 접속되어 있고, 이 소스 기기(110)의 데이터 송신부(112)의 디지털 인터페이스가 신규격인 경우에는, outA=「L」, outB=「H」가 된다. 또한, 소스 기기(110)가 접속되지 않은 경우에는, outA=「L」, outB=「L」이 된다.

[0102] 도 10, 도 11에 도시하는 액티브 범위 검출 회로(310, 320)를 마련함으로써, 소스 기기(110)가 접속되어 있는지의 여부의 판단, 및, 그 데이터 송신부(112)의 디지털 인터페이스가 HDMI 규격인지 신규격인지의 판단이 가능해진다.

[0103] 또한, 상술한 설명에서는, 싱크 기기(120)의 제어부(123) 내의 판별부(124)에 마련되는 액티브 범위 검출 회로(310, 320)에 관해 설명하였다. 그러나, 마찬가지의 액티브 범위 검출 회로를, 소스 기기(110)의 제어부(113) 내의 판별부(114)에 마련함으로써, 싱크 기기(120)가 접속되어 있는지의 여부의 판단, 및, 그 데이터 수신부(122)의 디지털 인터페이스가 HDMI 규격인지 신규격인지의 판단이 가능해진다.

- [0104] 이 경우, 소스 기기(110)의 데이터 송신부(112)가 HDMI 규격의 디지털 인터페이스로 동작하는 경우에 차동 신호를 출력하고, 또한, 소스 기기(110)의 송신부(112)가 신규격(도 5 참조)의 디지털 인터페이스로 동작하는 경우에 차동 신호를 출력하지 않는 한 쌍의 핀, 예를 들면 PIN(1, 3)에 대해, 액티브 범위 검출 회로가 마련된다. 이 액티브 범위 검출 회로의 검출 결과에 의해, 싱크 기기(120)의 데이터 수신부(122)의 디지털 인터페이스가 HDMI 규격인지 신규격인지의 판단이 가능해진다.

- [0105] 또한, 이 경우, 소스 기기(110)의 데이터 송신부(112)가 HDMI 규격의 디지털 인터페이스로 동작하는 경우 및 소스 기기(110)의 송신부(112)가 신규격(도 5 참조)의 디지털 인터페이스로 동작하는 경우의 어느 경우에도 차동 신호를 출력하는 한 쌍의 핀, 예를 들면 PIN(7, 9)에 대해, 액티브 범위 검출 회로가 마련된다. 이 액티브 범위 검출 회로의 검출 결과에 의해, 싱크 기기(120)가 케이블(200)을 통하여 접속되어 있는지의 여부의 판단이 가능해진다.

- [0106] [제2의 구성례]

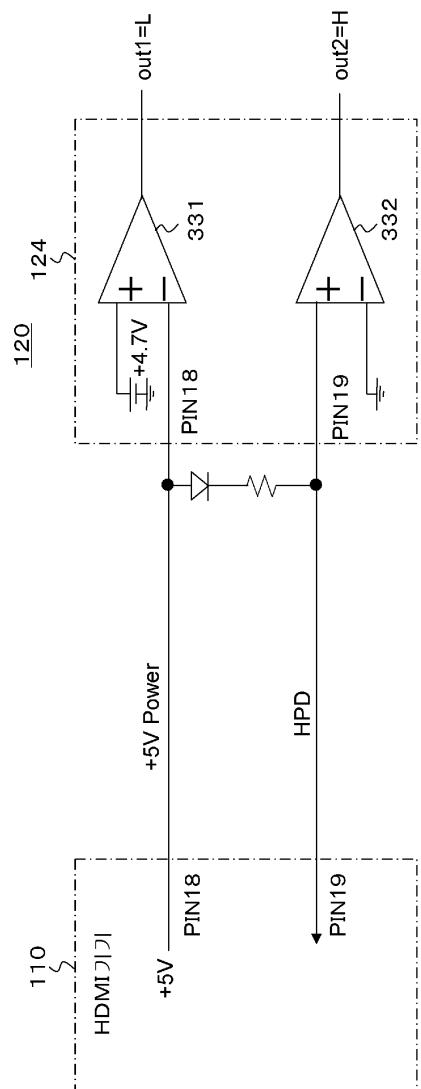

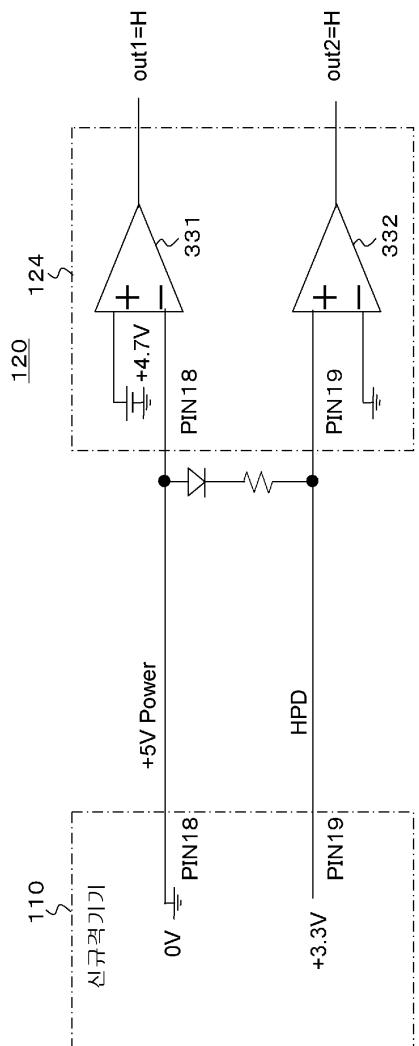

- [0107] 이 구성례는, TMDS 차동 신호선 이외에서 판별하는 예이다. 신규격(도 6 참조)에서는, 18핀에 접속되는 전원 라인(+5V Power Line), 및 19핀에 접속되는 HPD 라인은 사용되지 않는다. 그래서, 이 예에서는, 이 전원 라인 및 HPD 라인을 사용한다.

- [0108] 소스 기기(110)의 데이터 송신부(112)가 HDMI 규격의 디지털 인터페이스로 동작하는 경우, 도 12에 도시하는 바와 같이, 소스 기기(110)로부터 싱크 기기(120)에 전원 라인으로 +5V의 전원이 공급된다. 싱크 기기(120)에서는, 이 전원 라인이 접속되는 커넥터부(121)의 18핀과, HPD 라인이 접속되는 커넥터부(121)의 19핀이, 다이오드 및 저항을 통하여 접속되어 있다. 그 때문에, 소스 기기(110)에 싱크 기기(120)가 접속되는 경우에는 HPD 라인의 전압이 높아지기 때문에, 소스 기기(110)에서는 싱크 기기(120)가 접속된 것을 확인할 수 있다.

- [0109] 이 구성례에서는, 소스 기기(110)의 데이터 송신부(112)가 신규격(도 6 참조)의 디지털 인터페이스로 동작하는 경우, 도 13에 도시하는 바와 같이, 18핀은 HDMI 규격으로 인가되는 전압(최저 +4.7V)을 하회하는 전압, 예를 들면 0V로 설정된다. 또한, 19핀은, 18핀에 인가되는 전압보다 높은 전압, 예를 들면, +3.3V로 설정된다.

- [0110] 이 구성례에서는, 싱크 기기(120)의 제어부(123) 내의 판별부(124)에는, 2개의 전압 콤파레이터(331, 332)가 마련된다. 전압 콤파레이터(331)의 정 입력단자에는 +4.7V가 입력되고, 그 부 입력단자에는, 커넥터부(121)의 18핀의 전압이 입력된다. 또한, 전압 콤파레이터(332)의 정 입력단자에는, 커넥터부(121)의 19핀의 전압이 입력되고, 그 부 입력단자는 0V가 입력된다.

- [0111] 도 12, 도 13에 도시하는 전압 콤파레이터(331, 332)의 출력(out1, out2)은 이하와 같이 된다. 즉, 소스 기기(110)가 접속되어 있고, 이 소스 기기(110)의 데이터 송신부(112)의 디지털 인터페이스가 HDMI 규격인 경우에는, out1=「L」, out2=「H」가 된다. 또한, 소스 기기(110)가 접속되어 있고, 이 소스 기기(110)의 데이터 송신부(112)의 디지털 인터페이스가 신규격인 경우에는, out1=「H」, out2=「H」가 된다.

- [0112] 이와 같이, 이 구성례에서는, 전압 콤파레이터(331, 332)의 출력(out1, out2)에 의해, 데이터 송신부(112)의 디지털 인터페이스가 HDMI 규격인지 신규격인지의 판단이 가능해진다. 케이블 미접속인 경우, HPD 라인 +3.3V로 설정할 수가 없기 때문에, 케이블 접속 판정은 불필요하다. 또한, 다이오드와 저항은, HDMI 규격 기기의 경우 필요하지만, 신규격 접속의 경우에는 다이오드가 역바이어스이기 때문에 무도통이 되어, 전혀 동작에 지장은 없다.

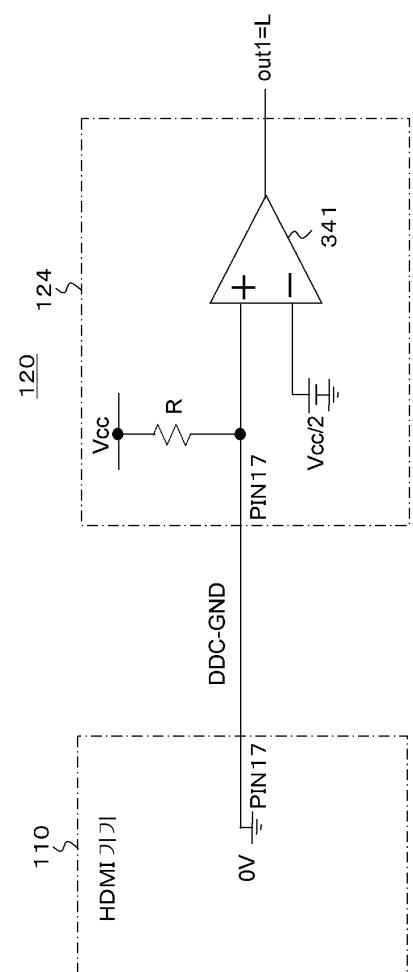

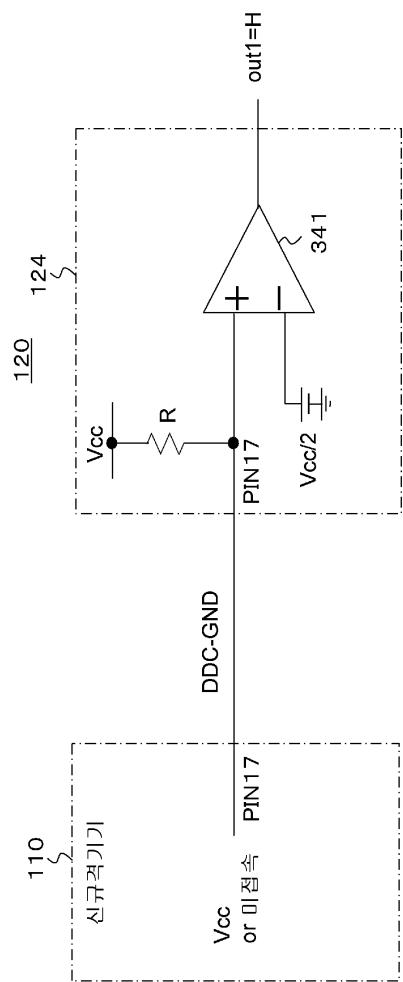

- [0113] [제3의 구성례]

- [0114] 이 구성례도, TMDS 차동 신호선 이외에서 판별하는 예이다. 신규격(도 6 참조)에서는, 17핀에 접속된 DDC-GND 라인은 사용되지 않는다. 그래서, 이 예에서는, 이 DDC-GND 라인을 사용한다.

- [0115] 소스 기기(110)의 데이터 송신부(112)가 HDMI 규격의 디지털 인터페이스로 동작하는 경우, 도 14에 도시하는 바와 같이, 소스 기기(110)에서, DDC-GND 라인이 접속되는 17핀은 접지된다. 이 구성례에서는, 소스 기기(110)의 데이터 송신부(112)가 신규격(도 6 참조)의 디지털 인터페이스로 동작하는 경우, 도 15에 도시하는 바와 같이, 17핀에는 Vcc(예를 들면 +5V)가 인가되던지, 또는 이 17핀은 미접속, 즉 전기적으로 끊어 상태가 된다.

- [0116] 이 구성례에서는, 싱크 기기(120)에서, 커넥터부(121)의 17핀은 저항(R)을 통하여 Vcc에 풀업된다. 또한, 싱크 기기(120)의 제어부(123) 내의 판별부(124)에는, 1개의 전압 콤파레이터(341)가 마련된다. 전압 콤파레이터(341)의 정 입력단자에는, 커넥터부(121)의 17핀의 전압이 입력된다. 또한, 전압 콤파레이터(341)의 부 입력단

자에는, Vcc/2가 입력된다.

[0117] 도 14, 도 15에 도시하는 전압 콤파레이터(341)의 출력(out1)은 이하와 같이 된다. 즉, 소스 기기(110)가 접속되어 있고, 이 소스 기기(110)의 데이터 송신부(112)의 디지털 인터페이스가 HDMI 규격인 경우에는, out1=「L」이 된다. 또한, 소스 기기(110)가 접속되어 있고, 이 소스 기기(110)의 데이터 송신부(112)의 디지털 인터페이스가 신규격인 경우에는, out1=「H」가 된다.

[0118] 이와 같이, 이 구성례에서는, 전압 콤파레이터(341)의 출력(out1)에 의해, 데이터 송신부(112)의 디지털 인터페이스가 HDMI 규격인지 신규격인지의 판단이 가능해진다. 이 구성례에서는, 소스 기기(110)의 데이터 송신부(112)의 디지털 인터페이스가 신규격인 경우와, 미접속인 경우의 구별이 되지 않기 때문에, 별도 케이블 접속 판정이 필요한다.

[0119] [제4의 구성례]

[0120] 이 구성례도, TMDS 차동 신호선 이외에서 판별하는 예이다. 신규격(도 6 참조)에서는, 17핀에 접속되는 DDC-GND 라인은 사용되지 않는다. 그래서, 이 예에서는, 이 DDC-GND 라인을 사용한다.

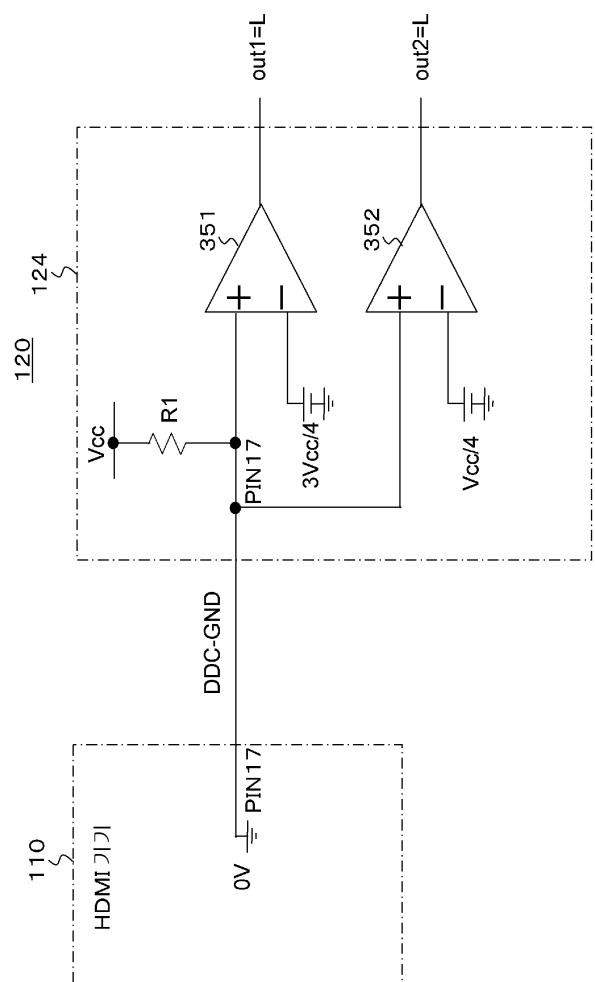

[0121] 소스 기기(110)의 데이터 송신부(112)가 HDMI 규격의 디지털 인터페이스로 동작하는 경우, 도 16에 도시하는 바와 같이, 소스 기기(110)에서, DDC-GND 라인이 접속되는 17핀은 접지된다. 이 구성례에서는, 소스 기기(110)의 데이터 송신부(112)가 신규격(도 6 참조)의 디지털 인터페이스로 동작하는 경우, 도 17에 도시하는 바와 같이, 17핀은 저항(R2)을 통하여 접지된다.

[0122] 이 구성례에서는, 싱크 기기(120)에서, 커넥터부(121)의 17핀은 저항(R1)(=R1)을 통하여 Vcc(예를 들면, +5V)에 풀업된다. 또한, 싱크 기기(120)의 제어부(123) 내의 판별부(124)에는, 2개의 전압 콤파레이터(351, 352)가 마련된다. 전압 콤파레이터(351, 352)의 정 입력단자에는, 커넥터부(121)의 17핀의 전압이 입력된다.

[0123] 또한, 전압 콤파레이터(351)의 부 입력단자에는, 3Vcc/4가 입력된다. 이 경우, 이 전압 콤파레이터(351)에서는, 17핀의 전압이, Vcc를 저항(R1)과 저항(R2)으로 분압하여 얻어지는 전압의 상측의 전압과 비교된다. 또한, 전압 콤파레이터(352)의 부 입력단자에는, Vcc/4가 입력된다. 이 경우, 이 전압 콤파레이터(352)에서는, 17핀의 전압이, Vcc를 저항(R1)과 저항(R2)으로 분압하여 얻어지는 전압의 하측의 전압과 비교된다.

[0124] 도 16, 도 17에 도시하는 전압 콤파레이터(351, 352)의 출력(out1, out2)은 이하와 같이 된다. 즉, 소스 기기(110)가 접속되어 있고, 이 소스 기기(110)의 데이터 송신부(112)의 디지털 인터페이스가 HDMI 규격인 경우에는, out1=「L」, out2=「L」이 된다. 또한, 소스 기기(110)가 접속되어 있고, 이 소스 기기(110)의 데이터 송신부(112)의 디지털 인터페이스가 신규격인 경우에는, out1=「L」, out2=「H」가 된다. 또한, 소스 기기(110)가 접속되어 있지 않은 경우에는, out1=「H」, out2=「H」가 된다.

[0125] 이와 같이, 이 구성례에서는, 전압 콤파레이터(351, 352)의 출력(out1, out2)에 의해, 소스 기기(110)가 접속되어 있는지의 여부의 판단, 데이터 송신부(112)의 디지털 인터페이스가 HDMI 규격인지 신규격인지의 판단이 가능해진다.

[0126] [제5의 구성례]

[0127] 이 구성례도, TMDS 차동 신호선 이외에서 판별하는 예이다. 신규격(도 6 참조)에서는, 17핀에 접속되는 DDC-GND 라인은 사용되지 않는다. 그래서, 이 예에서는, 이 DDC-GND 라인을 사용한다.

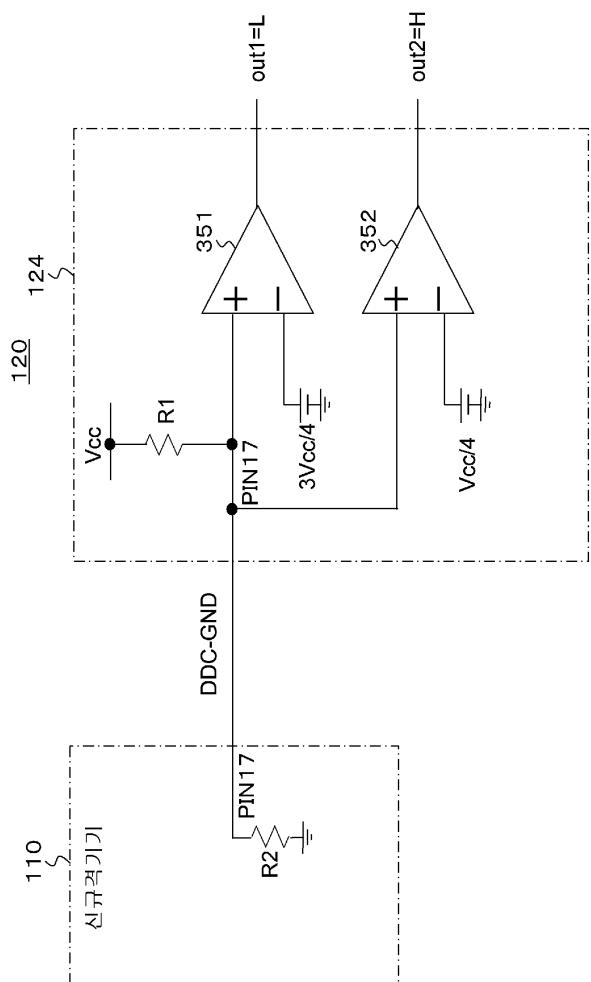

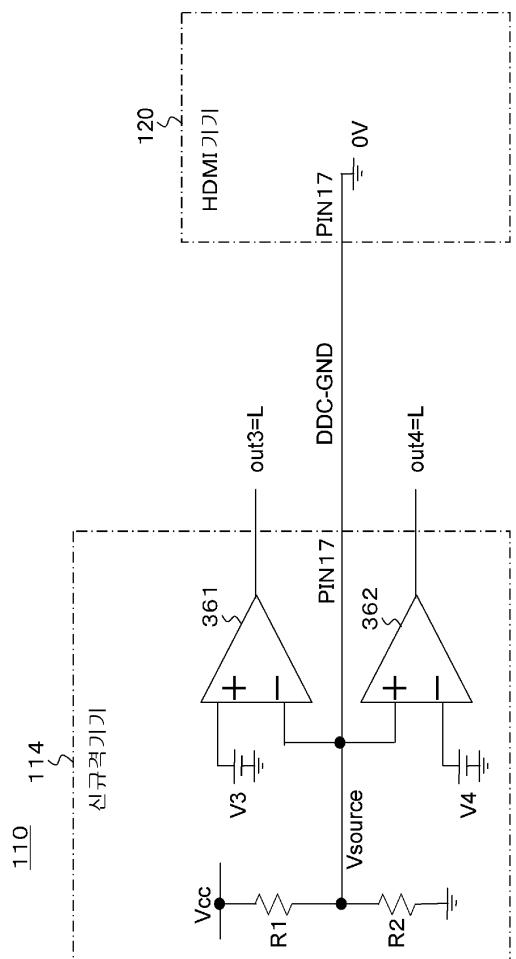

[0128] 소스 기기(110)가 HDMI 기기인 경우, 도 18에 도시하는 바와 같이, 소스 기기(110)에서, DDC-GND 라인이 접속되는 17핀은 접지된다. 또한, 소스 기기(110)가 신규격 기기(도 6 참조)인 경우, 도 19에 도시하는 바와 같이, Vcc(예를 들면, +5V)가 저항(R1과 R2)으로 분압되어서 얻어진 전압이, 17핀에 인가된다. 또한, 제어부(113) 내의 판별부(114)에는, 2개의 전압 콤파레이터(361, 362)가 마련된다. 이 전압 콤파레이터(361)의 부 입력단자 및 전압 콤파레이터(362)의 정 입력단자에는, 커넥터부(111)의 17핀의 전압이 입력된다. 또한, 전압 콤파레이터(361)의 정 입력단자에는, 전압(V3)이 입력된다. 또한, 전압 콤파레이터(362)의 부 입력단자에는, 전압(V4)이 입력된다.

[0129] 또한, 싱크 기기(120)가 HDMI 기기인 경우, 도 20에 도시하는 바와 같이, 싱크 기기(120)에서, DDC-GND 라인이 접속되는 17핀은 접지된다. 또한, 싱크 기기(120)가 신규격 기기(도 6 참조)인 경우, 도 19에 도시하는 바와 같이, 17핀은, 저항(R1)을 통하여 전압(Vcc)에 풀업된다. 또한, 제어부(123) 내의 판별부(124)에는, 2개의 전압 콤파레이터(363, 364)가 마련된다. 이 전압 콤파레이터(363)의 부 입력단자 및 전압 콤파레이터(364)의 정 입력

단자에는, 커넥터부(111)의 17핀의 전압이 입력된다. 또한, 전압 콤퍼레이터(363)의 정 입력단자에는, 전압(V1)이 입력된다. 또한, 전압 콤퍼레이터(364)의 부 입력단자에는, 전압(V2)이 입력된다.

[0130] 여기서,  $R1=2*R2$ 이 된다. 싱크 기기(120)측의 커넥터부(121)의 17핀의 전압(Vsink)은, 이하와 같이 계산된다. 즉, 도 18의 경우에는,  $Vsink=0$ , 도 19의 경우에는,  $Vsink=Vcc/2$ , 케이블 미접속인 경우에는,  $Vsink=Vcc$ 가 된다. 또한, 소스 기기(110)측의 커넥터부(111)의 17핀의 전압(Vsource)은, 이하와 같이 계산된다. 즉, 도 19의 경우에는,  $Vsource=Vcc/2$ , 도 20의 경우에는,  $Vsource=0$ , 케이블 미접속인 경우에는,  $Vsink=Vcc/3$ 이 된다.

[0131] 따라서, 비교 전압(V1, V2, V3, V4)을 다음의 식과 같이 설정하면, 전압 콤퍼레이터의 출력(out1과 out2, out3과 out4)의 조합으로 각 접속상태를 검출할 수 있다. 또한, 케이블 미접속인 경우는, out1 내지 out4 모든 출력이 「H」가 된다.

[0132]  $V1 = 3/4*Vcc$

[0133]  $V2 = 1/4*Vcc$

[0134]  $V3 = 5/12*Vcc$

[0135]  $V4 = 1/4*Vcc$

[0136] 또한, 도 19의 경우에는, 싱크 기기(120)의 전압 콤퍼레이터(363)에서는, 17핀의 전압이, Vcc를 저항(R1, R1)의 병렬 저항과 저항(R2)으로 분압하여 얻어지는 전압의 상측의 전압과 비교된다. 또한, 싱크 기기(120)의 전압 콤퍼레이터(364)에서는, 17핀의 전압이, Vcc를 저항(R1, R1)의 병렬 저항과 저항(R2)으로 분압하여 얻어지는 전압의 하측의 전압과 비교된다.

#### [제6의 구성례]

[0138] 이 구성례는, TMDS 차동 신호선만으로 판별하는 예이다. 이 구성례에서는, 소스 기기(110)의 데이터 송신부(112)가 HDMI 규격의 디지털 인터페이스로 동작하는 경우에 차동 신호가 입력되고, 또한, 소스 기기(110)의 송신부(112)가 신규격(도 5 참조)의 디지털 인터페이스로 동작하는 경우에 차동 신호가 입력되지 않는 한 쌍의 핀, 예를 들면 PIN(1, 3)에 주목한다.

[0139] 여기서, 싱크 기기측의 PIN(1)과 PIN(3)의 임피던스는, 이하와 같이 된다.

[0140] (1) HDMI 케이블이 삽입되지 않은 경우 : 하이 임피던스

[0141] (2) HDMI 케이블만 삽입되어 있는 경우 : 하이 임피던스

[0142] (3) HDMI 케이블+HDMI 소스 기기가 접속되어 있는 경우 : 하이 임피던스

[0143] 이상과 같이, 소스 기기가 접속되지 않은 2개의 케이스(1), (2)에서는, PIN(1), PIN(3)은 비접속이므로 하이 임피던스가 된다. 또한, HDMI 소스 기기가 접속되어 있는 경우에도, 기기를 보호하기 위해 하이 임피던스로 되어 있다.

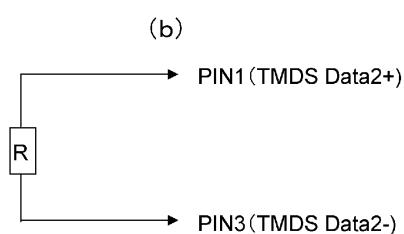

[0144] 한편, 신규격(도 5 참조)에서는, PIN(1, 3)은 미사용이므로, 도 21(a)와 같이 Type-A 플러그 내부에서 PIN(1)과 PIN(3)을 도선으로 쇼트시키던지, 또는, 도 21(b)에 도시하는 바와 같이, PIN(1)과 PIN(3)을 저항(R)(50Ω)으로 연결한다. 이에 의해, 신규격의 케이블이 싱크측 Type-A의 HDMI 리셉터클에 삽입되어 있는 경우, 소스 기기의 유무에 관계없이, PIN(1)과 PIN(3)의 사이에서는, 싱크 기기측에서 보아 도통하는 것이 된다. 또한, 여기서는 PIN(1)과 PIN(3)을 예로 들었지만, 신규격으로 사용하지 않는 핀 중, HDMI 소스 기기측에서 하이 임피던스가 되는 PIN의 조합이라면, 모두 적용 가능하다.

[0145] 상술한 바와 같이, PIN(1)과 PIN(3)의 임피던스 특성으로부터 신규격의 케이블이 삽입되어 있는지의 여부를 판단할 수 있다.

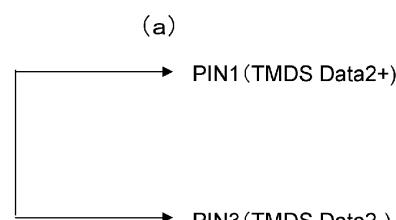

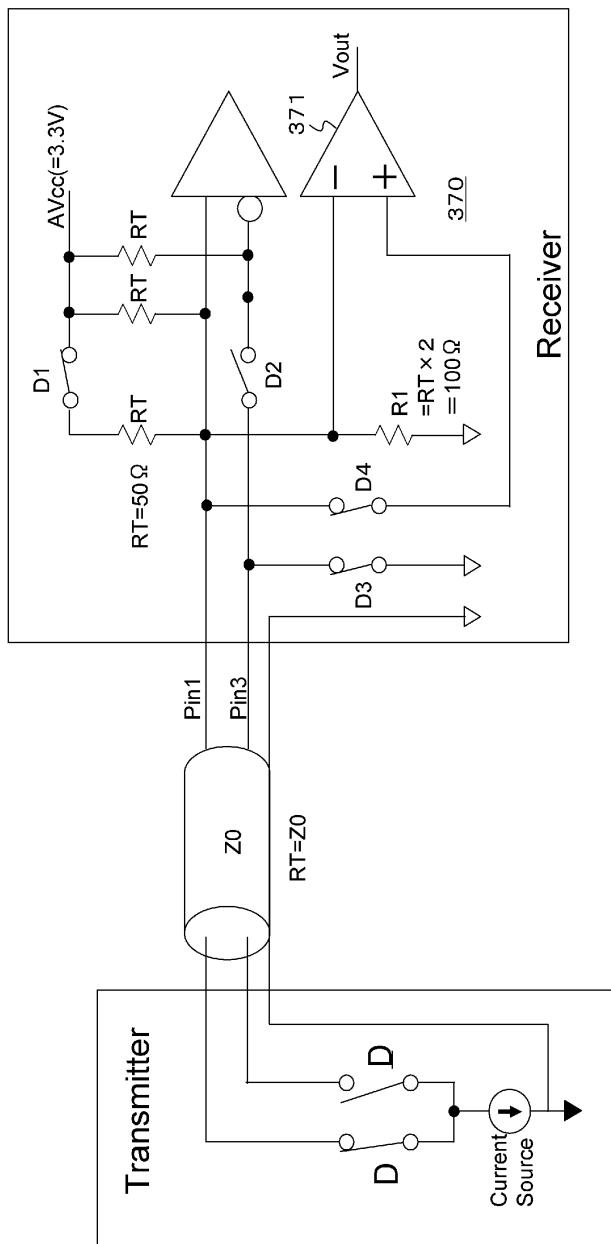

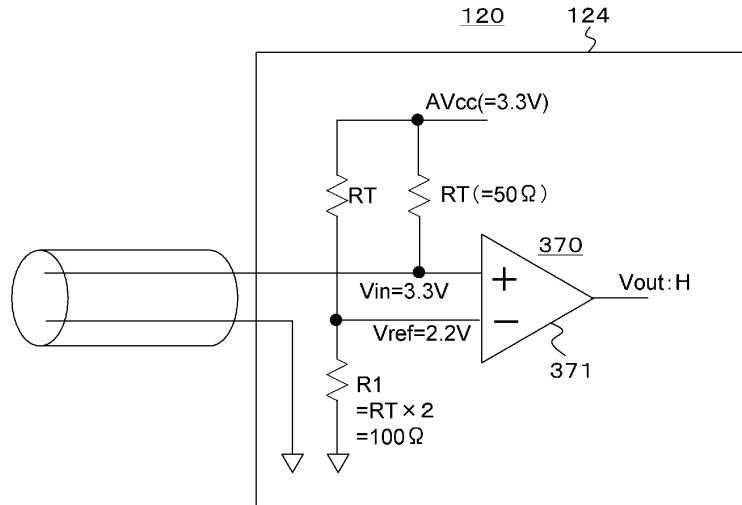

[0146] 도 22는, 싱크 기기(120)의 제어부(123) 내의 판별부(124)에 마련되는 케이블 검출 회로(370)를 도시하고 있다. 이 케이블 검출 회로(370)는, 전압 콤퍼레이터(371)에 의해 구성된다. 1핀은 저항(RT)을 통하여 전압(Vcc)에 풀업된다. 전압 콤퍼레이터(370)의 정 입력단자에는, 1핀의 전압이 입력된다. 또한, 이 전압 콤퍼레이터(371)의 부 입력단자에는, 전압이 저항(RT 및 R1)(=2RT)으로 분압되어서 얻어진 전압이, 레퍼런스 전압(Vref)(=2.2V)으로서 입력된다. 또한, PIN(3)은, 접지된다.

[0147] 도 23은, 도 8에 도시하는 TMDS 차동 페어 모식도에, 도 22의 케이블 검출 회로(370)를 삽입한 경우의 회로예이

다. 이 도 23에서, 케이블 검출을 행하는 경우, 스위치(D1) : ON, 스위치(D2) : OFF, 스위치(D3) : ON, 스위치(D4) : ON이 된다. 역으로, 스위치(D1) : OFF, 스위치(D2) : ON, 스위치(D3) : OFF, 스위치(D4) : OFF가 되면, 도 8과 동가의 회로로 되돌아온다. 도 22에 있어서, 신규격 케이블이 삽입된 경우만  $V_{out} = 'L'$ , 그 밖의 경우는  $V_{out} = 'H'$  가 된다. 그 이유를, 이하, 5개의 케이스별로 나타낸다.

[0148] (1) 케이블 미삽입시

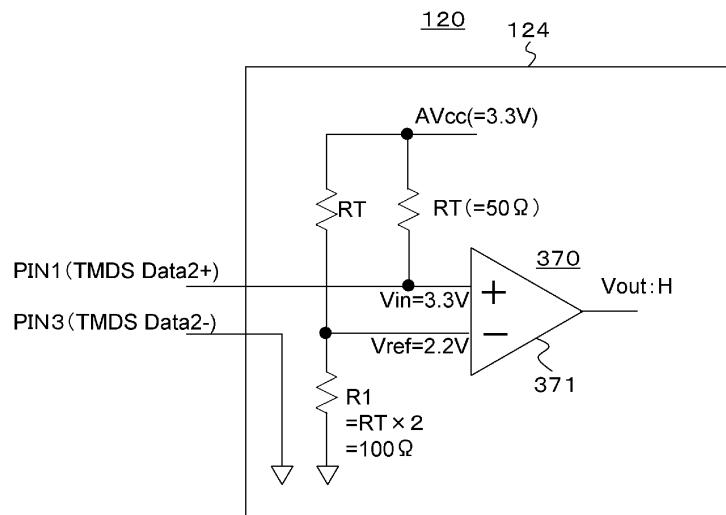

도 24는, 케이블 미삽입시에 전압 콤퍼레이터(371)에 입력하는 전압을 도시하고 있다. PIN(1)(TMDS Data2+), PIN(3)(TMDS Data2-)의 사이는 하이 임피던스이므로  $V_{in}=3.3V$ 가 되고,  $V_{out} = 'H'$  가 된다.

[0150] (2) 신규격 케이블 삽입시 1

도 25는, PIN(1)(TMDS Data2+), PIN(3)(TMDS Data2-)의 사이를 저항기(RT)(50Ω)로 연결한 신규격 케이블이 삽입된 경우를 도시하고 있다.  $V_{in}=1.65V$ 가 되고,  $V_{out} = 'L'$  이 된다.

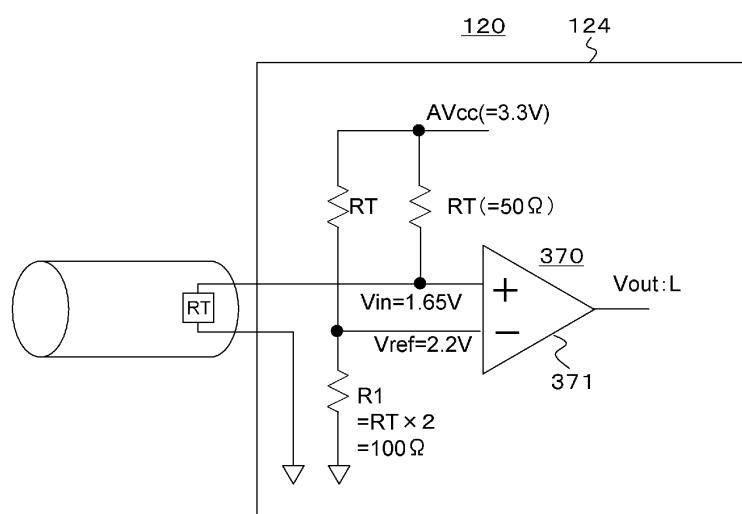

[0152] (3) 신규격 케이블 삽입시 2

도 26은, PIN(1)(TMDS Data2+), PIN(3)(TMDS Data2-)의 사이를 도선으로 쇼트시킨 신규격 케이블이 삽입된 경우를 도시하고 있다.  $V_{in}=0V$ 가 되고,  $V_{out} = 'L'$  이 된다.

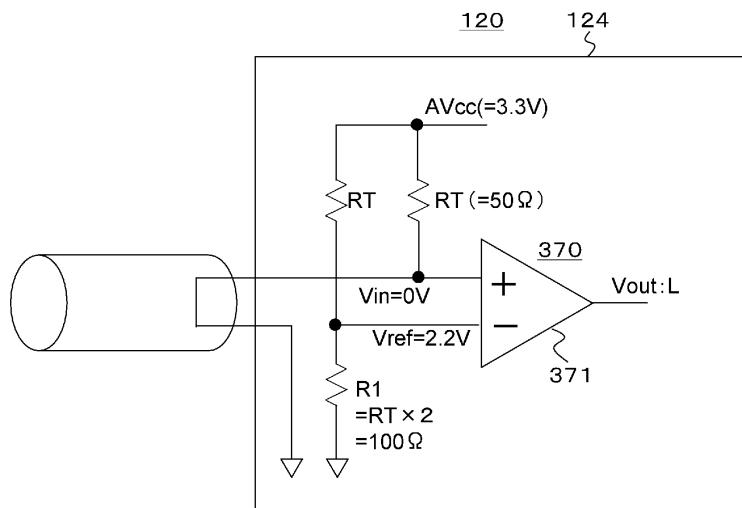

[0154] (4) HDMI 케이블 삽입시

도 27은, HDMI 케이블 삽입시(HDMI 소스 기기는 없음)에 전압 콤퍼레이터(371)에 입력하는 전압을 도시하고 있다. PIN(1)(TMDS Data2+), PIN(3)(TMDS Data2-)의 사이는 하이 임피던스이므로,  $V_{in}=3.3V$ 가 되고,  $V_{out} = 'H'$  가 된다.

[0156] (5) HDMI 케이블 + HDMI 소스 기기 삽입시

도 28은, HDMI 케이블 삽입시(HDMI Source 기기 있음)에 전압 콤퍼레이터(371)에 입력하는 전압을 도시하고 있다. PIN(1)(TMDS Data2+), PIN(3)(TMDS Data2-)의 사이는 하이 임피던스이므로,  $V_{in}=3.3V$ 가 되고,  $V_{out} = 'H'$  가 된다.

[0158] 이상, 5개의 케이스에서의 케이블 검출 회로(370)의 동작을 기술하였다. 다음에, 케이블 검출을 행하고 나서, HDMI 모드, 또는 신규격 모드로 전환할 때까지의 처리를 2개 기술한다. 여기서, 이중에서 기술하는 3개 모드, 즉 케이블 검출 모드, HDMI 모드, 신규격 모드는 이하와 같이 정의된다.

[0159] 「케이블 검출 모드」란, 싱크 기기(120)에 전원이 투입된 직후의 상태를 말한다. 이 모드시에만, 도 22에 도시하는 케이블 검출 회로(370)는 유효하다. 또한, 케이블 검출 회로(370)에 관계 없는 모든 신호선은, 소스 기기 예기치 못한 데미지를 주지 않도록, 하이 임피던스로 하여야 한다.

[0160] 「HDMI 모드」란, 도 2에서 도시하는 신호 구성에서, 또한 싱크 기기가 HDMI Ver1.4로 정의된 싱크 기기의 요건을 만족한 상태를 말한다.

[0161] 「신규격 모드」란, 한 예로서 들었던 도 5, 도 6에서 도시하는 신호 구성이며, 또한 싱크 기기가 신규격으로 정의된 싱크 기기의 요건을 만족하는 상태를 말한다.

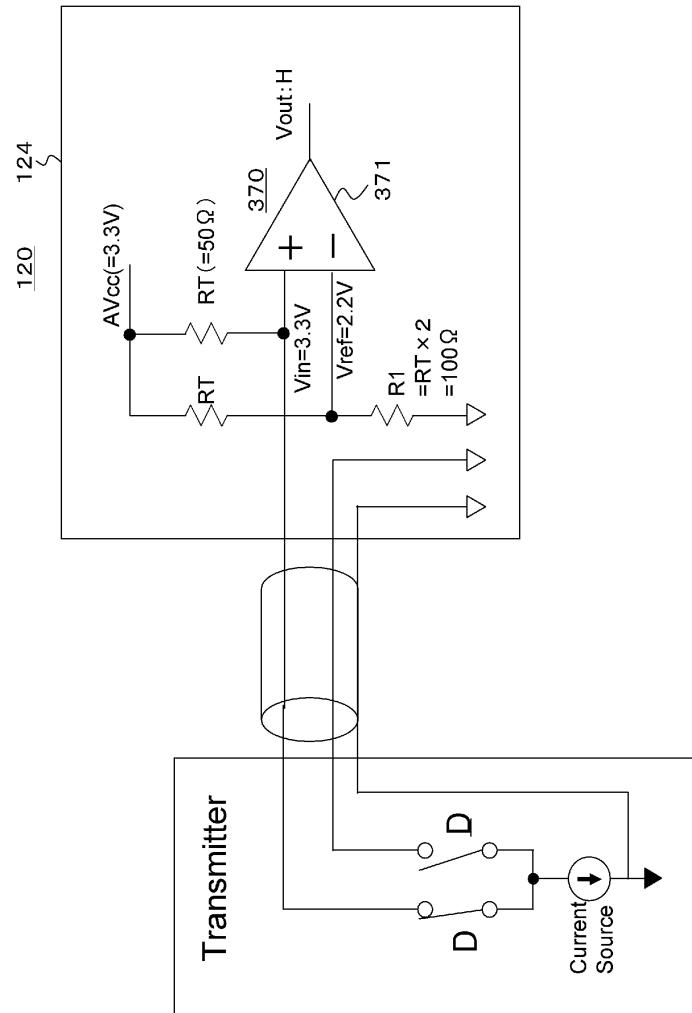

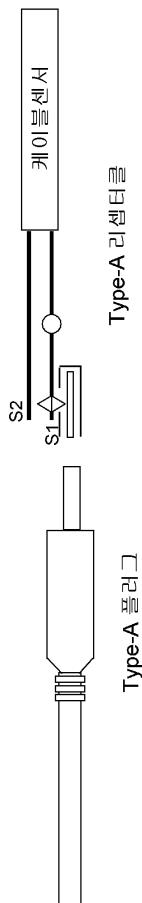

[0162] A. 「Type-A 리셉터를 내부 메카 스위치로 검출하는 방법」

도 29에서 도시하는 바와 같이, Type-A 리셉터를 내부에 스위치(S1)를 마련하고, Type-A 플러그 삽입의 유무를 판단할 수 있도록 한다. Type-A 플러그가 삽입되면 스위치(S1)가 접점(S2)과 접촉하는 구조로 한다. 스위치의 접촉, 비접촉 상태는 도면 중의 케이블 센서로 선출한다.

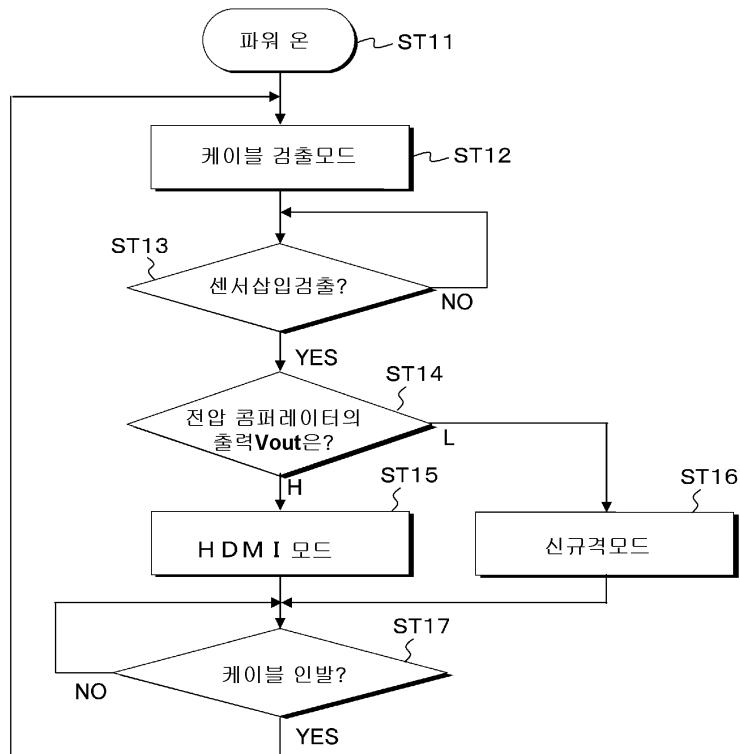

[0164] 도 30의 플로우 차트는, 이 검출 방법을 사용한 경우에 있어서의, 싱크 기기(120)의 제어부(123)의 제어 순서를 도시하고 있다. 우선, 제어부(123)는, 스텝 ST11에서, 파워 온으로 처리를 시작하고, 그 후에, 스텝 ST12의 케이블 검출 모드로 이동한다. 그리고, 제어부(123)는, 스텝 ST13에서, 케이블 센서(도 29 참조)가, 케이블의 삽입을 검출하였는지의 여부를 판단한다. 그리고, 케이블 센서가 케이블의 삽입을 검출한 때, 제어부(123)는, 스텝 ST14의 처리로 이동한다. 이 스텝 ST14에서, 제어부(123)는, 케이블 검출 회로(370)(도 22 참조)의 전압 콤퍼레이터(371)의 출력( $V_{out}$ )이 「H」인지 「L」인지를 판별한다.

[0165]  $V_{out} = 'H'$  일 때, 제어부(123)는, 스텝 ST15에서, 데이터 수신부(122)를, HDMI 규격의 디지털 인터페이스에 맞춘 동작 모드(HDMI 모드)로 제어한다. 또한,  $V_{out} = 'L'$  신규격일 때, 제어부(123)는, 스텝 ST16에서, 데이터

수신부(122)를, 신규격의 디지털 인터페이스에 맞춘 동작 모드(신규격 모드)로 제어한다. 제어부(123)는, 스텝 ST15 또는 스텝 ST16의 처리 이후에, 스텝 ST17에서, 케이블의 인발이 있었는지의 여부를 판별하고, 케이블의 인발이 없는 한, 데이터 수신부(122)의 동작 모드를 그대로 유지한다. 한편, 데이터의 인발이 있는 때는, 곧바로, 스텝 ST12로 되돌아온다.

[0166] B. 「+5V핀(18핀)의 전압을 감시하여 검출하는 방법」

+5V핀(18핀)의 전압을 감시하고, +5V의 검출시, 전압 콤파레이터 출력(Vout)을 보아 HDMI 모드, 또는 신규격 모드로의 전환을 행한다.

도 31의 플로우 차트는, 이 검출 방법을 사용한 경우에 있어서의, 싱크 기기(120)의 제어 순서를 도시하고 있다. 우선, 제어부(123)는, 스텝 ST21에서, 파워 온으로 처리를 시작하고, 그 후에, 스텝 ST22의 케이블 검출 모드로 이동한다. 그리고, 제어부(123)는, 스텝 ST23에서, +5V핀(18핀)의 전압이 +5V인지의 여부를 판별한다. 그리고, +5V핀(18핀)의 전압이 +5V일 때, 제어부(123)는, 스텝 ST24의 처리로 이동한다. 이 스텝 ST24에서, 제어부(123)는, 케이블 검출 회로(370)(도 22 참조)의 전압 콤파레이터(371)의 출력(Vout)이 「H」인지 「L」인지를 판별한다.

Vout=「H」일 때, 제어부(123)는, 스텝 ST25에서, 데이터 수신부(122)를, HDMI 규격의 디지털 인터페이스에 맞춘 동작 모드(HDMI 모드)로 제어한다. 또한, Vout=「L」 신규격일 때, 제어부(123)는, 스텝 ST26에서, 데이터 수신부(122)를, 신규격의 디지털 인터페이스에 맞춘 동작 모드(신규격 모드)로 제어한다.

제어부(123)는, 스텝 ST25 또는 스텝 ST26의 처리의 후, 스텝 ST27에서, 케이블의 인발이 있었는지의 여부를 판별한다. 즉, +5V핀(18핀)의 전압이 0V일 때는, 인발이 있다고 판단한다. 케이블의 인발이 없는 한, 데이터 수신부(122)의 동작 모드를 그대로 유지한다. 한편, 데이터의 인발이 있는 때, 제어부(123)는, 곧바로, 스텝 ST22로 되돌아온다.

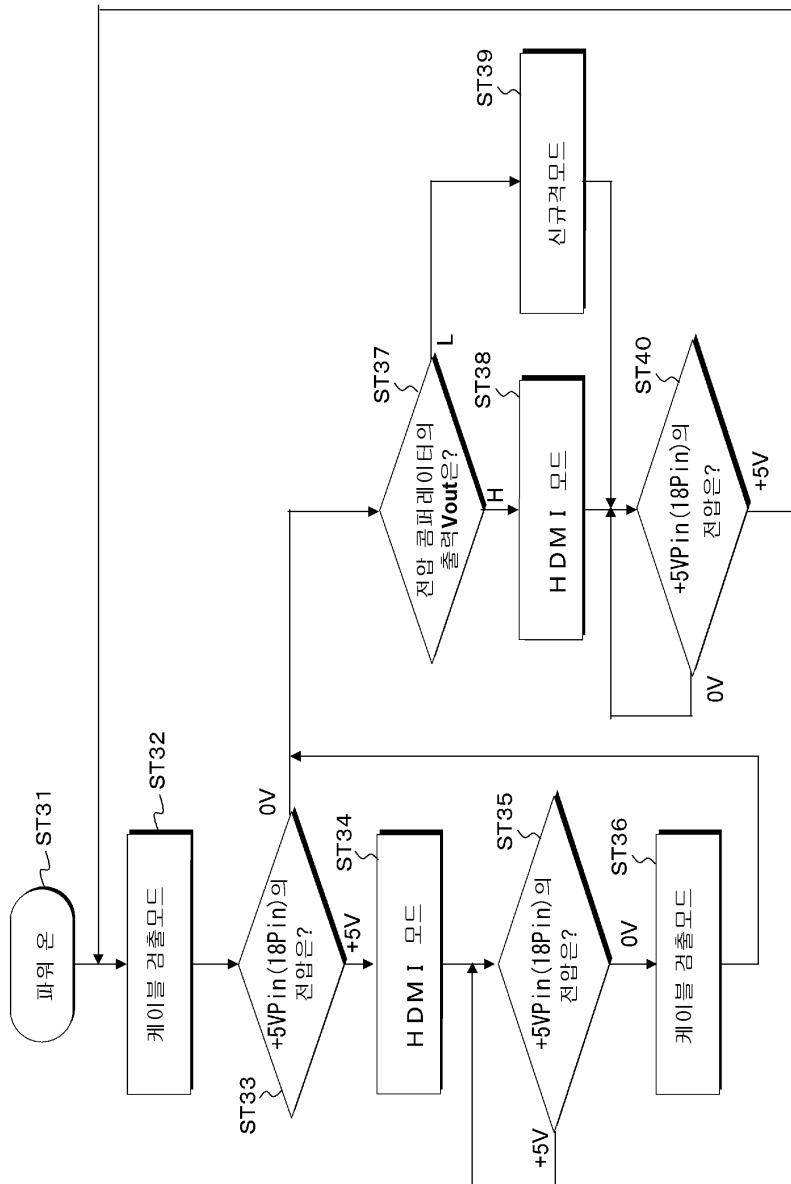

도 32의 플로우 차트도, +5V핀(18핀)의 전압을 감시하여 검출하는 방법을 사용한 경우에 있어서의, 싱크 기기(120)의 제어부(123)의 제어 순서를 도시하고 있다. 단, 신규격이 +5V핀을 사용하지 않는 경우의 처리이다. +5V핀에 +5V의 인가 중에는, 항상 HDMI 모드로 하는 점이, 상술한 도 31의 플로우 차트의 제어 순서와는 다르다. 또한, +5V핀에 +5V가 인가되어 있지 않은 경우, 전압 콤파레이터 출력(Vout)을 보고서, HDMI 모드 또는 신규격 모드로 천이한다.

우선, 제어부(123)는, 스텝 ST31에서, 파워 온으로 처리를 시작하고, 그 후에, 스텝 ST32의 케이블 검출 모드로 이동한다. 그리고, 제어부(123)는, 스텝 ST33에서, +5V핀(18핀)의 전압이 +5V인지의 여부를 판별한다. 그리고, +5V핀(18핀)의 전압이 +5V일 때, 제어부(123)는, 스텝 ST34에서, 데이터 수신부(122)를, HDMI 규격의 디지털 인터페이스에 맞춘 동작 모드(HDMI 모드)로 제어한다.

다음에, 제어부(123)는, 스텝 ST35에서, +5V핀(18핀)의 전압을 판별한다. +5V일 때, 제어부(123)는, 데이터 수신부(122)의 동작 모드(HDMI 모드)를 그대로 유지한다. 한편, 0V일 때, 제어부(123)는, 곧바로, 스텝 ST36에서, 케이블 검출 모드로 이동하고, 그 후에, 스텝 ST37의 처리로 이동한다.

스텝 ST33에서, +5V핀(18핀)의 전압이 0V일 때도, 제어부(123)는, 스텝 ST37의 처리로 이동한다. 이 스텝 ST37에서, 제어부(123)는, 케이블 검출 회로(370)(도 22 참조)의 전압 콤파레이터(371)의 출력(Vout)이 「H」인지 「L」인지를 판별한다.

Vout=「H」일 때, 제어부(123)는, 스텝 ST38에서, 데이터 수신부(122)를, HDMI 규격의 디지털 인터페이스에 맞춘 동작 모드(HDMI 모드)로 제어한다. 또한, Vout=「L」 신규격일 때, 제어부(123)는, 스텝 ST39에서, 데이터 수신부(122)를, 신규격의 디지털 인터페이스에 맞춘 동작 모드(신규격 모드)로 제어한다.

제어부(123)는, 스텝 ST38 또는 스텝 ST39의 처리의 후, 스텝 ST40에서, +5V핀(18핀)의 전압을 판별한다. 0V일 때, 제어부(123)는, 데이터 수신부(122)의 동작 모드(HDMI 모드 또는 신규격 모드)를 그대로 유지한다. 한편, +5V일 때, 제어부(123)는, 곧바로, 스텝 ST32로 되돌아온다.

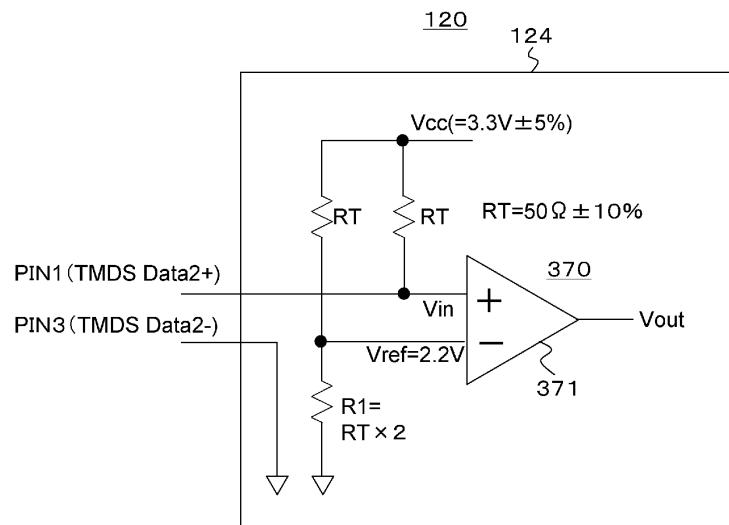

[0177] [제7의 구성례]

[0178] 이 구성례에서는, 소스 기기(110)의 데이터 송신부(112)가 HDMI 규격의 디지털 인터페이스로 동작하는 경우에 사용되고, 또한, 소스 기기(110)의 송신부(112)가 신규격(도 5 참조)의 디지털 인터페이스로 동작하는 경우에 사용되지 않는 한 쌍의 핀, 예를 들면 PIN(15)(SCL용의 핀) 및 PIN(16)(SDA용의 핀)에 주목한다.

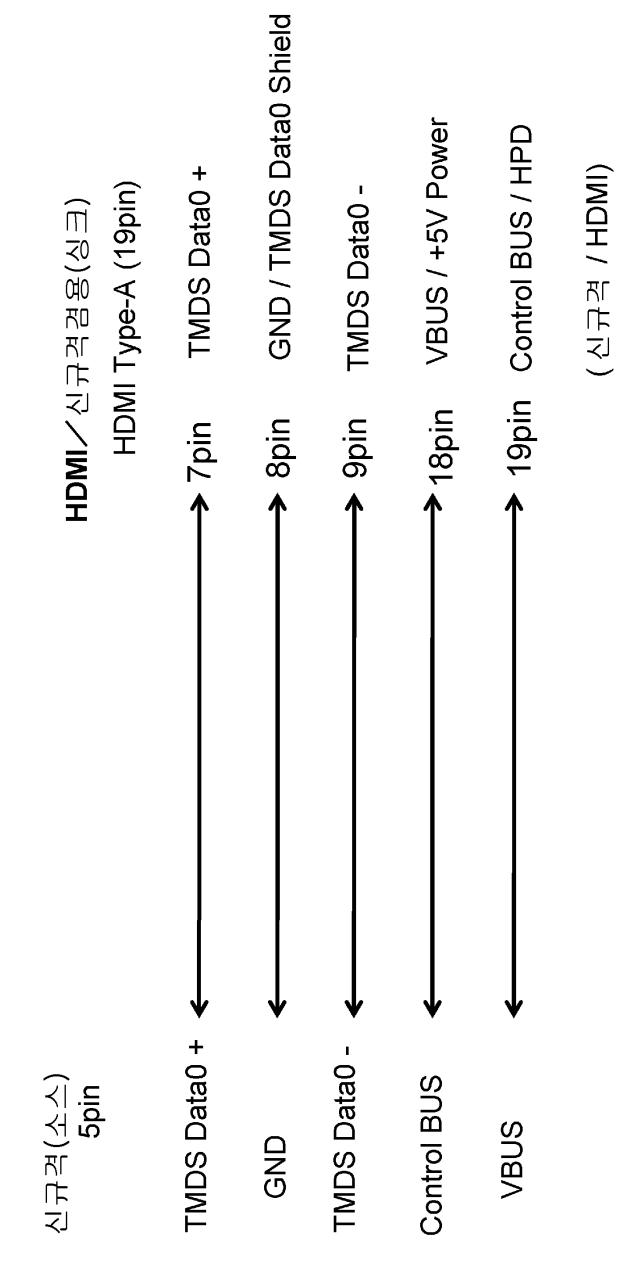

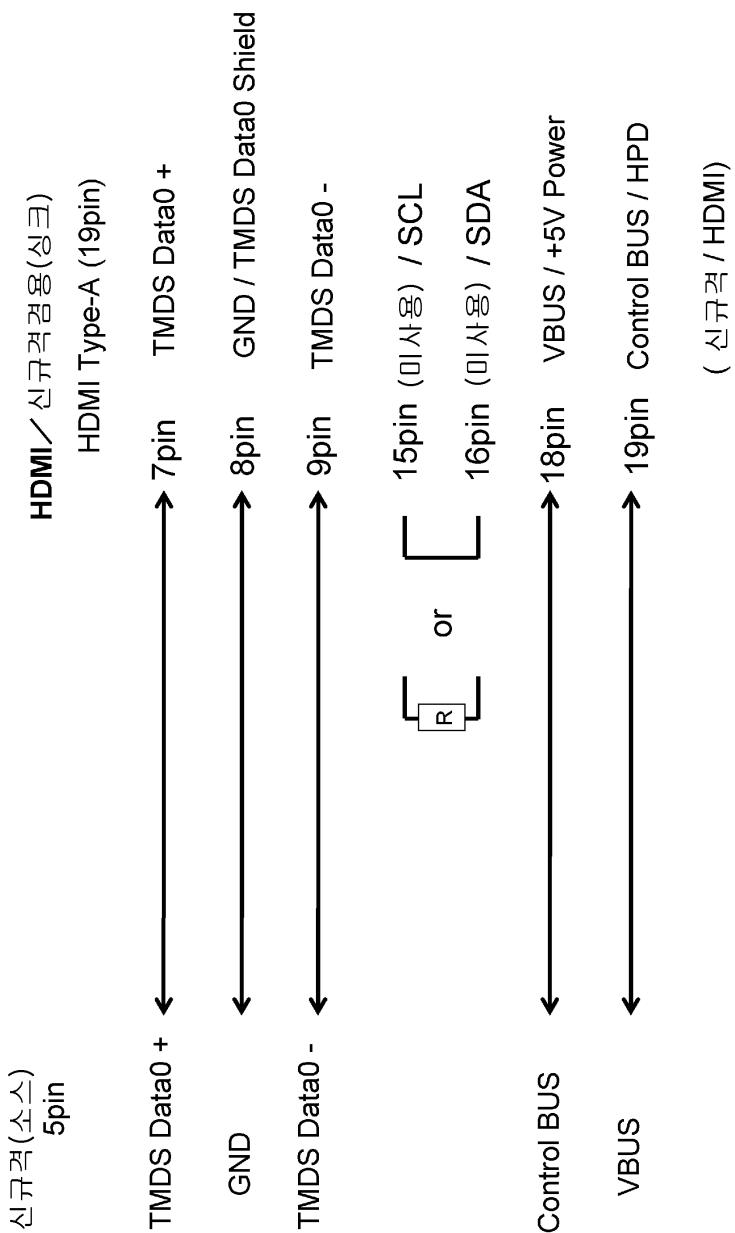

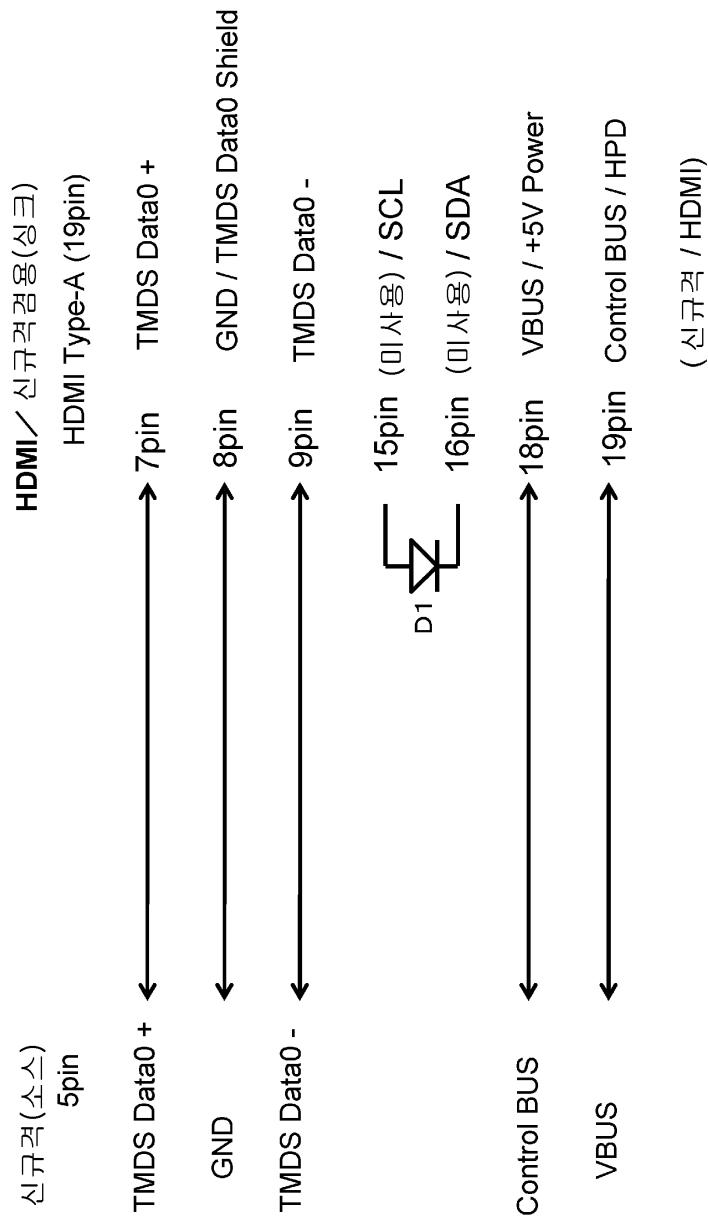

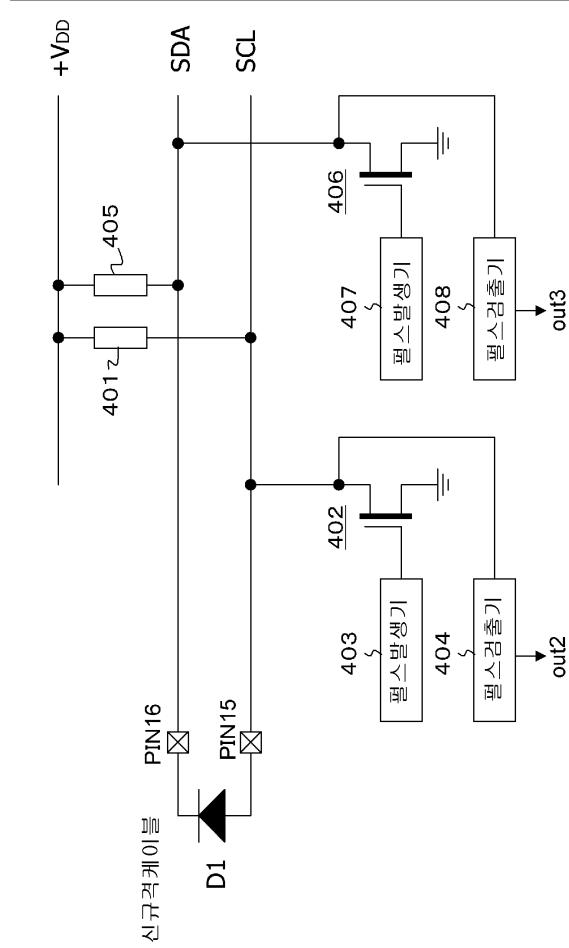

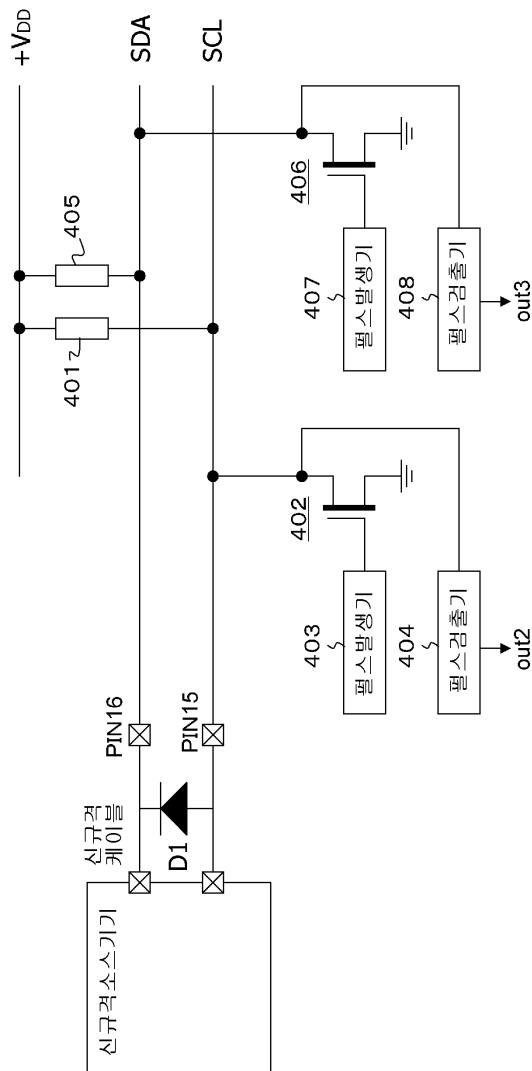

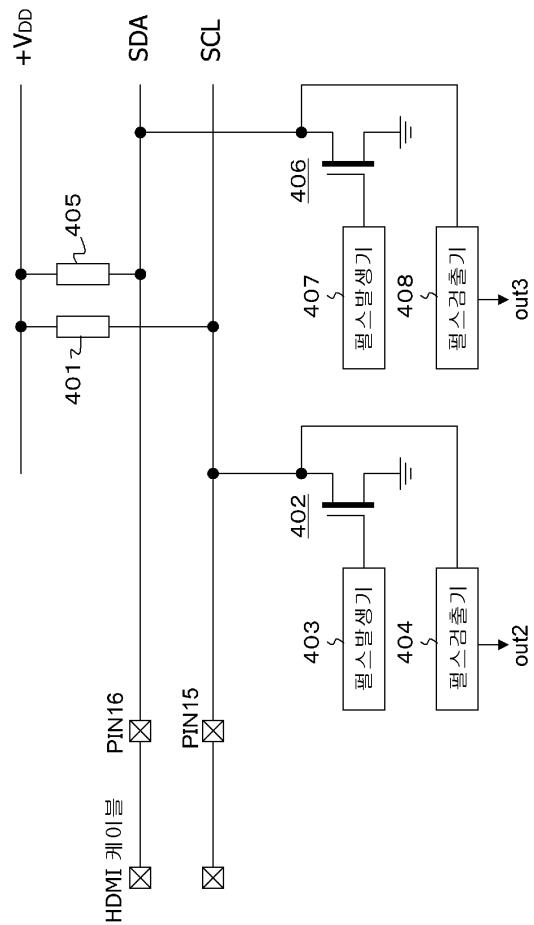

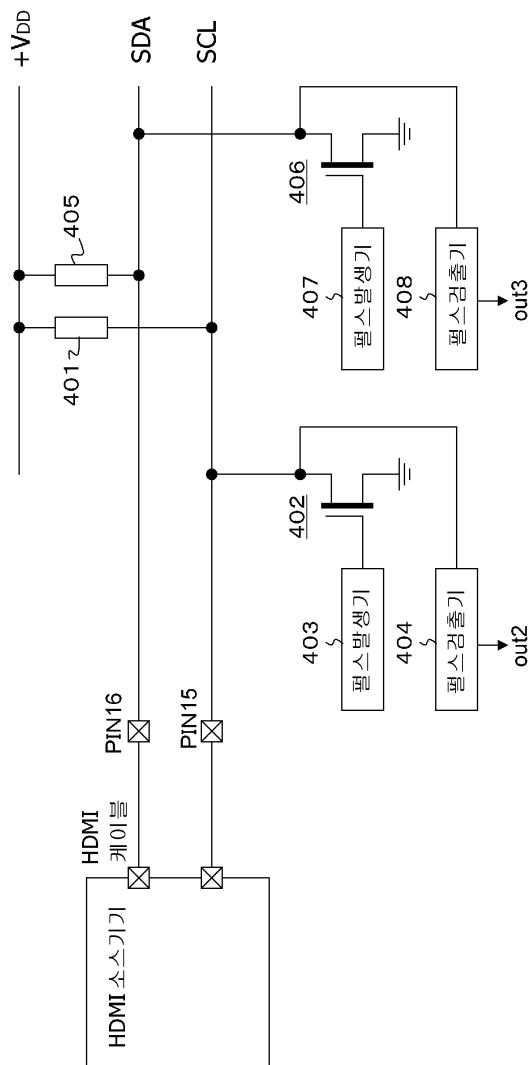

[0179] 도 33은, 신규격에 의거한, 케이블선 배치도를 도시하고 있다. 도 34는, 신규격 케이블의 케이블선 배치도를 도시하고 있다. 이 신규격 케이블의 싱크 기기측의 HDMI Type-A 플러그 내부에서, PIN(15)(15핀)과 PIN(16)(16핀)을 도선으로 단락(ショート)시키던지, 또는, PIN(15)과 PIN(16)을 저항(R)으로 연결한다.

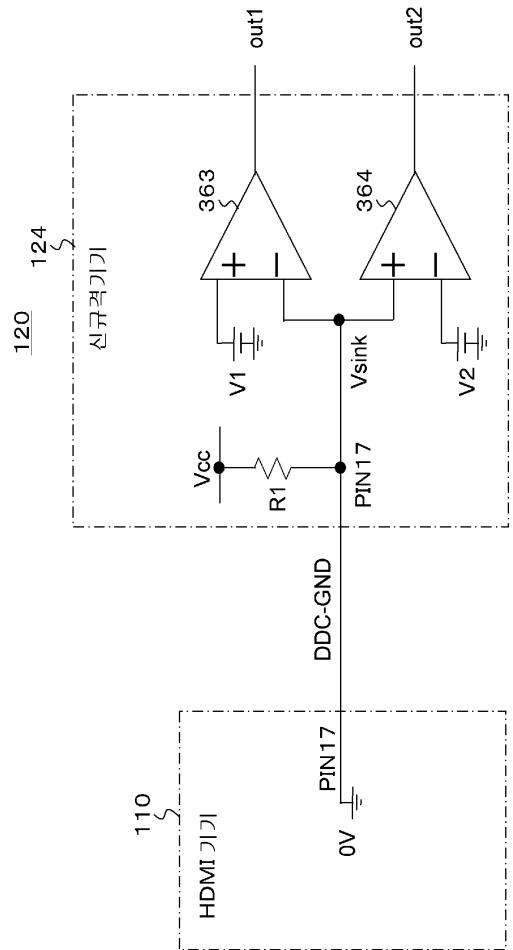

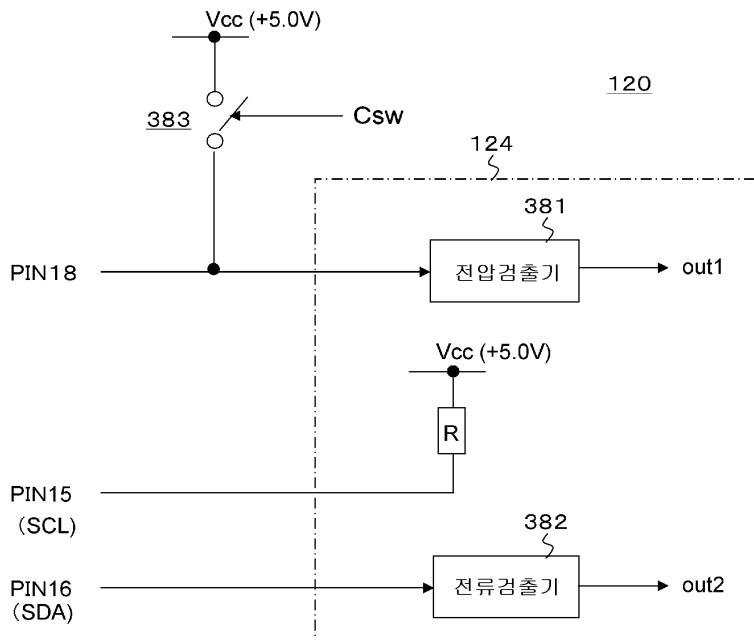

[0180] 도 35는, 싱크 기기(120)의 제어부(123) 내의 판별부(124)의 개략 구성을 도시하고 있다. 이 판별부(124)는, 전압 검출기(381)를 갖고 있다. 이 전압 검출기(381)의 입력측에 PIN(18)(18핀)이 접속된다. PIN(18)은, HDMI의 소스 기기가 접속될 때, 전원 라인(+5V Power Line)이 접속되는 전원 핀이다. 전압 검출기(381)는, PIN(18)의 전압 상태를 검출한다. 즉, 전압 검출기(381)는, PIN(18)의 전압 상태가 전원의 전압인지의 여부를 검출하고, 그 검출 결과(out1)를 출력한다.

[0181] 또한, 판별부(124)는, PIN(15)(15핀)을, 저항(R)을 통하여, 전원 전압(Vcc)에 풀업한다. 또한, 판별부(124)는, 전류 검출기(382)를 갖고 있다. 이 전류 검출기(382)의 입력측에 PIN(16)(16핀)이 접속된다. 이 전류 검출기(382)는, PIN(16)의 전류 상태를 검출한다. 즉, 전류 검출기(382)는, PIN(16)을 통하여 전류가 흐르고 있는지의 여부를 검출하고, 그 검출 결과(out2)를 출력한다.

[0182] 상술한 판별부(124) 내의 전압 검출기(381) 및 전류 검출기(382)의 검출 동작을, 이하의 6개의 케이스에 관해 고찰한다.

[0183] (1) 케이블 미접속인 경우

[0184] (2) HDMI 케이블이 접속된 경우

[0185] (3) HDMI 케이블+HDMI 소스 기기(전원 오프)가 접속된 경우

[0186] (4) HDMI 케이블+HDMI 소스 기기(전원 온)가 접속된 경우

[0187] (5) 신규격 케이블이 접속된 경우

[0188] (6) 신규격 케이블+신규격 소스 기기(전원 온/오프 양쪽)가 접속된 경우

[0189] 「(1) 케이블 미접속인 경우」

[0190] 소스측부터 PIN(18)(18핀)에 전원이 공급되지 않기 때문에, 전압 검출기(381)에서는, PIN(18)의 전압 상태는, 전원의 전압이 아니라고 검출된다. 또한, PIN(15)과 PIN(16)의 사이는 하이 임피던스 상태에 있기 때문에, PIN(16)을 통하여 전류가 흐르는 일은 없고, 전류 검출기(382)에서는 전류가 흐르지 않는다고 검출된다.

[0191] 「(2) HDMI 케이블이 접속된 경우」

[0192] 소스측부터 PIN(18)(18핀)에 전원이 공급되지 않기 때문에, 전압 검출기(381)에서는, PIN(18)의 전압 상태는, 전원의 전압이 아니라고 검출된다. 또한, HDMI 케이블 내의 SCL 라인과 SDA 라인은 미접속이다. 그 때문에, 이 경우도 PIN(15)과 PIN(16)의 사이는 하이 임피던스 상태에 있다. 그 때문에, PIN(16)을 통하여 전류가 흐르는 일은 없고, 전류 검출기(382)에서는 전류가 흐르지 않는다고 검출된다.

[0193] 「(3) HDMI 케이블+HDMI 소스 기기(전원 오프)가 접속된 경우」

[0194] HDMI 소스 기기의 전원은 오프로 되어 있기 때문에, 소스측부터 PIN(18)(18핀)에 전원이 공급되지 않는다. 그 때문에, 전압 검출기(381)에서는, PIN(18)의 전압 상태는, 전원의 전압이 아니라고 검출된다. 또한, HDMI 소스 기기측의 SCL-SDA 사이는, 전기적인 데미지를 회피하기 위해 하이 임피던스 상태에 있다. 그 때문에, PIN(16)을 통하여 전류가 흐르는 일은 없고, 전류 검출기(382)에서는 전류가 흐르지 않는다고 검출된다.

[0195] 「(4) HDMI 케이블+HDMI 소스 기기(전원 온)가 접속된 경우」

[0196] HDMI 소스 기기의 전원은 온으로 되어 있기 때문에, 소스측부터 PIN(18)(18핀)에 전원이 공급된다. 그 때문에, 전압 검출기(381)에서는, PIN(18)의 전압 상태는, 전원의 전압이라고 검출된다. 또한, HDMI 소스 기기측의 SCL-SDA 사이는, 전기적인 데미지를 회피하기 위해 하이 임피던스 상태에 있다. 그 때문에, PIN(16)을 통하여 전류가 흐르는 일은 없고, 전류 검출기(382)에서는 전류가 흐르지 않는다고 검출된다.

[0197] 「(5) 신규격 케이블이 접속된 경우」

[0198] 소스측부터 PIN(18)(18핀)에 전원이 공급되지 않기 때문에, 전압 검출기(381)에서는, PIN(18)의 전압 상태는, 전원의 전압이 아니라고 검출된다. 신규격 케이블의 싱크측 HDMI Type-A 플러그 내부에서, PIN(15)과 PIN(16)이 도선으로 단락(ショート)되고, 또는, 저항(R)을 통하여 접속되어 있다. 그 때문에, PIN(16)을 통하여 전류가

흐르고, 전류 검출기(382)에서는 전류가 흐른다고 검출된다.

[0199] 「(6) 신규격 케이블+신규격 소스 기기(전원 온/오프 양쪽)가 접속된 경우」

[0200] 소스측부터 PIN(18)(18핀)에 전원이 공급되지 않기 때문에, 전압 검출기(381)에서는, PIN(18)의 전압 상태는, 전원의 전압이 아니라고 검출된다. 신규격 케이블의 싱크측 HDMI Type-A 플러그 내부에서, PIN(15)과 PIN(16)이 도선으로 단락되고, 또는, 저항(R)을 통하여 접속되어 있다. 그 때문에, PIN(16)을 통하여 전류가 흐르고, 전류 검출기(382)에서는 전류가 흐른다고 검출된다.

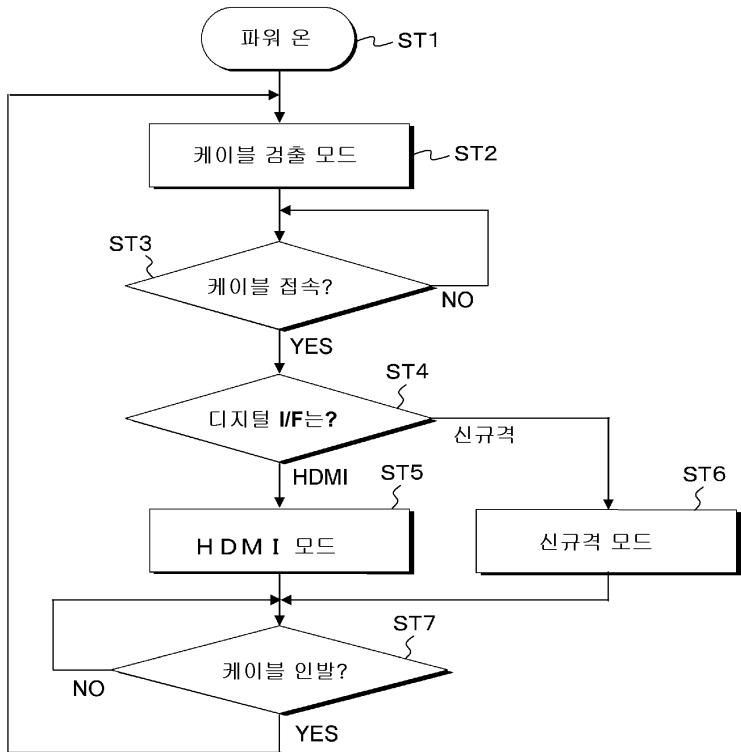

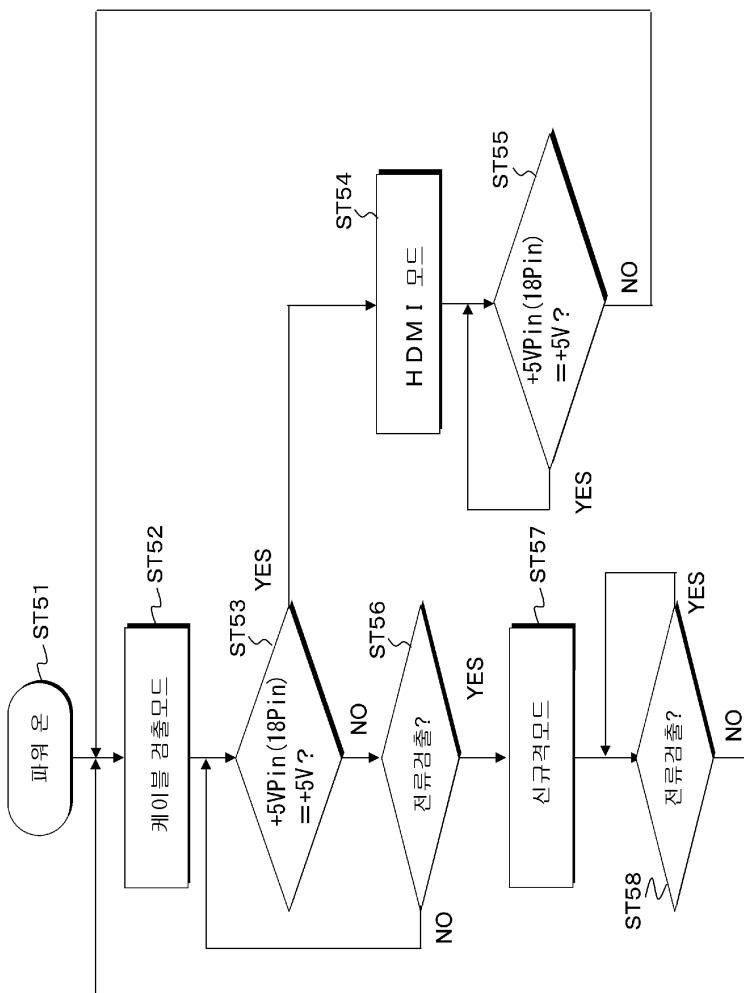

[0201] 이상의 고찰로부터, 이 제7의 구성례에서는, 전압 검출기(381) 및 전류 검출기(382)에 의해, 케이블 검출을 행한다. 도 36의 플로우 차트는, 이 검출 방법을 사용한 경우에 있어서의, 싱크 기기(120)의 제어부(123)의 제어 순서를 도시하고 있다.

[0202] 우선, 제어부(123)는, 스텝 ST51에서, 파워 온으로 처리를 시작하고, 그 후에, 스텝 ST52의 케이블 검출 모드로 이동한다. 이 케이블 검출 모드에서는, 제어부(123)는, 전압 검출기(381) 및 전류 검출기(382)의 검출 결과를 폴링한다. 그리고, 제어부(123)는, 스텝 ST53에서, 전압 검출기(381)에서 전원 전압인 것이 검출되어 있는지의 여부, 즉 +5V핀(18핀)의 전압이 +5V(전원 전압)인지의 여부를 판별한다.

[0203] 전원 전압이 검출되고 있을 때, 제어부(123)는, 상술한 「(4) HDMI 케이블+HDMI 소스 기기(전원 온)가 접속된 경우」에 상당한다고 하여, 스텝 ST54에서, 데이터 수신부(122)를, HDMI 규격의 디지털 인터페이스에 맞춘 동작 모드(HDMI 모드)로 제어한다. 그리고, 제어부(123)는 스텝 ST55에서, 전압 검출기(381)의 전압 검출 상태를 감시하고, 전원 전압을 검출하고 있는 동안은, 데이터 수신부(122)의 동작 모드(HDMI 모드)를 그대로 유지한다. 한편, 전압 검출기(381)에서 전원 전압이 검출되지 않게 된 때, 제어부(123)는, 곧바로, 스텝 ST52의 케이블 검출 모드로 되돌아온다.

[0204] 또한, 스텝 ST53에서, 전압 검출기(381)에서 전원 전압이 검출되지 않을 때, 스텝 ST56에서, 전류 검출기(382)에서 전류가 검출되어 있는지의 여부를 판별한다. 전류가 검출되지 않을 때, 제어부(123)는, 상술한 「(1) 케이블 미접속인 경우, (2) HDMI 케이블이 접속된 경우, (3) HDMI 케이블+HDMI 소스 기기(전원 오프)가 접속되는 경우」에 상당한다고 하여, 스텝 ST53, ST56의 폴링 처리를 반복한다.

[0205] 또한, 스텝 ST56에서 전류 검출기(382)에서 전류가 검출되고 있을 때, 제어부(123)는, 상술한 「(5) 신규격 케이블이 접속된 경우, (6) 신규격 케이블+신규격 소스 기기(전원 온/오프 양쪽)가 접속된 경우」에 상당한다고 하여, 제어부(123)는, 스텝 ST57에서, 데이터 수신부(122)를, 신규격의 디지털 인터페이스에 맞춘 동작 모드(신규격 모드)로 제어한다.

[0206] 그리고, 제어부(123)는 스텝 ST58에서, 전류 검출기(382)의 전류 검출 상태를 감시하고, 전류를 검출하고 있는 동안은, 데이터 수신부(122)의 동작 모드(신규격 모드)를 그대로 유지한다. 한편, 전류 검출기(382)에서 전류가 검출되지 않게 된 때, 제어부(123)는, 곧바로, 스텝 ST52의 케이블 검출 모드로 되돌아온다.

[0207] 또한, 제어부(123)는, 스텝 ST57에서, 데이터 수신부(122)를 신규격 모드로 제어할 때, 도 35에 도시하는 접속 스위치(383)에 스위치 제어 신호(Csw)를 공급하여, 온 상태로 한다. 이에 의해, 전원(Vcc)을, 소스 기기측에 공급할 수 있다.

[0208] 상술한 제7의 구성례에서는, 디지털 인터페이스가 신규격의 디지털 인터페이스인 소스 기기가 배터리 구동의 전자 기기로서, 이 배터리가 완전히 방전되어 있는 경우에도, 이 소스 기기의 디지털 인터페이스가 신규격의 디지털 인터페이스인 것을 판별할 수 있다. 그 때문에, 상술한 데이터 수신부(122)를 신규격 모드로 제어할 수 있고, 또한, 소스 기기에 전원을 공급하여, 충전하는 것이 가능해진다.

[0209] 또한, 상술한 제7의 구성례에서는, 소스 기기(110)의 데이터 송신부(112)가 HDMI 규격의 디지털 인터페이스로 동작하는 경우에 사용되고, 또한, 소스 기기(110)의 송신부(112)가 신규격(도 5 참조)의 디지털 인터페이스로 동작하는 경우에 사용되지 않는 한 쌍의 핀으로서, PIN(15)(SCL용의 핀) 및 PIN(16)(SDA용의 핀)에 주목하였다. 그러나, 상세 설명은 생략하지만, 그 밖의 한 쌍의 핀을 사용하여 마찬가지로 구성하는 것도 가능하다.

[0210] 또한, 상술한 제7의 구성례에서는, PIN(16)의 전류 상태를 검출하는 전류 검출기(382)를 갖는 구성을 도시하고 있다. 그러나, PIN(16)의 전류 상태가 아니라 전압 상태를 검출하는 구성을 하는 것도 생각된다.

[0211] [제8의 구성례]

[0212] 이 구성례도, 상술한 제7의 구성례와 마찬가지로, 한 쌍의 핀, 예를 들면 PIN(15)(SCL용의 핀) 및 PIN(16)(SDA

용의 펈)에 주목한다. 이 한 쌍의 펈은, 소스 기기(110)의 데이터 송신부(112)가 HDMI 규격의 디지털 인터페이스로 동작하는 경우에는 사용되고, 또한, 소스 기기(110)의 송신부(112)가 신규격(도 5 참조)의 디지털 인터페이스로 동작하는 경우에는 사용되지 않는다.

[0213] 도 37은, 신규격 케이블의 케이블선 배치도를 도시하고 있다. 이 신규격 케이블의 싱크 기기측의 HDMI Type-A 플러그 내부에서, PIN(16)(16핀)과 PIN(15)(15핀)은, 다이오드(D1)를 통하여 접속된다. 이 경우, 다이오드(D1)의 애노드는 PIN(15)에 접속되고, 그 캐소드는 PIN(16)에 접속되어, PIN(15)으로부터 PIN(16)으로 일방향으로 신호(전류)가 흐르도록 된다. 또한, 다이오드(D1) 대신에, 같은 기능을 갖는 다른 전자 소자를 사용하여도 좋다.

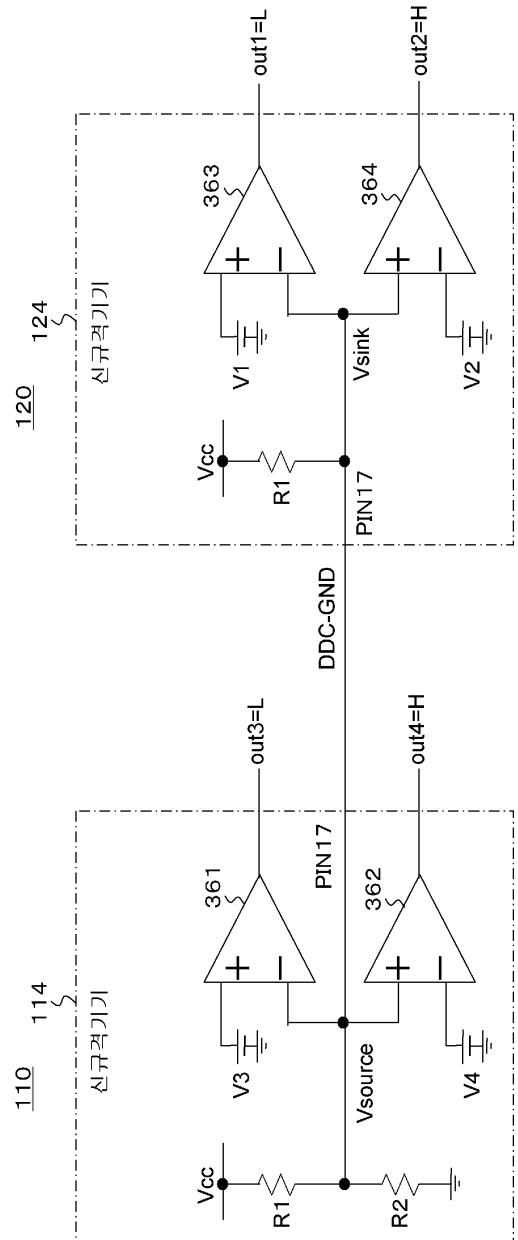

[0214] 도 38은, 싱크 기기(120)에서의 제어부(123) 내의 판별부(124)의 개략 구성을 도시하고 있다. 이 판별부(124)는, 전압 검출기(381)를 갖고 있다. 이 전압 검출기(381)의 입력측에 PIN(18)(18핀)이 접속된다. PIN(18)은, HDMI의 소스 기기가 접속될 때, 전원 라인(+5V Power Line)이 접속되는 전원 펈이다. 전압 검출기(381)는, PIN(18)의 전압 상태를 검출한다. 즉, 전압 검출기(381)는, PIN(18)의 전압 상태가 전원의 전압인지의 여부를 검출하고, 그 검출 결과(out1)을 출력한다.

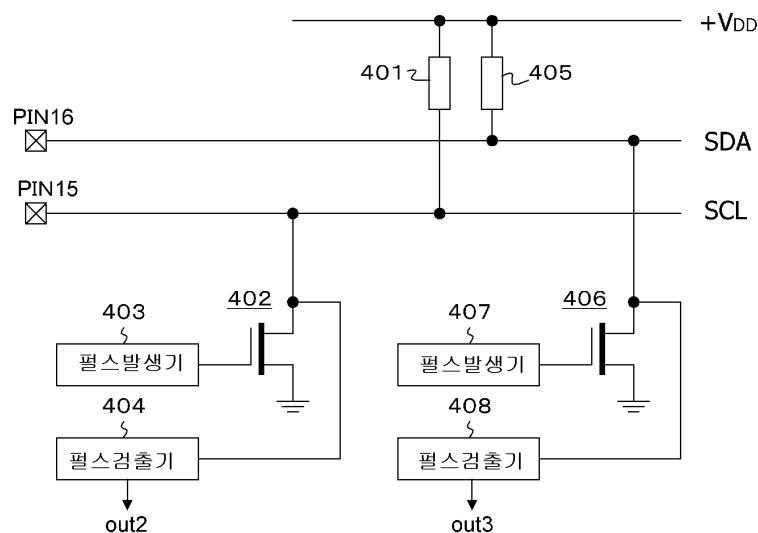

[0215] 또한, 판별부(124)는, 저항(저항 소자)(401)과, 전계효과 트랜지스터(402)와, 펄스 발생기(403)와, 펄스 검출기(404)와, 저항(저항 소자)(405)과, 전계효과 트랜지스터(406)와, 펄스 발생기(407)와, 펄스 검출기(408)를 갖고 있다. 여기서, 저항(401)은 제1의 저항 소자를 구성하고, 저항 소자(405)는 제2의 저항 소자를 구성하고 있다. 또한, 전계효과 트랜지스터(402)는 제1의 스위칭 소자를 구성하고, 전계효과 트랜지스터(406)는 제2의 스위칭 소자를 구성하고 있다.

[0216] 저항 소자(401), 전계효과 트랜지스터(402) 및 펄스 발생기(403)는, 제1의 신호 공급부를 구성하고 있다. 또한, 저항 소자(405), 전계효과 트랜지스터(406) 및 펄스 발생기(407)는, 제2의 신호 공급부를 구성하고 있다. 또한, 펄스 검출기(408)는 제1의 신호 검출부를 구성하고, 펄스 검출기(404)는 제2의 신호 검출부를 구성하고 있다.

[0217] 저항 소자(401)는, PIN(15)(15핀)을, 소정 전압, 여기서는 전원 전압(+Vdd)이 공급되는 전원 단자에 접속한다. 즉, 저항 소자(401)는, PIN(15)을, 전원 전압(+Vdd)에 풀업한다. 또한, 전계효과 트랜지스터(402)의 드레인은 PIN(15)에 접속되고, 그 소스는 접지된다. 펄스 발생기(403)는, 스위칭 소자로서의 전계효과 트랜지스터(402)를 구동하는 펄스 신호를 발생한다. 즉, 펄스 발생기(403)에서 발생되는 펄스 신호는, 전계효과 트랜지스터(402)의 게이트에 공급된다.

[0218] 전계효과 트랜지스터(402)는, 펄스 발생기(403)로부터의 펄스 신호에 의거하여, 온(도통), 오프(무도통)가 교대로 반복된다. 즉, 펄스 신호의 하이 레벨 기간에서는, 전계효과 트랜지스터(402)는 온(도통)이 되고, PIN(15)의 전위는 접지 전위(0V)가 된다. 한편, 펄스 신호의 로우 레벨 기간에서는, 전계효과 트랜지스터(402)는 오프(무도통)가 되고, PIN(15)의 전위는 전원 전압(+Vdd)이 된다. 이와 같이, 펄스 발생기(403)로부터 전계효과 트랜지스터(402)에 펄스 신호가 공급될 때, PIN(15)에는, 하이 레벨(H)이 「+Vdd」이고, 로우 레벨(L)이 「0V」인 펄스 신호가 공급된다.

[0219] 저항 소자(405)는, PIN(16)(16핀)을, 소정 전압, 여기서는 전원 전압(+Vdd)이 공급되는 전원 단자에 접속한다. 즉, 저항 소자(405)는, PIN(16)을, 전원 전압(+Vdd)에 풀업한다. 또한, 전계효과 트랜지스터(406)의 드레인은 PIN(16)에 접속되고, 그 소스는 접지된다. 펄스 발생기(407)는, 스위칭 소자로서의 전계효과 트랜지스터(406)를 구동하는 펄스 신호를 발생한다. 즉, 펄스 발생기(407)에서 발생되는 펄스 신호는, 전계효과 트랜지스터(406)의 게이트에 공급된다.

[0220] 전계효과 트랜지스터(406)는, 펄스 발생기(407)로부터의 펄스 신호에 의거하여, 온(도통), 오프(무도통)가 교대로 반복된다. 즉, 펄스 신호의 하이 레벨 기간에서는, 전계효과 트랜지스터(406)는 온(도통)이 되고, PIN(16)의 전위는 접지 전위(0V)가 된다. 한편, 펄스 신호의 로우 레벨 기간에서는, 전계효과 트랜지스터(406)는 오프(무도통)가 되고, PIN(16)의 전위는 전원 전압(+Vdd)이 된다. 이와 같이, 펄스 발생기(407)로부터 전계효과 트랜지스터(406)에 펄스 신호가 공급될 때, PIN(16)에는, 하이 레벨(H)이 「+Vdd」이고, 로우 레벨(L)이 「0V」인 펄스 신호가 공급된다.

[0221] 펄스 검출기(404)는, 상술한 바와 같이 PIN(16)에, 하이 레벨(H)이 「+Vdd」이고, 로우 레벨(L)이 「0V」인 펄스 신호가 공급되는 기간에, PIN(15)에 얻어지는 신호를 검출하고, 그 검출 결과(out2)를 출력한다. 또한, 펄스 검출기(408)는, 상술한 바와 같이 PIN(15)에, 하이 레벨(H)이 「+Vdd」이고, 로우 레벨(L)이 「0V」인 펄스 신호가 공급되는 기간에, PIN(16)에 얻어지는 신호를 검출하고, 그 검출 결과(out3)를 출력한다.

- [0222] 판별부(124)는, 이하의 검출 순서(A, B)로 얻어지는 검출 결과(out2) 및 검출 결과(out3)의 조합에 의거하여, 신규격 케이블이 접속된 케이스를 추출한다. 우선, 검출 순서(A, B)에 관해 설명한다.

- [0223] 「검출 순서(A)」

- [0224] 펠스 발생기(403)로부터 펠스 신호를 전계효과 트랜지스터(402)의 게이트에 공급하고, PIN(15)에, 하이 레벨(H)이 「+Vdd」이고, 로우 레벨(L)이 「0V」인 펠스 신호가 공급되는 상태로 한다. 이 상태에서, 펠스 검출기(408)에서 PIN(16)에 얻어지는 신호를 검출하고, 검출 결과(out3)를 출력한다. 이 경우, 펠스 검출기(408)가 출력하는 검출 결과(out3)는, 이하와 같이 된다.

- [0225] 펠스 검출기(408)는, 전혀 펠스 신호를 검출하지 않은 경우, 즉, PIN(16)의 전압이 전원 전압(+Vdd)인 채로 변화하지 않는 경우, 검출 결과(out3)로서 「N(No)」을 출력한다. 또한, 펠스 검출기(408)는, 완전한 펠스 신호를 검출한 경우, 즉, 하이 레벨(H)이 「+Vdd」이고, 로우 레벨(L)이 「0V」인 펠스 신호를 검출한 경우, 검출 결과(out3)로서 「Y(Yes)」를 출력한다. 또한, 펠스 검출기(408)는, 불완전한 펠스 신호를 검출한 경우, 즉 로우 레벨(L)이,  $0V < L < +Vdd$ 인 펠스 신호를 검출한 경우, 검출 결과(out3)로서 「M(Medium)」을 출력한다.

- [0226] 「검출 순서(B)」

- [0227] 펠스 발생기(407)로부터 펠스 신호를 전계효과 트랜지스터(406)의 게이트에 공급하고, PIN(16)에, 하이 레벨(H)이 「+Vdd」이고, 로우 레벨(L)이 「0V」인 펠스 신호가 공급되는 상태로 한다. 이 상태에서, 펠스 검출기(404)에서 PIN(15)에 얻어지는 신호를 검출하고, 검출 결과(out2)를 출력한다. 이 경우, 펠스 검출기(404)가 출력하는 검출 결과(out2)는, 이하와 같이 된다.

- [0228] 펠스 검출기(404)는, 전혀 펠스 신호를 검출하지 않은 경우, 즉, PIN(15)의 전압이 전원 전압(+Vdd)인 채로 변화하지 않는 경우, 검출 결과(out2)로서 「N(No)」을 출력한다. 또한, 펠스 검출기(404)는, 완전한 펠스 신호를 검출한 경우, 즉, 하이 레벨(H)이 「+Vdd」이고, 로우 레벨(L)이 「0V」인 펠스 신호를 검출한 경우, 검출 결과(out2)로서 「Y(Yes)」를 출력한다. 또한, 펠스 검출기(404)는, 불완전한 펠스 신호를 검출한 경우, 즉 로우 레벨(L)이,  $0V < L < +Vdd$ 인 펠스 신호를 검출한 경우, 검출 결과(out2)로서 「M(Medium)」을 출력한다.

- [0229] 상술한 검출 순서(A, B)에서의 검출 결과(out2) 및 검출 결과(out3)를, 이하의 5개의 케이스에 관해 고찰한다.

- [0230] (1) 케이블 미접속인 경우

- [0231] (2) 신규격 케이블이 접속된 경우

- [0232] (3) 신규격 케이블+신규격 소스 기기(전원 온/오프 양쪽)가 접속된 경우

- [0233] (4) HDMI 케이블이 접속된 경우(소스 기기 없음)

- [0234] (5) HDMI 케이블+HDMI 소스 기기(전원 온/오프)가 접속된 경우

- [0235] 「(1) 케이블 미접속인 경우」

- [0236] 이 경우, 도 39에 도시하는 바와 같이, PIN(15)(SCL)과 PIN(16)(SDA)의 사이는, 미접속(하이 임피던스)이다. 그 때문에, 검출 순서(A)를 실행한 경우, PIN(16)의 전압은 전원 전압(+Vdd)인 채로 변화하지 않고, 펠스 검출기(408)는, 전혀 펠스 신호를 검출하지 않는다. 그 때문에, 펠스 검출기(408)는, 검출 결과(out3)로서 「N(No)」을 출력한다. 또한, 검출 순서(B)를 실행한 경우, PIN(15)의 전압은 전원 전압(+Vdd)인 채로 변화하지 않고, 펠스 검출기(404)는, 전혀 펠스 신호를 검출하지 않는다. 그 때문에, 펠스 검출기(404)는, 검출 결과(out2)로서 「N(No)」을 출력한다.

- [0237] 「(2) 신규격 케이블이 접속된 경우」

- [0238] 이 경우, 도 40에 도시하는 바와 같이, PIN(15)(SCL)과 PIN(16)(SDA)의 사이는, 다이오드(D1)로 접속되어 있다. 이 경우, PIN(15)(SCL)으로부터 PIN(16)(SDA)의 방향이 로우 임피던스, 역으로, PIN(16)(SDA)으로부터 PIN(15)(SCL)의 방향이 하이 임피던스가 된다.

- [0239] 그 때문에, 검출 순서(A)를 실행한 경우, PIN(16)에는, 하이 레벨(H)이 「+Vdd」이고, 로우 레벨(L)이 「0V」인 완전한 펠스 신호가 얻어진다. 따라서 펠스 검출기(408)는, 완전한 펠스 신호를 검출하고, 검출 결과(out3)로서 「Y(Yes)」를 출력한다. 또한, 검출 순서(B)를 실행한 경우, PIN(15)의 전압은 전원 전압(+Vdd)인 채로 변화하지 않고, 펠스 검출기(404)는, 전혀 펠스 신호를 검출하지 않는다. 그 때문에, 펠스 검출기(404)는, 검출 결과

(out2)로서 「N(No)」을 출력한다.

[0240] 「(3) 신규격 케이블+신규격 소스 기기가 접속된 경우」

이 경우, 도 41에 도시하는 바와 같이, PIN(15)(SCL)과 PIN(16)(SDA)의 사이는, 다이오드(D1)로 접속되어 있다. 그 때문에, 검출 순서(A)를 실행한 경우의 검출 결과(out3)와, 검출 순서(B)를 실행한 경우의 검출 결과(out2)는, 상술한 「(2) 신규격 케이블이 접속된 경우」와 같다. 즉, 검출 순서(A)를 실행한 경우, 펠스 검출기(408)는, 검출 결과(out3)로서 「Y(Yes)」를 출력한다. 또한, 검출 순서(B)를 실행한 경우, 펠스 검출기(404)는, 검출 결과(out2)로서 「N(No)」을 출력한다.

[0242] 「(4) HDMI 케이블이 접속된 경우」

이 경우, 도 42에 도시하는 바와 같이, PIN(15)(SCL)과 PIN(16)(SDA)의 사이는, 미접속(하이 임피던스)이다. 그 때문에, 검출 순서(A)를 실행한 경우의 검출 결과(out3)와, 검출 순서(B)를 실행한 경우의 검출 결과(out2)는, 상술한 「(1) 케이블 미접속인 경우」와 같다. 검출 순서(A)를 실행한 경우, 펠스 검출기(408)는, 검출 결과(out3)로서 「N(No)」을 출력한다. 또한, 검출 순서(B)를 실행한 경우, 펠스 검출기(404)는, 검출 결과(out2)로서 「N(No)」을 출력한다.

[0244] 「(5) HDMI 케이블+HDMI 소스 기기가 접속된 경우」

도 43은, 이 경우의 접속상태를 도시하고 있다. 이 경우, PIN(15)(SCL)과 PIN(16)(SDA) 사이의 임피던스는, HDMI 소스 기기측의 상태에 의해, 이하의 (5-1) 내지 (5-3)의 어느 하나이다.

[0246] (5-1) : 하이 임피던스

[0247] (5-2) : 로우 임피던스

[0248] (5-3) : 하이 임피던스와 로우 임피던스의 중간

단, PIN(15)(SCL)으로부터 PIN(16)(SDA)의 방향과, PIN(16)(SDA)으로부터 PIN(15)(SCL)의 방향에서, 같은 임피던스 값을 나타내야 할 것이다. 따라서(5-1)의 경우는, 검출 순서(A)를 실행한 경우, 펠스 검출기(408)는, 검출 결과(out3)로서 「N(No)」을 출력한다. 또한, 검출 순서(B)를 실행한 경우, 펠스 검출기(404)는, 검출 결과(out2)로서 「N(No)」을 출력한다.

또한, (5-2)의 경우는, 검출 순서(A)를 실행한 경우, 펠스 검출기(408)는, 검출 결과(out3)로서 「Y(Yes)」를 출력한다. 또한, 검출 순서(B)를 실행한 경우, 펠스 검출기(404)는, 검출 결과(out2)로서 「Y(Yes)」를 출력한다. 또한, (5-3)의 경우는, 검출 순서(A)를 실행한 경우, 펠스 검출기(408)는, 검출 결과(out3)로서 「M(Medium)」을 출력한다. 또한, 검출 순서(B)를 실행한 경우, 펠스 검출기(404)는, 검출 결과(out2)로서 「M(Medium)」을 출력한다.

도 44는, 상술한 (1) 내지 (5)의 각 경우에 있어서의 검출 순서(A), 검출 순서(B)에서의 검출 결과(out3, out2)를 정리하여 나타내고 있다. 이 도면으로부터 분명한 바와 같이, 「(2) 신규격 케이블이 접속된 경우 및 「(3) 신규격 케이블+신규격 소스 기기가 접속된 경우」, 검출 순서(A)의 검출 결과(out3)와 검출 순서(B)의 검출 결과(out2)가 정반대가 된다. 이들은, 신규격 케이블을 사용한 케이스이고, 임피던스에 있어서 극단적인 이방성 (SCL→SDA 방향이 로우 임피던스, SDA→SCL 방향이 하이 임피던스)를 갖기 때문이다. 또한, 그 밖의 경우는, 임피던스에 있어서 등방성을 갖기 때문에, 검출 순서(A)의 검출 결과(out3)와 검출 순서(B)의 검출 결과(out2)가 일치한다.

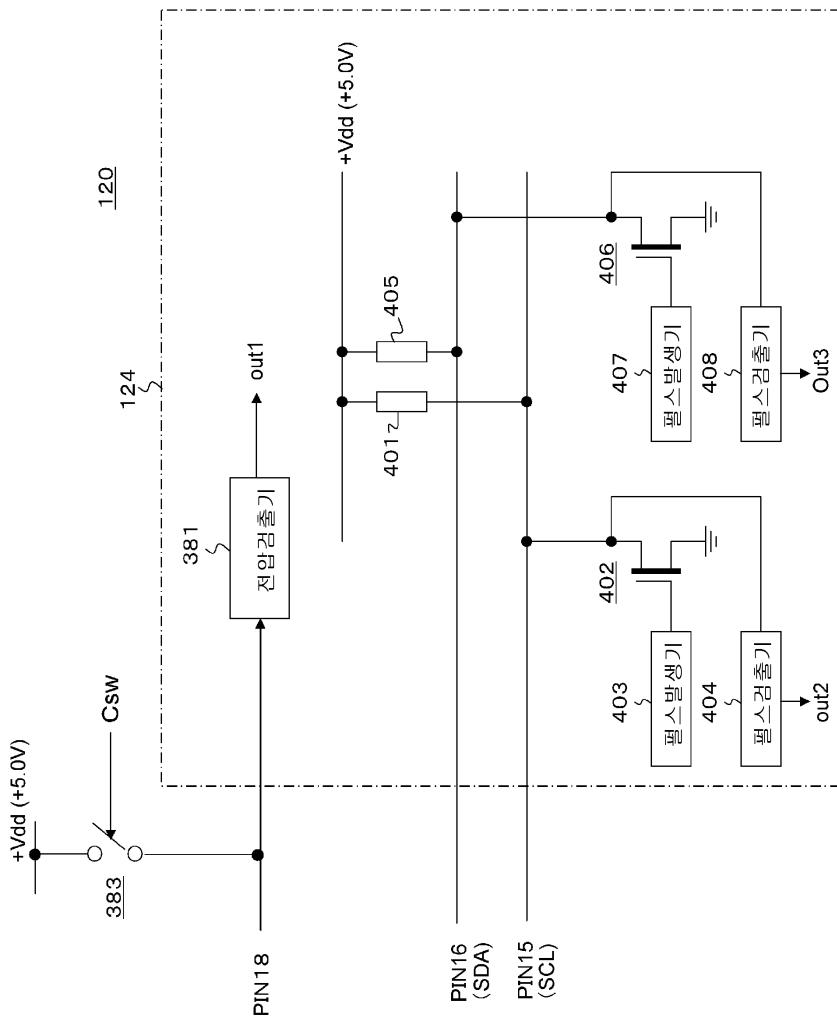

[0252] 이상의 결과로부터, 검출 순서(A)의 검출 결과(out3)가 Y(완전한 펠스를 검출), 또한 검출 순서(B)의 검출 결과(out2)가 N(전혀 펠스를 검출하지 않았다)인 경우일 때만, 도 37에 도시하는 신규격 케이블이 접속되어 있다고 판단할 수 있다. 도 45의 플로우 차트는, 이 검출 방법을 사용한 경우에 있어서의, 싱크 기기(120)의 제어부(123)의 제어 순서를 도시하고 있다.

[0253] 우선, 제어부(123)는, 스텝 ST71에서, 파워 온으로 처리를 시작하고, 그 후에, 스텝 ST72의 케이블 검출 모드로 이동한다. 이 케이블 검출 모드는, 도 38에 도시하는 케이블 검출 회로를 유효로 하고, 그 밖의 편은 무효로 하는 모드이다. 다음에, 제어부(123)는, 스텝 ST73에서, 검출 순서(A)를 실행하고, 펠스 검출기(408)로부터 출력되는 검출 결과(out3)를 취득한다. 다음에, 제어부(123)는, 스텝 ST74에서, 검출 순서(B)를 실행하고, 펠스 검출기(404)로부터 출력되는 검출 결과(out2)를 취득한다.

- [0254] 다음에, 제어부(123)는, 스텝 ST75에서, 검출 순서(A)의 검출 결과(out3)가 「Y(Yes)」, 또한 검출 순서(B)의 검출 결과(out2)가 「N(No)」이라는 조건을 충족시키는지의 여부를 판단한다. 이 조건을 충족시킨 때, 제어부(123)는, 스텝 ST76의 처리로 이동한다. 이 스텝 ST76에서, 제어부(123)는, 데이터 수신부(122)를, 신규격의 디지털 인터페이스에 맞춘 동작 모드(신규격 모드)로 제어한다.

- [0255] 다음에, 제어부(123)는, 스텝 ST77에서, 검출 순서(A)를 실행하고, 펠스 검출기(408)로부터 출력되는 검출 결과(out3)를 취득한다. 또한, 제어부(123)는, 스텝 ST78에서, 검출 순서(B)를 실행하고, 펠스 검출기(404)로부터 출력되는 검출 결과(out2)를 취득한다. 그리고, 제어부(123)는, 스텝 ST79에서, 검출 순서(A)의 검출 결과(out3)가 「Y(Yes)」, 또한 검출 순서(B)의 검출 결과(out2)가 「N(No)」라는 조건을 충족시키는지의 여부를 판단한다.

- [0256] 조건을 충족시킬 때, 제어부(123)는, 데이터 수신부(122)의 동작 모드(신규격 모드)를 그대로 유지한다. 한편, 이 조건을 충족시키지 않게 된 때, 제어부(123)는, 신규격 케이블이 빠졌다고 판단하고, 스텝 ST72의 케이블 검출 모드로 되돌아온다.

- [0257] 또한, 스텝 ST75에서 조건을 충족시키지 않을 때, 스텝 ST80의 처리로 이동한다. 이 스텝 ST80에서, 제어부(123)는, 전압 검출기(381)에서 전원 전압인 것이 검출되어 있는지의 여부, 즉 +5V핀(18핀)의 전압이 +5V(전원 전압)인지의 여부를 판별한다. 전압 검출기(381)에서 전원 전압이 검출되지 않을 때, 제어부(123)는, 스텝 ST73으로 되돌아와, 검출 순서(A), 검출 순서(B)의 처리를 반복한다.

- [0258] 전원 전압이 검출되어 있을 때, 제어부(123)는, 스텝 ST81에서, 데이터 수신부(122)를, HDMI 규격의 디지털 인터페이스에 맞춘 동작 모드(HDMI 모드)로 제어한다. 그리고, 제어부(123)는 스텝 ST82에서, 전압 검출기(381)의 전압 검출 상태를 감시하고, 전원 전압을 검출하고 있는 동안은, 데이터 수신부(122)의 동작 모드(HDMI 모드)를 그대로 유지한다. HDMI 모드중, SDA 라인, SCL 라인은, EDID 판독이나, HDCP 인증 등, HDMI 본래의 용도로 사용되기 때문에, 검출 순서(A, B)는 실행하지 않는다. 전압 검출기(381)에서 전원 전압이 검출되지 않게 된 때, 제어부(123)는, 곧바로, 스텝 ST72의 케이블 검출 모드로 되돌아온다.

- [0259] 또한, 제어부(123)는, 스텝 ST76에서, 데이터 수신부(122)를 신규격 모드로 제어할 때, 도 38에 도시하는 접속 스위치(383)에 스위치 제어 신호(Csw)를 공급하여, 온 상태로 한다. 이에 의해, 전원(Vcc)을, 소스 기기측에 공급할 수 있다.

- [0260] 상술한 제8의 구성례에서는, 디지털 인터페이스가 신규격의 디지털 인터페이스인 소스 기기가 배터리 구동의 전자 기기로서, 이 배터리가 완전히 방전되어 있는 경우에도, 이 소스 기기의 디지털 인터페이스가 신규격의 디지털 인터페이스인 것을 판별할 수 있다. 그 때문에, 상술한 데이터 수신부(122)를 신규격 모드로 제어할 수 있고, 또한, 소스 기기에 전원을 공급하여, 충전하는 것이 가능해진다.

- [0261] 또한, 상술한 제8의 구성례에서는, 소스 기기(110)의 데이터 송신부(112)가 HDMI 규격의 디지털 인터페이스로 동작하는 경우에 사용되고, 또한, 소스 기기(110)의 송신부(112)가 신규격(도 5 참조)의 디지털 인터페이스로 동작하는 경우에 사용되지 않는 한 쌍의 핀으로서, PIN(15)(SCL용의 핀) 및 PIN(16)(SDA용의 핀)에 주목하였다. 그러나, 상세 설명은 생략하지만, 그 밖의 한 쌍의 핀을 사용하여 마찬가지로 구성하는 것도 가능하다.

- [0262] 또한, 상술한 제8의 구성례에서는, 검출 순서(A)에서는 전계효과 트랜지스터(402)를 펠스 신호로 구동하고, 검출 순서(B)에서는 전계효과 트랜지스터(406)를 펠스 신호로 구동하고 있다. 그러나, 이들의 검출 순서(A, B)에서, 전계효과 트랜지스터(402, 406)를 오프로부터 온의 상태로 변화시켜서, 펠스 검출기(408, 404)로, 전압 레벨의 변화를 검출하여, 검출 결과(out3, out2)를 취득하는 구성도 생각된다. 이 경우에는, 펠스 발생기(403, 407)는 불필요하게 된다.

- [0263] <2. 변형례>

- [0264] 또한, 상술한 실시의 형태에서는, HDMI 규격, 신규 규격의 디지털 인터페이스로 동작하는 외부 기기를 접속하기 위한 커넥터부로서 HDMI 리셉터를을 겸용하는 예를 나타냈다. 그러나, 본 발명은 이것으로 한정되는 것이 아니고, 그 밖의 마찬가지의 디지털 인터페이스부에 적용할 수 있음을 물론이다. 3개 이상의 규격의 디지털 인터페이스로 동작하는 외부 기기를 접속하기 위한 커넥터부로서 하나의 규격의 커넥터부를 겸용하는 것도 마찬가지로 생각된다.

- [0265] 산업상 이용 가능성

- [0266] 본 발명은, 예를 들면, 소스 기기 및 싱크 기기를 디지털 인터페이스를 통하여 접속하여 이루어지는 AV 시스템

등에 적용할 수 있다.

### 부호의 설명

[0267]

100 : AV 시스템

110 : 소스 기기

111 : 커넥터부

112 : 테이터 송신부

113 : 제어부

114 : 판별부

120 : 싱크 기기

121 : 커넥터부

122 : 테이터 수신부

123 : 제어부

124 : 판별부

200 : 케이블

310, 320 : 액티브 범위 검출 회로

331, 332, 341, 351, 352, 361 내지 364 : 전압 콤파레이터

370 : 케이블 검출 회로

371 : 전압 콤파레이터

381 : 전압 검출기

382 : 전류 검출기

383 : 접속 스위치

401, 405 : 저항(저항 소자)

402, 406 : 전계효과 트랜지스터

403, 407 : 펄스 발생기

404, 408 : 펄스 검출기

## 도면

## 도면1

## 도면2

## 도면3

## 도면4

| PIN | Signal Assignment           | PIN | Signal Assignment |

|-----|-----------------------------|-----|-------------------|

| 1   | TMDS Data2+                 | 2   | TMDS Data2 Shield |

| 3   | TMDS Data2-                 | 4   | TMDS Data1+       |

| 5   | TMDS Data1 Shield           | 6   | TMDS Data1-       |

| 7   | TMDS Data0+                 | 8   | TMDS Data0 Shield |

| 9   | TMDS Data0-                 | 10  | TMDS Clock+       |

| 11  | TMDS Clock Shield           | 12  | TMDS Clock-       |

| 13  | CEC                         | 14  | Utility/HEAC+     |

| 15  | SCL                         | 16  | SDA               |

| 17  | DDC/CEC Ground /HEAC Shield | 18  | +5V Power         |

| 19  | Hot Plug Detect/HEAC-       |     |                   |

도면5

도면6

## 도면7

도면8

도면9

도면10

도면11

도면12

도면13

도면14

도면15

## 도면16

## 도면17

## 도면18

## 도면19

도면20

도면21

## 도면22

도면23

## 도면24

## 도면25

## 도면26

도면27

도면28

도면29

도면30

도면31

도면32

## 도면33

## 도면34

## 도면35

### 도면36

### 도면37

도면38

도면39

## 도면40

도면41

도면42

도면43

## 도면44

|                                      | 검출수순 <b>A</b> (out3)<br>(SCL→SDA)             | 검출수순 <b>B</b> (out2)<br>(SDA→SCL) |

|--------------------------------------|-----------------------------------------------|-----------------------------------|

| 1. 케이블 미접속                           | N                                             | N                                 |

| 2. 신규격 케이블                           | Y                                             | N                                 |

| 3. 신규격 케이블+신규격 소스기기                  | Y                                             | N                                 |

| 4. <b>HDMI</b> 케이블                   | N                                             | N                                 |

| 5. <b>HDMI</b> 케이블+ <b>HDMI</b> 소스기기 | 5-1: 하이 임피던스<br>5-2: 로우 임피던스<br>5-3: 하이로우의 중간 | N<br>Y<br>M                       |

## 도면45