(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2011-520249

(P2011-520249A)

(43) 公表日 平成23年7月14日(2011.7.14)

(51) Int.Cl.

**H01L 21/3065 (2006.01)**

**H01L 27/105 (2006.01)**

**H01L 45/00 (2006.01)**

**H01L 49/00 (2006.01)**

**H01L 51/05 (2006.01)**

F 1

H01L 21/302 104C

H01L 27/10 448

H01L 45/00 Z

H01L 49/00 Z

H01L 29/28 100B

テーマコード(参考)

5FO04

5FO83

審査請求 未請求 予備審査請求 未請求 (全 22 頁) 最終頁に続く

(21) 出願番号 特願2011-504204 (P2011-504204)

(86) (22) 出願日 平成21年4月10日 (2009.4.10)

(85) 翻訳文提出日 平成22年10月25日 (2010.10.25)

(86) 國際出願番号 PCT/US2009/040215

(87) 國際公開番号 WO2009/126891

(87) 國際公開日 平成21年10月15日 (2009.10.15)

(31) 優先権主張番号 61/044,314

(32) 優先日 平成20年4月11日 (2008.4.11)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 61/081,029

(32) 優先日 平成20年7月15日 (2008.7.15)

(33) 優先権主張国 米国(US)

(71) 出願人 507318624

サンディスク スリーディー, エルエルシ

ー

アメリカ合衆国、95035、カリフォル

ニア州、ミルピタス、マッカシー ブルバ

ード 601

(74) 代理人 100075144

弁理士 井ノ口 喬

(72) 発明者 シュリッカー, エイプリル ディー.

アメリカ合衆国、94306、カリフォル

ニア州、パロ アルト、マンザニータ ア

ベニュー 255

最終頁に続く

(54) 【発明の名称】不揮発性メモリに使用されるカーボンナノチューブ膜をエッティングする方法

## (57) 【要約】

炭素ベースの可逆抵抗率スイッチング材料に結合されているステアリング素子を含むメモリセルと、そのメモリセルを形成する方法とが提供される。特定の実施形態では、本発明に従う方法は、基板の上に形成されたカーボンナノチューブ(「CNT」)膜をエッティングする方法であって、基板をマスキング層でコーティングすることと、マスキング層をパターニングすることと、パターニングされたマスキング層を通して非酸素ベースの化学的手法を用いてCNT膜をエッティングすることを含む。他の態様も記載されている。

FIG. 1

**【特許請求の範囲】****【請求項 1】**

基板の上に形成されたカーボンナノチューブ(「CNT」)膜をエッティングする方法であって、

前記基板をマスキング層でコーティングするステップと、

前記マスキング層をパターニングするステップと、

前記パターニングされたマスキング層を通して非酸素ベースの化学的手法を用いて前記CNT膜をエッティングするステップと、

を含む方法。

**【請求項 2】**

請求項1記載の方法において、

前記CNT膜をエッティングするステップは、

前記基板をプラズマエッティングチャンバの中に装填するステップと、

三塩化ホウ素(「BCl<sub>3</sub>」)およびジクロリン(「Cl<sub>2</sub>」)を用いて前記基板をエッティングするステップと、

を含む方法。

**【請求項 3】**

請求項2記載の方法において、

前記基板をエッティングするステップは、約70:1から約3:5までのBCl<sub>3</sub>対Cl<sub>2</sub>比を用いることを含む方法。

**【請求項 4】**

請求項2記載の方法において、

前記基板をエッティングするステップは、約4:1から約1.8:1までのBCl<sub>3</sub>対Cl<sub>2</sub>比を用いることを含む方法。

**【請求項 5】**

請求項2記載の方法において、

前記基板をエッティングするステップは、約5:2のBCl<sub>3</sub>対Cl<sub>2</sub>比を用いることを含む方法。

**【請求項 6】**

請求項2記載の方法において、

前記基板をエッティングするステップは、アルゴン(「Ar」)を用いることをさらに含む方法。

**【請求項 7】**

請求項6記載の方法において、

前記基板をエッティングするステップは、約70:1:1から約3:5:5までのBCl<sub>3</sub>対Cl<sub>2</sub>対Ar比を用いることを含む方法。

**【請求項 8】**

請求項6記載の方法において、

前記基板をエッティングするステップは、約4:1:1から約1.8:1:1までのBCl<sub>3</sub>対Cl<sub>2</sub>対Ar比を用いることを含む方法。

**【請求項 9】**

請求項6記載の方法において、

前記基板をエッティングするステップは、約5:2:2のBCl<sub>3</sub>対Cl<sub>2</sub>対Ar比を用いることを含む方法。

**【請求項 10】**

請求項1記載の方法において、

前記マスキング層は、フォトレジストを含む方法。

**【請求項 11】**

請求項10記載の方法において、

前記フォトレジストを灰化するステップをさらに含む方法。

10

20

30

40

50

## 【請求項 1 2】

請求項 1 1 記載の方法において、

前記フォトレジストは、前記基板をエッチングする前に灰化される方法。

## 【請求項 1 3】

請求項 1 1 記載の方法において、

前記フォトレジストは、前記基板をエッチングした後に灰化される方法。

## 【請求項 1 4】

請求項 1 1 記載の方法において、

前記灰化するステップは、2ステップ灰化手続きを含む方法。

## 【請求項 1 5】

請求項 1 記載の方法を用いて形成されたメモリセル。

10

## 【請求項 1 6】

メモリセルを形成する方法であって、

基板より上にカーボンナノチューブ（「CNT」）材料の層を形成するステップと、

三塩化ホウ素（「BCl<sub>3</sub>」）およびジクロリン（「Cl<sub>2</sub>」）ならびに約50および

約150ワットの間の基板バイアス電力を用いて前記CNT材料をプラズマエッチングチ

ヤンバ内でエッチングするステップと、

を含む方法。

## 【請求項 1 7】

請求項 1 6 記載の方法において、

20

前記基板バイアス電力は、約85および約110ワットの間にある方法。

## 【請求項 1 8】

請求項 1 6 記載の方法において、

前記基板バイアス電力は、約100ワットである方法。

## 【請求項 1 9】

請求項 1 6 記載の方法において、

前記CNT材料をエッチングするステップは、約70:1から約3:5までのBCl<sub>3</sub>

対Cl<sub>2</sub>比を用いることを含む方法。

## 【請求項 2 0】

請求項 1 6 記載の方法において、

30

前記CNT材料をエッチングするステップは、約4:1から約1.8:1までのBCl<sub>3</sub>

対Cl<sub>2</sub>比を用いることを含む方法。

## 【請求項 2 1】

請求項 1 6 記載の方法において、

前記CNT材料をエッチングするステップは、約5:2のBCl<sub>3</sub>対Cl<sub>2</sub>比を用いる

ことを含む方法。

## 【請求項 2 2】

請求項 1 7 記載の方法において、

前記CNT材料をエッチングするステップは、アルゴン（「Ar」）を用いることをさ

らに含む方法。

40

## 【請求項 2 3】

請求項 2 2 記載の方法において、

前記CNT材料をエッチングするステップは、約70:1:1から約3:5:5までの

BCl<sub>3</sub>対Cl<sub>2</sub>対Ar比を用いることを含む方法。

## 【請求項 2 4】

請求項 2 2 記載の方法において、

前記CNT材料をエッチングするステップは、約4:1:1から約1.8:1:1までの

BCl<sub>3</sub>対Cl<sub>2</sub>対Ar比を用いることを含む方法。

## 【請求項 2 5】

請求項 2 2 記載の方法において、

50

前記 CNT 材料をエッティングするステップは、約 5 : 2 : 2 の BC<sub>1</sub><sub>3</sub> 対 Cl<sub>2</sub> 対 Ar 比を用いることを含む方法。

【請求項 26】

請求項 17 記載の方法において、

前記 CNT 層に結合されるステアリング素子を形成するステップをさらに含む方法。

【請求項 27】

請求項 26 記載の方法において、

前記ステアリング素子は、ダイオードを含む方法。

【請求項 28】

請求項 27 記載の方法において、

10

前記ステアリング素子を形成するステップは、

前記基板より上にシリコンの 1 つ以上の層を形成するステップと、

前記シリコンの 1 つ以上の層をエッティングするステップと、

を含む方法。

【請求項 29】

請求項 28 記載の方法において、

前記シリコンの 1 つ以上の層と前記 CNT 層とを単一のエッティングステップでエッティングするステップを含む方法。

【請求項 30】

請求項 28 記載の方法において、

20

前記シリコンの 1 つ以上の層と前記 CNT 層とを別々にエッティングするステップを含む方法。

【請求項 31】

請求項 17 記載の方法を用いて形成されたメモリセル。

【請求項 32】

メモリセルを形成する方法であって、

基板より上にカーボンナノチューブ（「CNT」）材料の層を形成するステップと、ほとんど垂直の側壁を有するとともに前記 CNT 材料のアンダーカットをほとんどあるいは全く有しないように前記 CNT 材料をエッティングするために非酸素ベースの化学的手法を用いるステップと、

30

を含む方法。

【請求項 33】

請求項 32 記載の方法において、

前記 CNT 層に結合されるステアリング素子を形成するステップをさらに含む方法。

【請求項 34】

請求項 33 記載の方法において、

前記ステアリング素子は、ダイオードを含む方法。

【請求項 35】

請求項 34 記載の方法において、

40

前記ステアリング素子を形成するステップは、

前記基板より上にシリコンの 1 つ以上の層を形成するステップと、

前記シリコンの 1 つ以上の層をエッティングするステップと、

を含む方法。

【請求項 36】

請求項 35 記載の方法において、

前記シリコンの 1 つ以上の層と前記 CNT 層とを単一のエッティングステップでエッティングするステップを含む方法。

【請求項 37】

請求項 35 記載の方法において、

前記シリコンの 1 つ以上の層と前記 CNT 層とを別々にエッティングするステップを含む

50

方法。

【請求項 3 8】

請求項 3 2 記載の方法を用いて形成されたメモリセル。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は、不揮発性メモリに関し、特に、炭素ベースの記憶素子を含むメモリセルとそれを形成する方法とに関する。

【0 0 0 2】

関連出願との相互参照

本願は、あらゆる目的のためにその全体が本願明細書において参照により援用されている、2008年4月11日に出願された「METHODS FOR ETCHING CARBON NANO-TUBE FILMS FOR USE IN NON-VOLATILE MEMORIES」という米国仮特許出願第61/044,314号（特許文献1）の利益を主張するとともに、2008年7月15日に出願された「METHODS FOR ETCHING CARBON NANO-TUBE FILMS」という米国仮特許出願第61/081,029号（特許文献2）の利益を主張する。

【背景技術】

【0 0 0 3】

可逆抵抗スイッチング素子から形成される不揮発性メモリが知られている。例えば、あらゆる目的のためにその全体が本願明細書において参照により援用されている、2007年12月31日に出願された「MEMORY CELL THAT EMPLOYS A SELECTIVELY FABRICATED CARBON NANO-TUBE REVERSIBLE RESISTANCE-SWITCHING ELEMENT AND METHODS OF FORMING THE SAME」という米国特許出願第11/968,154号（特許文献3）は、炭素などの、炭素ベースの可逆抵抗率スイッチング材料と直列に結合されたダイオードを含む再書き込み可能な不揮発性メモリセルを記述している。

しかし、再書き込み可能な抵抗率スイッチング材料からメモリ装置を製造することは技術的に難しく、抵抗率スイッチング材料を使用するメモリ装置を形成する改良された方法が望ましい。

【先行技術文献】

【特許文献】

【0 0 0 4】

【特許文献1】米国仮特許出願第61/044,314号

【特許文献2】米国仮特許出願第61/081,029号

【特許文献3】米国特許出願第11/968,154号

【特許文献4】米国特許出願第11/968,156号

【特許文献5】米国特許出願第11/968,159号

【特許文献6】米国特許出願第12/415,964号

【特許文献7】米国特許第7,176,064号

【特許文献8】米国特許出願第11/444,936号

【特許文献9】米国特許第5,915,167号

【特許文献10】米国特許出願第10/955,549号

【特許文献11】米国特許出願第11/148,530号

【特許文献12】米国特許第7,285,464号

【特許文献13】米国特許第6,952,030号

【発明の概要】

【0 0 0 5】

本発明の第1の態様において、基板の上に形成されたカーボンナノチューブ（「CNT」）膜をエッティングする方法が提供され、その方法は、基板をマスキング層でコーティングすることと、マスキング層をパターニングすることと、パターニングされたマスキング層を通して非酸素ベースの化学的手法を用いてCNT膜をエッティングすることとを含む。

10

20

30

40

50

## 【0006】

本発明の第2の態様において、メモリセルを形成する方法が提供され、その方法は、基板より上にCNT材料の層を形成することと、三塩化ホウ素（「BCl<sub>3</sub>」）およびジクロリン（「Cl<sub>2</sub>」）ならびに約50および約150ワットの間の基板バイアス電力を用いてCNT材料をプラズマエッティングチャンバ内でエッティングすることを含む。

## 【0007】

本発明の第3の態様において、メモリセルを形成する方法が提供され、その方法は、基板より上にCNT材料の層を形成することと、ほとんど垂直の側壁を有するとともにCNT材料のアンダーカットをほとんどあるいは全く有しないようにCNT材料をエッティングするために非酸素ベースの化学的手法を用いることを含む。

10

## 【0008】

本発明の他の特徴および態様は、次の詳細な記述、添付されている特許請求の範囲および添付の図面からより充分に明らかになるはずである。

本発明の特徴は添付の図面と関連して考慮される次の詳細な記述からより明らかに理解することができ、図面全体にわたって同じ参照数字は同じ要素を示す。

20

## 【図面の簡単な説明】

## 【0009】

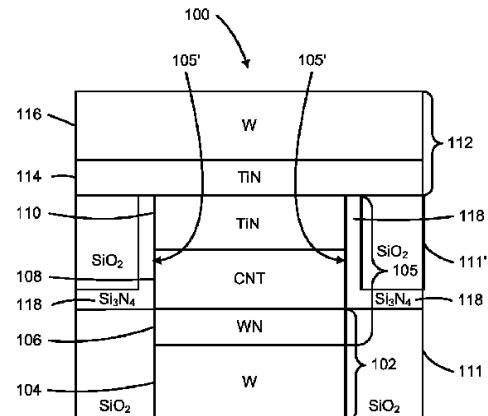

【図1】本発明の実施形態に従う代表的なメモリセルの立面横断面略図を描き、メモリセルは金属-絶縁体-金属構造を囲む側壁ライナを含む。

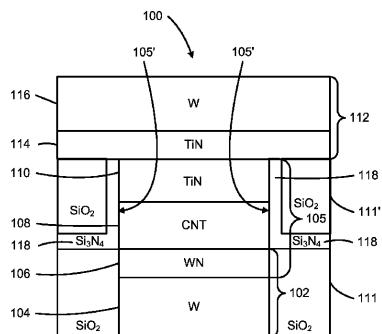

【図2A】本発明の実施形態に従う他の代表的なメモリセルの立面横断面図を描き、各メモリセルはダイオードと直列の金属-絶縁体-金属構造を囲む側壁ライナを含む。

30

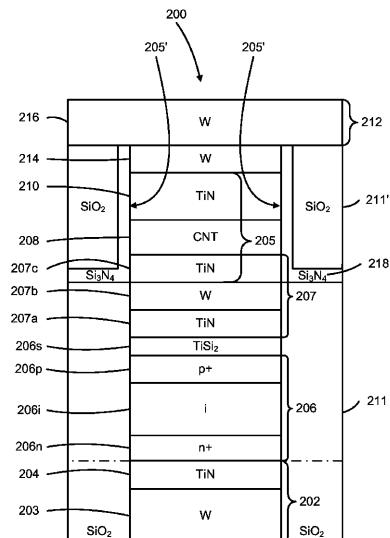

【図2B】本発明の実施形態に従う他の代表的なメモリセルの立面横断面図を描き、各メモリセルはダイオードと直列の金属-絶縁体-金属構造を囲む側壁ライナを含む。

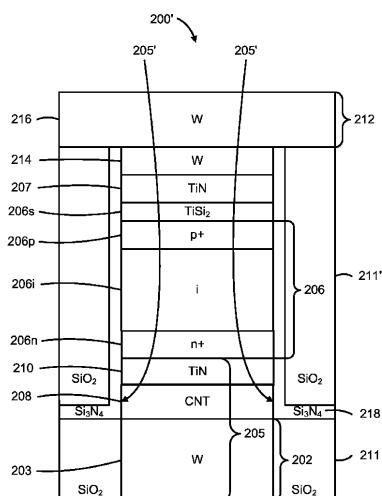

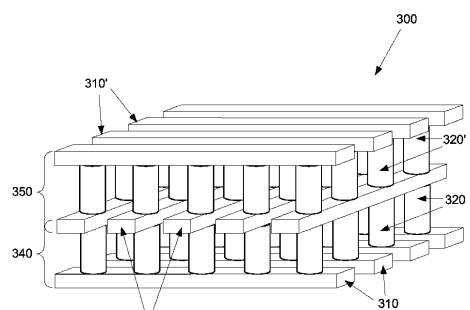

【図3】本発明に従って提供されるモノリシックな3次元メモリアレイの代表的なメモリレベルの透視図である。

## 【発明を実施するための形態】

## 【0010】

CNT、グラフェン、グラフェンの微晶質または他の領域を包含する非晶質炭素、および他の黒鉛状炭素膜などを含むがこれらに限定はされない或る炭素ベースの膜は、マイクロエレクトロニクス不揮発性メモリを形成するために使用され得る抵抗率スイッチング特性を示すことがある。従って、そのような膜は3次元メモリアレイ内に集積化され得る候補である。例えば、CNT材料は、オンおよびオフ状態間の100倍の分離ならびに中間域から高域の抵抗変化を有するメモリスイッチング特性を実験室スケールの装置において示している。オンおよびオフ状態の間のそのような分離の故に、CNT材料は、垂直ダイオード、薄膜トランジスタまたは他のステアリング素子と直列のCNT材料を用いて形成されるメモリセルの実現可能な候補となる。

30

## 【0011】

前述した例では、2つの金属または他の伝導性の層の間に挟まれた炭素ベースの材料から形成される金属-絶縁体-金属（metal-insulator-metal（「MIM」））スタックは、メモリセルのための抵抗変化材料として役立つことができる。さらに、炭素ベースのMIMスタックは、例えば特許文献3に記載されているような読み出し-書き込み可能なメモリ装置を作るためにダイオードまたはトランジスタと直列に統合され得る。

40

## 【0012】

しかし、メモリセルを形成するためにCNT材料が使用されるとき、堆積または成長させられたCNT材料は、しばしば、多数の山および谷などの顕著な厚さ変化を伴う粗い表面トポグラフィを有する。粗い表面トポグラフィは、メモリセルを形成するときに困難を引き起こし得る。例えば、CNT材料の粗い表面トポグラフィは、下に存在する基板を過剰にエッティングすることなくCNT材料をエッティングすることを困難にし、製造コストを増大させるとともに集積回路においてそれらを使用することに関連する複雑さを増大させることがある。

50

## 【0013】

本発明に従う代表的な方法は、C N T 材料から形成される記憶素子を含むメモリセルを形成する。特に、C N T 材料は、割合に低いバイアス条件（例えば、約 1 0 0 W）下でプラズマエッチャならびに B C l<sub>3</sub> および C l<sub>2</sub> 化学的手法を用いてエッチングされ得る。そのような手法を用いてエッチングされた C N T 材料は、ほぼ垂直の側壁を有するとともに C N T 材料のアンダーカットをほとんどあるいは全く有しないということが観察されている。

## 【0014】

少なくとも幾つかの実施形態では、C V D 成長手法、コロイダルスプレーオン手法、およびスピンオン手法によって純粋な C N T が堆積させられ得る。さらに、炭素材料堆積法は、ターゲットからのスパッタ堆積、プラズマ増強化学蒸着 (plasma-enhanced chemical vapor deposition (「P E C V D」))、P V D、C V D、アーク放電手法、およびレーザーアブレーションを含み得るが、これらに限定されない。堆積温度は約 3 0 0 から 9 0 0 に及び得る。前駆物質ガス源は、ヘキサン、シクロヘキサン、アセチレン、シングルおよびダブル短鎖炭化水素（例えば、メタン）、種々のベンゼンベースの炭化水素、多環芳香族、短鎖エステル、エーテル、アルコール、あるいはそれらの組み合わせを含み得るけれども、それらに限定されない。或る場合には、換算温度での成長を促進するために「シーディング (seeding)」面が使用され得る（例えば、他の厚さが使用され得るけれども、約 1 ~ 1 0 0 オングストロームの鉄（「F e」）、ニッケル（「N i」）、コバルト（「C o」）など）。

10

20

30

## 【0015】

或る実施形態では、炭素ベースの抵抗率スイッチング材料は、前に言及した手法のいずれかで堆積させられる非晶質炭素、あるいは黒鉛状炭素と混合された誘電体充填材料から構成され得る。この集積化方式の特定の実施形態は、C N T 材料のスピンまたはスプレー塗布と、それに続く、炭素ベースのライナ材料として用いられるアプライド・マテリアルズ・インコーポレイテッド (Applied Materials, Inc.) からの非晶質炭素、P r o d u c e r (登録商標) ツールの堆積とを含む。任意の炭素ベース保護ライナは、C N T 材料を堆積させるために使用されるものと同様のあるいは異なる堆積手法を用いて堆積させられ得る。

## 【0016】

炭素ベースの抵抗率スイッチング材料は任意の厚さに堆積させられ得る。或る実施形態では、炭素ベース抵抗率スイッチング材料は約 1 ~ 1 , 0 0 0 オングストロームの間であり得るけれども、他の厚さが使用されてもよい。本願明細書に記載されているものなどのデバイス構成に依存して、好ましい範囲は 2 0 0 ~ 4 0 0 オングストローム、4 0 0 ~ 6 0 0 オングストローム、6 0 0 ~ 8 0 0 オングストローム、および 8 0 0 ~ 1 , 0 0 0 オングストロームを含むことができる。

40

## 【0017】

代表的な実施形態

本発明の第 1 の代表的な実施形態に従って、マイクロエレクトロニクス構造の形成は、底部電極および頂部電極の間に配置されている炭素膜を有するM I M デバイスの形成を含み、炭素膜は、例えば、抵抗率スイッチング C N T 層を含む。構造は、誘電体充填ステップ中に炭素ベース材料を劣化から守るために設けられる誘電体側壁ライナをも含む。

## 【0018】

図 1 は、本発明に従って提供される、メモリセル 1 0 0 とも称される第 1 の代表的なマイクロエレクトロニクス構造 1 0 0 の横断面立面図である。メモリセル 1 0 0 は、基板（図示せず）の上、例えば基板の上の絶縁層の上に形成された第 1 の導体 1 0 2 を含む。第 1 の導体 1 0 2 は、タンゲステン（「W」）、銅（「C u」）、アルミニウム（「A l」）、金（「A u」）、または他の金属の層などの、第 1 の金属層 1 0 4 を含み得る。第 1 の導体 1 0 2 は、M I M 層スタック構造 1 0 5 の下側部分を含むことができ、M I M 1 0 5 の底部電極として機能することができる。窒化タンゲステン（「W N」）、窒化チタン

50

(「Tin」)、窒化タンタル(「TaN」)、モリブデン(「Mo」)などの接着層106、あるいは類似の層は任意のものであるけれども図1では第1の金属層104の上に形成されて示されている。一般的に、複数の第1の導体102が設けられて(例えば、第1の導体102の各々の間に二酸化ケイ素(「SiO<sub>2</sub>」)または他の誘電体材料絶縁を使用することによって)互いから絶縁させられ得る。例えば、第1の導体102は、格子パターニングされたアレイのワード線またはビット線であり得る。

【0019】

CNT材料108の層が、任意の適切なCNT形成プロセスを用いて第1の導体102の上に形成される。CNT材料108は、MIM層スタック構造105の中央部分を構成してMIM105のスイッチング層として機能することができる。CNT材料108は、種々の手法により堆積させられ得る。1つの手法は、第1の導体102の上にカーボンナノチューブ懸濁液をスプレーコーティングまたはスピンドルコーティングすることによってランダムなCNT材料を作ることを包含する。他の1つの手法は、CVD、PECVDなどによって基板に固着されたシードからカーボンナノチューブを成長させることを含む。種々のCNT堆積手法についての論議が、特許文献3と、関連する2007年12月31日に出願された「MEMORY CELL THAT EMPLOYS A SELECTIVELY FABRICATED CARBON NANO-TUBE REVERSIBLE RESISTANCE-SWITCHING ELEMENT FORMED OVER A BOTTOM CONDUCTOR AND METHODS OF FORMING THE SAME」という米国特許出願第11/968,156号(特許文献4)および2007年12月31日に出願された「MEMORY CELL WITH PLANARIZED CARBON NANOTUBE LAYER AND METHODS OF FORMING THE SAME」という米国特許出願第11/968,159号(特許文献5)とに見出され、これら特許出願はあらゆる目的のためにその全体が本願明細書において参照により援用されている。

10

20

30

【0020】

本発明に従う或る実施形態では、CNT材料108の堆積/形成後に、CNT材料108の特性を改変するためにアニーリングのステップが実行され得る。特に、アニーリングは、真空中あるいは1つ以上のフォーミングガスの存在下で、約350から約900までの範囲の温度で、約30分から約180分にわたって、実行され得る。アニーリングは、好ましくは、およそ80%(N<sub>2</sub>) : 20%(H<sub>2</sub>)混合物のフォーミングガス中に約625で約1時間にわたって実行される。

【0021】

適切なフォーミングガスはN<sub>2</sub>、Ar、およびH<sub>2</sub>のうちの1つ以上を含み得るが、好ましいフォーミングガスは約75%より多いN<sub>2</sub>またはArと約25%未満のH<sub>2</sub>とを有する混合物を含み得る。代わりに、真空が使用され得る。適切な温度は約350から約900に及ぶが、好ましい温度は約585から約675に及び得る。適切な持続時間は約0.5時間から約3時間に及び得るが、好ましい持続時間は約1時間から約1.5時間に及び得る。適切な圧力は約1mTから約760mTに及び得るが、好ましい圧力は約300mTから約600mTに及び得る。

【0022】

このアニーリングは、CNT材料108より上の頂部電極の形成の前に実行され得る。アニーリングと電極金属堆積との間の好ましくは約2時間の待ち時間が、アニーリングの使用に好ましくは伴う。ランプアップ持続時間は約0.2時間から約1.2時間に及ぶことができ、好ましくは約0.5時間および0.8時間の間にある。同様に、ランプダウン持続時間も約0.2時間から約1.2時間に及ぶことができ、好ましくは約0.5時間および0.8時間の間にある。

40

【0023】

いかなる特定の理論にも束縛されたくないけれども、CNT材料は空気から水を吸収するかも知れずかつ/またはCNT材料が形成された後に1つ以上の官能基がCNT材料に付着しているかも知れないと考えられる。ときには有機官能基が堆積前処理のために必要とされる。好ましい官能基の1つはカルボキシル基である。同様に、水分および/または有機官能基は、CNT材料の層割れの可能性を高めるかも知れないと考えられる。さらに

50

、官能基は、例えばクリーニングおよび／またはフィルタリングのプロセスの間にC N T材料に付着し得ると考えられる。炭素形成後のアニーリングは、C N T材料に関する水分および／またはカルボキシル基もしくは他の官能基を除去することができる。その結果として、或る実施形態では、C N T材料の上での頂部電極の形成前にC N T材料がアニーリングされれば、C N T材料および／または頂部電極材料の基板からの層割れは起こりにくくなる。

【0024】

そのようなC N T形成後のアニーリングの組み込みは、C N T材料を含むデバイス上に存在する他の層をも、それらの他の層もアニーリングにさらされることになるので、好ましくは考慮に入れるべきものである。例えば、前述した好ましいアニーリングのパラメータが他の層を損傷させる場合にはアニーリングは省略されてもよく、あるいはそのパラメータが調整されてもよい。アニーリングのパラメータは、アニーリングされるデバイスの層を損傷させることなく水分および／またはカルボキシル基もしくは他の官能基の除去という結果をもたらす範囲の中で調整され得る。例えば、形成されるデバイスの総熱余裕度内に留まるように温度が調整され得る。同様に、特定のデバイスに適する任意の適切なフォーミングガス、温度および／または持続時間が使用され得る。一般的に、そのようなアニーリングは、C N T材料、グラファイト、グラフェン、非晶質炭素などを有する層などの、任意のカーボンベースの層あるいは炭素含有材料に対して使用され得る。

10

【0025】

あらゆる目的のためにその全体が本願明細書において参照により援用されている、「ELECTRONIC DEVICES INCLUDING CARBON-BASED FILMS HAVING SIDEWALL LINERS, AND METHODS OF FORMING SUCH DEVICES」という2009年3月31日に出願された、本発明の譲受人により所有されている同時係属中の米国特許出願第12/415,964号（特許文献6）に記載されているように、本発明に従う或る実施形態では、C N T材料108の堆積／形成の後に、任意の第2の炭素ベース材料層（図示せず）が、C N T材料108を覆う保護ライナとして形成され得る。

20

【0026】

C N T材料108の形成後、T i N、T a N、W、W N、タンタルカーボンニトリド（「T a C N」）などの接着／障壁層110がC N T材料108の上に形成され得る。図1に示されているように、接着層110は、スイッチング層としてのC N T材料108と、底部電極としての第1の金属層104および任意の接着層106とを含むM I Mデバイス105の頂部電極として機能することができる。それゆえ、次のセクションでは、接着／障壁層110をM I M 105の「頂部電極110」と称する。

30

【0027】

本発明に従う或る実施形態では、頂部電極110は、例えば同様の材料のP V Dに用いられるものよりも低いエネルギーレベルを必要とするものなどの、低エネルギー堆積手法を用いて堆積させられ得る。そのような代表的な堆積手法は、非共形堆積、低バイアス電力物理蒸着（low bias power physical vapor deposition（「L B P - P V D」））、低温P V D、および他の類似の手法を含み得る。炭素材料上に頂部電極110を堆積するために非共形低エネルギー堆積手法を使用すれば、C N T材料108に対する堆積関連の損傷の可能性と、頂部電極110によるC N T材料108の浸透および／または侵入の可能性とを減少させることができる。任意の炭素ライナの使用を控える実施形態では、頂部電極110の堆積の有害な効果を制限するために低エネルギー堆積手法の使用は特に有利である。非共形である金属堆積手法が金属をC N T材料108の細孔の中に堆積させる可能性は低い。

40

【0028】

層108および110の層スタックは、例えば、標準的なフォトリソグラフィ手法を用いて約1～約1.5ミクロン、より好ましくは約1.2～約1.4ミクロンのフォトレジスト（「P R」）でパターニングされ得る。小さな限界寸法および技術ノードとともに薄いP R層が使用され得る。或る実施形態では、パターン転写を改善するとともにエッチ

50

グ中に下にある層を保護するためにP R層より下で酸化物ハードマスクが使用され得る。

【0029】

前に言及したように、C N T材料は一般的に、C N T材料をエッティングしにくくする顕著な厚さ変化を伴う粗い表面トポグラフィを有する。本発明に従う方法は、標準的な半導体ツーリングおよび／または処理設備と完全に両立し得る非酸素ベースの化学的手法を用いてC N T材料108をエッティングする方法を提供する。簡略化するために、残りの論議は、C N T材料108をエッティングするための代表的な手法に言及する。当業者であれば、頂部電極110をエッティングするために同じ手法が使用され得ることが理解できるはずである。

【0030】

特に、少なくとも本発明の或る実施形態では、C N T材料108は、三塩化ホウ素（「B C l<sub>3</sub>」）およびジクロリン（「C l<sub>2</sub>」）化学的手法を用いてエッティングされ得る。例えば、C N T材料108は、B C l<sub>3</sub>およびC l<sub>2</sub>ガスフロー入力を用いて、C N T材料108をエッティングするために使用され得る塩素イオン（C l<sup>+</sup>）などの反応種を生成するプラズマエッティングチャンバ内でエッティングされ得る。B C l<sub>3</sub>対C l<sub>2</sub>比は、約4：1から約1.8：1まで、より一般的には約70：1から約3：5までである。少なくとも1つの実施形態では、約100ワットの基板バイアス電力および約450ワットのプラズマ電力でC N T材料108をエッティングするために、およそ5：2のB C l<sub>3</sub>対C l<sub>2</sub>比が使用され得る。C N T材料108をエッティングするためのプラズマエッティングプロセスのための代表的な処理条件が次の表1において提供されている。他の比、流量、チャンバ圧力、電力レベル、プロセス温度、および／またはエッティング速度が使用され得る。

10

20

30

表1：代表的なプラズマエッティングのプロセスパラメータ

| プロセスパラメータ                       | 代表的な範囲  | 好ましい範囲  |

|---------------------------------|---------|---------|

| B C l <sub>3</sub> 流量 (s c c m) | 30～70   | 45～60   |

| C l <sub>2</sub> 流量 (s c c m)   | 0～50    | 15～25   |

| 圧力 (ミリトール)                      | 50～150  | 80～100  |

| 基板バイアスRF (ワット)                  | 50～150  | 85～110  |

| プラズマRF (ワット)                    | 350～550 | 390～410 |

| プロセス温度 (°C)                     | 45～75   | 60～70   |

| エッティング速度 (Å/秒)                  | 3～10    | 4～5     |

【0031】

本発明の代替の実施形態に従って、C N T材料108は、塩素およびアルゴン化学的手法を用いてエッティングされ得る。例えば、C N T材料108は、B C l<sub>3</sub>、C l<sub>2</sub>およびアルゴンのガスフロー入力を用い、C N T材料をエッティングすることのできる塩素イオン（C l<sup>+</sup>）およびアルゴンイオン（A r<sup>+</sup>）などの反応種を生成するプラズマエッティングチャンバの中でエッティングされ得る。B C l<sub>3</sub>：C l<sub>2</sub>：A rの比は約4：1：1から約1.8：1：1まで、より一般的には約70：1：1から約3：5：5まであり得る。少なくとも1つの実施形態では、約100ワットの基板バイアス電力でC N T材料108をエッティングするためにおよそ5：2：2のB C l<sub>3</sub>：C l<sub>2</sub>：A r比が使用され、また約450ワットのプラズマ電力が使用され得る。C N T材料のためのプラズマエッティングプロセスのための代表的な処理条件が次の表2において提供されている。他の比、流量、チャンバ圧力、電力レベル、プロセス温度、および／またはエッティング速度が使用され得る。

40

表2：代表的なプラズマエッチングのプロセスパラメータ

| プロセスパラメータ                  | 代表的な範囲  | 好ましい範囲    |

|----------------------------|---------|-----------|

| BC <sub>13</sub> 流量 (sccm) | 30～70   | 45～60     |

| Cl <sub>2</sub> 流量 (sccm)  | 0～50    | 15～25     |

| アルゴン流量 (sccm)              | 0～50    | 15～25     |

| 圧力 (ミリトール)                 | 50～150  | 80～100    |

| 基板バイアスRF (ワット)             | 100～200 | 125～175   |

| プラズマRF (ワット)               | 350～550 | 390～410   |

| プロセス温度 (°C)                | 45～75   | 60～70     |

| エッチング速度 (Å/秒)              | 10～20   | 13.8～14.5 |

10

20

30

40

## 【0032】

或る実施形態では、頂部電極110およびCNT材料108は、単一のエッチングステップを用いてパターニングされ得る。他の実施形態では、別々のエッチングステップが使用され得る。例えば、頂部電極110は塩素プロセス(表1あるいはアルゴンの流れを有しない表2のものと同様)を用いてエッチングされ、CNT材料108は塩素・アルゴン化学的手法(表2のものと同様)を用いてエッチングされ得る。他の実施形態では、単一のエッチング手続きが使用され得る(例えば、表2のように塩素・アルゴン化学を用いる)。研究によって、エッチング中にアルゴンを使用すればCNT材料108のエッチング速度を高めることができることが示された。

頂部電極110およびCNT材料108のエッチングは下方に第1の導体102まで進行してギャップ充填材料111を露出させる。そのようなエッチングされた層スタックはほとんど垂直の側壁105'を有するとともにCNT材料108のアンダーカットをほとんどあるいは全く有しないと観察されている。

## 【0033】

或る実施形態では、頂部電極110およびCNT材料108をエッチングする前に、PRは標準的な処理を用いて灰化され得る。他の実施形態では、PRはCNT材料108をエッチングした後に灰化される。PRが灰化される実施形態では、CNTエッチングは、約55～65秒にわたって約125～175ワットのバイアスを用い、約45～60sccmのBC<sub>13</sub>、約15～25sccmのCl<sub>2</sub>および約15～25sccmのアルゴンを含むことができる。PRが灰化されない実施形態では、より長いエッチング時間(例えば、約60～70秒)とともに同一の条件が使用され得る。いずれの場合にも、CNTエッチング中、60～70のチャック温度が使用され得る。CNTドライエッチングのための代表的な範囲は、約100～250ワットのバイアスと、約45～85のチャック温度と、約2:1から5:1までのBC<sub>13</sub>:Cl<sub>2</sub>、および約5:1から無アルゴンまでのAr:Cl<sub>2</sub>ガス比範囲とを含む。エッチング時間は、CNT厚さに比例し得る。

## 【0034】

CNT材料108がエッチングされた後に灰化が実行されるのであれば、例えば、灰化プロセスのバイアスおよび/または方向性構成要素は増大させられてよく、灰化プロセス中の酸素の圧力は下げられてよい。両方の属性が、CNT材料108のアンダーカッティングを減少させるのに役立ち得る。カリフォルニア州サンノゼのガソニクス・インターナショナル(GaSonics International)から入手し得るイリディアアッシャー(Iridia asher)などの、任意の適切な灰化ツールが使用され得る。

## 【0035】

少なくとも或る実施形態では、2ステップを含む灰化処理が使用される。第1の灰化ステップのための代表的なプロセス条件が次の表3において提供されている。第2の灰化ス

50

ステップのための代表的なプロセス条件が次の表 4 において提供されている。他の流量、圧力、RF 電力および / または時間が使用され得る。

表3：代表的な第1の灰化ステップのプロセスパラメータ

| プロセスパラメータ                               | 代表的な範囲  | 好ましい範囲  |

|-----------------------------------------|---------|---------|

| CF <sub>4</sub> 流量 (sccm)               | 10~50   | 20~30   |

| N <sub>2</sub> H <sub>2</sub> 流量 (sccm) | 80~120  | 90~110  |

| H <sub>2</sub> O <sub>2</sub> 流量 (sccm) | 200~350 | 260~290 |

| 圧力 (ミリトール)                              | 600~800 | 650~750 |

| 基板バイアスRF (ワット)                          | 0       | 0       |

| プラズマRF (ワット)                            | 350~450 | 400~430 |

| 時間 (秒)                                  | 20~120  | 50~70   |

10

表4：代表的な第2の灰化ステップのプロセスパラメータ

| プロセスパラメータ                | 代表的な範囲  | 好ましい範囲  |

|--------------------------|---------|---------|

| O <sub>2</sub> 流量 (sccm) | 350~450 | 380~420 |

| 圧力 (ミリトール)               | 200~600 | 380~440 |

| 基板バイアスRF (ワット)           | 50~200  | 90~120  |

| プラズマRF (ワット)             | 350~450 | 400~430 |

| 時間 (秒)                   | 20~120  | 50~70   |

20

### 【0036】

バイアス電力は通常処理のためにゼロから増大させられてよく、灰化時間は、使用されるPRの厚さに比例し得る。

30

頂部電極110およびCNT材料108のエッティング後、層スタックは、付加的な誘電体ギャップ充填材111'の形成前に洗浄され得る。データは、EKC型の洗浄ではCNT層が離層することを示しているので、スタックがエッティングされた後、希薄フッ化水素酸/硫酸洗浄が実行される。CNTエッティング後の洗浄は、CNTエッティング前にPR灰化が実行されてもされなくとも、モンタナ州カリスペルのセミツール(Semitoil)から入手し得るレイダーツール(Raider tool)などの任意の適切な洗浄ツールで実行され得る。代表的なCNTエッティング後の洗浄は、約60秒にわたる超希薄硫酸(例えば、約1.5~1.8重量%)および60秒にわたる超希薄フッ化水素(「HF」)酸(例えば、約0.4~0.6重量%)の使用を含み得る。メガソニックは使用されてもされなくてもよい。このような洗浄の後、残留フォトレジストは観察されなかった。フォトレジストがCNT材料と接触すれば、PRを除去することは困難であり、CNT材料の電気的性能は悪くなる。

40

### 【0037】

それゆえ、スタックをエッティングし洗浄するステップの代表的なシーケンスは、次のとおりである。すなわち、(1)PRをパターニングし、(2)パターンを酸化物ハードマスクの中に転写し、(3)PRを灰化除去し(金属がCNTを保護するので、ここに灰化ツールがあつてよい)、(4)希薄フッ化水素酸および硫酸洗浄を用いて洗浄し、(5)BCl<sub>3</sub>およびCl<sub>2</sub>化学的手法を用いてスタックをエッティングし(CNTは露出しているので、エッティング後灰化は使用されない)、(6)希薄HF/硫酸洗浄を用いて再び洗浄することである。エッティングおよび洗浄ステップの後に、誘電体側壁ライナが形成され

50

得る。

【0038】

洗浄後、一般的にはギャップ充填材の堆積が行われる。しかし、誘電体ギャップ充填材料111'を堆積させるための一般的なPECVD手法は、堆積の初期段階で生じる酸素プラズマ成分を使用することがある。この初期酸素プラズマは、CNT材料108を損傷させ、アンダーカッティングおよび良くない電気的性能の原因となることがある。そのような損傷を避けるために、本発明に従う方法は、残りのギャップ充填誘電体111'（例えば、 $\text{SiO}_2$ ）の堆積中にCNT材料108の側壁105'を保護するための誘電体側壁ライナ118を形成する。

【0039】

誘電体側壁ライナ118は、「貧酸素」誘電体を生じさせる低酸素含有量を有する堆積化学を用いて堆積させられる。1つの代表的な実施形態では、標準的PECVD  $\text{SiO}_2$  誘電体充填材111'が後に続く窒化シリコン誘電体側壁ライナ118が使用され得る。化学式どおりの窒化シリコンは $\text{Si}_3\text{N}_4$ であるが、化学式どおりおよび化学式どおりではない窒化シリコンを同様に指すために本願明細書では窒化シリコン（あるいは簡単に「 $\text{SiN}$ 」）が使用される。

【0040】

図1の実施形態では、ギャップ充填材部分111'、例えば誘電体ギャップ充填材の残りが堆積させられる前に、頂部電極/aC/CNT構造物のエッチングされた層スタックの上に誘電体側壁ライナ118が共形に堆積させられる。誘電体側壁ライナ118は、好みしくは、CNT材料108の外側壁105'を覆って、それらを誘電体充填材111'から絶縁させる。下にある誘電体ギャップ充填材料111のエッチングが生じるようCNT材料108がオーバーエッチングされたならば、誘電体側壁ライナ118はCNT材料108より下へ伸び得る。

【0041】

或る実施形態では、誘電体側壁ライナ118は、約200～約500オングストロームの $\text{SiN}$ を含み得る。しかし、構造は、他の層の厚さおよび/または他の材料、例えば $\text{Si}_x\text{C}_y\text{N}_z$ および $\text{Si}_x\text{O}_y\text{N}_z$ （低O含有量を有する）などを任意に含むことができ、ここでx、yおよびzは安定な化合物をもたらす非ゼロ数である。

画定された頂部電極/CNT構造物を $\text{SiO}_2$ または他の誘電体充填材111'で絶縁することができ、その後に頂部電極110、ギャップ充填材111'および誘電体側壁ライナ118を共同露出させるために平坦化することができる。第2の導体112が平坦面の上に形成され、頂部電極110を露出させることができる。第2の導体112は、 $\text{TiN}$ 、 $\text{TaN}$ 、 $\text{WN}$ 、 $\text{Mo}$ 、あるいは同様の材料などの障壁/接着層114と、金属層116（例えば、タンゲステンまたは他の伝導性材料）とを含むことができる。

【0042】

МИМデバイス105は、メモリセル100のために抵抗率スイッチング記憶素子として役立つことができる。CNT材料108はメモリセルの記憶素子の抵抗率スイッチング部分を形成することができ、記憶素子は2つ以上の抵抗率状態の間でスイッチングするようになされている。例えば、МИМデバイス105は、ダイオード、トンネル接合、または薄膜トランジスタ（「TFT」）などのステアリング素子と直列に結合され得る。少なくとも1つの実施形態では、ステアリング素子は多結晶質垂直ダイオードを含むことができる。

【0043】

メモリ動作は、高いバイアス電圧（例えば、>4V）の印加によるCNTスタック可能層108における双安定抵抗変化に基づく。メモリセルを通る電流は、CNT材料108の抵抗により調整される。メモリセルは、CNT材料108の抵抗を変化させない低電圧で読み出される。或る実施形態では、2つの状態間の抵抗率の差は100倍を上回り得る。メモリセルは、例えば、ステアリング素子（例えば、ダイオード）に対する高い順方向バイアスの印加によって、「0」から「1」へ変化させられ得る。メモリセルは、高い順

10

20

30

40

50

方向バイアスの印加によって逆に「1」から「0」へ変化させられ得る。前述したように、この集積化方式は、垂直柱ダイオードの代わりのステアリング素子としてのTFTまたはトンネル接合と直列のCNT材料を含むように拡張され得る。TFTまたはトンネル接合ステアリング素子は平坦あるいは垂直であり得る。

【0044】

本発明の第2の代表的な実施形態に従って、マイクロエレクトロニクス構造の形成は、底部電極および頂部電極の間に配置されている炭素膜と、炭素ベースの材料を誘電体充填ステップの間の劣化から守るために設けられる誘電体側壁ライナとを有する、MIMデバイスと直列のダイオードの形成を含む。誘電体ライナおよびその使用は、標準的な半導体製造装置と両立する。

10

【0045】

図2は、本発明に従って提供される代表的なメモリセル構造200の横断面立面図である。図2Aおよび2Bは、異なる順序で形成されるメモリセルの層を描いている。図2Aでは、メモリセル構造200は、誘電体側壁ライナと、底部電極および頂部電極の間に配置されているCNT膜とを有するMIMデバイスより下に配置されているダイオードを含む。図2Bでは、メモリセル構造200'は、MIMデバイスより上に配置されているダイオードを有する。

【0046】

図2Aに示されているように、メモリセル構造200は、基板(図示せず)の上に形成された第1の導体202を含む。第1の導体202は、W、Cu、Al、Au、または他の金属層などの第1の金属層203と、第1の金属層203の上に形成されたTiN、TaNまたは類似層などの第1の障壁/接着層204とを含むことができる。図2Bに示されているように、第1の導体202はMIM層スタック構造205の下側部分を含んでMIM205の底部電極として機能することができる。一般的に、複数の第1の導体202が設けられて、例えば、パターニングされエッチングされ、例えば各々の第1の導体202の間にSiO<sub>2</sub>または他の誘電体材料絶縁を使用することによって、互いから絶縁させることができる。

20

【0047】

垂直pin(またはnipp)ダイオード206が第1の導体202より上に形成される。例えば、ダイオード206は多結晶質(例えば、ポリシリコン、ポリゲルマニウム、シリコン-ゲルマニウム合金など)ダイオードを含むことができる。ダイオード206は、第1のタイプ(例えば、n形)のドーパントで強くドープされた半導体材料の層206nと、真性のあるいは軽くドープされた半導体材料の層206iと、第2のタイプ(例えば、p形)のドーパントで強くドープされた半導体材料の層206pとを含むことができる。あるいは、図2Bに示されているダイオード206と類似して、ダイオード206の層206n、206i、および206pの垂直方向順序は逆にされてもよい。

30

【0048】

或る実施形態では、任意のシリサイド領域206sがダイオード206の上に形成され得る。あらゆる目的のためにその全体が本願明細書において参照により援用されている米国特許第7,176,064号(特許文献7)に記載されているように、チタンおよびコバルトなどのシリサイド形成材料が、アニーリング中、堆積したシリコンと反応してシリサイド層を形成する。チタンシリサイドおよびコバルトシリサイドの格子面間隔はシリコンのものに近くて、そのようなシリサイド層は、堆積したシリコンが結晶化するときに、隣接する堆積したシリコンのための「結晶化テンプレート」または「シード」として役立ち得ると思われる(例えば、シリサイド層は、アニーリング中、ダイオード206の結晶構造を強化する)。これにより、低抵抗率シリコンが提供される。シリコン-ゲルマニウム合金および/またはゲルマニウムのダイオードのために同様の結果が成し遂げられ得る。ダイオード206を結晶化させるためにシリサイド領域206sを用いる或る実施形態では、完成した構造にシリコン領域206sが残らないように、シリサイド領域206sは、そのような結晶化の後に除去され得る。

40

50

## 【0049】

TiNまたは他の接着/障壁層または層スタック207がダイオード206より上に形成され得る。或る実施形態では、接着/障壁層207は、第1の接着/障壁層207aと、Wなどの金属層207bと、TiNなどのさらなる接着/障壁層207cとを含む層スタック207を含むことができる。

## 【0050】

層スタック207が使用される場合には、層207aおよび207bは、化学的機械的平坦化(「CMP」)ストップ層および/またはエッチングストップ層として作用し得る金属ハードマスクとして役立つことができる。そのような手法は、例えば、あらゆる目的のためにその全体が本願明細書において参照により援用されている、2006年5月31日に出願された「CONDUCTIVE HARD MASK TO PROTECT PATTERNED FEATURES DURING TRENCH ETCH」という米国特許出願第11/444,936号(特許文献8)に開示されている。例えば、ダイオード206と層207aおよび207bとを支柱を形成するためにパターニングしエッチングすることができ、それらの支柱の間に誘電体充填材料211が形成され得る。スタックは、その後、ギャップ充填材211および層207bを共同露出させるためにCMPまたはエッチバックなどによって平坦化され得る。その後、層207cが層207b上に形成され得る。あるいは、層207cは、ダイオード206と層207aおよび207bとともにパターニングされエッチングされ得る。或る実施形態では、層207cは除去されてもよく、CNT材料は金属層207b(例えば、W)と直に接続してもよい。

10

20

## 【0051】

その後、(前に説明したように)任意の適切なCNT形成プロセスを用いてCNT材料208が接着/障壁層または層スタック207の上に形成され得る。CNT材料208の堆積/形成後、前に説明したように、任意の第2の炭素ベース材料層(図示せず)が、CNT材料208を覆う保護ライナとして形成され得る。CNT材料208の堆積/形成後、TiN、TaN、WN、Moなどの第2の接着/障壁層210がCNT材料208の上に形成される。

30

## 【0052】

図2Aに示されているように、接着層207は、スイッチング層としてのCNT材料208と頂部電極としての接着層210とを含むMIM層スタック205の底部電極として機能することができる。それゆえ、次のセクションでは、図2Aに関して接着/障壁層207を「底部電極207」と称する。同様に、接着/障壁層210は、図2Aおよび図2BのMIM205の「頂部電極210」と称される。頂部電極210は、前に論じたように、低エネルギー堆積手法を用いて堆積させられ得る。(図に示されているように、)付加的なハードマスクおよび/またはCMPストップ層214も形成され得る。

40

## 【0053】

接着層(図示せず)および伝導層216を含み得る頂部導体212の形成前に、図1に関して前に論じたように、層スタックはパターニングおよびエッチングされ得る。前に言及した支柱を作るためにエッチングプロセスが行われるとすれば、エッチングは層208、210に適用され、またことによると207cおよび214にも適用され得る。例えば、層214、210はCNT材料208のためのハードマスクおよび/またはCMPストップとして役立ち得る。

50

## 【0054】

或る実施形態では、CNT材料208は、第2の接着/障壁層210のために使用されるエッチングステップとは異なるエッチングステップを用いてエッチングされ得る。他の実施形態では、単一のエッチングステップが使用され得る。そのようなエッチングされた膜スタックは、ほぼ垂直の側壁205'を有するとともにCNT材料208のアンダーカットをほとんどあるいは全く有しないということが観察されている。或る実施形態では、CNT材料208は、下にある誘電体ギャップ充填材料211のエッチングが生じ得るよう、オーバーエッチングされ得る。

50

## 【0055】

頂部電極 210 および CNT 材料 208 のエッティング後、付加的な誘電体ギャップ充填材 211' の堆積前に層スタックは洗浄され得る。洗浄後、ギャップ充填材 211' の堆積前に、酸素に富むギャップ充填誘電体 211' ( 例えば、SiO<sub>2</sub> ) の堆積の間の CNT 材料 208 の側壁 205' を保護するために貧酸素堆積化学的手法 ( 例えば、高酸素プラズマ成分なし ) で誘電体側壁ライナ 218 が形成され得る。誘電体側壁ライナ 218 は、誘電体前充填材ライナと称されてもよい。

## 【0056】

図 2 の実施形態では、標準的な PECVD SiO<sub>2</sub> 誘電体充填材 211' が後に続く窒化シリコン誘電体側壁ライナ 218 が使用され得る。窒化シリコン誘電体側壁ライナ 218 は、化学式どおりおよび / または化学式どおりでない窒化シリコンを含むことができる。或る実施形態では、誘電体側壁ライナ 218 は約 200 ~ 約 500 オングストロームの SiN を含むことができる。しかし、この構造は、他の層の厚さおよび / または他の材料、例えば Si<sub>x</sub>C<sub>y</sub>N<sub>z</sub> および Si<sub>x</sub>O<sub>y</sub>N<sub>z</sub> ( 低 O 含有量を有する ) などを任意に含むことができ、ここで x、y および z は安定な化合物をもたらす非ゼロ数である。

10

## 【0057】

誘電体側壁ライナ 218 は、例えば誘電体ギャップ充填材の残りなどのギャップ充填材部分 211' が堆積させられる前に頂部電極 / aC / CNT 構造物の層スタックの上に共形に堆積させられる。誘電体側壁ライナ 218 は、好ましくは CNT 材料 208 の外側壁 205' を覆い、それらを誘電体充填材 211' から絶縁させる。下にある誘電体ギャップ充填材 211 のエッティングが生じるように CNT 材料 208 がオーバーエッティングされる実施形態では、誘電体側壁ライナ 218 は CNT 材料 108 より下へ延びることができる。

20

## 【0058】

頂部電極 / CNT 構造物の画定された層スタックは、SiO<sub>2</sub> または他の誘電体充填材 211' で絶縁させられた後、頂部電極 210 、ギャップ充填材 211' 、および SiN 誘電体側壁ライナ 218 を共同露出させるために平坦化される。第 2 の接着 / 障壁層 210 の上に、あるいは、層 214 がハードマスクとして使用されて層 208 および 210 とともにエッティングされるならば層 214 の上に第 2 の導体 212 が形成される。第 2 の導体 212 は、図 1 および 2 に示されているように、TiN、TaN、WN または類似の層などの障壁 / 接着層と、W または他の伝導層などの金属層 216 とを含むことができる。

30

## 【0059】

図 1 とは対照的に、図 2 は、接着 / 障壁層 210 上に、スタックがエッティングされる前に堆積させられたタングステンの層 214 を描き、層 214 もエッティングされる。層 214 は、その下の層をエッティングするのに役立つ金属ハードマスクとして作用することができる。層 214 および 216 が両方ともタングステンであり得る限り、それらは互いによく接着するはずである。任意に、SiO<sub>2</sub> ハードマスクが使用され得る。

1 つの代表的な実施形態では、例えば前に援用されている特許文献 6 に記載されているように、SiN 誘電体側壁ライナ 218 が形成され得る。

40

## 【0060】

図 2B に示されているように、マイクロエレクトロニクス構造 200' は、他の層の再配置を生じさせて CNT 材料 208 より上に置かれたダイオード 206 を含むことができる。特に、CNT 材料 208 は、図 2A に示されているように接着 / 障壁層 204 上に、あるいは図 2B に示されているように下側導体 202 上に直接堆積させられ得る。下側導体からのタングステンは、例えば、CNT 材料 208 の形成を、それが成長させられるのであれば、触媒的に助けることができる。タングステンは、炭素によく付着するようにも思われる。接着 / 障壁層 210 を炭素ベースのスイッチング層 208 上に直接形成することができ、その後に、場合によってはシリサイド領域 206s を含むことのあるダイオード 206 が形成される。接着 / 障壁層 207 がダイオード 206 上に ( シリサイド領域 206s を伴って、あるいは伴わずに ) 形成され得る。

50

## 【0061】

図2Bは層207上にタングステンなどの層214を描き、この層214は、好みしくは同じくタングステンから作られる第2の導体212の金属層216に対して金属ハードマスクおよび／または接着層として役立つことができる。スタッツは、前に説明したように、パターニングされエッチングされて支柱になることができる。或る実施形態では、層206、207、208、210、および214の層スタッツ全体が、単一のフォトリソグラフィステップを用いてパターニングされ得る。

## 【0062】

図1に関して言及した任意の酸化物ハードマスクより上に、あるいはその代わりに、構造物サイズ、例えば限界寸法をさらに減少させるためにシリコンの層が形成されて可縮ハードマスクとして使用され得る。或る実施形態では、シリコンは、PECVD手法を用いて堆積させられたときに非晶質である。シリコンハードマスクを形成するためにPR層をパターニングしてパターンを非晶質シリコン内にエッチングした後、シリコンハードマスクはパターンの限界寸法を減少させるために収縮させられ得る。

10

## 【0063】

誘電体側壁ライナ218は、柱と、第1の導体202を絶縁させる誘電体充填材211との上に共形に堆積させられ得る。この場合、誘電体側壁ライナ218は、第1の導体202と第2の導体212との間の層スタッツの高さ全体に沿って上方に延びることができる。ギャップ充填材211'、金属ハードマスク層214、および誘電体側壁ライナ218を共同露出させるための平坦化の後に、図2Bに示されている構造200'を達成するために頂部導体212が形成される。

20

## 【0064】

本発明の第3の代表的な実施形態に従って、マイクロエレクトロニクス構造の形成は、メモリセルを含むモノリシックな3次元メモリアレイの形成を含み、各メモリセルは、底部電極と頂部電極との間に配置されて誘電体側壁ライナにより覆われた炭素ベースの記憶素子を有するMIMデバイスを含む。炭素ベース記憶素子は、頂部電極が浸透しておらず、かつ好みしくは浸潤してもいい、無損傷あるいは低損傷のCNT材料を覆う任意の炭素ベース保護層を含むことができる。MIM内の頂部電極は、任意に、低エネルギー堆積手法を用いて堆積させられ得る。

30

## 【0065】

図3は、本発明の第3の代表的な実施形態に従って形成された代表的なメモリセルのメモリアレイ300の一部分を示す。第1のメモリレベルは基板より上に形成され、それより上に追加のメモリレベルが形成され得る。メモリアレイ形成に関する詳しいことは、本願明細書において参照により援用されている特許文献に記載され、そのようなアレイは、本発明の実施形態に従う方法および構造を使用することから利益を得ることができる。

## 【0066】

図3に示されているように、メモリアレイ300は、ワード線またはビット線としてそれぞれ役立ち得る第1の導体310および310'、支柱320および320'（各支柱320、320'はメモリセルを含む）と、ビット線またはワード線としてそれぞれ役立ち得る第2の導体330とを含むことができる。第1の導体310、310'は、第2の導体330に対して実質的に垂直に描かれている。メモリアレイ300は、1つ以上のメモリレベルを含むことができる。第1のメモリレベル340は第1の導体310、支柱320および第2の導体330の組み合わせを含むことができ、第2のメモリレベル350は第2の導体330、支柱320'および第1の導体310'を含むことができる。このようなメモリレベルの製造は、本願明細書において参照により援用されている特許文献に詳しく記載されている。

40

## 【0067】

本発明の実施形態は、モノリシックな3次元メモリアレイを形成するために有用である。モノリシックな3次元メモリアレイは、複数のメモリレベルがウェハなどの単一の基板より上に、介在する基板なしで、形成されるものである。1つのメモリレベルを形成する

50

層は、既存の1つまたは複数のレベルの層の上に直接堆積あるいは成長させられる。対照的に、積層されたメモリは、Leedyの米国特許第5,915,167号(特許文献9)のように、複数のメモリレベルを別々の基板上に形成してそれらのメモリレベルを互いの上に接着させることによって構築されている。それらの基板は接着の前に薄くされるかあるいはメモリレベルから除去されるけれども、メモリレベルは最初に別々の基板の上に形成されるので、そのようなメモリは真のモノリシックな3次元メモリアレイではない。

#### 【0068】

関連するメモリが、2004年9月29日に出願されたHernerらの「NONVOLATILE MEMORY CELL WITHOUT A DIELECTRIC ANTIFUSE HAVING HIGH- AND LOW-IMPEDANCE STATES」という米国特許出願第10/955,549号(特許文献10)に記載され、あらゆる目的のためにその全体が本願明細書において参照により援用されている。特許文献10は、図2のダイオード206のような垂直に向けられたpinダイオードを含むモノリシックな3次元メモリアレイを記述している。形成されたとき、特許文献10のpinダイオードのポリシリコンは高抵抗状態にある。プログラミング電圧を印加すると、ポリシリコンの性質は恒久的に変化して低抵抗となる。あらゆる目的のためにその全体が本願明細書において参照により援用されている、2005年6月8日に出願されたHernerらの「NONVOLATILE MEMORY CELL OPERATING BY INCREASING ORDER IN POLYCRYSTALLINE SEMICONDUCTOR MATERIAL」という米国特許出願第11/148,530号(特許文献11)により充分に記載されているように、変化はポリシリコンにおける結晶配列の程度の高まりによって引き起こされると考えられる。

10

20

30

40

#### 【0069】

他の1つの関連するメモリがHernerらの米国特許第7,285,464号(特許文献12)に記載され、その全体が本願明細書において参照により援用されている。特許文献12に記載されているように、pinダイオードの高さを小さくすると有利である。ダイオードが短ければ、必要なプログラミング電圧は低く、隣接するダイオード間のギャップのアスペクト比は小さくなる。非常にアスペクト比の高いギャップを隙間(欠損)がないように充填するのは困難である。逆バイアス時のダイオードの電流リークを減少させるために真性領域については少なくとも600オングストロームの厚さがほしい。強くn形ドープされた層より上に貧シリコン真性層があって、その両者がシリコン-ゲルマニウムの薄い真性キャッピング層で分離されているダイオードを形成すれば、ドーパントのプロファイルのより鋭い遷移が考慮され、従ってダイオードの全高が小さくされることになる。

#### 【0070】

特に、類似するメモリレベルの製造に関する詳細な情報が、前に援用されている特許文献10および特許文献12で提供されている。関連するメモリの製造に関する多くの情報が、本発明の譲受人により所有され、あらゆる目的のためにその全体が本願明細書において参照により援用されている、Hernerらの「A HIGH-DENSITY THREE-DIMENSIONAL MEMORY CELL」という米国特許第6,952,030号(特許文献13)で提供されている。本発明を不明瞭にしないために、この詳細は本願明細書において繰り返して述べられないけれども、これらあるいは他の援用されている特許または特許出願のどの教示も除外されるべく意図されてはいない。前の例が非限定的であることおよび本願明細書において提供されている詳細は、結果が本発明の範囲内に属するような改変、省略あるいは拡張がなされ得るということが理解されるはずである。

#### 【0071】

前の記述は本発明の代表的な実施形態を開示している。前に開示された装置および方法の、本発明の範囲に属する改変は、当業者にとってすべて明らかになるはずである。従って、本発明は代表的な実施形態と関連して開示されたけれども、添付の特許請求の範囲により定義される発明の趣旨および範囲に他の実施形態が属し得るということが理解されるべきである。

【図1】

FIG. 1

【図2A】

FIG. 2A

【図2B】

FIG. 2B

【図3】

FIG. 3

## 【国際調査報告】

## INTERNATIONAL SEARCH REPORT

International application No

PCT/US2009/040215

A. CLASSIFICATION OF SUBJECT MATTER

INV. H01L21/311 H01L21/3213

According to International Patent Classification (IPC) or to both national classification and IPC

## B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

H01L

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practical, search terms used)

EPO-Internal, WPI Data, INSPEC

## C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                                               | Relevant to claim No.   |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| X         | US 2007/004191 A1 (GU SHIQUN [US] ET AL GU SHIQUN [US] ET AL)<br>4 January 2007 (2007-01-04)<br>the whole document                                                                                                                                                               | 1,10-12,<br>14          |

| Y         |                                                                                                                                                                                                                                                                                  | 32-37                   |

| A         |                                                                                                                                                                                                                                                                                  | 16                      |

| X         | US 2005/214195 A1 (JUNG HEE T [KR] ET AL)<br>29 September 2005 (2005-09-29)<br>paragraphs [0053] - [0059]; figure 4                                                                                                                                                              | 1,10,11,<br>13,14<br>16 |

| A         |                                                                                                                                                                                                                                                                                  |                         |

| X         | WO 2008/021900 A (NANTERO INC [US]; BERTIN CLAUDE L [US]; RUECKES THOMAS [US]; HUANG X M) 21 February 2008 (2008-02-21)<br>paragraphs [0417] - [0454]; figure 35<br>paragraphs [0589] - [0659]; figures<br>40,47,48<br>paragraph [0762]<br>paragraphs [0821] - [0834]; figure 68 | 15,31,38                |

| Y         |                                                                                                                                                                                                                                                                                  | 32-37                   |

Further documents are listed in the continuation of Box C.

See patent family annex.

## \* Special categories of cited documents :

- "A" document defining the general state of the art which is not considered to be of particular relevance

- "E" earlier document but published on or after the international filing date

- "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- "O" document referring to an oral disclosure, use, exhibition or other means

- "P" document published prior to the international filing date but later than the priority date claimed

"T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

"X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

"Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.

"&" document member of the same patent family

| Date of the actual completion of the International search                                                                                                            | Date of mailing of the International search report |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 19 June 2009                                                                                                                                                         | 26/06/2009                                         |

| Name and mailing address of the ISA/<br>European Patent Office, P.B. 5818 Patentlaan 2<br>NL - 2280 HV Rijswijk<br>Tel. (+31-70) 340-2040,<br>Fax: (+31-70) 340-3016 | Authorized officer<br><br>Szarowski, Anne          |

## INTERNATIONAL SEARCH REPORT

Information on patent family members

International application No

PCT/US2009/040215

| Patent document cited in search report | Publication date | Patent family member(s)                                                                 |  | Publication date                                                   |

|----------------------------------------|------------------|-----------------------------------------------------------------------------------------|--|--------------------------------------------------------------------|

| US 2007004191                          | A1 04-01-2007    | NONE                                                                                    |  |                                                                    |

| US 2005214195                          | A1 29-09-2005    | CN 1673870 A<br>KR 20050095742 A                                                        |  | 28-09-2005<br>30-09-2005                                           |

| WO 2008021900                          | A 21-02-2008     | EP 2057633 A2<br>EP 2057683 A2<br>EP 2070088 A2<br>WO 2008021911 A2<br>WO 2008021912 A2 |  | 13-05-2009<br>13-05-2009<br>17-06-2009<br>21-02-2008<br>21-02-2008 |

## フロントページの続き

|              |           |                     |

|--------------|-----------|---------------------|

| (51) Int.Cl. | F I       | テーマコード(参考)          |

| H 01 L 51/30 | (2006.01) | H 01 L 29/28 250 E  |

| H 01 L 51/40 | (2006.01) | H 01 L 29/28 310 E  |

|              |           | H 01 L 21/302 104 H |

(81) 指定国 AP(BW,GH,GM,KE,LS,MW,MZ,NA,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HR,HU,IE,IS,IT,LT,LU,LV,MC,MK,MT,NL,NO,PL,PT,RO,SE,SI,S,K,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AO,AT,AU,AZ,BA,BB,BG,BH,BR,BW,BY,BZ,CA,CH,CN,CO,CR,CU,CZ,DE,DK,DM,DO,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,GT,HN,HR,HU,ID,IL,IN,IS,JP,K,E,KG,KM,KN,KP,KR,KZ,LA,LC,LK,LR,LS,LT,LU,LY,MA,MD,ME,MG,MK,MN,MW,MX,MY,MZ,NA,NG,NI,NO,NZ,OM,PG,PH,PL,PT,RO,RS,RU,SC,SD,SE,SG,SK,SL,SM,ST,SV,SY,TJ,TM,TN,TR,TT,TZ,UA,UG,US,UZ,VC,VN,ZA,ZM,ZW

(72) 発明者 フ , アンディー

アメリカ合衆国、94582、カリフォルニア州、サン ラモン、セアー レーン 5512

(72) 発明者 コネベッキー , マイケル

アメリカ合衆国、95126、カリフォルニア州、サンノゼ、サウスウェスト エクスプレスウェイ 2032、#73

(72) 発明者 マックスウェル , スティーブン

アメリカ合衆国、94087、カリフォルニア州、サニーベール、クエッタ ドライブ 720、アパートメント キュー

F ターム(参考) 5F004 AA16 BD01 CA06 DA04 DA11 DA23 DB00 DB26 DB27 EB02

5F083 FZ10 GA06 GA09 GA10 GA27 JA35 JA36 JA37 JA38 JA39

JA40 JA60 LA02 PR01 PR03 PR07 PR21 PR23 PR33