(12)发明专利

(10)授权公告号 CN 105874577 B

(45)授权公告日 2019.04.02

(21)申请号 201480071099.2

(72)发明人 斋藤顺 藤原广和 池田知治

(22)申请日 2014.08.04

渡边行彦 山本敏雅

(65)同一申请的已公布的文献号

申请公布号 CN 105874577 A

(74)专利代理机构 北京金信知识产权代理有限公司 11225

(43)申请公布日 2016.08.17

代理人 苏萌萌 许梅钰

(30)优先权数据

2013-269264 2013.12.26 JP

(51)Int.Cl.

H01L 21/336(2006.01)

H01L 21/265(2006.01)

H01L 29/06(2006.01)

H01L 29/12(2006.01)

H01L 29/78(2006.01)

(85)PCT国际申请进入国家阶段日

2016.06.24

(56)对比文件

JP 4735235 B2, 2011.07.27,

CN 101048874 A, 2007.10.03,

JP 4488935 B2, 2010.06.23,

(86)PCT国际申请的申请数据

PCT/JP2014/070520 2014.08.04

审查员 颜庙青

(87)PCT国际申请的公布数据

W02015/098167 JA 2015.07.02

权利要求书3页 说明书10页 附图12页

(73)专利权人 丰田自动车株式会社

地址 日本爱知县

(54)发明名称

绝缘栅型半导体装置的制造方法及绝缘栅型半导体装置

(57)摘要

使绝缘栅型半导体装置高耐压化。一种制造在表面电极和背面电极之间进行开关的绝缘栅型半导体装置的方法，具有：向栅极沟槽的底面注入第一第二导电型杂质并使注入的第一第二导电型杂质扩散的工序、以及向外周沟槽的底面注入第二第二导电型杂质并使注入的第二第二导电型杂质扩散的工序。

1. 一种制造绝缘栅型半导体装置的方法，所述绝缘栅型半导体装置具有：半导体基板；表面电极，其被形成在所述半导体基板的表面上；背面电极，其被形成在所述半导体基板的背面，并且，所述绝缘栅型半导体装置在所述表面电极和所述背面电极之间进行开关，其中，

所述绝缘栅型半导体装置具有：

第一导电型的第一区，其与所述表面电极连接；

第二导电型的第二区，其与所述第一区相接；

第一导电型的第三区，其通过所述第二区而与所述第一区分离；

多个栅极沟槽，其被形成在所述半导体基板的所述表面上，并贯穿所述第二区而到达所述第三区；

栅极绝缘膜以及栅电极，所述栅极绝缘膜以及所述栅电极被配置在所述栅极沟槽内；

第二导电型的第四区，其被形成在于所述栅极沟槽的底面上露出的范围内；

多个外周沟槽，所述多个外周沟槽在所述第二区的外侧的区域内被形成在所述半导体基板的所述表面上；

绝缘层，其被配置在所述外周沟槽内；

第二导电型的第五区，其被形成在于所述外周沟槽的底面上露出的范围内，

所述制造绝缘栅型半导体装置的方法具有：

形成所述栅极沟槽的工序；

形成所述外周沟槽的工序；

通过向所述栅极沟槽的底面注入第一第二导电型杂质，并使注入的所述第一第二导电型杂质扩散，从而形成所述第四区的工序；

通过向所述外周沟槽的底面注入第二第二导电型杂质，并使注入的所述第二第二导电型杂质扩散，从而形成所述第五区的工序，

形成所述第五区的工序中的所述第二第二导电型杂质的扩散系数大于形成所述第四区的工序中的所述第一第二导电型杂质的扩散系数。

2. 如权利要求1所述的制造绝缘栅型半导体装置的方法，其中，

所述第一第二导电型杂质为与所述第二第二导电型杂质不同的元素。

3. 如权利要求1所述的制造绝缘栅型半导体装置的方法，其中，

所述第一第二导电型杂质和所述第二第二导电型杂质为硼，

在形成所述第四区的所述工序中，向所述栅极沟槽的底面注入硼和碳。

4. 如权利要求1至3中的任意一项所述的制造绝缘栅型半导体装置的方法，其中，

在形成所述第五区的所述工序中，向所述外周沟槽的底面注入所述第二第二导电型杂质以及第三第二导电型杂质，所述第三第二导电型杂质与所述第二第二导电型杂质相比而在形成所述第五区的工序中的扩散系数较小。

5. 如权利要求1至3中的任意一项所述的制造绝缘栅型半导体装置的方法，其中，

在形成所述第五区的所述工序中，以如下浓度注入所述第二第二导电型杂质，所述浓度为，使构成所述外周沟槽的底面的半导体层的至少一部分发生非结晶化的浓度。

6. 如权利要求1至3中的任意一项所述的制造绝缘栅型半导体装置的方法，其中，

在形成所述第五区的所述工序中，以 $1 \times 10^{18} \text{ atoms/cm}^3$ 以上的浓度向所述外周沟槽的

底面注入所述第二第二导电型杂质。

7. 如权利要求1至3中的任意一项所述的制造绝缘栅型半导体装置的方法,其中,各个所述第五区之间的间隔小于各个所述第四区之间的间隔的二分之一。

8. 一种绝缘栅型半导体装置,具有:半导体基板;表面电极,其被形成在所述半导体基板的表面上;背面电极,其被形成在所述半导体基板的背面上,并且,所述绝缘栅型半导体装置在所述表面电极和所述背面电极之间进行开关,

其中,

所述绝缘栅型半导体装置具有:

第一导电型的第一区,其与所述表面电极连接;

第二导电型的第二区,其与所述第一区相接;

第一导电型的第三区,其通过所述第二区而与所述第一区分离;

多个栅极沟槽,所述多个栅极沟槽被形成在所述半导体基板的所述表面上,并贯穿所述第一区和所述第二区而到达所述第三区;

栅极绝缘膜以及栅电极,所述栅极绝缘膜以及所述栅电极被配置在所述栅极沟槽内;

第二导电型的第四区,其被形成在于所述栅极沟槽的底面上露出的范围内;

多个外周沟槽,所述多个外周沟槽在与所述第二区不相接的位置处被形成在所述半导体基板的所述表面上;

绝缘层,其被配置在所述外周沟槽内;

第二导电型的第五区,其被形成在于所述外周沟槽的底面上露出的范围内,

所述第五区的宽度宽于所述第四区的宽度,

被包含在所述第四区内的第二导电型杂质为,与被包含在所述第五区内的第二导电型杂质不同的元素。

9. 一种绝缘栅型半导体装置,具有:半导体基板;表面电极,其被形成在所述半导体基板的表面上;背面电极,其被形成在所述半导体基板的背面上,并且,所述绝缘栅型半导体装置在所述表面电极和所述背面电极之间进行开关,

其中,

所述绝缘栅型半导体装置具有:

第一导电型的第一区,其与所述表面电极连接;

第二导电型的第二区,其与所述第一区相接;

第一导电型的第三区,其通过所述第二区而与所述第一区分离;

多个栅极沟槽,所述多个栅极沟槽被形成在所述半导体基板的所述表面上,并贯穿所述第一区和所述第二区而到达所述第三区;

栅极绝缘膜以及栅电极,所述栅极绝缘膜以及所述栅电极被配置在所述栅极沟槽内;

第二导电型的第四区,其被形成在于所述栅极沟槽的底面上露出的范围内;

多个外周沟槽,所述多个外周沟槽在与所述第二区不相接的位置处被形成在所述半导体基板的所述表面上;

绝缘层,其被配置在所述外周沟槽内;

第二导电型的第五区,其被形成在于所述外周沟槽的底面上露出的范围内,

所述第五区的宽度宽于所述第四区的宽度,

被包含在所述第四区内的第二导电型杂质和被包含在所述第五区内的第二导电型杂质均为硼，

在所述第四区内还包含碳。

10. 一种绝缘栅型半导体装置，具有：半导体基板；表面电极，其被形成在所述半导体基板的表面上；背面电极，其被形成在所述半导体基板的背面上，并且，所述绝缘栅型半导体装置在所述表面电极和所述背面电极之间进行开关，

其中，

所述绝缘栅型半导体装置具有：

第一导电型的第一区，其与所述表面电极连接；

第二导电型的第二区，其与所述第一区相接；

第一导电型的第三区，其通过所述第二区而与所述第一区分离；

多个栅极沟槽，所述多个栅极沟槽被形成在所述半导体基板的所述表面上，并贯穿所述第一区和所述第二区而到达所述第三区；

栅极绝缘膜以及栅电极，所述栅极绝缘膜以及所述栅电极被配置在所述栅极沟槽内；

第二导电型的第四区，其被形成在于所述栅极沟槽的底面上露出的范围内；

多个外周沟槽，所述多个外周沟槽在与所述第二区不相接的位置处被形成在所述半导体基板的所述表面上；

绝缘层，其被配置在所述外周沟槽内；

第二导电型的第五区，其被形成在于所述外周沟槽的底面上露出的范围内，

所述第五区的宽度宽于所述第四区的宽度，

在所述第五区内包含有第一特定的第二导电型杂质和第二特定的第二导电型杂质，所述第二特定的第二导电型杂质与所述第一特定的第二导电型杂质相比而在所述半导体基板内的扩散系数较小。

11. 如权利要求8至10中的任意一项所述的绝缘栅型半导体装置，其中，

所述外周沟槽的底面的至少一部分为非结晶层。

12. 如权利要求8至10中的任意一项所述的绝缘栅型半导体装置，其中，

所述外周沟槽的底面的至少一部分以 $1 \times 10^{18} \text{ atoms/cm}^3$ 以上的浓度而含有第二导电型杂质。

13. 如权利要求8至10中的任意一项所述的绝缘栅型半导体装置，其中，

各个所述第五区之间的间隔小于各个所述第四区之间的间隔的二分之一。

## 绝缘栅型半导体装置的制造方法及绝缘栅型半导体装置

[0001] (关联申请的相互参照)

[0002] 本申请是2013年12月26日申请的日本专利申请特愿2013-269264的关联申请,且要求基于该日本专利申请的优先权,并援引该日本专利申请中记载的全部的内容作为构成本说明书的内容。

### 技术领域

[0003] 本说明书所公开的技术涉及一种绝缘栅型半导体装置。

### 背景技术

[0004] 在日本专利公开2008-135522号公报(以下,称为专利文献1)中,公开了一种绝缘栅型半导体装置,其具有形成有MOS结构的元件区以及该区周围的外周区。在元件区内形成有多个栅极沟槽,并在栅极沟槽内形成有栅极绝缘膜及栅电极。在露出于栅极沟槽的底面的范围内,形成有p型的底面围绕区(以下,称为元件部底面围绕区)。在外周区内,以包围元件区的方式而形成有多条沟槽,并在各沟槽内填充有绝缘层。在于外周区的各沟槽的底面上露出的范围内,形成有p型的底面围绕区(以下,称为外周部底面围绕区)。当MOSFET关闭时,在元件区内,耗尽层从元件部底面围绕区向漂移区内延展。由此,促进元件区内的漂移区的耗尽化。此外,在外周区内,耗尽层从外周部底面围绕区向漂移区内延展。由此,促进外周区内的漂移区的耗尽化。因此,使绝缘栅型半导体装置的耐压提高。

### 发明内容

[0005] 发明所要解决的课题

[0006] 在专利文献1的绝缘栅型半导体装置中,在元件区内,耗尽层大致同时从各元件部底面围绕区延展。因此,由于被夹在两个元件部底面围绕区之间的部分的漂移区从两侧起进行耗尽化,因而容易被耗尽化。与此相对,在外周区内,当从元件区延展的耗尽层到达外周区内的起始的外周部底面围绕区(与元件区最接近的外周部底面围绕区)时,耗尽层从起始的外周部底面围绕区朝向第二个外周部底面围绕区(从元件区向第二个外周部底面围绕区)延伸。在耗尽层到达第二个外周部底面围绕区时,耗尽层从第二个外周部底面围绕区朝向第三个外周部底面围绕区延伸。如此,耗尽层经由各外周部底面围绕区而依次延展。因此,在被夹于两个外周部底面围绕区之间的部分的漂移区内,仅从一侧进行耗尽化。因此,外周区难以被耗尽化。因此,希望实现外周区的进一步的高耐压化。

[0007] 用于解决课题的方法

[0008] 在本说明书所公开的制造方法中,制造一种绝缘栅型半导体装置,其具有:半导体基板;表面电极,其被形成在所述半导体基板的表面上;背面电极,其被形成在所述半导体基板的背面,并且,所述绝缘栅型半导体装置在所述表面电极和所述背面电极之间进行开关。所述绝缘栅型半导体装置具有:第一导电型的第一区,其与所述表面电极连接;第二导电型的第二区,其与所述第一区相接;第一导电型的第三区,其通过所述第二区而与所述第

一区分离；多个栅极沟槽，其被形成在所述半导体基板的所述表面上，并贯穿所述第二区而到达所述第三区；栅极绝缘膜以及栅电极，所述栅极绝缘膜以及所述栅电极被配置在所述栅极沟槽内；第二导电型的第四区，其被形成在露出于所述栅极沟槽的底面的范围内；多个外周沟槽，所述多个外周沟槽在所述第二区的外侧的区域内被形成在所述半导体基板的所述表面上；绝缘层，其被配置在所述外周沟槽内；第二导电型的第五区，其被形成在于所述外周沟槽的底面上露出的范围内。该制造方法包括：形成所述栅极沟槽的工序、形成所述外周沟槽的工序、通过向所述栅极沟槽的底面注入第一p型杂质并使注入的所述第一p型杂质扩散从而形成所述第四区的工序、通过向所述外周沟槽的底面注入第二p型杂质并使注入的所述第二p型杂质扩散从而形成所述第五区的工序。形成所述第五区的工序中的所述第二p型杂质的扩散系数大于形成所述第四区的工序中的所述第一p型杂质的扩散系数。

[0009] 另外，对于栅极沟槽和外周沟槽，可以先形成任何一个。此外，对于朝向栅极沟槽的底面的杂质的注入与朝向外周沟槽的底面的杂质的注入，可以先实施任何一个。此外，对于向栅极沟槽的底面注入的杂质的扩散与向外周沟槽的底面注入的杂质的扩散，既可以先实施任何一个，也可以同时实施二者。

[0010] 在该方法中，形成第五区的工序中的第二p型杂质的扩散系数较大。因此，通过使第二p型杂质向更广的范围扩散，从而能够形成宽度更宽的第五区。因此，能够缩小各个第五区之间的间隔，使这些间隔更容易被耗尽化。因此，根据该方法，能够使外周部的耐压提高。另一方面，形成第四区的工序中的第一p型杂质的扩散系数较小。因此，第一p型杂质的扩散范围缩小，由此而使第四区的宽度缩小。通过以这种方式缩小第四区的宽度，从而能够确保各个第四区之间的间隔（即，电流路径）较宽。由此，能够降低绝缘栅型半导体装置的导通电压。

[0011] 在上述的方法中，可以采用如下方式，即，所述第一p型杂质为与所述第二p型杂质不同的元素。

[0012] 此外，在上述的方法中，可以采用如下方式，即，所述第一p型杂质和所述第二p型杂质为硼，在形成所述第四区的所述工序中，向所述栅极沟槽的底面注入硼和碳。

[0013] 通过这些方法中的任意一种方法，均能够将形成第五区的工序中的第二p型杂质的扩散系数设为大于形成第四区的工序中的第一p型杂质的扩散系数。

[0014] 此外，在上述的任意一种方法中，也可以采用如下方式，即，在形成所述第五区的所述工序中，向所述外周沟槽的底面注入所述第二p型杂质以及第三p型杂质，所述第三p型杂质与所述第二p型杂质相比，在形成所述第四区的工序中的扩散系数较小。

[0015] 此外，在上述的任意一种方法中，也可以采用如下方式，即，在形成所述第五区的所述工序中，以使构成所述外周沟槽的底面的半导体层的至少一部分发生非结晶化的浓度来注入所述第二p型杂质。

[0016] 此外，在上述的任意一种方法中，也可以采用如下方式，即，在形成所述第五区的所述工序中，以 $1 \times 10^{18} \text{ atoms/cm}^3$ 以上的浓度向所述外周沟槽的底面注入所述第二p型杂质。

[0017] 通过这些方法中的任意一种方法，能够将第五区中的外周沟槽的底面周边的区的p型杂质浓度提高。由此，能够对在外周沟槽的底面附近产生较高的电场的情况进行抑制。

[0018] 在上述的任意一种方法中，也可以采用如下方式，即，各个所述第五区之间的间隔

在各个所述各第四区之间的间隔的二分之一以下。

[0019] 根据这种结构,会先于外周部而在元件部处产生雪崩击穿。由于元件部的雪崩耐量较高,因此通过在元件部中先产生雪崩击穿,从而提高绝缘栅型半导体装置的耐压。

[0020] 此外,本说明书提出了一种新的绝缘栅型半导体装置。该绝缘栅型半导体装置具有:半导体基板;表面电极,其被形成在所述半导体基板的表面上;背面电极,其被形成在所述半导体基板的背面上,并且,所述绝缘栅型半导体装置在所述表面电极和所述背面电极之间进行开关。该绝缘栅型半导体装置还具有:第一导电型的第一区,其与所述表面电极连接;第二导电型的第二区,其与所述第一区相接;第一导电型的第三区,其通过所述第二区而从所述第一区分离;多个栅极沟槽,所述多个栅极沟槽被形成在所述半导体基板的所述表面上,并贯穿所述第一区和所述第二区,到达所述第三区;栅极绝缘膜以及栅电极,所述栅极绝缘膜以及所述栅电极被配置在所述栅极沟槽内;第二导电型的第四区,其被形成在于所述栅极沟槽的底面上露出的范围内;多个外周沟槽,所述多个外周沟槽在与所述第二区不相接的位置处被形成在所述半导体基板的所述表面上;绝缘层,其被配置在所述外周沟槽内;第二导电型的第五区,其被形成在露出于所述外周沟槽的底面的范围内。所述第五区的宽度宽于所述第四区的宽度。可以采用如下方式,即,被包含在所述第四区内的第二导电型杂质为,与被包含在所述第五区内的第二导电型杂质不同的元素。可以采用如下方式,即,被包含在所述第四区内的第二导电型杂质和被包含在所述第五区内的第二导电型杂质均为硼,在所述第四区内还包含碳。可以采用如下方式,即,在所述第五区内包含有第一特定的第二导电型杂质和第二特定的第二导电型杂质,所述第二特定的第二导电型杂质与所述第一特定的第二导电型杂质相比而在所述半导体基板内的扩散系数较小。可以采用如下方式,即,所述外周沟槽的底面的至少一部分为非结晶层。可以采用如下方式,即,所述外周沟槽的底面至少一部分以在 $1 \times 10^{18} \text{ atoms/cm}^3$ 以上的浓度而含有第二导电型杂质。可以采用如下方式,即,各个所述第五区之间的间隔小于各个所述第四区之间的间隔的二分之一。根据这种结构,能够使绝缘栅型半导体装置的耐压提高。

## 附图说明

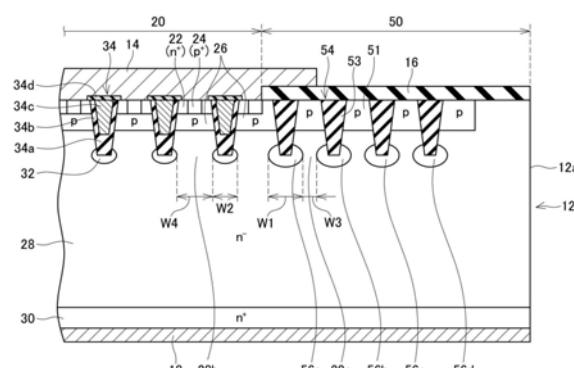

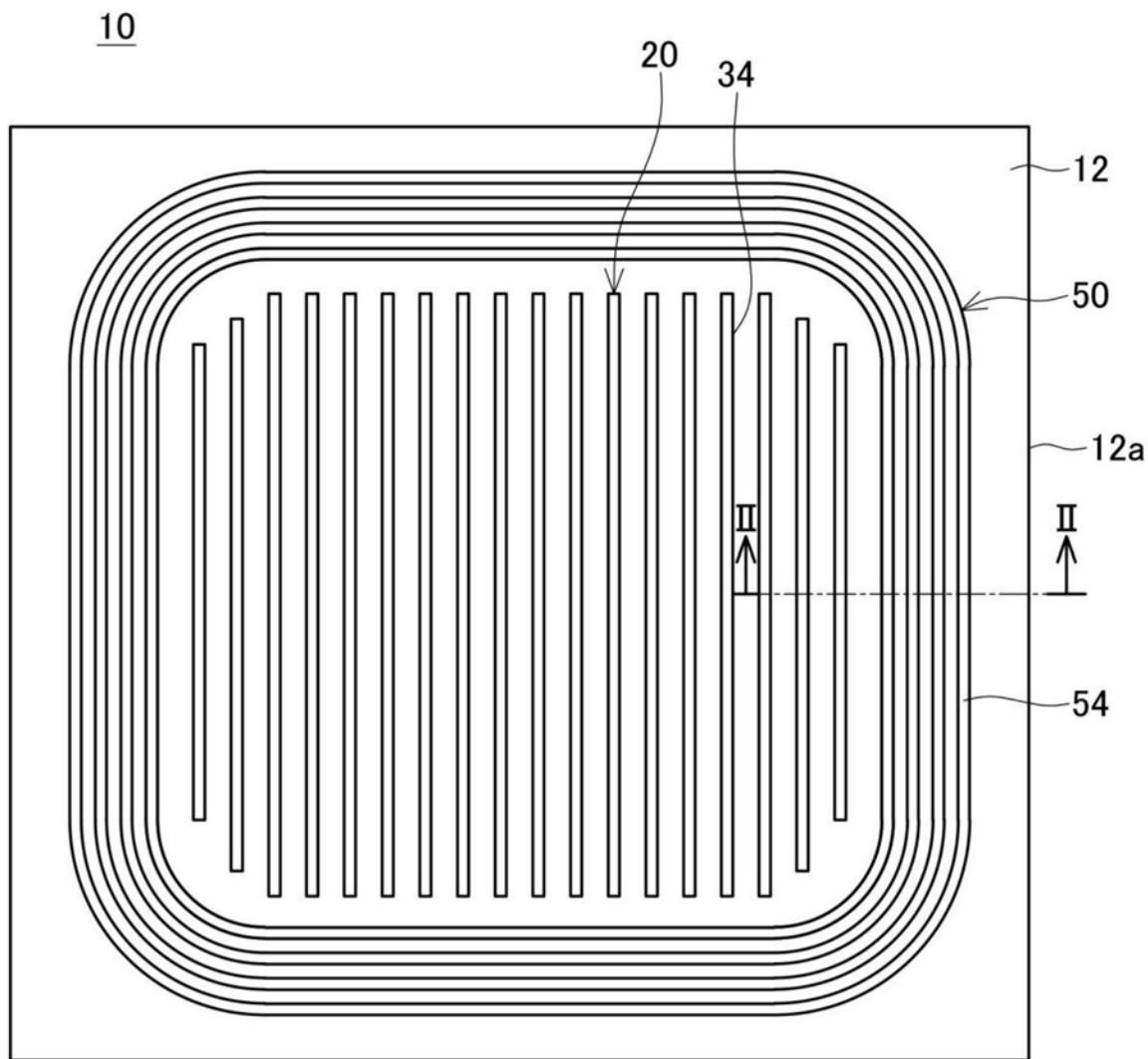

[0021] 图1为半导体装置10的俯视图。

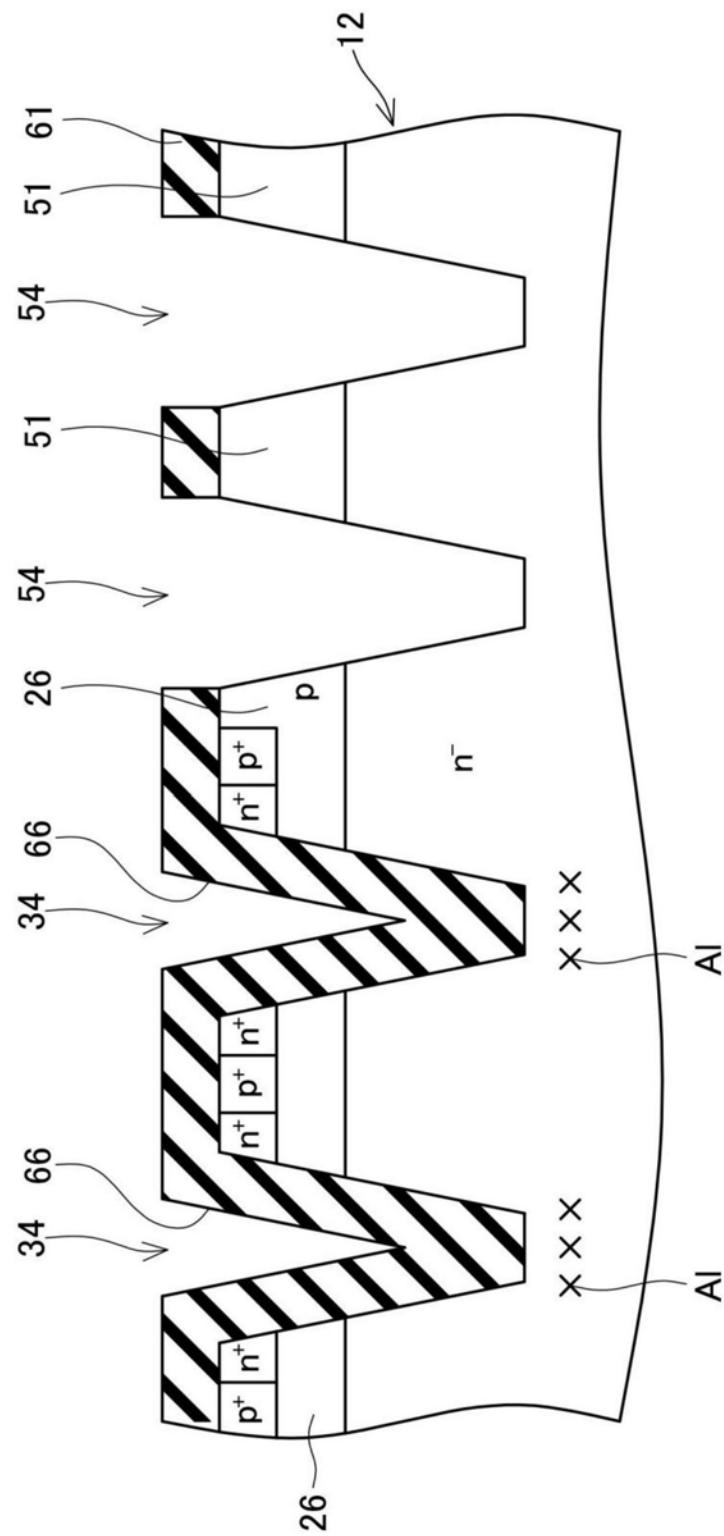

[0022] 图2为图1的Ⅱ—Ⅱ线的半导体装置10的纵剖视图。

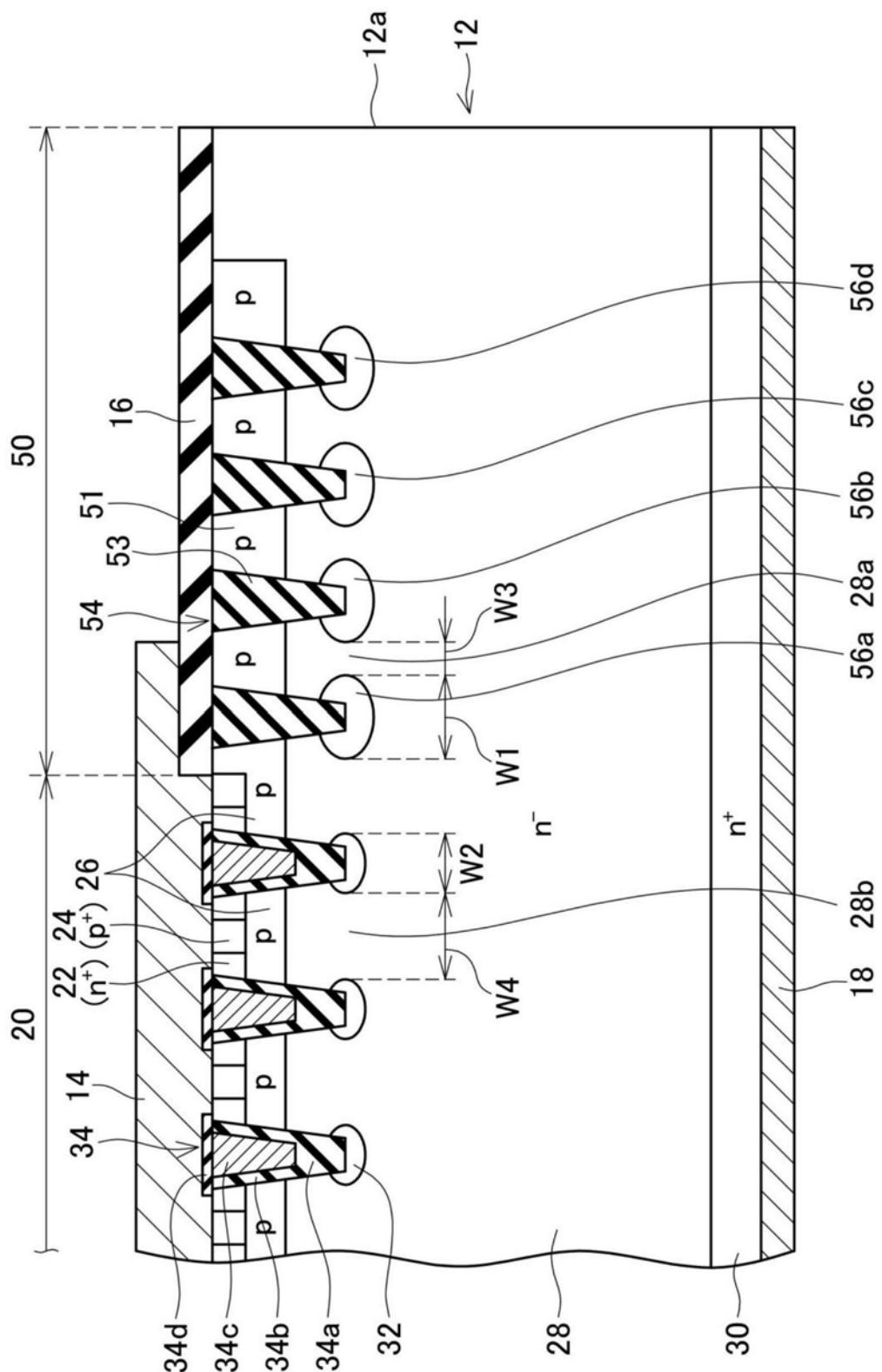

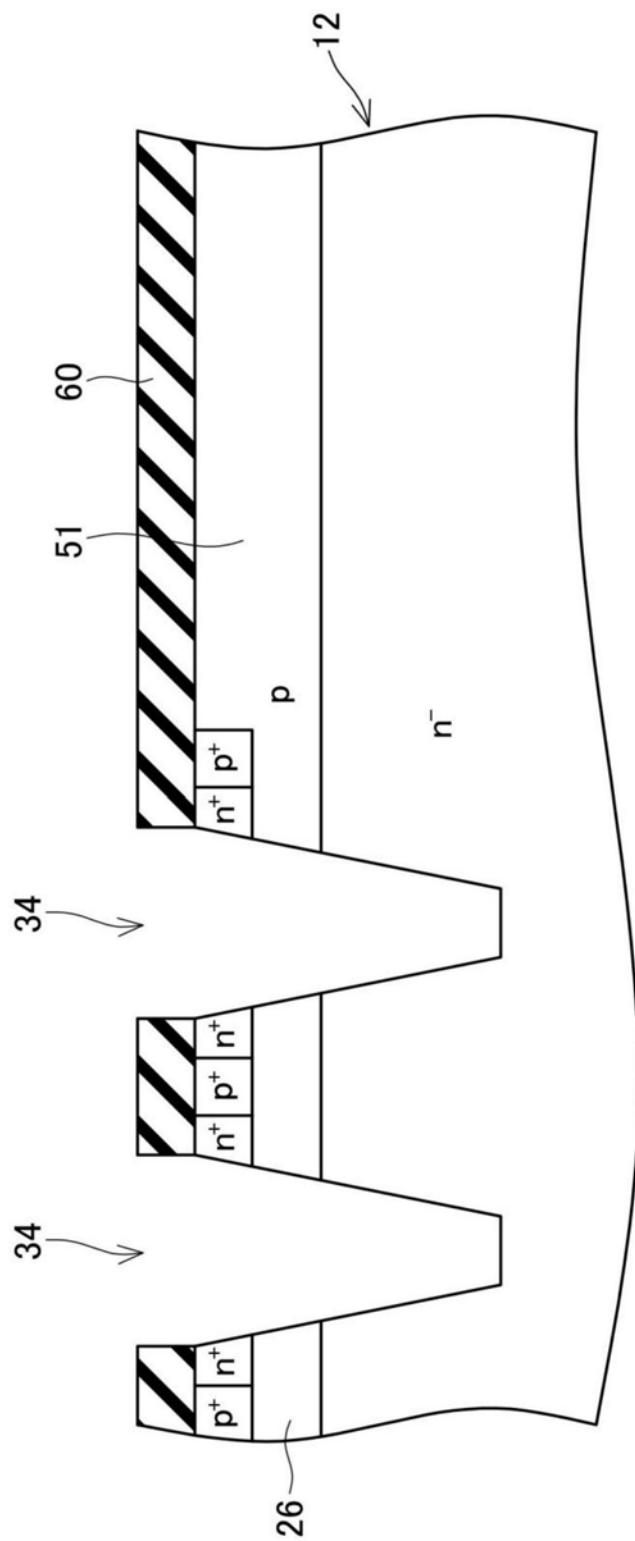

[0023] 图3为半导体装置10的制造工序的说明图(形成有p型浮动区32和底面区56的区域的放大剖视图)。

[0024] 图4为半导体装置10的制造工序的说明图(形成有p型浮动区32和底面区56的区域的放大剖视图)。

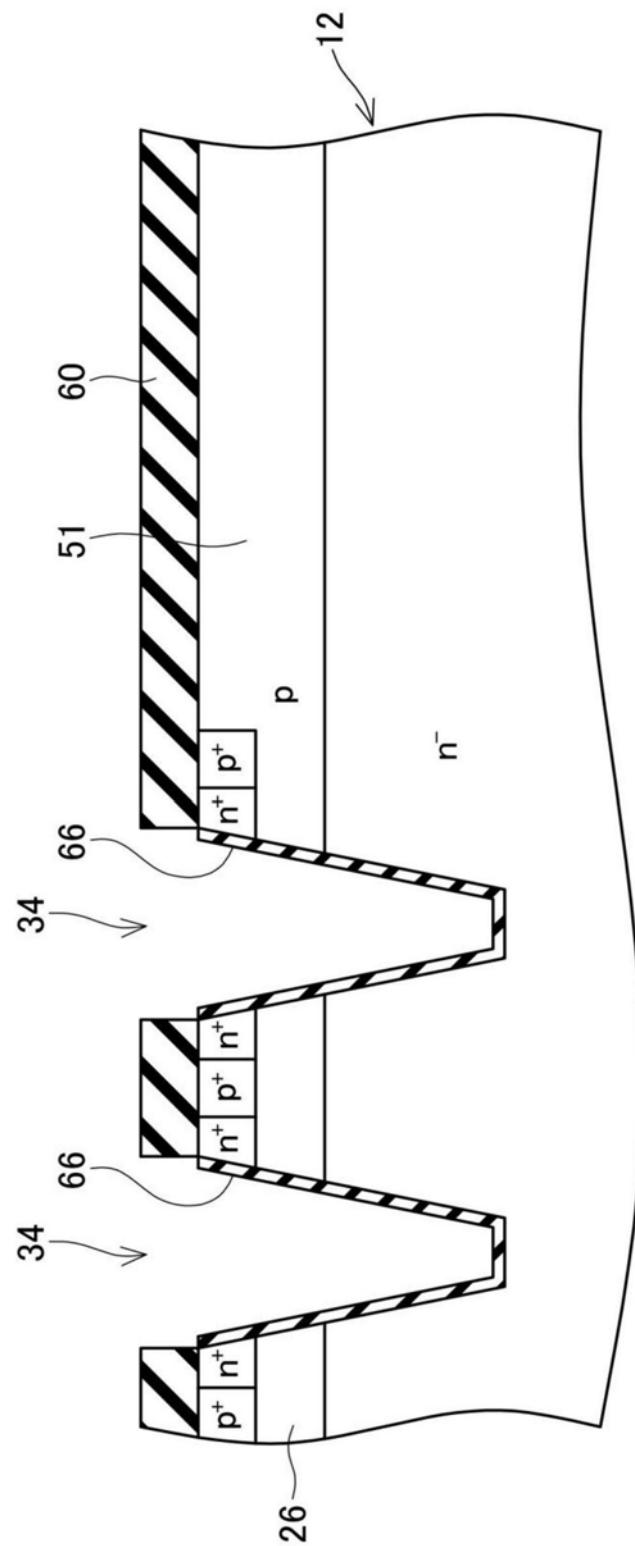

[0025] 图5为半导体装置10的制造工序的说明图(形成有p型浮动区32和底面区56的区域的放大剖视图)。

[0026] 图6为半导体装置10的制造工序的说明图(形成有p型浮动区32和底面区56的区域的放大剖视图)。

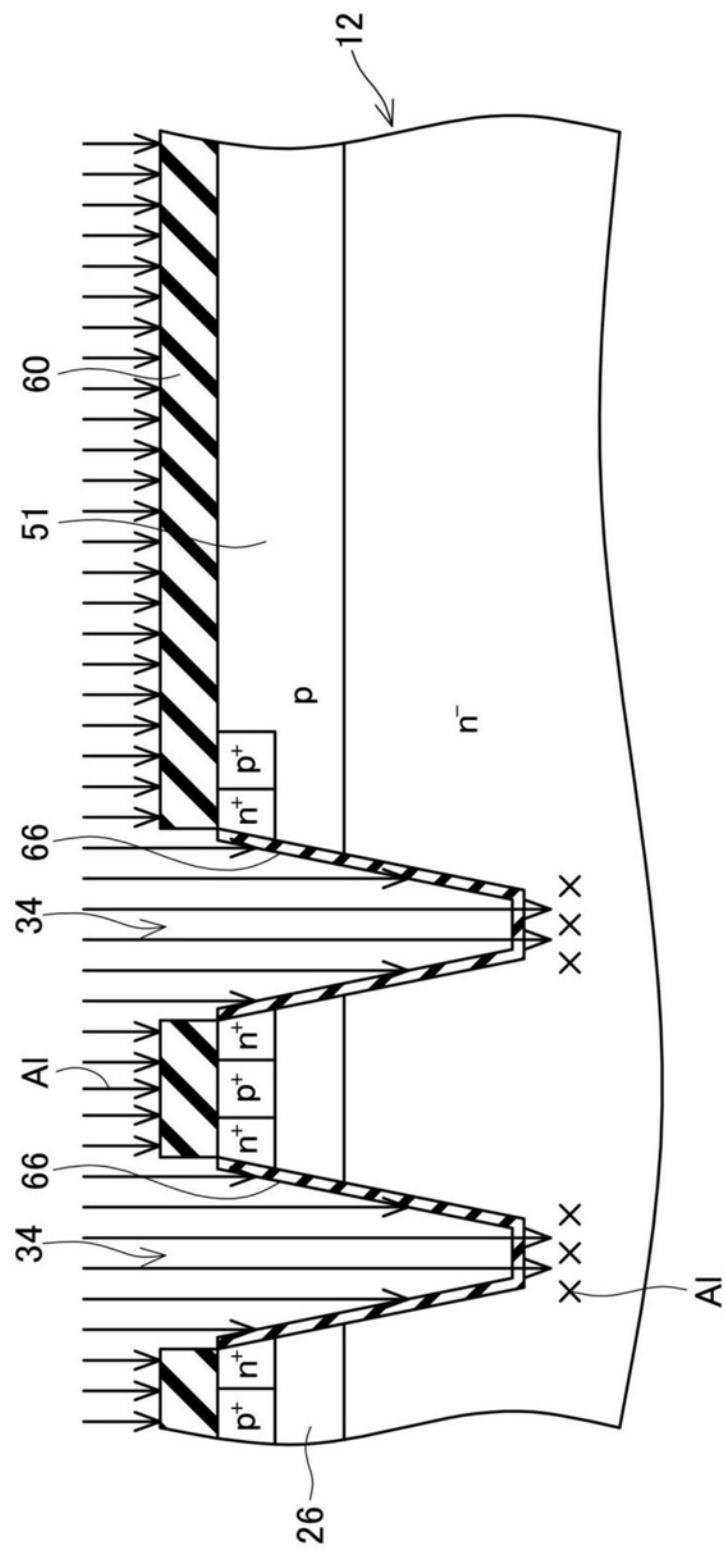

[0027] 图7为半导体装置10的制造工序的说明图(形成有p型浮动区32和底面区56的区域的放大剖视图)。

[0028] 图8为半导体装置10的制造工序的说明图(形成有p型浮动区32和底面区56的区域

的放大剖视图)。

[0029] 图9为半导体装置10的制造工序的说明图(形成有p型浮动区32和底面区56的区域的放大剖视图)。

[0030] 图10为半导体装置10的制造工序的说明图(形成有p型浮动区32和底面区56的区域的放大剖视图)。

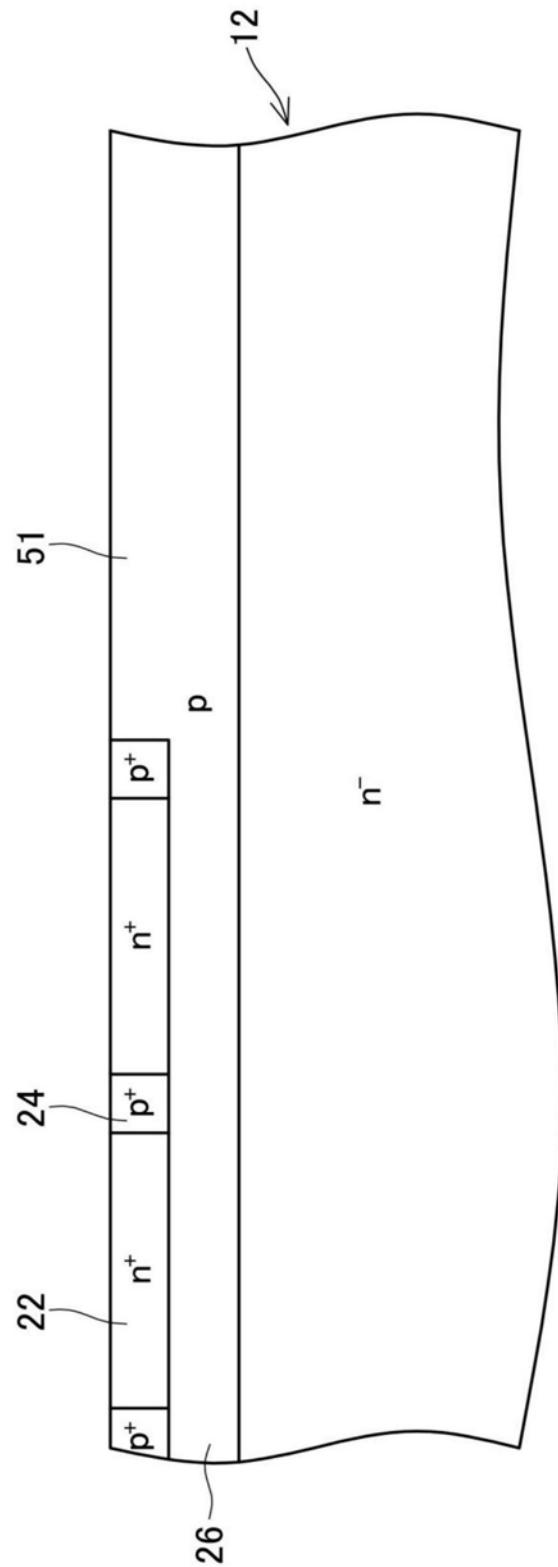

[0031] 图11为表示以高浓度注入了B的情况下的B的扩散情况的曲线图。

[0032] 图12为半导体装置10的制造工序的说明图(形成有p型浮动区32和底面区56的区域的放大剖视图)。

## 具体实施方式

[0033] 实施例

[0034] 图1所示的半导体装置10具有由SiC组成的半导体基板12。半导体基板12具有单元区20和外周区50。单元区20内形成有MOSFET(Metal Oxide Semiconductor Field-Effect Transistor:金属氧化物场效应晶体管)。外周区50为单元区20与导体基板12的端面12a之间的区。

[0035] 如图2所示,在半导体基板12的表面上形成有表面电极14和绝缘层16。绝缘层16对外周区50内的半导体基板12的表面进行覆盖。表面电极14在单元区20内与半导体基板12相接。换言之,表面电极14与半导体基板12相接的接触区的下侧的区为单元区20,与接触区相比靠外周侧(端面12a侧)的区为外周区50。在半导体基板12的背面形成有背面电极18。背面电极18覆盖半导体基板12的大致全部背面。

[0036] 在单元区20内形成有源极区22、体接触区24、体区26、漂移区28、漏极区30、p型浮动区32以及栅极沟槽34。

[0037] 源极区22为以高浓度包含n型杂质的n型区。源极区22被形成在于半导体基板12的上表面上露出的范围内。源极区22相对于表面电极14而欧姆连接。

[0038] 体接触区24为以高浓度包含p型杂质的p型区。体接触区24以于半导体基板12的上表面上露出的方式而被形成在未形成有源极区22的位置。体接触区24相对于表面电极14而欧姆连接。

[0039] 体区26为以低浓度包含p型杂质的p型区。体区26的p型杂质浓度低于体接触区24的p型杂质浓度。体区26被形成在源极区22以及体接触区24的下侧,并与这两个区相接。

[0040] 漂移区28为以低浓度包含n型杂质的n型区。漂移区28的n型杂质浓度低于源极区22的n型杂质浓度。漂移区28被形成在体区26的下侧。漂移区28与体区26相接,并通过体区26而与源极区22分离。

[0041] 漏极区30为以高浓度包含n型杂质的n型区。漏极区30的n型杂质浓度高于漂移区28的n型杂质浓度。漏极区30被形成在漂移区28的下侧。漏极区30与漂移区28相接,并通过漂移区28而与体区26分离。漏极区30被形成在于半导体基板12的下表面上露出的范围内。漏极区30相对于背面电极18而欧姆连接。

[0042] 如图1、2所示,在单元区20内的半导体基板12的上表面上,形成有多个栅极沟槽34。各个栅极沟槽34在半导体基板12的表面以相互平行且呈直线状的方式延伸。各个栅极沟槽34以贯穿源极区22和体区26而到达漂移区28的方式被形成。在各个栅极沟槽34内形成

有底部绝缘层34a、栅极绝缘膜34b以及栅电极34c。底部绝缘层34a为被形成在栅极沟槽34的底部的较厚的绝缘层。底部绝缘层34a的上侧的栅极沟槽34的侧面被栅极绝缘膜34b覆盖。底部绝缘层34a的上侧的栅极沟槽34内形成有栅电极34c。栅电极34c隔着栅极绝缘膜34b而与源极区22、体区26以及漂移区28对置。栅电极34c通过栅极绝缘膜34b以及底部绝缘层34a而与半导体基板12绝缘。栅电极34c的上表面被绝缘层34d覆盖。通过绝缘层34d, 从而使栅电极34c与表面电极14绝缘。

[0043] p型浮动区32被形成在半导体基板12内且与各栅极沟槽34的底面相接的范围内。各个p型浮动区32的周围被漂移区28包围。各个p型浮动区32通过漂移区28而相互分离。

[0044] 在外周区50内的露出于半导体基板12的表面的范围内, 形成有p型的表面区51。表面区51扩大至与体区26大致相同的深度。上述的漂移区28及漏极区30扩大到外周区50。漂移区28和漏极区30扩大到半导体基板12的端面12a。漂移区28从下侧与表面区51相接。

[0045] 在外周区50内的半导体基板12的上表面上, 形成有多个外周沟槽54。各个外周沟槽54以贯穿表面区51而达到漂移区28的方式被形成。在各个外周沟槽54内形成有绝缘层53。如图1所示, 在从上侧观察半导体基板12时, 各个外周沟槽54被形成为绕单元区20的周围一周的环状。各个外周沟槽54以相互间隔距离的方式被形成。表面区51通过外周沟槽54而与体区26(即, 与表面电极14导通的p型区)分离。此外, 各个表面区51通过各个外周沟槽54而相互分离。

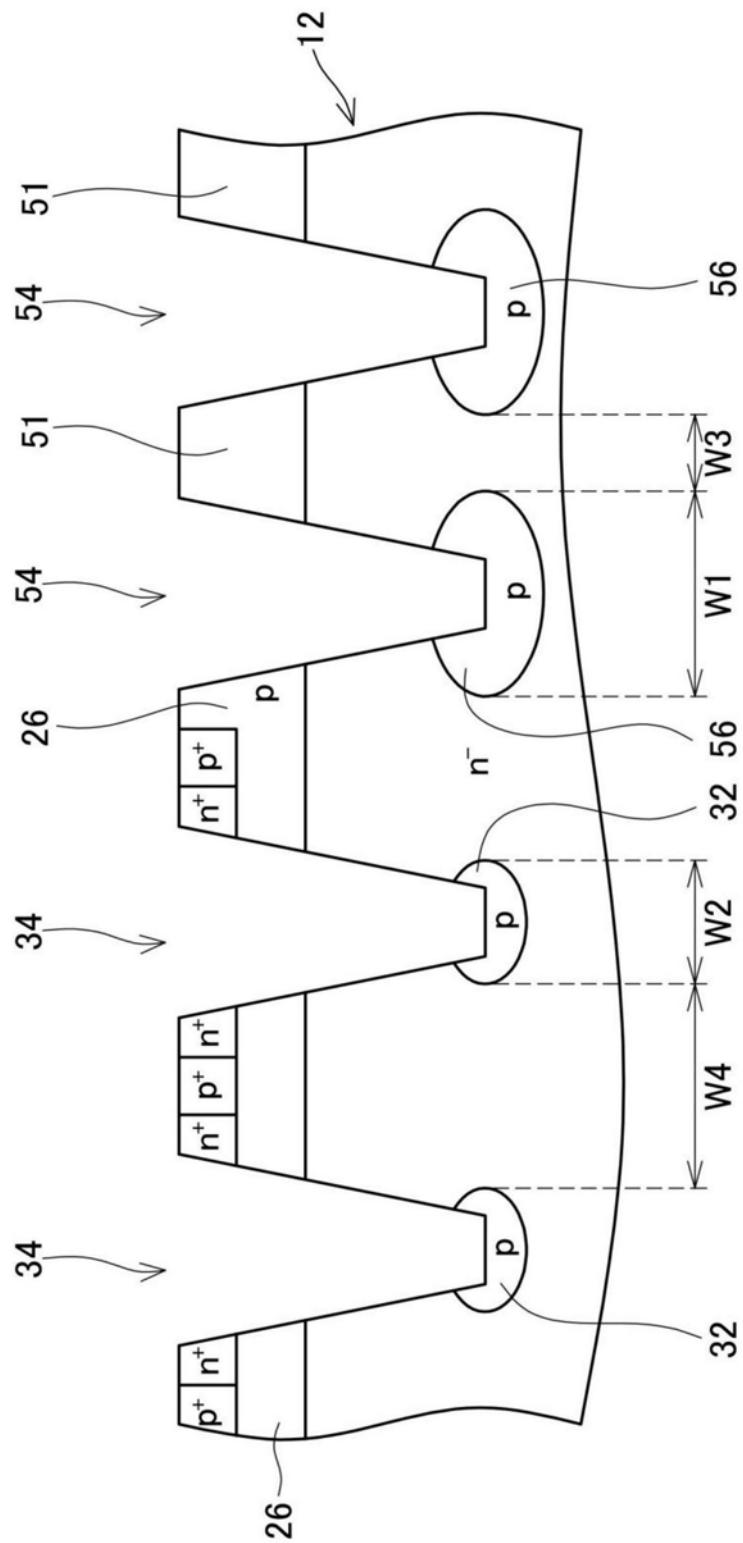

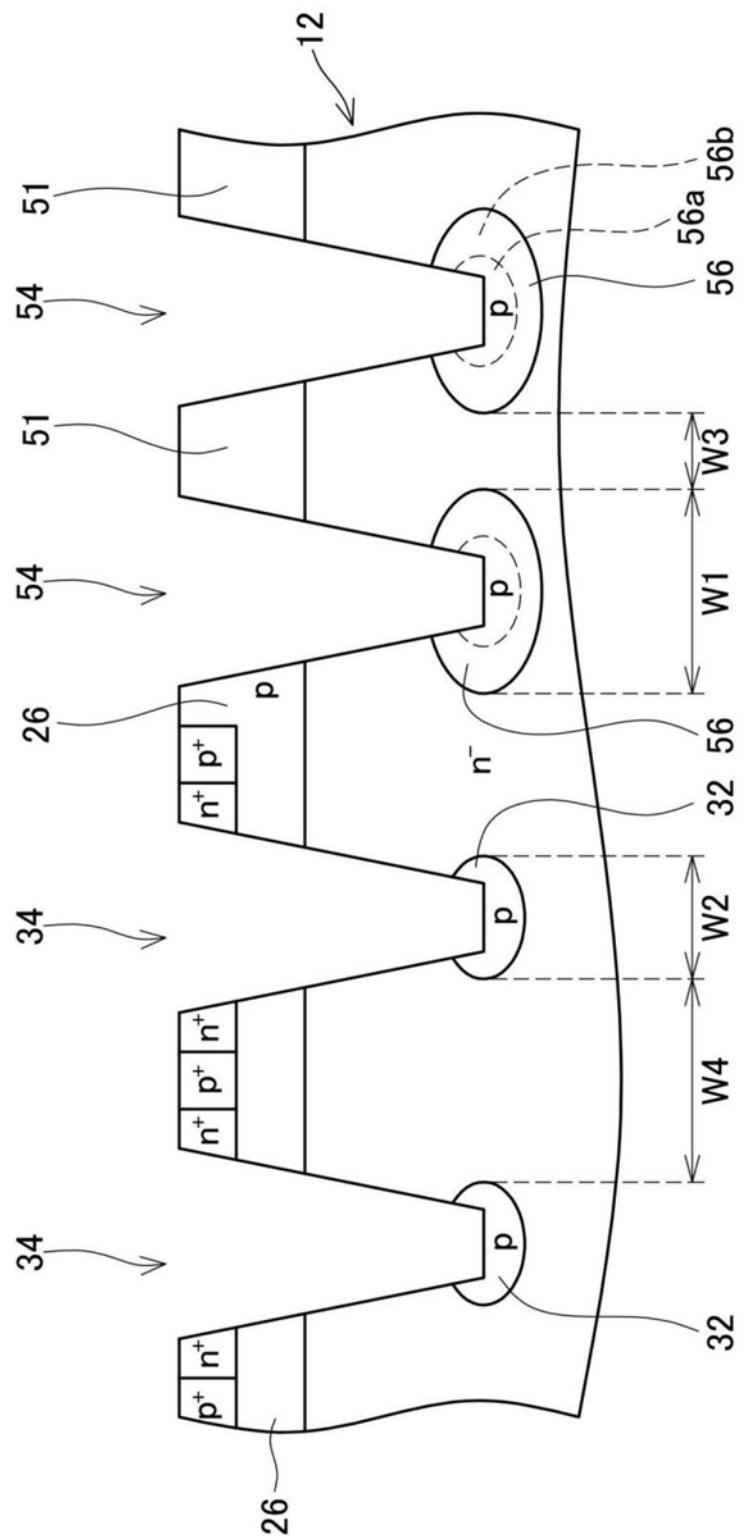

[0046] 在半导体基板12内且与各外周沟槽54的底面相接的范围内, 形成有p型的底面区56。底面区56以覆盖外周沟槽54的底面整体的方式沿着外周沟槽54而被形成。各个底面区56的周围被漂移区28包围。各个底面区56通过漂移区28而相互分离。如附图所示, 各个底面区56的宽度W1与各个p型浮动区32的宽度W2相比而较宽。在此, 底面区56的宽度W1是指横穿外周沟槽54的方向(即, 外周沟槽54的宽度方向)上的底面区56的尺寸。此外, p型浮动区32的宽度W2是指横穿栅极沟槽34的方向(即, 栅极沟槽34的宽度方向)上的p型浮动区32的尺寸。

[0047] 接下来, 对半导体装置10的动作进行说明。在使半导体装置10进行动作时, 向背面电极18与表面电极14之间施加使背面电极18成为正极的电压。而且, 通过对栅电极34c施加栅极导通电压, 从而使单元区20内的MOSFET导通。即, 在与栅电极34c对置的位置的体区26内形成沟道, 电子从表面电极14经由源极区22、沟道、漂移区28、漏极区30而向背面电极18流动。此时, 电子以穿过位于两个p型浮动区32之间的漂移区28b的方式流动。在半导体装置10中, 各个p型浮动区32的宽度W2变窄, 由此使漂移区28b的宽度W4变宽。如此, 由于确保流通有电流的漂移区28b的宽度较宽, 因此MOSFET的导通电压较低。

[0048] 在停止朝向栅电极34c施加栅极导通电压时, 沟道消失, MOSFET截断。当MOSFET截断时, 耗尽层从体区26与漂移区28的边界部的pn结处向漂移区28内延展。在耗尽层到达单元区20内的p型浮动区32时, 耗尽层也从p型浮动区32向漂移区28内延展。因此, 耗尽层从两侧的p型浮动区32向位于两个p型浮动区32之间的漂移区28b延展。如此, 通过耗尽层在单元区20内扩展, 从而实现单元区20内的较高的耐压。

[0049] 另外, 如上文所述, 位于两个p型浮动区32之间的漂移区28b的宽度W4较宽。然而, 如上文所述, 漂移区28b从两侧被耗尽化。因此, 即使漂移区28b的宽度W4较宽, 漂移区28b也比较容易被耗尽化。

[0050] 此外,上述的从pn结开始延伸的耗尽层到达位于最靠单元区20侧的外周沟槽54的下侧的底面区56a内。如此一来,耗尽层从底面区56a向外周侧的底面区56b延伸。在耗尽层到达底面区56b时,耗尽层从该底面区56b向外周侧的底面区556c延伸。如此,在外周区50内,耗尽层经由各个底面区56而顺序地向外周侧扩展,从而使耗尽层延伸到最靠外周侧的底面区56d内。通过如此使耗尽层扩展到外周区50内,从而实现外周区50内的较高的耐压。另外,由于在外周区50内耗尽层以这种方式扩展,因此位于两个底面区56之间的漂移区28a仅从单侧(单元区20侧)被耗尽化。然而,漂移区28a的宽度W3变窄,由此,漂移区28a切实地被耗尽化。

[0051] 在本实施例中,漂移区28a的宽度W3小于漂移区28b的宽度W4的二分之一。因此,漂移区28a先于漂移区28b被耗尽化。根据这种结构,能够在向半导体装置10施加过大的电压时,于单元区20内产生雪崩击穿。即,外周区50由于面积较小而电流路径较小,从而容易在产生雪崩击穿时使雪崩电流的密度升高。因此,外周区50的雪崩耐量较低。与此相对,单元区20由于面积较广而使电流路径较宽,从而即使产生雪崩击穿,雪崩电流的密度也会降低。因此,与外周区50相比,单元区20的雪崩耐量较高。因此,通过如上文那样设置为在单元区20内产生雪崩击穿,从而能够使作为半导体装置10整体的耐雪崩量提高。

[0052] 接下来,对半导体装置10的制造方法进行说明。另外,由于本说明书所公开的制造方法在形成p型浮动区32以及底面区56的工序中具有特征,因此,在下文中主要对形成这两区的工序进行说明。本说明书提出实施例1~4的制造方法。

### [0053] 实施例1

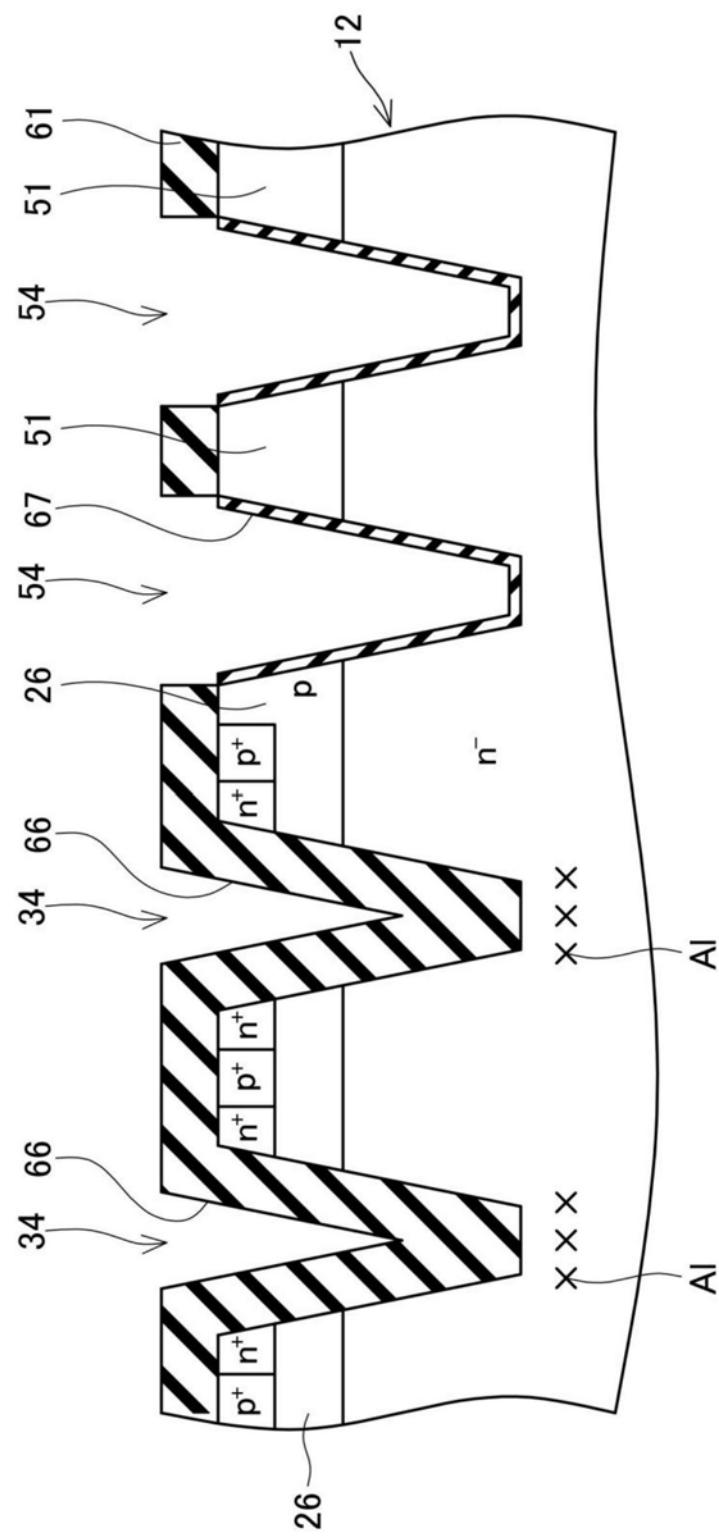

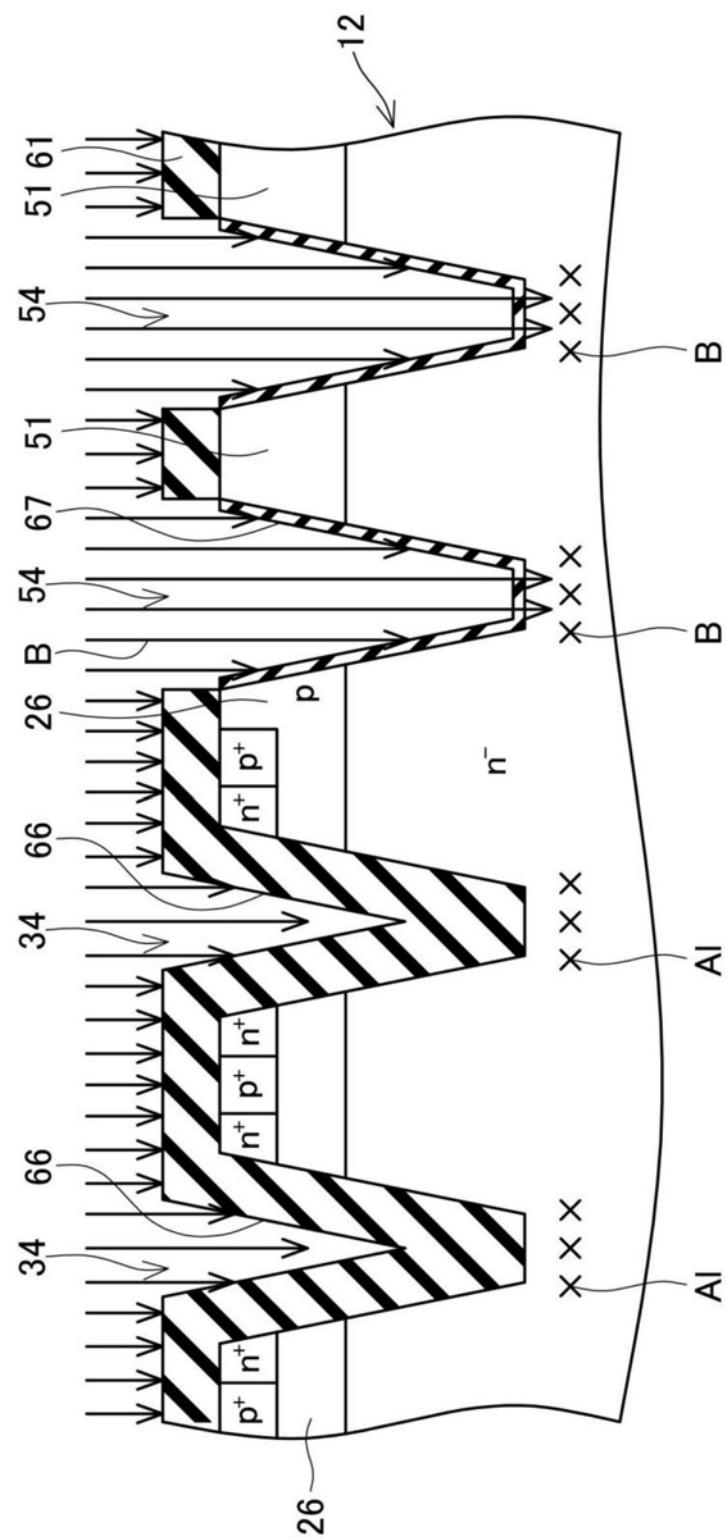

[0054] 在实施例1的制造方法中,首先,如图3所示,通过外延生长、离子注入等,在半导体基板12上形成源极区22、体接触区24、体区26以及表面区51。接下来,如图4所示,在半导体基板12的表面上形成具有开口的掩膜60(例如氧化膜),通过利用各向异性蚀刻对开口内的半导体基板12进行蚀刻,从而形成栅极沟槽34。此时,栅极沟槽34的侧面成为呈锥状倾斜的形状。接下来,如图5所示,通过CVD(Chemical Vapor Deposition:化学气相沉积)法或热氧化法而在栅极沟槽34的内表面形成保护膜66(氧化膜)。

### [0055] (第一注入工序)

[0056] 接下来,如图6所示,朝向半导体基板12照射Al(铝)。被照射出的Al贯穿栅极沟槽34的底面的保护膜66,而被注入到栅极沟槽34的底面。此外,通过保护膜66来防止Al被注入到栅极沟槽34的侧面上。因此,Al仅被注入到栅极沟槽34的底面上。之后,去除掩膜60和保护膜66。

[0057] 接下来,如图7所示,在半导体基板12的表面上形成具有开口的掩膜61(例如氧化膜),并通过利用各向异性蚀刻对开口内的半导体基板12进行蚀刻,从而形成外周沟槽54。此时,外周沟槽54的侧面成为呈锥状倾斜的形状。接下来,如图8所示,通过CVD法或热氧化法而在外周沟槽54的内表面形成保护膜67(氧化膜)。

### [0058] (第二注入工序)

[0059] 接下来,如图9所示,向半导体基板12照射B(硼)。被照射出的B贯穿外周沟槽54的底面的保护膜67,而被注入到外周沟槽54的底面上。此外,通过保护膜67来防止B被注入到外周沟槽54的侧面上。因此,B仅被注入到外周沟槽54的底面上。之后,去除掩膜61和保护膜67。

[0060] (活化退火工序)

[0061] 接下来,利用1600℃以上的温度对半导体基板12进行退火。由此,使被注入到半导体基板12内的A1和B活化。由此,如图10所示,在栅极沟槽34的底面的周围形成p型浮动区32,并且在外周沟槽54的底面的周围形成底面区56。在此,在半导体基板12(即,SiC)中,B的扩散系数远大于A1的扩散系数。因此,在活性退火工序中,B的扩散距离大于A1的扩散距离。因此,如图10所示,底面区56(即,B的扩散范围)的尺寸大于p型浮动区32(即,A1的扩散范围)的尺寸。因此,底面区56的宽度W1与p型浮动区32的宽度W2相比而较宽,两个底面区56之间的间隔W3与两个p型浮动区32之间的间隔W4相比而较窄。之后,通过形成需要的结构(图1所示的沟槽栅极构造、绝缘层16、表面电极14、漏极区30以及背面电极18),从而完成图1所示的半导体装置10。

[0062] 如以上所说明的那样,在实施例1的制造方法中,一方面以向外周沟槽54的底面注入扩散系数较大的B的方式形成宽度W1较宽的底面区56,另一方面以向栅极沟槽34的底面注入扩散系数较小的A1的方式形成宽度W2较窄的p型浮动区32。如此,通过在底面区56和p型浮动区32分开使用注入的p型杂质,从而能够将底面区56的宽度宽于p型浮动区32的宽度。由此,能够在外周区50内通过缩小底面区56之间的宽度W3而使耐压提高,并且通过确保单元区20中的电流路径的宽度W4较宽而使MOSFET的导通电压提高。

[0063] 另外,即使缩小外周沟槽54之间的间隔,也可能会缩小底面区56之间的间隔W3。然而,由于外周沟槽54的加工精度所带来的限制,会在缩小外周沟槽54之间的间隔时存在极限。与此相对,根据上述的实施例1的方法,由于利用B的扩散来缩小底面区56之间的间隔W3,因此能够与外周沟槽54的加工精度所带来的限制无关地缩小间隔W3。另外,通过在限制的范围内尽量缩小外周沟槽54之间的间隔,且通过B的注入而形成底面区56,从而有可能会进一步缩小宽度W3。

[0064] 实施例2

[0065] 在实施例2的制造方法中,上述的第一注入工序与实施例1的制造方法不同。其他的工序与实施例1的制造方法相同。

[0066] 在实施例2的第一注入工序中,向栅极沟槽34的底面注入C(碳),接着,向栅极沟槽34的底面注入B。另外,在第一注入工序中,优选为,以与B相比而较高的浓度注入C。此外,在第一注入工序中,也可以在注入C之前注入B。在第二注入工序中,与实施例1的制造方法同样地向外周沟槽54的底面注入B。C未被注入到外周沟槽54的底面上。在活化退火工序中,以与实施例1的制造方法同样的方式对半导体基板12进行退火,并使被注入到半导体基板12内的B扩散。在此,被注入到外周沟槽54的底面上的B以与实施例1同样的方式较宽地扩散。与此相对,被注入到栅极沟槽34的底面上的B并未以这种程度而较宽地扩散。这是由于在注入有C的SiC区内,B的扩散系数较低的原因。因此,如图10所示,在外周沟槽54的底面的周围形成有宽度W1较宽的底面区56,在栅极沟槽34的底面的周围形成有宽度W2较窄的p型浮动区32。

[0067] 另外,在实施例2的第一注入工序中,优选为,将注入C的范围设为与注入B的范围相比而较宽。通过以这种方式注入C,从而能够更有效地抑制活化退火工序中的B的扩散。

[0068] 此外,在实施例2的第二注入工序中,也可以向外周沟槽54的底面注入B和C。在这种结构中,只要被注入到外周沟槽54的底面上的C的浓度低于被注入到栅极沟槽34的底面

上的C的浓度，则外周沟槽54的底面附近的B的扩散距离也将长于栅极沟槽34的底面附近的B的扩散距离。因此，能够将底面区56形成为宽度与p型浮动区32相比而较宽。

[0069] 实施例3

[0070] 在实施例3的制造方法中，上述的第二注入工序与实施例1的制造方法不同。其他的工序与实施例1的制造方法等同。

[0071] 在实施例3的第二注入工序中，以极高浓度向外周沟槽54的底面注入B。具体而言，以构成外周沟槽54的底面的半导体层的至少一部分含有 $1 \times 10^{18} \text{ atoms/cm}^3$ 以上的浓度的B的方式注入B。在此如此以高浓度注入B时，在以高浓度注入B的区内产生极多的结晶缺陷。根据情况，以高浓度注入B的区会发生非结晶化。其结果为，在以高浓度注入B的区中，B的扩散系数降低。

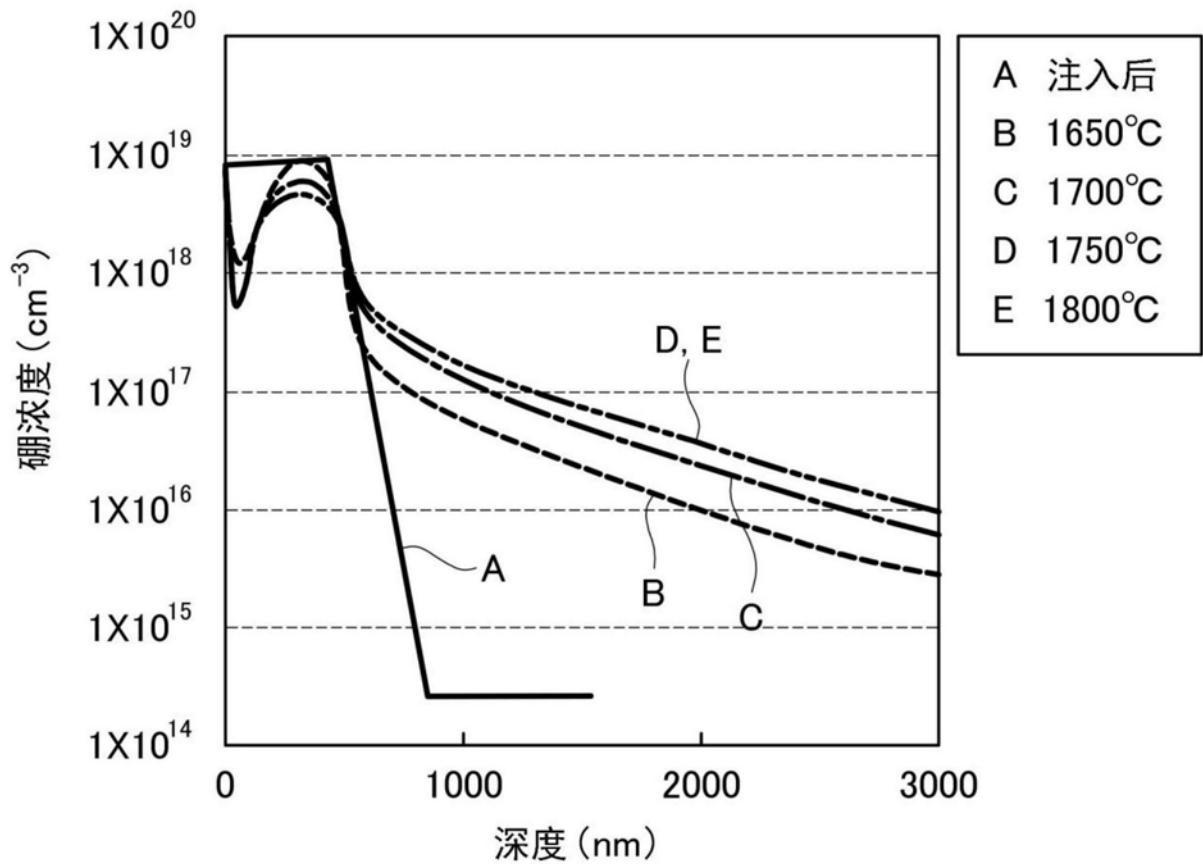

[0072] 图11表示向由SiC组成的半导体基板的较浅的区域(更详细而言，浅于1000nm的区)内注入B时的B的浓度分布。在图11中，曲线A表示刚刚注入B之后的浓度分布。此外，曲线B~E表示在所对应的温度内实施了30分钟的退火之后的浓度分布。另外，在图11中，曲线D和曲线E重叠。在曲线A中，B仅分布在浅于1000nm的区域内。如曲线B~E所示，在实施热处理时，B的分布范围向较深的方向延展。这表示B在SiC中扩散了。但是，通过对曲线A和曲线B~E进行比较可知，在B的浓度为 $1 \times 10^{18} \text{ atoms/cm}^3$ 以上的区域内，在曲线A~E中，B的浓度几乎没有发生变化。这意味着在含有 $1 \times 10^{18} \text{ atoms/cm}^3$ 以上的高浓度的B的区域内，B难以扩散。由于在含有 $1 \times 10^{18} \text{ atoms/cm}^3$ 以上的高浓度的B的区域内，缺陷极多，因此可知B的扩散系数变小。

[0073] 在实施例3的制造方法中，在第二注入工序中以高浓度向外周沟槽54的底面注入B，之后实施活化退火工序。如此，由于在外周沟槽54的底面附近的以高浓度含有B的区域内，B不太扩散，因此外周沟槽54的底面附近残留有B的浓度较高的区域。由此，形成图12所示的高浓度底面区57。此外，在高浓度底面区57的周围，通过使B较宽地扩散，从而形成低浓度底面区58。另外，更具体而言，高浓度底面区57为，含有 $1 \times 10^{18} \text{ atoms/cm}^3$ 以上的浓度的B的区，低浓度底面区58为，含有小于 $1 \times 10^{18} \text{ atoms/cm}^3$ 的浓度的B的区。另外，高浓度底面区57也可以是非结晶化的区。如此，如果在外周沟槽54的底面附近形成高浓度底面区57，则能够防止在耗尽层向外周区50内伸展时耗尽层到达外周沟槽54的底面上的情况。由此，能够对在外周沟槽54的底面附近产生较高的电场的情况进行抑制。此外，通过使低浓度底面区58较宽地分布，从而使底面区56的宽度W1变宽，实现外周区50的耐压的提高。

[0074] 实施例4

[0075] 在实施例4的制造方法中，上述的第二注入工序与实施例1的制造方法不同。其他的工序与实施例1的制造方法等同。

[0076] 在实施例4的第二注入工序中，向外周沟槽54的底面注入B，接着，向外周沟槽54的底面注入A1。另外，也可以先注入A1，然后再注入B。在活化退火工序中，以与实施例1的制造方法同样的方式对半导体基板12进行退火，并使被注入到半导体基板12内的p型杂质(即，B和A1)扩散。在此，在外周沟槽54的底面附近，B从底面向其周围较宽地扩散，相对于此，A1由于难以扩散而滞留在底面的附近。因此，如图12所示，在外周沟槽54的底面的周围，形成有p型杂质浓度较高的高浓度底面区57，在该高浓度底面区57的周围，形成有p型杂质浓度较低的低浓度底面区58。在实施例4中，高浓度底面区57为A1大量存在的区域，低浓度底面区58

为B大量存在的区域。因此,即使在通过实施例4的制造方法而被制造出的半导体装置10中,也能够在耗尽层向外周区50扩展时防止耗尽层到达外周沟槽54的底面上。由此,能够对在外周沟槽54的底面附近产生较高的电场的情况进行抑制。

[0077] 如以上所说明的那样,在实施例1~4的制造方法中,以如下方式对与p型杂质及与p型杂质一起注入的元素进行选择,即,对于活化退火工序中的p型杂质的扩散距离,与被注入到栅极沟槽34的底面上的p型杂质相比,被注入到外周沟槽54的底面上的p型杂质的扩散距离较长。由此,实现使底面区56形成为宽度与p型浮动区32相比而较宽。另外,在上述的实施例1~4中,也可以取代Al而将Ga(钙)或In(铟)作为p型杂质来使用。由于Ga、In在SiC中的扩散距离较短,因此能够以与Al同样的方式来使用。此外,Al、Ga、In的扩散距离短于注入了B和C的情况下B的扩散距离。因此,也可以在第一注入工序中,将Al、Ga或In注入到栅极沟槽34的底面上,而在第二注入工序中向外周沟槽54的底面注入C和B。此外,也可以将实施例3、4的第二注入工序应用到实施例2中。

[0078] 另外,虽然在上述的实施例中,使用了SiC制的半导体基板,但也可以使用其他的半导体基板。但是,在SiC制的半导体基板中,B的扩散系数与其他的p型杂质的扩散系数相比而极大。因此,通过将实施例应用在SiC制的半导体基板上,从而能够将p型浮动区32的宽度设置为最小限度,并将底面区56的宽度充分扩大。

[0079] 此外,虽然在上述的实施例中对MOSFET的制造方法进行了说明,但也可以将上述技术应用到IGBT等其他的绝缘栅型半导体装置的制造工序中。

[0080] 此外,虽然在上述的实施例中,于栅极沟槽34的下端形成有p型浮动区32,但也可以取代p型浮动区32而形成与预定的电位连接的p型区。

[0081] 以上,虽然对本发明的具体例进行了详细说明,但这些只不过是例示,并不是对权利要求的范围进行限定的内容。在权利要求书中所记载的技术中,包括对以上所例示的具体例进行各种变形、变更的技术。

[0082] 本说明书或附图中所说明的技术要素为通过单独或各种的组合而发挥技术有用性的要素,并不限定于申请时权利要求记载的组合。此外,本说明书或附图中所例示的技术为同时实现多个目的的技术,且为实现其中的一个目的本身就具有技术有用性的技术。

[0083] 符号说明

[0084] 10:半导体装置;

[0085] 12:半导体基板;

[0086] 14:表面电极;

[0087] 16:绝缘层;

[0088] 18:背面电极;

[0089] 20:单元区;

[0090] 22:源极区;

[0091] 24:体接触区;

[0092] 26:体区;

[0093] 28:漂移区;

[0094] 30:漏极区;

[0095] 32:p型浮动区;

- [0096] 34:栅极沟槽;

- [0097] 34a:底部绝缘层;

- [0098] 34b:栅极绝缘膜;

- [0099] 34c:栅电极;

- [0100] 34d:绝缘层;

- [0101] 50:外周区;

- [0102] 51:表面区;

- [0103] 53:绝缘层;

- [0104] 54:外周沟槽;

- [0105] 56:底面区。

图1

图2

图3

图4

图5

图6

图7

图8

图9

图10

图11

图12