(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6651894号

(P6651894)

(45) 発行日 令和2年2月19日(2020.2.19)

(24) 登録日 令和2年1月27日(2020.1.27)

(51) Int.Cl.

F 1

|             |           |            |      |

|-------------|-----------|------------|------|

| HO1L 29/78  | (2006.01) | HO1L 29/78 | 652J |

| HO1L 29/12  | (2006.01) | HO1L 29/78 | 652T |

| HO1L 21/336 | (2006.01) | HO1L 29/78 | 653A |

| HO1L 29/06  | (2006.01) | HO1L 29/78 | 652H |

| HO1L 21/265 | (2006.01) | HO1L 29/78 | 658E |

請求項の数 13 (全 15 頁) 最終頁に続く

(21) 出願番号

特願2016-32292(P2016-32292)

(22) 出願日

平成28年2月23日(2016.2.23)

(65) 公開番号

特開2017-152489(P2017-152489A)

(43) 公開日

平成29年8月31日(2017.8.31)

審査請求日

平成30年4月27日(2018.4.27)

(73) 特許権者 000004260

株式会社デンソー

愛知県刈谷市昭和町1丁目1番地

(73) 特許権者 000003207

トヨタ自動車株式会社

愛知県豊田市トヨタ町1番地

(73) 特許権者 000003609

株式会社豊田中央研究所

愛知県長久手市横道41番地の1

(74) 代理人 110001128

特許業務法人ゆうあい特許事務所

(72) 発明者 竹内 有一

愛知県刈谷市昭和町1丁目1番地 株式会社デンソー内

最終頁に続く

(54) 【発明の名称】 化合物半導体装置およびその製造方法

## (57) 【特許請求の範囲】

## 【請求項1】

化合物半導体装置であって、

化合物半導体にて構成される第1導電型の下地層(2、42)を有する半導体基板(1、2、41、42)と、

前記下地層に対して形成されたディープトレニチ(15、44)の底部における角部に形成された第1導電型領域(16、46)と、

前記ディープトレニチ内において前記第1導電型領域を覆うように形成された第2導電型のディープ層(5、45)と、を有し、

前記第1導電型領域は、断面形状が三角形状もしくは前記ディープ層と接する部分が凹んで曲面となった三角ラウンド形状とされている化合物半導体装置。 10

## 【請求項2】

前記第1導電型領域は、前記下地層よりも第1導電型不純物濃度が高い請求項1に記載の化合物半導体装置。

## 【請求項3】

裏面側に備えられた高不純物濃度となる裏面層(1)と、表面側に備えられ前記下地層を構成すると共に前記裏面層よりも低不純物濃度とされた第1導電型のドリフト層(2)と、を有する前記半導体基板(1、2)と、

前記ドリフト層の上に形成された第2導電型のベース領域(3)と、

前記ベース領域の上層部に形成され、前記ドリフト層よりも高不純物濃度の第1導電型 20

のソース領域(4)と、

前記ソース領域の表面から前記ベース領域よりも深くまで形成されたゲートトレンチ(6)内に形成され、該ゲートトレンチの内壁面に形成されたゲート絶縁膜(7)と、前記ゲート絶縁膜の上に形成されたゲート電極(8)と、を有して構成されたトレンチゲート構造と、

前記ソース領域に電気的に接続されるソース電極(9)と、

前記半導体基板の裏面側における前記裏面層と電気的に接続されるドレイン電極(10)と、を有する縦型MOSFETを備え、

前記ソース領域および前記ベース領域を貫通して前記ドリフト層に至り、かつ、前記ゲートトレンチよりも深い位置まで前記ディープトレンチ(15)が形成され、該ディープトレンチ内における前記ベース領域よりも下方に、前記ベース領域から離れて前記第1導電型領域(16)が形成されていると共に、該ディープトレンチ内において前記第1導電型領域を覆うように前記ディープ層(5)が形成されている請求項1または2に記載の化合物半導体装置。10

#### 【請求項4】

裏面側に備えられた高不純物濃度となる裏面層(41)と、表面側に備えられ前記下地層を構成すると共に前記裏面層よりも低不純物濃度とされた第1導電型のドリフト層(42)と、を有する前記半導体基板(41、42)と、

前記ドリフト層の上に形成され、前記ドリフト層よりも高不純物濃度となる第1導電型高濃度層(43)と、を有するジャンクションバリアダイオードを備え。20

前記第1導電型高濃度層を貫通し、前記ドリフト層に達するように前記ディープトレンチ(44)が形成され、該ディープトレンチ内における底部の角部に前記第1導電型領域(46)が形成されていると共に、該ディープトレンチ内において前記第1導電型領域を覆うように前記ディープ層(45)が形成されている請求項1または2に記載の化合物半導体装置。

#### 【請求項5】

前記ディープ層を上方ディープ層(5a)として、前記ディープトレンチの下方に、前記上方ディープ層と接すると共に底部の角部が丸まつた第2導電型の下方ディープ層(5b)が形成されている請求項1ないし4のいずれか1つに記載の化合物半導体装置。

#### 【請求項6】

化合物半導体装置の製造方法であって、

化合物半導体にて構成される第1導電型の下地層(2、42)を有する半導体基板(1、2、41、42)を用意することと、

前記下地層に対してディープトレンチ(15、44)を形成することと、

エピタキシャル成長装置内に第1導電型ドーパントを含むドーパントガスを導入しつつ、前記化合物半導体の原料ガスを導入し、前記ディープトレンチの底部における角部に、断面形状が三角形状もしくは表面が凹んで曲面となる三角ラウンド形状の第1導電型領域(16、46)を形成すること、

前記第1導電型領域を形成したのち、第2導電型ドーパントを含むドーパントガスを導入しつつ、前記化合物半導体の原料ガスを導入し、前記第1導電型領域を覆いつつ前記ディープトレンチ内に第2導電型のディープ層(5、45)をエピタキシャル成長させることと、を含む化合物半導体装置の製造方法。40

#### 【請求項7】

前記第1導電型領域を形成すること、および、前記ディープ層をエピタキシャル成長させることは、前記化合物半導体のエッティングガスを導入しつつ前記エピタキシャル成長装置内の昇温を行うとともに、昇温期間中から前記第1導電型ドーパントを含むドーパントガスの導入を行い、前記昇温期間後に前記第2導電型ドーパントを含むドーパントガスの導入を行うと共に前記化合物半導体の原料ガスを導入することによって行われる請求項6に記載の化合物半導体装置の製造方法。

#### 【請求項8】

50

前記第1導電型領域を形成すること、および、前記ディープ層をエピタキシャル成長させることでは、前記化合物半導体の原料ガスの導入の前もしくは後において、前記第1導電型ドーパントを含むドーパントガスの導入から前記第2導電型ドーパントを含むドーパントガスの導入への切替えを行う請求項6または7に記載の化合物半導体装置の製造方法。

#### 【請求項9】

前記第2導電型ドーパントを含むドーパントガスとしてトリメチルアルミニウムを用いる請求項6ないし8のいずれか1つに記載の化合物半導体装置の製造方法。

#### 【請求項10】

前記第1導電型ドーパントを含むドーパントガスとして窒素を用いる請求項6ないし9のいずれか1つに記載の化合物半導体装置の製造方法。 10

#### 【請求項11】

前記ディープ層を上方ディープ層(5a)として、

前記ディープトレンチを形成した後、該ディープトレンチの底部に対してイオン注入することで、第2導電型の下方ディープ層(5b)を形成することを含む請求項6ないし10のいずれか1つに記載の化合物半導体装置の製造方法。

#### 【請求項12】

裏面側に備えられた裏面層(1)と、表面側に備えられ前記下地層を構成すると共に前記裏面層よりも低不純物濃度とされた第1導電型のドリフト層(2)と、を有する前記半導体基板(1、2)を用意することと、 20

前記ドリフト層(2)の上に第2導電型のベース領域(3)を形成することと、

前記ベース領域の上層部に、前記ドリフト層よりも高不純物濃度の第1導電型のソース領域(4)を形成することと、

前記ソース領域の表面から前記ベース領域よりも深くまでゲートトレンチ(6)を形成することと、

前記ゲートトレンチの内壁面にゲート絶縁膜(7)を形成すると共に、前記ゲート絶縁膜の上にゲート電極(8)を形成することでトレンチゲート構造を構成することと、

前記ソース領域に電気的に接続されるソース電極(9)を形成することと、

前記半導体基板の裏面側における前記裏面層と電気的に接続されるドレイン電極(10)を形成することと、を含み、 30

前記ディープトレンチを形成することとして、前記ソース領域の表面から前記ベース領域を貫通して前記ドリフト層に達し、かつ、前記ゲートトレンチより深い位置まで前記ディープトレンチ(15)を形成することを行い、

前記第1導電型領域を形成することとして、前記ディープトレンチ底部角部に前記第1導電型領域を形成する請求項6ないし11のいずれか1つに記載の化合物半導体装置の製造方法。

#### 【請求項13】

裏面側に備えられた高不純物濃度となる裏面層(41)と、表面側に備えられ前記下地層を構成すると共に前記裏面層よりも低不純物濃度とされた第1導電型のドリフト層(42)と、を有する前記半導体基板(41、42)と、 40

前記ドリフト層の上に、前記ドリフト層よりも高不純物濃度な第1導電型高濃度層(43)を形成することと、

前記第1導電型高濃度層に接触するショットキー電極(47)を形成することと、

前記裏面層に接触する裏面電極(48)を形成することと、を含み、

前記ディープトレンチを形成することとして、前記第1導電型高濃度層の表面から該第1導電型高濃度層を貫通して前記ドリフト層に達するように前記ディープトレンチ(44)を形成することを行う請求項6ないし11のいずれか1つに記載の化合物半導体装置の製造方法。

#### 【発明の詳細な説明】

#### 【技術分野】

**【0001】**

本発明は、例えば炭化珪素（以下、SiCという）や窒化ガリウム（以下、GaNという）などの化合物半導体を用いた化合物半導体装置およびその製造方法に関する。

**【背景技術】****【0002】**

従来、特許文献1に、トレンチゲート構造の縦型スイッチング素子として、反転型のトレンチゲート構造の縦型MOSFETを備えたSiC半導体装置が提案されている。反転型のトレンチゲート構造の縦型MOSFETでは、ゲートトレンチ内のゲート電極に対してゲート電圧を印加することで、ゲートトレンチ側面に位置するp型ベース領域にチャネルを形成し、このチャネルを通じてドレイン・ソース間に電流を流す。このようなトレンチゲート構造の縦型MOSFETでは、トレンチゲート構造に備えられるゲート絶縁膜に対して高電界が加わると絶縁破壊が生じて素子耐圧が低下してしまう。10

**【0003】**

このため、特許文献1に記載のSiC半導体装置では、トレンチゲート構造を挟んだ両側に、n<sup>+</sup>型ソース領域およびp型ベース領域を貫通してn<sup>-</sup>型ドリフト層に達するディープトレンチを形成し、このトレンチ内にp型ディープ層を備えるようにしている。このようなp型ディープ層を備えることで電界がゲート絶縁膜に入り込むことを抑制でき、ゲート絶縁膜を高電界から保護して絶縁破壊が起こり難くなつて、素子耐圧を向上することが可能となる。20

**【先行技術文献】****【特許文献】****【0004】****【特許文献1】特開2014-236189号公報****【発明の概要】****【発明が解決しようとする課題】****【0005】**

しかしながら、エピタキシャル成長によってディープトレンチ内に均一濃度でp型ディープ層を形成しようとすると、ディープトレンチの底部における角部が尖っているため、角部においてオフ時の電界強度が高くなり、耐圧低下を引き起す。30

**【0006】**

また、オフ時にトレンチゲート構造におけるゲート絶縁膜に加わる電界を低下させるためにはp型ディープ層を深くすれば良いが、p型ディープ層によって電流経路が狭まるJFET部が増加するため、オン抵抗を増大させてしまうというトレードオフがある。30

**【0007】**

なお、ここではディープ層を有する構造として、縦型MOSFETを例に挙げて説明したが、縦型MOSFETに限らない。例えば、ジャンクションバリアダイオード（以下、JBSという）などにおいても、ディープ層を備えた構造とすることができます。その場合においても、ディープ層が深くなると、JFET部が増加することになり、オン抵抗を増大させるという上記と同様の課題が発生し得る。40

**【0008】**

本発明は上記点に鑑みて、オン抵抗の増大を抑制することが可能となる化合物半導体装置およびその製造方法を提供することを目的とする。

**【課題を解決するための手段】****【0009】**

上記目的を達成するため、請求項1に記載の化合物半導体装置では、化合物半導体にて構成される第1導電型の下地層（2、42）を有する半導体基板（1、2、41、42）と、下地層に対して形成されたディープトレンチ（15、44）の底部における角部に形成された第1導電型領域（16、46）と、ディープトレンチ内において第1導電型領域を覆うように形成された第2導電型のディープ層（5、45）と、を有し、第1導電型領域は、断面形状が三角形状もしくはディープ層と接する部分が凹んで曲面となった三角ラ

50

ウンド形状とされている。

**【0010】**

このように、ディープ層の底部側の角部、つまりディープトレンチにおける底部側の角部に第1導電型領域が形成されるようにしている。このため、ディープ層の底部側の角部の断面形状を鈍角もしくは丸みを帯びた形状にできる。これにより、ディープ層の底部側の角部においてオフ時に電界集中によって電界強度が高くなることを抑制できる。また、耐圧低下を抑制できることから、ディープ層を必要以上に深く形成しなくても済み、オン抵抗の増大を抑制することが可能となる。

**【0011】**

なお、上記各手段の括弧内の符号は、後述する実施形態に記載の具体的手段との対応関係の一例を示すものである。 10

**【図面の簡単な説明】**

**【0012】**

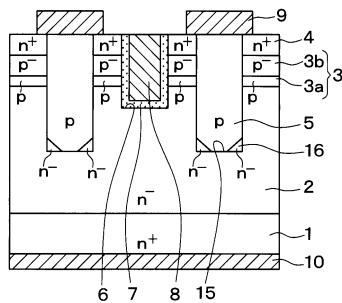

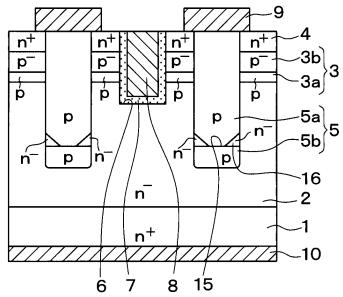

**【図1】**第1実施形態にかかる縦型MOSFETを備えたSiC半導体装置の断面図である。

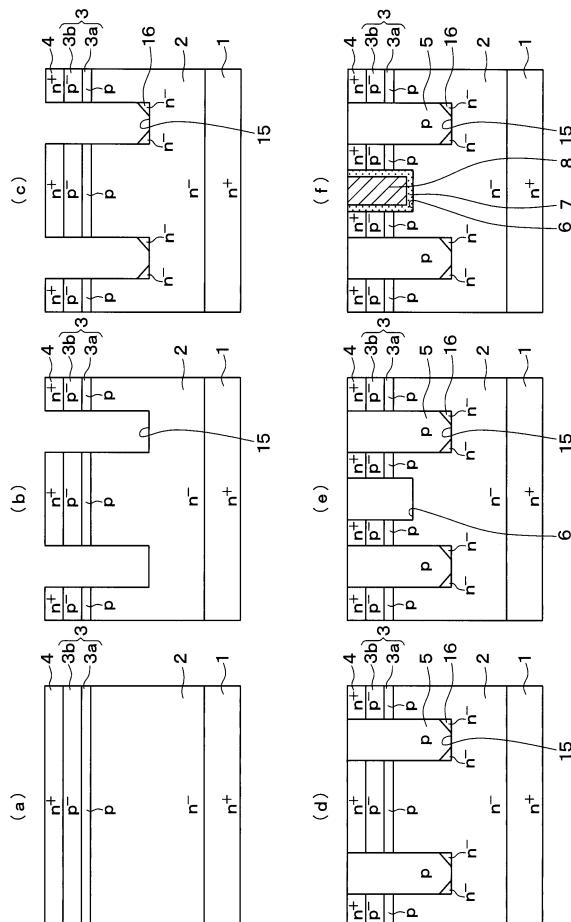

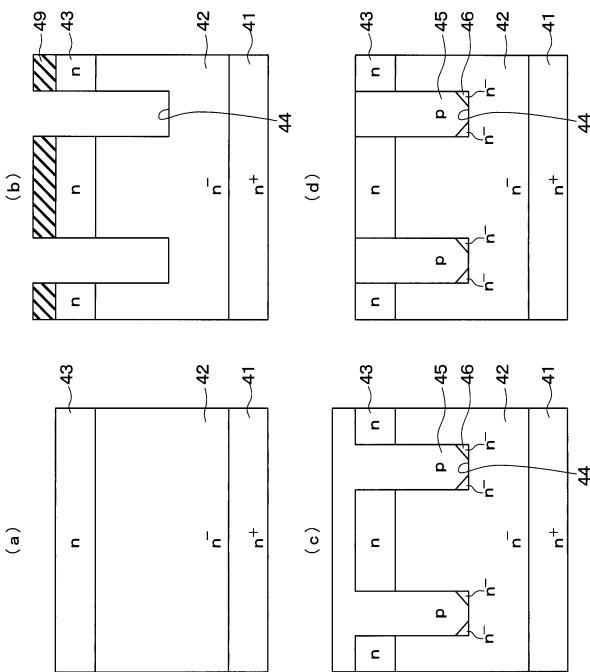

**【図2】**図1に示すSiC半導体装置の製造工程を示した断面図である。

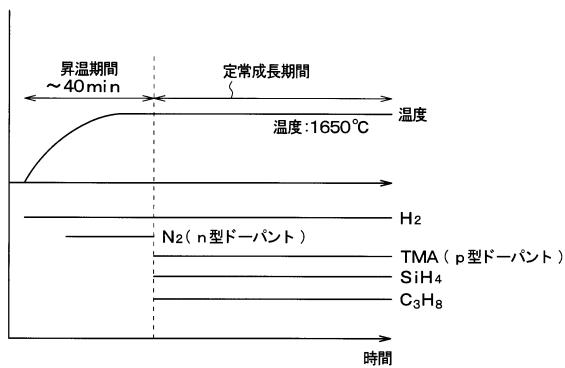

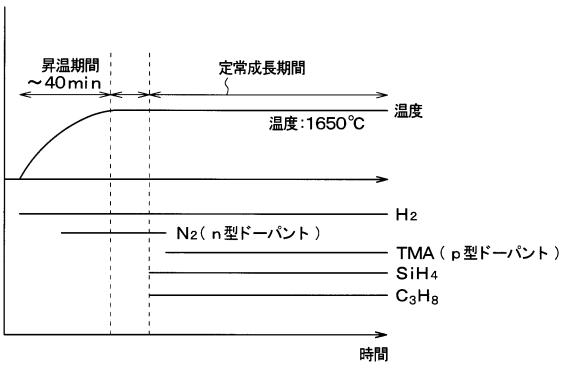

**【図3】**第1実施形態にかかるディープトレンチ内へのn<sup>-</sup>型領域およびp型ディープ層の成長プログラムを示したタイムチャートである。

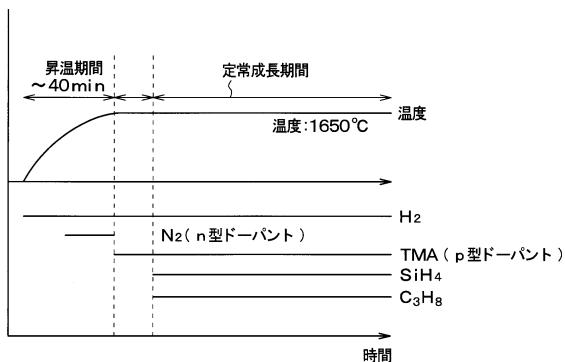

**【図4】**第2実施形態にかかるディープトレンチ内へのn<sup>-</sup>型領域およびp型ディープ層の成長プログラムを示したタイムチャートである。 20

**【図5】**第2実施形態の変形例で説明するディープトレンチ内へのn<sup>-</sup>型領域およびp型ディープ層の成長プログラムを示したタイムチャートである。

**【図6】**第3実施形態にかかる縦型MOSFETを備えたSiC半導体装置の断面図である。

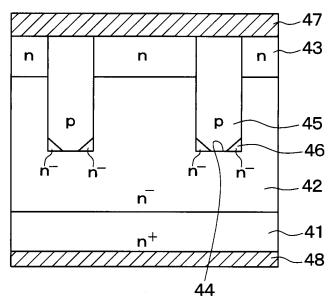

**【図7】**第4実施形態にかかるJBSを備えたSiC半導体装置の断面図である。

**【図8】**図7に示すSiC半導体装置の製造工程を示した断面図である。

**【発明を実施するための形態】**

**【0013】**

以下、本発明の実施形態について図に基づいて説明する。なお、以下の各実施形態相互において、互いに同一もしくは均等である部分には、同一符号を付して説明を行う。 30

**【0014】**

(第1実施形態)

本発明の第1実施形態にかかるトレンチゲート構造の反転型の縦型MOSFETが形成されたSiC半導体装置について、図1を参照して説明する。

**【0015】**

図1に示すSiC半導体装置は、セル領域にトレンチゲート構造の縦型MOSFETが形成され、図示していないが、セル領域を囲む外周領域に外周耐圧構造が備えられた構成とされている。

**【0016】**

SiC半導体装置は、SiCからなる高濃度不純物層を構成するn<sup>+</sup>型基板1の表面側に、n<sup>+</sup>型基板1よりも低不純物濃度のSiCからなるn<sup>-</sup>型ドリフト層2が形成された半導体基板を用いて形成されている。n<sup>+</sup>型基板1は、例えばn型不純物濃度が1.0×10<sup>19</sup>/cm<sup>3</sup>とされ、表面が(0001)Si面とされている。n<sup>-</sup>型ドリフト層2は、例えばn型不純物濃度が0.5~2.0×10<sup>16</sup>/cm<sup>3</sup>とされている。 40

**【0017】**

n<sup>-</sup>型ドリフト層2の上層部にはベース領域3が形成されている。本実施形態の場合、ベース領域3は、n<sup>-</sup>型ドリフト層2よりも高不純物濃度のp型SiCで構成されており、p型不純物濃度が比較的高くされた高濃度ベース領域3aと、それよりもp型不純物濃度が低くされた低濃度ベース領域3bとが順に積層された構造とされている。

**【0018】**

10

20

30

40

50

高濃度ベース領域3aは、例えばp型不純物濃度が $5 \times 10^{17} / \text{cm}^3$ 以上、例えば $1 \times 10^{18} / \text{cm}^3$ とされ、厚みが $50 \sim 200 \text{ nm}$ とされている。低濃度ベース領域3bは、例えばp型不純物濃度が $1.0 \times 10^{16} / \text{cm}^3$ 以下とされ、厚みが $0.3 \sim 1.0 \mu\text{m}$ とされている。

#### 【0019】

さらに、ベース領域3の上層部分にはn<sup>+</sup>型ソース領域4が形成されている。また、n<sup>+</sup>型ソース領域4の表面からn<sup>+</sup>型ソース領域4およびベース領域3を貫通し、n<sup>-</sup>型ドリフト層2に達するようにp型ディープ層5が形成されている。具体的には、n<sup>+</sup>型ソース領域4の表面からn<sup>+</sup>型ソース領域4およびベース領域3を貫通し、n<sup>-</sup>型ドリフト層2に達するディープトレンチ15が形成されており、このディープトレンチ15内にp型ディープ層5が埋め込まれている。例えば、ディープトレンチ15は、アスペクト比が2以上の深さとされている。さらに、p型ディープ層5の底部の角部、換言すればディープトレンチ15の底部における角部に、n<sup>-</sup>型領域16が備えられている。

#### 【0020】

n<sup>+</sup>型ソース領域4は、後述するトレンチゲート構造の両側に配置されており、p型ディープ層5は、n<sup>+</sup>型ソース領域4を挟んでトレンチゲート構造と反対側においてトレンチゲート構造よりも深い位置まで形成されており、n<sup>-</sup>型領域16を覆いつつディープトレンチ15内を埋め込むように形成されている。n<sup>+</sup>型ソース領域4は、表層部におけるn型不純物濃度が例えば $2.5 \times 10^{18} \sim 1.0 \times 10^{19} / \text{cm}^3$ 、厚さ $0.5 \mu\text{m}$ 程度で構成されている。また、p型ディープ層5は、ベース領域3よりも高不純物濃度とされ、p型不純物濃度が例えば $1.0 \times 10^{17} \sim 1.0 \times 10^{19} / \text{cm}^3$ とされている。本実施形態では、p型ディープ層5は、後述するソース電極9と電気的接続が行われるコンタクト領域も兼ねている。n<sup>-</sup>型領域16は、ベース領域3よりも下方において、ベース領域3から離れて形成されている。n<sup>-</sup>型領域16は、断面形状が三角形状、もしくはp型ディープ層5と接する部分が凹んで曲面となった三角ラウンド形状とされており、n型不純物濃度がn<sup>-</sup>型ドリフト層2よりも高く、例えば $1.0 \times 10^{16} \sim 4.0 \times 10^{16} / \text{cm}^3$ とされている。このようなn<sup>-</sup>型領域16が形成されることにより、p型ディープ層5の底部側の角部の断面形状が垂直もしくは鋭角にはならず、鈍角もしくは丸みを帯びた形状となっている。

#### 【0021】

また、ベース領域3およびn<sup>+</sup>型ソース領域4を貫通してn<sup>-</sup>型ドリフト層2に達するように、紙面垂直方向を長手方向とするトレンチ6が形成されている。このトレンチ6の側面と接するように上述したベース領域3における高濃度ベース領域3aや低濃度ベース領域3bおよびn<sup>+</sup>型ソース領域4が配置されている。

#### 【0022】

さらに、ベース領域3のうちn<sup>+</sup>型ソース領域4とn<sup>-</sup>型ドリフト層2との間に位置する部分の表層部をチャネル領域として、このチャネル領域を含むトレンチ6の内壁面にはゲート絶縁膜7が形成されている。そして、ゲート絶縁膜7の表面にはドープドPoly-Siにて構成されたゲート電極8が形成されており、これらゲート絶縁膜7およびゲート電極8によってトレンチ6内が埋め尽くされている。

#### 【0023】

このようにして、トレンチゲート構造が構成されている。このトレンチゲート構造は、図1の紙面垂直方向を長手方向として延設されており、複数のトレンチゲート構造が図1中の左右方向に並べられることでストライプ状とされている。また、上述したn<sup>+</sup>型ソース領域4およびp型ディープ層5もトレンチゲート構造の長手方向に沿って延設されたレイアウト構造とされている。

#### 【0024】

また、n<sup>+</sup>型ソース領域4およびp型ディープ層5の表面やゲート電極8の表面には、ソース電極9やゲート配線（図示せず）が形成されている。ソース電極9およびゲート配線は、複数の金属（例えばNi / Al等）にて構成されている。そして、複数の金属のう

ち少なくとも n 型 SiC ( 具体的には  $n^+$  型ソース領域 4 や n 型ドープの場合のゲート電極 8 ) と接触する部分は n 型 SiC とオーミック接触可能な金属で構成されている。また、複数の金属のうち少なくとも p 型 SiC ( 具体的には p 型ディープ層 5 ) と接触する部分は p 型 SiC とオーミック接触可能な金属で構成されている。なお、これらソース電極 9 およびゲート配線は、図示しない層間絶縁膜上に形成されることで電気的に絶縁されている。そして、層間絶縁膜に形成されたコンタクトホールを通じて、ソース電極 9 は  $n^+$  型ソース領域 4 および p 型ディープ層 5 と電気的に接触させられ、ゲート配線はゲート電極 8 と電気的に接触させられている。

#### 【 0 0 2 5 】

さらに、 $n^+$  型基板 1 の裏面側には  $n^+$  型基板 1 と電気的に接続されたドレイン電極 10 が形成されている。このような構造により、n チャネルタイプの反転型のトレンチゲート構造の縦型 MOSFET が構成されている。そして、この縦型 MOSFET が形成されたセル領域の外周領域に、図示しない外周耐圧構造が備えられることで、本実施形態にかかる SiC 半導体装置が構成されている。

#### 【 0 0 2 6 】

このような SiC 半導体装置に備えられる反転型のトレンチゲート構造の縦型 MOSFET は、ゲート電極 8 にゲート電圧を印加すると、ベース領域 3 のうちトレンチ 6 に接している表面にチャネルが形成される。これにより、ソース電極 9 から注入された電子が  $n^+$  型ソース領域 4 からベース領域 3 に形成されたチャネルを通った後、 $n^-$  型ドリフト層 2 に到達し、ソース電極 9 とドレイン電極 10 との間に電流を流すという動作が行われる。

#### 【 0 0 2 7 】

このとき、本実施形態の SiC 半導体装置では、ディープトレンチ 15 をすべて p 型ディープ層 5 によって埋め込んでしまうのではなく、ディープトレンチ 15 の底部における角部を  $n^-$  型領域 16 としている。このため、 $n^-$  型領域 16 が形成されることにより、p 型ディープ層 5 の底部側の角部の断面形状が垂直もしくは鋭角にはならず、鈍角もしくは丸みを帯びた形状となる。これにより、p 型ディープ層 5 の底部側の角部においてオフ時に電界集中によって電界強度が高くなることを抑制できる。したがって、縦型 MOSFET の耐圧低下を抑制することが可能となる。そして、このように  $n^-$  型領域 16 を形成することによって縦型 MOSFET の耐圧低下を抑制できることから、p 型ディープ層 5 を必要以上に深く形成しなくても済み、オン抵抗の増大を抑制することが可能となる。

#### 【 0 0 2 8 】

また、ベース領域 3 を高濃度ベース領域 3a と低濃度ベース領域 3b によって構成しており、これら高濃度ベース領域 3a と低濃度ベース領域 3b によってチャネルが形成されるようにしている。このため、高濃度ベース領域 3a によってベース領域 3 内における空乏層の拡がりを抑制できる。したがって、ベース領域 3 内が完全空乏化してパンチスルーしてしまうことを防止でき、素子耐圧確保が可能になると共にトレンチ 6 の底部のゲート絶縁膜 7 の劣化防止も可能になる。また、閾値電圧が高濃度ベース領域 3a の p 型不純物濃度に依存することになるため、高閾値電圧を得ることも可能となる。

#### 【 0 0 2 9 】

また、低濃度ベース領域 3b の部分においてチャネル移動度が高められるため、高濃度ベース領域 3a を備えていたとしても、オン抵抗低減を図ることが可能となる。したがって、オン抵抗低減および素子耐圧確保が可能で、かつ、高閾値電圧が得られるトレンチゲート構造の縦型 MOSFET とすることができる。

#### 【 0 0 3 0 】

また、高濃度ベース領域 3a が存在することで、オフ時においては、 $n^-$  型ドリフト層 2 とベース領域 3 との接合から発生するキャリアの引き抜き効果が高められるため、ドレンリーク電流を低減できる。

#### 【 0 0 3 1 】

また、ベース領域 3 のうち  $n^-$  型ドリフト層 2 と接触する部分がすべて p 型不純物濃度が高い高濃度ベース領域 3a とされていることから、 $n^-$  型ドリフト層 2 とベース領域 3

10

20

30

40

50

とのP N接合にて構成される内蔵ダイオードに電流が流れる際の立上り電圧が低減できる。このため、内蔵ダイオードのオン電圧が低減され、内蔵ダイオードを積極的に用いた同期整流駆動時の損失低減を図ることも可能となる。

#### 【0032】

さらに、オフ時において、高濃度ベース領域3a側からn<sup>-</sup>型ドリフト層2側に延びる空乏層によって、トレンチゲート構造の下方に等電位線が入り込み難くなるようにできる。このため、トレンチ6の底面においてゲート絶縁膜7に印加される電界集中を緩和でき、ゲート絶縁膜7の寿命向上、逆バイアス寿命向上を図ることが可能となる。

#### 【0033】

続いて、図1のように構成された本実施形態にかかるSiC半導体装置の製造方法について、図2および図3を参照して説明する。

10

#### 【0034】

##### 〔図2(a)に示す工程〕

まず、半導体基板として、SiCからなるn<sup>+</sup>型基板1の表面上にSiCからなるn<sup>-</sup>型ドリフト層2がエピタキシャル成長させられた、いわゆるエピ基板を用意する。そして、このエピ基板をエピタキシャル成長装置内に配置し、n<sup>-</sup>型ドリフト層2の表面に高濃度ベース領域3a、低濃度ベース領域3b、n<sup>+</sup>型ソース領域4を順にエピタキシャル成長する。

#### 【0035】

##### 〔図2(b)に示す工程〕

20

n<sup>+</sup>型ソース領域4の表面にマスク材(図示せず)を配置したのち、フォトリソグラフィによってマスク材のうちのp型ディープ層5およびn<sup>-</sup>型領域16の形成予定位置を開口させる。そして、マスク材を配置した状態でRIE(Reactive Ion Etching)などの異方性エッティングを行うことで、p型ディープ層5およびn<sup>-</sup>型領域16の形成予定位置にディープトレンチ15を形成する。

#### 【0036】

##### 〔図2(c)、(d)に示す工程〕

図示しないエピタキシャル成長装置を用いて、図2(c)に示すn<sup>-</sup>型領域16を形成する工程と、図2(d)に示すp型ディープ層15を形成する工程を連続して行う。

30

#### 【0037】

具体的には、図3に示すように、まず昇温期間としてエピタキシャル成長装置内の温度を例えば1650まで上昇させる。昇温期間については、例えば40分以内程度の時間としている。また、このときにn型ドーパントを含むドーパントガスを導入する。その後、n型ドーパントを含むドーパントガスからp型ドーパントを含むドーパントガスに切替えると共にSiC原料ガスを導入することでn<sup>-</sup>型領域16を形成しつつp型ディープ層5をエピタキシャル成長させる。

#### 【0038】

SiC原料ガスとしては、例えばSi原料となるシラン(SiH<sub>4</sub>)やC原料となるブロパン(C<sub>3</sub>H<sub>8</sub>)等を用いることができる。また、p型ディープ層5を形成する際のドーパントガスとしては、p型ドーパントを含むTMA(トリメチルアルミニウム)を用いている。また、n<sup>-</sup>型領域16を形成する際のドーパントガスとしては、n型ドーパントとなる窒素(N<sub>2</sub>)を用いている。さらに、必要に応じて、エッティングガスとして、例えば水素(H<sub>2</sub>)も導入している。

40

#### 【0039】

このとき、SiC原料ガスを導入する前に窒素を導入しておくと、雰囲気中への昇華などによって存在するSi元素やC元素に基づいて、もしくは、SiC原料ガスが導入された初期時に、ディープトレンチ15の底部にn<sup>-</sup>型領域16を形成することができる。このときのn<sup>-</sup>型領域16の形成はp型ディープ層5の形成よりも前に行われ、n<sup>-</sup>型領域16が形成されてからp型ディープ層5が形成されるようにできる。特に、p型ドーパントのように有機金属材料がドーパントとされる場合、そのドーパントがガス導入初期時に工

50

ピタキシャル成長装置のチャンバ内壁面に貼り付いて所望の p 型不純物濃度となるまでに時間が掛かる立上り遅れが発生する。このため、n<sup>-</sup>型領域 16 がより容易に形成されるようになる。さらに、エッティングガスを導入しつつエピタキシャル成長装置のチャンバ内の昇温を行っているため、昇温期間中にはエッティングと SiC デポジションの平衡状態となる。その昇温期間中から n 型ドーパントを導入していることから、より的確にディープトレンチ 15 の角部にのみ n<sup>-</sup>型領域 16 が形成されるようになる。

#### 【0040】

そして、研削や CMP (Chemical Mechanical Polishing) などによる平坦化によって、p 型ディープ層 5 の形成の際に n<sup>+</sup>型ソース領域 4 の上に形成された p 型不純物層を除去し、n<sup>+</sup>型ソース領域 4 の表面を露出させる。これにより、ディープトレンチ 15 内にのみ n<sup>-</sup>型領域 16 や p 型ディープ層 5 が配置された構造が形成される。10

#### 【0041】

〔図 2 (e) に示す工程〕

n<sup>+</sup>型ソース領域 4 や p 型ディープ層 5 の表面にマスク材（図示せず）を配置したのち、フォトリソグラフィによってマスク材のうちのトレンチ 6 の形成予定位置を開口させる。そして、マスク材を配置した状態で RIE などの異方性エッティングを行うことにより、セル領域においてトレンチ 6 を形成する。その後、マスク材を除去する。

#### 【0042】

そして、必要に応じて、1600 度以上の減圧下における水素雰囲気、例えば 1625 、  $2.7 \times 10^4 \text{ Pa}$  (= 200 Torr) の高温水素雰囲気での熱処理による水素エッティングを実施する。この水素エッティングによってトレンチ 6 の内壁面の丸め処理が行われ、トレンチ 6 の開口入口やコーナー部を丸められると共に、トレンチエッティングのダメージ除去が行われる。20

#### 【0043】

〔図 2 (f) に示す工程〕

ウェット雰囲気による熱酸化によってゲート絶縁膜 7 を形成したのち、ゲート絶縁膜 7 の表面にドープド Poly-Si 層を成膜し、このドープド Poly-Si 層をパターニングすることでトレンチ 6 内に残し、ゲート電極 8 を形成する。

#### 【0044】

この後の工程については、従来と同様である。すなわち、層間絶縁膜の形成工程、フォト・エッティングによるコンタクトホール形成工程、電極材料をデポジションしたのちパターニングすることでソース電極 9 やゲート配線層を形成する工程、n<sup>+</sup>型基板 1 の裏面にドレイン電極 10 を形成する工程等を行う。これにより、図 1 に示すトレンチゲート構造の縦型 MOSFET がセル領域に備えられた SiC 半導体装置が完成する。30

#### 【0045】

以上説明したように、本実施形態で説明した反転型のトレンチゲート構造の縦型 MOSFET を備えた SiC 半導体装置では、p 型ディープ層 5 の底部側の角部、つまりディープトレンチ 15 における底部側の角部に n<sup>-</sup>型領域 16 が形成されるようになっている。このため、p 型ディープ層 5 の底部側の角部の断面形状を鈍角もしくは丸みを帯びた形状にできる。これにより、p 型ディープ層 5 の底部側の角部においてオフ時に電界集中によって電界強度が高くなることを抑制できる。したがって、縦型 MOSFET の耐圧低下を抑制することが可能となる。そして、このように n<sup>-</sup>型領域 16 を形成することによって縦型 MOSFET の耐圧低下を抑制できることから、p 型ディープ層 5 を必要以上に深く形成しなくても済み、オン抵抗の増大を抑制することが可能となる。40

#### 【0046】

（第 2 実施形態）

第 2 実施形態について説明する。本実施形態は、第 1 実施形態に対して p 型ディープ層 5 および n<sup>-</sup>型領域 16 の製造プロセスを変更したものであり、その他については第 1 実施形態と同様であるため、第 1 実施形態と異なる部分についてのみ説明する。

#### 【0047】

50

本実施形態では、p型ディープ層5およびn<sup>-</sup>型領域16の形成の際ににおけるn型ドーパントを含むドーパントガスとp型ドーパントを含むドーパントガスの導入のタイミングを第1実施形態に対して変更している。

#### 【0048】

具体的には、図4に示すように、昇温期間中にn型ドーパントを含むドーパントガスを導入しているが、その後、SiC原料ガスを導入する前に、n型ドーパントを含むドーパントガスからp型ドーパントを含むドーパントガスに切替えている。そして、ドーパントガスの切替えが終わってから、SiC原料ガスの導入を行うようにしている。

#### 【0049】

このように、ドーパントガスの切替えをSiC原料ガスの導入前に行い、SiC原料ガスの導入前からp型ドーパントを含むドーパントガスが導入されるようにしても良い。これにより、SiC原料ガスが導入される前に、エピタキシャル成長装置のチャンバ内壁面に貼り付くようにできることから、SiC原料ガス導入後に貼りつくp型ドーパントの量を低減できる。したがって、より早くからp型ディープ層5が形成されるようにでき、n<sup>-</sup>型領域16の形成される範囲の縮小を図ることが可能となる。10

#### 【0050】

##### (第2実施形態の変形例)

上記第2実施形態では、SiC原料ガスの導入前に、ドーパントガスの切替えを行うようにしているが、逆に、図5に示すように、SiC原料ガスの導入後にドーパントガスの切替えを行うようにすることもできる。このようにすれば、より遅くからp型ディープ層5が形成されるようにでき、n<sup>-</sup>型領域16の形成される範囲の拡大を図ることが可能となる。20

#### 【0051】

##### (第3実施形態)

第3実施形態について説明する。本実施形態は、第1実施形態に対してp型ディープ層5の構成を変更したものであり、その他については第1実施形態と同様であるため、第1実施形態と異なる部分についてのみ説明する。

#### 【0052】

図6に示すように、本実施形態のSiC半導体装置に備えられる縦型MOSFETでは、p型ディープ層5を二層構造としており、第1実施形態で説明したp型ディープ層5を上方p型ディープ層5aとして、この上方p型ディープ層5aおよびn<sup>-</sup>型領域16の下方に、さらに下方p型ディープ層5bを備えた構造としている。下方p型ディープ層5bは、上方p型ディープ層5aと繋がっており、これらは共にソース電位とされる。また、下方p型ディープ層5bは、その底部の角部が丸まっている形状となっている。30

#### 【0053】

このように、p型ディープ層5を上方p型ディープ層5aと下方p型ディープ層5bの二層構造によって実現することもできる。このような構造とする場合においても、下方p型ディープ層5bの底部の角部が丸まっていることから、電界集中を抑制できて、上記第1実施形態と同様の効果を得ることができる。

#### 【0054】

また、このような構造とする場合、p型ディープ層5の側面にn<sup>-</sup>型領域16が形成された構造になることから、この部分においてp型ディープ層5よりn<sup>-</sup>型ドリフト層2側に伸びる空乏層の伸びを抑制することが可能となる。したがって、空乏層の伸びを抑制できる分、JFET部の空乏化領域を縮小することができ、電流経路が広がるようにできるため、オン抵抗の低減を図ることが可能となる。40

#### 【0055】

なお、本実施形態にかかる縦型MOSFETの製造方法は、基本的には第1実施形態と同様である。ただし、ディープトレンチ15を形成した後に、例えばディープトレンチ15を形成する際に用いたマスクをそのまま用いてp型ドーパントのイオン注入を行うことで下方p型ディープ層5bを形成する工程を行うようにする必要がある。このようにイオ50

ン注入を行うことによって下方 p 型ディープ層 5 b を形成すると、下方 p 型ディープ層 5 b の底部の角部が丸まった形状になるようにできる。

#### 【 0 0 5 6 】

##### ( 第 4 実施形態 )

第 4 実施形態について説明する。本実施形態では、半導体素子として縦型 M O S F E T に代えて縦型の J B S を備えた S i C 半導体装置について説明する。

#### 【 0 0 5 7 】

図 7 に示すように、本実施形態の S i C 半導体装置も、S i C からなる高濃度不純物層を構成する n<sup>+</sup>型基板 4 1 の表面側に、n<sup>+</sup>型基板 4 1 よりも低不純物濃度の S i C からなる n<sup>-</sup>型ドリフト層 4 2 が形成された半導体基板を用いて形成されている。この半導体基板としては、第 1 実施形態と同様のものを用いている。10

#### 【 0 0 5 8 】

n<sup>-</sup>型ドリフト層 4 2 の上には、n<sup>-</sup>型ドリフト層 2 よりも高不純物濃度とされた n 型層 4 3 が形成されている。また、n 型層 4 3 を貫通して n<sup>-</sup>型ドリフト層 2 に達するようにディープトレンチ 4 4 が形成され、このディープ層 4 5 が形成されていると共に、ディープ層 4 5 の角部、つまりディープトレンチ 4 4 の底部の角部に n<sup>-</sup>型領域 4 6 が形成されている。

#### 【 0 0 5 9 】

さらに、n 型層 4 3 やディープ層 4 5 の上には、これらと接触するようにショットキー電極 4 7 が形成されている。そして、n<sup>+</sup>型基板 4 1 の裏面側、つまり n<sup>-</sup>型ドリフト層 4 2 と反対側に裏面電極に相当するオーミック電極 4 8 が備えられることで、図 7 に示す縦型 J B S を備えた S i C 半導体装置が構成されている。20

#### 【 0 0 6 0 】

このように、J B S を備えた S i C 半導体装置においても、p 型ディープ層 4 5 の角部に n<sup>-</sup>型領域 4 6 を備えることで、p 型ディープ層 4 5 の底部側の角部の断面形状が垂直もしくは鋭角にはならず、鈍角もしくは丸みを帯びた形状となる。これにより、p 型ディープ層 4 5 の底部側の角部においてオフ時に電界集中によって電界強度が高くなることを抑制できる。したがって、耐圧低下を抑制できることから、p 型ディープ層 4 5 を必要以上に深く形成しなくても済み、オン抵抗の増大を抑制することが可能となる。

#### 【 0 0 6 1 】

続いて、図 7 のように構成された本実施形態にかかる S i C 半導体装置の製造方法について、図 8 を参照して説明する。

#### 【 0 0 6 2 】

##### [ 図 8 ( a ) に示す工程 ]

まず、半導体基板として、S i C からなる n<sup>+</sup>型基板 4 1 の表面上に S i C からなる n<sup>-</sup>型ドリフト層 4 2 がエピタキシャル成長させられた、いわゆるエピ基板を用意する。

#### 【 0 0 6 3 】

##### [ 図 8 ( b ) に示す工程 ]

n<sup>-</sup>型ドリフト層 4 2 の表面にマスク材 4 9 を配置したのち、フォトリソグラフィによってマスク材 4 9 のうちの p 型ディープ層 4 5 および n<sup>-</sup>型領域 4 6 の形成予定位置を開口させる。そして、マスク材 4 9 を配置した状態で R I E などの異方性エッチングを行うことで、p 型ディープ層 4 5 および n<sup>-</sup>型領域 4 6 の形成予定位置にディープトレンチ 4 4 を形成する。40

#### 【 0 0 6 4 】

##### [ 図 8 ( c ) に示す工程 ]

マスク材 4 9 を除去したのち、図 2 ( c )、( d ) と同様の工程を行う。これにより、ディープトレンチ 4 4 内が p 型ディープ層 4 5 および n<sup>-</sup>型領域 4 6 によって埋め込まれる。

#### 【 0 0 6 5 】

##### [ 図 8 ( d ) に示す工程 ]

10

20

30

40

50

n型層43の表面上に形成されたp型ディープ層45を構成するp型SiC層を研削やCMPなどによって除去し、n型層43を露出させる。

#### 【0066】

この後の工程については図示しないが、n型層43やp型ディープ層45の表面上にショットキー電極47を形成する工程と、n<sup>+</sup>型基板41の裏面上にオーミック電極48を形成する工程を行うことで、図7に示す縦型JBSが備えられたSiC半導体装置が完成する。

#### 【0067】

以上説明したように、縦型JBSを備えるSiC半導体装置に対しても、p型ディープ層45およびn<sup>-</sup>型領域46を備える構造を適用することができる。

10

#### 【0068】

##### (他の実施形態)

本発明は上記した実施形態に限定されるものではなく、特許請求の範囲に記載した範囲内において適宜変更が可能である。

#### 【0069】

例えは、上記各実施形態では、n<sup>+</sup>型ソース領域4をエピタキシャル成長によって形成しているが、n<sup>+</sup>型ソース領域4についてはベース領域3の上層部に形成されれば良いため、イオン注入などの他の手法によって形成することもできる。

#### 【0070】

また、第2実施形態では、ベース領域3を高濃度ベース領域3aと低濃度ベース領域3bに分けたが、単一の不純物濃度で構成しても良い。また、不純物濃度を異ならせる構成では、高濃度ベース領域3aと低濃度ベース領域3bの境界部において不純物濃度が徐々に変化し、その境界部を挟んでp型不純物濃度が異なった高濃度ベース領域3aと低濃度ベース領域3bとが積層された形態でも良い。また、低濃度ベース領域3bについては、ノンドープ(つまり、ほとんどp型ドーパントがドープされていない)であるi型半導体によって構成されていても構わない。例えは、低濃度ベース領域3bのドープ量について、エピタキシャル成長時に雰囲気中に残留しているp型ドーパントがドープされる程度とすることができる。その場合、低濃度ベース領域3bでの高チャネル移動度化を更に実現することが可能となり、更なる低オン抵抗化が可能になる。

20

#### 【0071】

さらに、上記各実施形態では、裏面側が高不純物濃度の裏面層、表面側がそれよりも低不純物濃度なドリフト層とされた半導体基板として、n<sup>+</sup>型基板1の表面にn<sup>-</sup>型ドリフト層2を形成した構造を例に挙げて説明した。しかしながら、これは半導体基板の一例を示したに過ぎず、例えはn<sup>-</sup>型ドリフト層2にて構成される基板の裏面側にn型ドーパントをイオン注入すること、もしくはエピタキシャル成長によって裏面層を構成した半導体基板であっても良い。

30

#### 【0072】

また、上記第4実施形態では、第1実施形態の構造および製造方法と同様のp型ディープ層45およびn<sup>-</sup>型領域46を例に挙げて説明したが、第2実施形態およびその変形例と同様の製造方法、第3実施形態と同様の構造および製造方法を適用することもできる。

40

#### 【0073】

また、上記各実施形態では、第1導電型をn型、第2導電型をp型としたnチャネルタイプの縦型MOSFETを例に挙げて説明したが、各構成要素の導電型を反転させたpチャネルタイプの縦型MOSFETに対しても本発明を適用することができる。その場合、半導体基板の表面の面方位を(000-1)カーボン面とすることで、ディープトレンチの側面にはp型の制限層を優位にエピタキシャル成長させられ、ディープトレンチの底部にはn型のディープ層を優位にエピタキシャル成長させることができる。

#### 【0074】

さらに、上記各実施形態では、化合物半導体としてSiCを例に挙げ、ディープトレンチ内に第2導電型のディープ層をエピタキシャル成長させる一例として下地層となるn<sup>-</sup>

50

型ドリフト層2の上にp型ディープ層5を形成する場合を例に挙げて説明した。しかしながら、これも単なる一例を示したに過ぎない。すなわち、化合物半導体にて構成される第1導電型の下地層に対してディープトレンチを形成し、そのディープトレンチに第2導電型の化合物半導体にて構成されるディープ層をエピタキシャル成長する構造について、本発明を適用することができる。

## 【0075】

なお、結晶の方位を示す場合、本来ならば所望の数字の上にバー( - )を付すべきであるが、電子出願に基づく表現上の制限が存在するため、本明細書においては、所望の数字の前にバーを付すものとする。

## 【符号の説明】

## 【0076】

- |        |                       |

|--------|-----------------------|

| 1、4 1  | n <sup>+</sup> 型基板    |

| 2、4 2  | n <sup>-</sup> 型ドリフト層 |

| 3      | ベース領域                 |

| 4      | n <sup>+</sup> 型ソース領域 |

| 5、4 5  | p型ディープ層               |

| 6      | トレンチ                  |

| 8      | ゲート電極                 |

| 16、4 6 | n <sup>-</sup> 型領域    |

| 15、4 4 | ディープトレンチ              |

10

20

【図1】

【図2】

【図3】

【 図 4 】

【 四 5 】

【 四 6 】

【 図 7 】

【 四 8 】

---

フロントページの続き

| (51)Int.Cl. |       | F I                   |

|-------------|-------|-----------------------|

| H 0 1 L     | 21/20 | (2006.01)             |

|             |       | H 0 1 L 29/06 3 0 1 D |

|             |       | H 0 1 L 29/06 3 0 1 V |

|             |       | H 0 1 L 21/265 Z      |

|             |       | H 0 1 L 21/20         |

|             |       | H 0 1 L 29/78 6 5 2 C |

(72)発明者 秋葉 敦也

愛知県刈谷市昭和町1丁目1番地 株式会社デンソー内

(72)発明者 鈴木 克己

愛知県豊田市トヨタ町1番地 トヨタ自動車株式会社内

(72)発明者 青井 佐智子

愛知県長久手市横道41番地の1 株式会社豊田中央研究所内

審査官 恩田 和彦

(56)参考文献 特開2013-038308 (JP, A)

特開2014-236189 (JP, A)

特開2009-302091 (JP, A)

特開2013-145770 (JP, A)

(58)調査した分野(Int.Cl., DB名)

|         |             |

|---------|-------------|

| H 0 1 L | 2 9 / 7 8   |

| H 0 1 L | 2 1 / 2 0   |

| H 0 1 L | 2 1 / 2 6 5 |

| H 0 1 L | 2 1 / 3 3 6 |

| H 0 1 L | 2 9 / 0 6   |

| H 0 1 L | 2 9 / 1 2   |