(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7155103号

(P7155103)

(45)発行日 令和4年10月18日(2022.10.18)

(24)登録日 令和4年10月7日(2022.10.7)

(51)国際特許分類

|         |                 |     |         |       |         |

|---------|-----------------|-----|---------|-------|---------|

| G 0 6 F | 11/14 (2006.01) | F I | G 0 6 F | 11/14 | 6 1 0   |

| G 0 6 F | 12/00 (2006.01) |     | G 0 6 F | 12/00 | 5 7 1 A |

| G 0 6 F | 11/07 (2006.01) |     | G 0 6 F | 11/07 | 1 4 0 N |

|         |                 |     | G 0 6 F | 11/07 | 1 9 3   |

請求項の数 15 (全17頁)

|                   |                                  |          |                                                                                                                                                                                       |

|-------------------|----------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (21)出願番号          | 特願2019-501916(P2019-501916)      | (73)特許権者 | 591016172<br>アドバンスト・マイクロ・ディバイシズ<br>・インコーポレイテッド<br>A D V A N C E D M I C R O D E V I<br>C E S I N C O R P O R A T E D<br>アメリカ合衆国 9 5 0 5 4 カリフォル<br>ニア州、サンタクララ、オガスティ<br>ン ドライブ 2 4 8 5 |

| (86)(22)出願日       | 平成29年7月11日(2017.7.11)            | (74)代理人  | 100108833<br>弁理士 早川 裕司                                                                                                                                                                |

| (65)公表番号          | 特表2019-527424(P2019-527424<br>A) | (74)代理人  | 100111615<br>弁理士 佐野 良太                                                                                                                                                                |

| (43)公表日           | 令和1年9月26日(2019.9.26)             | (74)代理人  | 100162156<br>弁理士 村雨 圭介                                                                                                                                                                |

| (86)国際出願番号        | PCT/US2017/041559                | (72)発明者  | ジェームズ アール・マグロ<br>最終頁に続く                                                                                                                                                               |

| (87)国際公開番号        | WO2018/013584                    |          | 最終頁に続く                                                                                                                                                                                |

| (87)国際公開日         | 平成30年1月18日(2018.1.18)            |          |                                                                                                                                                                                       |

| 審査請求日             | 令和2年7月6日(2020.7.6)               |          |                                                                                                                                                                                       |

| (31)優先権主張番号       | 62/363,075                       |          |                                                                                                                                                                                       |

| (32)優先日           | 平成28年7月15日(2016.7.15)            |          |                                                                                                                                                                                       |

| (33)優先権主張国・地域又は機関 | 米国(US)                           |          |                                                                                                                                                                                       |

| (31)優先権主張番号       | 15/375,076                       |          |                                                                                                                                                                                       |

| (32)優先日           | 平成28年12月9日(2016.12.9)            |          |                                                                                                                                                                                       |

|                   | 最終頁に続く                           |          |                                                                                                                                                                                       |

(54)【発明の名称】 DDR メモリエラーリカバリ

## (57)【特許請求の範囲】

## 【請求項 1】

メモリアクセス要求を受信して記憶するコマンドキュー(520)と、

前記コマンドキューに接続され、メモリコマンドのシーケンスをメモリチャネル(130/140)に提供するアービタ(538)と、

前記メモリコマンドのシーケンスを前記メモリチャネル(130/140)に記憶し、

メモリが第1タイプである場合、前記メモリチャネル(130/140)からの応答を未

だ受信していないメモリアクセスコマンドを記憶し続け、前記メモリが第2タイプである

場合、所定の信号の受信に基づいてエラーが発生した可能性がある、以前に発行された連

続するメモリコマンドのシーケンスを記憶し続けるリプレイキュー(530)と、

10

を備えるメモリコントローラ(500)であって、

対応するメモリコマンドがエラーなく完了したことが応答によって示された場合、前記

リプレイキュー(530)は、さらなるアクションを行わずに、前記対応するメモリコマ

ンドを削除し、

エラーが応答によって示され、前記メモリチャネルが前記第1タイプのメモリを備える

場合、前記リプレイキュー(530)は、前記エラーが発生した前記対応するメモリコマ

ンドをリプレイし、前記メモリが前記第2タイプの場合、前記リプレイキューは、前記所

定の信号の受信に基づいて前記エラーが発生した可能性がある、以前に発行された連

続するメモリコマンドのシーケンスをリプレイする、

メモリコントローラ(500)。

**【請求項 2】**

前記対応するメモリコマンドのエラー訂正コード（ECC）を計算し、計算したECCを、前記メモリチャネル（130/140）から返されたECCと比較するために前記リプレイキュー（530）に接続されたECCチェックブロック（542）をさらに備える、請求項1のメモリコントローラ（500）。

**【請求項 3】**

メモリアクセス要求を受信し記憶するために前記コマンドキュー（520）に接続されたメモリインタフェースキュー（514）をさらに備え、

前記メモリインタフェースキュー（514）は、前記メモリチャネル（130/140）にディスパッチされたコマンドと、前記コマンドに応じて前記メモリチャネル（130/140）から受信した応答と、を提供するために前記リプレイキュー（530）に接続されている、

10

請求項1のメモリコントローラ（500）。

**【請求項 4】**

前記リプレイキュー（530）は、前記メモリインタフェースキュー（514）からの応答の受信に応じて、エラー訂正コードを計算し、前記エラー訂正コードを前記メモリチャネル（130/140）から受信したエラー訂正コードと比較することによって、前記応答にエラーが存在することを判別する、

請求項3のメモリコントローラ（500）。

**【請求項 5】**

前記リプレイキュー（530）は、前記メモリインタフェースキュー（514）からのエラーを含む応答の受信に応じて、前記対応するメモリコマンドと、前記対応するメモリコマンドの後に前記メモリインタフェースキュー（514）が前記メモリチャネル（130/140）に提供した追加のコマンドと、をリプレイする、

20

請求項3のメモリコントローラ（500）。

**【請求項 6】**

メモリアクセス要求を受信して記憶するコマンドキュー（520）と、

前記コマンドキュー（520）に接続され、メモリコマンドのシーケンスをメモリチャネル（130/140）に提供するアービタ（538）と、

前記コマンドキュー（520）に接続され、メモリアクセス要求を受信して記憶するメモリインタフェースキュー（514）と、

30

前記メモリインタフェースキュー（514）に接続され、前記メモリコマンドのシーケンスを前記メモリチャネル（130/140）に記憶し、メモリが第1タイプである場合、前記メモリチャネル（130/140）からの応答を未だ受信していないメモリアクセスコマンドを記憶し続け、前記メモリが第2タイプである場合、所定の信号の受信に基づいてエラーが発生した可能性がある、以前に発行された連続するメモリコマンドのシーケンスを記憶し続けるリプレイキュー（530）と、

を備えるメモリコントローラ（500）であって、

前記メモリコントローラ（500）は、エラーを検出しない限り通常状態（610）に留まり、前記メモリインタフェースキュー（514）は、前記通常状態において、前記アービタ（538）によって選択されたコマンドを前記コマンドキュー（520）から受信し続け、

40

前記メモリコントローラ（500）は、エラーと、前記メモリチャネルが前記第1タイプのメモリを備えることと、を検出したことに応じてリカバリ状態（630/640）に移行し、前記リプレイキュー（530）は、前記リカバリ状態において、前記エラーが発生した対応するメモリコマンドをリプレイし、前記メモリが前記第2タイプの場合、前記リプレイキューは、前記所定の信号の受信に基づいて前記エラーが発生した可能性がある、以前に発行された連続するコマンドのシーケンスをリプレイする、

メモリコントローラ（500）。

**【請求項 7】**

10

20

30

40

50

前記メモリコントローラ(500)は、前記リプレイキュー(530)が、メモリエラーを発生させた全てのメモリコマンドをさらなるエラーなしにリプレイするまで、前記リカバリ状態(630/640)に留まる、

請求項6のメモリコントローラ(500)。

【請求項8】

前記メモリコントローラ(500)は、コマンド及びアドレスエラーに応じてエラーリカバリ状態(640)に移行し、データエラーに応じてコマンドリプレイ状態(630)に移行する、

請求項6のメモリコントローラ(500)。

【請求項9】

前記メモリコントローラ(500)は、エラーが発生した可能性があるコマンドのリプレイに応じて、前記エラーリカバリ状態(640)から前記コマンドリプレイ状態(630)に移行し、

前記メモリコントローラ(500)は、全てのリプレイされたコマンドに対する応答をエラーなしに受信したことに応じて、前記コマンドリプレイ状態(630)から前記通常状態(610)に移行する、

請求項8のメモリコントローラ(500)。

【請求項10】

前記メモリコントローラ(500)は、エラーが発生した可能性があるコマンドのリプレイに応じて、前記エラーリカバリ状態(640)から前記コマンドリプレイ状態(630)に移行し、

前記メモリコントローラ(500)は、さらなるエラーに応じて、前記さらなるエラーがコマンド/アドレスエラーである場合に前記エラーリカバリ状態(640)に移行し、それ以外の場合に前記コマンドリプレイ状態(630)に移行する、

請求項8のメモリコントローラ(500)。

【請求項11】

前記メモリコントローラ(500)は、前記対応するメモリコマンドをリプレイして所定回数のエラーを受信したことに応じて、システムエラーを示す、

請求項7のメモリコントローラ(500)。

【請求項12】

メモリアクセス要求を提供するメモリアクセスエージェント(110/210/220)と、

メモリシステム(120)と、

請求項1~11の何れかのメモリコントローラ(290/500)と、

を備えるデータ処理システム(100)であって、

前記メモリコントローラ(290/500)は、前記メモリアクセスエージェント(110/210/220)及び前記メモリシステム(120)に接続されている、

データ処理システム(100)。

【請求項13】

メモリアクセス要求を受信して記憶することと、

記憶されたメモリアクセス要求からのメモリコマンドのシーケンスをメモリチャネル(130/140)に提供することと、

前記メモリコマンドのシーケンスを前記メモリチャネル(130/140)に記憶し、メモリが第1タイプである場合、前記メモリチャネル(130/140)からエラーなしの応答を未だ受信していないメモリコマンドを記憶し続け、前記メモリが第2タイプである場合、所定の信号の受信に基づいてエラーが発生した可能性がある、以前に発行された連続するメモリコマンドのシーケンスを記憶し続けることと、

前記メモリチャネル(130/140)から受信した応答にエラーが発生したか否かを検出することと、

メモリエラーが検出されなかったことに応じて通常状態(610)に留まり、前記通常

10

20

30

40

50

状態（610）の間、前記メモリが前記第1タイプである場合に、記憶されたメモリアクセス要求からコマンドを提供し続け、前記メモリが前記第2タイプである場合に、前記所定の信号の受信に基づいてエラーが発生した可能性がある、以前に発行された連続するメモリコマンドのシーケンスを提供し続けることと、

エラーの検出に応じてリカバリ状態（630/640）に移行し、前記リカバリ状態（630/640）の間、記憶されたメモリコマンドを、前記エラーが発生した対応するメモリコマンドからリプレイし始めることと、を含み、

前記リプレイすることは、前記メモリチャネルが前記第1タイプのメモリを備える場合に、前記エラーが発生した可能性がある前記対応するメモリコマンドをリプレイし、又は、前記メモリが前記第2タイプの場合に、前記所定の信号の受信に基づいて前記エラーが発生した可能性がある、以前に発行された連続するコマンドのシーケンスをリプレイすることを含む、

方法。

#### 【請求項14】

前記リカバリ状態（630/640）に移行する前に、少なくとも1つのメモリがパワー・ダウン状態から起動したという確認を待つことをさらに含む、

請求項13の方法。

#### 【請求項15】

メモリエラーを生じた全てのメモリコマンドがさらなるエラーなしにリプレイされるまで前記リカバリ状態（630/640）に留まることをさらに含む、

請求項13の方法。

#### 【発明の詳細な説明】

##### 【背景技術】

##### 【0001】

コンピュータシステムは、通常、安価で高密度のダイナミックランダムアクセスメモリ（DRAM）チップをメインメモリとして使用する。今日販売されている多くのDRAMチップは、半導体技術協会（JEDDEC：Joint Electron Devices Engineering Council）によって公表された様々なダブルデータレート（DDR）DRAM規格と互換性がある。DDR DRAMは、様々な低電力モードを設けることによって、高性能及び低電力動作の両方を提供する。

##### 【0002】

最新のDDRメモリコントローラは、保留中のメモリアクセス要求を記憶するためのキューを維持して、保留中のメモリアクセス要求を、生成又は記憶された順序から外れた順序で選択するのを可能にし、これによって効率を高める。例えば、メモリコントローラは、所定のメモリランクの同じ行への複数のメモリアクセス要求をキューから取り出し、これらをメモリシステムに連続的に発行することによって、現在の行をプリチャージして他の行をアクティブにするオーバーヘッドを回避することができる。

##### 【0003】

DDRメモリシステムは、例えばパリティビット、巡回冗長コード（CRC）、エラー検出コード（EDC）、又は、DDR DRAM内にデータと共に記憶される他のエラー訂正コード（ECC）等のように、エラー検出及びリカバリのための様々なメカニズムを含む。DDRメモリコントローラは、メモリアクセスを実行する場合に、記憶されたCRC又はECCビットを、メモリアクセスに伴って計算されたCRC又はECCビットと比較する。DDRメモリコントローラは、エラーの検出に応じて、可能であればエラーを訂正し、エラーをオペレーティングシステムに報告する。そして、オペレーティングシステムは、実行すべき是正措置を決定する。しかし、DRAMバスは、2400メガヘルツ（MHz）等の比較的高いクロックレートで動作し、クロックサイクルの両遷移でデータを転送する。データレートが高いため、DDRメモリバスは、偶発的なランダムエラー又はメモリバス上の「グリッヂ」の影響を受けやすい。既知のDDRメモリコントローラは、これらのエラーを検出及び訂正するメカニズムを有するが、このようなメカニズムは、オ

10

20

30

40

50

ペーリングシステムコールによって引き起こされるオーバーヘッドのためにシステムパフォーマンスを著しく低下させる。

【図面の簡単な説明】

【0004】

【図1】いくつかの実施形態による、データ処理システムのブロック図である。

【図2】図1のデータ処理システムでの使用に適したアクセラレーテッドプロセッシングユニット（APU：accelerated processing unit）のブロック図である。

【図3】いくつかの実施形態による、図2のAPUでの使用に適したメモリコントローラ及び関連する物理インタフェース（PHY）のブロック図である。

【図4】いくつかの実施形態による、図2のAPUでの使用に適した他のメモリコントローラ及び関連するPHYのブロック図である。

【図5】いくつかの実施形態による、メモリコントローラのブロック図である。

【図6】図5のメモリコントローラの有限状態マシンの動作に関連する状態図である。

【発明を実施するための形態】

【0005】

以下の説明では、異なる図面において同じ参照番号を使用して、類似又は同一の項目を示している。特に断りのない限り、「接続された」という単語及びこれに関連する動詞形は、当技術分野において既知の手段による直接接続及び間接的な電気接続の両方を含む。特に断りのない限り、直接接続の説明は、適切な形態の間接的な電気接続を使用する代替の実施形態をも意味している。

【0006】

一形態では、メモリコントローラは、コマンドキューと、アービタと、リプレイキューと、を含む。コマンドキューは、メモリアクセス要求を受信して記憶する。アービタは、メモリコマンドのシーケンスをメモリチャネルに提供するために、コマンドキューに接続されている。リプレイキューは、メモリコマンドのシーケンスをメモリチャネルに記憶し、メモリチャネルからの応答を未だ受信していないメモリアクセスコマンドを記憶し続ける。対応するメモリコマンドがエラーなく完了したことが応答によって示された場合、リプレイキューは、さらなるアクションを行わずに、対応するメモリコマンドを削除する。対応するメモリコマンドがエラーを伴って完了したことが応答によって示された場合、リプレイキューは、少なくとも当該対応するメモリコマンドをリプレイする。

【0007】

他の形態では、メモリコントローラは、コマンドキューと、アービタと、メモリインタフェースキューと、リプレイキューと、を含む。コマンドキューは、メモリアクセス要求を受信して記憶する。アービタは、メモリコマンドのシーケンスをメモリチャネルに提供するために、コマンドキューに接続されている。メモリインタフェースキューは、メモリアクセス要求を受信して記憶するために、コマンドキューに接続されている。リプレイキューは、メモリインタフェースキューに接続されており、メモリコマンドのシーケンスをメモリチャネルに記憶し、メモリチャネルからの応答を未だ受信していないメモリアクセスコマンドを記憶し続ける。メモリコントローラは、エラーを検出しない限り通常状態に留まり、メモリインタフェースキューは、通常状態において、アービタによって選択されたコマンドをコマンドキューから受信し続ける。メモリコントローラは、エラーの検出に応じてリカバリ状態に移行し、リプレイキューは、リカバリ状態において、少なくとも1つの対応するメモリコマンドをメモリインタフェースキューに送信することによって、少なくとも1つの対応するメモリコマンドをリプレイする。

【0008】

さらに他の形態では、データ処理システムは、メモリアクセスエージェントと、メモリシステムと、メモリコントローラと、を含む。メモリアクセスエージェントは、メモリアクセス要求を提供する。メモリコントローラは、メモリアクセスエージェント及びメモリシステムに接続されている。メモリコントローラは、コマンドキューと、アービタと、リプレイキューと、を含む。コマンドキューは、メモリアクセス要求を受信して記憶する。

10

20

30

40

50

アービタは、メモリコマンドのシーケンスをメモリシステムに提供するために、コマンドキューに接続されている。リプレイキューは、メモリコマンドのシーケンスをメモリチャネルに記憶し、メモリチャネルからの応答を未だ受信していないメモリアクセスコマンドを記憶し続ける。対応するメモリコマンドがエラーなく完了したことが応答によって示された場合、リプレイキューは、さらなるアクションを行わずに、対応するメモリコマンドを削除する。対応するメモリコマンドがエラーを伴って完了したことが応答によって示された場合、リプレイキューは、少なくとも当該対応するメモリコマンドをリプレイする。

#### 【 0 0 0 9 】

さらに他の形態では、方法は、メモリアクセス要求を受信して記憶することを含む。記憶されたメモリアクセス要求からのメモリコマンドのシーケンスがメモリチャネルに提供され、メモリチャネルからエラーなしの応答を未だ受信していないメモリコマンドが記憶され続ける。メモリエラーが発生したか否かは、メモリチャネルから受信した応答において検出される。メモリコントローラは、メモリエラーが検出されないことに応じて、通常状態に留まり、通常状態の間、記憶されたメモリアクセス要求の中からコマンドが提供され続ける。エラーの検出に応じてリカバリ状態に移行し、リカバリ状態の間、記憶されたメモリコマンドは、エラーが発生した対応するメモリコマンドからリプレイし始める。

10

#### 【 0 0 1 0 】

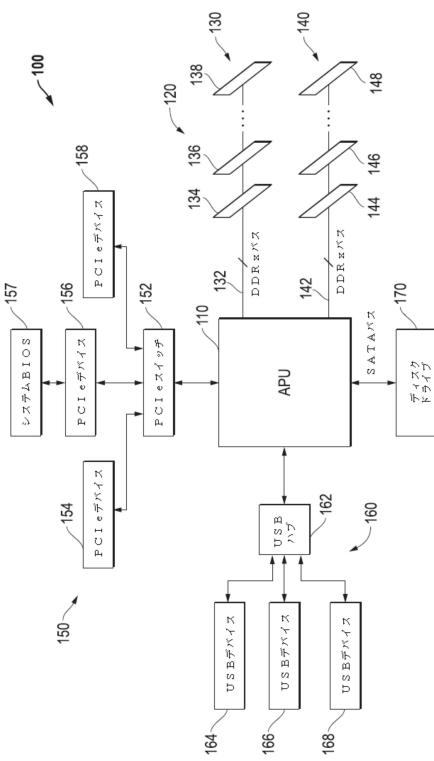

図1は、いくつかの実施形態による、データ処理システム100のブロック図である。データ処理システム100は、概して、アクセラレーテッドプロセッシングユニット(APU)の形態のデータプロセッサ110と、メモリシステム120と、周辺機器相互接続エクスプレス(PCIe)システム150と、ユニバーサルシリアルバス(USB)システム160と、ディスクドライブ170と、を含む。データプロセッサ110は、データ処理システム100の中央処理装置(CPU)として動作し、現代のコンピュータシステムにおいて有用な様々なバス及びインターフェースを提供する。これらのインターフェースには、2つのダブルデータレート(DDRx)メモリチャネルと、PCIeリンクへの接続用のPCIeルートコンプレックスと、USBネットワークへの接続用のUSBコントローラと、Serial Advanced Technology Attachment( SATA )大容量記憶デバイスへのインターフェースと、が含まれる。

20

#### 【 0 0 1 1 】

メモリシステム120は、メモリチャネル130と、メモリチャネル140と、を含む。メモリチャネル130は、本例において別々のランクに対応する代表的なDIMM134, 136, 138を含む、DDRxバス132に接続されたデュアルインラインメモリモジュール(DIMM)のセットを含む。同様に、メモリチャネル140は、代表的なDIMM144, 146, 148を含む、DDRxバス142に接続されたDIMMのセットを含む。

30

#### 【 0 0 1 2 】

PCIeシステム150は、データプロセッサ110内のPCIeルートコンプレックスに接続されたPCIeスイッチ152と、PCIeデバイス154と、PCIeデバイス156と、PCIeデバイス158と、を含む。PCIeデバイス156は、システム基本入出力システム(BIOS)メモリ157に接続されている。システムBIOSメモリ157は、例えば読み出し専用メモリ(ROM)、フラッシュEEPROM(electrically erasable programmable ROM)等の様々な不揮発性メモリタイプの何れかであってもよい。

40

#### 【 0 0 1 3 】

USBシステム160は、データプロセッサ110内のUSBマスタに接続されたUSBハブ162と、USBハブ162にそれぞれ接続された代表的なUSBデバイス164, 166, 168と、を含む。USBデバイス164, 166, 168は、例えばキーボード、マウス、フラッシュEEPROMポート等のデバイスであってもよい。

#### 【 0 0 1 4 】

ディスクドライブ170は、SATAバスを介してデータプロセッサ110に接続され

50

ており、オペレーティングシステム、アプリケーションプログラム、アプリケーションファイル等のための大容量ストレージを提供する。

【0015】

データ処理システム100は、メモリチャネル130及びメモリチャネル140を設けることによって、最新のコンピューティングアプリケーションでの使用に適している。各メモリチャネル130, 140は、例えばDDRバージョン4(DDR4)、低電力DDR4(LPDDR4)、グラフィックスDDRバージョン5(GDDR5)及び高帯域幅メモリ(HBM)等の最新のDDRメモリに接続されてもよいし、将来のメモリ技術に適応されてもよい。これらのメモリは、高いバス帯域幅及び高速動作を提供する。同時に、これらは、ラップトップコンピュータ等のパッテリ駆動アプリケーションの電力を節約する低電力モードも設けており、組み込み型サーマルモニタリングも提供する。

10

【0016】

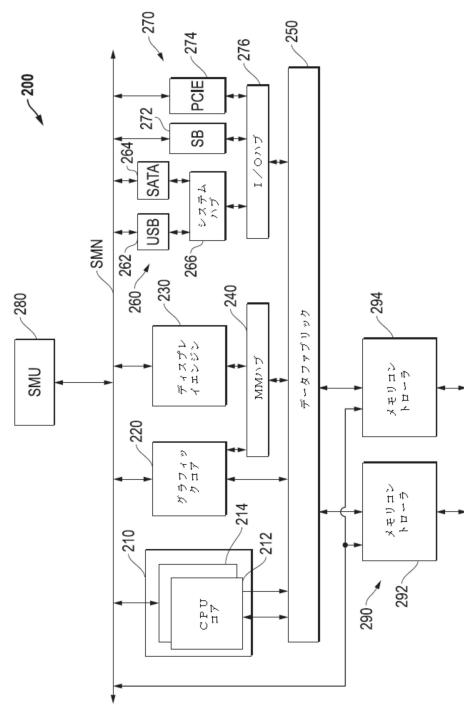

図2は、図1のデータ処理システム100での使用に適したAPU200のブロック図である。APU200は、概して、中央処理装置(CPU)コアコンプレックス210と、グラフィックスコア220と、ディスプレイエンジン230のセットと、メモリ管理ハブ240と、データファブリック250と、周辺コントローラ260のセットと、周辺バスコントローラ270のセットと、システム管理ユニット(SMU)280と、メモリコントローラ290のセットと、を含む。

【0017】

CPUコアコンプレックス210は、CPUコア212と、CPUコア214と、を含む。本例において、CPUコアコンプレックス210は2つのCPUコアを含むが、他の実施形態では、CPUコアコンプレックス210は任意の数のCPUコアを含んでもよい。各CPUコア212, 214は、制御ファブリックを形成するシステム管理ネットワーク(SMN)及びデータファブリック250に対して双方向に接続されており、メモリアクセス要求をデータファブリック250に提供することができる。各CPUコア212, 214は、單一コアであってもよいし、例えばキャッシュ等の特定のリソースを共有する2つ以上の单一コアを有するコアコンプレックスであってもよい。

20

【0018】

グラフィックスコア220は、例えば、頂点処理、フラグメント処理、シェーディング、テクスチャブレンド等のグラフィックス操作を、高度に統合された並列形式で実行することの可能な高性能グラフィックス処理ユニット(GPU)である。グラフィックスコア220は、SMN及びデータファブリック250に対して双方向に接続されており、メモリアクセス要求をデータファブリック250に提供することができる。これに関して、APU200は、CPUコアコンプレックス210及びグラフィックスコア220が同じメモリ空間を共有するユニファイドメモリアーキテクチャ、又は、CPUコアコンプレックス210及びグラフィックスコア220がメモリ空間の一部を共有するメモリアーキテクチャをサポートしてもよいが、グラフィックスコア220は、CPUコアコンプレックス210がアクセスできない専用のグラフィックスメモリを使用してもよい。

30

【0019】

ディスプレイエンジン230は、グラフィックスコア220によって生成されたオブジェクトをレンダリング及びラスタライズして、モニタに表示する。グラフィックスコア220及びディスプレイエンジン230は、メモリシステム120の適切なアドレスに一様に変換されるために共通のメモリ管理ハブ240に対して双方向に接続されており、メモリ管理ハブ240は、かかるメモリアクセスを生成し、メモリシステムから返された読出しデータを受信するために、データファブリック250に対して双方向に接続されている。

40

【0020】

データファブリック250は、任意のメモリアクセスエージェントとメモリコントローラ290との間でメモリアクセス要求及びメモリ応答をルーティングするためのクロスバースイッチを含む。また、データファブリック250は、システム構成に基づくメモリアクセスの宛先と、仮想接続毎のバッファとを判断するためのシステムメモリマップであつ

50

て、BIOSによって定義されたシステムメモリマップを含む。

【0021】

周辺コントローラ260は、USBコントローラ262と、SATAインターフェースコントローラ264と、を含み、これらの各々が、システムハブ266及びSMNバスに対して双方向に接続されている。これらの2つのコントローラは、APU200で使用可能な周辺コントローラの単なる例示である。

【0022】

周辺バスコントローラ270は、システムコントローラ（即ち「サウスブリッジ」（SB））272と、PCIeコントローラ274と、を含み、これらの各々が、入出力（I/O）ハブ276及びSMNバスに対して双方向に接続されている。また、I/Oハブ276は、システムハブ266及びデータファブリック250に対して双方向に接続されている。したがって、例えば、CPUコアは、データファブリック250がI/Oハブ276を介してルーティングするアクセスを通じて、USBコントローラ262、SATAインターフェースコントローラ264、SB272、又は、PCIeコントローラ274内のレジスタをプログラムすることができる。

10

【0023】

SMU280は、APU200上のリソースの動作を制御し、それらの間の通信を同期させるローカルコントローラである。SMU280は、APU200上の様々なプロセッサのパワーアップシーケンシングを管理し、リセット、イネーブル及び他の信号を介して複数のオフチップデバイスを制御する。SMU280は、APU200の各コンポーネントにクロック信号を提供するために、図2に示されていない1つ以上のクロック源（例えば位同期ループ（PLL）等）を含む。また、SMU280は、様々なプロセッサ及び他の機能ブロックの電力を管理し、CPUコア212, 214及びグラフィックスコア220から測定された電力消費値を受信して、適切な電力状態を判断してもよい。

20

【0024】

また、APU200は、様々なシステムモニタリング及び省電力機能を実装する。特に、1つのシステムモニタリング機能は、サーマルモニタリングである。例えば、SMU280は、APU200が高温になると、CPUコア212, 214及び/又はグラフィックスコア220の周波数及び電圧を低減させてもよい。APU200が非常に高温になった場合には、APU200が完全にシャットダウンされてもよい。サーマルイベントは、SMU280によって、外部センサからSMNバスを介して受信されてもよく、SMU280は、これに応じてクロック周波数及び/又は電源電圧を低下させてもよい。

30

【0025】

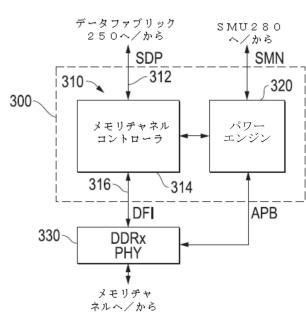

図3は、いくつかの実施形態による、図2のAPU200での使用に適したメモリコントローラ300及び関連する物理インターフェース（PHY）330のブロック図である。メモリコントローラ300は、メモリチャネル310と、パワーエンジン320と、を含む。メモリチャネル310は、ホストインターフェース312と、メモリチャネルコントローラ314と、物理インターフェース316と、を含む。ホストインターフェース312は、メモリチャネルコントローラ314を、スケーラブルデータポート（SDP）を介してデータファブリック250に双方向に接続する。物理インターフェース316は、メモリチャネルコントローラ314を、DDR-PHYインターフェース仕様（DFI）に準拠するバスを介してPHY330に双方向に接続する。パワーエンジン320は、SMNバスを介してSMU280に双方向に接続されており、APB（Advanced Peripheral Bus）を介してPHY330に双方向に接続されており、メモリチャネルコントローラ314にも双方向に接続されている。PHY330は、例えば図1のメモリチャネル130又はメモリチャネル140等のメモリチャネルに対する双方向接続を有する。メモリコントローラ300は、単一のメモリチャネルコントローラ314を使用した単一のメモリチャネル用のメモリコントローラの例示であり、以下にさらに説明するメモリチャネルコントローラ314の動作を制御するためのパワーエンジン320を有する。

40

【0026】

50

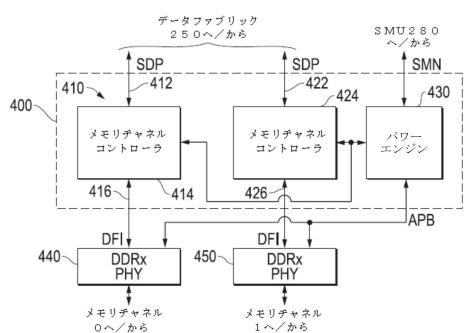

図4は、いくつかの実施形態による、図2のAPU200での使用に適した別のメモリコントローラ400及び関連するPHY440, 450のブロック図である。メモリコントローラ400は、メモリチャネル410, 420と、パワーエンジン430と、を含む。メモリチャネル410は、ホストインターフェース412と、メモリチャネルコントローラ414と、物理インターフェース416と、を含む。ホストインターフェース412は、メモリチャネルコントローラ414を、SDPを介してデータファブリック250に双方向に接続する。物理インターフェース416は、DFI仕様に準拠しており、メモリチャネルコントローラ414をPHY440に双方向に接続する。メモリチャネル420は、ホストインターフェース422と、メモリチャネルコントローラ424と、物理インターフェース426と、を含む。ホストインターフェース422は、メモリチャネルコントローラ424を、別のSDPを介してデータファブリック250に双方向に接続する。物理インターフェース426は、DFI仕様に準拠しており、メモリチャネルコントローラ424をPHY450に双方向に接続する。パワーエンジン430は、SMNバスを介してSMU280に双方向に接続されており、APBを介してPHY440, 450に双方向に接続されており、メモリチャネルコントローラ414, 424にも双方向に接続されている。PHY440は、例えば図1のメモリチャネル130等のメモリチャネルに対する双方向接続を有する。PHY450は、例えば図1のメモリチャネル140等のメモリチャネルに対する双方向接続を有する。メモリコントローラ400は、2つのメモリチャネルコントローラを有するメモリコントローラの例示であり、共有のパワーエンジン430を使用して、以下にさらに説明するように、メモリチャネルコントローラ414及びメモリチャネルコントローラ424の各々の動作を制御する。

#### 【0027】

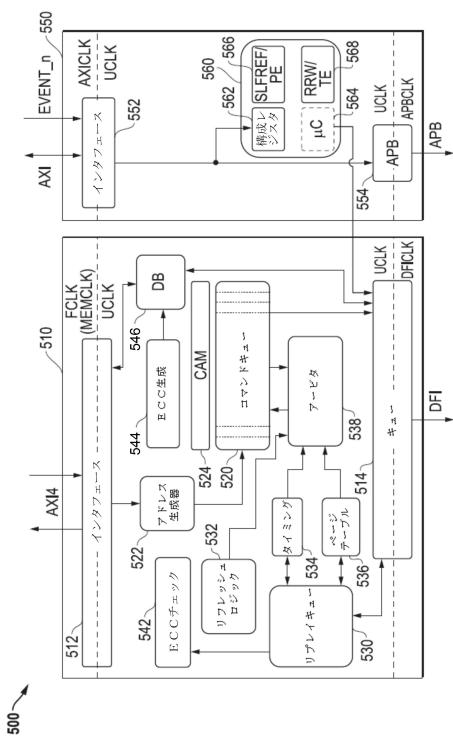

図5は、いくつかの実施形態による、メモリコントローラ500のブロック図である。メモリコントローラ500は、メモリチャネルコントローラ510と、電力コントローラ550と、を含む。メモリチャネルコントローラ510は、インターフェース512と、キュー514と、コマンドキュー520と、アドレス生成器522と、コンテンツアドレス可能メモリ(CAM)524と、リプレイキュー530と、リフレッシュロジックブロック532と、タイミングブロック534と、ページテーブル536と、アービタ538と、エラー訂正コード(ECC)チェックブロック542と、ECC生成ブロック544と、データバッファ(DB)546と、を含む。

#### 【0028】

インターフェース512は、外部バスを介したデータファブリック250との第1双方向接続と、出力と、を有する。メモリコントローラ500において、この外部バスは、「AXI4」として知られている、英国ケンブリッジのARM Holdings, PLCによって仕様化されたアドバンストエクステンシブルインターフェースバージョン4と互換性があるが、他の実施形態では、他のタイプのインターフェースであってもよい。インターフェース512は、FCLK(又はMEMCLK)ドメインとして知られる第1クロックドメインから、UCLKドメインとして知られるメモリコントローラ500の内部の第2クロックドメインへのメモリアクセス要求を変換する。同様に、キュー514は、UCLKドメインから、DFIインターフェースに関連するDFICLKドメインへのメモリアクセスを提供する。

#### 【0029】

アドレス生成器522は、データファブリック250からAXI4バスを介して受信したメモリアクセス要求のアドレスを復号化する。メモリアクセス要求は、正規化されたアドレスとして表わされる物理アドレス空間内のアクセスアドレスを含む。アドレス生成器522は、正規化されたアドレスを、メモリシステム120内の実際のメモリデバイスをアドレス指定し、関連するアクセスを効率的にスケジュールするのに使用可能なフォーマットに変換する。このフォーマットは、メモリアクセス要求を特定のランク、行アドレス、列アドレス、バンクアドレス及びバンクグループに関連付ける領域識別子を含む。システムB IOSは、起動時に、メモリシステム120内のメモリデバイスにクエリしてその

10

20

30

40

50

サイズ及び構成を判断し、アドレス生成器 522 に関連する構成レジスタのセットをプログラムする。アドレス生成器 522 は、構成レジスタに記憶された構成を使用して、正規化されたアドレスを適切なフォーマットに変換する。コマンドキュー 520 は、データ処理システム 100 内のメモリアクセスエージェント（例えば、CPU コア 212, 214 及びグラフィックスコア 220 等）から受信したメモリアクセス要求のキューである。コマンドキュー 520 は、アドレス生成器 522 によって復号化されたアドレスフィールドと、アクセスタイプ及びサービス品質（QoS）識別子を含むメモリアクセスをアービタ 538 が効率的に選択するのを可能にする他のアドレス情報と、を記憶する。CAM 524 は、例えばライトアフターライト（WAW）及びリードアフターライト（RAW）順序付けルール等の順序付けルールを実施するための情報を含む。

10

#### 【0030】

リプレイキュー 530 は、例えば、アドレス及びコマンドパリティ応答、DRAM の書き込み巡回冗長検査（CRC）応答、又は、GDDR5 DRAM の書き込み及び読み出し CRC 応答等の応答を待つアービタ 538 によって取り出されたメモリアクセスを記憶するための一時的なキューである。リプレイキュー 530 は、ECC チェックプロック 542 にアクセスして、返された ECC が正しいか否か又はエラーを示しているか否かを判別する。リプレイキュー 530 は、何れかのサイクルでパリティ又は CRC エラーの場合にアクセスがリプレイされるのを可能にする。

#### 【0031】

リフレッシュロジック 532 は、メモリアクセスエージェントから受信した通常の読み出し及び書き込みメモリアクセス要求とは別に生成される様々なパワーダウン、リフレッシュ、及び、終端抵抗（ZQ）較正サイクルのためのステートマシンを含む。例えば、メモリランクがプリチャージパワーダウンにある場合には、リフレッシュサイクルを実行するために定期的に起動されなければならない。リフレッシュロジック 532 は、オートリフレッシュコマンドを定期的に生成して、DRAM チップ内のメモリセルのチャージオフストレージキャパシタのリークによって生じるデータエラーを防止する。さらに、リフレッシュロジック 532 は、ZQ を定期的に較正して、システム内の熱変化によるオンダイ終端抵抗のミスマッチを防止する。また、リフレッシュロジック 532 は、どの場合に DRAM デバイスを別のパワーダウンモードにするのかを決定する。

20

#### 【0032】

アービタ 538 は、コマンドキュー 520 に双方向に接続されており、メモリチャネルコントローラ 510 の中心部分である。アービタ 538 は、メモリバスの利用を改善するために、インテリジェントなアクセススケジューリングによって効率を改善する。アービタ 538 は、タイミングプロック 534 を使用して、コマンドキュー 520 内の特定のアクセスの発行に適しているか否かを DRAM タイミングパラメータに基づいて判断することによって、適切なタイミング関係を実施する。例えば、各 DRAM は、同じバンクへの起動コマンド間の最小指定時間（「t<sub>RC</sub>」として知られる）を有する。タイミングプロック 534 は、リプレイキュー 530 に双方向に接続されており、このタイミングパラメータ及び JEDDEC 仕様で指定された他のタイミングパラメータに基づいて適格性を判断するカウンタのセットを維持する。ページテーブル 536 は、リプレイキュー 530 に双方向に接続されており、アービタ 538 のメモリチャネルの各バンク及びランクのアクティブページに関する状態情報を維持する。

30

#### 【0033】

ECC 生成プロック 544 は、インタフェース 512 から受信した書き込みメモリアクセス要求に応じて、書き込みデータに従って ECC を計算する。DB 546 は、受信したメモリアクセス要求の書き込みデータ及び ECC を記憶する。アービタ 538 が、メモリチャネルにディスパッチするための対応する書き込みアクセスを選ぶと、DB 546 は、結合した書き込みデータ / ECC をキュー 514 に出力する。

40

#### 【0034】

電力コントローラ 550 は、アドバンストエクテンシブルインタフェースバージョン 1

50

(AXI)へのインターフェース552と、APBインターフェース554と、パワーエンジン560と、を含む。インターフェース552は、SMNへの第1双方向接続であって、図5に別に示された「EVENT\_n」と付されたイベント信号を受信するための入力を含む第1双方向接続と、出力と、を含む。APBインターフェース554は、インターフェース552の出力に接続された入力と、APBを介してPHYに接続するための出力と、を有する。パワーエンジン560は、インターフェース552の出力に接続された入力と、キューリーフィルタ514の入力に接続された出力と、を有する。パワーエンジン560は、構成レジスタ562のセットと、マイクロコントローラ(μC)564と、セルフリフレッシュコントローラ(SLFREF/PE)566と、信頼性のある読み出し/書き込みトレーニングエンジン(RRW/TE)568と、を含む。構成レジスタ562は、AXIバスを介してプログラムされており、メモリコントローラ500内の様々なブロックの動作を制御するための構成情報を記憶する。したがって、構成レジスタ562は、図5に詳細に示されていないこれらのブロックに接続された出力を有する。セルフリフレッシュコントローラ566は、リフレッシュロジック532によるリフレッシュの自動生成に加えて、リフレッシュの手動生成を可能にするエンジンである。信頼性のある読み出し/書き込みトレーニングエンジン568は、DDRインターフェース読み出しレイテンシトレーニング及びループバックテスト等の目的のために、連続的なメモリアクセスストリームをメモリ又はI/Oデバイスに提供する。

#### 【0035】

メモリチャネルコントローラ510は、関連するメモリチャネルへのディスパッチのためにメモリアクセスを選択することを可能にする回路を含む。アドレス生成器522は、所望のアービトレーションの決定を行うために、アドレス情報を、メモリシステム内のランク、行アドレス、列アドレス、バンクアドレス及びバンクグループを含むプリデコードされた情報に復号化し、コマンドキュー520は、プリデコードされた情報を記憶する。構成レジスタ562は、受信したアドレス情報をアドレス生成器522がどのように復号するのかを決定するために、構成情報を記憶する。アービタ538は、復号化されたアドレス情報と、タイミングブロック534によって示されたタイミング適格性情報と、ページテーブル536によって示されたアクティブページ情報と、を使用して、例えばQoS要件等の他の基準を遵守しながらメモリアクセスを効率的にスケジューリングする。例えば、アービタ538は、メモリページを変更するのに必要なプリチャージ及びアクティブ化コマンドのオーバーヘッドを避けるために、オープンページへのアクセスを優先し、或るバンクへのオーバーヘッドアクセスを、他のバンクへの読み出し及び書き込みアクセスをインタリープすることによって隠す。特に、アービタ538は、通常動作中に、異なるページを選択する前にプリチャージされる必要があるまで、異なるバンク内のページオープンを維持することを決定してもよい。

#### 【0036】

アービタ538は、タイミングブロック534を使用して、保留中のアクセスのタイミング適格性を判別し、次に、効率性及び公平性の両方を保証する基準のセットに基づいて、コマンドキュー520から適格なアクセスを選択する。アービタ538は、効率性及び公平性の両方を保証する2つのメカニズムをサポートする。第1に、アービタ538は、コマンドキュー520に記憶されたメモリアクセス要求の属性と、書き込みが許可されているのと同時に読み出しが許可される条件を制御するためのプログラム可能な閾値と、を調べることによって読み出し/書き込みトランザクション管理を実行して効率性及び公平性の両方を保証する。第2に、アービタ538は、特定のタイプのアクセスのストリークがメモリバスを無期限に保持するのを許可しないように保証するストリークカウンタを含む。これらの2つのメカニズムについて説明する。

#### 【0037】

##### (DDRメモリエラーリカバリ)

上述したように、リブレイキュー530は、アドレス及びコマンドパリティ応答、DDR4DRAMの書き込み巡回冗長検査(CRC)応答、又は、GDDR5DRAMの書

10

20

30

40

50

き込み及び読み出し C R C 応答等の応答を待っているアービタ 5 3 8 によって選択されたメモリアクセスを記憶する一時的なキューである。リプレイキュー 5 3 0 は、E C C チェックブロック 5 4 2 にアクセスして、返された E C C が正しいかどうか又はエラーを示しているかどうかを判別する。リプレイキュー 5 3 0 は、これらのサイクルのうち 1 つのサイクルにパリティ又は C R C エラーがあった場合に、アクセスがリプレイされることを可能にする。また、リプレイキュー 5 3 0 は、現在の D D R D R A M で利用可能なエラー報告メカニズムを利用して、リプレイに関する決定を行う。メモリエラーが通常一時的であって、メモリチャネルが直ぐにリカバリすると仮定することによって、リプレイキュー 5 3 0 は、冗長で破壊的なリカバリシーケンスを回避するための適切なバックアップ及びリプレイメカニズムを提供する。

10

#### 【 0 0 3 8 】

いくつかのデバイスは、転送時のデータ保護をサポートする（例えば、エラー検出及び訂正（E D C）を伴う G D D R 5 読み出し及び書き込みデータ転送、書き込み C R C によって保護された D D R 4 書き込みデータ転送等）。G D D R 5 デバイスは、C R C データを転送するための単方向 E D C バスを提供する。これにより、要求が読み出しか書き込みかにかかわらず、E D C 値がデバイスからコントローラに常に伝えられる。G D D R 5 の読み出し応答データの転送中に、E D C バンドルが、パラメータ  $t_{c r c r l}$  に基づいて、応答データと共に又は応答データの直後に返される。書き込みデータの転送中、E D C バンドルが、G D D R 5 デバイスが書き込みデータを受信した後に（受信した書き込みデータから E D C 値が計算されるため）返される。読み出し時に、メモリコントローラ 5 0 0 は、受信した読み出しデータ応答から E D C 値を計算し、E D C 値を、その読み出しから受信した E D C データと比較する。書き込み時に、メモリコントローラ 5 0 0 は、予想 E D C 値を計算し、書き込みデータサイクル後に G D D R 5 から返された E D C パケットと後で比較するために、計算した予想 E D C 値をメモリコントローラ 5 0 0 に一時的に記憶する。予想書き込みデータ E D C 値は、メモリコントローラ 5 0 0 内の E D C キューロジック（E D C Q）に記憶される。

20

#### 【 0 0 3 9 】

メモリコントローラ 5 0 0 は、レイテンシを短縮するために「早期応答」をサポートし、リプレイキュー 5 3 0 は、E D C 応答が返される時間に対して「早期」に早期応答をメモリチャネルに返す。この「早期応答」サポートは、E D C の結果が「不良」に戻った場合に応答が「キャンセル」されることを要求する。メモリコントローラ 5 0 0 は、E D C の結果が不良に戻った場合に、「早期応答」パケット及び「応答キャンセル」をメモリチャネルに応答する。E D C が「良好」と返された場合、さらなる措置が不要となる。読み出し要求又は書き込み要求が失敗すると、リプレイキュー 5 3 0 は、サイクル要求の再試行を実行する。書き込み要求は、発行時にメモリチャネルに確認応答される。書き込みが失敗した場合、リプレイキュー 5 3 0 は、メモリチャネルとは無関係にコマンドを再試行し、書き込みデータの順序を維持する。

30

#### 【 0 0 4 0 】

D D R 4 デバイスは、書き込みコマンドでの C R C チェックのみをサポートする。C R C 情報は、最新の 2 ビット時間の間に書き込みデータと共に送信される。よって、G D D R 5 の E D C とは異なり、C R C 情報が D D R 4 デバイスでチェックされ、デバイスは、エラー検出時に A L E R T # 信号をアサートする。A L E R T # 信号はオープンドレインであり、D R A M M E M C L K 又は任意の内部コントローラクロックと非同期であるとみなされ、これにより同期を必要とすることから、連続するバーストのシーケンスにおいてエラーを引き起こした特定の書き込みトランザクションを識別するメモリコントローラ 5 0 0 の能力が制限され、メモリコントローラ 5 0 0 は、以前に発行された様々な書き込みコマンドをリプレイして、失敗した書き込みのリプレイを確実にする。G D D R 5 及び D D R 4 の両方のメモリに対して、リプレイキュー 5 3 0 は、書き込み及び読み出しトランザクションをリプレイし、失敗したサイクルが正常に完了するまで、コマンドキュー 5 2 0 から発行されている新たなトランザクションを停止する。

40

50

## 【0041】

リプレイキュー530の具体的な実施形態及び動作について説明する。

## 【0042】

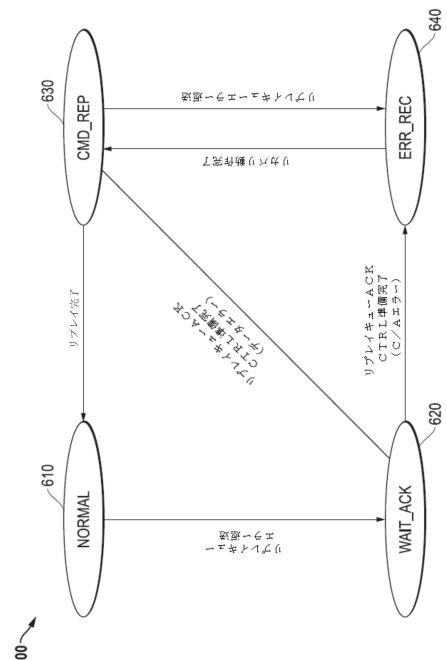

図6は、図5のメモリコントローラ500の有限状態マシン600の動作に関する状態図である。有限状態マシン600は、NORMAL状態610と、「WAIT\_ACK」と付された待機確認状態620と、「CMD\_RESP」と付されたコマンドリプレイ状態630と、「ERR\_REC」と付されたエラーリカバリ状態640と、によって定義される。メモリコントローラ500は、DRAMエラーが検出されない限り、NORMAL状態610に留まる。この状態の間、アービタ538は、メモリシステムへのメモリアクセスコマンドの順序付けの制御を保持し、その通常の優先順位ルールに従ってコマンドキュー520からコマンドを選択することによって、通常のトラフィックを送信する。メモリコントローラ500は、リプレイキュー530から返されたDRAMエラーを検出すると、NORMAL状態610を離れ、一時的にWAIT\_ACK状態620に移行する。次に、キュー514は、アービタ538によって選択されたコマンドの受け付けを停止し、選択されたリカバリフェーズにおいてリプレイキュー530からのコマンドの受信を開始する。リプレイキュー530は、メモリアクセスコマンドの発行を制御し、DRAMタイプ及びエラータイプに基づいてリカバリシーケンスを実行する。例えば、DDR4システムにおけるコマンド/アドレスエラーの場合、メモリコントローラ500は、ERR\_REC状態640に移行し、コマンドが正しく提供されたことを保証するために、リプレイキュー530が最後のリカバリコマンドを送信した後の待機時間までこの状態に留まる。このとき、メモリコントローラ500は、CMD\_RESP状態630に移行する。CMD\_RESP状態630において、リプレイキュー530は、エラーが発生した可能性のある1つ以上のコマンドをリプレイする。CMD\_RESP状態630は、エラーが発生した可能性がある最後のコマンドをリプレイキュー530が送信したときに終了する。

10

20

30

## 【0043】

例えば、典型的なシーケンスは以下のように進行する。

## 【0044】

1) 起動時に、有限状態マシン600は、NORMAL状態610で開始する。

## 【0045】

2) DDR4システムの場合、リプレイキュー530はエラー(ALERT\_n=0)をサンプリングし、GDDR5システムの場合、リプレイキュー530がキュー514から返されたCRCエラーを受信すると、リプレイキュー530は、キュー514からの制御を要求し、有限状態マシン600は、WAIT\_ACK状態620に移行する。

30

## 【0046】

3) アービタ538及びキュー514は、リカバリ要求を確認する前に任意のDRAMをパワーダウンモードから起動して、リプレイキュー530が制御している間、動的なパワーダウンを無効にする必要がある。

## 【0047】

4) キュー514が要求を確認すると、状態マシン600は、ERR\_REC状態640に移行してコマンド/アドレスエラーリカバリシーケンスを実行するか、CMD\_RESP状態630に直接移行する。

40

## 【0048】

5) コマンド/アドレスエラーリカバリが完了すると、状態マシン600はCMD\_RESP状態630に移行する。

## 【0049】

6) CMD\_RESP状態630において、エラートランザクションがリプレイされ、メモリシステムに再送される。さらなるエラーが発生した場合、状態マシン600は、CMD\_RESP状態630に留まるか、コマンド/アドレスエラーの場合にはERR\_REC状態640に移行する。

## 【0050】

50

7) リプレイが完了してクールダウン時間が経過すると、リプレイキュー 530 は、トランザクションの制御をアービタ 538 に解放し、有限状態マシン 600 は、NORMA L 状態 610 に戻り、メモリコントローラ 500 は、再び通常のコマンドを提供する用意を整える。メモリコントローラ 500 がメモリコマンドをリプレイし、所定の回数だけエラーを受信した場合、システムエラーを示す。エラーが繰り返し発生するということは、メモリバス上の一時的な状態ではなく、実際のシステム障害を示しているので、オペレーティングシステムによって他の措置を取る必要がある。

#### 【 0051 】

図 5 のメモリコントローラは、ハードウェア及びソフトウェアの様々な組み合わせによって実装されてもよい。例えば、ハードウェア回路は、プライオリティエンコーダ、有限ステートマシン、プログラマブルロジックアレイ (PLA) 等を含んでもよい。例えば、アービタ 538 は、保留中のコマンドの相対的なタイミング適格性を評価するために、記憶されたプログラム命令を実行するマイクロコントローラを用いて実装することができる。この場合、いくつかの命令は、マイクロコントローラによって実行されるために、非一時的なコンピュータメモリ又はコンピュータ可読記憶媒体に記憶されてもよい。様々な実施形態では、非一時的なコンピュータ可読記憶媒体は、磁気若しくは光ディスク記憶デバイス、例えばフラッシュメモリ等のソリッドステート記憶デバイス、又は、他の不揮発性メモリデバイスを含む。非一時的なコンピュータ可読記憶媒体に記憶されたコンピュータ可読命令は、ソースコード、アセンブリ言語コード、オブジェクトコード、又は、1つ以上のプロセッサによって解釈及び／若しくは実行可能な他の命令フォーマットであってもよい。

10

#### 【 0052 】

図 5 のメモリコントローラ又はその一部（例えば、リプレイキュー 530）は、プログラムによって読み出され、集積回路を製造するために直接的若しくは間接的に使用されるデータベース又は他のデータ構造の形態のコンピュータアクセス可能なデータ構造によって記述されてもよいし表現されてもよい。例えば、このデータ構造は、例えば Verilog 又は VHDL 等の高水準設計言語 (HDL) におけるハードウェア機能の動作レベル記述であってもよいし、レジスタ転送レベル (RTL) 記述であってもよい。記述は、ゲートのリストを含むネットリストを合成ライブラリから生成するために当該記述を合成し得る合成ツールによって読み出されてもよい。ネットリストは、集積回路を含むハードウェアの機能を表すゲートのセットを含む。そして、ネットリストを配置及びルーティングして、マスクに適用される幾何学的形状を記述するデータセットを生成してもよい。マスクは、集積回路を製造するために様々な半導体製造工程で使用されてもよい。或いは、コンピュータアクセス可能な記憶媒体上のデータベースは、所望により、ネットリスト（合成ライブラリ有り若しくは無し）又はデータセットであってもよいし、グラフィックデータシステム (GDS) II データであってもよい。

20

30

#### 【 0053 】

特定の実施形態について説明してきたが、これらの実施形態に対する様々な変更が当業者には明らかであろう。例えば、メモリチャネルコントローラ 510 及び／又は電力コントローラ 550 の内部アーキテクチャは、様々な実施形態において変更することができる。メモリコントローラ 500 は、DDR × メモリ以外の他のタイプのメモリ（例えば、高帯域幅メモリ (HBM)、RAM バス DRAM (RDRAM) 等）にインターフェースすることができる。図示した実施形態は、別々のDIMM に対応する各ランクのメモリを示したが、他の実施形態では、各DIMM は複数のランクをサポートすることができる。

40

#### 【 0054 】

したがって、添付の特許請求の範囲によって、開示された実施形態の範囲に含まれる、開示された実施形態の全ての変更を包含することが意図される。

50

【図面】

【図 1】

【 図 2 】

【 3 】

〔 4 〕

【図 5】

【図 6】

---

フロントページの続き

(33)優先権主張国・地域又は機関

米国(US)

アメリカ合衆国 7 8 7 3 5 テキサス州、オースティン、サウスウェスト パークウェイ 7 1 7 1

(72)発明者 ルイファ ベン

アメリカ合衆国 9 5 0 5 4 カリフォルニア州、サンタ クララ、オーガスティン ドライブ 2 4 8 5

(72)発明者 アンソニー アサロ

カナダ国 L 3 T 7 X 6 オンタリオ州、マーカム、1 コマース バリー ドライブ イースト

(72)発明者 ケダーナス バラクリシュナン

アメリカ合衆国 7 8 7 3 5 テキサス州、オースティン、サウスウェスト パークウェイ 7 1 7 1

(72)発明者 スコット ピー. マーフィ

アメリカ合衆国 9 5 0 5 4 カリフォルニア州、サンタ クララ、オーガスティン ドライブ 2 4 8 5

(72)発明者 ユビン ヤオ

中華人民共和国 2 0 1 2 0 3 シャンハイ、プードン ディストリクト、チャンドン ロード 1 3

8 7 番、チャンジヤン ハイテック パーク、リバー フロント ハーバー ビルディング # 4 8

審査官 金田 孝之

(56)参考文献 特表 2 0 0 9 - 5 2 7 8 1 9 ( J P , A )

米国特許第 0 8 3 6 5 0 1 5 ( U S , B 1 )

米国特許出願公開第 2 0 1 1 / 0 0 4 0 9 2 4 ( U S , A 1 )

特開 2 0 1 6 - 0 7 6 0 7 6 ( J P , A )

(58)調査した分野 (Int.Cl. , DB名)

G 0 6 F 1 1 / 1 4

G 0 6 F 1 1 / 0 7

G 0 6 F 1 2 / 0 0

G 1 1 C 2 9 / 5 2