(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第4236722号

(P4236722)

(45) 発行日 平成21年3月11日(2009.3.11)

(24) 登録日 平成20年12月26日(2008.12.26)

(51) Int.Cl.

F 1

H01L 29/78 (2006.01)

H01L 29/78 301H

H01L 21/8234 (2006.01)

H01L 27/08 102B

H01L 27/088 (2006.01)

H01L 29/78 301C

請求項の数 3 (全 16 頁)

(21) 出願番号

特願平10-39560

(22) 出願日

平成10年2月5日(1998.2.5)

(65) 公開番号

特開平11-224946

(43) 公開日

平成11年8月17日(1999.8.17)

審査請求日

平成17年1月24日(2005.1.24)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 宮永 昭治

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 久保 伸夫

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 大嶋 洋一

最終頁に続く

(54) 【発明の名称】 半導体装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の導電型の半導体基板上にゲイト絶縁膜及びゲイト電極を積層形成する第1の工程と、

前記ゲイト電極上に、前記ゲイト電極を横切り且つマスクの幅が少なくともソースノードレインの接合深さの2倍以上のストライプ状のレジストマスクを形成する第2の工程と、

前記ゲイト電極及び前記レジストマスクをマスクとして、前記半導体基板の鉛直方向に對して7~83°の斜め方向から第1の導電型不純物を添加する第3の工程と、

前記ゲイト電極をマスクとして自己整合的に垂直に第2の導電型不純物を添加することで、ソース領域、ドレイン領域及びチャネル形成領域を形成する第4の工程と、

10

を有し、

前記第1の導電型不純物は前記第2の導電型不純物とは逆導電型であり、

前記第1の導電型不純物を含む不純物領域は前記半導体基板よりも前記第1の導電型不純物を高濃度に含んだ領域であり、

前記第3及び前記第4の工程によって、前記チャネル形成領域の前記ドレイン領域との接合部には、当該接合部に沿って前記ゲイト電極の下部にもぐり込むようにして局所的に前記第1の導電型不純物を含む不純物領域が形成されることを特徴とする半導体装置の作製方法。

## 【請求項 2】

第1の導電型の半導体基板上にゲイト絶縁膜及びゲイト電極を積層形成する第1の工程

20

と、

前記ゲイト電極上に、前記ゲイト電極を横切り且つマスクの幅が少なくともソース／ドレインの接合深さの2倍以上のストライプ状のレジストマスクを形成する第2の工程と、

前記ゲイト電極及び前記レジストマスクをマスクとして、前記半導体基板の鉛直方向に對して7～83°の斜め方向から第1の導電型不純物を添加する第3の工程と、

前記ゲイト電極をマスクとして自己整合的に垂直に第2の導電型不純物を添加することで、ソース領域、ドレイン領域及びチャネル形成領域を形成する第4の工程と、

を有し、

前記第1の導電型不純物は前記第2の導電型不純物とは逆導電型であり、

前記第3及び前記第4の工程によって、前記チャネル形成領域の前記ドレイン領域との接合部及び前記チャネル形成領域の前記ソース領域との接合部に沿って、前記ゲイト電極の下部にもぐり込むようにして局所的に前記第1の導電型不純物を含む不純物領域が形成され、

前記第1の導電型不純物を含む不純物領域は前記チャネル形成領域の前記ドレイン領域との接合部に沿って形成された第1の不純物領域と、前記チャネル形成領域の前記ソース領域との接合部に沿って形成された第2の不純物領域とを有し、

前記第1の不純物領域と前記第2の不純物領域とは、チャネル幅方向の同一の位置において互いに向かい合うように形成され、

前記第1の導電型不純物を含む不純物領域は前記半導体基板よりも前記第1の導電型不純物を高濃度に含んだ領域であることを特徴する半導体装置の作製方法。

### 【請求項3】

請求項1又は2において、

前記チャネル形成領域の中心を通りチャネル幅方向に切った断面には、前記第1の導電型不純物を含む不純物領域が形成されていないことを特徴とする半導体装置の作製方法。

### 【発明の詳細な説明】

#### 【0001】

#### 【発明が属する技術分野】

本願発明は、単結晶シリコン基板を利用して形成された半導体装置、特に絶縁ゲイト型電界効果トランジスタ(MOSFETまたはIGFETと呼ばれる)の構成に関する。特に、チャネル長が0.3μm以下(代表的には0.05～0.2μm)の微細素子を作製する場合において効果を發揮する技術である。

#### 【0002】

また、本願発明はMOSFETを集積化して構成されたIC、VLSI、ULSIなどの様々な半導体回路に応用することが可能である。

#### 【0003】

#### 【従来の技術】

MOSFETは、ゲート電圧によって、ゲート直下の半導体(シリコン)界面の電位を変化させ、ソース・ドレイン間の電子流、或いは、正孔流をオン・オフ制御する。

#### 【0004】

ところがトランジスタのチャネル長を短くしていくと、ソースとドレイン近傍の空間電荷領域(空乏層ともいう)が接するようになる。このとき、ゲートに近い半導体界面の電位はゲート電位で制御可能であるが、ゲートから深い部分の電位はゲート電圧を下げてもドレイン電圧の影響を受けて高いままである。

#### 【0005】

即ち、トランジスタをオフにするためにゲート電圧を0Vにしても、半導体基板の電位の高い部分(空間電荷領域の広がった部分)を通って漏れ電流が流れてしまう。これが、短チャネル効果と呼ばれるもので、S値(サブスレッシュホールド係数)の増加やしきい値電圧の低下といった現象として現れる。

#### 【0006】

短チャネル効果の程度の大きい現象として、電流が流れっぱなしとなるパンチスルーが生

10

20

30

40

50

じる。MOSFETの微細化へのメリットは、低電圧化・高速化にある。この成功のためには、短チャネル効果の抑制、及び、オン時の抵抗低減が鍵となる。

#### 【0007】

短チャネル効果を抑制しながら、MOSFETを微細化する目安として、1974年にDennardによって提案されたスケーリング法がある。この方法から短チャネル効果を抑制したままゲート長を短くしていくためには、(1)ゲート絶縁膜を薄くする、(2)ソース／ドレイン接合深さを浅くする、(3)空間電荷領域幅(空乏層幅)を抑える、といった手段が有効である。

#### 【0008】

(1)については、現行3nmが限界である。(2)に関してもイオンドーピング装置の工夫やレーザードーピングといった検討が行われているが、ディープサブミクロンサイズ以下では様々な問題を残している。10

#### 【0009】

(3)の方法としては、まず考えられるのがチャネル形成領域の濃度を高めること、即ち、チャネルドープである。しかし、 $0.18 \mu\text{m}$ ルールといった微細寸法でMOSFETを形成するには、 $1 \times 10^{18} \text{atoms/cm}^3$ 程度の不純物を添加する必要があり、オン電流を大幅に低下させる原因となってしまう。

#### 【0010】

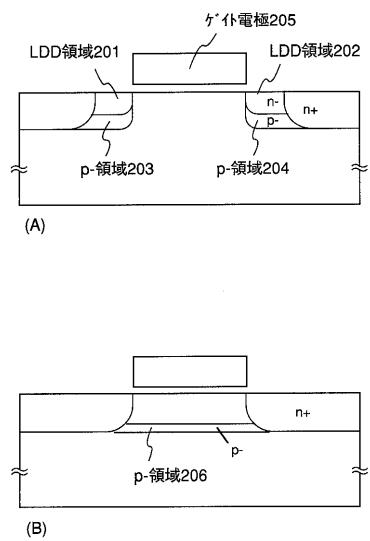

その他の方法として、図2(A)に示す様なDouble Implanted LDDと呼ばれる方法が挙げられる。これはイオン打ち込みによってn⁻領域(LDD領域)201、202の直下またはそれを囲む様にやや弱めのP型(p⁻)領域203、204を設けた構造である。特にLDD領域を囲む様にして設けた場合にはポケット構造と呼ばれることもある。20

#### 【0011】

さらに、チャネル部の基板内部に基板より高濃度のP型領域(p⁻領域)206を形成するパンチスルーストッパー構造(図2(B))も提案されている。これらの方針は、全て基板深さ方向、或いは、ゲート(チャネル)長方向のエンジニアリングである。

#### 【0012】

##### 【発明が解決しようとする課題】

ところが、従来例の図2(A)、(B)に述べた様な構造ではいくつかの問題もある。図2(A)の構造は、ドレイン領域(LDD領域も含めて)の直下のみにp⁻領域が設けられた構造であるため、あまり短チャネル効果の抑制効果を期待できない。30

#### 【0013】

また、ポケット構造と呼ばれるタイプではキャリア(電子を例にとる)はドレイン領域に到達する前に必ずp⁻領域を通過することになるので、移動度の低下を招くといった問題が生じる。

#### 【0014】

また、図2(B)の構造は通常ゲート電極を形成した後に、スルードーピングによって深さ方向の濃度制御を行う。従って、濃度分布の制御が非常に困難である上、半導体層界面の結晶性を崩してしまうため、移動度を高めるためには好ましい手段とは言えない。

#### 【0015】

そこで本願発明では、プロセス制御性の高い構造で効果的に短チャネル効果を抑制しうるMOSFETを提供することを課題とする。

#### 【0016】

##### 【課題を解決するための手段】

本願発明は、短チャネル効果を抑制するための不純物領域をチャネル幅方向に対して局所的(一か所乃至数カ所)に施すという構成を基本とする。即ち、チャネル幅方向にソース／ドレインとは逆導電型の高抵抗領域を形成することにより、ドレインからの空間電荷領域(空乏層)の広がりを抑制し、且つ、高オン電流を得ることが可能となる。

#### 【0017】

従来の深さ、或いは、チャネル長方向のエンジニアリングに比べて、チャネル幅方向の工50

ンジニアリングの優位性は、次の点にある。

(1) プロセス制御性が容易である。

(2) 空間電荷領域抑制領域とチャネル形成領域とが分離しているので、反転層（チャネル領域）内における不純物濃度を低くすることが可能である（オン時の抵抗が小さくなりキャリア移動度が向上する）。

#### 【0018】

なお、空間電荷領域抑制領域（空乏層抑制領域）とは、ドレイン側空乏層のソース側への広がりを抑えるために形成された不純物領域を指している。本発明者らは空乏層を抑止する効果があたかも空乏層をピン止めする様に捉えられることから、この領域をピニング領域（pinning region）と呼んでいる。

10

#### 【0019】

##### 【発明の実施の形態】

本願発明の実施の形態について、以下に示す実施例でもって詳細な説明を行うこととする。

#### 【0020】

##### 〔実施例1〕

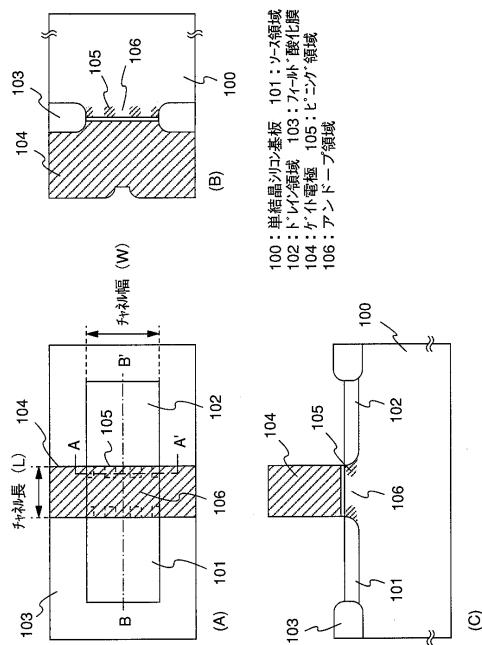

本願発明のMOSFETの構成の一部（ソース／ドレイン電極は省略している）を図1に示す。図1(A)は上面図であり、図1(B)は図1(A)をA-A'で切った断面、図1(C)は図1(A)をB-B'で切った断面である。

20

#### 【0021】

図1(A)、(B)、(C)において、101はソース領域、102はドレイン領域、103はフィールド酸化膜、104はゲイト電極である。そして、ゲイト電極104の下にもぐり込む様にして形成された不純物領域105が、本願発明の特徴であるピニング領域である。

#### 【0022】

なお、本明細書中ではソース領域101、ドレイン領域102しか記載していないが、この中にはLDD領域やオフセット領域などの高抵抗領域も含めるものとする。重要なのはピニング領域をチャネル形成領域とドレイン領域との境界（接合部）付近に設けて空乏層の広がりを抑制するという構成であり、LDD構造やオフセット構造の有無は問題ではない。

30

#### 【0023】

また、本明細書中においてチャネル形成領域とは、ゲイト電極の下に位置する半導体領域を指す。ピニング領域も半導体表面ではチャネルが形成されうるので広義な意味ではチャネル形成領域に含まれる。

#### 【0024】

そこで本明細書ではチャネル形成領域をピニング領域（不純物領域）105と、不純物が添加されなかった領域（以下、アンドープ領域と呼ぶ）106とに区別して記載する。即ち、アンドープ領域とはシリコン基板濃度またはウェル濃度がそのまま残った領域と考えてよい。

40

#### 【0025】

ところで、ピニング領域105はソース／ドレイン領域とは逆導電型の不純物を添加して形成される。空乏層はPN接合部の濃度差によって幅が決定するため、チャネル形成領域よりも濃度の高い領域を形成することで空乏層の広がりを抑えることができる。

#### 【0026】

例えば、Nチャネル型MOSFETを形成するにあたってチャネル形成領域としてP型シリコン基板そのものを利用する場合、ピニング領域は基板よりも強いP型の不純物領域で構成すれば良い。

#### 【0027】

具体的には、チャネル形成領域がP型ならば13族から選ばれた元素（代表的にはボロン）を添加して形成する。また、チャネル形成領域がN型ならば15族から選ばれた元素（

50

代表的にはリン又は砒素)を添加すれば良い。勿論、チャネル形成領域はシリコン基板を利用するのであっても、不純物添加で形成したウェルを利用するのであっても良い。

#### 【0028】

なお、上述の13族又は15族から選ばれた元素は単結晶シリコンのエネルギー・バンドをシフトさせることでキャリア(電子または正孔)にとってのエネルギー障壁を形成している。そういう意味で、ピニング領域はエネルギー・バンドをシフトさせてなる領域と呼ぶこともできる。

#### 【0029】

不純物を添加しないアンドープ領域とピニング領域との間にはバンドギャップがシフトした分に相当するエネルギー差が生まれる。この電位的な障壁はしきい値電圧の相違といった形で現れる。

10

#### 【0030】

この障壁の高さは実効キャリア濃度(N型、P型の相対的な濃度差)によって変化するが、不純物元素の添加濃度で調節できる。本願発明では、添加する不純物元素の濃度を $1 \times 10^{17} \sim 5 \times 10^{19}$ atoms/cm<sup>3</sup>(好ましくは $1 \times 10^{18} \sim 5 \times 10^{19}$ atoms/cm<sup>3</sup>)の範囲で調節する。

#### 【0031】

また、ピニング領域105は、最も典型的には図1(A)に示す様にチャネル形成領域(ゲート電極104直下の半導体領域)とソースまたはドレイン領域101、102との接合部に配列して形成される。即ち、接合部付近ではピニング領域105とアンドープ領域106とが交互に並んで配置される。

20

#### 【0032】

この様子を断面で見ると、図1(B)に示す様になる。この様に、キャリアが優先的に移動する領域(アンドープ領域106)と空乏層を抑制する領域(ピニング領域105)とが分離されているため、キャリア移動度を低下させることなくTFTを動作させることが可能である。

#### 【0033】

なお、図1(B)において100で示されるのは単結晶シリコン基板である。これはP型であってもN型であっても良い。本願発明では上述の特殊な構造によって短チャネル効果が抑制されるので、チャネル形成領域としてシリコン基板を用いる場合には、基板濃度を $1 \times 10^{16} \sim 5 \times 10^{17}$ atoms/cm<sup>3</sup>(好ましくは $5 \times 10^{16} \sim 1 \times 10^{17}$ atoms/cm<sup>3</sup>)と低めに抑えることができる。

30

#### 【0034】

また、ピニング領域は少なくともドレイン側の接合部に設けられていれば短チャネル効果の抑制効果を得ることができる。ソース/ドレインが特定される様な回路に用いられるMOSFETの場合、ドレイン側のみにピニング領域を設ける様な構成として良い。

#### 【0035】

ところで、前述の様なピニング領域105はゲート電極104を形成した後、レジストマスクによって所定位置を隠した状態で不純物添加工程を行うことで形成することができる。この時、ゲート電極104に対して斜め方向から不純物を添加することで、図1(C)に示す様にゲート電極104の下にもぐり込む様な形状のピニング領域105を形成することが可能となる。チャネル形成領域とドレイン領域102との接合部付近に配列して形成されるピニング領域は、チャネル形成領域とソース領域101との接合部付近には達しない。つまりピニング領域は、チャネル形成領域とドレイン領域との接合部付近、及びチャネル形成領域とソース領域との接合部付近それぞれに配列して形成され、互いに分離して形成される。

40

#### 【0036】

この斜めからの角度はシリコン基板の鉛直方向に対して $7 \sim 83^\circ$ (好ましくは $43 \pm 3^\circ$ )で行うことが望ましい。 $0 \sim 7^\circ$ ではチャネリングを起こして不純物が深く打ち込まれ過ぎるので好ましくない。また、 $83 \sim 90^\circ$ では角度が浅すぎてゲート電極の下に不

50

純物を添加することが困難である。

**【 0 0 3 7 】**

本実施例ではシリコン基板の面方位が(100)面であるため結晶学的には45°([110]方向を意味する)の時にチャネリングを起こして最も深くまで打ち込まれる。しかし本発明者らがシミュレーションによって計算した結果では、43°が最も好ましい角度であった。そのため、本願発明を実施するには43±3°とすることが望ましいと言える。

**【 0 0 3 8 】**

また、その際、ピニング領域105の形成深さはソース／ドレイン領域の接合深さと同程度とすることが望ましい。従って、ピニング領域の形成深さは0.02～0.3μm(好ましくは0.05～0.1μm)となる様に調節する。10

**【 0 0 3 9 】**

なお、ピニング領域105の形成は非常に微細な加工技術を要する。レジストパターンを形成してイオンインプランテーション法等で不純物を打ち込む方法を用いる場合、非常に精密なフォトリソグラフィ技術が必要である。また、パターン形成時に電子描画を用いることも有効である。さらに、FIB(Focused Ion Beam)法を用いてマスクレスで不純物を添加することも可能である。

**【 0 0 4 0 】**

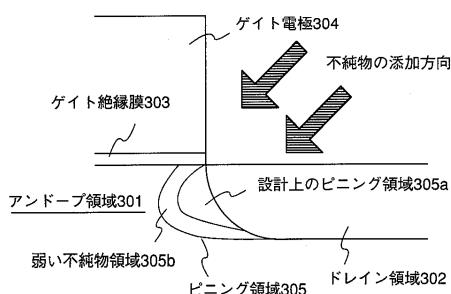

また、不純物を斜め方向から添加してピニング領域を形成すると、図3に示す様な形状でピニング領域が形成される。図3において、301はアンドープ領域、302はドレイン領域、303はゲイト絶縁膜、304はゲイト電極、305はピニング領域である。ピニング領域305の一部はチャネル形成領域とドレイン領域302との接合部に接している。20

**【 0 0 4 1 】**

斜めから不純物が打ち込まれることで、ピニング領域305はゲイト電極304の下にも形成される。この時、ピニング領域305を形成する際に不純物の散乱が起こるため、実際には設計上のピニング領域305aの周囲に散乱によって形成される弱い不純物領域305bを考慮する必要がある(実際にはもっと連続的に複雑な分布を示すがここでは簡略化して示す)。

**【 0 0 4 2 】**

この弱い不純物領域305bは半導体表面(チャネルが形成される部分)にまで到達してしまうが、散乱によって回り込んだ不純物しか存在しないので実効キャリア濃度としては $1 \times 10^{17} \sim 5 \times 10^{17} \text{ atoms/cm}^3$ 程度である。30

**【 0 0 4 3 】**

即ち、従来の0.2μmルールのMOSFETではチャネル形成領域の実効キャリア濃度が $1 \times 10^{18} \text{ atoms/cm}^3$ 程度が必要であることを鑑みれば、十分にチャネル形成領域として機能しうる領域であることが判る。また、従来のチャネルドープを施した構造よりも実効キャリア濃度の低い領域をキャリア(電子または正孔)が通過する分、高いオン電流を得ることができる。

**【 0 0 4 4 】**

この傾向は弱い不純物領域305bの不純物濃度をイオン打ち込み条件によって低く抑えることでより顕著になる。この様に、本願発明ではゲイト電極直下の半導体表面は実質的に全てチャネル形成領域と見なして良い。40

**【 0 0 4 5 】**

さらに、図1(A)、(B)に示す様にピニング領域の間にはスリット状にアンドープな領域が存在するので、キャリアは優先的にそこを流れてドレイン領域に到達すると考えられる。

**【 0 0 4 6 】**

即ち、従来例で述べたポケット構造はp+領域がキャリアの移動を妨げていたのに対し、本願発明ではキャリアの通り道となる領域が残されているので、オン電流が低下するとい50

った問題がない。

**【0047】**

以上の様に、本願発明のMOSFETはピニング領域によって短チャネル効果を抑制すると同時に、ピニング領域とは分離して形成されたアンドープ領域がソース・ドレイン間を結ぶので高い動作速度を維持することができる。

**【0048】**

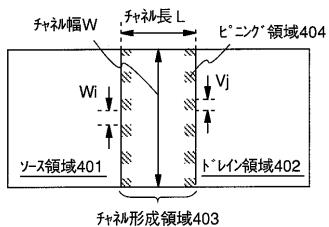

ここでチャネル長およびチャネル幅の定義を図4を用いて行う。図4においてソース領域401とドレイン領域402との間の距離をチャネル長( $L$ )と定義する。本願発明はこの長さが $0.3\mu m$ 以下、典型的には $0.05\sim 0.2\mu m$ である微細なMOSFETに対して有効である。また、このチャネル長に沿った方向をチャネル長方向と呼ぶ。

10

**【0049】**

また、チャネル長方向と直交する方向におけるチャネル形成領域403の長さをチャネル幅( $W$ )とする。なお、このチャネル幅に沿った方向をチャネル幅方向と呼ぶ。

**【0050】**

チャネル幅はどの様な回路として用いるかによって異なるが、チャネル長と同程度とする場合もあれば数百 $\mu m$ と広くする場合もある。例えば、モノリシック型LCDのバッファ回路やサンプリング回路の様に大電流を流す必要のある回路は数百 $\mu m$ のチャネル幅を必要とする。

**【0051】**

また、任意のピニング領域404の形成幅をピニング幅( $v_j$ )と定義する。ピニング幅に特に上限はないが、チャネル幅の $1/3$ 以下でないとドレイン接合部のアンドープ領域が狭くなるので好ましくない。また、下限はフォトリソグラフィ技術のパターン加工精度の限界が下限となる。本願発明の場合、 $0.05\sim 0.3\mu m$ の範囲が実質的なピニング幅と言えるであろう。ピニング領域404のチャネル長方向の長さは、チャネル長( $L$ )よりも短い。

20

**【0052】**

さらに、隣接する個々のピニング領域間の間隔( $w_i$ )は少なくともソース／ドレインの接合深さの2倍以上として設計する必要がある。

**【0053】**

ピニング領域の深さはソース／ドレインの接合深さ程度であるので、不純物散乱によって接合深さと同程度だけ横方向へのパターン広がりが起こる。即ち、ピニング領域のパターン設計段階で接合深さの少なくとも2倍以上の間隔をあけておかないと、隣接するピニング領域が接触してしまい、アンドープ領域を塞いでしまい好ましくない。従って、本願発明では $w_i$ は $0.04\sim 0.6\mu m$ (好ましくは $0.1\sim 0.2\mu m$ )とすれば良い。

30

**【0054】**

勿論、ピニング領域間の間隔( $w_i$ )が広すぎてもピニング効果が弱まってしまうため、適切な間隔とすることが重要である。本発明者らは $w_i$ の上限をその基板濃度で形成しうる最大空乏層幅と考えている。

**【0055】**

即ち、アンドープ領域の実効キャリア濃度が $1\times 10^{16}atoms/cm^3$ 程度ならば形成されるドレイン側の空乏層の幅は $0.3\mu m$ 程度であるので、 $w_i$ を $0.3\mu m$ 以下とすることが好ましい。また、同様に実効キャリア濃度が $1\times 10^{17}atoms/cm^3$ 程度ならば $w_i$ は $0.1\mu m$ 以下とすれば良い。この様にアンドープ領域の実効キャリア濃度(基板濃度またはウェル濃度)が決まれば最大空乏層幅の決まるので、それを踏まえて設計を行えば良い。

40

**【0056】**

以上の様に、本願発明では短チャネル効果を抑制するためのエンジニアリングをチャネル幅方向に対して施している。基本的にはゲート電極に対して斜め方向から不純物を添加するだけなのでプロセス的には簡易である。

**【0057】**

従来の技術と異なる点は、不純物を添加する際にチャネル幅方向に局在的に不純物領域(

50

ピニング領域)を設けることで、MOSFETのモビリティを低下させることなく、短チャネル効果を抑制することができる点にある。

#### 【0058】

ここで本願発明のMOSFETの効果を以下にまとめる。まず、第1の効果は短チャネル効果(特にパンチスルーハイドロゲン接合部に設けられたピニング領域によって効果的に抑制される点である。そのため、スケーリング則に従って微細化を進めても空乏層の広がりによる悪影響を防ぐことができる。

#### 【0059】

第2の効果は、MOSFETが動作している時のキャリア(電子または正孔)の移動は、アンドープ領域で優先的に行われるため非常に高速動作が可能な点である。アンドープ領域は基板濃度またはウェル濃度がそのまま残っている領域であるため、実効キャリア濃度は少なくとも $5 \times 10^{17} \text{ atoms/cm}^3$ 以下(好ましくは $1 \times 10^{17} \text{ atoms/cm}^3$ 以下)である。

10

#### 【0060】

なお、例えばP型シリコン基板に対して $1 \times 10^{17} \text{ atoms/cm}^3$ の実効キャリア濃度を持つN型ウェルを形成する場合、P型シリコン基板のボロン濃度が $1 \times 10^{16} \text{ atoms/cm}^3$ 程度であれば、N型ウェルには $1 \times 10^{16} \text{ atoms/cm}^3$ 程度のボロンと $1 \sim 2 \times 10^{17} \text{ atoms/cm}^3$ 程度のリンが含まれることになる。しかしながら、不純物散乱が問題となるのはその不純物濃度が $1 \times 10^{17} \text{ atoms/cm}^3$ 以上となった場合であるため、N型ウェル内のボロンは無視して良いと言える。

#### 【0061】

20

また、従来のチャネルドープを用いた構造では $1 \times 10^{18} \text{ atoms/cm}^3$ 程度の不純物がチャネル形成領域全面に添加されるので、不純物散乱の影響は非常に大きくなってしまう。その点、本願発明ではキャリアが優先的に通過する領域(アンドープ領域)の実効キャリア濃度は少なくとも $5 \times 10^{17} \text{ atoms/cm}^3$ 以下(好ましくは $1 \times 10^{17} \text{ atoms/cm}^3$ 以下)であるため、不純物散乱の影響はあっても極めて小さいという利点を持つ。

#### 【0062】

第3の効果は、ソース領域側にピニング領域を設けた構成ではソース側のピニング領域が正孔の引き出し線として利用できる点にある。MOSFETの動作時、ドレイン接合部のインパクトイオン化現象によって発生した正孔は基板へと流れ寄生バイポーラを導通させる恐れがある。

30

#### 【0063】

しかしながら、ソース側に設けられたピニング領域によってチャネル下部に移動してきた正孔をソース領域へと引き抜くことができるため、寄生バイポーラの導通によるソース-ドレイン間耐圧の低下を防ぐことができる。

#### 【0064】

以上の様に、本願発明のMOSFETは短チャネル効果を抑制したまま素子サイズを微細化することができるため、高い信頼性を維持したまま、高い動作性能を実現することができる。さらに、キャリアの移動する領域に余計な不純物を打ち込む必要がないので、高いモビリティ(電界効果移動度)を有するMOSFETを実現しうる。

#### 【0065】

40

なお、本実施例ではNチャネル型MOSFETを例にとって説明を行ったが、同様にしてPチャネル型MOSFETに適用することもできる。その場合、ピニング領域に打ち込む不純物の導電型を変更すれば良いだけである。

#### 【0066】

#### 〔実施例2〕

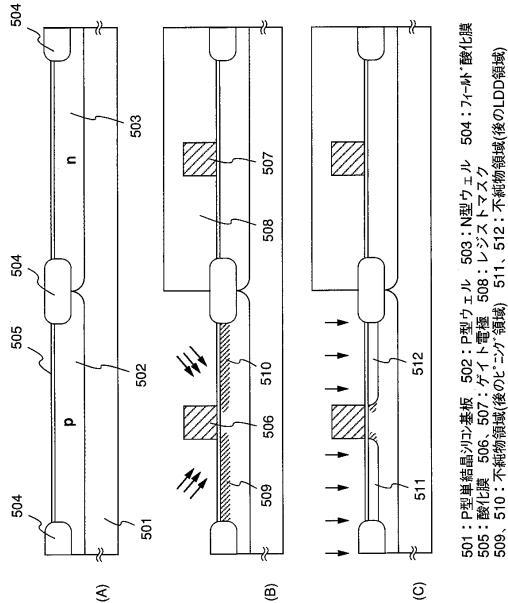

本実施例では、実施例1に示した構造を有する本願発明のMOSFETを利用してCMOS回路を構成した場合の例について図5を用いて説明する。

#### 【0067】

まず、P型単結晶シリコン基板501を準備し、不純物イオン注入によってP型ウェル502、N型ウェル503を形成する。この様な構成はいわゆるツインタブ構造であり、ウ

50

エル濃度は実施例 1 に示した様に  $1 \times 10^{16} \sim 5 \times 10^{17}$  atoms/cm<sup>3</sup> の範囲で形成される。

**【 0 0 6 8 】**

次に、公知の L O C O S 法などにより選択酸化を行い、フィールド酸化膜 5 0 4 を形成した後、熱酸化工程によってシリコン表面に 30nm 厚の酸化膜（後のゲイト絶縁膜）5 0 5 を形成する。（図 5（A））

**【 0 0 6 9 】**

次に、ゲイト電極 5 0 6、5 0 7 を形成する。本実施例ではゲイト電極を構成する材料として導電性を有するシリコン膜を用いるが、他にもタンタル、クロム、タンクスチル、モリブデン等の導電膜を用いることができる。なお、本実施例ではゲイト電極幅を 0.18 μm とする。

10

**【 0 0 7 0 】**

ゲイト電極を形成したら、後に P チャネル型 M O S F E T となる領域（図面向かって右側）をレジストマスク 5 0 8 で覆い、その状態で斜め方向から 13 族から選ばれた元素（代表的にはボロン）を添加する。

**【 0 0 7 1 】**

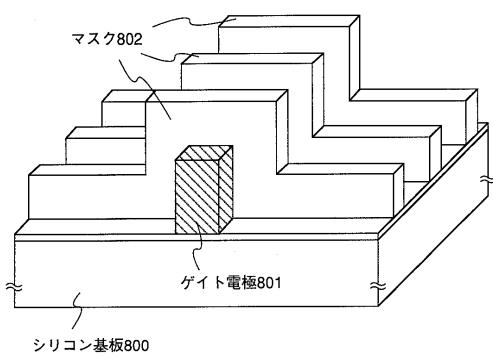

また、N チャネル型 M O S F E T となる領域（図面向かって左側）に対しても、ピニング領域を形成するためのマスクをレジストマスク 5 0 8 と同時に形成する。この様子を図 8 に示す。図 8 において、8 0 0 はシリコン基板、8 0 1 はゲイト電極である。

**【 0 0 7 2 】**

この時、ゲイト電極 8 0 1 を横切る様にしてストライプ状にレジストマスク 8 0 2 を形成する。即ち、マスク 8 0 2 で隠された部分がアンドープ領域となり、露出した部分（ただしゲイト電極 8 0 1 の下の部分）がピニング領域となる。

20

**【 0 0 7 3 】**

なお、ここで形成される不純物領域は非常に狭い範囲に打ち込まれることになるのでできるだけ不純物散乱の影響を受けない様な装置や条件を用いて添加することが望ましい。

**【 0 0 7 4 】**

そこで本実施例では、イオンインプランテーション法（イオン注入法）によりボロンを  $1 \times 10^{18}$  atoms/cm<sup>3</sup> の濃度で添加する。また、注入ガスは B F<sub>2</sub>、加速電圧は 30keV、ドーズ量は  $1 \times 10^{13}$  atoms/cm<sup>2</sup> とする。そして、シリコン基板に対して 30° の角度でイオンが注入される様に調節する。

30

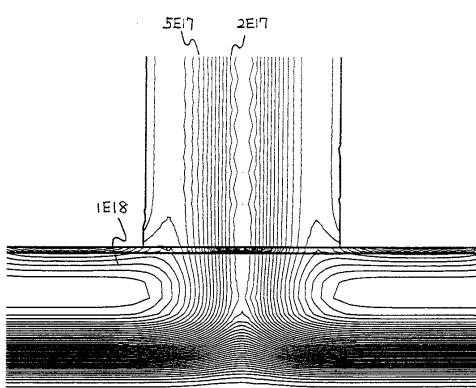

**【 0 0 7 5 】**

この様な条件はシミュレーションによって予め決定することができる。本発明者らによるシミュレーション結果では、本実施例の条件に従えば図 10 に示した様なプロファイルで不純物が添加されることが確認されている。

**【 0 0 7 6 】**

こうして後にピニング領域となる不純物領域 5 0 9、5 1 0 が形成される。実際にはこれらの領域 5 0 9、5 1 0 の先端部分（ゲイト電極の下にもぐり込んだ部分）のみがピニング領域として機能する。（図 5（B））

**【 0 0 7 7 】**

次に、今度はシリコン基板に対して垂直に 15 族から選ばれた不純物元素を添加する。本実施例では不純物として砒素を用い、 $5 \times 10^{18} \sim 1 \times 10^{19}$  atoms/cm<sup>3</sup> となる様に添加条件を調節する。ここでは 20 ~ 40nm 程度の浅い接合を形成するためにイオンプランテーション法、プラズマドーピング法、レーザードーピング法のいずれかの手段を用いる。

40

**【 0 0 7 8 】**

こうして形成される不純物領域 5 1 1、5 1 2 の一部は後に N チャネル型 M O S F E T の L D D (Lightly doped drain) 領域として機能する。（図 5（C））

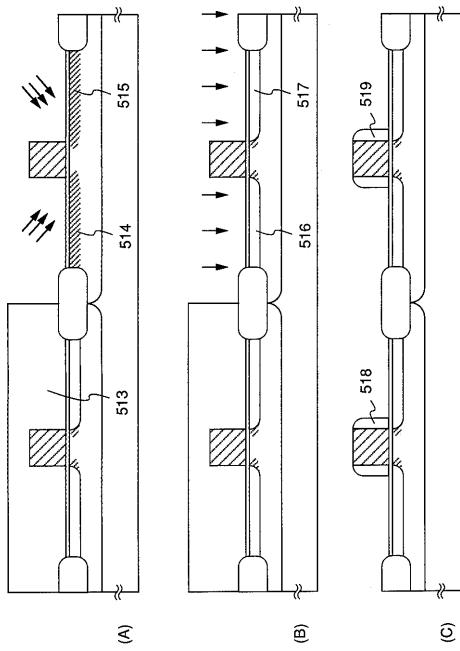

**【 0 0 7 9 】**

次に、N チャネル型 M O S F E T となる領域をレジストマスク 5 1 3 で覆う。この時、P チャネル型 M O S F E T となる領域には図 8 に示した様な構造でピニング領域形成用のマスクが設けられている（図示せず）。

50

**【0080】**

こうしてレジストマスク 513を形成したら、シリコン基板に対して斜め方向から15族から選ばれた元素（代表的にはリン）を添加して後にピニング領域となる不純物領域514、515を形成する。添加条件はシミュレーションで前もって実験的に決定しておく。

**【0081】**

本実施例では、イオンインプランテーション法（イオン注入法）によりリン  $1 \times 10^{18} \text{ atom s/cm}^3$  の濃度で添加する。また、注入ガスはPH<sub>3</sub>、加速電圧は30keV、ドーズ量は  $1 \times 10^{13} \text{ atoms/cm}^2$  とする。そして、シリコン基板に対して30°の角度でイオンが注入される様に調節する。（図6（A））

**【0082】**

さらに、シリコン基板に対して垂直にボロンを添加し、後にPチャネル型MOSFETのLDD領域として機能する不純物領域516、517を形成する。この場合も浅い接合を形成することが望ましい。（図6（B））

**【0083】**

図6（B）の状態が得られたら、次に酸化珪素膜（図示せず）を堆積してエッチバックを行い、サイドウォール518、519を形成する。（図6（C））

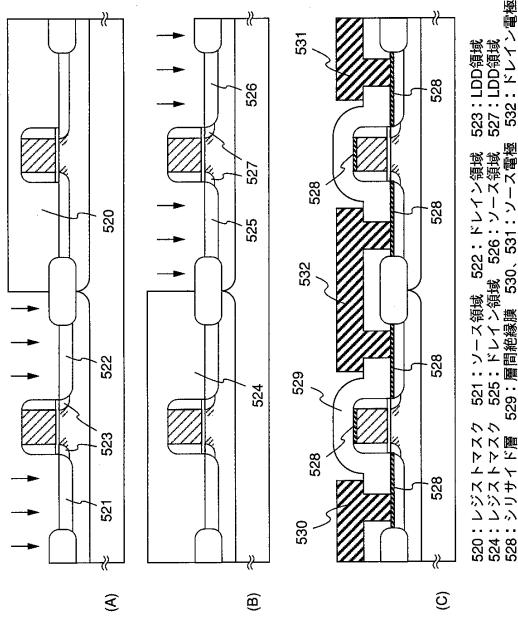

**【0084】**

次に、再びPチャネル型MOSFETとなる領域をレジストマスク520で覆い、砒素を  $1 \times 10^{20} \text{ atoms/cm}^3$  の濃度で添加する。こうしてソース領域521、ドレイン領域522が形成され、サイドウォール518の下にはLDD領域523が形成される。（図7（A））

**【0085】**

なお、ソース／ドレイン領域を形成する場合もイオンプランテーション法、プラズマドーピング法、レーザードーピング法のいずれかの手段を用いて浅い接合を形成することが望ましい。

**【0086】**

また、同様にNチャネル型MOSFETとなる領域をレジストマスク524で覆い、ボロンを  $1 \times 10^{20} \text{ atoms/cm}^3$  の濃度で添加する。こうしてドレイン領域525、ソース領域526が形成され、サイドウォール519の下にはLDD領域527が形成される。（図7（B））

**【0087】**

図7（B）の状態が得られたら、熱またはレーザーによるアニール処理を行い、添加した不純物の活性化を行う。この時、不純物の拡散をできるだけ小さくする様な条件を設定することが必要である。

**【0088】**

ソース／ドレイン領域の活性化が終了したら、チタン膜を成膜してアニール処理を行い、ソース／ドレイン領域及びゲート電極の表面にチタンシリサイド層528を形成する。勿論、他の金属膜を用いた金属シリサイドを形成することもできる。シリサイド層を形成した後、チタン膜は除去する。

**【0089】**

次に、層間絶縁膜529を形成し、コンタクトホールを開けてソース電極530、531、ドレイン電極532を形成する。勿論、電極形成後に水素化を行うことも有効である。

**【0090】**

以上の様な工程によって、図7（C）に示す様なCMOS回路を得ることができる。このCMOS回路はNチャネル型、Pチャネル型の両MOSFETに対してピニング領域を設けているが、どちらか一方のみに設けた構成とすることも可能である。

**【0091】****[実施例3]**

実施例1、2ではゲート電極の両側から斜めに不純物を添加することでソース接合部とドレイン接合部とにピニング領域を形成している。この時、ソース／ドレイン接合部の両方

10

20

30

40

50

に設けられたピニング領域が、互いにゲイト電極の直下で電気的に接続する様な構成としても良い。

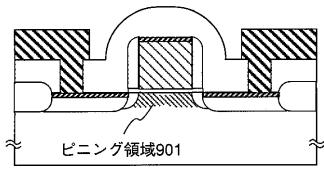

【0092】

本実施例の構造を図9に示す。図9は本願発明の構造を有するNチャネル若しくはPチャネル型のMOSFETである。注目すべきは、斜め添加によって形成されたピニング領域がゲイト電極直下で接触し、ソース・ドレイン間に渡る一つのピニング領域901を形成している点である。

【0093】

勿論、ピニング領域901は図1で説明した様にチャネル幅方向に対してスリット状に設けられた構成となっており、チャネル幅方向に対して配列された各ピニング領域間にはアンドープ領域(図示せず)が形成されている。

10

【0094】

本実施例の構造とすると、実効的なアンドープ領域の面積は減少するがドレン側からの空乏層の広がりを抑えるピニング効果が高まる。なお、チャネル長が $0.1\mu m$ 以下となってしまうと不純物添加の制御性の問題から必然的に本実施例の構造になると予想される。

【0095】

【実施例4】

本願発明は、埋め込みチャネル型のMOSFETに対して適用することも可能である。埋め込みチャネル型はゲイト絶縁膜との界面よりも下にチャネルが形成され、そこをキャリアが移動する。

20

【0096】

従って、表面散乱によるキャリア移動度の低下がなく、表面チャネル型に比べて高いモビリティを得ることができる。しかし一方で埋め込みチャネル型はパンチスルーワークに弱く、耐圧特性が低いという欠点がある。

【0097】

しかしながら、本願発明の構造を採用した埋め込みチャネル型MOSFETは高いモビリティを維持したままパンチスルーワークによるソース・ドレイン間耐圧の低下を抑止することが可能である。

【0098】

【実施例5】

30

本願発明は従来のIC技術全般に適用することが可能である。即ち、現在市場に流通している全ての半導体装置(MOSFETを部品として含む製品)に適用しうる。なお、本明細書中において「半導体装置」とは、単体素子だけでなく、複数の単体素子で構成された集積化回路およびその様な集積化回路を搭載した電子機器(応用製品)をも範疇に含むものとする。

【0099】

例えば、ワンチップ上に集積化されたRISCプロセッサ、ASICプロセッサ等のマイクロプロセッサに適用しうる。また、D/Aコンバータ等の信号処理回路から携帯機器(携帯電話、PHS、モバイルコンピュータ)用の高周波回路に至るまで、半導体を利用する全ての集積化回路に適用しうる。

40

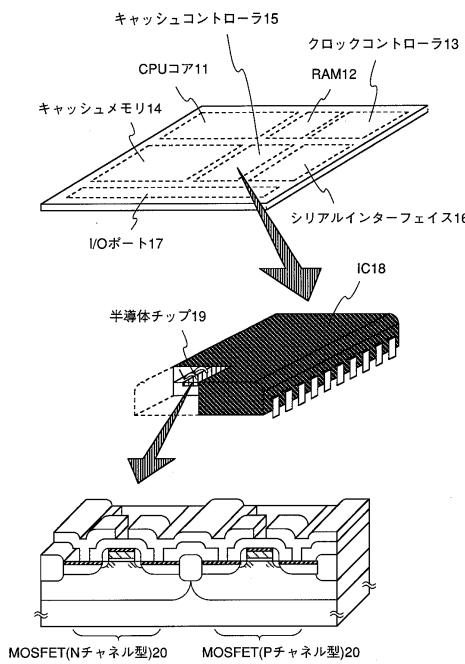

【0100】

図11に示すのは、マイクロプロセッサの一例である。マイクロプロセッサは典型的にはCPUコア11、RAM12、クロックコントローラ13、キャッシュメモリー14、キヤッシュコントローラ15、シリアルインターフェース16、I/Oポート17等から構成される。

【0101】

勿論、図11に示すマイクロプロセッサは簡略化した一例であり、実際のマイクロプロセッサはその用途によって多種多様な回路設計が行われる。

【0102】

しかし、どの様な機能を有するマイクロプロセッサであっても中枢として機能するのはI

50

C (Integrated Circuit) 18 である。IC18 は半導体チップ19 上に形成された集積化回路をセラミック等で保護した機能回路である。

【0103】

そして、その半導体チップ19 上に形成された集積化回路を構成するのが本願発明の構造を有するMOSFET20 (Nチャネル型)、20 (Pチャネル型) である。なお、基本的な回路はCMOS回路を最小単位として構成することで消費電力を抑えることができる。

【0104】

また、本実施例に示したマイクロプロセッサは様々な電子機器に搭載されて中枢回路として機能する。代表的な電子機器としてはパソコンコンピュータ、携帯型情報端末機器、その他あらゆる家電製品が挙げられる。また、車両(自動車や電車等)の制御用コンピュータなども挙げられる。

【0105】

【発明の効果】

本願発明によりディープサブミクロンプロセスが必要となってもプロセス制御性の高い構造で効果的に短チャネル効果を抑制しうるMOSFETを提供することが可能となる。

【0106】

さらに、キャリアの移動経路となる領域が確保されているので短チャネル効果の抑制と同時に高いモビリティを有するMOSFETが実現される。即ち、高いモビリティと高い信頼性とを同時に実現する半導体装置が得られる。

【0107】

本願発明を利用した半導体装置は、今現在市場に流通している全ての半導体装置(応用製品も含めて)と置き換えが可能であり、全ての半導体装置の高性能化、高信頼性化を実現しうる。

【図面の簡単な説明】

【図1】 本願発明のMOSFET構造を説明するための図。

【図2】 従来のMOSFET構造を説明するための図。

【図3】 ピニング領域の形状を示す図。

【図4】 ピニング領域の配置構成を示す図。

【図5】 本願発明のMOSFETの作製工程を示す図。

30

【図6】 本願発明のMOSFETの作製工程を示す図。

【図7】 本願発明のMOSFETの作製工程を示す図。

【図8】 ピニング領域形成時のレジストの配置例を示す図。

【図9】 本願発明のMOSFET構造を説明するための図。

【図10】 ピニング領域形成時のシミュレーション結果を示す図。

【図11】 電子機器の一例を示す図。

【図1】

【図2】

【図3】

【図4】

【図5】

501: P型単結晶シリコン基板 502: P型ウェル

503: N型ウェル 504: 7-t埋・酸化膜

505: 隔離膜 506, 507: ゲート電極

508: レジストマスク 509, 510: 不純物領域(後)のLDD領域

511, 512: 不純物領域(後)のLDD領域

【図6】

513: レジストマスク

514、515: 不純物領域(後のLDドレイン)

516、517: 不純物領域(後のビニグ領域)

518、519: サイドウォール

【図7】

520: レジストマスク

521: ソース領域

522: ドレイン領域

523: ドレイン領域

524: レジストマスク

525: ドレイン領域

526: ソース領域

527: LDドレイン

528: 層間絕縁層

529: シリサイド層

530: ソース電極

531: ドレイン電極

【図8】

【図9】

【図10】

【図11】

---

フロントページの続き

(56)参考文献 特開平06-260638(JP,A)

特開平04-003468(JP,A)

特開平08-274330(JP,A)

特開平09-252132(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 29/78

H01L 21/8234

H01L 27/088

H01L 21/336