(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5643555号

(P5643555)

(45) 発行日 平成26年12月17日(2014.12.17)

(24) 登録日 平成26年11月7日(2014.11.7)

(51) Int.Cl.

F 1

H04N 5/3745 (2011.01)

H01L 27/14 (2006.01)H04N 5/335 745

H01L 27/14 D

請求項の数 7 (全 19 頁)

(21) 出願番号 特願2010-155259 (P2010-155259)

(22) 出願日 平成22年7月7日 (2010.7.7)

(65) 公開番号 特開2012-19360 (P2012-19360A)

(43) 公開日 平成24年1月26日 (2012.1.26)

審査請求日 平成25年7月8日 (2013.7.8)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

(74) 代理人 100134175

弁理士 永川 行光

最終頁に続く

(54) 【発明の名称】 固体撮像装置及び撮像システム

## (57) 【特許請求の範囲】

## 【請求項 1】

光電変換素子をそれぞれ有するとともに、行列状に配された複数の画素と、前記光電変換素子を覆う遮光層とを備える固体撮像装置であって、

前記遮光層は、前記複数の画素のそれぞれの光電変換素子に対して、当該光電変換素子への入射光の一部分を遮るための遮光部と、前記入射光の別の一部分を通すための開口部とを有し、

前記複数の画素は、複数の第1画素及び複数の第2画素を含み、

前記第1画素の前記光電変換素子の平面視における面積は、前記第2画素の前記光電変換素子の平面視における面積よりも大きく、

前記第1画素の前記光電変換素子に対する前記遮光部の面積は、前記第2画素の前記光電変換素子に対する前記遮光部の面積よりも大きく、

前記第1画素の前記光電変換素子に対する前記開口部と前記第2画素の前記光電変換素子に対する前記開口部とはそれぞれ、行又は列に沿う方向である第1方向に沿う第1部分と、前記第1方向に交差する第2方向に沿う第2部分とを含む十字型の部分を含み、

前記第1画素の前記光電変換素子に対する前記第1部分の前記第1方向に沿った長さと、前記第2画素の前記光電変換素子に対する前記第1部分の前記第1方向に沿った長さとは互いに等しいことを特徴とする固体撮像装置。

## 【請求項 2】

前記複数の画素のそれぞれの光電変換素子に対する前記開口部の面積は互いに等しいこ

10

20

とを特徴とする請求項 1 に記載の固体撮像装置。

【請求項 3】

前記固体撮像装置は前記複数の画素から出力される信号を読み出すための走査回路を備え、

前記固体撮像装置には、前記第 1 画素を有する第 1 単位セルと前記第 2 画素を有する第 2 単位セルとを含む複数の単位セルが配され、

前記走査回路は前記第 2 単位セルに配されており、前記第 1 単位セルに配されていないことを特徴とする請求項 1 又は 2 に記載の固体撮像装置。

【請求項 4】

前記複数の画素において、前記光電変換素子の平面視における面積の大きい画素ほど前記遮光部の面積が大きいことを特徴とする請求項 1 乃至 3 のいずれか 1 項に記載の固体撮像装置。 10

【請求項 5】

放射線を可視光に変換するシンチレータをさらに備え、

前記光電変換素子が、前記シンチレータから入射する前記可視光に基づいて電荷を生成することを特徴とする請求項 1 乃至 4 のいずれか 1 項に記載の固体撮像装置。

【請求項 6】

請求項 1 乃至 5 のいずれか 1 項に記載の固体撮像装置と、

前記固体撮像装置から出力される信号を処理するプロセッサと備えることを特徴とする撮像システム。 20

【請求項 7】

請求項 5 に記載の固体撮像装置と、

前記固体撮像装置から出力される信号を処理するプロセッサと備えることを特徴とする放射線撮像システム。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は固体撮像装置及び撮像システムに関する。

【背景技術】

【0002】

近年、固体撮像装置に用いられるセンサパネルの大型化が進んでいる。センサパネルの大型化に伴って、複数の撮像素子ブロックをタイル状に貼り合わせることによって大型のセンサパネルを実現する技術が一般的になっている。複数の撮像素子ブロックを貼り合わせる際にいくつかの問題が生じることが知られている。特許文献 1 は、走査回路等が画素アレイの外周部に配置された撮像素子ブロックを貼りあわせた場合に、撮像素子ブロック間にライン欠陥が生じてしまうことを問題とする。この問題を解決するために、特許文献 1 では、図 7 に示されるように、単位セル内に走査回路等を配置する。単位セル内に走査回路等を配置した結果、走査回路等を含む単位セルの光電変換素子の平面視における面積は、走査回路等を含まない単位セルの光電変換素子の平面視における面積よりも小さくなる。また、特許文献 2 では、撮像素子ブロックの間の隙間を挟んで隣接する画素の間隔は、撮像素子ブロック内で隣接する画素の間隔よりも広くなるため、画像に歪みが生じることを問題とする。この問題を解決するために、特許文献 2 では図 7 に示されるように、撮像素子ブロックの縁に最も近い画素の光電変換素子の平面視における面積を他の画素の光電変換素子のものよりも小さくする。それにより、複数の撮像素子ブロックにわたって光電変換素子の重心間の距離を均一にしている。 40

【先行技術文献】

【特許文献】

【0003】

【特許文献 1】特開 2002 - 90462 号公報

【特許文献 2】特開 2002 - 44522 号公報

10

20

30

40

50

**【発明の概要】****【発明が解決しようとする課題】****【0004】**

上述のように、光電変換素子の面積が異なる画素を固体撮像装置が含む場合に、画素間で感度のばらつきが生じてしまう。そこで、本発明は、光電変換素子の面積が異なる画素を含む固体撮像装置において、画素間の感度のばらつきを低減する技術を提供することを目的とする。

**【課題を解決するための手段】****【0005】**

上記課題に鑑みて、本発明の一つの側面に係る固体撮像装置は、光電変換素子をそれぞれ有するとともに、行列状に配された複数の画素と、前記光電変換素子を覆う遮光層とを備える固体撮像装置であって、前記遮光層は、前記複数の画素のそれぞれの光電変換素子に対して、当該光電変換素子への入射光の一部分を遮るための遮光部と、前記入射光の別的一部分を通すための開口部とを有し、前記複数の画素は、複数の第1画素及び複数の第2画素を含み、前記第1画素の前記光電変換素子の平面視における面積は、前記第2画素の前記光電変換素子の平面視における面積よりも大きく、前記第1画素の前記光電変換素子に対する前記遮光部の面積は、前記第2画素の前記光電変換素子に対する前記遮光部の面積よりも大きく、前記第1画素の前記光電変換素子に対する前記開口部と前記第2画素の前記光電変換素子に対する前記開口部とはそれぞれ、行又は列に沿う方向である第1方向に沿う第1部分と、前記第1方向に交差する第2方向に沿う第2部分とを含む十字型の部分を含み、前記第1画素の前記光電変換素子に対する前記第1部分の前記第1方向に沿った長さと、前記第2画素の前記光電変換素子に対する前記第1部分の前記第1方向に沿った長さとは互いに等しいことを特徴とする。

10

**【発明の効果】****【0006】**

上記手段により、光電変換素子の面積が異なる画素を含む固体撮像装置において、画素間の感度のばらつきを低減する技術が提供される。

**【図面の簡単な説明】****【0007】**

【図1】本発明の実施形態の固体撮像装置の概略構成例を説明する図。

30

【図2】本発明の実施形態の撮像ブロックの構成例を説明する図。

【図3】本発明の実施形態の画素の構成例を説明する図。

【図4】本発明の実施形態のシフトレジスタの構成例を説明する図。

【図5】本発明の実施形態のタイミングチャートの一例を説明する図。

【図6】本発明の一つの実施形態の遮光層600を説明する図。

【図7】本発明の別の実施形態の遮光層700を説明する図。

【図8】本発明の別の実施形態の遮光層800を説明する図。

【図9】放射線撮像システムを例示する図。

**【発明を実施するための形態】****【0008】**

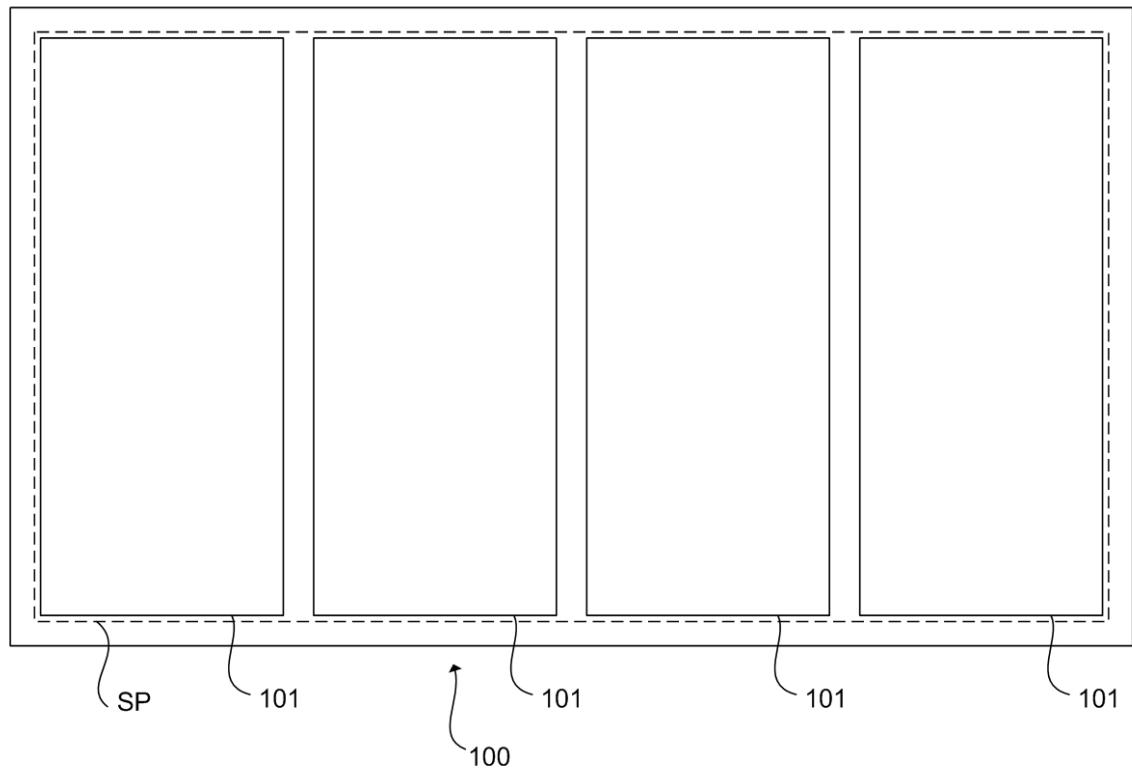

図1を参照しながら本発明の1つの実施形態としての固体撮像装置100の概略構成を説明する。固体撮像装置100は、例えば、複数の撮像ブロック101を配列して構成されうる。この場合、複数の撮像ブロック101の配列によって1つの撮像領域を有するセンサパネルSPが形成されうる。複数の撮像ブロック101は、支持基板102の上に配置されうる。固体撮像装置100が1つの撮像ブロック101で構成される場合には、当該1つの撮像ブロック101によってセンサパネルSPが形成される。複数の撮像ブロック101の各々は、例えば、半導体基板に回路素子を形成したものであってもよいし、ガラス基板等の上に半導体層を形成し、その半導体層に回路素子を形成したものであってもよい。複数の撮像ブロック101の各々は、複数の行および複数の列を構成するように複数の画素が配列された画素アレイを有する。

40

50

## 【0009】

固体撮像装置100は、例えば、X線等の放射線の像を撮像する装置として構成されてもよいし、可視光の像を撮像する装置として構成されてもよい。固体撮像装置100が放射線の像を撮像する装置として構成される場合は、典型的には、放射線を可視光に変換するシンチレータ103がセンサパネルSPの上に設けられる。シンチレータ103は、放射線を可視光に変換し、この可視光がセンサパネルSPに入射し、センサパネルSP(撮像ブロック101)の各光電変換素子によって光電変換される。

## 【0010】

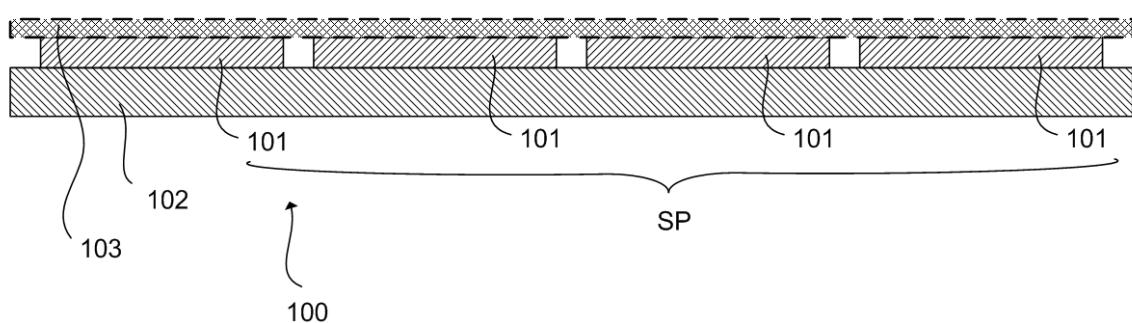

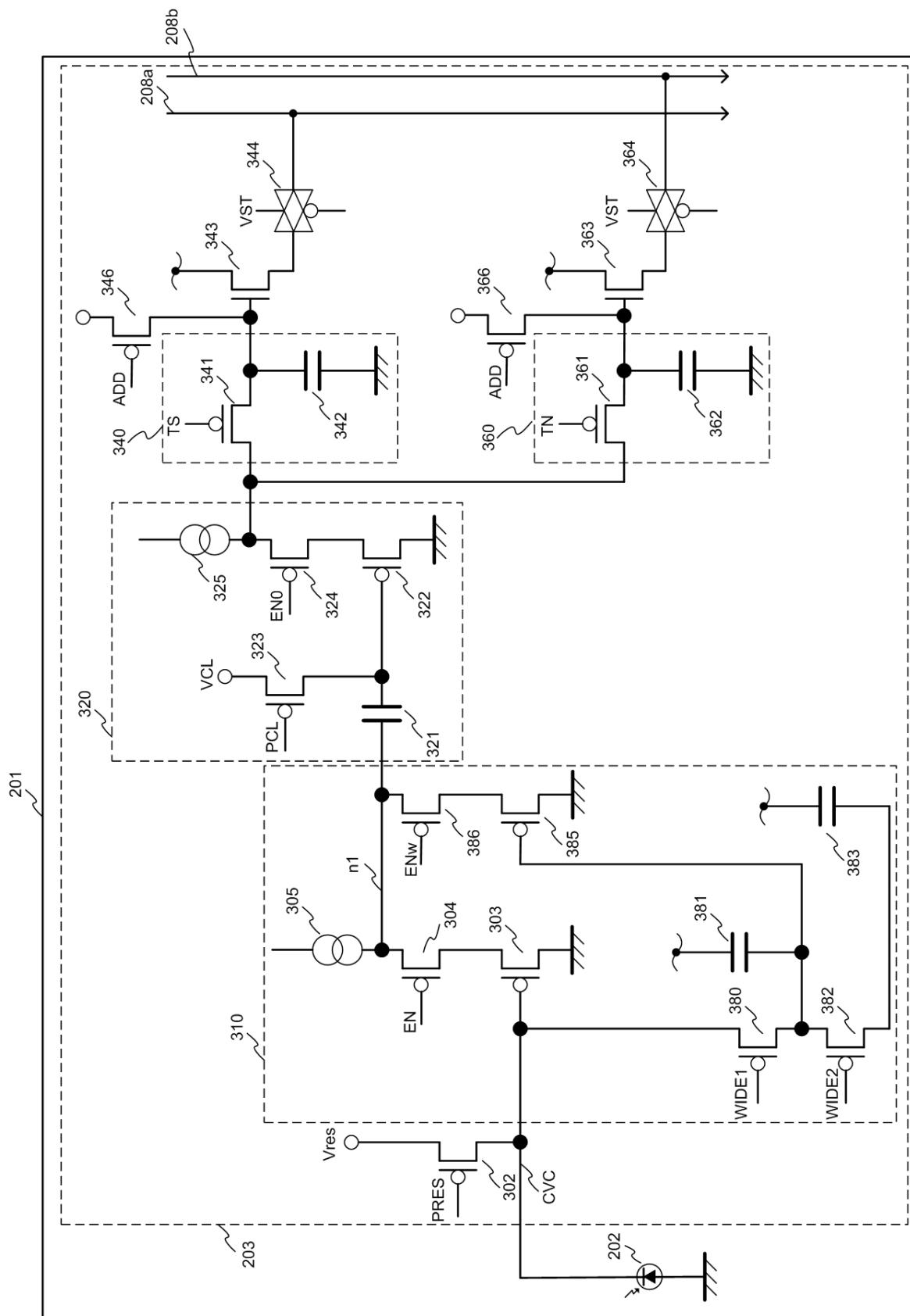

次に、図2を参照しながら各撮像ブロック101の構成例を説明する。なお、固体撮像装置100が1つの撮像ブロック101で構成される場合には、1つの撮像ブロック101を固体撮像装置として考えることができる。撮像ブロック101は、複数の行および複数の列を構成するように複数の画素201が配列され、複数の列信号線208aが配置された画素アレイGAを有する。複数の画素201の各々は、光電変換素子(例えば、フォトダイオード)202と、光電変換素子202で発生した電荷に応じた信号(光信号)を列信号線208aに出力する画素内読出回路203とを含む。画素アレイGAには、複数の列信号線208bが更に配置されてもよく、画素内読出回路203は、画素内読出回路203のノイズを列信号線208bに出力するように構成されうる。行方向に沿って隣接する2つの画素201のそれぞれにおける画素内読出回路203は、例えば、当該2つの画素201の境界線を対称軸として線対称に配置されうる。

## 【0011】

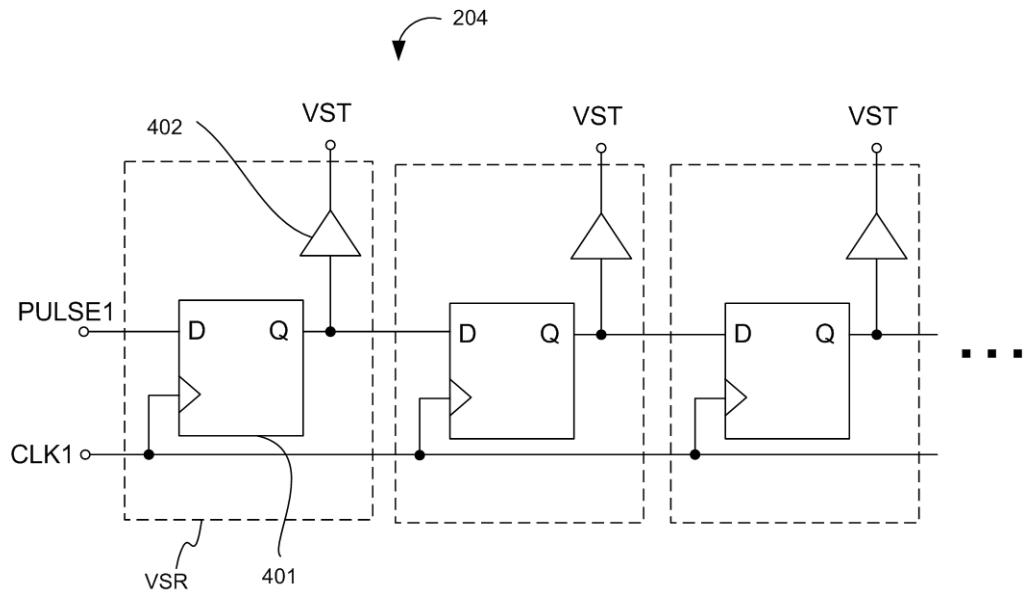

撮像ブロック101は、垂直走査回路204と水平走査回路205とを含む。垂直走査回路204は、例えば、隣接する2つの列の光電変換素子202の間に配置されうるが、画素アレイGAにおける最も外側の列の光電変換素子202の外側に配置されてもよい。垂直走査回路204は、例えば、第1クロックCLK1に従ってシフト動作する垂直シフトレジスタを含み、垂直シフトレジスタによるシフト動作に応じて画素アレイGAにおける複数の行を走査する。垂直シフトレジスタは、複数のレジスタを直列接続して構成され、初段のレジスタによって取り込まれたパルスが第1クロックCLK1に従って順次次段のレジスタに転送される。パルスを保持しているレジスタに対応する行が、選択されるべき行である。

## 【0012】

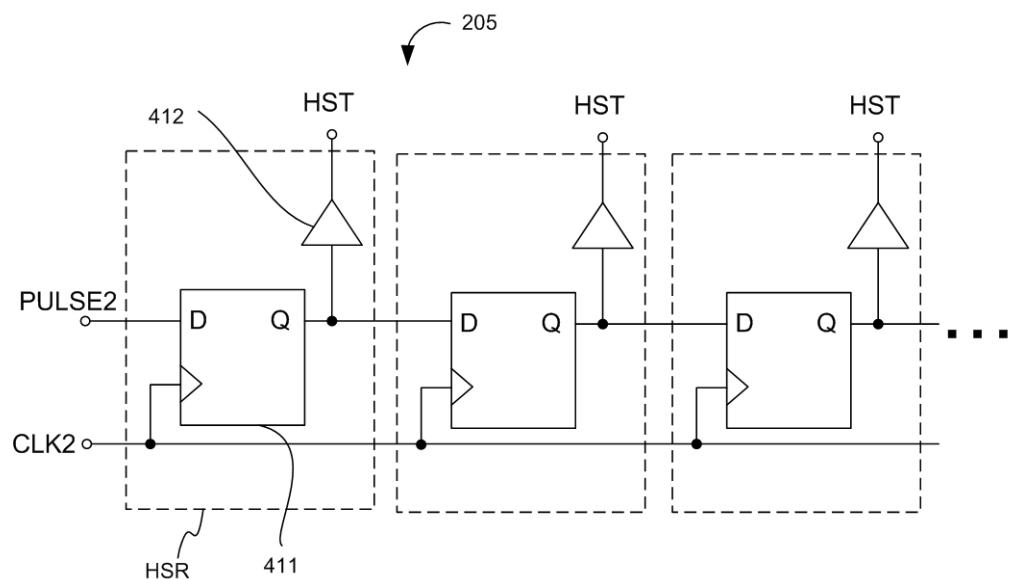

水平走査回路205は、例えば、隣接する2つの行の光電変換素子202の間に配置されうるが、画素アレイGAにおける最も外側の行の光電変換素子202の外側に配置されてもよい。水平走査回路205は、例えば、第2クロックCLK2に従ってシフト動作する水平シフトレジスタを含み、水平シフトレジスタによるシフト動作に応じて画素アレイGAにおける複数の列を走査する。水平シフトレジスタは、複数のレジスタを直列接続して構成され、初段のレジスタによって取り込まれたパルスが第2クロックCLK2に従って順次次段のレジスタに転送される。パルスを保持しているレジスタに対応する列が、選択されるべき列である。

## 【0013】

垂直走査回路204は、垂直シフトレジスタを構成するための1つのレジスタをそれぞれ含む複数の単位垂直走査回路VSRを垂直方向に配列して構成されうる。各単位垂直走査回路VSRは、ある列(図2では、最も左側の列(即ち、第1列)。)に属する画素の光電変換素子202とその列に隣接する列(図2では、左側から2番目の列(即ち、第2列)。)に属する画素の光電変換素子202とによって挟まれる領域に配置されうる。各単位垂直走査回路VSRは、垂直シフトレジスタを通してパルスが転送されると、それが属する行の画素201が選択されるように、行選択信号VSTをアクティブルレベルに駆動する。選択された行の画素201の光信号、ノイズは、それぞれ列信号線208a、208bに出力される。ここで、図2では、列信号線208aと列信号線208bとが1本の線で示されている。水平走査回路205、垂直走査回路204の不図示の入力端子には、パルス信号(スタートパルス)PULSE1、PULSE2がそれぞれ供給される。

10

20

30

40

50

## 【0014】

水平走査回路 205 は、水平シフトレジスタを構成するための 1 つのレジスタをそれぞれ含む複数の単位水平走査回路 HSR を水平方向に配列して構成されうる。各単位水平走査回路 HSR は、1 つの行（図 2 では、上から 4 番目の行（即ち、第 4 行）。）に属する隣接する 2 つの画素からなる各対（第 1 列の画素と第 2 列の画素からなる対、第 3 列の画素と第 4 列の画素からなる対、・・・。）における 2 つの光電変換素子 202 によって挟まれる領域に配置されている。しかし、各単位水平走査回路 HSR は、列方向に隣接する 2 つの画素における 2 つの光電変換素子 202 によって挟まれる領域には配置されていない。このような構成は、列方向における光電変換素子 202 間の隙間を小さくするために有利である。単位水平走査回路 HSR は、水平シフトレジスタを通してパルスが転送されると、それが属する列が選択されるように、即ち、当該列の列信号線 208a、208b が水平信号線 209a、209b に接続されるようにスイッチ 207 を制御する。即ち、選択された行の画素 201 の光信号、ノイズが列信号線 208a、208b に出力され、選択された列（即ち、選択された列信号線 208a、208b）の信号が水平信号線 209a、209b に出力される。これにより X Y アドレッシングが実現される。水平信号線 209a、209b は、出力アンプ 210a、210b の入力に接続されていて、水平信号線 209a、209b に出力された信号は、出力アンプ 210a、210b によって増幅されてパッド 211a、211b を通して出力される。10

## 【0015】

画素アレイ GA は、それぞれ画素 201 を含む複数の単位セル 200 が複数の行および複数の列を構成するように配列されたものとして考えることができる。単位セル 200 は、いくつかの種類を含みうる。ある単位セル 200 は、単位垂直走査回路 VSR の少なくとも一部分を含む。図 2 に示す例では、2 つの単位セル 200 の集合が 1 つの単位垂直走査回路 VSR を含んでいるが、1 つの単位セル 200 が 1 つの単位垂直走査回路 VSR を含んでもよいし、3 以上の複数の単位セル 200 の集合が 1 つの単位垂直走査回路 VSR を含んでもよい。他の単位セル 200 は、単位水平走査回路 HSR の少なくとも一部分を含む。図 2 に示す例では、1 つの単位セル 200 が 1 つの単位水平走査回路 HSR を含んでいるが、複数の単位セル 200 の集合が 1 つの単位水平走査回路 VSR を含んでもよい。他の単位セル 200 は、単位垂直走査回路 VSR の少なくとも一部分および単位水平走査回路 HSR の少なくとも一部分を含む。他の単位セル 200 としては、出力アンプ 210a の少なくとも一部分を含む単位セル、出力アンプ 210b の少なくとも一部分を含む単位セル、スイッチ 207 を含む単位セルなどを挙げることができる。20

## 【0016】

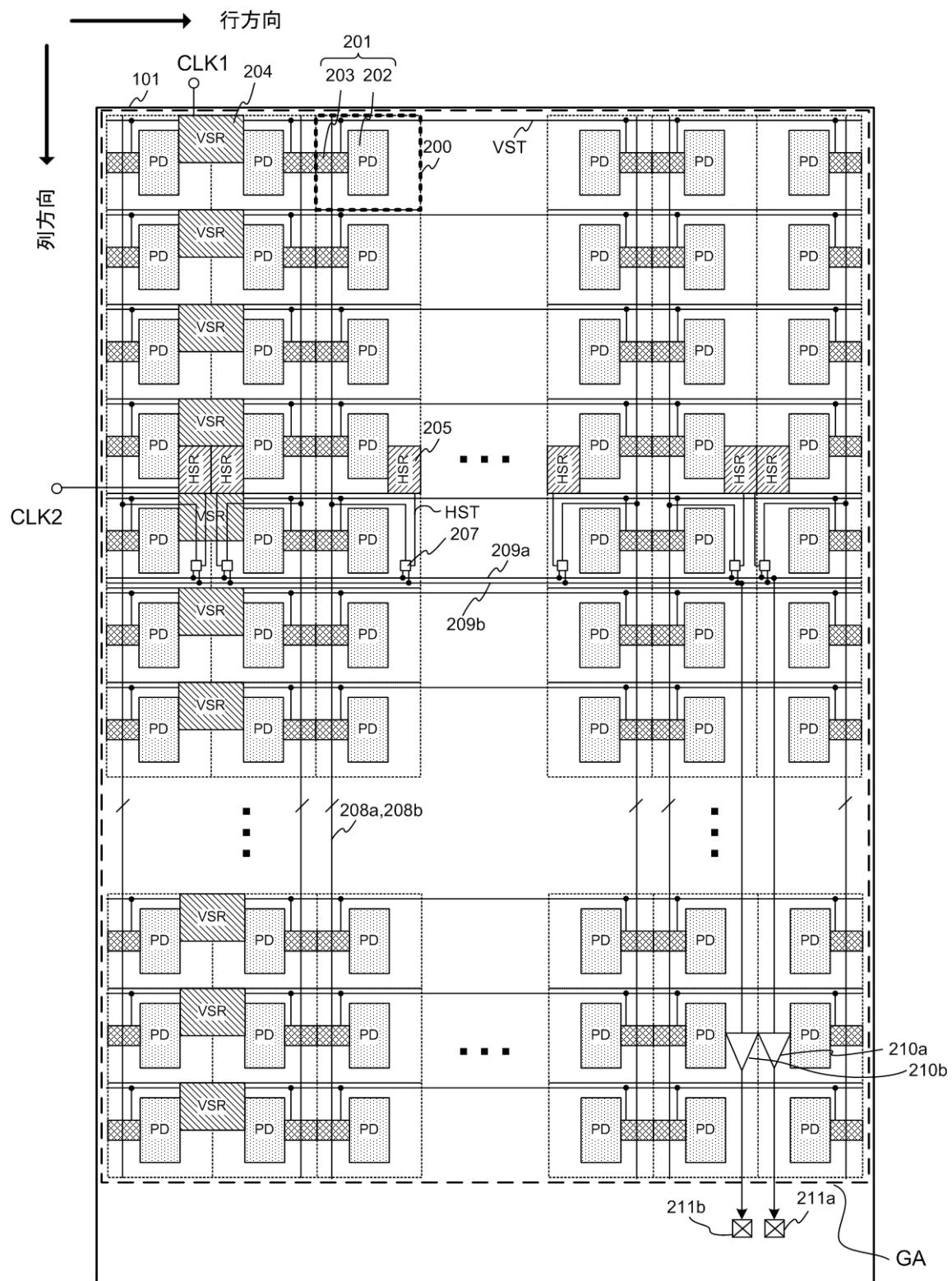

図 3 を参照しながら各画素 201 の構成例を説明する。前述のとおり、画素 201 は、光電変換素子 202 と、画素内読出回路 203 とを含む。光電変換素子 202 は、典型的にはフォトダイオードでありうる。画素内読出回路 203 は、例えば、第 1 増幅回路 310、クランプ回路 320、光信号サンプルホールド回路 340、ノイズサンプルホールド回路 360、第 2 増幅回路の NMOS トランジスタ 343、363、行選択スイッチ 344、364 を含みうる。30

## 【0017】

光電変換素子 202 は、電荷蓄積部を含み、該電荷蓄積部は、第 1 増幅回路 310 の PMOS トランジスタ 303 のゲートに接続されている。PMOS トランジスタ 303 のソースは、PMOS トランジスタ 304 を介して電流源 305 に接続されている。PMOS トランジスタ 303 と電流源 305 とによって第 1 ソースフォロア回路が構成されている。PMOS トランジスタ 303 によってソースフォロア回路を構成することは、1/f ノイズの低減に有効である。PMOS トランジスタ 304 は、そのゲートに供給されるイネーブル信号 EN がアクティブルレベルになるとオンして第 1 ソースフォロア回路を動作状態にするイネーブルスイッチである。第 1 増幅回路 310 は、電荷電圧変換部 CVC の電位に応じた信号を中間ノード n1 に出力する。40

## 【0018】

50

50

50

50

図3に示す例では、光電変換素子202の電荷蓄積部およびPMOSトランジスタ303のゲートが共通のノードを構成していて、このノードは、該電荷蓄積部に蓄積された電荷を電圧に変換する電荷電圧変換部CVCとして機能する。即ち、電荷電圧変換部CVCには、該電荷蓄積部に蓄積された電荷Qと電荷電圧変換部CVCが有する容量値Cとによって定まる電圧V( $= Q / C$ )が現れる。電荷電圧変換部CVCは、リセットスイッチとしてのPMOSトランジスタ302を介してリセット電位Vresに接続されている。リセット信号PRESがアクティブルレベルになると、PMOSトランジスタ302がオンして、電荷電圧変換部CVCの電位がリセット電位Vresにリセットされる。

#### 【0019】

クランプ回路320は、リセットした電荷電圧変換部CVCの電位に応じて第1增幅回路310によって中間ノードn1に出力されるノイズをクランプ容量321によってクランプする。つまり、クランプ回路320は、光電変換素子202で光電変換により発生した電荷に応じて第1ソースフォロア回路から中間ノードn1に出力された信号から、このノイズをキャンセルするための回路である。この中間ノードn1に出力されるノイズはリセット時のkTCノイズを含む。クランプは、クランプ信号PCLをアクティブルレベルにしてPMOSトランジスタ323をオン状態にした後に、クランプ信号PCLを非アクティブルレベルにしてPMOSトランジスタ323をオフ状態にすることによってなされる。クランプ容量321の出力側は、PMOSトランジスタ322のゲートに接続されている。PMOSトランジスタ322のソースは、PMOSトランジスタ324を介して電流源325に接続されている。PMOSトランジスタ322と電流源325とによって第2ソースフォロア回路が構成されている。PMOSトランジスタ324は、そのゲートに供給されるイネーブル信号EN0がアクティブルレベルになるとオンして第2ソースフォロア回路を動作状態にするイネーブルスイッチである。

#### 【0020】

光電変換素子202で光電変換により発生した電荷に応じて第2ソースフォロア回路から出力される信号は、光信号として、光信号サンプリング信号TSがアクティブルレベルになることによってスイッチ341を介して容量342に書き込まれる。電荷電圧変換部CVCの電位をリセットした直後にPMOSトランジスタ323をオン状態とした際に第2ソースフォロア回路から出力される信号は、ノイズである。このノイズは、ノイズサンプリング信号TNがアクティブルレベルになることによってスイッチ361を介して容量362に書き込まれる。このノイズには、第2ソースフォロア回路のオフセット成分が含まれる。

#### 【0021】

垂直走査回路204の単位垂直走査回路VSRが行選択信号VSTをアクティブルレベルに駆動すると、容量342に保持された信号(光信号)が第2增幅回路のNMOSトランジスタ343および行選択スイッチ344を介して列信号線208aに出力される。また、同時に、容量362に保持された信号(ノイズ)が第2增幅回路のNMOSトランジスタ363および行選択スイッチ364を介して列信号線208bに出力される。第2增幅回路のNMOSトランジスタ343は、列信号線208aに設けられた不図示の定電流源とソースフォロア回路を構成する。同様に、第2增幅回路のNMOSトランジスタ363は列信号線208bに設けられた不図示の定電流源とソースフォロア回路を構成する。

#### 【0022】

画素201は、隣接する複数の画素201の光信号を加算する加算スイッチ346を有してもよい。加算モード時には、加算モード信号ADDがアクティブルレベルになり、加算スイッチ346がオン状態になる。これにより、隣接する画素201の容量342が加算スイッチ346によって相互に接続されて、光信号が平均化される。同様に、画素201は、隣接する複数の画素201のノイズ信号を加算する加算スイッチ366を有してもよい。加算スイッチ366がオン状態になると、隣接する画素201の容量362が加算スイッチ366によって相互に接続されて、ノイズが平均化される。

#### 【0023】

10

20

30

40

50

画素 201 は、感度を変更するための機能を有してもよい。画素 201 は、例えば、第 1 感度変更スイッチ 380 および第 2 感度変更スイッチ 382、並びにそれらに付随する回路素子を含みうる。第 1 変更信号 WIDE1 がアクティブルーレベルになると、第 1 感度変更スイッチ 380 がオンして、電荷電圧変換部 CVC の容量値に第 1 付加容量 381 の容量値が追加される。これによって画素 201 の感度が低下する。第 2 変更信号 WIDE2 がアクティブルーレベルになると、第 2 感度変更スイッチ 382 がオンして、電荷電圧変換部 CVC の容量値に第 2 付加容量 383 の容量値が追加される。これによって画素 201 の感度が更に低下する。

#### 【0024】

このように画素 201 の感度を低下させる機能を追加することによって、より大きな光量を受光することが可能となり、ダイナミックレンジを広げることができる。第 1 変更信号 WIDE1 がアクティブルーレベルになる場合には、イネーブル信号 ENW をアクティブルーレベルにして、PMOS トランジスタ 303 に加えて PMOS トランジスタ 385 をソースフォロア動作させてもよい。

10

#### 【0025】

垂直走査回路 204 は、種々の構成を有しうるが、例えば、図 4 (a) に示された構成を有しうる。図 4 (a) に示された垂直走査回路 204 は、各単位垂直走査回路 VSR が 1 つの D 型フリップフロップ 401 を含み、D 型フリップフロップ 401 のクロック入力に対して第 1 クロック CLK1 が供給される。初段の単位垂直走査回路 VSR の D 型フリップフロップ 401 の D 入力には、パルス信号 PULSE1 が供給され、第 1 クロック CLK1 によって第 1 パルス信号 PULSE1 が取り込まれる。初段の D 型フリップフロップ 401 は、第 1 クロック CLK1 の 1 周期分の長さを有するパルス信号を Q 出力から出力する。各単位垂直走査回路 VSR の D 型フリップフロップ 401 の Q 出力は、その単位垂直走査回路 VSR が属する行を選択するために使用され、例えば、バッファ 402 を介して行選択信号 VST として出力される。各単位垂直走査回路 VSR の D 型フリップフロップ 401 の Q 出力は、次段の単位垂直走査回路 VSR の D 型フリップフロップ 401 の D 入力に接続されている。

20

#### 【0026】

水平走査回路 205 は、種々の構成を有しうるが、例えば、図 4 (b) に示された構成を有しうる。図 4 (b) に示された水平走査回路 205 は、各単位垂直走査回路 HSR が 1 つの D 型フリップフロップ 411 を含み、D 型フリップフロップ 411 のクロック入力に対して第 2 クロック CLK2 が供給される。初段の単位水平走査回路 HSR の D 型フリップフロップ 411 の D 入力には、第 2 パルス信号 PULSE2 が供給され、第 2 クロック CLK2 によって第 2 パルス信号 PULSE2 が取り込まれる。初段の単位水平走査回路 HSR は、第 2 クロック CLK2 の 1 周期分の長さを有するパルス信号を Q 出力から出力する。各単位水平走査回路 HSR の Q 出力は、その単位水平走査回路 HSR が属する列を選択するために使用され、例えば、バッファ 412 を介して列選択信号 HST として出力される。各単位水平走査回路 HSR の D 型フリップフロップ 411 の Q 出力は、次段の単位水平走査回路 HSR の D 型フリップフロップ 411 の D 入力に接続されている。ここで、垂直走査回路 204 による走査期間である垂直走査期間は、水平走査回路 205 による水平走査期間に画素アレイ GA の行数を乗じた時間である。そして、水平走査期間は、画素アレイ GA の全ての列を走査するために要する期間である。よって、列を選択する列選択信号 HST を発生する水平走査回路 205 に供給される第 2 クロック CLK2 の周波数は、行を選択する行選択信号 VST を発生する垂直走査回路 204 に供給される第 1 クロック CLK1 の周波数よりも遙かに高い。

40

#### 【0027】

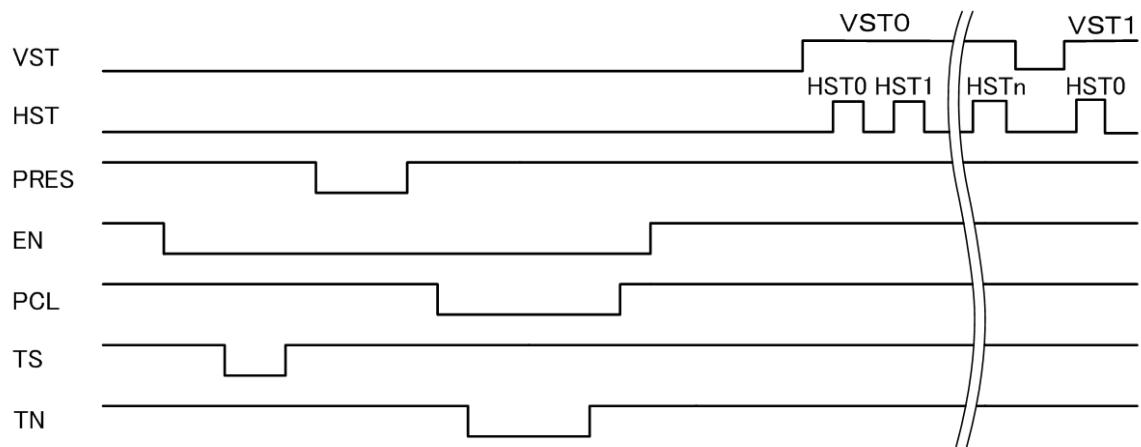

図 5 を参照しながら各画素 201 に供給される主な信号について説明する。リセット信号 PRES、イネーブル信号 EN、クランプ信号 PCL、光信号サンプリング信号 TS、ノイズサンプリング信号 TN は、ローアクティブの信号である。イネーブル信号 EN0 は、図 5 に示されていないが、イネーブル信号 EN と同様の信号でありうる。イネーブル信

50

号 E N w は、図 5 に示されていないが、第 1 変更信号 W I D E 1 がアクティブにされる場合には、イネーブル信号 E N と同様に遷移しうる。

#### 【 0 0 2 8 】

まず、画素アレイ G A の全ての行についてイネーブル信号 E N がアクティブになり、次いで、光信号サンプリング信号 T S がパルス状にアクティブルレベルになって、光信号が容量 3 4 2 に書き込まれる。次いで、リセット信号 P R E S がパルス状にアクティブルレベルになって、電荷電圧変換部 C V C の電位がリセットされる。次いで、クランプ信号 P C L がパルス状にアクティブルレベルになる。クランプ信号 P C L がアクティブルレベルであるときに、ノイズサンプリング信号 T N がパルス状にアクティブルレベルになって、ノイズが容量 3 6 2 に書き込まれる。

10

#### 【 0 0 2 9 】

その後、垂直走査回路 2 0 4 の第 1 行に対応する単位垂直走査回路 V S R がその行選択信号 V S T ( V S T 0 ) をアクティブルレベルにする。これは、垂直走査回路 2 0 4 が画素アレイ G A の第 1 行を選択することを意味する。この状態で、水平走査回路 2 0 5 の第 1 列から最終列に対応する単位水平走査回路 H S R が列選択信号 H S T ( H S T 0 ~ H S T n ) をアクティブルレベルにする。これは、水平走査回路 2 0 5 が画素アレイ G A の第 1 列から最終列までを順に選択することを意味する。これにより、出力アンプ 2 1 0 a 、 2 1 0 b から画素アレイ G A の第 1 行における第 1 列から最終列までの画素の光信号、ノイズが出力される。その後、垂直走査回路 2 0 4 の第 2 行に対応する単位垂直走査回路 V S R がその行選択信号 V S T ( V S T 1 ) をアクティブルレベルにする。水平走査回路 2 0 5 の第 1 列から最終列に対応する単位水平走査回路 H S R が列選択信号 H S T ( H S T 0 ~ H S T n ) をアクティブルレベルにする。このような動作を最終行まで行うことによって 1 つの画像が画素アレイ G A から出力される。

20

#### 【 0 0 3 0 】

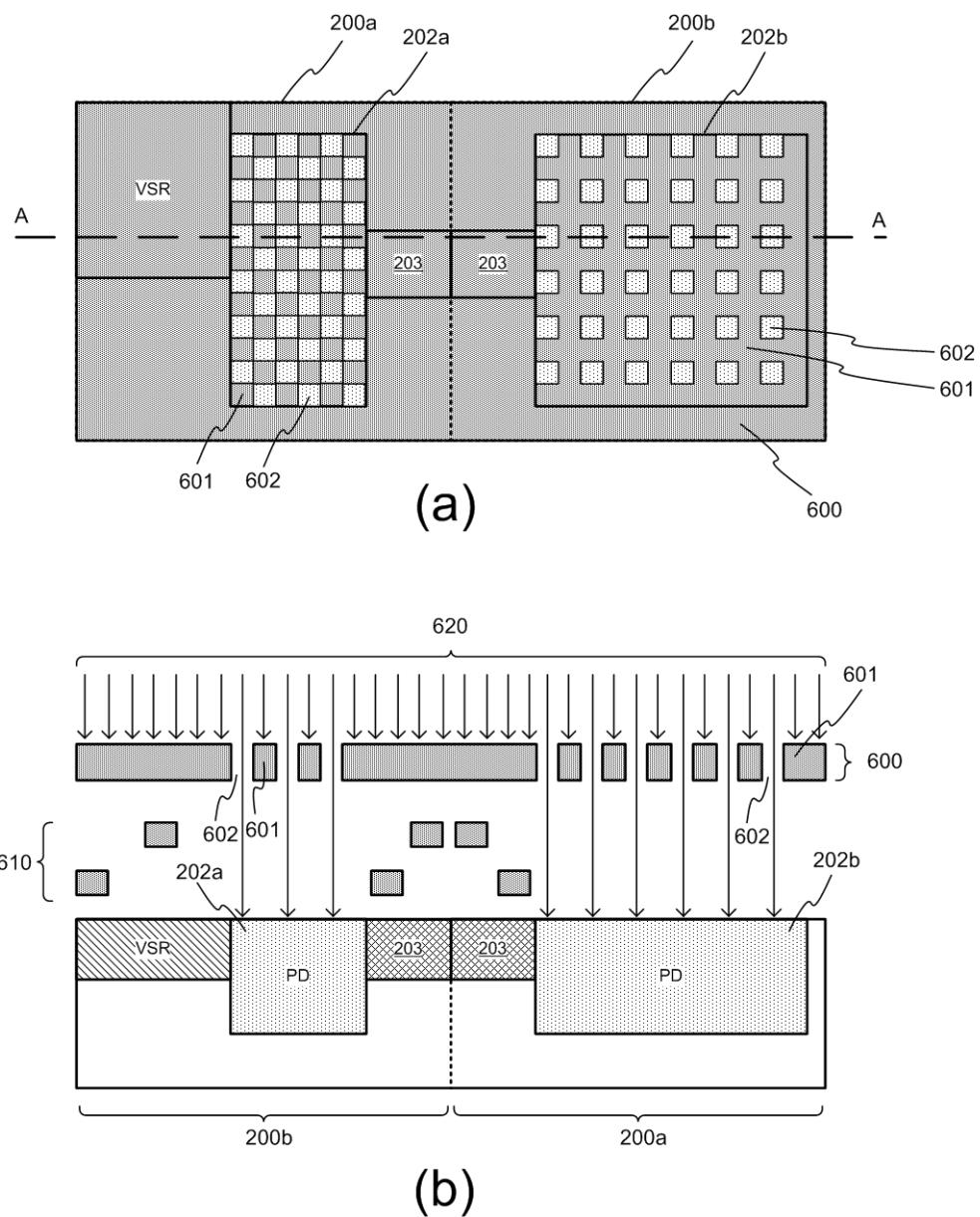

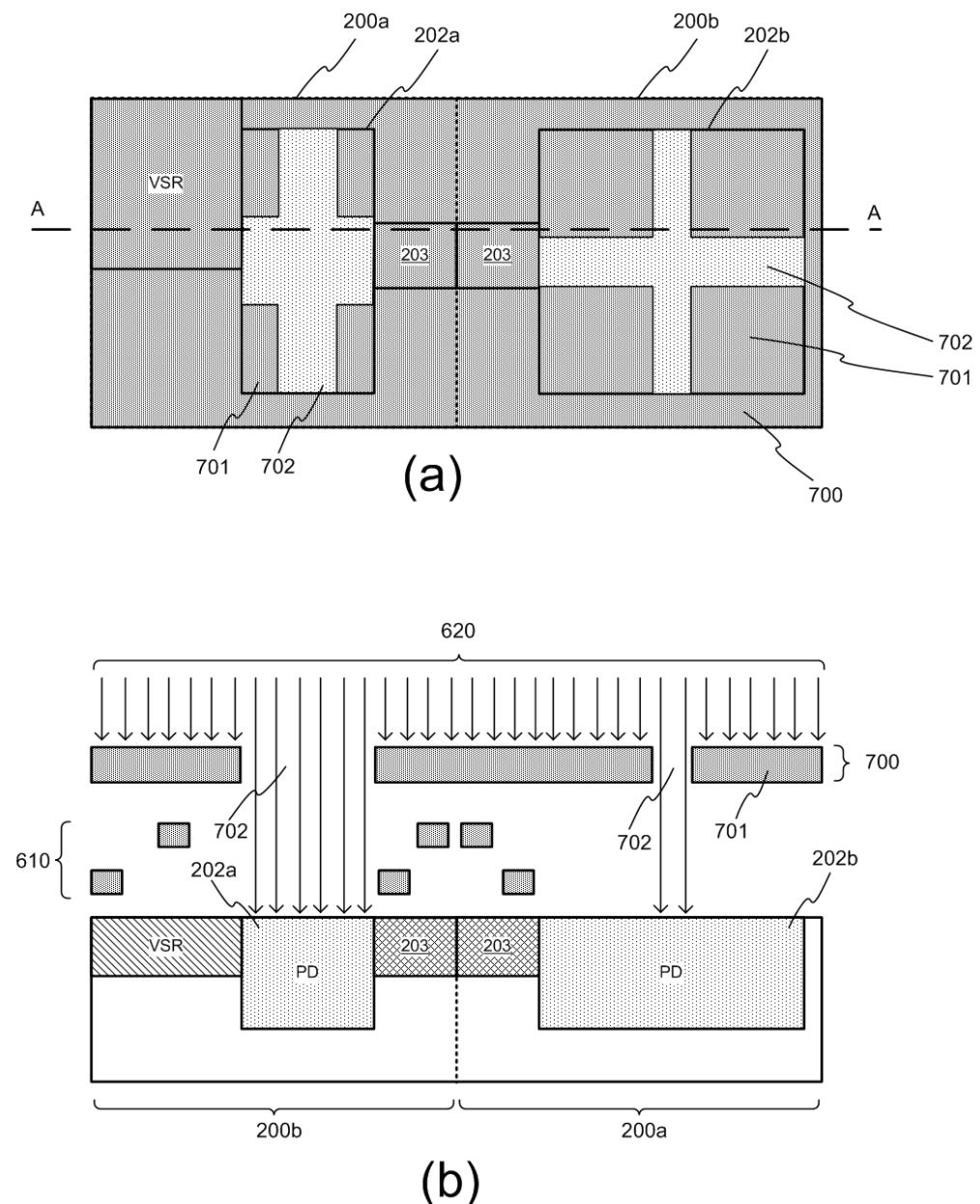

本発明の一つの実施形態に係る固体撮像装置 1 0 0 は遮光層 6 0 0 をさらに備える。図 6 を用いて、本実施形態の遮光層 6 0 0 について説明する。図 6 では、図 2 に示された画素アレイ G A の単位セル 2 0 0 のうち、単位垂直走査回路 V S R を含む第 1 単位セル 2 0 0 a と、単位垂直走査回路 V S R と単位水平走査回路 H S R とのいずれも含まない第 2 単位セル 2 0 0 b とに着目する。図 6 ( a ) は第 1 単位セル 2 0 0 a 及び第 2 単位セル 2 0 0 b の平面図を示し、図 6 ( b ) はその A A 線断面図を示す。

30

#### 【 0 0 3 1 】

第 1 単位セル 2 0 0 a に含まれる画素を第 1 画素とよび、第 2 単位セル 2 0 0 b に含まれる画素を第 2 画素と呼ぶ。第 1 単位セル 2 0 0 a は単位垂直走査回路 V S R を含んでおり、第 1 光電変換素子 2 0 2 a は単位垂直走査回路 V S R に隣接している。一方、第 1 単位セル 2 0 0 a は単位垂直走査回路 V S R と単位水平走査回路 H S R とのいずれも含んでいない。すなわち、第 2 光電変換素子 2 0 2 b はいずれの走査回路にも隣接していない。単位垂直走査回路 V S R が配置された領域に光電変換素子 2 0 2 を重ねて配置することはできないため、第 1 光電変換素子 2 0 2 a の平面視における面積は第 2 光電変換素子 2 0 2 b の平面視における面積よりも小さくなる。そのため、それぞれの光電変換素子の全面に入射光 6 2 0 が照射される場合には、第 1 光電変換素子 2 0 2 a の方が第 2 光電変換素子 2 0 2 b よりも感度が低くなりうる。そこで、本実施形態では、第 1 光電変換素子 2 0 2 a の一部と第 2 光電変換素子 2 0 2 b の一部とをそれぞれ遮光層 6 0 0 で覆うことによって、第 1 画素と第 2 画素との感度の差を低減しうる。

40

#### 【 0 0 3 2 】

遮光層 6 0 0 は単位セル 2 0 0 a 、 2 0 0 b を覆う位置に配置される。すなわち、遮光層 6 0 0 は、光電変換素子 2 0 2 a 、 2 0 2 b 、画素内読出回路 2 0 3 及び単位垂直走査回路 V S R を覆う。遮光層 6 0 0 は、それぞれの光電変換素子 2 0 2 a 、 2 0 0 b を覆う位置において、遮光部 6 0 1 と開口部 6 0 2 とを有しうる。遮光部 6 0 1 は、光電変換素子 2 0 2 a 、 2 0 2 b への入射光 6 2 0 の一部分を遮光する。一方、開口部 6 0 2 は光電変換素子 2 0 2 a 、 2 0 2 b を覆う位置に配置され、入射光 6 2 0 の残り部分を通す。す

50

なわち、開口部 602 を通る入射光 620 は光電変換素子 202a、202b へ照射される。

【 0 0 3 3 】

本実施形態では、第2光電変換素子202bを覆う遮光部601の面積を、第1光電変換素子202aを覆う遮光部601の面積よりも大きくなるように遮光層600を形成する。これにより、遮光層600による第2画素の感度の低下量を、遮光層600による第1画素の感度の低下量よりも大きくすることができる。さらに、第1光電変換素子202aを覆う開口部602の面積と、第2光電変換素子202bを覆う開口部602の面積とが等しくなるように遮光層600を形成してもよい。ここで、図6に示されるように一つの光電変換素子を覆う開口部602が複数の開口を含む場合に、一つの光電変換素子を覆う開口部602の面積とは当該複数の開口の面積の合計値を表す。このように、開口部602の面積を等しくすることによって、第1画素と第2画素との感度は等しくなりうる。

[ 0 0 3 4 ]

本実施形態において、遮光層 600 は、第 1 アルミ層、第 2 アルミ層で形成された配線層 610 の上の第 3 アルミ層で形成されうる。光電変換素子を覆う遮光層と、単位垂直操作回路 VSR を覆う遮光層と、画素内読出回路 203 を覆う遮光層とは図 6 (b) に示すように同一層に形成されてもよいし、それぞれが別々の層に形成されてもよい。本実施形態の遮光層 600 は、周期的に配置された複数の開口を開口部 602 として有する。これにより、各光電変換素子 202 において、光電変換素子 202 のそれぞれの部分への入射光 620 を満遍なく受光することが可能となる。

〔 0 0 3 5 〕

図6では単位垂直走査回路V S Rを含む第1単位セル2 0 0 aと単位走査回路を含まない第2単位セル2 0 0 bとに注目した。同様に、単位水平走査回路H S Rを含む単位セル2 0 0や垂直・水平両方の単位走査回路を含む単位セル2 0 0も第2単位セル2 0 0 bよりも光電変換素子の平面視における面積が小さい。そのため、これらの単位セル2 0 0についても、第2単位セル2 0 0 bと比較して、光電変換素子2 0 2を覆う遮光部6 0 1の面積が小さくよう遮光層6 0 0を形成してもよい。一般的には、本実施形態は、光電変換素子2 0 2の平面視における面積が異なる少なくとも2種類の画素を含む場合に適用する。光電変換素子2 0 2の平面視における面積の大きい画素2 0 1ほど、この光電変換素子2 0 2への入射光6 2 0を遮るための遮光部6 0 1の面積が大きくなるように遮光層6 0 0を形成しうる。

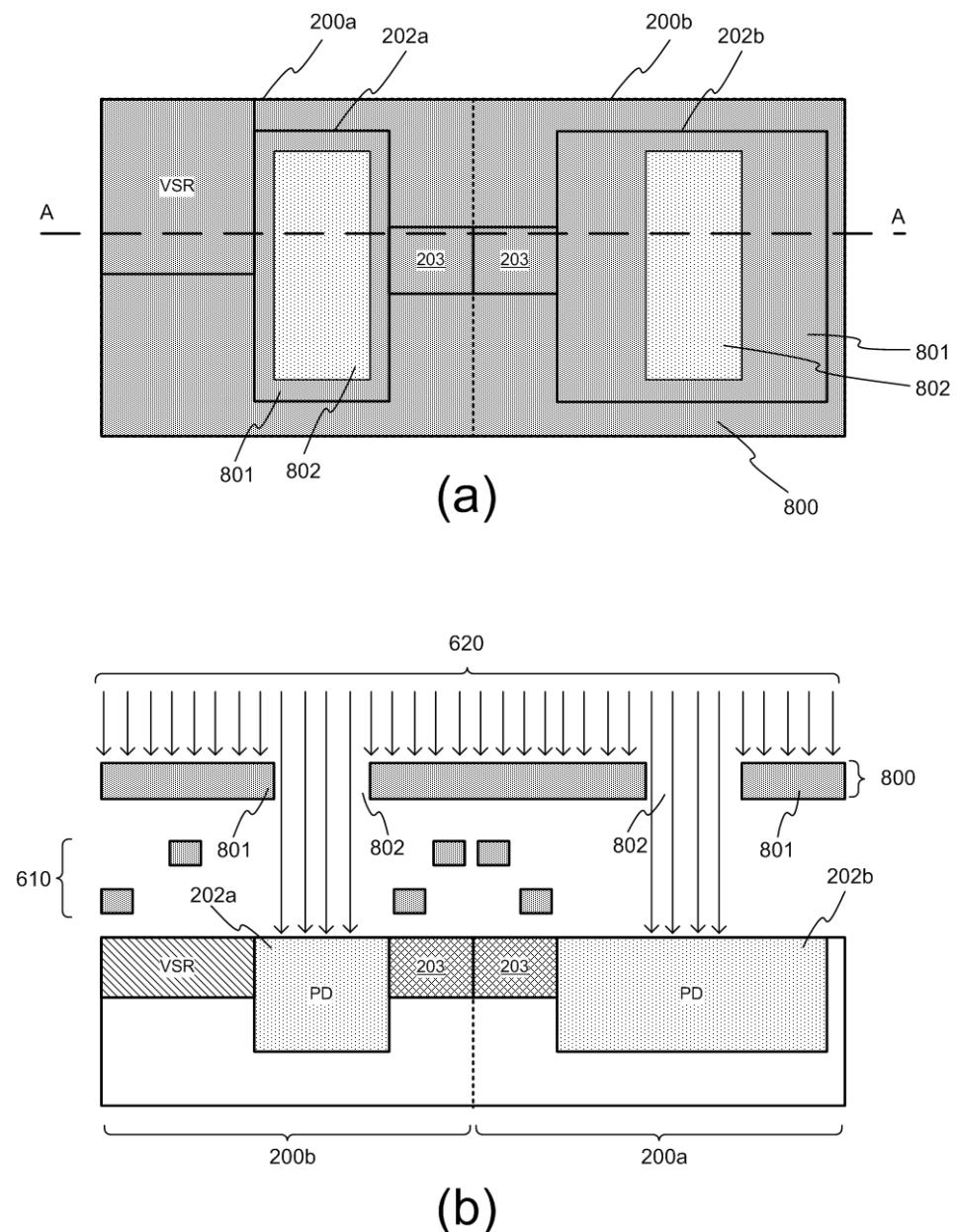

〔 0 0 3 6 〕

続いて、図7を用いて本発明の別の実施形態に係る固体撮像装置について説明する。本実施形態に係る固体撮像装置は遮光層700を備える。図6と図7とは遮光層700の形状以外は同様のため、以下では遮光層700についてのみ説明し、他の部分の説明を省略する。遮光層700の遮光部701は、それぞれの光電変換素子202a、202bの四隅を覆う位置に配置され、その結果として、十字型の形状の開口部702が形成される。本実施形態でも、第1画素の光電変換素子202aを覆う遮光部701の面積よりも、第2画素の光電変換素子202bを覆う遮光部701の面積の方が大きくなるように遮光層700が形成される。また、第1画素の光電変換素子202aを覆う開口部702の面積と、第2画素の光電変換素子202bを覆う開口部702の面積とが等しくなるように遮光層700が形成されてもよい。

【 0 0 3 7 】

続いて、図8を用いて本発明の別の実施形態に係る固体撮像装置について説明する。本実施形態に係る固体撮像装置は遮光層800を備える。図6と図8とは遮光層800の形状以外は同様のため、以下では遮光層800についてのみ説明し、他の部分の説明を省略する。遮光層800の遮光部801は、それぞれの光電変換素子202a、202bの外側の領域を環状に覆う位置に配置され、その結果として、光電変換素子202a、202bの内側の領域を覆う矩形状の形状の開口部802が形成される。本実施形態でも、第1画素の光電変換素子202aを覆う遮光部801の面積よりも、第2画素の光電変換素子

202bを覆う遮光部801の面積の方が大きくなるように遮光層800が形成される。また、第1画素の光電変換素子202aを覆う開口部802の面積と、第2画素の光電変換素子202bを覆う開口部802の面積とが等しくなるように遮光層800が形成されてもよい。さらに、それぞれの光電変換素子202を覆う開口部802が互いに同一の形状であってもよい。遮光層800のように光電変換素子202の内側の領域を覆う位置に開口部802を形成することで、例えばマイクロレンズ等により入射光620が集約される場合に有利である。

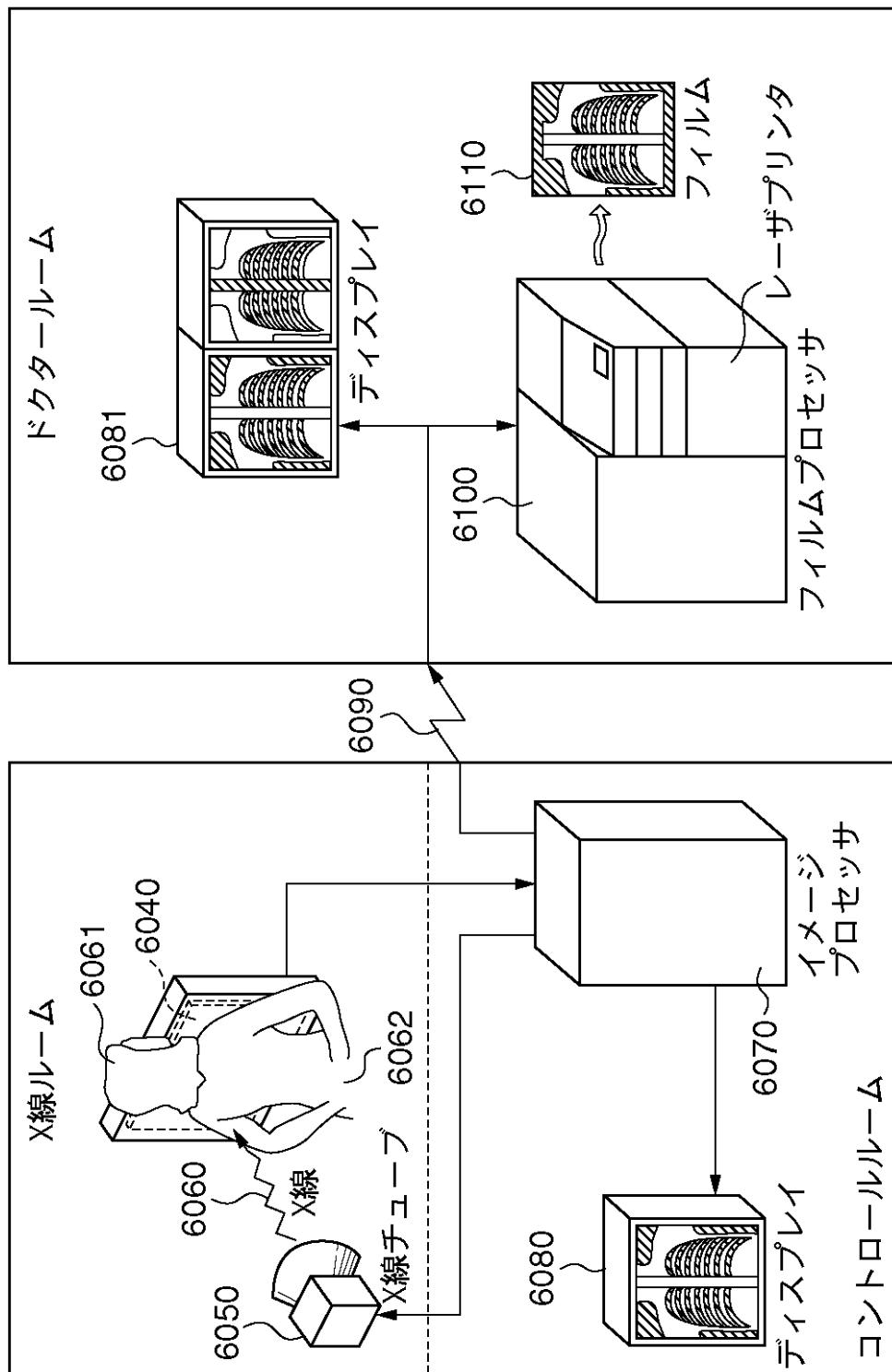

#### 【0038】

図9は本発明に係る固体撮像装置をX線診断システム(放射線撮像システム)応用した例を示した図である。放射線撮像システムは、放射線撮像装置6040と、放射線撮像装置6040から出力される信号を処理するイメージプロセッサ6070とを備える。放射線撮像装置6040は、前述の固体撮像装置100を図1(b)に例示されるように放射線を撮像する装置として構成したものである。X線チューブ(放射線源)6050で発生したX線6060は患者あるいは被験者6061の胸部6062を透過し、放射線撮像装置6040に入射する。この入射したX線には被験者6061の体内部の情報が含まれている。イメージプロセッサ(プロセッサ)6070は、放射線撮像装置6040から出力される信号(画像)を処理し、例えば、処理によって得られた信号に基づいて制御室のディスプレイ6080に画像を表示させることができる。

#### 【0039】

また、イメージプロセッサ6070は、処理によって得られた信号を伝送路6090を介して遠隔地へ転送することができる。これにより、別の場所のドクタールームなどに配置されたディスプレイ6081に画像を表示させたり、光ディスク等の記録媒体に画像を記録したりすることができる。記録媒体は、フィルム6110であってもよく、この場合、フィルムプロセッサ6100がフィルム6110に画像を記録する。

#### 【0040】

本発明に係る固体撮像装置は、可視光の像を撮像する撮像システムに応用することもできる。そのような撮像システムは、例えば、固体撮像装置100と、固体撮像装置100から出力される信号を処理するプロセッサとを備えうる。該プロセッサによる処理は、例えば、画像の形式を変換する処理、画像を圧縮する処理、画像のサイズを変更する処理および画像のコントラストを変更する処理の少なくとも1つを含みうる。

10

20

30

【図1】

(a)

(b)

【図2】

【図3】

【図4】

(a)

(b)

【図5】

【図6】

【図7】

【図8】

【図9】

---

フロントページの続き

(72)発明者 河野 祥士

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 菊池 伸

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 山下 雄一郎

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 藤村 大

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 清水 伸一郎

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 有嶋 優

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 松永 隆志

(56)参考文献 特開2002-090462 (JP, A)

特開平06-045577 (JP, A)

国際公開第00/026966 (WO, A1)

特開2008-177191 (JP, A)

特開平04-206773 (JP, A)

特開2001-111026 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/3745

H01L 27/14