(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第5072208号

(P5072208)

(45) 発行日 平成24年11月14日(2012.11.14)

(24) 登録日 平成24年8月31日(2012.8.31)

(51) Int.Cl.

F 1

|        |        |           |

|--------|--------|-----------|

| HO 1 L | 27/12  | (2006.01) |

| HO 1 L | 21/02  | (2006.01) |

| HO 1 L | 21/336 | (2006.01) |

| HO 1 L | 29/786 | (2006.01) |

| HO 1 L | 27/146 | (2006.01) |

|         |       |         |

|---------|-------|---------|

| HO 1 L  | 27/12 | B       |

| HO 1 L  | 29/78 | 6 2 7 D |

| HO 1 L  | 27/14 | C       |

| G 0 6 K | 19/00 | H       |

| G 0 6 K | 19/00 | K       |

請求項の数 3 (全 30 頁) 最終頁に続く

(21) 出願番号

特願2005-275070 (P2005-275070)

(22) 出願日

平成17年9月22日 (2005.9.22)

(65) 公開番号

特開2006-121060 (P2006-121060A)

(43) 公開日

平成18年5月11日 (2006.5.11)

審査請求日

平成20年9月17日 (2008.9.17)

(31) 優先権主張番号

特願2004-278548 (P2004-278548)

(32) 優先日

平成16年9月24日 (2004.9.24)

(33) 優先権主張国

日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 萩原 周治

最終頁に続く

(54) 【発明の名称】 半導体装置の作製方法

(57) 【特許請求の範囲】

## 【請求項 1】

第1の基板上に剥離層を選択的に形成し、

前記第1の基板及び前記剥離層に接するように第1の絶縁層を形成し、

前記第1の絶縁層上に第1の薄膜トランジスタ及び第2の薄膜トランジスタを形成し、

前記第1の薄膜トランジスタ及び前記第2の薄膜トランジスタ上に第2の絶縁層を形成し、

前記第1の絶縁層及び前記第2の絶縁層に、前記第1の基板に達する第1の開口部を形成し、

前記第2の絶縁層に、前記第1の薄膜トランジスタに達する第2の開口部と、前記第2の薄膜トランジスタに達する第3の開口部と、を形成し、

前記第1の開口部及び前記第2の開口部に第1の導電層を形成し、

前記第3の開口部に第2の導電層を形成し、

前記第1の絶縁層及び前記第2の絶縁層に、前記剥離層に達する第4の開口部を形成し、

前記第4の開口部にエッチング剤を導入して前記剥離層を除去し、

前記第2の導電層と、第2の基板上に設けられた第3の導電層とが電気的に接続するよう、前記第1の基板と前記第2の基板とを貼り合わせ、

前記第1の基板を剥離して、前記第2の基板に前記第1の薄膜トランジスタ及び前記第2の薄膜トランジスタを転置し、

前記第1の導電層と、第3の基板上に設けられた第4の導電層とが電気的に接続するよう、前記第2の基板と前記第3の基板とを貼り合わせることを特徴とする半導体装置の作製方法。

**【請求項2】**

請求項1において、

前記剥離層として、タンゲステン又はモリブデンを含む層を形成することを特徴とする半導体装置の作製方法。

**【請求項3】**

請求項1又は請求項2において、

前記エッチング剤はフッ化ハロゲンを含む気体又は液体であることを特徴とする半導体装置の作製方法。 10

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、半導体装置及びその作製方法、並びに電子機器に関する。

**【背景技術】**

**【0002】**

近年、絶縁基板上に設けられた薄膜集積回路を転置する技術開発が進められている。このような技術として、例えば、薄膜集積回路と基板の間に剥離層を設けて、当該剥離層を、ハロゲンを含む気体を用いて除去することにより、薄膜集積回路を支持基板から分離し、その後転置する技術がある（特許文献1参照）。 20

【特許文献1】特開平8-254686号公報

**【発明の開示】**

**【発明が解決しようとする課題】**

**【0003】**

しかしながら、上記の特許文献1によると、基板の一表面に剥離層を形成し、当該剥離層上に複数の素子を形成し、続いて剥離層を除去する。そうすると、複数の素子は基板から剥離され、基板と複数の素子の間には空間が生じる。その後、複数の素子を基板に接着させるが、当該複数の素子は数 $\mu\text{m}$ 程度と薄く、また大変軽い。そのため、複数の素子を基板に接着させる前に、当該複数の素子が基板から飛散してしまうことがあった。 30

**【0004】**

そこで本発明は、複数の素子の飛散を防止しながら半導体装置を作製することを課題とする。また、複数の機能を有する半導体装置及びその作製方法を提供することを課題とする。

**【課題を解決するための手段】**

**【0005】**

本発明の一は、薄膜集積回路と、センサ又はアンテナを有する第1の基板と、アンテナを有する第2の基板を有し、センサ又はアンテナを有する第1の基板とアンテナを有する第2の基板とは、薄膜集積回路を挟持している半導体装置であることを要旨とする。

**【0006】**

上記半導体装置において、薄膜集積回路とセンサ、薄膜集積回路とアンテナそれぞれは、導電性粒子で電気的に接続されている。また、薄膜集積回路とセンサ、薄膜集積回路とアンテナそれぞれは、導電性粒子を有する樹脂を挟持している。更には、第1の基板及び第2の基板は、可とう性を有することを特徴とする。 40

**【0007】**

また、本発明の一は、第1の基板の一表面に剥離層を形成した後に、当該剥離層を選択的に除去して、剥離層が設けられた第1の領域と、剥離層が設けられていない第2の領域を形成する。続いて、第1の領域と第2の領域上に下地絶縁層を全面に形成する。そうすると、下地絶縁層は、第1の領域では剥離層に接し、第2の領域では第1の基板に接する。次に、下地絶縁層上に複数の薄膜トランジスタを含む薄膜集積回路を形成する。続いて 50

、絶縁層及び薄膜集積回路に形成される絶縁層に開口部を形成し、その後開口部にエッチング剤を導入して剥離層を除去する。この際、剥離層が設けられていた第1の領域では、基板と下地絶縁層との間に空間が生じるが、剥離層が設けられていない第2の領域では、基板と下地絶縁層が密着したままである。このように、剥離層を除去した後も、第1の基板と下地絶縁層とが密着した領域が設けられているため、下地絶縁層上に設けられた薄膜集積回路の飛散を防止することができる。剥離層を除去した後は、第2の基板上の導電層と、薄膜集積回路の接続用の第1の導電層とが接するように、薄膜集積回路とアンテナを有する第2の基板とを一体化させる。次に、第1の基板上から、薄膜集積回路と基体とを剥離するが、この際、裏面に接続用の第2の導電層が露出されるようにする。そして、第3の基板上の導電層と、薄膜集積回路の接続用の第2の導電層とが接するように、薄膜集積回路とアンテナまたはセンサを有する第3の基板とを貼り合わせることを要旨とする。

10

#### 【0008】

また、本発明の半導体装置の作製方法の一は、第1の基板上に剥離層を選択的に形成し、第1の基板及び剥離層に接するように下地絶縁層を形成し、下地絶縁層上に複数の薄膜トランジスタを形成し、第1の基板が露出するように、第1の開口部を形成し、複数の薄膜トランジスタのソース領域及びドレイン領域が露出するように、第2の開口部を形成し、第1の開口部を充填する第1の導電層及び第2の開口部を充填する第2の導電層を形成し、剥離層が露出するように第3の開口部を形成し、第3の開口部にエッチング剤を導入して剥離層を除去し、第2の導電層と、第2の基板上に設けられた第3の導電層とが接続するように、複数の薄膜トランジスタと第2の基板を貼り合わせた後、第1の基板から複数の薄膜トランジスタを剥離し、第1の導電層と、第3の基板上に設けられた第4の導電層とが接続するように、複数の薄膜トランジスタと第3の基板を貼り合わせることを特徴とする。

20

#### 【0009】

また、本発明である半導体装置の作製方法の一は、第1の基板上に剥離層を選択的に形成し、第1の基板及び剥離層に接するように下地絶縁層を形成し、下地絶縁層上に複数の薄膜トランジスタを形成し、第1の基板が露出するように、第1の開口部を形成し、複数の薄膜トランジスタのソース領域及びドレイン領域が露出するように、第2の開口部を形成し、第1の開口部を充填する第1の導電層及び第2の開口部を充填する第2の導電層を形成し、剥離層が露出するように第3の開口部を形成し、第3の開口部にエッチング剤を導入して剥離層を選択的に除去し、第2の導電層と、第2の基板上に設けられた第3の導電層とが接続するように、複数の薄膜トランジスタと第2の基板を貼り合わせた後、物理的手段（物理的な力）により、第1の基板から複数の薄膜トランジスタを剥離し、第1の導電層と、第3の基板上に設けられた第4の導電層とが接続するように、複数の薄膜トランジスタと第3の基板を貼り合わせることを特徴とする。

30

#### 【0010】

上記の作製方法において、第1の基板は、ガラス基板、石英基板、絶縁層を有する金属基板、作製工程の処理温度に耐えうるプラスチック基板等であることを特徴とする。また、剥離層として、タンゲステン(W)、モリブデン(Mo)、チタン(Ti)、タンタル(Ta)、ニオブ(Nb)、ニッケル(Ni)、コバルト(Co)、ジルコニウム(Zr)、亜鉛(Zn)、ルテニウム(Ru)、ロジウム(Rh)、鉛(Pd)、オスミウム(Os)、イリジウム(Ir)、珪素(Si)から選択された元素、又は前記元素を主成分とする合金材料、又は前記元素を主成分とする化合物材料からなる層で形成することを特徴とする。また、剥離層として、酸素雰囲気下で、スパッタリング法により、上記元素の酸化物を含む層を形成することを特徴とする。また、剥離層として、上記元素、又は前記元素を主成分とする合金材料、又は前記元素を主成分とする化合物材料を用いて形成し、その上層に珪素の酸化物を含む層を形成することを特徴とする。また、エッチング剤は、フッ化ハロゲンを含む気体又は液体であることを特徴とする。

40

#### 【0011】

また、本発明の半導体装置の一は、第1の基板上に設けられた第1の導電層と、第1の

50

導電層を覆う下地絶縁層と、下地絶縁層上に設けられた第1の薄膜トランジスタ及び第2の薄膜トランジスタと、第1の薄膜トランジスタ及び第2の薄膜トランジスタを覆う層間絶縁層と、層間絶縁層上に設けられた第2の導電層及び第3の導電層と、第2の基板上に設けられた第4の導電層を有し、第2の導電層は、層間絶縁層に設けられた開口部を介して第1の薄膜トランジスタのソース領域及びドレイン領域に接続し、且つ下地絶縁層と層間絶縁層の各々に設けられた開口部を介して第1の導電層に接続し、第3の導電層は、層間絶縁層に設けられた開口部を介して第2の薄膜トランジスタのソース領域及びドレイン領域に接続し、且つ第4の導電層に接続することを特徴とする。

【0012】

また、第1の基板及び第2の基板は、可撓性を有する。

10

【0013】

第1の導電層及び前記第2の導電層、並びに前記第3の導電層及び前記第4の導電層はそれぞれ、導電性粒子で電気的に接続されている。また、第1の基板及び前記下地絶縁層、並びに前記層間絶縁層及び前記第2の基板それぞれは、導電性粒子を有する樹脂に接している。

【0014】

また、第1の導電層及び第4の導電層は、アンテナとして機能してもよい。更には、第1の導電層は、アンテナとして機能し、第4の導電層はセンサに電気的に接続してもよい。

【0015】

20

また、第2の導電層は、導電性粒子を有する樹脂を介して第1の導電層と接する領域及び層間絶縁層に接する領域を有する。

【0016】

また、第1の薄膜トランジスタと第2の薄膜トランジスタの各々は、サイドウォール絶縁層を有してもよい。

【発明の効果】

【0017】

本発明は、基板と下地絶縁層が密着した領域を設けながら剥離層を除去することで、下地絶縁層の上方に設けられた複数の薄膜トランジスタの飛散を防止し、薄膜集積回路を含む半導体装置の製造を容易に行うことができる。

30

【0018】

また、本発明の半導体装置は、薄膜集積回路部と、複数のアンテナを有する。このため、一つのアンテナが破損しても、他のアンテナで外部装置から供給される電磁波を受信することが可能であるため、耐久性を向上させることが可能である。また、複数のアンテナの通信する周波数帯が異なる場合、複数の周波数帯を受信することが可能であるため、リーダライタの選択幅が広がる。

【0019】

また、本発明の半導体装置は、薄膜集積回路部と、アンテナと、センサとを有する。このためセンサで検知した情報を薄膜集積回路部で処理した後、情報を記録することが可能である。また、センサで検知した情報を信号化し、アンテナを介して該信号をリーダライタに出力することが可能である。このため、従来の無線チップ等の半導体装置より、高付加価値を有する半導体装置を作製することが可能である。

40

【発明を実施するための最良の形態】

【0020】

本発明の実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同じものを指す符号は異なる図面間で共通して用いる。

【0021】

50

(実施の形態 1 )

本発明の半導体装置の作製方法について、図面を参照して説明する。

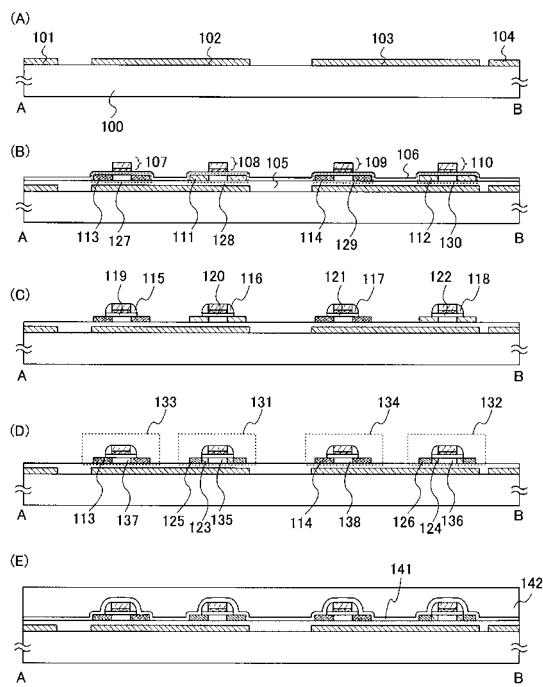

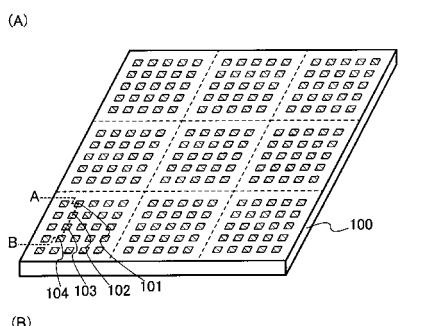

【 0 0 2 2 】

まず、基板 100 の一表面に、剥離層 101 ~ 104 を形成する（図 1 ( A ) の断面図と図 5 ( A ) の斜視図参照、図 1 ( A ) 中の A - B は図 5 ( A ) 中の A - B と対応する）。

【 0 0 2 3 】

図 1 ( A ) に示すように、基板 100 は、ガラス基板、石英基板、金属基板やステンレス基板の一表面に絶縁層を形成したもの、本工程の処理温度に耐えうる耐熱性があるプラスチック基板等を用いる。上記に挙げた基板 100 には、大きさや形状に制約がないため、例えば、基板 100 として、1 辺が 1 メートル以上あって、矩形状のものを用いれば、生産性を格段に向上させることができる。この利点は、円形のシリコン基板を用いる場合と比較すると、大きな優位点である。10

【 0 0 2 4 】

また、基板 100 上に設けられる薄膜集積回路は、後に基板 100 上から剥離される。従って、基板 100 を再利用して、当該基板 100 上に新たに薄膜集積回路を形成してもよい。この結果、コストを削減することができる。なお、再利用する基板 100 には、石英基板を用いることが好ましい。

【 0 0 2 5 】

剥離層 101 ~ 104 は、基板 100 の一表面に薄膜を形成した後、フォトリソグラフィ法により形成したレジストマスクを用いてエッチングして選択的に形成する。剥離層 101 ~ 104 は、公知の手段（スパッタリング法やプラズマ CVD 法等）により、タンゲステン ( W ) 、モリブデン ( Mo ) 、チタン ( Ti ) 、タンタル ( Ta ) 、ニオブ ( Nb ) 、ニッケル ( Ni ) 、コバルト ( Co ) 、ジルコニウム ( Zr ) 、亜鉛 ( Zn ) 、ルテニウム ( Ru ) 、ロジウム ( Rh ) 、鉛 ( Pb ) 、オスミウム ( Os ) 、イリジウム ( Ir ) 、珪素 ( Si ) から選択された元素、又は前記元素を主成分とする合金材料、又は前記元素を主成分とする化合物材料からなる層を、単層又は積層して形成する。珪素を含む層の結晶構造は、非晶質、微結晶、多結晶のいずれの場合でもよい。20

【 0 0 2 6 】

剥離層 101 ~ 104 が単層構造の場合、好ましくは、タンゲステン層、モリブデン層、又はタンゲステンとモリブデンの混合物を含む層を形成する。又は、タンゲステンの酸化物若しくは酸化窒化物を含む層、モリブデンの酸化物若しくは酸化窒化物を含む層、又はタンゲステンとモリブデンの混合物の酸化物若しくは酸化窒化物を含む層を形成する。なお、タンゲステンとモリブデンの混合物とは、例えば、タンゲステンとモリブデンの合金に相当する。30

【 0 0 2 7 】

剥離層 101 ~ 104 が積層構造の場合、好ましくは、1 層目としてタンゲステン層、モリブデン層、又はタンゲステンとモリブデンの混合物を含む層を形成し、2 層目として、タンゲステン、モリブデン又はタンゲステンとモリブデンの混合物の酸化物、窒化物、酸化窒化物又は窒化酸化物を形成する。

【 0 0 2 8 】

剥離層 101 ~ 104 として、タンゲステンを含む層とタンゲステンの酸化物を含む層の積層構造を形成する場合、タンゲステンを含む層を形成し、その上層に酸化珪素を含む層を形成することで、タンゲステン層と酸化珪素層との界面に、タンゲステンの酸化物を含む層が形成されることを活用してもよい。さらには、タンゲステンを含む層の表面を、熱酸化処理、酸素プラズマ処理、オゾン水等の酸化力の強い溶液での処理等を行ってタンゲステンの酸化物を含む層を形成してもよい。これは、タンゲステンを含む層を形成し、その上層にタンゲステンの窒化物、酸化窒化物及び窒化酸化物を含む層を形成する場合も同様であり、タンゲステンを含む層を形成後、その上層に窒化珪素層、酸化窒化珪素層、および窒化酸化珪素層を形成するとよい。40

【 0 0 2 9 】

10

20

30

40

50

タンゲステンの酸化物は、 $WO_x$ で表され、 $2 < x < 3$ であり、 $x$ が2の場合( $WO_2$ )、 $x$ が2.5の場合( $W_2O_5$ )、 $x$ が2.75の場合( $W_4O_{11}$ )、 $x$ が3の場合( $WO_3$ )などがある。タンゲステンの酸化物を形成するにあたり、上記に挙げた $x$ の値に特に制約はなく、そのエッチングレートなどを基に決めるといい。但し、エッティングレートの最も良いものは、酸素雰囲気下で、スパッタリング法により形成するタンゲステンの酸化物を含む層( $WO_x$ 、 $0 < x < 3$ )である。従って、作製時間の短縮のために、剥離層として、酸素雰囲気下でスパッタリング法によりタンゲステンの酸化物を含む層を形成するといい。

### 【0030】

また、上記の工程によると、基板100に接するように剥離層101～104を形成しているが、本発明はこの工程に制約されない。基板100に接するように下地絶縁層を形成し、その絶縁層に接するように剥離層101～104を設けてもよい。

10

### 【0031】

次に、剥離層101～104を覆うように、下地となる絶縁層105を形成する。絶縁層105は、公知の手段(スパッタリング法やプラズマCVD法等)により、珪素の酸化物又は珪素の窒化物を含む層を、単層又は積層で形成する。珪素の酸化物材料とは、珪素(Si)と酸素(O)を含む物質であり、酸化珪素、酸化窒化珪素、窒化酸化珪素等が該当する。珪素の窒化物材料とは、珪素と窒素(N)を含む物質であり、窒化珪素、酸化窒化珪素、窒化酸化珪素等が該当する。

### 【0032】

下地絶縁層105が2層構造の場合、例えば、1層目として窒化酸化珪素層を形成し、2層目として酸化窒化珪素層を形成するとよい。下地となる絶縁層が3層構造の場合、1層目の絶縁層として酸化珪素層を形成し、2層目の絶縁層として窒化酸化珪素層を形成し、3層目の絶縁層として酸化窒化珪素層を形成するとよい。又は、1層目の絶縁層として酸化窒化珪素層を形成し、2層目の絶縁層として窒化酸化珪素層を形成し、3層目の絶縁層として酸化窒化珪素層を形成するとよい。下地絶縁層は、基板100から後に形成される結晶質半導体層へ不純物が侵入されることを防止するプロッキング膜として機能する。

20

### 【0033】

次に、絶縁層105上に、非晶質半導体層(例えば非晶質珪素を含む層)を形成する。この非晶質半導体層は、公知の手段(スパッタリング法、LPCVD法、プラズマCVD法等)により、25～200nm(好ましくは30～150nm)の厚さで形成する。続いて、非晶質半導体層を公知の結晶化法(レーザ結晶化法、RTA又はファーネスアニール炉を用いる熱結晶化法、結晶化を助長する金属元素を用いる熱結晶化法、結晶化を助長する金属元素を用いる熱結晶化法とレーザ結晶化法を組み合わせた方法等)により結晶化して、結晶質半導体層を形成する。その後、得られた結晶質半導体層を所望の形状にエッチングして結晶質半導体層127～130を形成する。

30

### 【0034】

結晶質半導体層127～130の作製工程の具体例を挙げると、まず、プラズマCVD法を用いて、膜厚66nmの非晶質半導体層を形成する。次に、結晶化を助長する金属元素であるニッケルを含む溶液を非晶質半導体層上に保持させた後、非晶質半導体層に脱水素化の処理(500、1時間)と、熱結晶化の処理(550、4時間)を行って結晶質半導体層を形成する。その後、必要に応じてレーザ光を照射し、フォトリソグラフィ法を用いて形成したレジストマスクを用いて選択的にエッチングして結晶質半導体層127～130を形成する。

40

### 【0035】

なお、レーザ結晶化法で結晶質半導体層127～130を形成する場合、連続発振またはパルス発振の気体レーザ又は固体レーザを用いる。気体レーザとしては、エキシマレーザ、YAGレーザ、YVO<sub>4</sub>レーザ、YLFレーザ、YAlO<sub>3</sub>レーザ、ガラスレーザ、ルビーレーザ、Ti:サファイアレーザ等を用いる。固体レーザとしては、Cr、Nd、Er、Ho、Ce、Co、Ti又はTmがドーピングされたYAG、YVO<sub>4</sub>、YLF、YA

50

$\text{LO}_3$ などの結晶を使ったレーザを用いる。

【0036】

また、結晶化を助長する金属元素を用いて非晶質半導体層の結晶化を行うと、低温で短時間の結晶化が可能となるうえ、結晶の方向が揃うという利点がある一方、金属元素が結晶質半導体層に残存するためにオフ電流が上昇し、特性が安定しないという欠点がある。そこで、結晶質半導体層上に、ゲッタリングサイトとして機能する非晶質半導体層を形成するとよい。ゲッタリングサイトとなる非晶質半導体層には、リンやアルゴンの不純物元素を含有させる必要があるため、好適には、アルゴンを高濃度に含有させることができるとよい。その後、加熱処理（RTA法やファーネスアニール炉を用いた熱アニール等）を行って、非晶質半導体層中に金属元素を拡散させ、続いて、当該金属元素を含む非晶質半導体層を除去する。そうすると、結晶質半導体層中の金属元素の含有量を低減又は除去することができる。10

【0037】

次に、結晶質半導体層127～130を覆うゲート絶縁層106を形成する。ゲート絶縁層106は、公知の手段（プラズマCVD法やスパッタリング法）により、珪素の酸化物又は珪素の窒化物を含む層を、単層又は積層して形成する。具体的には、酸化珪素を含む層、酸化窒化珪素を含む層、窒化酸化珪素を含む層を、単層又は積層して形成する。

【0038】

次に、ゲート絶縁層106上に、第1の導電層と第2の導電層を積層して形成する。第1の導電層は、公知の手段（プラズマCVD法やスパッタリング法）により、20～100nmの厚さで形成する。第2の導電層は、公知の手段により、100～400nmの厚さで形成する。第1の導電層と第2の導電層は、タンタル（Ta）、タンゲステン（W）、チタン（Ti）、モリブデン（Mo）、アルミニウム（Al）、銅（Cu）、クロム（Cr）、ニオブ（Nb）等から選択された元素又はこれらの元素を主成分とする合金材料若しくは化合物材料で形成する。または、リン等の不純物元素をドーピングした多結晶珪素に代表される半導体材料により形成する。20

【0039】

第1の導電層と第2の導電層との組み合わせの例を挙げると、窒化タンタル（TaN）層とタンゲステン（W）層、窒化タンゲステン（WN）層とタンゲステン層、窒化モリブデン（MoN）層とモリブデン（Mo）層等が挙げられる。タンゲステンや窒化タンタルは、耐熱性が高いため、第1の導電層と第2の導電層を形成した後に、熱活性化を目的とした加熱処理を行うことができる。また、2層構造ではなく、3層構造の場合は、モリブデン層とアルミニウム層とモリブデン層の構造を採用するとよい。30

【0040】

更には、第1の導電層及び第2の導電層の積層構造の代わりに、第1の導電層又は第2の導電層と同様の材料を用いて、単層の導電層を形成してもよい。

【0041】

次に、フォトリソグラフィ法を用いてレジストからなるマスクを形成し、ゲート電極を形成するためのエッチング処理を行って、ゲート電極として機能する導電層（ゲート電極層とよぶことがある）107～110を形成する。40

【0042】

次に、結晶質半導体層128、130に、イオンドープ法又はイオン注入法により、N型を付与する不純物元素を低濃度に添加して、N型不純物領域111、112を形成する。N型を付与する不純物元素は、15族に属する元素を用いれば良く、例えばリン（P）、砒素（As）を用いる。

【0043】

続いて、結晶質半導体層127、129に、P型を付与する不純物元素を添加して、P型不純物領域113、114を形成する。P型を付与する不純物元素は、例えばボロン（B）を用いる。

【0044】

10

30

40

50

次に、ゲート絶縁層 106 と導電層 107～110 を覆うように、絶縁層を形成する。絶縁層は、公知の手段（プラズマ CVD 法やスパッタリング法）により、珪素、珪素の酸化物又は珪素の窒化物の無機材料を含む層（無機層と表記することがある）や、有機樹脂などの有機材料を含む層（有機層と表記することがある）を、単層又は積層して形成する。好ましくは、絶縁層として、珪素の酸化物からなる層を形成する。

#### 【0045】

次に、絶縁層を、垂直方向を主体とした異方性エッチングにより選択的にエッチングして、導電層 107～110 の側面に接する絶縁層（以下、サイドウォール絶縁層と呼ぶ。）

115～118 を形成する（図 1 (C) 参照）。サイドウォール絶縁層 115～118 は

、後に LDD 領域を形成するためのドーピング用のマスクとして用いる。

10

#### 【0046】

なお、サイドウォール絶縁層 115～118 を形成するためのエッチング工程により、ゲート絶縁層 106 もエッチングされ、ゲート絶縁層 119～122 が形成される。ゲート絶縁層 119～122 は、導電層 107～110 及びサイドウォール絶縁層 115～118 と重なる層である。このように、ゲート絶縁層 106 がエッチングされてしまうのは、ゲート絶縁層 106 とサイドウォール絶縁層 115～118 の材料のエッチングレートが同じであるためであり、図 1 (C) ではその場合を示している。従って、ゲート絶縁層 106 とサイドウォール絶縁層 115～118 の材料のエッチングレートが異なる場合には、サイドウォール絶縁層 115～118 を形成するためのエッチング工程を経ても、ゲート絶縁層 106 が残存する場合がある。

20

#### 【0047】

続いて、サイドウォール絶縁層 115～118 をマスクとして、結晶質半導体層 128、

130 に N 型を付与する不純物元素を添加して、第 1 の N 型不純物領域（LDD 領域とも

よぶ）123、124 と、第 2 の N 型不純物領域 125、126 とを形成する。第 1 の N

型不純物領域 123、124 が含む不純物元素の濃度は、第 2 の N 型不純物領域 125、

126 の不純物元素の濃度よりも低い。

#### 【0048】

なお、第 1 の N 型不純物領域 123、124 を形成するためには、ゲート電極を 2 層以上

の積層構造とし、該ゲート電極に異方性エッチングを行って該ゲート電極を構成する下

層の導電層をマスクとして用いる手法と、サイドウォール絶縁層をマスクとして用いる手

法がある。前者の手法を採用して形成された薄膜トランジスタは GOLD (Gate O

verlapped Lightly Doped drain) 構造と呼ばれる。本発明は、前者と後者のどちらの手法を用いてもよい。但し、後者のサイドウォール絶縁層を

マスクとして用いる手法を用いると、LDD 領域を確実に形成することができ、また、L

DD 領域の幅の制御が容易になるという利点がある。

30

#### 【0049】

上記工程を経て、N 型の薄膜トランジスタ 131、132 と、P 型の薄膜トランジスタ 1

33、134 が完成する。

#### 【0050】

N 型の薄膜トランジスタ 131 は、LDD 構造を有し、第 1 の N 型不純物領域 123（L

DD 領域ともよぶ）と第 2 の N 型不純物領域 125 とチャネル形成領域 135 を含む活性

層と、ゲート絶縁層 120 と、ゲート電極として機能する導電層 108 とを有する。

40

#### 【0051】

N 型の薄膜トランジスタ 132 は、LDD 構造を有し、第 1 の N 型不純物領域 124（L

DD 領域ともよぶ）と第 2 の N 型不純物領域 126 とチャネル形成領域 136 を含む活性

層と、ゲート絶縁層 122 と、ゲート電極として機能する導電層 110 とを有する。

#### 【0052】

P 型の薄膜トランジスタ 133 は、シングルドレイン構造を有し、P 型不純物領域 113

とチャネル形成領域 137 を含む活性層と、ゲート絶縁層 119 と、ゲート電極として機

能する導電層 107 とを有する。

50

**【0053】**

P型の薄膜トランジスタ134は、シングルドレイン構造を有し、P型不純物領域114とチャネル形成領域138を含む活性層と、ゲート絶縁層121と、ゲート電極として機能する導電層109とを有する。

**【0054】**

次に、薄膜トランジスタ131～134を覆うように、単層又は積層で絶縁層を形成する（図1（E）参照）。薄膜トランジスタ131～134を覆う絶縁層は、公知の手段（塗布法、液滴吐出法、CVD法、スパッタリング法等）により、珪素の酸化物や珪素の窒化物等の無機材料、ポリイミド、ポリアミド、ベンゾシクロブテン、アクリル、エポキシ、シロキサン等の有機材料等により、単層又は積層で形成する。シロキサンとは、例えば、シリコン（Si）と酸素（O）との結合で骨格構造が構成される物質に相当する。置換基として、少なくとも水素を含む有機基（例えばアルキル基、芳香族炭化水素）が用いられる。また、置換基として、フルオロ基を用いてもよい。さらには、置換基として、少なくとも水素を含む有機基と、フルオロ基とを用いてもよい。

10

**【0055】**

図示する断面構造では、薄膜トランジスタ131～134を覆うように、絶縁層を2層積層して形成した場合を示し、1層目の絶縁層141として酸化珪素を含む層を形成し、2層目の絶縁層142としてシロキサンを用いて形成する。さらには、第1の絶縁層と第2の絶縁層の間に窒化珪素を含む層を形成してもよい。

20

**【0056】**

なお、絶縁層141、142を形成する前、又は絶縁層141、142のうちの1つ又は両方の薄膜を形成した後に、半導体層の結晶性の回復や半導体層に添加された不純物元素の活性化、半導体層の水素化を目的とした加熱処理を行うとよい。加熱処理には、熱アニール、レーザアニール法又はRTA法などを適用するとよい。

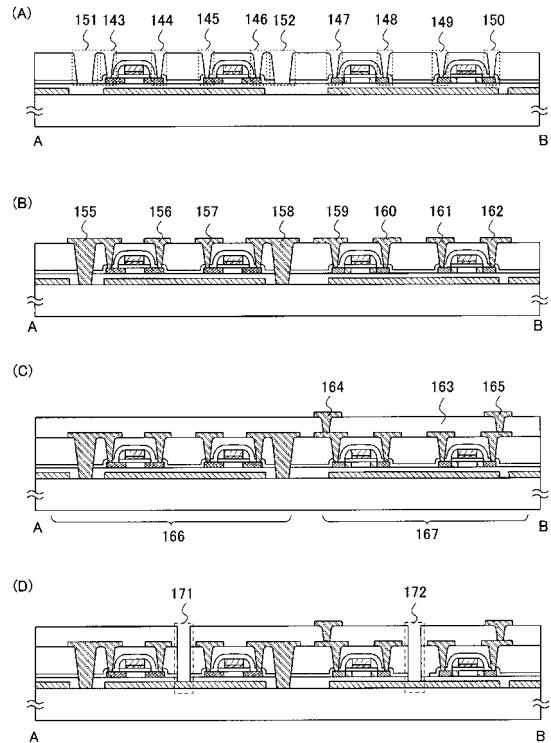

**【0057】**

次に、フォトリソグラフィ法により絶縁層141、142をエッチングして、P型不純物領域113、114と、第2のN型不純物領域125、126を露出させるコンタクトホール143～150、及び基板100を露出するコンタクトホール151、152を形成する（図2（A）参照）。

**【0058】**

30

なお、コンタクトホール151、152とは、剥離層に接しないように形成する。このような位置にコンタクトホール151、152を形成することで、剥離層を除去する際に、コンタクトホール内を充填する導電層も同時に除去することを回避することが可能である。この結果、不良な素子を削減することが可能であり、半導体装置の歩留まりを高めることが可能である。

**【0059】**

続いて、コンタクトホール143～152を充填するように、導電層を形成し、当該導電層をパターン加工して、導電層155～162を形成する（図2（B）参照）。なお、このようにして形成した導電層155、158の側面は、剥離層101～104に接しておらず、絶縁層141、142に接する。これは、剥離層101～104をエッチング剤により除去する際に、導電層155、158がエッチング剤により除去されないようにするためである。

40

**【0060】**

導電層155～162は、公知の手段（プラズマCVD法やスパッタリング法）により、チタン（Ti）、アルミニウム（Al）、ネオジウム（Nd）から選択された元素、又はこれらの元素を主成分とする合金材料若しくは化合物材料で、単層又は積層で形成する。アルミニウムを主成分とする合金材料とは、例えば、アルミニウムを主成分としニッケルを含む材料、又は、アルミニウムを主成分とし、ニッケルと、炭素と珪素の一方又は両方とを含む合金材料に相当する。

**【0061】**

50

導電層 155～162 は、例えば、バリア層とアルミニウムシリコン (Al-Si) 層とバリア層、バリア層とアルミニウムシリコン (Al-Si) 層と窒化チタン (TiN) 層とバリア層の積層構造を採用するとよい。なお、バリア層とは、チタン、チタンの窒化物、モリブデン、又はモリブデンの窒化物からなる層に相当する。アルミニウムやアルミニウムシリコンは抵抗値が低く、安価であるため、導電層 155～162 を形成する材料として最適である。また、上層と下層のバリア層を設けると、アルミニウムやアルミニウムシリコンのヒロックの発生を防止することができる。また下層のバリア層を設けると、アルミニウムやアルミニウムシリコンと、結晶質半導体層との、良好なコンタクトをとることができ。また、チタンは、還元性の高い元素であるため、チタンからなるバリア層を形成すると、結晶質半導体層上に薄い自然酸化膜ができていたとしても、この自然酸化膜を還元し、結晶質半導体層と良好なコンタクトをとることができる。

10

#### 【0062】

次に、導電層 155～162 を覆うように、単層又は積層で絶縁層 163 を形成する（図 2 (C) 参照）。導電層 155～162 を覆う絶縁層 163 は、薄膜トランジスタを覆う絶縁層 142 と同様の手法及び材料を用いて形成することができる。次に、導電層 155～162 を覆う絶縁層 163 にコンタクトホールを形成し、導電層 164、165 を形成する。導電層 164、165 は、外部の端子との接続用導電層として機能する。

#### 【0063】

次に、導電層 164、165 を覆うように、絶縁層を形成してもよい。当該絶縁層は、 DLC (ダイヤモンドライカーボン) などの炭素を含む層、窒化珪素を含む層、窒化酸化珪素を含む層、有機材料（好ましくはエポキシ樹脂）を含む層等に相当する。なお、絶縁層は、保護層として機能するものであり、必要がなければ形成しなくてもよい。また、絶縁層として、有機材料からなる層を形成すると、絶縁層 163 の膜厚を厚くすることが可能であり、この結果、剥離層 101～104 を除去した後でも、基板 100 上の複数の素子に重みがつき、基板 100 からの飛散を防止し、さらに、巻かれた形状にならぬく、素子の破壊や損傷を防止することができる。

20

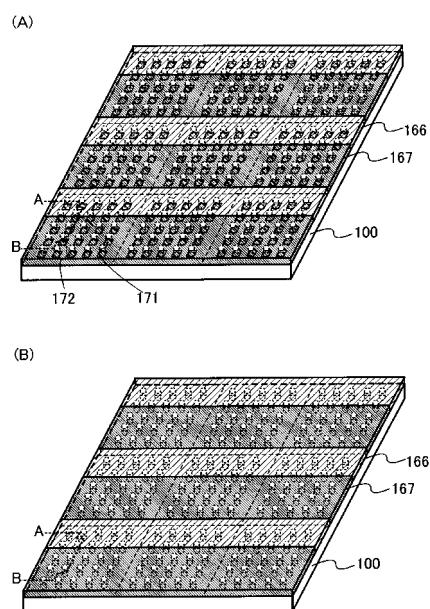

#### 【0064】

なお、ここでは、上記工程を経て完成した、薄膜トランジスタ 131、133 を含む素子と、導電層 155～158 とを合わせて第 1 の薄膜集積回路 166 とよび、薄膜トランジスタ 132、134 を含む素子と、導電層 159～162、164、165 とを合わせて、第 2 の薄膜集積回路 167 とよぶ（図 2 (C) の断面図と図 5 (B) の斜視図参照）。なお、図 2 (C) においては、第 1 の薄膜集積回路 166、第 2 の薄膜集積回路 167 それぞれ一つずつ示しているが、実際には図 5 (B) に示すように、第 1 の薄膜集積回路 166、第 2 の薄膜集積回路 167 が複数配列されている。このため、第 1 の薄膜集積回路 166、第 2 の薄膜集積回路 167 が複数配列されている層を、第 1 の薄膜集積回路 166 及び第 2 の薄膜集積回路 167 を有する層と示すときがある。

30

#### 【0065】

ここでは、第 1 の薄膜集積回路 166 は、後に接続される導電層 185 が受信する電磁波を処理する通信回路が少なくとも設けられている。また、第 2 の薄膜集積回路 167 は、後に接続される導電層 175 が受信する電磁波を処理する通信回路が少なくとも設けられている。なお、導電層 185 及び導電層 175 は、外部装置から供給される電磁波を受信するアンテナとして示している。

40

#### 【0066】

また、導電層 185 で構成されるアンテナ及び導電層 175 で構成されるアンテナが同一の周波数帯を受信することが可能な場合、それぞれの導電層は同一の薄膜集積回路に接続してもよい。この場合、導電層 185 で構成されるアンテナ及び導電層 175 で構成されるアンテナは、同一の形状であることが好ましい。

#### 【0067】

また、導電層 185 で構成されるアンテナ及び導電層 175 で構成されるアンテナが異なる周波数帯を受信することが可能な場合、それぞれの導電層は異なる薄膜集積回路に接続

50

する。この場合、導電層 185 で構成されるアンテナ及び導電層 175 で構成されるアンテナの形状は異なっていてもよい。このため、アンテナの選択幅が広がる。

#### 【0068】

次に、剥離層 101～104 の一部又は全部が露出するように、フォトリソグラフィ法により絶縁層 105、141、142、163 をエッチングして、開口部 171、172 を形成する（図 2（D）の断面図と図 6（A）の斜視図参照）。

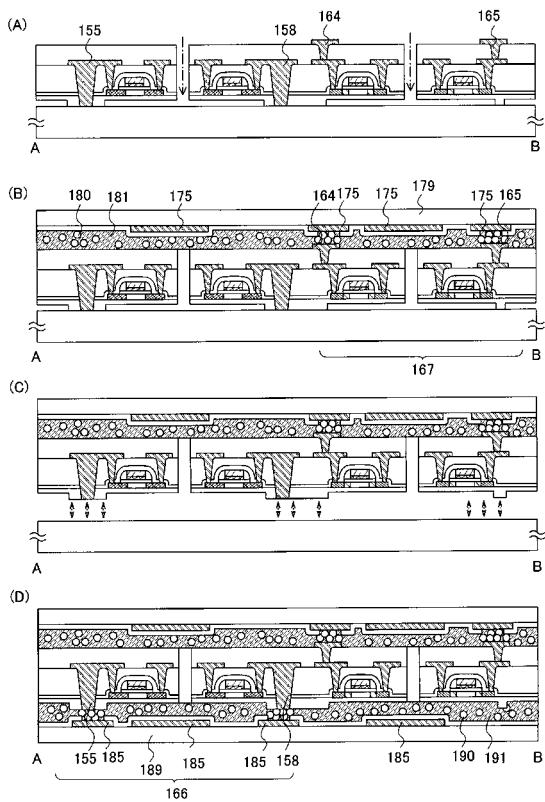

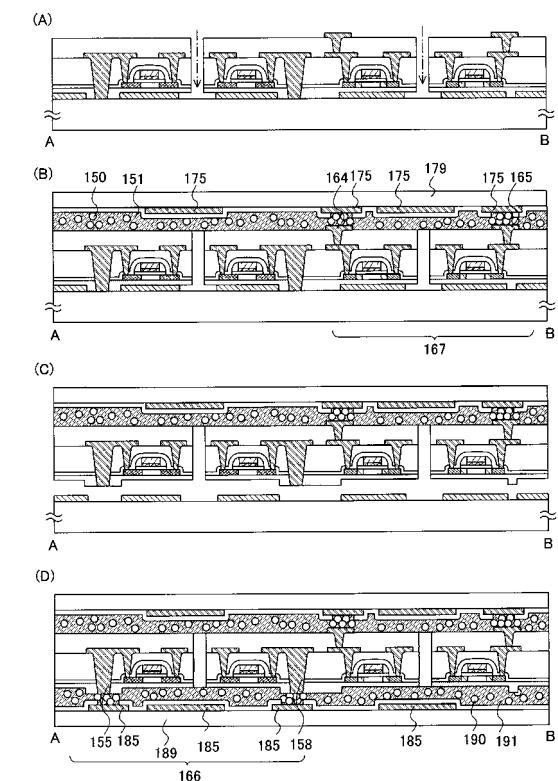

#### 【0069】

次に、開口部 171、172 にエッチング剤を導入して、剥離層 101～104 を除去する（図 3（A）の断面図と図 6（B）の斜視図参照）。エッチング剤は、ウェットエッチングであれば、フッ酸を水やフッ化アンモニウムで希釈した混液、フッ酸と硝酸の混液、フッ酸と硝酸と酢酸の混液、過酸化水素と硫酸の混液、過酸化水素とアンモニア水と水の混液、過酸化水素と塩酸と水の混液等を用いる。また、ドライエッチングであれば、フッ素等のハロゲン系の原子や分子を含む気体、又は酸素を含む気体を用いる。好ましくは、エッチング剤として、フッ化ハロゲン又はハロゲン間化合物を含む気体又は液体を使用する。例えば、フッ化ハロゲンを含む気体として三フッ化塩素（ $C_1F_3$ ）を使用する。なお、導電層 155、158 は、剥離層 101～104 に接しないように設けられているため、この工程において、導電層 155、158 は、エッチング剤によりエッチングされない。

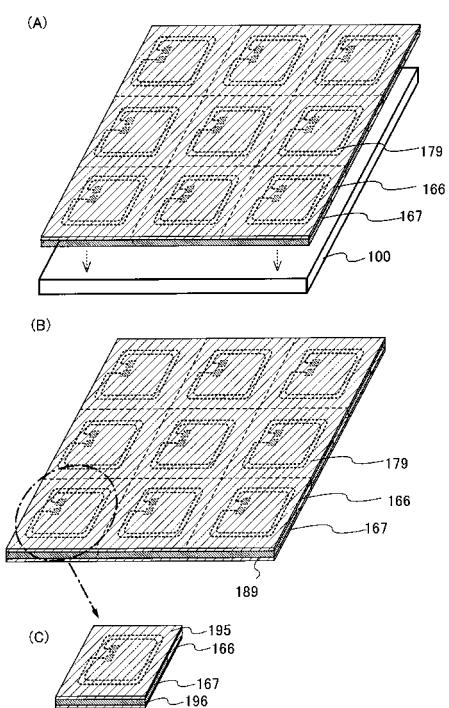

#### 【0070】

次に、第 1 の薄膜集積回路 166 及び第 2 の薄膜集積回路 167 を有する層の一方の面を、導電層 175 が設けられた基板 179 に接着させる（図 3（B）の断面図参照）。なお、第 1 の薄膜集積回路 166 及び第 2 の薄膜集積回路 167 を有する層の一方の面とは、導電層 164、165 及び開口部 171、172 が露出されている面のことである。この際、第 1 の薄膜集積回路 166 及び第 2 の薄膜集積回路 167 を有する層と、基板 179 とを、導電性粒子 180 を含む樹脂 181 を用いて接着して一体化させると共に、第 2 の薄膜集積回路 167 が含む導電層 164、165 と、基板 179 上の導電層 175 とを、導電性粒子 180 を介して接触させる。この後、基板 100 から、第 1 の薄膜集積回路 166 及び第 2 の薄膜集積回路 167 を完全に剥離する（図 3（C）の断面図と図 7（A）の斜視図参照）。

#### 【0071】

導電層 175 が設けられた基板 179 は、フィルム（ポリプロピレン、ポリエステル、ビニル、ポリフッ化ビニル、塩化ビニルなどからなる）、纖維質な材料からなる紙、基材フィルム（ポリエステル、ポリアミド、無機蒸着フィルム、紙類等）と接着性合成樹脂フィルム（アクリル系合成樹脂、エポキシ系合成樹脂等）との積層フィルムなどに相当する。フィルムは、熱圧着により、被処理体と封止処理が行われるものであり、封止処理を行う際には、フィルムの最表面に設けられた接着層か、又は最外層に設けられた層（接着層ではない）を加熱処理によって溶かし、加圧により接着する。

#### 【0072】

続いて、第 1 の薄膜集積回路 166 及び第 2 の薄膜集積回路 167 を有する層の他方の面を、導電層 185 が設けられた基板 189 に接着させる（図 3（D）の断面図と図 7（B）の斜視図参照）。なお、第 1 の薄膜集積回路 166 及び第 2 の薄膜集積回路 167 を有する層の他方の面とは、導電層 155、158 及び絶縁層 105 が露出されている面のことである。第 1 の薄膜集積回路 166 及び第 2 の薄膜集積回路 167 を有する層と、基板 189 とを、導電性粒子 190 を含む樹脂 191 を用いて接着して一体化させると共に、第 1 の薄膜集積回路 166 が含む導電層 155、158 と、基板 189 上の導電層 185 とを、導電性粒子 190 を介して接触させる。

#### 【0073】

次に、第 1 の薄膜集積回路 166 及び第 2 の薄膜集積回路 167 を有する層と、導電層を有する基板 179、189 とが一体化したものを、スライシング装置やレーザ照射装置等を用いて分断する（図 7（C）の斜視図参照）。上記工程を経て、分断された基板 195

10

20

30

40

50

、196と、分断された第1の薄膜集積回路166及び第2の薄膜集積回路167で形成される層とで構成される無線チップ（無線プロセッサ、無線メモリ、無線タグともよぶ）として機能する半導体装置が完成する。

#### 【0074】

なお、本実施形態では、第1の薄膜集積回路166及び第2の薄膜集積回路167を有する層と、導電層を有する基板179、189とを一体化させた後、分断して無線チップ（無線プロセッサ、無線メモリ、無線タグともよぶ）として機能する半導体装置を形成しているが、この工程に限定されない。第1の薄膜集積回路166及び第2の薄膜集積回路167を有する層と、導電層を有する基板179を一体化し、分断した後、分断された第1の薄膜集積回路166及び第2の薄膜集積回路167を有する層に導電層を有する基板を接着してもよい。10

#### 【0075】

本実施の形態では、分断された基板195、196上にアンテナとして機能する導電層175、185が設けられた場合を示している。アンテナとして機能する導電層は、アルミニウム、銅、銀を含む金属材料で形成する。例えば、銅又は銀のペースト状組成物を、スクリーン印刷、オフセット印刷、インクジェット方式の印刷法で形成することができる。また、スパッタリングなどでアルミニウム膜を形成し、エッチング加工により形成しても良い。その他、電解メッキ法、無電解メッキ法を用いて形成しても良い。

#### 【0076】

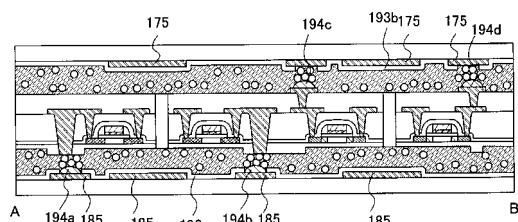

なお、上記の実施の形態によると、第1の薄膜集積回路166及び第2の薄膜集積回路167を有する層と導電層を有する基板179、189とは、導電性粒子180、190を含む樹脂181、191を用いて接着されている。しかし、本発明はこの形態に制約されず、バンプ194a～194dをさらに用いて、第1の薄膜集積回路166及び第2の薄膜集積回路167を有する層と基板179、189それぞれとを接着してもよい（図24参照）。20

#### 【0077】

なお、基板179、189上の導電層175、185は保護絶縁層193a、193bに覆われており、バンプ194a～194dや導電性粒子が接する箇所には、保護絶縁層193a、193bに開口部が設けられている。

#### 【0078】

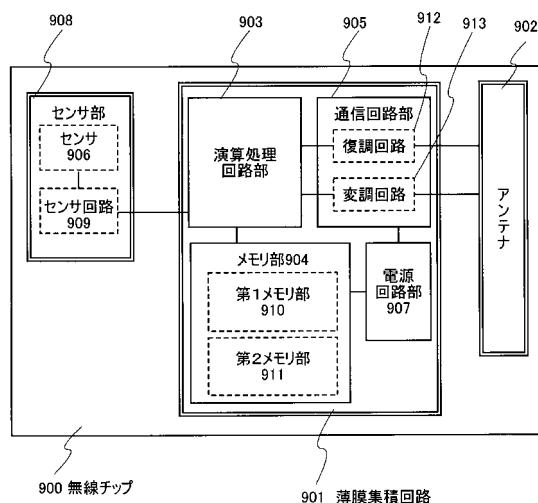

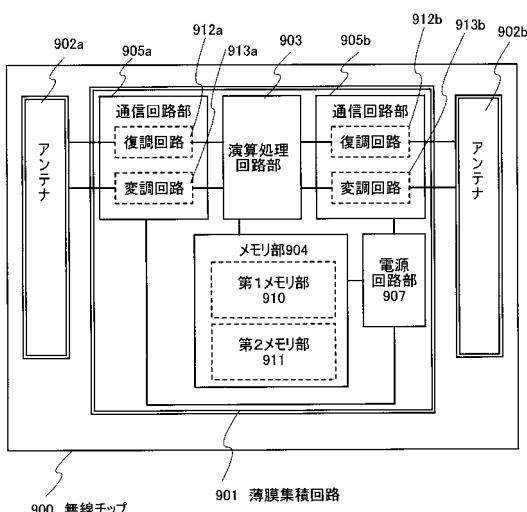

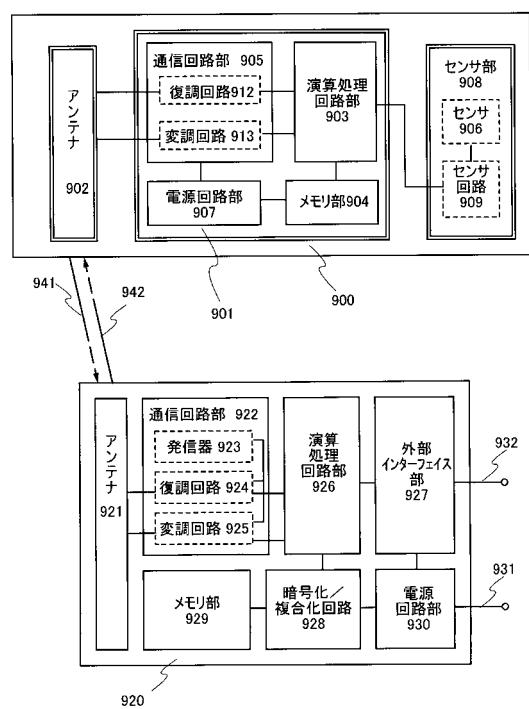

次に、図14に、本実施形態で示す無線チップ900の構成を示す。本実施形態の無線チップは、薄膜集積回路901、アンテナ902a、902bを備える。30

#### 【0079】

薄膜集積回路901は、図3乃至図7に示す第1の薄膜集積回路166及び第2の薄膜集積回路167で構成されており、演算処理回路部903、メモリ部904、通信回路部905a、905b、電源回路部907を備える。メモリ部904は、読み出し専用メモリや、書き換え可能メモリの一方若しくは双方を備えている。メモリ部904は、静态RAM(Static RAM)、EEPROM(Electrically Erasable Programmable Read-Only Memory)、フラッシュメモリなどで構成することで、アンテナ902a、902bを経由して受信した外部からの情報を隨時記録することができる。メモリ部904は、アンテナ902a、902bを経由して受信した信号を格納する第1メモリ部910と、リーダ/ライタ装置から書き込まれた情報を記録する第2メモリ部911に分けて構成することもできる。また、マスクROMやプログラマブルROMで読み出し専用メモリ部を設けておいても良い。40

#### 【0080】

第1メモリ部910は逐次書き込みを可能とするとともに、データが消失しないフラッシュメモリなどで構成することが好ましい。また、フローティングゲート構造の記憶素子であって、一度だけ書き込み可能な記憶素子を適用することが好ましい。

#### 【0081】

10

20

30

40

50

なお、メモリ部 904 の構成を逐次書き込みを可能とするとともに、データが消失しないフローティングゲート構造の記憶素子で構成してもよい。特に、フローティングゲート構造の記憶素子であって、一度だけ書き込み可能な記憶素子を適用することが好ましい。この構成の無線チップは、メモリ部に記憶した情報を読み出す機能のみを持っている。機能を単純化することにより、無線チップを小型化することができる。また、省電力化することができる。

#### 【0082】

通信回路部 905a、905b は、それぞれ復調回路 912a、912b、変調回路 913a、913b を含んでいる。復調回路 912a、912b は、それぞれアンテナ 902a、902b を経由して入力される信号を復調して、演算処理回路部 903 に出力する。信号には、メモリ部 904 に記憶させる情報を含んでいる。また、メモリ部 904 から読み出された情報は、演算処理回路部 903 を通して、それぞれ変調回路 913a、913b に出力される。変調回路 913a、913b は、この信号を無線通信可能な信号に変調して、それぞれアンテナ 902a、902b を介して外部装置に出力する。

#### 【0083】

アンテナ 902a、902b は、リーダ／ライタと呼ばれる外部装置から供給される電磁波を受信して、必要な電力を電源回路部 907 で発生させている。アンテナ 902a、902b は通信する周波数帯に応じて適宜設計すれば良い。電磁波の周波数帯は、135 kHz までの長波帯、6～60 MHz（代表的には 13.56 MHz）の短波帯、400～950 MHz の超短波帯、2～25 GHz のマイクロ波帯などを使用することができる。長波帯や短波帯のアンテナは、ループアンテナによる電磁誘導を利用したものが利用される。その他に相互誘導作用（電磁結合方式）又は静電気による誘導作用（静電結合方式）を利用したものであっても良い。電力は、アンテナを介して電源回路部 907 で生成する。また、当該電力を用いて、演算処理回路部 903、メモリ部 904 及び通信回路部 905a、905b を動作させる。なお、アンテナ 902a をデータ通信用アンテナとし、アンテナ 902b を電力供給用アンテナとして分離して設けても良い。

#### 【0084】

アンテナ 902a とアンテナ 902b が、同一の周波数帯を受信することが可能な場合、一つの通信回路部（例えば、通信回路部 905a）によって、信号の復調及び変調を行つても良い。但し、この場合、アンテナ 902a とアンテナ 902b は同一の形状であることが好ましい。

#### 【0085】

アンテナ 902a とアンテナ 902b が、異なる周波数帯を受信することが可能な場合、それぞれのアンテナ 902a とアンテナ 902b は異なる通信回路部 905a、905b に接続することが好ましい。この場合、アンテナ 902a とアンテナ 902b の形状は異なっていてもよい。

#### 【0086】

本実施の形態により、基板と下地用絶縁層が密着した領域を設けながら剥離層を除去することで、下地用絶縁層の上方に設けられた薄膜集積回路の飛散を防止しながら、薄膜集積回路を含む半導体装置を容易に製造することができる。

#### 【0087】

また、本実施の形態の半導体装置は、薄膜集積回路部と、複数のアンテナを有する。このため、一つのアンテナが破損しても、他のアンテナで外部装置から供給される電磁波を受信することが可能であるため、耐久性を向上させることができある。また、複数のアンテナの通信する周波数帯が異なる場合、複数の周波数帯を受信することができるため、異なる様式のリーダライタと送受信することが可能である。

#### 【0088】

##### (実施の形態 2)

上記の実施の形態によると、剥離層 101～104 は、エッチング剤により完全に除去している（図 3 (A) 参照）。しかし、本発明はこの形態に制約されず、剥離層 101～1

10

20

30

40

50

04を選択的に除去してもよい(図4(A)参照)。その後、第1の薄膜集積回路166及び第2の薄膜集積回路167を有する層上に導電層175が設けられた基板179を設けて、基板一体化した後、物理的手段(物理的な力)により、基板100から、第1の薄膜集積回路166及び第2の薄膜集積回路167を有する層と、導電層175が設けられた基板179基板とを剥離してもよい(図4(C)参照)。物理的手段(物理的な力)により、基板100から第1の薄膜集積回路166及び第2の薄膜集積回路167を有する層を剥離すると、剥離層101～104は基板100上に残存する場合と、基板100から剥離層101～104と第1の薄膜集積回路166、第2の薄膜集積回路167が共に剥離される場合の2つの場合があり、本形態では後者の場合を示す(図4(C)参照)。なお、物理的手段(物理的な力)とは、ノズルから吹き付けられるガスの風圧、超音波等の外部からストレスを与える手段に相当する。10

#### 【0089】

上記のように、剥離層101～104をエッティング剤により完全に除去するのではなく、剥離層101～104を選択的に除去して、物理的手段(物理的な力)を併用することにより、薄膜集積回路の飛散を防止すると共に、剥離層101～104を除去する時間を短時間で済ませることができるとため、生産性を向上させることができる。

#### 【0090】

##### (実施の形態3)

本実施の形態では、実施の形態1及び実施の形態2において、導電層を有する基板179又は導電層を有する基板189の一方の代わりにセンサを有する基板を接着する例を示す。20

#### 【0091】

センサとしては、温度、湿度、照度、ガス(気体)、重力、圧力、音(振動)、加速度、その他の特性を物理的又は化学的手段により検出する素子が挙げられる。センサは、代表的には抵抗素子、容量結合素子、誘導結合素子、光起電力素子、光電変換素子、熱起電力素子、トランジスタ、サーミスタ、ダイオードなどの素子で形成される。

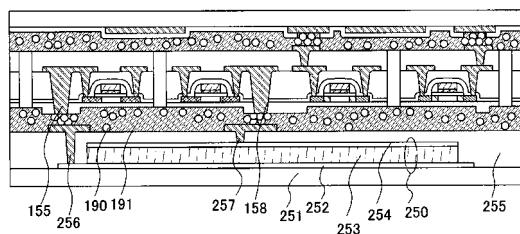

#### 【0092】

図8では、実施の形態1の導電層を有する基板189の代わりに、センサ、代表例として光センサを設けた半導体装置の断面を示す図である。基板251上には、第1の電極252、受光層253、第2の電極254で形成されるフォトダイオード250が形成されている。また、フォトダイオード250は、層間絶縁層255で覆われてあり、層間絶縁層255を介して第1の電極に接続されている接続用の導電層256、第2の電極に接続されている接続用の導電層257が形成されている。第2の薄膜集積回路の導電層155、158と、基板251上の導電層256、257とが、それぞれ導電性粒子190で接するように、第1の薄膜集積回路166及び第2の薄膜集積回路167を有する層と基板251とが接着されている。また、センサの他に、基板251上にセンサ回路を設けてよい。なお、図8ではフォトダイオードを用いて示したが、そのかわりフォトトランジスタを用いることができる。更には、光センサの代わりに、温度、湿度、照度、ガス(気体)、重力、圧力、音(振動)、加速度、その他の特性を検知する素子を適宜設けることが可能である。また、接続用の導電層256、257の代わりに、センサを構成する導電層が導電層155、158と接しても良い。30

#### 【0093】

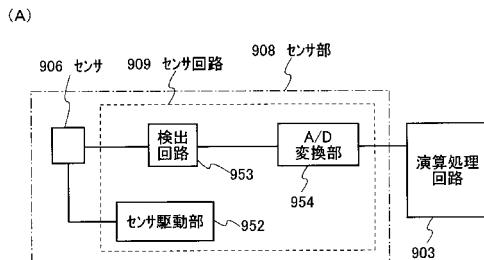

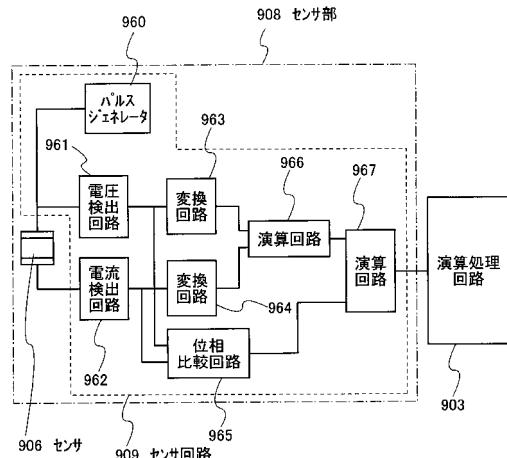

次に、図9に、薄膜集積回路901、センサ部908及びアンテナ902を備えた無線チップ900の構成を示す。センサ部908は、温度、湿度、照度、ガス(気体)、重力、圧力、音(振動)、加速度、その他の特性を物理的又は化学的手段により検出する。センサ部908は、センサ906とそれを制御するセンサ回路909が含まれている。センサ906は抵抗素子、容量結合素子、誘導結合素子、光起電力素子、光電変換素子、熱起電力素子、トランジスタ、サーミスタ、ダイオードなどの素子で形成される。センサ回路909はインピーダンス、リアクタンス、インダクタンス、電圧又は電流の変化を検出し、アナログ/デジタル変換(A/D変換)して演算処理回路部903に信号を出力する。4050

## 【0094】

薄膜集積回路901は、演算処理回路部903、メモリ部904、通信回路部905、電源回路部907を備える。メモリ部904は、センサ部908及びアンテナ902を経由して受信した外部からの情報を随時記録することができる。メモリ部904は、センサ部908で検知した信号を格納する第1メモリ部910と、リーダ/ライタ装置から書き込まれた情報を記録する第2メモリ部911に分けて構成することもできる。

## 【0095】

第1メモリ部910はセンサ部908で検知した情報を記録するために、逐次書き込みを可能とするとともに、データが消失しないフラッシュメモリなどで構成することが好ましい。また、フローティングゲート構造の記憶素子であって、一度だけ書き込み可能な記憶素子を適用することが好ましい。10

## 【0096】

通信回路部905は、復調回路912、変調回路913を含んでいる。復調回路912は、アンテナ902を経由して入力される信号を復調して、演算処理回路部903に出力する。信号にはセンサ部908を制御する信号や、メモリ部904に記憶させる情報を含んでいる。また、センサ回路909から出力される信号や、メモリ部904から読み出された情報は、演算処理回路部903を通して変調回路913に出力される。変調回路913は、この信号を無線通信可能な信号に変調して、アンテナ902を介して外部装置に出力する。

## 【0097】

演算処理回路部903、センサ部908、メモリ部904及び通信回路部905を動作させるのに必要な電力は、アンテナ902を介して供給される。20

## 【0098】

本実施の形態により、基板と下地絶縁層が密着した領域を設けながら剥離層を除去することで、下地絶縁層の上方に設けられた薄膜集積回路の飛散を防止しながら、薄膜集積回路を含む半導体装置を容易に製造することができる。

## 【0099】

また、本発明の半導体装置は、薄膜集積回路部と、アンテナと、センサとを有する。このためセンサで検知した情報を薄膜集積回路部で処理した後、情報を記録することができる。また、センサで検知した情報を信号化し、アンテナを介して該信号をリーダ/ライタに出力することができる。このため、従来の無線チップ等の半導体装置より、高付加価値を有する半導体装置を作製することができる。30

## 【0100】

## (実施の形態4)

上記の実施の形態では、無線チップとして機能する半導体装置について説明したが、本発明はこの形態に制約されない。そこで本実施の形態では、上記構成とは異なる半導体装置について説明する。

## 【0101】

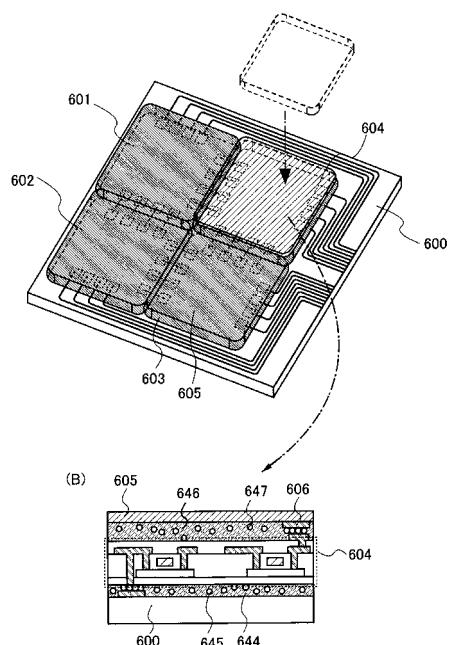

まず、複数の機能が集積された本発明の半導体装置について説明する(図18(A)(B)参照)。導電層が設けられた基板600上には、複数の薄膜集積回路601~604が接着されている。基板600上の導電層と、薄膜集積回路601~604の各々が含む一方の面の接続用導電層とは、導電性粒子645を含む樹脂644を用いて接着されている。薄膜集積回路601~603の各々は、中央処理ユニット(CPU、Central Processing Unit)、メモリ、ネットワーク処理回路、ディスク処理回路、画像処理プロセッサ、音声処理プロセッサ等から選択された1つ又は複数として機能する。40

また、薄膜集積回路604は、実施の形態1~実施の形態3で形成される薄膜集積回路を設けることができる。ここでは、一つのアンテナ及び薄膜集積回路を有する例を示す。薄膜集積回路604の他方の面の接続用導電層と、アンテナ等の導電層を有する基板605の接続用導電層606とが導電性粒子647を含む樹脂646を用いて接着されている。50

**【0102】**

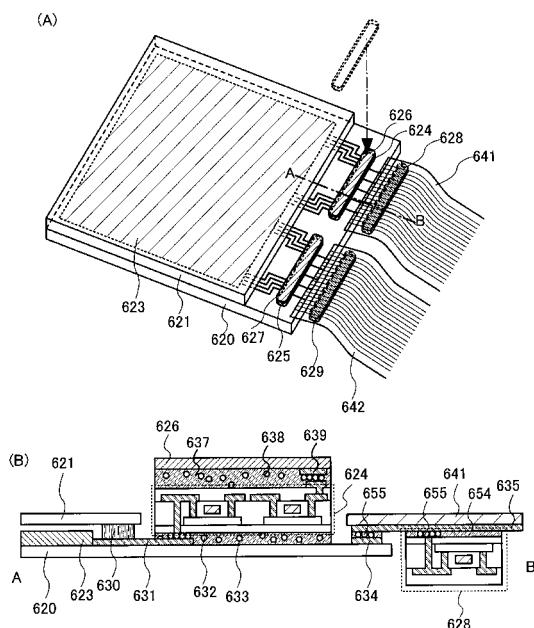

次に、表示部を有する本発明の半導体装置について説明する（図19（A）（B）参照）。図19（A）中のA-Bは図19（B）中のA-Bに対応する。）。基板620上には、薄膜集積回路624、625が接着され、接続フィルム641、642上には薄膜集積回路628、629が接着されている。薄膜集積回路624、625として、実施の形態1～実施の形態3で形成される薄膜集積回路を設けることが可能である。ここでは、一つのアンテナ及び薄膜集積回路を有する例を示す。

**【0103】**

表示部623と薄膜集積回路624の裏面の接続用導電層とは、基板620上の導電層631を介して接続する。また、薄膜集積回路624の表面の接続用導電層は、アンテナ等の導電層を有する基板626の接続用導電層639が導電性粒子638を含む樹脂637を用いて接着されている。10

**【0104】**

薄膜集積回路624と薄膜集積回路628とは、基板620上の導電層634と接続フィルム641上の導電層635を介して接続する。これらの導電層の接続には、導電性粒子655を含む樹脂654を用いている。また、基板620と対向基板621は、シール材630により接着されている。

**【0105】**

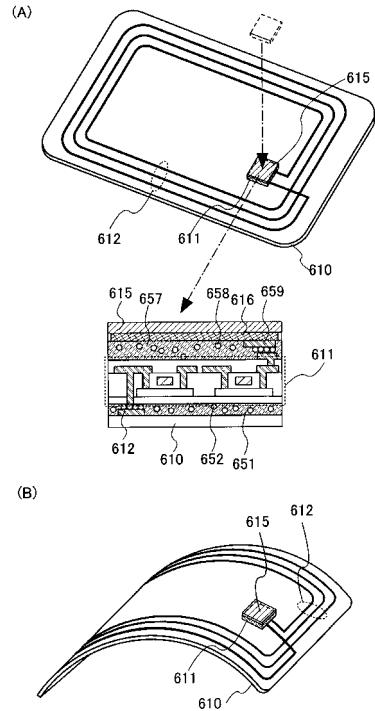

次に、I Cカードとして機能する本発明の半導体装置について説明する（図20（A）（B）参照）。基板610上には、薄膜集積回路611が接着されている。実施の形態1～実施の形態3で形成される薄膜集積回路を設けることが可能である。ここでは、センサ及び薄膜集積回路を有する例を示す。基板610上の導電層612と、薄膜集積回路611の裏面の接続用導電層とは、導電性粒子652を含む樹脂651を用いて接着されている。また、薄膜集積回路611の表面の接続用導電層は、センサ素子616を有する基板615の接続用導電層659と導電性粒子658を含む樹脂657を用いて接着している。20

**【0106】**

本発明の半導体装置が含む薄膜集積回路は小型、薄型、軽量を実現しており、複数のシステムを含む半導体装置（図18参照）、表示機能を有する半導体装置（図19参照）、I Cカード（図20）の各々に用いることにより、さらなる高機能化と高付加価値化を実現することができる。30

**【実施例1】****【0107】**

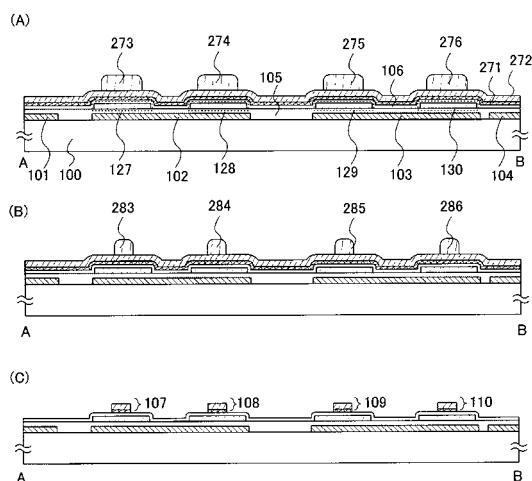

本実施例では、微細な導電層を形成する手法について説明する（図10参照。）。

**【0108】**

まず、絶縁表面を有する基板100上に、剥離層101～104、絶縁層105、結晶質半導体層127～130、ゲート絶縁層106、導電層271、272を形成する。次に、導電層271、272上に、フォトマスクを用いて、レジストマスク273～276を形成する（図10（A）参照）。

**【0109】**

次に、酸素プラズマ処理等の公知のエッチング処理により、レジストマスク273～276をエッチングして、新たなレジストマスク283～286を形成する（図10（B）参照）。上記の工程を経たレジストマスク283～286は、フォトリソグラフィ法により形成することができる限界を超えた、微細なものとすることができます。40

**【0110】**

次に、レジストマスク283～286を用いて、エッチング処理を行うと、微細な導電層107～110を作製することができる（図10（C）参照）。導電層107～110は、ゲート電極として機能する。

**【0111】**

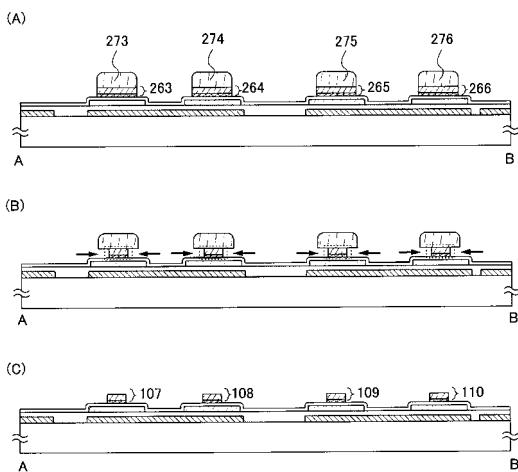

また、上記とは異なる手法として、まず、絶縁表面を有する基板100上に、剥離層10

50

1 ~ 1 0 4、絶縁層 1 0 5、結晶質半導体層 1 2 7 ~ 1 3 0、ゲート絶縁層 1 0 6、導電層 2 7 1、2 7 2、レジストマスク 2 7 3 ~ 2 7 6 を形成する(図 1 0 (A) 参照)。

#### 【0 1 1 2】

次に、レジストマスク 2 7 3 ~ 2 7 6 を用いて、導電層 2 7 1、2 7 2 をエッチングして、導電層 2 6 3 ~ 2 6 6 を形成する(図 1 1 (A) 参照)。

#### 【0 1 1 3】

続いて、レジストマスク 2 7 3 ~ 2 7 6 を除去せず、レジストマスク 2 7 3 ~ 2 7 6 と導電層 2 6 3 ~ 2 6 6 の積層体のうち、導電層 2 6 3 ~ 2 6 6 の側面のみを選択的にエッチングする(図 1 1 (B) 参照)。このようなエッチング方法としては、等方性のドライエッチングまたはウェットエッチングを用いればよい。そうすると、上記の手法と同様に、10 フォトリソグラフィ法により形成することができる限界を変えた微細な導電層 1 0 7 ~ 1 1 0 を形成することができる(図 1 1 (C) 参照)。導電層 1 0 7 ~ 1 1 0 は、ゲート電極として機能する。

#### 【0 1 1 4】

上記のいずれかの方法により、チャネル長が 0 . 5  $\mu\text{m}$  以下の微細な薄膜トランジスタを形成することができる。薄膜トランジスタが微細なものであれば、その分高集積化を可能とするので、素子が高性能化された半導体装置の作製が実現する。また、チャネル形成領域の幅が狭くなるため、高速動作を実現する。

#### 【実施例 2】

#### 【0 1 1 5】

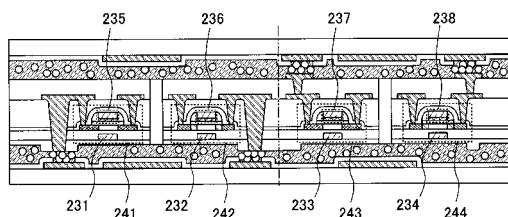

無線チップは、アンテナより電源を供給するため、電源の安定化が難しく、消費電力を極力抑制することが必要となる。仮に、無線チップの消費電力が増加すると、電磁波を強力に入力する必要があるため、リーダライタの消費電力の増加、他の装置や人体への悪影響、無線チップとリーダライタとの通信距離に制約が生じるなどの不都合が生じる。

#### 【0 1 1 6】

そこで、本発明は、下部ゲート電極 2 3 2、2 3 4 と上部ゲート電極 2 3 6、2 3 8 の2つのゲート電極をそれぞれ含むN型の薄膜トランジスタ 2 4 2、2 4 4 と、下部ゲート電極 2 3 1、2 3 3 と上部ゲート電極 2 3 5、2 3 7 の2つのゲート電極をそれぞれ含むP型の薄膜トランジスタ 2 4 1、2 4 3 を用いた半導体装置を提供する(図 1 2 参照)。

#### 【0 1 1 7】

消費電力を抑制するためには、下部ゲート電極 2 3 1 ~ 2 3 4 にバイアス電圧を印加する方法が有効であり、具体的には、N型の薄膜トランジスタ 2 4 2、2 4 4 の下部ゲート電極 2 3 2、2 3 4 に対する負のバイアス電圧の印加により、しきい値電圧を高めて、リーク電流を減少させることができる。また、正のバイアス電圧の印加により、しきい値電圧を下げて、チャネル形成領域に電流を流れやすくすることができる。従って、薄膜トランジスタ 2 4 2、2 4 4 を、より高速化、若しくはより低電圧で動作させることが可能である。

#### 【0 1 1 8】

P型の薄膜トランジスタ 2 4 1、2 4 3 の下部ゲート電極 2 3 1、2 3 3 に対する正のバイアス電圧の印加により、しきい値電圧を高めて、リーク電流を減少させることができる。また、負のバイアス電圧の印加により、しきい値電圧を下げて、チャネル形成領域に電流を流れやすくすることができる。従って、薄膜トランジスタ 2 4 1、2 4 3 を、より高速化、若しくは低電圧で動作させることができる。

#### 【0 1 1 9】

上記の通り、下部ゲート電極に印加するバイアス電圧を制御することで、薄膜トランジスタ 2 4 1 ~ 2 4 4 のしきい値電圧を変えて、リーク電流を減少させ、その結果、無線チップ自体の消費電力を抑制することができる。従って、暗号処理などの複雑な処理を行つても、電源が不安定になることがなく、電源の安定化を実現する。また、電磁波を入力する必要がなく、リーダライタとの通信距離を改善することができる。

#### 【0 1 2 0】

10

20

30

40

50

なお、薄膜トランジスタ 241～244に対するバイアス電圧の印加は、専用の制御回路を設けて制御するとよい。

**【実施例 3】**

**【0121】**

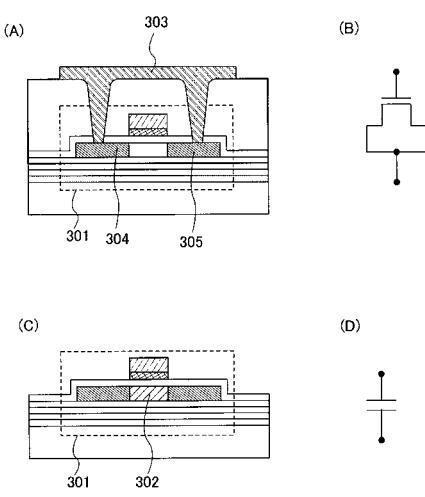

本発明の半導体装置に用いる容量用トランジスタの断面構造について説明する（図13（A）参照）。容量用トランジスタ301は、ソース電極とドレイン電極が互いに接続されている。即ち、導電層303によってソース領域304及びドレイン領域305が接続されている。このため、容量用トランジスタ301がオンすると、ゲート電極とチャネル形成領域との間に容量が形成される。このような容量用トランジスタ301の断面構造は、通常の薄膜トランジスタの断面構造と変わらない。等価回路図は、図13（B）のように表される。10

**【0122】**

但し、上記の構成では、容量を形成するのに、ゲート絶縁膜を用いるため、その容量値は、容量用トランジスタ301のしきい値電圧の変動に対して影響を受けてしまうことがある。従って、ゲート電極と重なる領域302に、不純物元素を添加した容量用トランジスタ301を用いてもよい（図13（C）参照）。上記構成の容量用トランジスタは、トランジスタのしきい値電圧とは無関係に容量が形成できるため、トランジスタのしきい値電圧のバラツキによる影響を防止することができる。この場合の等価回路図は図13（D）のように表される。20

**【実施例 4】**

**【0123】**

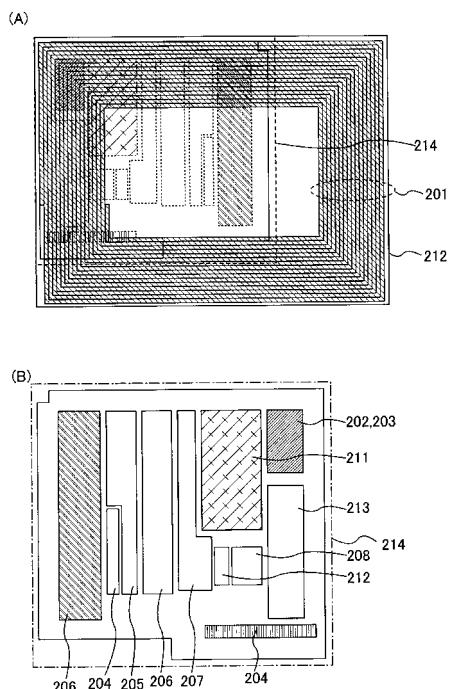

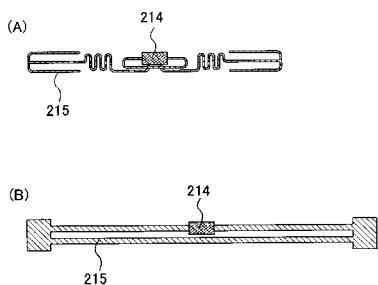

次に、実施の形態1、2に示す無線チップのレイアウトの一例について、図26を参照して説明する。まず、1つの無線チップの全体的なレイアウトについて説明する（図26（A）参照）。無線チップは、第1のアンテナ201と、電源部及びロジック部とを構成する素子群214と、第2のアンテナ（図示せず）とで、別々のレイヤーに形成されており、具体的には、素子群214上に第1のアンテナ201が形成されている。素子群214を形成する領域の一部と、第1のアンテナ201を形成する領域の一部は重なっている。図示する構成では、第1のアンテナ201を構成する配線の幅を150μm、配線と配線の間の幅を10μmで設計し、その巻き数は15巻きとした。また、第1のアンテナ201は、図26に示すように、巻いた形状に制約されない。第1のアンテナ201の形状は、曲線型（図27（A）参照）、直線型（図27（B）参照）のいずれの形状であってもよい。30

**【0124】**

なお、図示しないが、素子群214を介して第1のアンテナの反対側に第2のアンテナを有する。第2のアンテナも第1のアンテナと同様に、巻いた形状、曲線型、直線型のいずれの形状をもとることが可能である。

**【0125】**

次に、電源部及びロジック部を構成する素子群214のレイアウトについて説明する（図26（B）参照）。電源部を構成する整流回路202と保持容量203は同じ領域に設けられる。ロジック部は、復調回路204、クロック生成・補正回路205、各コード認識及び判定回路206、メモリコントローラ207、変調用抵抗を含む変調回路208を有する。復調回路204と、各コード認識及び判定回路206は、2カ所に分けて設けられる。マスクROM211とメモリコントローラ207は隣接して設けられる。クロック生成・補正回路205と各コード認識及び判定回路206は隣接して設けられる。復調回路204は、クロック生成・補正回路205と各コード認識及び判定回路206の間に設けられる。また、ロジック部用の検波容量212と、電源部用の検波容量213とが設けられる。変調用抵抗を含む変調回路208は、検波容量212と検波容量213の間に設けられる。40

**【0126】**

マスクROM211は、製造工程で記憶内容をメモリに作り込むものであり、ここでは、

10

20

30

40

50

高電位電源（VDDともよぶ）に接続する電源線と、低電位電源（VSSともよぶ）に接続する電源線の2本の電源線を設けて、メモリセルが記憶する記憶内容は、各メモリセルが含むトランジスタが、上記のどちらの電源線に接続しているかにより判断する。

#### 【実施例5】

##### 【0127】

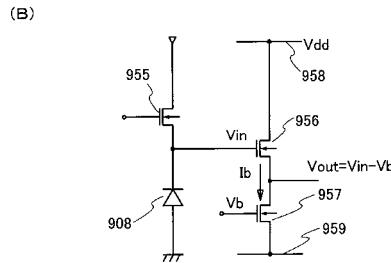

図15(A)は周囲の明るさ、若しくは光照射の有無を検知する無線チップにおいて、検出部であるセンサ部の一例を示している。センサ部908は、センサ906、センサ回路909を有する。センサ906は、フォトダイオード、フォトトランジスタなどで形成されている。センサ回路909は、センサ駆動回路952、検出回路953及びA/D変換回路954を含んでいる。

10

##### 【0128】

図15(B)は検出回路953を説明する回路図である。リセット用TFT955を導通状態にするとセンサ906には逆バイアス電圧が印加される。ここで、センサ906のマイナス側端子の電位が電源電圧の電位まで充電される動作を「リセット」と呼ぶ。その後、リセット用TFT955を非導通状態にする。そのとき、センサ906の起電力により、時間が経過するに従い電位状態が変化する。すなわち、電源電圧の電位まで充電されていたセンサ906のマイナス側端子の電位が、光電変換によって発生した電荷によって除々に低下する。ある一定時間を経過した後、バイアス用TFT957を導通状態とすると、增幅用TFT956を通って出力側に信号が出力される。この場合、增幅用TFT956とバイアス用TFT957は所謂ソースフォロワ回路として動作する。図15(B)ではソースフォロワ回路をnチャネル型TFTで形成した例で示されているが、勿論、pチャネル型TFTでも形成することができる。增幅側電源線958には電源電圧Vddが加えられている。バイアス側電源線959は基準電位0ボルトが与えられている。增幅用TFT956のドレイン側端子は増幅側電源線に接続され、ソース側端子はバイアス用TFT957のドレイン端子に接続されている。バイアス用TFT957のソース側端子はバイアス側電源線959に接続されている。バイアス用TFT957のゲート端子にはバイアス電圧Vbが印加され、このTFTにはバイアス電流Ibが流れる。バイアス用TFT957は基本的には定電流源として動作する。增幅用TFT956のゲート端子には入力電圧Vinが加えられ、ソース端子が出力端子となる。このソースフォロワ回路の入出力関係は、 $V_{out} = V_{in} - V_b$ となる。この出力電圧VoutはA/D変換回路954によりデジタル信号に変換する。デジタル信号は演算処理回路部903に出力する。

20

##### 【0129】

図16はセンサ906に静電容量を検出する素子を設けた一例を示している。静電容量を検出する素子は、一対の電極を備えている。電極間に液体又は気体など検知する対象物が充填されるようになっている。この一対の電極間の、静電容量の変化を検知することで、例えば容器に密封された内容物の状態を判断する。また、一対の電極間にポリイミド、アクリルその他吸湿性の誘電体を介在させて、電気抵抗の微小な変化を読み取ることにより湿度の変化を検知することもできる。

30

##### 【0130】

センサ回路909は、以下に示す構成となっている。パルスジェネレータ（発振回路）960は測定基準信号を生成し、センサ906の電極にその信号を入力する。このときの電圧は電圧検出回路961にも入力される。電圧検出回路961により検出された基準信号は、変換回路963で実効値を示す電圧信号に変換される。センサ906の電極間に流れる電流は、電流検出回路962により検出する。電流検出回路962により検出された信号は、変換回路964により実効値を示す電流信号に変換される。演算回路966は、変換回路963の出力である電圧信号と、変換回路964の出力である電流信号を演算処理してインピーダンス若しくはアドミタンスなどの電気パラメータを算出する。また、電圧検出回路961の出力と電流検出回路962の出力は、位相比較回路965に入力される。位相比較回路965はこの両者の信号の位相差を、演算回路967に出力する。演算回路967は、演算回路966と位相比較回路965の出力信号を用いて静電容量を算出

40

50

する。そして、その信号を演算処理回路部 903 に出力する。

#### 【0131】

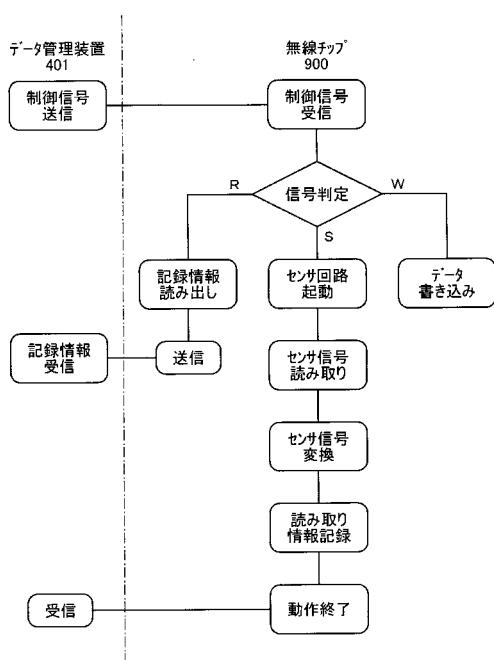

図17はデータ管理装置401と無線チップ900との動作を説明するフローチャートである。データ管理装置401は、センサ起動信号、データ読み出し信号、データ書き込み信号などの制御信号を送信する。その制御信号を無線チップ900が受信する。無線チップ900は、演算処理回路で制御信号を識別する。そして、センサ部908を動作させてデータの測定及び記録を行う動作、メモリ部に記録されているデータを読み出す動作、メモリ部にデータを書き込む動作の中からどの動作を行うか判定する。データの測定及び記録を行う動作は、センサ回路を動作させ、センサの信号を読み取り、センサ回路を介して二値化を行い、メモリ部に記録させる作業を行う。データを書き込む動作では、データ管理装置401から送信されたデータをメモリ部904に書き込みを行う。メモリ部に記録されているデータを読み出す動作では、メモリ部904のデータを読み出し、それをデータ管理装置401に送信する動作を行う。回路の動作に必要な電力は、信号の送信とともに、若しくは隨時行うものとする。

10

#### 【0132】

次に、無線チップのセンサで検知した情報（以下、センサ検知情報と示す。）を、リーダライタと送受信するシステムについて、図25を用いて説明する。図25は、本発明の半導体装置である無線チップ900と、無線チップ900の情報の送受信を行うリーダライタ920の一例を示す。リーダライタ920は、アンテナ921と、発信器923、復調回路924、変調回路925を備えた通信回路部922を備えている。その他に演算処理回路部926、外部インターフェイス部927を備える。制御信号を暗号化して送受信するには、暗号化／複合化回路部928とメモリ部929を備えておけば良い。電源回路部930は各回路に電力を供給するものであり、外部電源931から供給された電力を各回路へ供給する。

20

#### 【0133】

無線チップ900のセンサ部908で検知した情報は、演算処理回路部903で処理した後、メモリ部904に保持される。リーダライタ920の変調回路925を介して電波として送られてきた信号942は、無線チップ900のアンテナ902において、電磁誘導により交流の電気信号に変換される。通信回路部905の復調回路912では、該交流の電気信号を復調し、演算処理回路部903に送信する。演算処理回路部903では、入力された信号に従ってメモリ部904に保持されているセンサ検知情報を呼び出す。そして、演算処理回路部903から変調回路913に信号を送り、変調回路913で交流の電気信号に変調する。そして、該交流の電気信号941をアンテナ902を介して、リーダライタ920のアンテナ921に送信する。

30

#### 【0134】

リーダライタ920のアンテナ921で受信した交流の電気信号を、通信回路部922の復調回路924で復調し、演算処理回路部926、外部インターフェイス部927に送信する。そして外部インターフェイス部927に接続されるディスプレイ、コンピュータなどの情報処理装置932で、センサ検知情報を表示する。

#### 【実施例6】

#### 【0135】

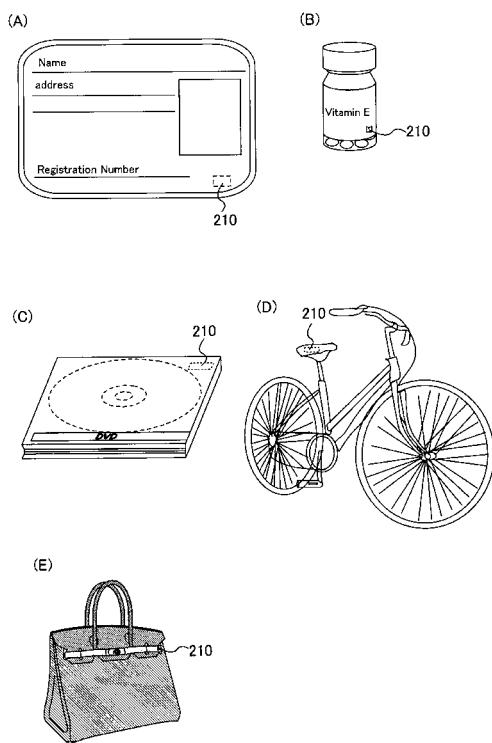

本発明により作製される半導体装置の使用形態は広範にわたるが、例えば、紙幣、硬貨、有価証券類、無記名債券類、証書類（運転免許証や住民票等、図21（A）参照）、包装用容器類（包装紙やボトル等、図21（B）参照）、記録媒体（DVDソフトやビデオテープ等、図21（C）参照）、乗物類（自転車等、図21（D）参照）、身の回り品（鞄や眼鏡等、図21（E）参照）、食品類、植物類、動物類、人体、衣類、生活用品類、電子機器等に設けて使用することができる。電子機器とは、液晶表示装置、EL表示装置、テレビジョン装置（単にテレビ、テレビ受像機、テレビジョン受像機とも呼ぶ）及び携帯電話等を指す。また、植物類、動物類、人体等に用いることが出来る。

#### 【0136】

50

50

50

40

50

本発明の半導体装置は、物品の表面に貼ったり、物品に埋め込んだりして、物品に固定される。例えば、本なら紙に埋め込んだり、有機樹脂からなるパッケージなら当該有機樹脂に埋め込んだりするとよい。紙幣、硬貨、有価証券類、無記名債券類、証書類等に半導体装置を設けることにより、偽造を防止することができる。また、包装用容器類、記録媒体、身の回り品、食品類、衣類、生活用品類、電子機器等に半導体装置を設けることにより、検品システムやレンタル店のシステムなどの効率化を図ることができる。小型、薄型、軽量を実現する本発明の半導体装置は、物品に実装しても、デザイン性を損なうことがない。また、複数のアンテナを設けることでリーダライタの選択幅が広がる。更には、センサを有することで、物品の状態を管理することが可能である。

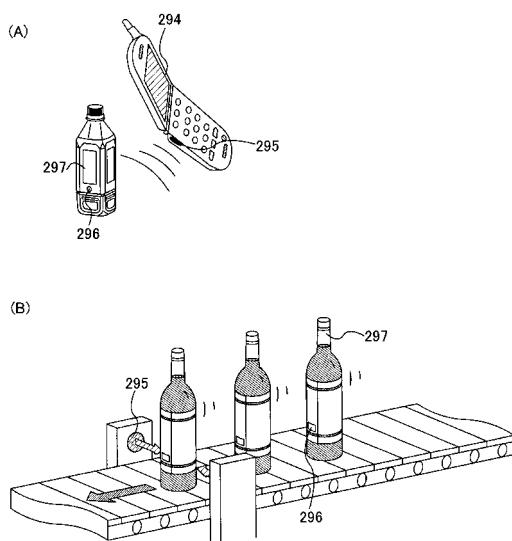

## 【0137】

10

また、本発明の半導体装置を、物の管理や流通のシステムに応用することで、システムの高機能化を図ることができる。例えば、表示部294を含む携帯端末の側面にリーダライタ295を設けて、物品297の側面に半導体装置296を設ける場合が挙げられる(図22(A)参照)。この場合、リーダライタ295に半導体装置296をかざすと、表示部294に物品297の原材料や原産地、流通過程の履歴等の情報が表示されるシステムになっている。また、別の例として、ベルトコンベアの脇にリーダライタ295を設ける場合が挙げられる(図22(B)参照)。この場合、物品297の検品を簡単に行うことができる。

## 【0138】

20

本発明のセンサを有する半導体装置の代表的な使用形態を図23を用いて説明する。

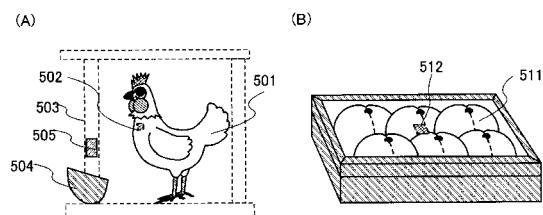

## 【0139】

図23(A)に示すように、動物類501に温度センサを有する半導体装置502を埋め込み、動物の温度を測定した情報を半導体装置のメモリ部に記録する。檻503又は餌箱504等の動物付近に設けられた設備にリーダライタ505を設け、該リーダライタで記録された情報を定期的に読み取ることで、動物の健康状態等を容易に管理することができる。

## 【0140】

30

また、図23(B)に示すように、腐敗しやすい食品511にガスセンサを有する半導体装置512を設け、食品から発する腐敗ガスを検知する。陳列棚又はベルトコンベアの脇に設けられたリーダライタで、半導体装置に記録された情報を定期的に読み取ることで、食品の鮮度を管理すると共に、腐敗が始まった食品を容易に選別することができる。

## 【0141】

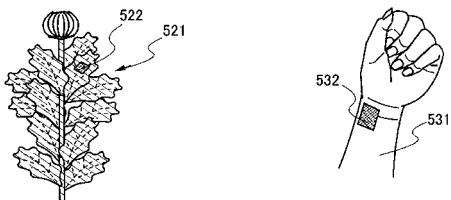

また、図23(C)に示すように、長日植物や短日植物の花芽形成を制御するために、植物521の葉など光の当たるところに、光センサを有する半導体装置522を設け、日照時間を半導体装置内のメモリに記録する。記録された情報をリーダライタで定期的に読み取り、電照時間を制御することで、花の開花時期や出荷時期を容易に制御することができる。

## 【0142】

40

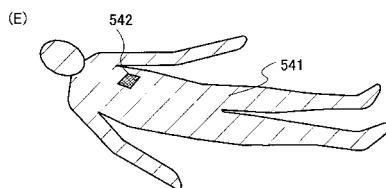

また、図23(D)、(E)に示すように、人体の表面又は内部に、温度センサ、圧力センサ等のセンサを有する半導体装置532、542を設けて、脈拍数、心拍数、体温、血圧、心電図、筋電図等の生体情報を半導体装置内のメモリに記録する。図23(D)は、腕531に圧力センサを有する半導体装置を貼り付けて、脈拍を測定する図である。図23(E)は、人体541の心臓付近に圧力センサを有する半導体装置を張りつけて、心電図を測定する図である。本発明の半導体装置は、薄型であり且つ小型であるため、人体を拘束せよとも生体情報を読み取ることが可能である。また、記録された情報をリーダライタで定期的に読み取ることで、人体の健康状態や運動状態を管理すると共に、疾病の予防、予測が可能である。また、インターネット等のネットワークを用いて、リーダライタで読み取った生体情報を得ることで、在宅医療監視システムなどが可能となる。

## 【図面の簡単な説明】

50

## 【0143】

- 【図1】本発明の半導体装置の作製方法を説明する図である。

- 【図2】本発明の半導体装置の作製方法を説明する図である。

- 【図3】本発明の半導体装置の作製方法を説明する図である。

- 【図4】本発明の半導体装置の作製方法を説明する図である。

- 【図5】本発明の半導体装置の作製方法を説明する図である。

- 【図6】本発明の半導体装置の作製方法を説明する図である。

- 【図7】本発明の半導体装置の作製方法を説明する図である。

- 【図8】本発明の半導体装置の構造を説明する図である。

- 【図9】本発明の半導体装置の構造を説明する図である。 10

- 【図10】本発明の半導体装置の作製方法を説明する図である。

- 【図11】本発明の半導体装置の作製方法を説明する図である。

- 【図12】本発明の半導体装置の構造を説明する図である。

- 【図13】本発明の半導体装置を説明する図である。

- 【図14】本発明の半導体装置の構造を説明する図である。

- 【図15】本発明の半導体装置の構造を説明する図である。

- 【図16】本発明の半導体装置の構造を説明する図である。

- 【図17】本発明の半導体装置の動作について説明する図である。 20

- 【図18】本発明の半導体装置の構造を説明する図である。

- 【図19】本発明の半導体装置の構造を説明する図である。

- 【図20】本発明の半導体装置の構造を説明する図である。

- 【図21】本発明の半導体装置の使用形態について説明する図である。

- 【図22】本発明の半導体装置の使用形態について説明する図である。

- 【図23】本発明の半導体装置の使用形態について説明する図である。

- 【図24】本発明の半導体装置の構造を説明する図である。

- 【図25】本発明の半導体装置の構造を説明する図である。

- 【図26】本発明の半導体装置の構造を説明する図である。

- 【図27】本発明の半導体装置の構造を説明する図である。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

(C) (D)

【図25】

【図26】

【図27】

---

フロントページの続き

(51)Int.Cl. F I

G 0 6 K 19/07 (2006.01)

G 0 6 K 19/077 (2006.01)

(56)参考文献 特開2004-233444 (JP, A)

特開2003-100450 (JP, A)

特開2002-353235 (JP, A)

特開2001-272923 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 0 1 L 2 7 / 1 2

H 0 1 L 2 1 / 0 2

G 0 6 K 1 9 / 0 0 - 1 9 / 1 8

H 0 1 L 2 1 / 3 3 6

H 0 1 L 2 7 / 1 4 - 2 7 / 1 4 8

H 0 1 L 2 9 / 7 8 6