(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6319880号

(P6319880)

(45) 発行日 平成30年5月9日(2018.5.9)

(24) 登録日 平成30年4月13日(2018.4.13)

(51) Int.Cl.

F 1

G06F 8/41 (2018.01)

G06F 9/50 (2006.01)G06F 9/44 322 F

G06F 9/46 465 E

請求項の数 9 (全 21 頁)

(21) 出願番号 特願2014-6009 (P2014-6009)

(22) 出願日 平成26年1月16日 (2014.1.16)

(65) 公開番号 特開2014-160453 (P2014-160453A)

(43) 公開日 平成26年9月4日 (2014.9.4)

審査請求日 平成28年12月6日 (2016.12.6)

(31) 優先権主張番号 特願2013-10194 (P2013-10194)

(32) 優先日 平成25年1月23日 (2013.1.23)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 899000068

学校法人早稲田大学

東京都新宿区戸塚町1丁目104番地

(74) 代理人 110000800

特許業務法人創成国際特許事務所

(72) 発明者 笠原 博徳

東京都新宿区大久保3-4-1 早稲田大学理工学術院基幹理工学部情報理工学科内

(72) 発明者 木村 啓二

東京都新宿区大久保3-4-1 早稲田大学理工学術院基幹理工学部情報理工学科内

(72) 発明者 林 明宏

東京都新宿区大久保3-4-1 早稲田大学理工学術院基幹理工学部情報理工学科内

最終頁に続く

(54) 【発明の名称】並列性の抽出方法及びプログラムの作成方法

## (57) 【特許請求の範囲】

## 【請求項1】

元プログラムの並列性をコンピュータによって抽出する方法であって、

前記方法は、

前記元プログラムを、複数のマクロタスクに分割する処理と、

前記複数のマクロタスクの最早実行可能条件を解析する処理と、

前記最早実行可能条件の解析結果に基づいて、条件分岐の同一の分岐方向に制御依存する複数のマクロタスクである複数の後続マクロタスクの相互の間で並列実行可能な前記条件分岐を抽出する処理と、

抽出された前記条件分岐を複製することにより前記条件分岐をそれぞれ含む複数のマクロタスクである複数の先行マクロタスクを生成する処理と、を含むことを特徴とする並列性の抽出方法。

## 【請求項2】

請求項1に記載の並列性の抽出方法であって、

前記条件分岐として、前記複数の後続マクロタスクの相互の間でデータ依存がない条件分岐を抽出することを特徴とする並列性の抽出方法。

## 【請求項3】

請求項1又は2に記載の並列性の抽出方法であって、

前記元プログラムから分割された前記複数のマクロタスクを並列に実行するための複数のバスのうち、実行時間が最も長いバスに含まれる条件分岐を複製することを特徴とする

並列性の抽出方法。

**【請求項 4】**

請求項 1 ~ 3 のうちいずれか 1 項記載の並列性の抽出方法であって、

前記元プログラムから分割された前記複数のマクロタスクを並列に実行するための複数のパスのうち、実行時間が最も長いパスに含まれる条件分岐を複製することによって生成された複数の先行マクロタスクに繋がるパスの中で実行時間が最も長いパスに含まれる条件分岐をさらに複製することを特徴とする並列性の抽出方法。

**【請求項 5】**

請求項 1 ~ 4 のうちいずれか 1 項記載の並列性の抽出方法であって、

前記複数の後続マクロタスクのうちの第 1 後続マクロタスクを前記複数の先行マクロタスクのうちの 1 つの第 1 先行マクロタスクに後続させ、

前記複数の後続マクロタスクのうちの前記第 1 後続マクロタスクと異なる第 2 後続マクロタスクを前記複数の先行マクロタスクのうちの前記第 1 先行マクロタスクとは異なる第 2 先行マクロタスクに後続させることを特徴とする並列性の抽出方法。

**【請求項 6】**

請求項 1 ~ 5 のうちいずれか 1 項記載の並列性の抽出方法であって、

前記複数の後続マクロタスクとは異なる一のマクロタスクにデータ依存し、かつ、前記複数の後続マクロタスクに含まれる第 3 後続マクロタスクと、前記一のマクロタスクにデータ依存せず、かつ、前記複数の後続マクロタスクに含まれる第 4 後続マクロタスクとが存在する場合、前記第 4 後続マクロタスクを、前記一のマクロタスク及び前記第 3 後続マクロタスクが含まれるパスとは異なるパスに含まれるように、前記複数の先行マクロタスクに前記複数の後続マクロタスクを後続させることを特徴する並列性の抽出方法。

**【請求項 7】**

請求項 1 ~ 6 のうちいずれか 1 項記載の並列性の抽出方法であって、

前記条件分岐は、実行時の不確定性を有することを特徴とする並列性の抽出方法。

**【請求項 8】**

請求項 1 ~ 7 のうちいずれか 1 項記載の並列性の抽出方法であって、

前記条件分岐は、ループ制御文とは異なることを特徴とする並列性の抽出方法。

**【請求項 9】**

元プログラムからコンピュータによって複数のプロセッサコアを含むマルチコアプロセッサ上で実行可能なプログラムを作成する方法であって、

請求項 1 ~ 8 のうちいずれか 1 項記載の並列性の抽出方法を用いて生成された複数の条件分岐をそれぞれ含む複数の先行マクロタスクを、前記複数のプロセッサコアの各々が実行するように割り当て、

前記複数の条件分岐のそれを含む先行マクロタスクを実行するプロセッサコアが、それぞれ、前記複数の後続マクロタスクの各々を実行するように割り当てることによって、前記実行可能なプログラムを作成する方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、逐次処理の元プログラムに潜在する並列性を抽出する方法、及びその並列性の抽出方法を用いて複数のプロセッサコアによって構成されるマルチコアプロセッサ上で実行される並列化プログラムを作成する方法に関する。

**【背景技術】**

**【0002】**

複数のプロセッサコアを集積したマルチコアプロセッサが、各マイクロプロセッサーによって次々に発表されている。スーパーコンピュータ、サーバ、デスクトップコンピュータ及び P C サーバ分野の他、情報家電及び装置組み込みの分野（例えば、携帯電話機、ゲーム機、カーナビゲーションシステム、デジタルテレビ受像機、H D D / D V D レコーダ・プレーヤ等）においても、マイクロプロセッサのマルチコア化の動きが見られる。

10

20

30

40

50

**【0003】**

また、より安全、快適、省エネを実現する次世代自動車の開発のため、エンジン制御のようなリアルタイム制御系、人認識・他車認識のような外界認識、運転に必要な情報の提示、音楽・映像等を提示する情報系、制御系と情報系を統合して、制御する統合制御系、それぞれの高度化が重要となっている。

**【0004】**

これらの制御系、情報系、および統合制御系の高度化のためには、プロセッサの高能力化が重要となる。例えば、安全、快適、省エネな自動車開発のために重要なエンジン制御系を高度化するためには、制御アルゴリズムの高度化、新制御機能の実現など計算負荷の増大を避けられない。

10

**【先行技術文献】****【特許文献】****【0005】**

【特許文献1】特開2001-175619号公報

**【非特許文献】****【0006】**

【非特許文献1】Seo, K., et al., Coordinated implementation and processing of a unified chassis control algorithm with multi-central processing unit, J AUT01346, Vol. 224 (2009)

20

【非特許文献2】Seo, K., et al.: An Investigation into Multi-Core Architectures to Improve a Processing Performance of the Unified Chassis Control Algorithms, SAE Int.J.Passeng.Cars-Elect1on.Electr.Syst., Vol.3, pp.53-62 (2010)

【非特許文献3】OSEK/VDX-Portal:<http://portal.osek-vdx.org/>

【非特許文献4】Kawahara, H., et al.: Automatic Coarse Grain Task Parallel Processing on SMP using Open MP, Proc. of The 13th International Workshop on Languages and Compilers for Parallel Computing(LCPC2000) (2000)

【非特許文献5】Y. Yuyama, et al., A 45nm 37.3GOPS/W Heterogeneous Multi-Core SoC, ISSCC2010

【非特許文献6】H. Kawahara, et al., OSCAR FORTRAN COMPILER, 1991 International Logic Programming Symposium, Workshop on Compilation of (symbolic) Languages for parallel Computers, Oct.31-Nov.1, 1991, San Diego, U.S.A.

30

**【発明の概要】****【発明が解決しようとする課題】****【0007】**

このようなエンジン制御系の高度化の要求に伴う計算負荷の増大という問題を解決するためには、エンジン制御に用いられるプロセッサの高能力化が必須となる。

**【0008】**

従来は、プロセッサの高能力化のためにプロセッサの動作周波数を上げることが必要である。しかし、消費電力は動作周波数の三乗に比例して増大するために消費電力の大幅な増加を招くこと、また、自動車における過酷な動作環境下でも安定動作を保証する必要があることなどのため、自動車などの装置に適用することは困難である。このため1チップ上に複数の低動作周波数プロセッサコアを集積し、低周波数化・低電圧化したプロセッサコアを並列動作させることにより、処理の高速化と低消費電力化とを同時に実現可能なマルチコアプロセッサへの移行が求められている。

40

**【0009】**

このような要求に対し、自動車業界におけるマルチコアを利用した技術が提案されている。例えば、非特許文献1及び非特許文献2に記載されるように、統合シャシ制御(UC)アルゴリズムを利用したマルチコアアーキテクチャでは、マルチコアプロセッサを用いた電子制御ユニットが提案されている。このマルチコアプロセッサは三つのプロセッサコアで構成され、電子制御ユニットを三つの機能に分割し、その各々を前記三つのプロセ

50

ツサコアに割り当てるにより機能を分散している。この方法は、いわゆる A M P (Asymmetric Multicore Processing) と言われており、機能分散を実現することによってスループットを向上することが可能であるが、レイテンシの削減が困難である。また、機能毎の負荷バランスが均等でないとマルチコア資源を最大限に活用することができないという問題がある。

#### 【 0 0 1 0 】

本発明では、自動車制御系の主要機能であるエンジン制御に対し、後述するように並列処理を適用し、レイテンシの削減すなわち高速化する方法を提案する。このようなマルチコア上で、エンジン制御等の計算を、従来の一つのプロセッサコア上の処理より高速に行うためには、計算を分割し、計算負荷を複数のプロセッサに適切に割り当てる、計算を実行する方法、すなわち S M P (Symmetric Multicore Processing) が重要となる。このような S M P という計算実行方法は一般的に並列処理と呼ばれ、この並列処理のためのプログラムを並列化プログラムと称する。そして、1 プロセッサ上で動作する逐次処理の元プログラムから並列化プログラムを作成あるいは生成することをプログラムの並列化と称する。

10

#### 【 0 0 1 1 】

しかし、このプログラムの並列化を人手で行うことには、開発期間の増大、それに伴うソフトウェア開発費の増大、さらには並列化プログラムの信頼性の低下など、大きな問題があった。この問題を解決するために、並列化プログラムを逐次処理のプログラムから自動生成するためのソフトウェアに関する研究が行われてきた。

20

#### 【 0 0 1 2 】

従来の並列化の方法として、発明者等が研究開発を行ってきたマルチグレイン並列処理を行うコンパイラ、通称 O S C A R コンパイラが知られている。以下に O S C A R コンパイラの一般的な機能について説明する。コンパイラとは、一般的にはコンパイル対象のソースプログラムをいわゆる計算機が実行可能なプログラム（機械語のプログラム等）に変換するプログラムを指すが、以下に説明する並列化コンパイラ（O S C A R コンパイラ）は逐次処理プログラムのソースコードから並列化プログラムのソースコード（場合によってはオブジェクトコード）を生成する機能を持つ。

#### 【 0 0 1 3 】

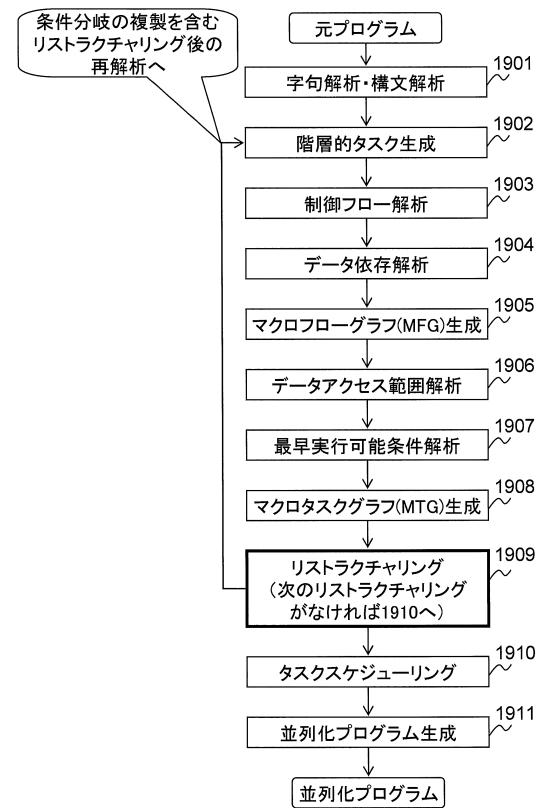

まず、O S C A R コンパイラの特徴であるマルチグレイン並列処理とは、元プログラムに存在する、ループやサブルーチン等の粗粒度タスク間の並列性を利用する粗粒度タスク並列処理、ループイタレーションレベルの並列性を利用する中粒度並列処理、基本ブロック内部のステートメントレベルの並列性を利用する近細粒度並列処理を階層的に組み合わせてプログラム全域にわたって行う並列処理である。その詳細は非特許文献 4 に詳述されているが、以下に図 17 のフローチャートを用いてその概要を説明する。

30

#### 【 0 0 1 4 】

粗粒度並列処理では、コンパイラは、図 17 のフローチャートにおける 1901 の「軸解析・構文解析」のステップ、ステップ 1902 の「マクロタスク生成」のステップを経て、ソースとなる元プログラムを疑似代入文ブロック（B P A）、繰り返しブロック（R B）、サブルーチンブロック（S B）の三種類の粗粒度タスク（以下、「マクロタスク（M T）」と称する。）に分割する。M T 生成後、コンパイラは、ステップ 1903 の「制御フロー解析」およびステップ 1904 の「データ依存解析」を経て、B P A、R B、S B、等の M T 間の制御フロー及びデータ依存関係を表現したマクロフローグラフ（以下、「M F G」と略称）を生成する（ステップ 1905）。さらに、ステップ 1906 の「データアクセス範囲解析」およびステップ 1907 の「最早実行可能条件解析」を経て、M F G から M T 間の並列性を抽出した結果をマクロタスクグラフ（以下、「M T G」と略称）として表現する（ステップ 1908）。その後コンパイラは、ステップ 1907 の「各種のリストラクチャリング」において、タスク融合（非特許文献 6 を参照）、キャッシュメモリの最適化、ローカルメモリ管理などのための各種のリストラクチャリングを行う。このリストラクチャリングのステップの処理の後、ステップ 1902 に処理を戻し、ステ

40

50

ツップ1902から1907までのステップにおいてプログラムの再解析を繰り返すが、再解析の必要がなくなれば、ステップ1910の「タスクスケジューリング」に進み、そのステップにおいてMTG上のMTを、少なくとも一つのプロセッサコア(PE)をグループングしたプロセッサグループ(PG)に割り当てるスケジューリング処理を行い、ステップ1911の「並列化プログラムの生成」において、前記スケジューリング処理の情報も含む並列化プログラムを生成する。

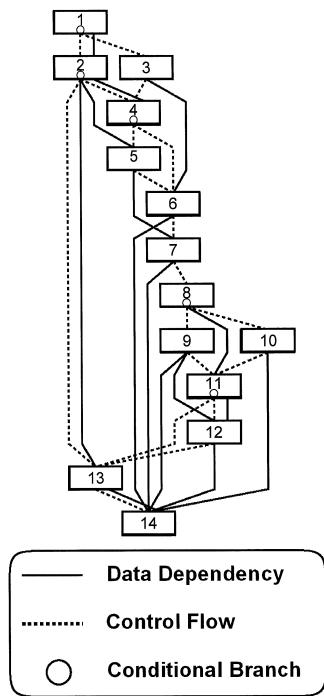

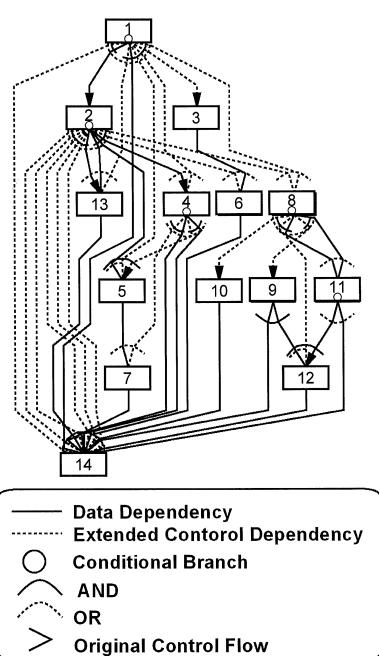

#### 【0015】

以上のようなコンパイラの並列化プログラム生成のための処理の過程で生成される前記のMFGの例を図18Aに示し、前記のMTGの例を図18Bに示す。MFGにおいてノードはMTを表し、実線エッジはデータ依存を、点線エッジは制御フローを表す。また、ノード内の小円は条件分岐を表す。MTGにおけるノードもMFGと同様にMTを表し、ノード内の小円はMT内の条件分岐を表す。また、実線エッジはデータ依存を表し、点線エッジは拡張された制御依存を表す。拡張された制御依存とは、通常の制御依存だけではなく、データ依存と制御依存を複合的に満足させるため、先行ノードが実行されることを確定する条件分岐を含む。また、エッジを束ねるアークには2つの意味があり、実線アークはアークによって束ねられたエッジがAND関係にあることを、点線アークは束ねられたエッジがOR関係にあることを表す。MTGにおいてエッジの矢印は省略したが、下向きである。また、矢印を持つエッジはオリジナルの制御フローを表す。

10

#### 【0016】

粗粒度タスク並列処理では、各階層で生成されたマクロタスクはPGに割り当てられて実行される。どのPGにマクロタスクを割り当てるかを決定するスケジューリング方法として、ダイナミックスケジューリングとスタティックスケジューリングとがあり、そのいずれを選択するかは、並列化コンパイラがMTGの形状、実行時非決定性などに基づいて決定する。

20

#### 【0017】

条件分岐などの実行時の不確定性が存在する場合には、ダイナミックスケジューリングが適しており、ダイナミックスケジューリングによって実行時にマクロタスクをPGに割り当てる。ダイナミックスケジューリングルーチンは、マクロタスクの終了又は分岐方向の決定に応じて、マクロタスク実行管理テーブルを操作し、各マクロタスクの最早実行可能条件を探索する。マクロタスクが実行可能であればレディキューにマクロタスクが投入される。レディキュー内のマクロタスクはその優先順位に従ってソートされ、レディキューの先頭のマクロタスクがアイドル状態のプロセッサコアに割り当たられる。また、ダイナミックスケジューリングコード生成時には、一つの専用のプロセッサがスケジューリングを行う集中スケジューリング方法と、スケジューリング機能を各プロセッサに分散した分散スケジューリング方法とを、使用するプロセッサ台数及びシステムの同期オーバーヘッドを考慮して、使い分けることができる。

30

#### 【0018】

一方、スタティックスケジューリングは、MTGがデータ依存エッジのみを持つ場合に適しており、自動並列化コンパイラがコンパイル時にマクロタスクのPGへの割り当てを決める方法である。スタティックスケジューリングでは、実行時スケジューリングオーバーヘッドを低減し、データ転送及び同期のオーバーヘッドを低減することが可能である。

40

#### 【0019】

並列化プログラムは、APIを用いて、並列化CあるいはFortran77によってsource-to-sourceで生成することも可能である。この場合には、様々なプラットフォームにおいて実行可能な形にするため、例えば、OSCAR API標準解釈系を用いて、API部分をランタイムライブラリコールに変換した後、各プロセッサ用のコードを逐次コンパイラでコンパイルし、バイナリコードを生成してもよい。

#### 【0020】

以上、図17のフローチャートを用いて説明した従来のOSCARコンパイラに、後述するような逐次処理のエンジン制御プログラムを元プログラムとして入力し、出力として

50

得られる並列化プログラムを後述するマルチコアプロセッサ R P - X (非特許文献 5 を参照) 上で実行させてもコア数に見合った速度向上を実現することができなかった。そのため、発明者はその原因を詳細に分析した結果、元プログラムの特性に従来の O S C A R コンパイラによる並列性の抽出方法が適応していないことが判明した。

#### 【 0 0 2 1 】

その理由は以下のとおりである。前述したエンジン制御プログラムには条件分岐などが多いために、従来の O S C A R コンパイラでは、条件分岐以降のマクロタスクの計算処理を複数個のプロセッサコアを含むマルチコアプロセッサ上で効率的に動作させるための並列化をスタティックスケジューリングによって行うことが困難であり、並列化プログラムの実行時にプロセッサコアの割り当てを行うダイナミックスケジューリングによらざるを得なかった。のために、並列化プログラム実行時に分岐毎に別のプロセッサコアに処理を割り当てる場合、コア間で処理の同期のための制御オーバーヘッドが増加し、並列化による実行速度の向上が低かったことが判明した。10

#### 【 0 0 2 2 】

このため、本発明では、条件分岐を含むプログラムに潜在する並列性を抽出して、マルチコアプロセッサ上で実行するのに適する並列化プログラムを生成するための効果的な並列性の抽出方法を提案する。

#### 【課題を解決するための手段】

#### 【 0 0 2 3 】

本願において開示される発明の代表的な一例を示せば以下の通りである。すなわち、元プログラムの並列性をコンピュータによって抽出する方法であって、前記方法は、前記元プログラムを、複数のマクロタスクに分割する処理と、前記複数のマクロタスクの最早実行可能条件を解析する処理と、前記最早実行可能条件の解析結果に基づいて、条件分岐の同一の分岐方向に制御依存する複数のマクロタスクである複数の後続マクロタスクの相互の間で並列実行可能な前記条件分岐を抽出する処理と、抽出された前記条件分岐を複製することにより前記条件分岐をそれぞれ含む複数のマクロタスクである複数の先行マクロタスクを生成する処理と、を含む。20

#### 【発明の効果】

#### 【 0 0 2 4 】

本発明の代表的な実施の形態によれば、条件分岐を含む元プログラムでも、適切に並列化をすることができる。また、制御プログラムのようにリアルタイム性が必要なプログラムにおいても、適切に並列化をすることができる。30

#### 【図面の簡単な説明】

#### 【 0 0 2 5 】

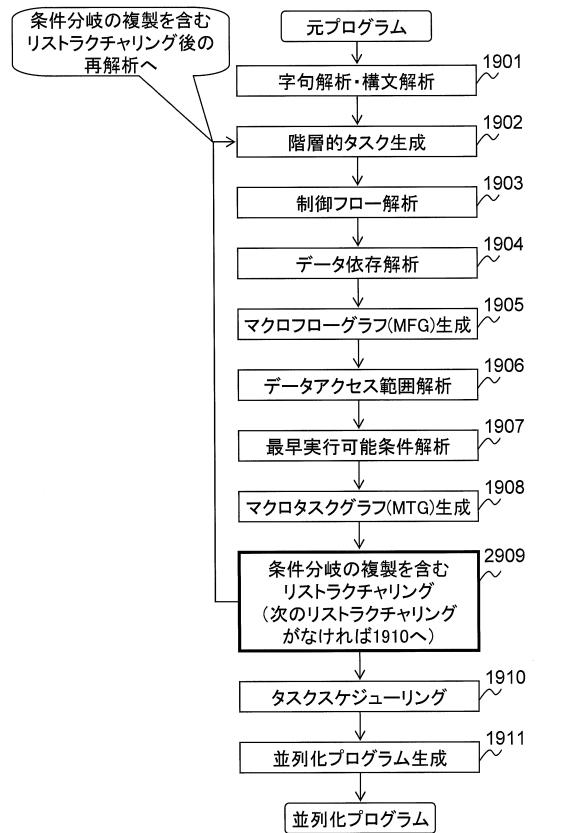

【図 1 A】本発明の並列性の抽出方法の実施形態を用いた並列化コンパイラの処理フローである。

【図 1 B】本発明の並列性の抽出方法の実施形態を用いた並列化コンパイラの処理ステップ 2 9 0 9 の詳細フローである。

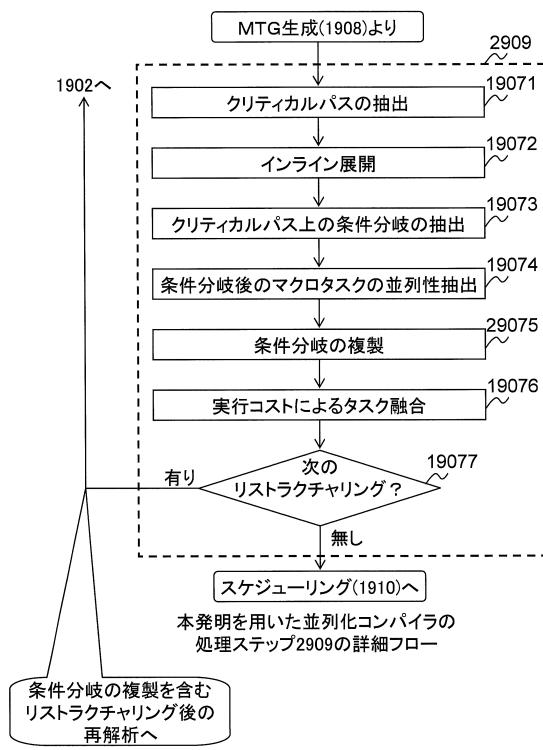

#### 【図 2】本発明の実施形態の並列化コンパイラを実行する計算機のブロック図である。

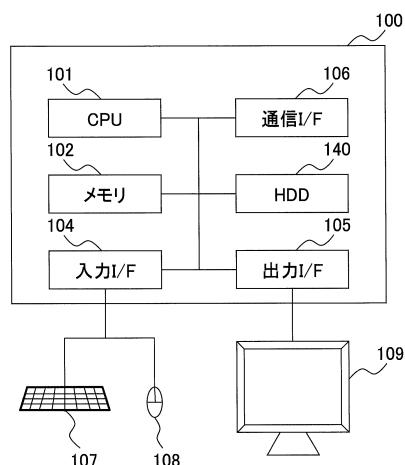

【図 3】元プログラムであるエンジン制御プログラムの実行プロファイル結果を説明する図である。

#### 【図 4】T a s k 1 5 m a i n の M T G である。

【図 5】T a s k 1 5 m a i n 内の各マクロタスクの実行コスト (単位 : クロック) を説明する図である。

#### 【図 6】本発明の実施形態の条件分岐内の並列性を説明する図である。

#### 【図 7】本発明の実施形態の条件分岐の複製を説明する図である。

#### 【図 8】本発明の実施形態のインライン展開・条件分岐の複製後の M F G である。

#### 【図 9】本発明の実施形態のタスク融合を行った後の M T G である。

#### 【図 1 0】本発明の実施例に用いた T a s k 1 5 m a i n を元プログラムとして生成した50

並列化プログラムの性能評価に用いた組込用マルチコアプロセッサの構成を説明する図である。

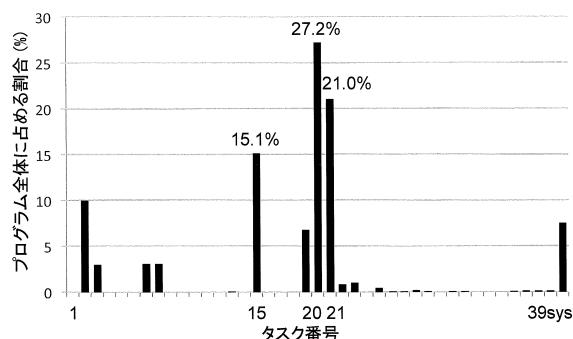

【図11】本発明の実施形態の実行プロファイル結果である。

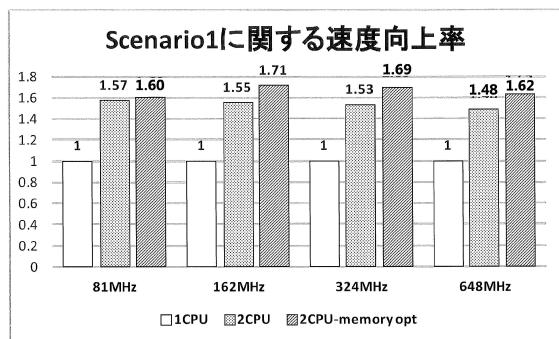

【図12】本発明の実施形態のシナリオ1の速度向上率を説明する図である。

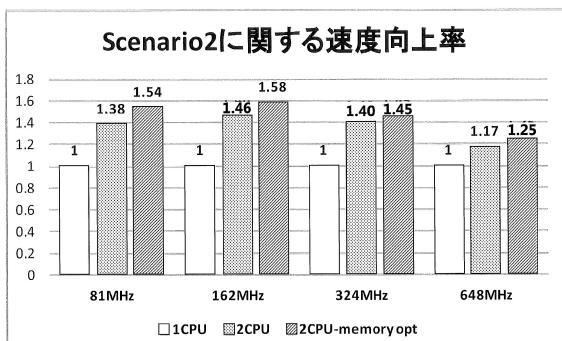

【図13】本発明の実施形態のシナリオ2の速度向上率を説明する図である。

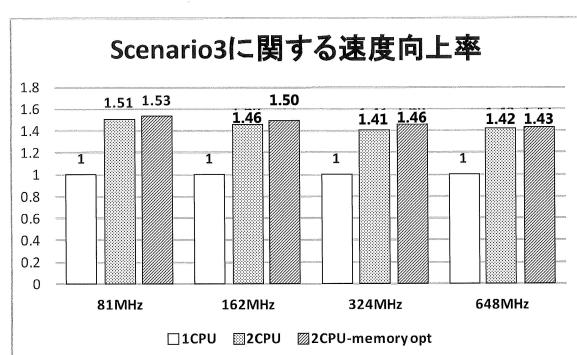

【図14】本発明の実施形態のシナリオ3の速度向上率を説明する図である。

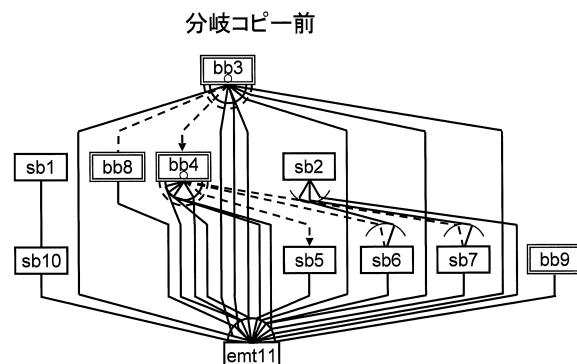

【図15】本発明の実施形態の説明のために挙げた条件分岐複製前のMTGの例である。

【図16】本発明の実施形態の説明のために挙げた条件分岐複製後のMTGの例である。

【図17】従来の並列化コンパイラの処理フローである。

【図18A】MFGの例を説明する図である。

10

【図18B】MTGの例を説明する図である。

【発明を実施するための形態】

【0026】

以下、本発明の実施形態について図面を用いて説明する。

【0027】

本実施形態では、元プログラムとして、ループ処理がなく、条件分岐や代入文などの基本ブロックが連続していて従来の並列化方法では並列化が困難なエンジン制御プログラムにおける並列性の抽出方法およびその抽出方法を用いた並列化方法について説明する。なお、本発明は、本実施形態で説明するエンジン制御プログラムだけでなく、条件分岐や代入文などの基本ブロックが連続しているなどの特徴を有する他の（制御）プログラムの並列化にも適用することができる。

20

【0028】

【コンパイル処理】

図1Aは、本発明の実施形態の並列性の抽出方法を用いた並列化コンパイラ（以下「本発明の実施形態のコンパイラ」と略称）が実行する処理のフローチャートである。

【0029】

ここでは、条件分岐の多い逐次処理の元プログラムから高性能の並列化プログラムを生成する本発明の実施形態のコンパイラが、計算機上で実行する並列化プログラム生成までの処理、なかんずく並列性の抽出処理について説明する。図1Aに示す並列化コンパイラは、従来のOSCARコンパイラに比して、ステップ1907のリストラクチャリング機能に以下に説明する並列性の抽出のための条件分岐の複製を追加したことに特徴がある。従って、以下の説明において、ステップ1901から1908までおよびステップ1910、1911における処理は従来の並列化コンパイラに実装されている。また、本発明の並列性の抽出方法を用いた並列化コンパイラ（以下「本発明のコンパイラ」と略称）のステップ2909を「条件分岐の複製を含むリストラクチャリング」と称することとするが、ステップ2909は、従来の並列化コンパイラのステップ1907の「各種のリストラクチャリング」に本発明の特徴である条件分岐の複製の機能を追加したものである。以下にその具体的な内容および効果について説明する。

30

【0030】

まず、並列化コンパイラは、ソースプログラムの字句を解析し、プログラムの構文を解析する（ステップ1901）。なお、本実施形態では、コンパイラがプログラムを解析しているが、簡単なプログラム等の場合はプログラマ（人）がプログラムを解析してもよい。また、ソースプログラムの作成時に、コンパイラに必要なプログラムの情報を作成してもよい。

40

【0031】

次に、並列化コンパイラは、構文の解析結果に基づいて、プログラムの階層的マクロタスクによる表現を生成する（ステップ1902）。ここでは、粗粒度タスク（マクロタスク）を生成する。なお、生成されたマクロタスクがループイタレーションレベルの並列処理や逐次処理が可能な場合、ローカルメモリ等のメモリサイズを考慮して、異なる複数のマクロタスクに分割する（ループ整合分割）。

50

**【0032】**

その後、生成されたマクロタスク間の制御依存関係（制御フロー）を解析し（ステップ1903）、マクロタスク間のデータ依存を解析し（ステップ1904）、その結果に基づきMFGを生成する（ステップ1905）。次に、そのMFGを基にして各マクロタスクによってアクセスされるデータの範囲を解析する（ステップ1906）。

**【0033】**

その後、以上に述べたプログラムの解析結果を使用して、プログラムが最も早く実行できる最早実行条件を解析し（ステップ1907）、最早実行条件の解析結果を使用して、並列処理区間やマクロタスクを割り当てるプロセッサ数を決定し、MTGを生成する（ステップ1908）。

10

**【0034】**

その後、同一の条件で実行が決定される複数のマクロタスクのうち、前記実行される複数のマクロタスクの相互の間で並列実行可能な（例えば、データ依存がない）条件分岐を抽出し、抽出された条件分岐を複製する（ステップ2909の「条件分岐の複製を含むリストラクチャリング」）。複製された条件分岐の中に、さらに複製すべき条件分岐があれば、複製後のプログラムを再度解析するためにステップ1902に処理を戻し、ステップ1902から1908までを実行した上で、ステップ2909を実行する。なお、ステップ2909は、条件分岐の複製及び他のリストラクチャリングがなくなるまで繰り返し実行される。

**【0035】**

20

その後、各マクロタスクの実行順序を決定するタスクスケジューリングを実行する（1910）。ここで実行されるタスクスケジューリングは、メモリ管理・タスクスケジューリング、データ転送スケジューリング、及び低消費電力スケジューリングを含む。

**【0036】**

メモリ管理・タスクスケジューリングとは、マルチコアプロセッサ中の各プロセッサコアのローカルメモリを介した効率的なデータの授受を実行するためのスケジューリングである。データ転送スケジューリングとは、ブレロードやポストストアのように、各プロセッサコアにおけるデータ転送、及びマルチコアプロセッサ全体におけるデータ転送の最適化を実現するためのスケジューリングである。低消費電力スケジューリングとは、マルチコアプロセッサ中の汎用プロセッサ（CPU）、アクセラレータ（ACC）、データ転送ユニット（DTU）などが待ち状態になる場合に、待ち時間に応じてクロック周波数を低周波数に変化させたり、電源を遮断させたりする電力制御を実現するためのスケジューリングである。

30

**【0037】**

その後、ステップ1910におけるタスクスケジューリングに基づいて、マルチコアプロセッサにおいて実行可能な並列化プログラムを生成する（ステップ1911）。この並列化プログラムは、マルチコアプロセッサの構成に基づいて生成されるため、汎用プロセッサ（CPU）用のマクロタスク、ACC用のマクロタスク、DTU用のマクロタスクの命令文を含む。ここで生成される並列化プログラムでは、互いに依存のある汎用プロセッサ（CPU）用のマクロタスク、ACC用のマクロタスク、及びDTU用のマクロタスクの命令文には、フラグセット文、フラグチェック文が挿入される。これらACC用のマクロタスク、DTU用のマクロタスクの命令文、及びフラグ領域は分散共有メモリ（URAM）、ローカルメモリ（ILM、DLM）、オンチップ集中共有メモリ、オフチップ集中共有メモリのうちの少なくとも一つのメモリに配置される。

40

**【0038】**

図2は、本発明の実施形態のコンパイラの処理を実行する計算機100の物理的な構成を示すブロック図である。

**【0039】**

計算機100は、プロセッサ（CPU）101、メモリ102、不揮発性の記憶装置（HDD）103、及び通信インターフェース106を有する計算機である。

50

**【0040】**

プロセッサ101は、メモリ102に格納されたプログラムを実行する。

**【0041】**

メモリ102は、例えば、D R A M (Dynamic Random Access Memory) のような高速かつ揮発性の記憶装置であり、オペレーティングシステム( O S )及びアプリケーションプログラムを格納する。プロセッサ101が、オペレーティングシステムを実行することによって、計算機100の基本機能が実現され、アプリケーションプログラムを実行することによって、並列化コンパイラの機能が実装される。

**【0042】**

記憶装置103は、例えば、磁気記憶装置、フラッシュメモリ等の大容量かつ不揮発性の記憶装置であり、プロセッサ101によって実行されるコンパイラ及び元プログラムを格納する。すなわち、プロセッサ101が実行するコンパイラは、記憶装置103から読み出されて、メモリ102にロードされて、プロセッサ101によって実行される。

10

**【0043】**

通信インターフェース106は、計算機100と他の計算機との通信を制御する。

**【0044】**

計算機100は、入力インターフェース104及び出力インターフェース105を有してもよい。入力インターフェース104は、入力機器であるキーボード107及びマウス108からの入力を受ける。出力インターフェース105は、出力装置であるディスプレイ装置109に接続されており、ディスプレイ装置109に演算結果を表示するための信号を出力する。

20

**【0045】**

計算機100は、論理的又は物理的に構成された一つ又は複数の計算機上で稼働するシステムである。並列化コンパイラは、一つの計算機上で動作してもよく、複数の物理的計算機資源上に構築された仮想計算機上で動作してもよい。

**【0046】**

プロセッサ101によって実行されるプログラムは、リムーバブルメディア( C D - R O M、フラッシュメモリなど)又はネットワークを介して各サーバに提供され、非一時的記憶媒体である記憶装置103に格納される。このため、各サーバは、リムーバブルメディアを読み込むインターフェースを備えるとよい。

30

**【0047】**

[逐次処理のエンジン制御プログラムの概要]

次に、本実施例における元プログラムを含むエンジン制御プログラムの概要を示す。

**【0048】**

本実施例におけるエンジン制御プログラムは、C言語で記述されており、自動車向けリアルタイムO SであるO S E K / V D X上( 例えば、非特許文献3参照 )で動作する。

**【0049】**

プログラムの動作を以下に示す。

**【0050】**

以下の説明において、エンジン制御プログラムにおける「タスク」は自動車制御用プログラムで使われる用語であり、前述した並列化コンパイラに入力する元プログラムに相当する。

40

**【0051】**

前記エンジン制御プログラムが従来の單一コアプロセッサ上で実行される場合は、まず、C言語のm a i n関数からO S E K / V D Xが提供するA P IであるS t a r t O S関数をコールすることによってO Sを起動する。

**【0052】**

その後、エントリタスクから周期的に実行されるタスクの実行を予約する。本エンジン制御プログラムでは、タスクはT a s k 2 - T a s k 3 9の合計38個が定義されており、周期タスクであるT a s k 2 2 - T a s k 3 9の実行が予約される。なお、T a s k 2

50

- Task 21 は周期タスクから間接的に呼び出されるタスクである。

#### 【0053】

その後、OS 内のタイマにより、周期タスクが周期的に実行される。

#### 【0054】

図 3 に実行プロファイルの結果を示す。なお、本結果は実際にエンジン制御プログラムを動作させている車載向けマイコンを用いて、測定した結果である。図 3 において、横軸はタスク番号、縦軸は各タスクの実行時間がプログラム全体実行時間に占める割合を示している。図 3 より、Task 20、Task 21、Task 15 の順番で処理時間が大きいことがわかる。このうち、Task 20、Task 21 はアイドルタスク（演算処理を行わない時間待ちのためだけに用意されているタスク）であるため、本実施例では実質的に処理量が一番大きい Task 15 に着目し、Task 15 を元プログラムとしてその並列性を抽出し、並列化プログラムを生成する。

10

#### 【0055】

##### [ エンジン制御プログラムからの並列性の抽出との並列化手法 ]

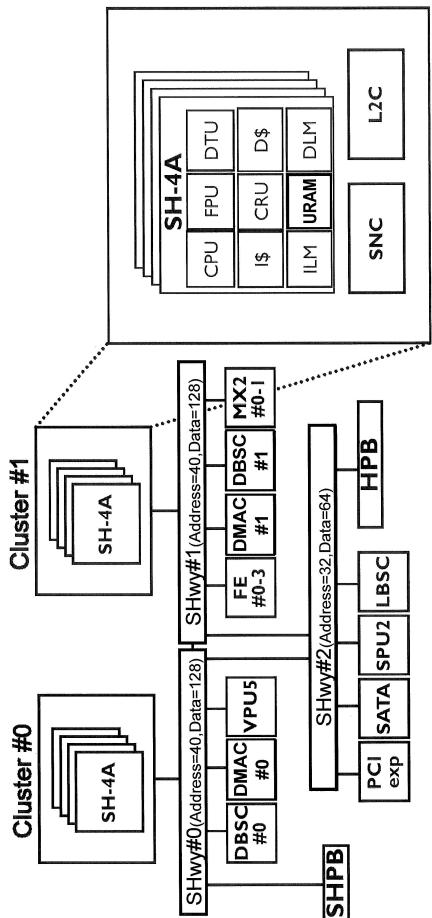

次に、前記エンジン制御プログラム中の Task 15 からの並列性の抽出方法と並列化方法について以下に説明する。また、生成される並列化プログラムを図 10 に示すマルチコアプロセッサ RP-X 上で動作させ、性能評価を行うことを前提に本発明のコンパイラによる並列化処理を行う。

#### 【0056】

まず、Task 15 の並列性を解析する。この並列性解析における 1901 から 1908 までのコンパイラの処理ステップは、図 17 に示す従来の OSCAR コンパイラの処理ステップと変わることはない。Task 15 にはエントリ関数があり、これを Task 15 main と称する。当該エンジン制御プログラムは、Task 15 計算部本体とテストドライバからなり、テストドライバはシナリオ 1、シナリオ 2、シナリオ 3 からなる三つの実行シナリオで Task 15 を実行する。以下の説明では、Task 15 main を元プログラムとして焦点を当て、その並列性の抽出方法について説明する。

20

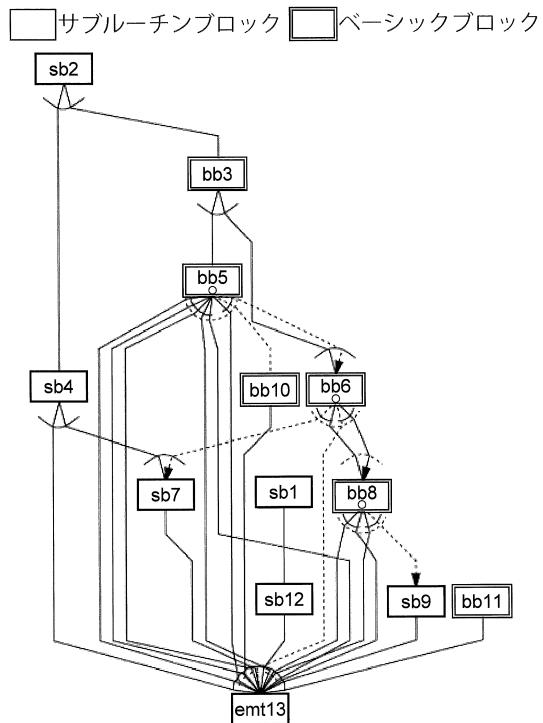

#### 【0057】

図 4 に、図 1A に示した本発明の実施形態のコンパイラが実行する処理のフロー チャートにおけるステップ 1907 の「最早実行可能条件解析」を経て生成された Task 15 main の MTG を示す。図 4 の MTG において、sb2 や sb4 などのように四角で囲んだマクロタスクはサブルーチンブロック、bb3 や bb5 などのように二重四角で囲んだマクロタスクはベーシックブロックを示す。図 5 に各タスクの実行シナリオ別のマクロタスクの実行コスト（時間）を示す。図 5 における実行コストの単位はクロック（clock）である。

30

#### 【0058】

図 5 に示すマクロタスクの実行コストは、RP-X 上で 648MHz にて計測したもので、コンパイラによる Task 15 main の並列化処理におけるステップ 1907 の「最早実行可能時間解析」などに必要なデータとしてコンパイラに予め入力される。なお、RP-X は、組込用マルチコアプロセッサであり、その構成は図 10 を用いて後に説明する。

40

#### 【0059】

Task 15 main の MTG 生成後、コンパイラは図 1A のステップ 2909 に示す、本発明の並列性抽出方法の特徴である「条件分岐の複製を含むリストラクチャリング」のステップに入る。このステップは、すでに述べたように、図 17 に示す従来の並列化コンパイラのステップ 1907 の「各種のリストラクチャリング」の機能に本発明の条件分岐の複製の機能を追加したものである。以下の説明では単に「リストラクチャリング」と呼ぶこともある。ステップ 2909 における処理をさらに細かく展開した処理フローである図 1B を用いて詳細を説明する。なお、図 1B において、19071 から 19074 までのステップと 19076、19077 のステップは、図 17 に示す従来の並列化コンパイラのステップ 1907 に含まれており、ステップ 2909 は本発明の特徴である条件

50

分岐の複製のステップである。

#### 【0060】

図4より、この階層では、s b 1、b b 3、s b 4をそれぞれ並列に実行可能であるため、並列度は3であるが、図5より、s b 4の実行時間の占める割合が、シナリオ1で94.3%、シナリオ2で92.6%と相対的に大きい。このため、これらのシナリオではs b 4の内部を並列化することが重要である。シナリオ3では、s b 4が29%、s b 7が68.9%となるため、s b 4及びs b 7の内部をそれぞれ並列化することが重要である。いずれにしても、s b 4及びs b 7を含むパスがクリティカルパスとなる。このようにクリティカルパスを見出す処理が図1Bのステップ19071のクリティカルパスの抽出である。

10

#### 【0061】

また、プログラムの構造に、大きなループ処理がなく、条件分岐及び代入文が連続する場合、すでに述べたように、従来の並列性の抽出方法を用いる並列化コンパイラではダイナミックスケジューリングに依らざるを得ない。しかし、図5よりわかるように、実行時間が非常に短いため、並列化した際の同期処理オーバーヘッドや、ダイナミックスケジューリングのスケジューリングオーバーヘッドが相対的に大きくなる問題点がある。

#### 【0062】

そこで、当該プログラムを並列化するために、代入文の並列性や関数間の並列性を利用する粗粒度並列化と、スタティックスケジューリングとを適用することが重要となる。

20

#### 【0063】

次に、並列性向上のために行った逐次処理の元プログラムへのリストラクチャリングの次のステップ19072のインライン展開について述べる。

#### 【0064】

まず、図4のs b 4及びs b 7が内包する並列性を有効活用するため、s b 4及びs b 7の内部関数のMTG及びRP-Xのプロファイル情報に基づいて、並列性があり、かつ相対的に実行コストが大きい関数を選択し、その関数をTask15mainの階層までインライン展開をしていく。これにより、Task15mainの階層における並列性が向上する。

#### 【0065】

インライン展開した後のMTGにおいて並列処理時間を短縮するために、MTG上の最長の処理時間を示すパス（クリティカルパス）上にある条件分岐を抽出し（ステップ19073）、抽出した条件分岐のうち条件分岐に後続する複数のマクロタスク間の並列性（すなわち、当該マクロタスク間でデータ依存がないこと）を抽出する（ステップ19074）。その抽出した並列性に基づき、条件分岐を複製する（ステップ29095）。

30

#### 【0066】

この実施例で取り上げた元プログラムの例では、s b 7は条件分岐内に存在するため、s b 7をインライン展開しても、それらは一つの条件分岐内に収まってしまい、一つのマクロタスクとしてプロセッサに割り当てられる。そこで、条件分岐内の並列性を抽出するために、コンパイラが条件分岐を複製する。例えば、図6に示す条件分岐があり、条件分岐内の3個の関数が並列化可能だとし、条件式（condition）が条件分岐内で変更されない場合を考える。

40

#### 【0067】

図6に示す状態では、この条件分岐を一つのプロセッサに割り当てるうことになり、func1 - func3の並列性を活かすことができない。そこで、図7のようにプログラムを書き換える。この処理によって、各条件分岐が合計3つのマクロタスクに複製され、各マクロタスクを別々のプロセッサに割り当てることが可能となる。以上の条件分岐の複製のための一連の処理はステップ29095において行われる。また、この処理の結果、MTG上で他のパスがクリティカルパスになることがある。その場合には、処理をステップ1902に戻し、ステップ1902から1908までの処理を経て、ステップ2909において新たなクリティカルパスに対して条件分岐の複製を適用する。これらの処理は条件

50

分岐の複製と後述するタスク融合が必要な限り行う。これにより、条件分岐内の並列性を抽出することが可能となり、Task15mainの階層における並列性を向上することができる。

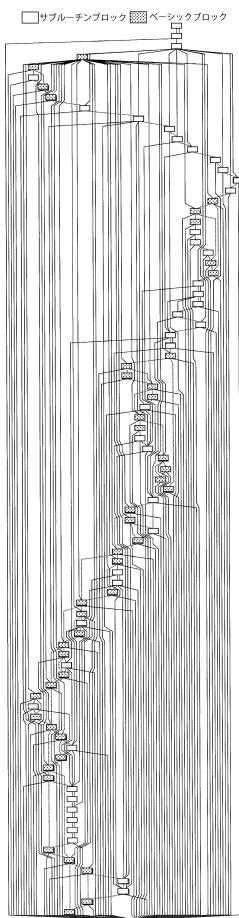

#### 【0068】

図8に、オンライン展開や条件分岐の複製を行い、並列性を向上した後にステップ1905を経て生成されたTask15mainのMFGを示す。図8のMFGは、ステップ2909においてオンライン展開を行ったまま条件分岐の複製を行った後にステップ1905にて生成されたものなので、粒度の小さなマクロタスクが多数存在する。

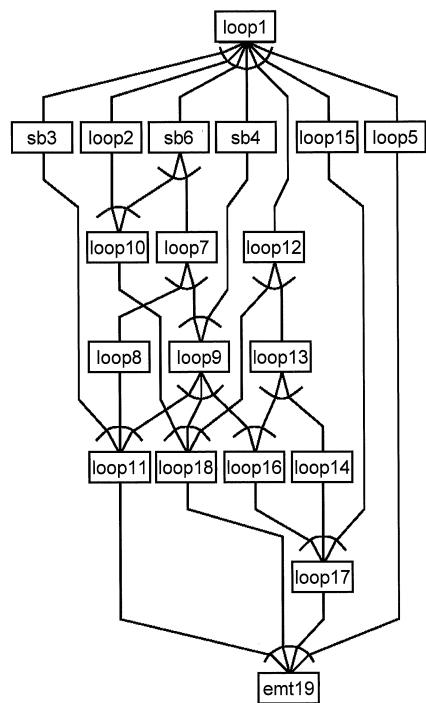

#### 【0069】

そのため、ステップ1908において、図8のMFGからMTGを生成した後に、本実施例では、ステップ2909の中のステップ19076において実行コストが小さい複数のタスクを一つの粗粒度タスク（マクロタスク）として融合するタスク融合を行った。このタスク融合により生成されたMTGを図9に示す。図9において、タスク融合を行ったブロックはloopと表示される。図9からわかるように、並列性が損なわれない範囲で条件分岐や代入文をタスク融合することによって、一つ一つのマクロタスクを、プログラムの制御オーバーヘッドが相対的に小さくなるような処理コストを持った粒度とすることが可能である。また、このような処理を経て、データ依存のみの2並列程度の並列性を抽出することができる。これにより、制御フローを全てデータ依存の形に集約することができ、低オーバーヘッドなスタティックスケジューリングの適用が可能となる。なお、実行コストに基づくタスク融合の処理機能（ステップ19076）は、すでに述べたように本発明の特徴ではなく、従来のOSCARコンパイラにも実装されている（非特許文献6を参照）。

10

#### 【0070】

以上、条件分岐の複製を含むリストラクチャリングによる並列性の抽出と並列化プログラムの作成を本発明のコンパイラにより実行した場合のフローを説明してきたが、その中で実行された条件分岐の複製について、その具体例を用いて以下に簡単に説明する。

#### 【0071】

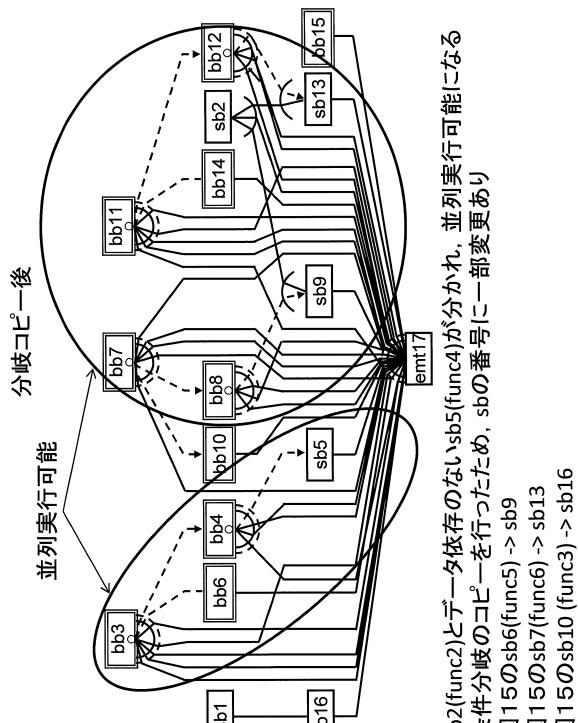

図15は、条件分岐の複製のステップ29095をより具体的に説明するために用意した条件分岐の複製前のMTGの一例であり、図16は、図15のMTGに条件分岐の複製の処理を施した後のMTGである。

20

#### 【0072】

図15に示す条件分岐の複製前のMTGによると、sb2(func2)はsb6(func5)及びsb7(func6)にデータ依存するが、sb5(func4)にデータ依存しない。従って、図15のMTGに表された条件分岐を複製して2つの条件分岐を生成し、その一方にsb2を含むパスが含まれ、もう一方の条件分岐にはsb2と並列実行可能なsb5が含まれるようにすることができる。

30

#### 【0073】

このように、図16に示す条件分岐の複製後のMTGによると、sb2(func2)とデータ依存のないsb5(func4)とが分かれ、並列実行可能となるので、その各々を2つのプロセッサコアに割り当てることができる。なお、条件分岐を複製したため、一部のサブブロック番号が変更されている。

40

|       |             |       |      |

|-------|-------------|-------|------|

| 分岐複製前 | sb6(func5)  | 分岐複製後 | sb9  |

| 分岐複製前 | sb7(func6)  | 分岐複製後 | sb13 |

| 分岐複製前 | sb10(func3) | 分岐複製後 | sb16 |

#### 【0074】

##### [性能評価]

本項では、実施形態の説明のために挙げた自動車エンジン制御プログラムを本発明の並列性の抽出方法を用いて並列化したプログラムを組込用マルチコアプロセッサRPP-X上で実行させ、その並列処理性能を評価する。

#### 【0075】

50

まず、これまでの説明で述べた方法で並列化したエンジン制御プログラムの性能評価を行った組込用マルチコアプロセッサ R P - X の構成について説明する。

#### 【 0 0 7 6 】

図 1 0 に示すように、R P - X は、4 5 n m L o w P o w e r テクノロジ、1 5 コアのマルチコアプロセッサで、汎用プロセッサコアとして動作周波数を 6 4 8 M H z、3 2 4 M H z、1 6 2 M H z、8 1 M H z と変更して動作する S H - 4 A コアを 8 個、アクセラレータコアとして 3 2 4 M H z で動作する F E - G A を 4 個、その他ハードウェア I P を搭載している。

#### 【 0 0 7 7 】

各汎用プロセッサコア内メモリは、命令キャッシュ (3 2 K B)、データキャッシュ (3 2 K B)、ローカルメモリ (I L M、D L M : 1 6 K B)、分散共有メモリ (U R A M : 6 4 K B) 及びデータ転送ユニットを有する。また、アクセラレータコアはコントローラなしアクセラレータであり、オンチップバス (S H w y # 1) に接続されている。10

#### 【 0 0 7 8 】

現在のエンジン制御系で 2 コアのマルチコアが検討されているため、本実施例では、汎用プロセッサコアとして 2 個の S H - 4 A コアを計算資源として用いた。また、汎用コアの動作周波数を 6 4 8 M H z から 3 2 4 M H z、1 6 2 M H z、8 1 M H z と変化させた時のバスの動作周波数は 3 2 4 M H z に固定し、性能を評価した。これはバスの動作周波数を固定し、汎用コアの動作周波数を下げるこによって、メモリアクセスレイテンシを相対的に低くするためであり、メモリアクセスレイテンシが小さい車載向けマイコンの環境に近付けるためである。20

#### 【 0 0 7 9 】

次に、組込用マルチコアプロセッサ R P - X 上での並列処理性能評価条件を説明する。

#### 【 0 0 8 0 】

図 1 1 に R P - X 上 6 4 8 M H z 実行時の T a s k 1 5 m a i n の実行プロファイル結果を示す。なお、単位は c l o c k である。R P - X 上で性能評価を行うにあたっては、各シナリオ毎にコンパイラに本プロファイル情報を与え、スタティックスケジューリングを行うことで、負荷を分散する。図 1 1 より、各シナリオで実行コストが異なる。これは、各シナリオにおいて処理を高速化するためには、負荷分散が重要なためである。

#### 【 0 0 8 1 】

また通常、グローバル変数はオフチップ共有メモリに配置する。この場合、キャッシュヒットの際には 1 サイクルでデータを読み出せるが、キャッシュミスの際には、データの読み出しに 5 5 サイクルを必要とする。エンジン制御プログラムのようなマイクロ秒オーダーで動作するプログラムにおいて、このペナルティは非常に大きい。そこで、メモリアクセスレイテンシが小さいローカルメモリにグローバル変数を配置することが重要となる。しかし、全てのグローバル変数をローカルメモリに配置すると、メモリ容量を超えるため、メモリ容量内に収めるために、初期値無しのグローバル変数 (約 7 . 5 k b y t e) のみをローカルメモリに配置する。また、プロセッサコア間の同期を担う同期変数を、オフチップ共有メモリに配置すると、メモリアクセスレイテンシのペナルティが大きいため、レイテンシが小さい分散共有メモリに配置する。これにより、高速化が可能となる。30

#### 【 0 0 8 2 】

メモリ配置による性能差を比較するため、グローバル変数全てを共有メモリに配置した場合と、グローバル変数の一部をローカルメモリに配置し、プロセッサコア間の同期を担う同期変数を分散共有メモリに配置した場合の性能を評価する。

#### 【 0 0 8 3 】

次に、組込用マルチコア R P - X 上での並列処理性能評価結果を説明する。

#### 【 0 0 8 4 】

図 1 2 にシナリオ 1 を 1 C P U、2 C P U、メモリ配置を工夫した 2 C P U で実行した場合の速度向上率を示す。図 1 2 において、横軸は動作周波数、縦軸は 1 C P U 実行時にに対する速度向上率である。具体的な実行時間は表 1 に示すとおりである。8 1 M H z で 14050

.57倍、162MHzで1.55倍、324MHzで1.53倍、648MHzで1.48倍に速度が向上した。メモリ配置を工夫した場合、81MHzで1.60倍、162MHzで1.71倍、324MHzで1.69倍、648MHzで1.62倍に速度が向上した。メモリ配置を工夫することによって、2%から11%の性能が改善した。

【0085】

【表1】

|                 | 81MHz   | 162MHz  | 324MHz  | 648MHz  |

|-----------------|---------|---------|---------|---------|

| 1CPU            | 356.2us | 253.9us | 198.5us | 174.7us |

| 2CPU            | 227.0us | 163.8us | 129.8us | 118.3us |

| 2CPU-memory opt | 222.4us | 148.1us | 117.1us | 107.7us |

10

### シナリオ1を実行した場合の処理時間をまとめた表

【0086】

図13にシナリオ2を1CPU、2CPU、メモリ配置を工夫した2CPUで実行した場合の速度向上率を示す。図13において、横軸は動作周波数、縦軸は1CPU実行時にに対する速度向上率である。具体的な実行時間は表2に示すとおりである。81MHzで1.38倍、162MHzで1.46倍、324MHzで1.40倍、648MHzで1.17倍の速度向上が得られた。メモリ配置を工夫した場合、81MHzで1.54倍、162MHzで1.58倍、324MHzで1.45倍、648MHzで1.25倍に速度が向上した。メモリ配置を工夫することによって、3%から11%の性能が改善した。

20

【0087】

【表2】

|                 | 81MHz   | 162MHz | 324MHz | 648MHz |

|-----------------|---------|--------|--------|--------|

| 1CPU            | 122.0us | 74.4us | 49.9us | 37.2us |

| 2CPU            | 88.6us  | 51.0us | 35.6us | 31.7us |

| 2CPU-memory opt | 79.5us  | 47.1us | 34.5us | 29.9us |

30

### シナリオ2を実行した場合の処理時間をまとめた表

【0088】

図14にシナリオ3を1CPU、2CPU、メモリ配置を工夫した2CPUで実行した場合の速度向上率を示す。図14において、横軸は動作周波数、縦軸は1CPU実行時にに対する速度向上率である。具体的な実行時間は表3に示す通りである。81MHzで1.51倍、162MHzで1.46倍、324MHzで1.41倍、648MHzで1.42倍の速度向上が得られた。メモリ配置を工夫した場合、81MHzで1.53倍、162MHzで1.50倍、324MHzで1.46倍、648MHzで1.43倍に速度が向上した。メモリ配置を工夫することによって、1%から3%の性能が改善した。

40

【0089】

## 【表3】

|                 | 81MHz   | 162MHz  | 324MHz  | 648MHz  |

|-----------------|---------|---------|---------|---------|

| 1CPU            | 546.3us | 356.2us | 255.5us | 207.7us |

| 2CPU            | 360.8us | 243.2us | 181.1us | 146.7us |

| 2CPU-memory opt | 356.5us | 237.7us | 175.1us | 145.4us |

シナリオ3を実行した場合の処理時間をまとめた表

10

## 【0090】

先に述べた本発明の実施例では、逐次処理の自動車エンジン制御プログラムを並列化してマルチコアプロセッサ上で実行させる場合を例に挙げて、本発明の特徴である並列性の抽出方法とその方法を用いたプログラムの並列化方法を説明した。また、本発明を適用した並列化コンパイラを用いて、逐次処理の元プログラムの並列性を抽出するために行なった、相対的に実行コストが大きい関数のインライン展開と条件分岐の複製を含む並列性の抽出、およびスタティックスケジューリング適用のためのタスク融合を行なった後、すなわち逐次処理の元プログラムのリストラクチャリングを行なった後、並列化プログラムを生成し、組込用マルチコアプロセッサ上で並列処理性能の評価を行なった。その結果、マルチコア上で従来並列化に成功した例がない、極めて並列化が困難であった自動車エンジン制御プログラムにおいて、2プロセッサコアを用いた場合、1プロセッサコアを使用した場合と比較して、シナリオ1における162MHzの場合、1.71倍の性能向上が得られた。

20

## 【0091】

本実施例では、コンパイラによる並列化を利用し、高速化を実現でき、自動車エンジン制御プログラムの自動並列化及び高速化が可能であることが確認できた。このように、本発明の方法を用いることにより、自動車エンジン制御プログラム又は一般的な制御用プログラムのような、条件分岐や代入文の多いプログラムにおいても、並列処理による高速化が可能となる。

## 【0092】

以上、本発明を添付の図面を参照して詳細に説明したが、本発明はこのような具体的構成に限定されるものではなく、添付した請求の範囲の趣旨内における様々な変更及び同等の構成を含むものである。

30

## 【0093】

特許請求の範囲に記載した以外の本発明の観点の代表的なものとして、次のものがあげられる。

## 【0094】

(1) 複数のプロセッサコアを含むマルチコアプロセッサの制御方法であって、前記複数のプロセッサコアによって実行されるプログラムは、1以上の条件分岐の集合を含み、

前記方法は、

2以上の前記プロセッサコアの各々が、少なくとも一つの前記複数の条件分岐の集合を実行し、

前記2以上のプロセッサコアの各々が、前記実行した条件分岐の集合の同一条件を満たした後に実行されるべき1以上のマクロタスクを実行するように、前記マルチコアプロセッサを制御する方法。

40

## 【0095】

(2) 複数のプロセッサコアを含むマルチコアプロセッサ上で実行可能プログラムを元プログラムからコンピュータによって作成する方法であって、

同一の条件で実行が決定される複数のマクロタスクのうち、前記実行される複数のマクロタスクの相互の間でデータ依存がない条件分岐の集合を前記元プログラムから抽出し、

50

前記抽出された条件分岐の集合を複製し、

前記複製された条件分岐の集合を、2以上の前記プロセッサコアの各々が実行するよう

に割り当てることによって実行可能プログラムを作成する方法。

【0096】

(3) 複数のプロセッサコアを含むマルチコアプロセッサの制御方法であって、

前記複数のプロセッサコアによって実行されるプログラムは、1以上の条件分岐の集合

を含み、

前記方法は、

1以上の前記プロセッサコアの各々が、少なくとも一つの前記1以上の条件分岐の集合

を実行し、

前記1以上のプロセッサコアの各々が、前記実行した条件分岐の集合の同一条件を満た

した後に実行されるべき1以上のマクロタスクを実行するように、前記マルチコアプロセ

ッサを制御する方法。

【0097】

(4) 前記条件分岐の集合は、一つの条件判断の結果による分岐、あるいは一つの条件

判断の結果によるさらなる条件分岐を1又は複数含むことを特徴とする(3)に記載の制御

方法。

【0098】

(5) 複数のプロセッサコアを含むマルチコアプロセッサ上で実行可能プログラムを元

プログラムからコンピュータによって作成する方法であって、

同一の条件で実行が決定される複数のマクロタスクのうち、前記実行される複数のマク

ロタスクの相互の間でデータ依存がない条件分岐の集合を前記元プログラムから抽出し、

前記抽出された条件分岐の集合を複製し、

前記複製された条件分岐の集合を、1以上の前記プロセッサコアの各々が実行するよう

に割り当てることによって実行可能プログラムを作成する方法。

【0099】

(6) 前記条件分岐の集合は、一つの条件判断の結果による分岐、あるいは一つの条件

判断の結果によるさらなる条件分岐を1又は複数含むことを特徴とする(5)に記載のブ

ログラムの作成方法。

【符号の説明】

【0100】

100 計算機

101 プロセッサ(CPU)

102 メモリ

103 記憶装置(HDD)

106 通信インターフェース

10

20

30

【図1A】

本発明を用いた並列化コンパイラの処理フロー

【図1B】

【図2】

【図3】

【図4】

【図5】

| Scenario1 |      |        |       |        |        |

|-----------|------|--------|-------|--------|--------|

| sb1       | sb2  | sb4    | sb12  | 全体     |        |

| 978       | 3415 | 114739 | 519   | 121680 |        |

| Scenario2 |      |        |       |        |        |

| sb1       | sb2  | sb4    | sb9   | sb12   | 全体     |

| 42        | 489  | 20031  | 393   | 38     | 21641  |

| Scenario3 |      |        |       |        |        |

| sb1       | sb2  | sb4    | sb7   | sb12   | 全体     |

| 40        | 228  | 37225  | 88476 | 455    | 128364 |

【図6】

```

If (condition){

func1();

func2();

func3();

}

```

【図7】

```

If (condition){

func1();

}

If (condition){

func2();

}

If (condition){

func3();

}

```

【図8】

【図9】

【図 1 0】

【図 1 2】

【図 1 3】

【図 1 1】

|       | Scenario1 | Scenario2 | Scenario3 | Scenario1 | Scenario2 | Scenario3 |

|-------|-----------|-----------|-----------|-----------|-----------|-----------|

| loop1 | 6038      | 987       | 586       | loop10    | 22476     | 1485      |

| loop2 | 9665      | 2518      | 1558      | loop11    | 38288     | 4672      |

| Sb3   | 4204      | 197       | 1090      | loop12    | 285       | 357       |

| Sb4   | 1720      | 727       | 403       | loop13    | 370       | 129       |

| loop5 | 7371      | 7961      | 4583      | loop14    | 403       | 127       |

| sb6   | 5606      | 3096      | 11696     | loop15    | 116       | 129       |

| loop7 | 12957     | 2518      | 2291      | loop16    | 351       | 129       |

| loop8 | 4234      | 323       | 1393      | loop17    | 426       | 129       |

| loop9 | 10326     | 3742      | 4641      | loop18    | 380       | 324       |

|       |           |           |           |           | 15219     |           |

【図 1 4】

【図 1 5】

【図16】

【図17】

従来の並列化コンパイラの処理フロー

【図18A】

(a) Macro Flow Graph (MFG)

【図18B】

(b) Macro Task Graph (MTG)

---

フロントページの続き

(72)発明者 見神 広紀

東京都新宿区大久保3 - 4 - 1 早稲田大学理工学術院基幹理工学部情報理工学科内

(72)発明者 金羽木 洋平

東京都新宿区大久保3 - 4 - 1 早稲田大学理工学術院基幹理工学部情報理工学科内

(72)発明者 梅田 弾

東京都新宿区大久保3 - 4 - 1 早稲田大学理工学術院基幹理工学部情報理工学科内

(72)発明者 沢田 光男

愛知県豊田市トヨタ町1番地 トヨタ自動車株式会社内

審査官 坂庭 剛史

(56)参考文献 國際公開第2010/047174 (WO, A1)

特開2002-116916 (JP, A)

特開2006-154971 (JP, A)

合田憲人、岡本雅巳、吉田明正、本多弘樹、笠原博徳、マクロデータフロー処理におけるマクロタスク分割・融合手法、電子情報通信学会技術研究報告、日本、社団法人電子情報通信学会、1991年7月16日、Vol. 91, No. 130, p. 205-212 (CPSY91-30)

岩澤京子、黒澤 隆、菊池純男、並列化支援システムによるFortran DOループの並列化方法、情報処理学会論文誌、日本、社団法人情報処理学会、1995年8月15日、Vol. 36, No. 8, p. 1995-2006, ISSN0387-5806

梅田 弾、金羽木洋平、見神広紀、林 明宏、谷 充弘、森 裕司、木村啓二、笠原博徳、エンジン基本制御ソフトウェアモデルのマルチコア上での並列処理、情報処理学会研究報告 2012(平成24)年度 3 [CD-ROM]、日本、一般社団法人情報処理学会、2012年10月15日、Vol.2012-ARC-201, No.22, p. 1 - 7, ISSN1884-0930