(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6428341号

(P6428341)

(45) 発行日 平成30年11月28日(2018.11.28)

(24) 登録日 平成30年11月9日(2018.11.9)

(51) Int.Cl.

H03B 19/14 (2006.01)

H03F 3/60 (2006.01)

F 1

H03B 19/14

H03F 3/60

請求項の数 4 (全 7 頁)

(21) 出願番号 特願2015-26705 (P2015-26705)

(22) 出願日 平成27年2月13日 (2015.2.13)

(65) 公開番号 特開2016-149708 (P2016-149708A)

(43) 公開日 平成28年8月18日 (2016.8.18)

審査請求日 平成29年7月18日 (2017.7.18)

(73) 特許権者 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目7番3号

(74) 代理人 100082175

弁理士 高田 守

(74) 代理人 100106150

弁理士 高橋 英樹

(74) 代理人 100148057

弁理士 久野 淑己

(72) 発明者 久留須 整

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

(72) 発明者 塚原 良洋

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

最終頁に続く

(54) 【発明の名称】周波数遅倍器

## (57) 【特許請求の範囲】

## 【請求項 1】

入力端子と、

出力端子と、

前記入力端子から高周波信号が入力される第1ゲートと、前記出力端子へ出力信号を出す第1ドレインと、第1ソースとを有する第1トランジスタと、

第2ゲートと、前記入力端子から前記高周波信号が入力される第2ソースと、前記出力端子へ出力信号を出す第2ドレインと、を有する第2トランジスタと、

一端が前記第2ゲートに接続され、他端が接地導体に直接接続、又はキャパシタを介して接地金属と接続された安定化抵抗と、を備え、

前記入力端子と前記出力端子の間の経路上に抵抗素子がなく、

前記安定化抵抗の抵抗値は、前記安定化抵抗を出力側から見たときの反射係数であるS22の絶対値が1を超えない値に設定したことを特徴とする周波数遅倍器。

## 【請求項 2】

前記第1ゲートに接続された第1ゲートバイアス回路と、

前記第1ソースに接続された第1ソースバイアス回路と、

前記第2ソースに接続された第2ソースバイアス回路と、を備え、

前記第1ゲートバイアス回路と、前記第1ソースバイアス回路と、前記第2ソースバイアス回路は、抵抗で形成されたことを特徴とする請求項1に記載の周波数遅倍器。

## 【請求項 3】

10

20

前記第2ゲートに接続されたキャパシタを備えたことを特徴とする請求項1又は2に記載の周波数倍器。

**【請求項4】**

前記高周波信号が通過する主線路から分岐する分岐線路に接続され、前記第1ドレインと前記第2ドレインに電位を供給する電源と、

前記分岐線路に直列に接続された抵抗と、を備えたことを特徴とする請求項1～3のいずれか1項に記載の周波数倍器。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

10

本発明は、例えばマイクロ波又はミリ波の高周波帯の電力を倍率する周波数倍器に関する。

**【背景技術】**

**【0002】**

特許文献1には、ソース接地トランジスタとゲート接地トランジスタを並列に接続する周波数倍器が開示されている。この周波数倍器に入力された基本周波数の電力は、ソース接地トランジスタで逆相出力され、ゲート接地トランジスタで同相出力されるので出力側の電力合成で打ち消される。そして、両トランジスタで同相出力される2倍波周波数電力を出力端子から取り出す。

**【0003】**

20

特許文献2には、両トランジスタの出力側にダンピング抵抗を設けて安定化を図ることが開示されている。

**【先行技術文献】**

**【特許文献】**

**【0004】**

**【特許文献1】特開平3-158008号公報**

**【特許文献2】特開2001-244746号公報**

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0005】**

30

特許文献1に開示の周波数倍器では、周波数の高いマイクロ波又はミリ波帯において、ゲート接地トランジスタが負性抵抗特性を示すことにより発振が生じるという問題点があった。

**【0006】**

特許文献2に開示の周波数倍器では、トランジスタで生成した2倍波周波数の電力がダンピング抵抗によって消費され、周波数倍器の特性である変換利得が低下するという問題点があった。

**【0007】**

本発明は、上述のような課題を解決するためになされたもので、高周波信号が通過する経路上に抵抗を設けることなく、ゲート接地トランジスタが示す負性抵抗特性等の不安定性を安定化できる周波数倍器を提供することを目的とする。

40

**【課題を解決するための手段】**

**【0008】**

本願の発明に係る周波数倍器は、入力端子と、出力端子と、該入力端子から高周波信号が入力される第1ゲートと、該出力端子へ出力信号を出す第1ドレインと、第1ソースとを有する第1トランジスタと、第2ゲートと、該入力端子から該高周波信号が入力される第2ソースと、該出力端子へ出力信号を出す第2ドレインと、を有する第2トランジスタと、一端が該第2ゲートに接続され、他端が接地導体に直接接続、又はキャパシタを介して接地金属と接続された安定化抵抗と、を備え、該入力端子と該出力端子の間の経路上に抵抗素子がなく、該安定化抵抗の抵抗値は、該安定化抵抗を出力側から見たときの反射

50

係数である S 2 2 の絶対値が 1 を超えない値に設定したことを特徴とする。

【発明の効果】

【0009】

本発明によれば、ゲート接地トランジスタのゲートに抵抗を接続したので、ゲート接地トランジスタを安定化させることができる。

【図面の簡単な説明】

【0010】

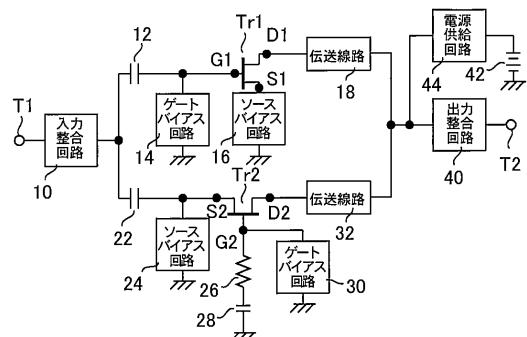

【図1】実施の形態1に係る周波数倍器の回路図である。

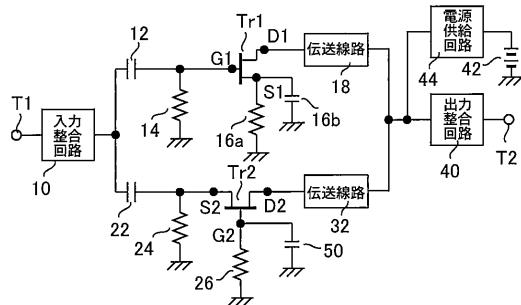

【図2】実施の形態2に係る周波数倍器の回路図である。

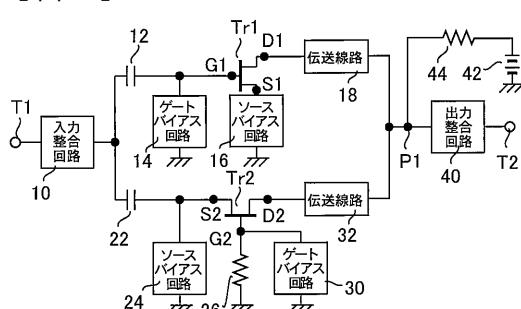

【図3】実施の形態3に係る周波数倍器の回路図である。

10

【図4】実施の形態4に係る周波数倍器の回路図である。

【発明を実施するための形態】

【0011】

本発明の実施の形態に係る周波数倍器について図面を参照して説明する。同じ又は対応する構成要素には同じ符号を付し、説明の繰り返しを省略する場合がある。

【0012】

実施の形態1.

図1は、本発明の実施の形態1に係る周波数倍器の回路図である。この周波数倍器は入力端子T1に入力された高周波信号の周波数を整数倍して出力端子T2に出力するものである。入力端子T1には入力整合回路10が接続されている。出力端子T2には出力整合回路40が接続されている。

20

【0013】

実施の形態1に係る周波数倍器は、ソース接地トランジスタである第1トランジスタTr1とゲート接地トランジスタである第2トランジスタTr2を備えている。第1トランジスタTr1は、入力端子T1から高周波信号が入力される第1ゲートG1と、出力端子T2へ出力信号を出す第1ドレインD1と、接地された第1ソースS1とを有する。

【0014】

第1ゲートG1は、直流遮断用キャパシタ12を介して入力整合回路10に接続されている。第1ゲートG1と接地導体との間には第1ゲートバイアス回路14が接続されている。第1ソースS1と接地導体との間には第1ソースバイアス回路16が接続されている。第1ドレインD1は伝送線路18を介して出力整合回路40に接続されている。

30

【0015】

第2トランジスタTr2は、第2ゲートG2と、入力端子T1から高周波信号が入力される第2ソースS2と、出力端子T2へ出力信号を出す第2ドレインD2とを有する。

【0016】

第2ソースS2は、直流遮断用キャパシタ22を介して入力整合回路10に接続されている。第2ソースS2と接地導体との間には第2ソースバイアス回路24が接続されている。第2ゲートG2と接地の間には抵抗である安定化抵抗26とキャパシタ28が接続されている。さらに、第2ゲートG2と接地導体との間には第2ゲートバイアス回路30が接続されている。第2ドレインD2は伝送線路32を介して出力整合回路40に接続されている。

40

【0017】

伝送線路18、32の出力側には電源42に接続された電源供給回路44が接続されている。図1から明らかなように、入力端子T1から出力端子T2までの高周波信号の経路上には抵抗がない。

【0018】

本発明の実施の形態1に係る周波数倍器の動作について説明する。まず、第1トランジスタTr1のゲートソース間バイアス電圧を第1トランジスタTr1のピンチオフ電圧付近とする。また、第2トランジスタTr2のゲートソース間バイアス電圧を第2トランジスタTr2のピンチオフ電圧付近とする。

50

## 【0019】

そして、入力端子T<sub>1</sub>に高周波信号（正弦波）を供給すると、第1トランジスタT<sub>r1</sub>は正の半波を整流したものを出力し、第2トランジスタT<sub>r2</sub>は負の半波を整流し極性を反転させたものを出力する。第1トランジスタT<sub>r1</sub>のドレインから出力された信号と第2トランジスタT<sub>r2</sub>のドレインから出力された信号に含まれる基本波と奇数次高調波は位相が逆相であるので相殺される。第1トランジスタT<sub>r1</sub>と第2トランジスタT<sub>r2</sub>のドレインから出力された偶数次高調波は同相であるので強めあう。よって、2倍波周波数電力を出力端子T<sub>2</sub>から取り出すことができる。

## 【0020】

ところで、寄生成分を記述しない簡略化された第1トランジスタT<sub>r1</sub>のYパラメータ（Y<sub>Source</sub>）は次のように表される。10

## 【0021】

## 【数1】

$$Y_{\text{Source}} = \begin{pmatrix} j\omega(C_{gs} + C_{dg}) & -j\omega C_{dg} \\ g_m - j\omega C_{dg} & j\omega(C_{ds} + C_{dg}) \end{pmatrix}$$

## 【0022】

第2トランジスタT<sub>r2</sub>のYパラメータ（Y<sub>Gate</sub>）は次のように表される。

## 【0023】

## 【数2】

$$Y_{\text{Gate}} = \begin{pmatrix} g_m + j\omega(C_{gs} + C_{ds}) & -j\omega C_{ds} \\ -(g_m + j\omega C_{ds}) & j\omega(C_{ds} + C_{dg}) \end{pmatrix}$$

20

## 【0024】

ここから、出力側の反射係数を表すSパラメータであるS<sub>22</sub>は次のように表される。この式では安定化抵抗R<sub>6</sub>を考慮していない。

## 【0025】

## 【数3】

$$S_{22} = \frac{1 + g_m + \omega^2(C_{gs}C_{ds} + C_{gs}C_{dg} + C_{ds}C_{dg}) + j\omega(C_{gs} - C_{dg} - g_mC_{dg})}{1 + g_m - \omega^2(C_{gs}C_{ds} + C_{gs}C_{dg} + C_{ds}C_{dg}) + j\omega(C_{gs} + C_{dg} + 2C_{ds} + g_mC_{dg})}$$

30

## 【0026】

この式は、周波数が0及びのときに|S<sub>22</sub>|=1となり、その間の周波数ではすべて1以上であることを示している。実際の素子の特性においては周波数が0及びの場合に抵抗成分などにより|S<sub>22</sub>|<1を示すが、マイクロ波帯やミリ波帯では|S<sub>22</sub>|>1となり負性抵抗を示す。このように、第2トランジスタ（ゲート接地トランジスタ）を用いた回路では負性抵抗を示す周波数帯域が存在する。その結果、周波数倍器全体においても負性抵抗が観測され、特性が不安定となる。

## 【0027】

本発明の実施の形態1の周波数倍器は、第2ゲートG<sub>2</sub>に安定化抵抗R<sub>6</sub>を接続したので、S<sub>22</sub>は次のように表される。40

## 【0028】

## 【数4】

$$S_{22} = \frac{1 + g_m + \omega^2(C_{gs}C_{ds} + C_{gs}C_{dg} + C_{ds}C_{dg}) + j\omega(C_{gs} - C_{dg} - g_mC_{dg} + R(C_{gs} + C_{dg}))}{1 + g_m - \omega^2(1+2R)(C_{gs}C_{ds} + C_{gs}C_{dg} + C_{ds}C_{dg}) + j\omega(C_{gs} + C_{dg} + 2C_{ds} + (1+2R)g_mC_{dg} + R(C_{gs} + C_{dg}))}$$

## 【0029】

安定化抵抗R<sub>6</sub>を設けることで、分母虚数項に2Rg<sub>m</sub>C<sub>dg</sub>が生じる。したがって、R（安定化抵抗R<sub>6</sub>）を適切に決定することにより|S<sub>22</sub>|が1を超えないようにすることが可能となる。これによりゲート接地トランジスタである第2トランジスタT<sub>r2</sub>が負

50

性抵抗を示さなくなり、周波数倍器を安定に動作させることが可能となる。

#### 【0030】

このように、安定化抵抗 $R_6$ の抵抗値を、出力側から見たときの反射係数である $S_{22}$ の絶対値が1を超えない値(1以下)に設定することで、第2トランジスタ $T_{r2}$ により生成される反射利得を抑制する。また、高周波信号が通過する経路上に抵抗(ダンピング抵抗)を設けないので、2倍波周波数の電力がダンピング抵抗によって消費され周波数倍器の変換利得が低下することを回避できる。

#### 【0031】

本発明の実施の形態1に係る周波数倍器は様々な変形をなし得るものである。例えば、ソース接地トランジスタ(第1トランジスタ $T_{r1}$ )とゲート接地トランジスタ(第2トランジスタ $T_{r2}$ )のゲートソース間バイアス電圧をピンチオフ電圧付近とする手段は特に限定されない。以下の実施の形態に係る周波数倍器でも同様である。なお、以下の実施の形態に係る周波数倍器は、実施の形態1との共通点が多いので実施の形態1との相違点を中心に説明する。10

#### 【0032】

実施の形態2.

図2は、本発明の実施の形態2に係る周波数倍器の回路図である。第1ゲート $G_1$ に接続された第1ゲートバイアス回路 $1_4$ は抵抗で形成されている。第1ソース $S_1$ に接続された第1ソースバイアス回路 $1_6$ は抵抗 $1_6a$ とキャパシタ $1_6b$ の並列回路で形成されている。このように構成することで、第1トランジスタ $T_{r1}$ のゲート電圧及びソース電圧を印加するために個別の電源を必要としない。20

#### 【0033】

第2ソース $S_2$ に接続された第2ソースバイアス回路 $2_4$ は抵抗で形成されている。このように構成することで、第2トランジスタ $T_{r2}$ のソース電圧を印加するために個別の電源を必要としない。

#### 【0034】

安定化抵抗 $R_6$ は一端が第2トランジスタ $T_{r2}$ のゲートに接続され、他端が接地金属に直接接続されている。この場合、安定化抵抗 $R_6$ がゲートバイアス回路の役割を果たし、ゲート電圧を印加するための個別の電源を必要としない。

#### 【0035】

これにより、第1トランジスタ $T_{r1}$ と第2トランジスタ $T_{r2}$ のドレイン端子に接続された単一の電源 $4_2$ を用いて、周波数倍器を駆動することができる。30

#### 【0036】

実施の形態3.

図3は、本発明の実施の形態3に係る周波数倍器の回路図である。安定化抵抗 $R_6$ の抵抗値 $R$ は、第2トランジスタ $T_{r2}$ の負性抵抗を抑制すると同時に、第2トランジスタ $T_{r2}$ の利得を減少させる。

#### 【0037】

そこで、安定化抵抗 $R_6$ と並列にキャパシタ $5_0$ を設けた。つまり、第2ゲート $G_2$ と接地との間にキャパシタ $5_0$ を接続することで、第2トランジスタ $T_{r2}$ の利得減少を抑制した。キャパシタ $5_0$ が入出力整合を変化させ、第2トランジスタ $T_{r2}$ の利得減少を抑制する。ただし、キャパシタ $5_0$ を設けることで安定化の作用(負性抵抗抑制効果)が低下するため、キャパシタ $5_0$ の容量は小さくする必要がある。40

#### 【0038】

実施の形態4.

図4は、本発明の実施の形態4に係る周波数倍器の回路図である。高周波信号が通過する主線路から分岐する分岐線路に第1ドレイン $D_1$ と第2ドレイン $D_2$ に電位を供給する電源 $4_2$ が設けられている。そして、電源供給回路 $4_4$ として抵抗が設けられている。つまり、分岐線路に直列に抵抗が接続されている。なお、分岐線路と主線路の接続点は接続点 $P_1$ である。50

## 【0039】

マイクロ波又はミリ波帯で用いる素子では、使用周波数に対して $1/4$ 波長の線路長の線路と、線路端を高周波で短絡するための容量を用いることが多い。このような線路は、高周波が通る経路に対する接続点から見ると開放端にみえることで、高周波特性への影響をなくしている。

## 【0040】

接続点P1から見て高周波特性への影響をなくす程度に抵抗値の高い抵抗を電源供給回路として設けると、同時に電圧降下が起きる。よって、増幅器において、電源供給回路を抵抗で形成すると効率が著しく低下する。

## 【0041】

マイクロ波を周波数倍する周波数倍器においても、電源供給回路44を抵抗で形成すると、電圧降下は発生する。しかし、周波数倍器を流れる電流値は低いため効率低下の影響はシステム全体では小さい。抵抗で形成された電源供給回路44は、 $1/4$ 波長線路よりも占有面積が非常に小さいので、周波数倍器の小型化を図ることが可能である。

## 【0042】

なお、ここまでで説明した各実施の形態に係る周波数倍器の特徴は適宜に組み合わせてもよい。

## 【符号の説明】

## 【0043】

10 入力整合回路、12 直流遮断用キャパシタ、14 第1ゲートバイアス回路、16 第1ソースバイアス回路、22 直流遮断用キャパシタ、24 第2ソースバイアス回路、26 安定化回路、30 第2ゲートバイアス回路、40 電源、42 電源供給回路、Tr1 第1トランジスタ、Tr2 第2トランジスタ、T1 入力端子、T2 出力端子

10

20

【図1】

【図3】

【図2】

【図4】

---

フロントページの続き

審査官 高 橋 徳浩

(56)参考文献 特開平03-158008(JP,A)

特開2011-166280(JP,A)

特開2001-244746(JP,A)

特開2000-196365(JP,A)

特開2007-336048(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03B11/00 - H03B29/00

H03F3/46 - H03F3/66

H03F7/00 - H03F7/06