(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-179343

(P2004-179343A)

(43) 公開日 平成16年6月24日(2004.6.24)

(51) Int.Cl.<sup>7</sup>

H01L 21/56

F 1

H01L 21/56

テーマコード(参考)

E

5 F 0 6 1

審査請求 未請求 請求項の数 8 O L (全 9 頁)

|           |                              |           |                                           |

|-----------|------------------------------|-----------|-------------------------------------------|

| (21) 出願番号 | 特願2002-342938 (P2002-342938) | (71) 出願人  | 000005832<br>松下电工株式会社<br>大阪府門真市大字門真1048番地 |

| (22) 出願日  | 平成14年11月26日 (2002.11.26)     | (74) 代理人  | 100087767<br>弁理士 西川 晃清                    |

|           |                              | (74) 代理人  | 100085604<br>弁理士 森 厚夫                     |

|           |                              | (72) 発明者  | 山中 浩<br>大阪府門真市大字門真1048番地松下電工株式会社内         |

|           |                              | (72) 発明者  | 松居 栄太郎<br>大阪府門真市大字門真1048番地松下電工株式会社内       |

|           |                              | F ターム(参考) | 5F061 AA01 BA03 CA04                      |

(54) 【発明の名称】半導体基板とその製造方法

## (57) 【要約】

【課題】封止材が少量であってもペアチップ上に所要の厚みの封止材が確保されたものとする。

【解決手段】ペアチップ2と、該ペアチップ2が表面実装される実装基板1と、実装基板1上に実装されたペアチップ2を被覆する封止材3とからなる。実装基板1はそのペアチップ2が実装されるチップ実装部10の周囲に外周ほど低くなった傾斜面12もしくは下方に伸びる壁面を備える。ペアチップ2を被覆している封止材3はその最外周縁が上記傾斜面12もしくは上記壁面上に位置している。封止材の外周縁における実質的な接触角を大きくすることができ、少量の封止材で厚みを持たせることができる。

【選択図】 図1

1 実装基板

2 ペアチップ

3 封止材

10 チップ実装部

12 傾斜面

**【特許請求の範囲】****【請求項 1】**

ベアチップと、該ベアチップが表面実装される実装基板と、実装基板上に実装されたベアチップを被覆する封止材とからなる半導体基板であり、実装基板はそのベアチップが実装されるチップ実装部の周囲に外周ほど低くなつた傾斜面もしくは下方に伸びる壁面を備えており、ベアチップを被覆している封止材はその最外周縁が上記傾斜面もしくは上記壁面上に位置していることを特徴とする半導体基板。

**【請求項 2】**

実装基板におけるチップ実装部の周囲に凹溝が形成されているとともに該凹溝の内周壁が外周ほど低くなつた傾斜面もしくは下方に伸びる壁面となっており、該傾斜面もしくは壁面上に封止材の最外周縁が位置していることを特徴とする請求項 1 記載の半導体基板。 10

**【請求項 3】**

実装基板におけるチップ実装部が実装基板に設けた凸部の上面に設けられて該凸部の周壁が外周ほど低くなつた傾斜面もしくは下方に伸びる壁面となっており、該傾斜面もしくは壁面上に封止材の最外周縁が位置していることを特徴とする請求項 1 記載の半導体基板。

**【請求項 4】**

チップ実装部と傾斜面との境界部が面取りされた面もしくは曲面となっていることを特徴とする請求項 1 ~ 3 のいずれかの項に記載の半導体基板。

**【請求項 5】**

境界部に施したメッキで曲面が形成されていることを特徴とする請求項 4 記載の半導体基板。 20

**【請求項 6】**

封止材の最高点から近い距離にある傾斜面の傾斜角度が封止材の最高点から遠い距離にある傾斜面の傾斜角度より大で急傾斜面となっていることを特徴とする請求項 1 ~ 3 のいずれかの項に記載の半導体基板。

**【請求項 7】**

ベアチップと、該ベアチップが表面実装される実装基板と、実装基板上に実装されたベアチップを被覆する封止材とからなる半導体基板の製造方法であつて、実装基板としてベアチップが実装されるチップ実装部の周囲に外周ほど低くなつた傾斜面もしくは下方に伸びる壁面を備えたものを用いて、回路パターンが表面に形成された上記実装基板の上記チップ実装部上にベアチップの表面実装を行い、次いで上記チップ実装部上に流体状態にある封止材を供給して封止材の最外周縁を上記傾斜面もしくは壁面に至らせ、この状態で封止材を硬化させることを特徴とする半導体基板の製造方法。 30

**【請求項 8】**

チップ実装部の外周に外周ほど低くなつた傾斜面もしくは下方に伸びる壁面を備えた実装基板に対し、その表面に薄膜導電層を形成し、次いでレーザによって上記薄膜導電層の回路パターンとして残すべき部分と非回路部との境界部を除去して両者を絶縁し、その後、薄膜導電層における回路パターンとして残した部分に電気メッキを施して回路パターンを形成することを特徴とする請求項 7 記載の半導体基板の製造方法。

**【発明の詳細な説明】****【0001】****【発明の属する技術分野】**

本発明はベアチップを実装基板上に実装して封止材でベアチップの封止を行つた半導体基板とその製造方法に関するものである。

**【0002】****【従来の技術】**

半導体素子や、焦電素子、圧電素子等のセンサ素子などのベアチップを実装基板上に実装し、さらに封止材でベアチップの封止を行つた半導体基板がある。このような半導体基板で高密度実装を行う場合、ベアチップや実装基板におけるチップ実装部の端子部分のピッチの縮小はもちろんのこと、特開 2001-110935 号公報などにも示されているよ 50

うに、解決すべき点は多々存在している。

【0003】

【特許文献1】

特開2001-110935号公報

【0004】

【発明が解決しようとする課題】

そして、この問題の一つとして解決しなくてはならないのがペアチップを被覆する封止材の広がりである。封止材は流体の状態にあるものをペアチップ上に供給してペアチップを封止材で被覆するとともに硬化させて封止を行うのであるが、この時、封止材が大きく広がると、ペアチップ上での封止材の高さ（厚み）を十分確保することができなくなつてペアチップの一部が封止されなくなる虞があり、これを補うには封止材が多量に必要となる。

10

【0005】

また、他のチップの実装エリアまで封止材が広がってしまうことが問題となる場合もある。

【0006】

本発明はこのような点に鑑みなされたものであつて、その目的とするところは封止材が少量であつてもペアチップ上に所要の厚みの封止材が所望の範囲内に確保されている半導体基板とその製造方法を提供するにある。

20

【0007】

【課題を解決するための手段】

しかして本発明に係る半導体基板は、ペアチップと、該ペアチップが表面実装される実装基板と、実装基板上に実装されたペアチップを被覆する封止材とからなる半導体基板であり、実装基板はそのペアチップが実装されるチップ実装部の周囲に外周ほど低くなつた傾斜面もしくは下方に伸びる壁面を備えており、ペアチップを被覆している封止材はその最外周縁が上記傾斜面もしくは上記壁面上に位置していることに特徴を有している。傾斜面もしくは下方に伸びる壁面の傾斜角度が封止材の外周縁における接触角に加わつて実質的な接触角（傾斜角度 + 接触角）を大きくすることができるために、少量の封止材で厚みを持たせることができる。

30

【0008】

この場合、実装基板におけるチップ実装部の周囲に凹溝が形成されるとともに該凹溝の内周壁が外周ほど低くなつた傾斜面もしくは下方に伸びる壁面となっており、該傾斜面もしくは壁面上に封止材の最外周縁が位置しているものであつても、実装基板におけるチップ実装部が実装基板に設けた凸部の上面に設けられて該凸部の周壁が外周ほど低くなつた傾斜面もしくは下方に伸びる壁面となっており、該傾斜面もしくは壁面上に封止材の最外周縁が位置しているものであつてもよい。

30

【0009】

また、チップ実装部と傾斜面との境界部が面取りされた面もしくは曲面となつていてもよく、この曲面は境界部に施したメッキで形成したものであつてもよい。

40

【0010】

また、封止材の最高点から近い距離にある傾斜面の傾斜角度が封止材の最高点から遠い距離にある傾斜面の傾斜角度より大で急傾斜面となつてていることも好ましい。

40

【0011】

そして本発明に係る半導体基板の製造方法は、ペアチップと、該ペアチップが表面実装される実装基板と、実装基板上に実装されたペアチップを被覆する封止材とからなる半導体基板の製造方法であつて、実装基板としてペアチップが実装されるチップ実装部の周囲に外周ほど低くなつた傾斜面もしくは下方に伸びる壁面を備えたものを用いて、回路パターンが表面に形成された上記実装基板の上記チップ実装部上にペアチップの表面実装を行い、次いで上記チップ実装部上に流体状態にある封止材を供給して封止材の最外周縁を上記傾斜面もしくは壁面に至らせ、この状態で封止材を硬化させることに特徴を有している。

50

## 【0012】

この時、チップ実装部の外周に外周ほど低くなつた傾斜面もしくは下方に伸びる壁面を備えた実装基板に対し、その表面に薄膜導電層を形成し、次いでレーザによって上記薄膜導電層の回路パターンとして残すべき部分と非回路部との境界部を除去して両者を絶縁し、その後、薄膜導電層における回路パターンとして残した部分に電気メッキを施して回路パターンを形成することも好ましい。

## 【0013】

## 【発明の実施の形態】

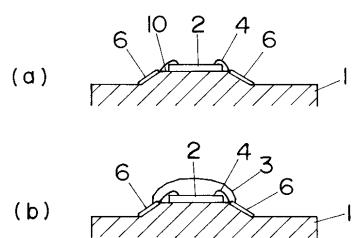

以下本発明を実施の形態の一例に基づいて詳述すると、図1及び図2は本発明に係る半導体基板を示しており、図中1は実装基板、2は実装基板1に実装された半導体素子などのペアチップであり、実装基板1上の回路パターンとはワイヤ4によるワイヤボンディングで接続されている。そしてペアチップ2とワイヤ4は封止材3によって被覆されて封止されている。

## 【0014】

ここで実装基板1におけるペアチップ2が実装されたチップ実装部10は実装基板1に設けた凸部の表面に設けられているとともに、ペアチップ2にワイヤボンディングされる実装基板1側の端子は上記凸部の表面上に設けられている。そして該凸部の側壁は、外周ほど低くなる傾斜面12として形成されており、ペアチップ1及びワイヤボンディングのワイヤ4を被覆する封止材3はその外周縁が上記傾斜面12に位置するように設けられている。

## 【0015】

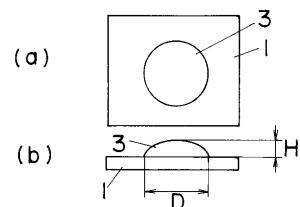

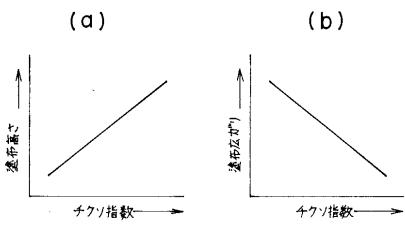

上記封止材3はたとえばエポキシ樹脂のような熱硬化性樹脂や紫外線硬化型樹脂であり、流体の状態にある封止材3を塗布して熱硬化あるいは紫外線硬化させることで封止を行うのであるが、凹凸のない平面上に封止材3を塗布した場合、封止材2は図2に示すように円形となるとともに、封止材3の塗布量が一定の場合、その塗布高さH及び塗布広がりDは、封止材3のチクソ指数によって変化する。つまり、図3に示すように、チクソ指数が大きければ塗布高さHが大きく、塗布広がりDが小さくなり、チクソ指数が小さければ塗布高さHが小さく、塗布広がりDが大きくなる。

## 【0016】

ここにおいて、ペアチップ2だけでなく、ワイヤ4も完全に覆うためには、塗布高さHを十分に確保しなくてはならないが、この場合、塗布高さHとして0.8mmを確保しようとすると、通常良く使用される樹脂を封止材3に用いた場合、そのチクソ指数が1.5程度であることから、塗布広がりDが4~5mmとなってしまう。

## 【0017】

しかし、上記塗布広がりDは塗布面が平面の場合であり、封止材3の外周縁が外周ほど低くなっている傾斜面12(傾斜角度)上に位置する場合、上記塗布広がりDを小さくすることができる。

## 【0018】

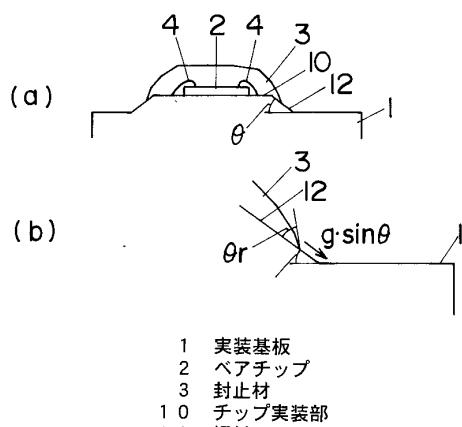

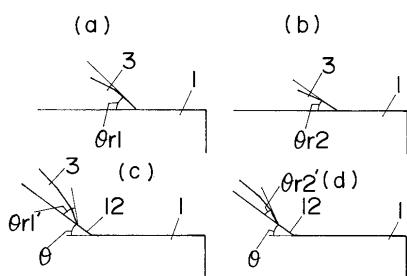

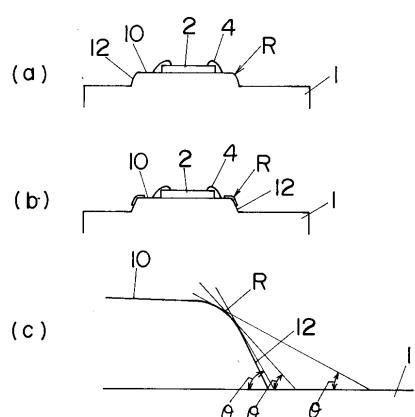

すなわち、傾斜角度が0°である平面上でたとえば図4(a)(b)に示すような接触角r1, r2を持つことになるチクソ指数を備えた封止材3は、傾斜角度の傾斜面12上では重力の傾斜面12方向成分g·sinθの影響を受けて、図4(c)(d)に示すように、接触角r1', r2'を持つとともに、これら接触角r1', r2'は上記接触角r1, r2と比較した場合、r1' < r1, r2' < r2となるが、r1' > r2である時、r1' > r2'の関係は保たれるとともに、傾斜面12の傾斜角度θを含めた実質的な接触角+r1', +r2'は、夫々+r1' > r1, +r2' > r2となり、傾斜面12上に外周縁を位置させた封止材3の平面に対する実質的な接触角(+r)が大きくなる。この結果、同じ塗布広がりDである場合、傾斜面12上に外周縁を位置させた時の方が封止材3の塗布高さHを大きくすることができるものである。なお、封止材3の外周縁の全周が傾斜面12にある必要はなく、一部は傾斜面12で囲まれたチップ実装部10上に留まっていてもよい

10

20

30

40

50

。

### 【 0 0 1 9 】

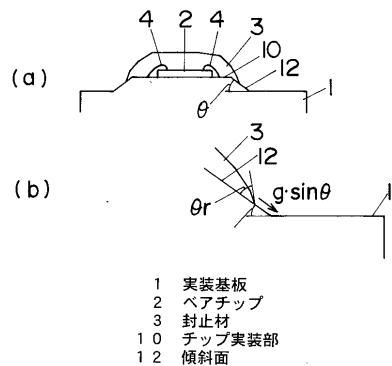

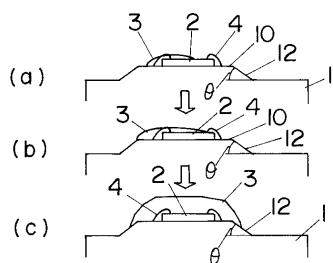

また、封止材3の外周縁が傾斜面12上に位置するということは、塗布広がり形状の制御も容易となる。つまり、封止材(樹脂)3を塗布した時、図5(a)に示すように塗布位置からもっとも近い傾斜面12に封止材3がかかると、図5(b)に示すようにその部分では上述の理由で塗布高さHに余裕ができて封止材3の流れが止まるものであり、この状態から塗布量を増やせば、他の平面部へと封止材3が流れて図5(c)に示すようにペアチップ2全体を覆う。

### 【 0 0 2 0 】

封止材3の流れがチップ実装部10を囲む傾斜面12で制御されることになるものあり 10

、封止材3の塗布量の管理が容易になる上に、近くに半田実装用のメッキパッドなどがある場合も、封止材3がそこまで流れることがなく、品質の確保にも有利である。

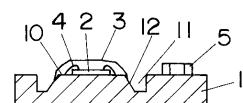

### 【 0 0 2 1 】

図6に他例を示す。これは実装基板1の表面にチップ実装部10を囲む凹溝11を形成して該凹溝11の内周壁を外周ほど低くなる傾斜面12として形成したものを見ている。この場合、ペアチップ2を実装するチップ実装部10を他の表面実装部品5が実装される実装基板1表面と同じ高さにすることができるために、実装基板1表面への回路パターンの形成にスクリーン印刷方法を適用することができ、量産性が向上する。

### 【 0 0 2 2 】

図7はチップ実装部10とその外周の傾斜面12との境界部分をなだらかな曲面Rで形成したものを示している。曲面Rに代えて、面取り面を形成してもよい。また、曲面Rは図 20

7(b)に示すように上記境界部分への電気メッキや無電解メッキによって形成してもよい。

### 【 0 0 2 3 】

境界部分に曲面Rや面取り面を設けた場合、封止材3の塗布に際して傾斜面12へと封止材3が流れる時、進行すればするほど傾斜角度nが大となるものであり、角度が急になれば封止材3の進行が止まるために封止材3の塗布高さに余裕がされることになる。

### 【 0 0 2 4 】

傾斜面12の傾斜角度が一定である場合と比較すると、封止材3が流れるほど塗布高さの余裕が増大し、塗布量の変化に対して塗布広がりの変化を抑えることができることになり 30

、塗布量の管理が更に容易となる。なお、曲面Rや面取り面のほか、傾斜面12を角度が徐々に急になる複数の傾斜面12で形成してもよいのはもちろんである。

### 【 0 0 2 5 】

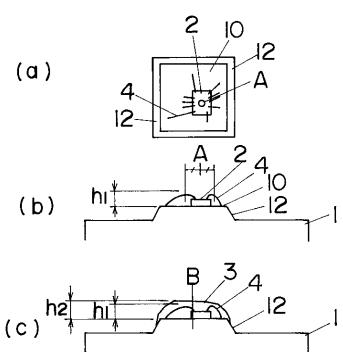

ところで図8に示すようにペアチップ2を傾斜面12で囲まれた実装部2の中央から離れたところに実装する場合も考えられるが、この時、四周の傾斜面12の各傾斜角度が同じであると、実装部の中央Bで封止材3の高さが最も高くなることから、ペアチップ2付近のA範囲において封止材3の高さh1を確保したい場合、上記中央Bでの高さh2(h2>h1)を確保しなくてならず、封止材3の樹脂量も増えてしまう。

### 【 0 0 2 6 】

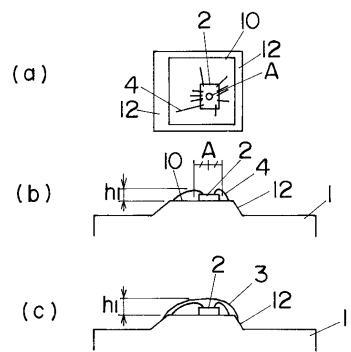

しかし、図9に示すように、チップ実装部10の周囲を囲む傾斜面12のうち、ペアチップ2に近い傾斜面12、つまり封止材3の最も高くしたい部分から近い距離にある傾斜面12の傾斜角度nを、他の遠い距離にある傾斜面12の傾斜角度fより大で急傾斜面12となるようにしておけば、チップ実装部10上を被覆する封止材3の最も高くなる部分をチップ実装部10の中央ではなくペアチップ2上に位置させることができ、この結果、封止材3の樹脂量を少なくすることができると同時に、確実な封止が可能となる。

### 【 0 0 2 7 】

また、封止材3と実装基板1との接触角rは、封止材3のチクソ指数だけでなく、封止材3に対する実装基板1の濡れ性の影響も受ける。つまり濡れ性を悪くすれば接触角rを大きくして、封止材3の高さを高くすることができる。この点から、図10に示すように、実装基板1におけるチップ実装部10を囲む傾斜面12にフッ素樹脂6を塗布したり 50

、傾斜面12の表面粗さを粗くする粗面化処理を行って封止材3との界面自由エネルギーを低くすると、好ましい結果を得ることができる。

#### 【0028】

傾斜面12の傾斜角度は、その傾斜面12を回路パターンが通るかどうかによって変更するようにしてもよい。前述したところから明らかなように、傾斜角度が大であるほうが封止材3の高さを高くする点で好ましいのであるが、この傾斜角度が大となるほど、傾斜面12への回路パターンの形成が困難となることから、回路パターンが通る傾斜面12の傾斜角度は小さくし、回路パターンが通らない傾斜面12の傾斜角度は大きくするのである。

#### 【0029】

このような半導体基板は、前述したところから明らかなように、実装基板1としてベアチップが実装されるチップ実装部10の周囲に外周ほど低くなった傾斜面12を備えたものを用いて、回路パターンが表面に形成された上記実装基板1のチップ実装部10上にベアチップ2の表面実装を行い、次いで上記チップ実装部10上に流体状態にある封止材3を供給して封止材3の最外周縁を上記傾斜面12に至らせ、この状態で封止材3を硬化させることで得ることができるが、ここで用いる実装基板1は、次の方法で製作したものをお適に用いることができる。

#### 【0030】

つまり、PPAやLCP(液晶ポリマ)などの樹脂を射出成形や圧縮成形することで、チップ実装部10の周囲に外周ほど低くなった傾斜面12を備えた実装基板1を得る。次いで、実装基板1の材料やプロセスにもよるが、実装基板1に対してたとえば150~200程度で2時間ほどのアニール処理を行う。この後、実装基板1の表面にスパッタリングなどの手法で0.1~3μm程度の厚みの銅薄膜のような薄膜導電層を形成し、次いでレーザを表面に照射することで上記薄膜導電層の回路パターンとして残すべき部分と非回路部との境界部を除去して両者を絶縁する。その後、薄膜導電層における回路パターンとして残した部分に電気メッキ(たとえば5~20μm厚の銅メッキと5~20μm厚のニッケルメッキと0.5μm厚の金メッキ)を施して回路パターンを形成する。

#### 【0031】

この場合、チップ実装部10上に設ける端子に至るまでの配線を傾斜面12に形成することが容易である。

#### 【0032】

なお、以上の各例では、チップ実装部10の周囲に外周ほど低くなった傾斜面12を設けたものを示したが、この傾斜面12に代えて、下方に伸びる壁面を形成してベアチップ2を被覆している封止材3の最外周縁が上記壁面上に位置するようにしたものでもよい。つまり、傾斜面12の傾斜角度は90°近いものであってもよい。

#### 【0033】

##### 【発明の効果】

以上のように本発明に係る半導体基板は、ベアチップと、該ベアチップが表面実装される実装基板と、実装基板上に実装されたベアチップを被覆する封止材とからなり、実装基板はそのベアチップが実装されるチップ実装部の周囲に外周ほど低くなった傾斜面もしくは下方に伸びる壁面を備え、ベアチップを被覆している封止材はその最外周縁が上記傾斜面もしくは上記壁面上に位置していることから、封止材の外周縁の実質的な接触角(傾斜面の傾斜角度+接触角)を大きくすることができるものであり、このために少量の封止材で厚みを持たせることができて、確実な封止を行うことができる。

#### 【0034】

この場合、実装基板におけるチップ実装部の周囲に凹溝が形成されているとともに該凹溝の内周壁が外周ほど低くなった傾斜面もしくは下方に伸びる壁面となっており、該傾斜面もしくは壁面上に封止材の最外周縁が位置しているものであってもよい。チップ実装部の表面を実装基板の表面と同じ高さにすることができる、製造上有利となる。

#### 【0035】

10

20

30

40

50

実装基板におけるチップ実装部が実装基板に設けた凸部の上面に設けられて該凸部の周壁が外周ほど低くなった傾斜面もしくは下方に伸びる壁面となっており、該傾斜面もしくは壁面上に封止材の最外周縁が位置しているものとしてもよい。立体的な部品配置が可能であり、小型化について有利となる。

#### 【0036】

また、チップ実装部と傾斜面との境界部が面取りされた面もしくは曲面となっていると、接触角の増大や封止材の流れの制御の点で好ましい結果を得ることができる。

#### 【0037】

この曲面は境界部に施したメッキで形成したものであると、境界部に曲面を得ることが容易となる。

10

#### 【0038】

また、封止材の最高点から近い距離にある傾斜面の傾斜角度が封止材の最高点から遠い距離にある傾斜面の傾斜角度より大で急傾斜面となっていると、封止材の最高点をチップ実装部のペアチップが位置する部分に位置させることができるとなる。

#### 【0039】

そして本発明に係る半導体基板の製造方法は、実装基板としてペアチップが実装されるチップ実装部の周囲に外周ほど低くなった傾斜面もしくは下方に伸びる壁面を備えたものを用いて、回路パターンが表面に形成された上記実装基板の上記チップ実装部上にペアチップの表面実装を行い、次いで上記チップ実装部上に流体状態にある封止材を供給して封止材の最外周縁を上記傾斜面もしくは壁面に至らせ、この状態で封止材を硬化させることから、上記特性を持つ半導体基板を容易に製造することができる。

20

#### 【0040】

この時、チップ実装部の周囲に外周ほど低くなった傾斜面もしくは下方に伸びる壁面を備えた実装基板に対し、その表面に薄膜導電層を形成し、次いでレーザによって上記薄膜導電層の回路パターンとして残すべき部分と非回路部との境界部を除去して両者を絶縁し、その後、薄膜導電層における回路パターンとして残した部分に電気メッキを施して回路パターンを形成すると、傾斜面もしくは壁面への回路パターンの形成も容易となる。

30

#### 【図面の簡単な説明】

【図1】本発明の実施の形態の一例を示すもので、(a)は断面図、(b)は部分拡大断面図である。

30

【図2】(a)は封止材の塗布時の平面図、(b)は封止材塗布時の塗布高さと塗布広がりを示す側面図である。

40

【図3】(a)は封止材のチクソ指数と塗布高さとの相関図、(b)は封止材のチクソ指数と塗布広がりとの相関図である。

【図4】(a)(b)(c)(d)は接触角に関する説明図である。

【図5】(a)(b)(c)は同上の封止材の塗布に関する説明図である。

【図6】他例の断面図である。

【図7】(a)(b)(c)は夫々更に他例の断面図である。

【図8】別の例を示すもので、(a)は平面図、(b)は断面図、(c)は封止材による封止後の断面図である。

【図9】更に別の例を示すもので、(a)は平面図、(b)は断面図、(c)は封止材による封止後の断面図である。

【図10】(a)(b)は更に別の例の断面図である。

#### 【符号の説明】

1 実装基板

2 ペアチップ

3 封止材

10 チップ実装部

12 傾斜面

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】