(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5577492号

(P5577492)

(45) 発行日 平成26年8月27日(2014.8.27)

(24) 登録日 平成26年7月18日(2014.7.18)

(51) Int.Cl.

A63F 7/02 (2006.01)

F 1

A 6 3 F 7/02 3 1 5 Z

A 6 3 F 7/02 3 2 6 Z

A 6 3 F 7/02 3 3 4

請求項の数 1 (全 22 頁)

(21) 出願番号 特願2011-157927 (P2011-157927)

(22) 出願日 平成23年7月19日 (2011.7.19)

(65) 公開番号 特開2012-40368 (P2012-40368A)

(43) 公開日 平成24年3月1日 (2012.3.1)

審査請求日 平成24年4月17日 (2012.4.17)

(31) 優先権主張番号 特願2010-165412 (P2010-165412)

(32) 優先日 平成22年7月23日 (2010.7.23)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 395018239

株式会社高尾

愛知県名古屋市中川区中京南通三丁目22

番地

(72) 発明者 有田 武

愛知県名古屋市中川区太平通1丁目3番地

株式会社高尾内

審査官 大浜 康夫

最終頁に続く

(54) 【発明の名称】遊技機

## (57) 【特許請求の範囲】

## 【請求項 1】

遊技における当否判定に用いられる第1乱数を発生させる第1乱数発生手段と、少なくとも、前記第1乱数に基づく当否判定制御を行なう主制御手段と、該主制御手段の処理に用いられるデータを不揮発的に保持可能な第1RAMと、前記主制御手段からの指令に基づき、当該遊技機の遊技者に対して価値担体を払い出す制御を行なう払出制御手段と、該払出制御手段の処理に用いられるデータを不揮発的にデータを保持可能な第2RAMと、前記第1RAMおよび前記第2RAMの保持内容をクリアする時に操作されるクリアスイッチとを備えた遊技機において、

当該遊技機に通電されると起動して、該通電された際に前記クリアスイッチが操作されていたか否かを推定する推定手段と、

該推定手段により前記クリアスイッチが操作されていたと推定された場合に、該クリアスイッチが操作されていない状態に遷移したか否かを判定し、該状態に遷移したと判定した場合に非操作信号を出力する非操作信号出力手段と、

当該遊技機に通電されると起動して、前記第1乱数とは独立した第2乱数を、時間経過と共に更新させつつ発生させる第2乱数発生手段と、

前記非操作信号出力手段により非操作信号が出力されると、前記第2乱数発生手段が発生した乱数に基づいて算出した数値を、当否判定に用いる乱数の初期値として設定する初期値設定手段と

前記推定手段により、前記クリアスイッチが操作されていたと推定されると、少なくと

10

20

も前記非操作信号出力手段により前記非操作信号が出力された後に、前記第1RAMに保持されたデータをクリアする第1RAMクリア手段と、

前記推定手段により、前記クリアスイッチが操作されていたと推定されると、前記非操作信号出力手段により前記非操作信号が出力されるのを待つことなく、前記第2RAMに保持されたデータをクリアする第2RAMクリア手段と、

前記推定手段により、前記クリアスイッチが操作されていなかったと推定されると、前記第1RAMおよび前記第2RAMに保持されたデータに基づいて当該遊技機の遊技状態を復旧する復旧手段と、

を備え、

前記推定手段は、

10

当該遊技機に通電された際に前記クリアスイッチが操作されていると、RAMクリア信号を予め定められた時間、出力するRAMクリア信号発生回路と、

該RAMクリア信号発生回路によりRAMクリア信号が出力されている場合に、当該遊技機に通電された際に前記クリアスイッチが操作されていたと判定する判定手段と

を備えたことを特徴とする遊技機。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、遊技機に関するものであり、特に、遊技状態を不揮発的に記憶し、電源を投入すると、電源断時の遊技状態を前記記憶に基づいて復旧可能に構成された遊技機に関するものである。

20

【背景技術】

【0002】

パチンコ機やパチスロ機と呼ばれる遊技機においては、内部で乱数を発生させ、始動入賞やレバー操作時に取得した乱数カウンタの値（以下単に乱数と言う）に応じて当否判定が主制御基板において行なわれている。例えばパチンコ機においては、始動入賞時に乱数を取得し、この値が予め定められた大当たり値（例えば7）であると、大当たり遊技を発生させるといったことが行なわれている。乱数カウンタは、所定の確率で大当たり値が発生するように構成されているが、狙い撃ちされないように、非周期的に大当たり値が発生するように設計されている。しかしながら、電源投入時などには、乱数カウンタに特有の初期値で乱数を生成する遊技機が多く、これでは大当たり値が発生するタイミングが初回に限り分かることになる。これを悪用して、遊技機に不正基板を取り付け、電源を遮断・再投入することにより大当たり値を狙い打つという不正行為が行なわれることがある。

30

【0003】

こうした不正行為を防止するために特許文献1では、乱数カウンタの値がパチンコ機固有の識別番号に一致するまで待機させることにより、電源投入から大当たり値が生成されるまでのタイミングをパチンコ機ごとに変化させている。

【先行技術文献】

【特許文献】

【0004】

40

【特許文献1】特開2005-040520号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、特許文献1に記載の発明においても、そのパチンコ機の識別番号が一旦特定されると、識別番号は変化しないので、その遊技機においては従来と同様に不正行為が繰り返し行なわれる可能性がある。遊技状態をRAMなどに不揮発的に記憶して、電源が遮断された後に再投入されると、電源断時の遊技状態を前記RAMなどに基づいて復旧する遊技機が多いが、こうした機種においても、RAMクリア操作を受けることにより、乱数が初期化されてしまい、前記と同様の不正行為が行なわれることがある。

50

また、RAMクリア操作が行なわれると、主制御基板の備えるRAMだけでなく、払出制御基板（パチンコ機においては、遊技球を遊技者に払い出す制御を行なう回路基板）のRAMもクリアされる。払出制御基板は、主制御基板から受信した払出指令信号に基づいて、払出装置を駆動して払出動作（パチンコ機においては、遊技球を遊技者に払い出す）を制御するものであるが、払出指令信号以外にも主制御基板から信号（例えば、払出制御基板が起動していることを確認するための信号）を受信することも考えられるので、RAMクリアを受けた払出制御基板が速やかに起動することも重要である。

本発明は係る課題に鑑みなされたものであり、遊技機の電源の入切を悪用した不正行為を防止するとともに、RAMクリア後も払出制御基板が速やかに起動可能にすることを目的とする。

10

【課題を解決するための手段】

【0006】

上記課題を解決するためになされた本発明の請求項1記載の遊技機は、遊技における当否判定に用いられる第1乱数を発生させる第1乱数発生手段と、少なくとも、前記第1乱数に基づく当否判定制御を行なう主制御手段と、該主制御手段の処理に用いられるデータを不揮発的に保持可能な第1RAMと、前記主制御手段からの指令に基づき、当該遊技機の遊技者に対して価値担体を払い出す制御を行なう払出制御手段と、該払出制御手段の処理に用いられるデータを不揮発的にデータを保持可能な第2RAMと、前記第1RAMおよび前記第2RAMの保持内容をクリアする時に操作されるクリアスイッチとを備えた遊技機において、当該遊技機に通電されると起動して、該通電された際に前記クリアスイッチが操作されていたか否かを推定する推定手段と、該推定手段により前記クリアスイッチが操作されていたと推定された場合に、該クリアスイッチが操作されていない状態に遷移したか否かを判定し、該状態に遷移したと判定した場合に非操作信号を出力する非操作信号出力手段と、当該遊技機に通電されると起動して、前記第1乱数とは独立した第2乱数を、時間経過と共に更新させつつ発生させる第2乱数発生手段と、前記非操作信号出力手段により非操作信号が出力されると、前記第2乱数発生手段が発生した乱数に基づいて算出した数値を、当否判定に用いる乱数の初期値として設定する初期値設定手段と、前記推定手段により、前記クリアスイッチが操作されていたと推定されると、少なくとも前記非操作信号出力手段により前記非操作信号が出力された後に、前記第1RAMに保持されたデータをクリアする第1RAMクリア手段と、前記推定手段により、前記クリアスイッチが操作されていたと推定されると、前記非操作信号出力手段により前記非操作信号が出力されるのを待つことなく、前記第2RAMに保持されたデータをクリアする第2RAMクリア手段と、前記推定手段により、前記クリアスイッチが操作されていなかったと推定されると、前記第1RAMおよび前記第2RAMに保持されたデータに基づいて当該遊技機の遊技状態を復旧する復旧手段と、を備え、前記推定手段は、当該遊技機に通電された際に前記クリアスイッチが操作されていると、RAMクリア信号を予め定められた時間、出力するRAMクリア信号発生回路と、該RAMクリア信号発生回路によりRAMクリア信号が出力されている場合に、当該遊技機に通電された際に前記クリアスイッチが操作されていたと判定する判定手段とを備えたことを特徴とする。

20

【0008】

30

本発明の参考例2は、参考例1の遊技機において、前記非操作信号は、前記RAMクリア信号の出力停止により実現されることを特徴とする。

40

本発明の参考例3は、請求項1、参考例1、参考例2のいずれか一に記載の遊技機において、前記非操作信号出力手段は、前記クリアスイッチが操作されていない状態に遷移したと判定してから所定時間後に前記非操作信号を出力するものであって、該所定時間は、少なくとも、当該遊技機の通電後、前記初期値設定手段が正常に稼動するまでに要する時間であることを特徴とする。

【発明の効果】

【0009】

請求項1に記載の遊技機において、RAMクリアを行なうには、遊技機が通電されてい

50

ない状態からクリアスイッチを操作し、そのまま通電させる。すると、推定手段が、「通電された際にクリアスイッチが操作されていた」と推定する。すると非操作信号出力手段が、クリアスイッチが操作されていない状態に遷移したか否かを判定し、該状態に遷移したと判定した場合に非操作信号を出力する。そして初期値設定手段が、当否判定に用いる第1乱数の初期値として、第2乱数発生手段が発生した第2乱数に基づいて算出した数値を設定する。第2乱数発生手段は、第1乱数とは独立した第2乱数を、時間経過と共に更新させつつ発生させるものである。このため、非操作信号が発生された時点に応じて第2乱数の値は変化する。この第2乱数の値に基づいて算出された値を第1乱数の初期値として設定するので、RAMクリアの都度、第1乱数は異なる値となることが期待できる。これにより、大当たり値が発生するタイミングは同じ遊技機においてもRAMクリアをする度、変わることとなり、前述のような不正行為が極めて困難となる。

また、通電された際にクリアスイッチが操作されていたか否かは、推定手段が推定するので、非通電状態においてもクリアスイッチが操作されているか否かを常時監視している必要が無い。なお、推定手段が「通電された際にクリアスイッチが操作されていなかった」と推定した場合には、復旧手段が、第1RAMおよび第2RAMに保持されたデータに基づいて当該遊技機の遊技状態を復旧するので、第1乱数の値も電源断時の値に復旧することになり、不正行為をするのはやはり困難である。

#### 【0010】

クリアスイッチが操作されていた場合は、主制御手段のデータを記憶する第1RAM、ならびに払出御装置のデータを記憶する第2RAMの双方がクリアされるが、そのタイミングが異なる。第1RAM内のデータは、非操作信号出力手段によって非操作信号が出力された後（直後とは限らない）に第1RAMクリア手段によってクリアされ、第2RAMに保持されたデータは、非操作信号が出力されるのを待たずに第2RAMクリア手段によってクリアされる。RAMがクリアされる場合、各制御手段が本来行う処理（メイン処理）は、当然、RAMクリア後でないと適切に実行できない。従って、払出制御手段においても非操作信号の出力を待ってRAMをクリアする構成に比べ、早い時点で払出制御手段が起動することが可能となる。

#### 【0011】

なお、主制御手段や払出制御手段を構成するコンピュータシステムでは、一般に起動時にセキュリティチェックを行なうが、払出制御手段は価値担体（パチンコ機ならば遊技球、回胴式遊技機ならばメダル）を払い出すという単純な作業を行なうのに対し、主制御手段は前記乱数の発生、当否判定制御、払出制御手段に対する指令の出力など様々な処理（前述していない当選後の遊技動作全般を制御するのも通常、主制御手段が行なう）を行なう。このため、これらのプログラムを格納する主制御手段のROMは、一般に払出制御手段のROMよりも大容量となり、セキュリティチェックには払出制御手段よりも時間が掛かる。主制御手段ではこのセキュリティチェックに加え、前述のように非操作信号の出力を待つので、主制御手段のメイン処理が起動した時点では、既に払出制御手段のメイン処理が起動されている可能性は極めて高い。従って、払出制御手段は主制御手段より送信されてくる信号を着実に受信することができる。

#### 【0012】

なお、第1乱数の初期値は、第1乱数として出力されうる最初の値に限らない。例えば、一般に乱数を生成するに際し用いられるシード（乱数種）と呼ばれる値も第1乱数の初期値に含まれる。また、設定される値は第2乱数の値から算出されるわけだが、この「算出」には、第2乱数の値をそのまま用いる様も含む。そのまま用いる場合の値は、元の値に0を加えたり、1倍したりしたものと解釈できるからである。また、第2乱数の値と、これに対応する第1乱数の初期値として設定すべき数値とを対応づけたテーブルを用意しておき、このテーブルを参照することも、ここでは「算出」と呼ぶこととする。この様では、テーブルを参照することにより第2乱数から算出された値を、第1乱数の初期値を設定することになる。

また、クリアスイッチに対する「操作」としては、クリアスイッチのタイプにより様々

10

20

30

40

50

な態様が考えられる。クリアスイッチがモーメンタリ動作をする押しボタンであれば、押すことが操作であり、スライドスイッチであれば、そのつまみを一方向にスライドさせることが操作であり、レバーであれば、そのレバーをいずれか一方に回動させることが操作である。なお、本発明の遊技機に対してRAMクリアを行なう操作者は、操作していたクリアスイッチの操作をやめる必要があるのだが、これは、クリアスイッチがスライドスイッチならスライドさせたつまみを元に戻す、レバーなら一方向に回動させたレバーを逆方向に回動させるという自然な動作である。特にクリアスイッチがモーメンタリ動作の押しボタンであれば、手や指をボタンから離すだけで非操作状態になるので好適である。

#### 【0013】

更に本発明の遊技機では、推定手段の構成の一例を示している。すなわち、この推定手段は、RAMクリア信号発生回路と、判定手段とを備えている。RAMクリア信号発生回路は、当該遊技機に通電された際にクリアスイッチが操作されていると、RAMクリア信号を予め定められた時間、出力する（クリアスイッチが操作されていないと、RAMクリア信号は出力されない）。判定手段は、このRAMクリア信号が出力されている場合に、「当該遊技機に通電された際にクリアスイッチが操作されていた」と判定する。

#### 【0014】

遊技機が通電されていない状態からクリアスイッチを操作し、そのまま通電させれば、RAMクリア信号発生回路が、予め定められた時間、RAMクリア信号を発生させてるので、判定手段は、このRAMクリア信号を検出することにより「遊技機が通電された際に、クリアスイッチが操作されていた」と判定することができる。RAMクリア信号発生回路は、タイマー回路や順序回路等により容易に構成できるので、遊技機の非通電状態において、クリアスイッチが操作されているか否かをソフトウェア等で常時監視したり、クリアスイッチの立ち上がり（または立ち下がり。以下、立ち上がりで代表）を検知したりする必要が無い。本発明も立ち上がり検出であるが、それは「遊技機への通電」という遊技機の動作において必然的に発生する立ち上がり信号であるため、遊技機への通電状態が遮断された状態において、クリアスイッチへの操作の有無などを検出するための通電状態を別途用意する必要は無い。

なお、「予め定められた時間」とは、判定手段がRAMクリア信号を検出するまでに要する時間よりも長い時間であればいいが、数十msなどといった具体的な値とは限らない。例えば第2乱数の値に応じて変化させても良いし、参考例1のようにしてもよい。

#### 【0015】

参考例1の遊技機では、非操作信号を、RAMクリア信号の出力停止により実現している。これに反し、非操作信号をRAMクリア信号とは別に構成しても構わないが、こうすると入力ポートなどにおいて、非操作信号のための設定が必要となる。この点、参考例1に記載の遊技機によれば、RAMクリア信号で非操作信号を兼用することになるので、RAMクリア信号さえ監視すればよい。例えば、当該遊技機に通電された際にクリアスイッチが操作されていると、RAMクリア信号をオンにし、クリアスイッチが操作されなくなるとRAMクリア信号をオフにすることが考えられる。また、クリアスイッチが操作されたことを、確実に判定手段に検知させるために、クリアスイッチが操作されなくなった時点から一定時間（例えば100ms）はRAMクリア信号をオンのままにしておいてよい。こうすれば、判定手段がRAMクリア信号を確実に検出することと、クリアスイッチが非操作状態に遷移したことをRAMクリア信号だけで検出することと、非操作状態に遷移した時点に応じて第1乱数の初期値を変化させることとを全て成立させることができる。また、参考例2のようにすることも考えられる。

#### 【0016】

参考例2の遊技機の非操作信号出力手段は、クリアスイッチが操作されていない状態に遷移したと判定してから所定時間後に非操作信号を出力するものとなっている。この所定時間は、少なくとも、当該遊技機の通電後、初期値設定手段が正常に稼動するまでに要する時間となっている。

これに反し、クリアスイッチが操作されている状態から操作されていない状態に遷移す

10

20

30

40

50

ると直ちに非操作信号が出力されるように構成すると、第2乱数発生手段が発生した第2乱数に基づいて、当否判定に用いる第1乱数の初期値を初期値設定手段が設定しようとしても、初期値設定手段自体が正常に稼動していない可能性がある。なぜなら、操作者が通電とクリアスイッチに対する非操作をほぼ同時に行なう可能性があるからである。こうした場合には、非操作信号が出力されても、その際には通電後、間ないので、初期値設定手段が正常に動作せず、初期値が適切に設定されない恐れがある。

【0017】

この点、参考例2の遊技機では、たとえクリアスイッチが操作されていない状態に遷移しても、初期値設定手段が正常に稼動するまでに要する時間が経過するまでは非操作信号が出力されない。従って、非操作信号が検出されたときには、初期値設定手段は正常に稼動しているので、確実に初期値の設定を行なうことができる。なお、「当該遊技機の通電後、初期値設定手段が正常に稼動するまでに要する時間」とは、通電してから初期値設定手段が正常に稼動するまでに要する時間の全体を指しているのではない。前述のように、遊技機に通電すると、クリアスイッチが操作されているか否かを判定したり、その操作が停止されたか否かを判定したり等、様々な処理（前述したものに限らない）が初期値設定手段の稼動前に行なわれる。こうした様々な処理に要する時間は、「通電してから初期値設定手段が正常に稼動するまでに要する時間の全体」から差し引いてよい。

10

【図面の簡単な説明】

【0018】

【図1】本発明に係る遊技機の正面図

20

【図2】遊技機の遊技盤の正面図

【図3】遊技機の裏面図

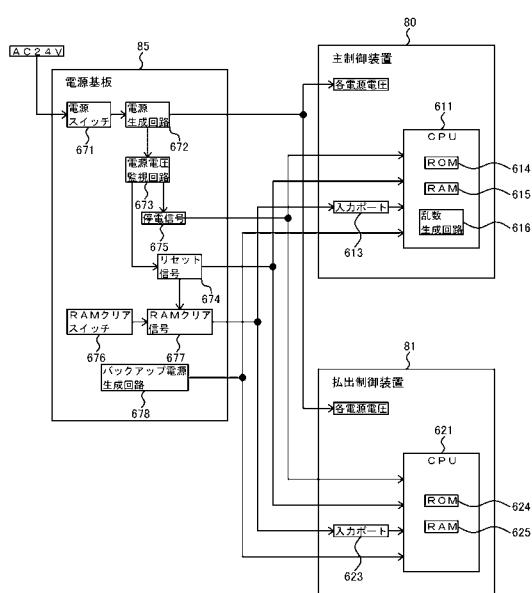

【図4】遊技機の電気プロック図

【図5】遊技機の要部の詳細電気構成を示すブロック図

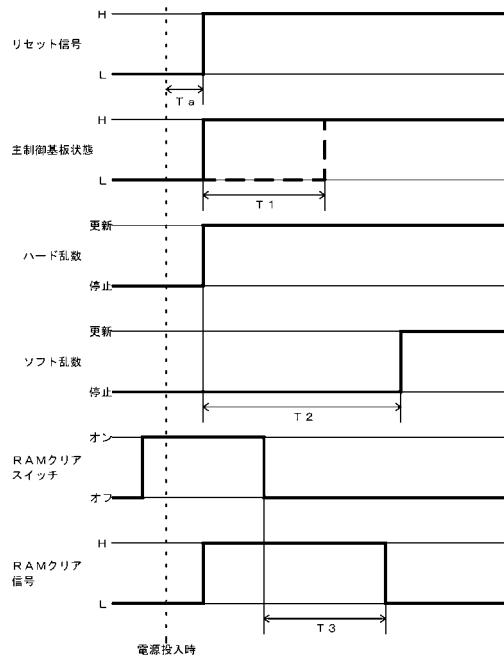

【図6】遊技機の動作を示すタイミングチャート

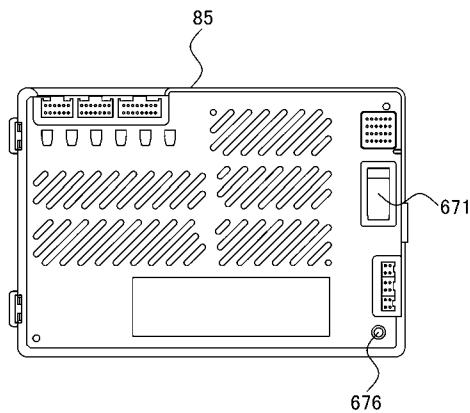

【図7】遊技機の電源基板の正面図

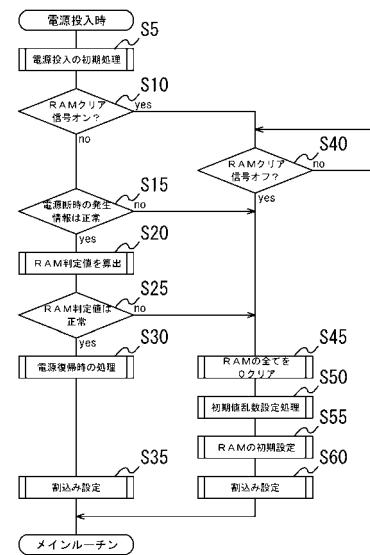

【図8】遊技機を構成する主制御装置のCPUが電源投入時に実行する処理のフローチャート

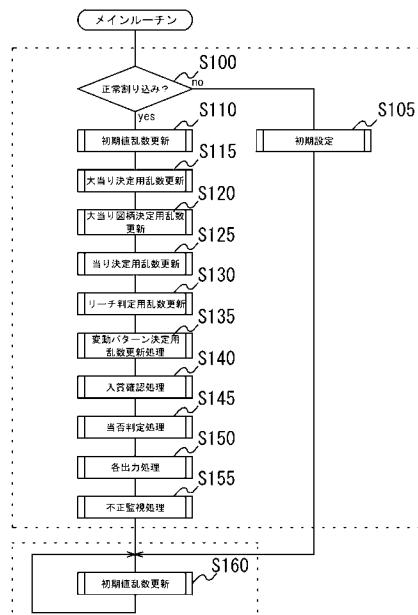

【図9】主制御装置のCPUが実行するメイン処理のフローチャート

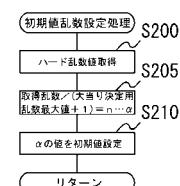

【図10】主制御装置のCPUが実行する初期値乱数設定処理のフローチャート

30

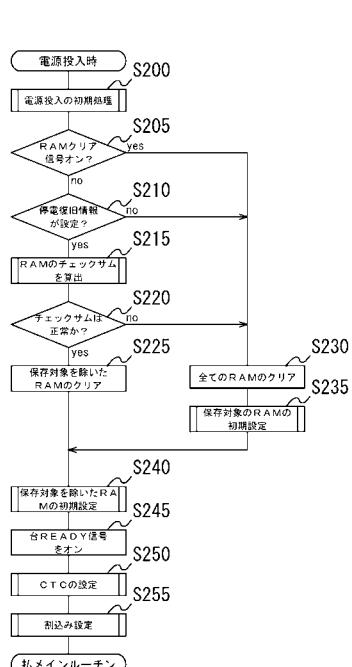

【図11】遊技機が備える払出制御装置のCPUが電源投入時に実行する処理のフローチャート

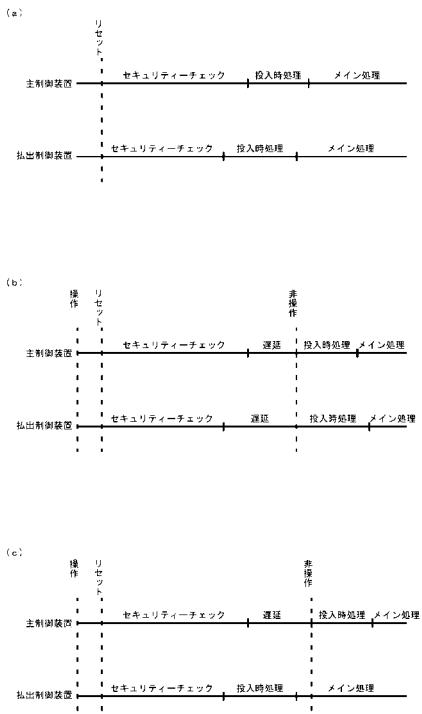

【図12】(a)が従来の主制御装置と払出制御装置にてRAMクリアを行なう際にそれぞれ行なわれる処理の概略を示すタイムチャート、(b)がRAMクリアを行なう際に主制御装置および払出制御装置の双方にてRAMクリア信号がオフとなるのを待つ場合の処理の概略を示すタイムチャート、(c)がRAMクリアを行なう際に主制御装置のみRAMクリア信号がオフとなるのを待つ場合の処理の概略を示すタイムチャート

【発明を実施するための形態】

【0019】

以下に本発明の好適な実施形態について説明する。尚、本発明の実施の形態は下記の実施例に何ら限定されるものではなく、本発明の技術的範囲に属する種々の形態を探ることができ、各実施例に記載された内容を適宜組み合わせることが可能なことはいうまでもない。

40

[実施例1]

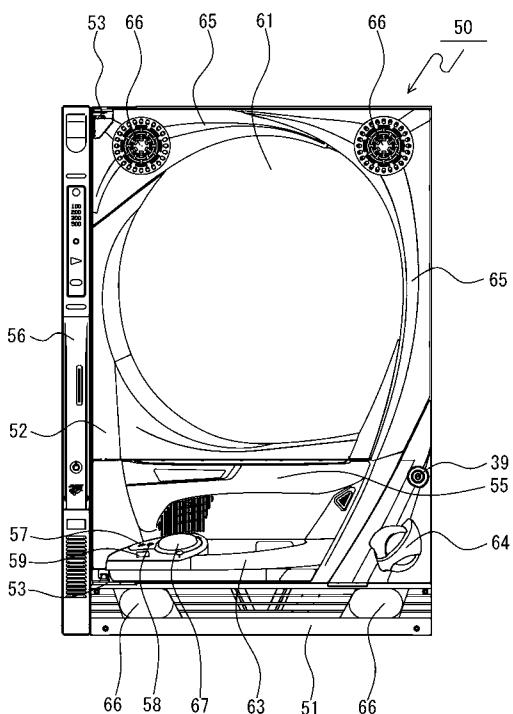

【0020】

図1に示すように、弾球遊技機の一種であるパチンコ機50は、縦長の固定外郭保持枠をなす外枠51にて構成の各部を保持する構造である。外枠51の左側上下には、ヒンジ53が設けられており、該ヒンジ53の他方側には図3に記載する内枠70が取り付けられており、内枠70は外枠51に対して開閉可能な構成になっている。前枠52には、板ガラス61が取り外し自在に設けられており、板ガラス61の奥には図2に記載する遊技

50

盤1が内枠70に取り付けられている。

【0021】

前枠52の上側左右及び外枠51の下側左右には、スピーカ66が設けられており、パチンコ機50から発生する遊技音が出力され、遊技者の趣向性を向上させる。また、遊技者の趣向性を向上させるために前枠52に遊技状態に応じて発光する枠側装飾ランプ65も複数設けられている。前枠52の下方には、上皿55と下皿63が一体に形成されている。下皿63の右側には発射ハンドル64が取り付けられており、該発射ハンドル64を時計回りに回動操作することによって発射装置(図示省略)が稼働して、上皿55から供給された遊技球が遊技盤1に向けて発射される。

【0022】

10

下皿63の左側には、遊技者が操作可能な演出ボタン67が備えられており、遊技者が所定期間中に、該演出ボタン67を操作することで後述する演出図柄表示装置6に表示される内容が変化したり、スピーカ66より出力される遊技音が変化したりする。また、このパチンコ機50はいわゆるCR機であって、プリペイドカードの読み書き等を行うためのプリペイドカードユニット(CRユニット)56が付属しており、パチンコ機50には、貸出ボタン57、精算ボタン58及び残高表示器59を有するCR精算表示装置が備わっている。

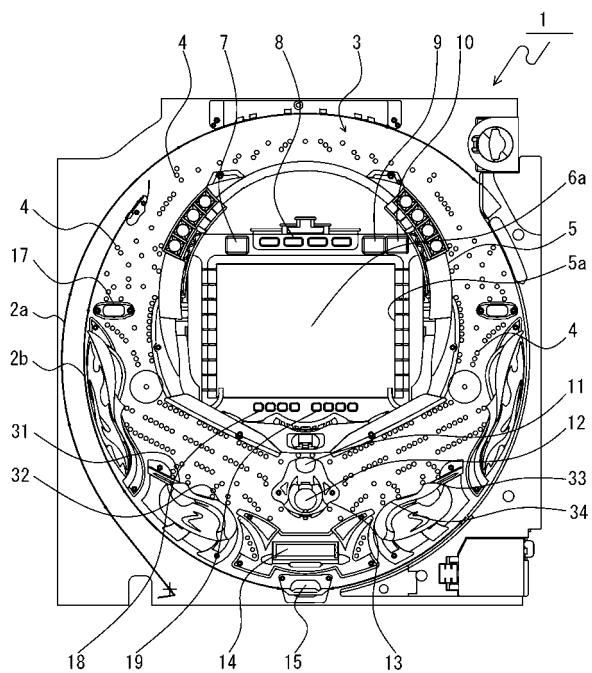

【0023】

図2は、本実施例のパチンコ機50の遊技盤1の正面図である。なお、このパチンコ機50の全体的な構成は公知技術に従っているので図示及び説明は省略する。図2に示すように遊技盤1には、公知のガイドレール2a、2bによって囲まれた略円形の遊技領域3が設けられている。この遊技領域3には多数の遊技釘4が打ち付けられている。

20

【0024】

遊技領域3のほぼ中央部には、センタークース5が配されている。センタークース5は、公知のものと同様に、ワープ入口、ワープ通路、ステージ、演出図柄表示装置6(液晶表示装置であり擬似図柄を表示する。)の画面6aを臨ませる窓5a等を備えている。

窓5aの上側にはドットマトリクスの普通図柄表示装置7及び7セグメントの第1特別図柄表示装置9と第2特別図柄表示装置10と4個のLEDからなる普通図柄保留記憶表示装置8が設置され、下側には第1特別図柄保留記憶表示装置18と第2特別図柄保留表示装置19が設置されている。

30

センタークース5の向かって左横には普通図柄作動ゲート17が配置されている。センタークース5の下方には、第1始動口11と第2始動口12とがユニット化された複合入賞装置13が配置されている。

【0025】

第1始動口11は、いわゆるチャッカーであり、常時入球可能である。

第2始動口12は電動チューリップであり、周知の電動チューリップと同様に開閉変化するが、上方に第1始動口11があるために図示の閉鎖状態では遊技球を入球させることができない。しかし、遊技球が普通図柄作動ゲート17を通過すると行われる普通図柄抽選で当り、普通図柄表示装置7に当りの普通図柄が確定表示されると、第2始動口12は開放されて入球容易になる。

40

【0026】

複合入賞装置13の下方にはアタッカー式の大入賞口14が配置され、その下方にはアウト穴15が設けられている。また、複合入賞装置13の左側には第1左入賞口31と第2左入賞口32が、右側には第1右入賞口33と第2右入賞口34がガイドレール2bに沿うように設けられている。なお、この第1左入賞口31、第2左入賞口32、第1右入賞口33、第2右入賞口34が、常時、入球率が変化しない普通入賞口である。

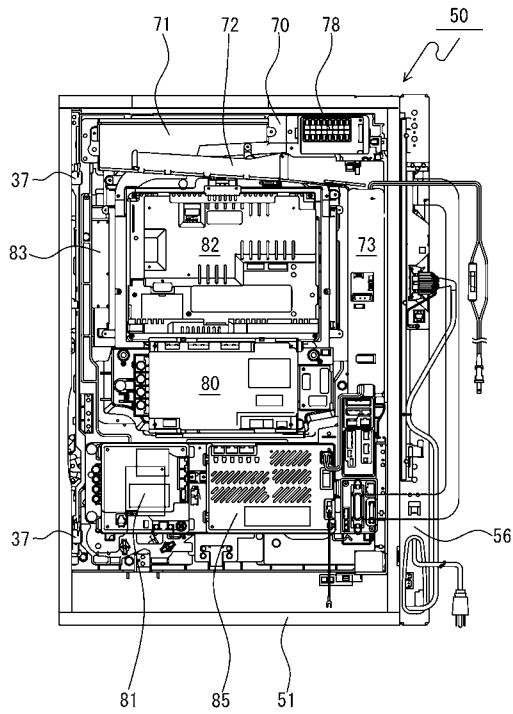

【0027】

パチンコ機50の裏面は図3に示すとおり、前述した遊技盤1を脱着可能に取り付ける内枠70が前述した外枠51に収納されている。この内枠70には、上方から、球タンク71、タンクレール72及び払出装置73が設けられている。この構成により、遊技盤1

50

上の入賞口に遊技球の入賞があれば球タンク 7 1 からタンクレール 7 2 を介して所定個数の遊技球を払出装置 7 3 により前述した上皿 5 5 に排出することができる。また、パチンコ機 5 0 の裏側には、主制御装置 8 0 、払出制御装置 8 1 、演出図柄制御装置 8 2 、サブ統合制御装置 8 3 、発射制御装置 8 4 、電源基板 8 5 が設けられている。なお、演出図柄制御装置 8 2 、サブ統合制御装置 8 3 がサブ制御装置に該当する。

#### 【 0 0 2 8 】

主制御装置 8 0 、演出図柄制御装置 8 2 、サブ統合制御装置 8 3 は遊技盤 1 に設けられており、払出制御装置 8 1 、発射制御装置 8 4 、電源基板 8 5 が内枠 7 0 に設けられている。なお、図 3 では、発射制御装置 8 4 が描かれていないが、発射制御装置 8 4 は払出制御装置 8 1 の下に設けられている。また、球タンク 7 1 の右側には、外部接続端子 7 8 が設けられており、この外部接続端子 7 8 より、遊技状態や遊技結果を示す信号が図示しないホールコンピュータに送られる。なお、従来はホールコンピュータへ信号を送信するための外部接続端子 7 8 には、盤用（遊技盤側から出力される信号をホールコンピュータへ出力するための端子）と枠用（枠側（前枠 5 2 、内枠 7 0 、外枠 5 1 ）から出力される信号をホールコンピュータへ出力するための端子）の 2 種類を用いているが、本実施例では、一つの外部接続端子 7 8 を介してホールコンピュータへ遊技状態や遊技結果を示す信号を送信している。

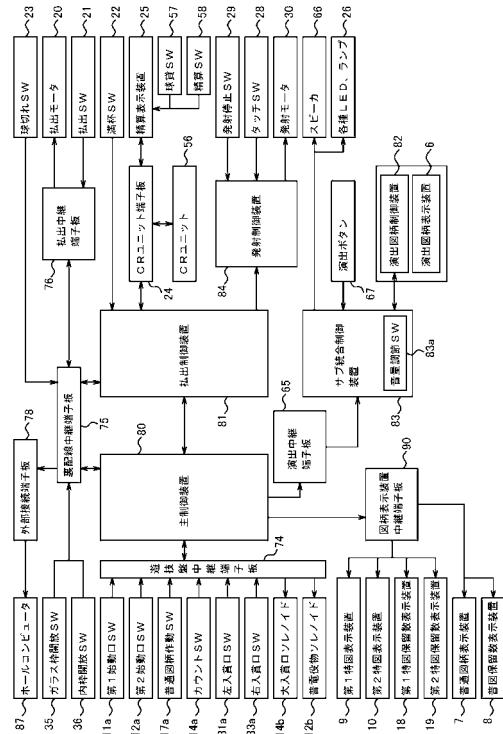

#### 【 0 0 2 9 】

このパチンコ機 5 0 の電気的構成は、図 4 のブロック図に示すとおり、主制御装置 8 0 を中心にして構成されている。なお、このブロック図には、単に信号を中継するだけのためのいわゆる中継基板及び電源回路等は記載していない。また、詳細の図示は省略するが、主制御装置 8 0 、払出制御装置 8 1 、演出図柄制御装置 8 2 、サブ統合制御装置 8 3 のいずれも C P U 、 R O M 、 R A M 、入力ポート、出力ポート等を備えているが、本実施例では発射制御装置 8 4 には C P U 、 R O M 、 R A M は設けられていない。しかし、これに限るわけではなく、発射制御装置 8 4 に C P U 、 R O M 、 R A M 等を設けてもよい。

#### 【 0 0 3 0 】

主制御装置 8 0 には、第 1 始動口 1 1 に入球した遊技球を検出する第 1 始動口スイッチ 1 1 a 、第 2 始動口 1 2 に入球した遊技球を検出する第 2 始動口スイッチ 1 2 a 、普通図柄作動ゲート 1 7 に進入した遊技球を検出する普通図柄作動スイッチ 1 7 a 、大入賞口 1 4 に入球した遊技球を計数するためのカウントスイッチ 1 4 a 、第 1 左入賞口 3 1 、第 2 左入賞口 3 2 に入球した遊技球を検出する左入賞口スイッチ 3 1 a 、第 1 右入賞口 3 3 、第 2 右入賞口 3 4 に入球した遊技球を検出する右入賞口スイッチ 3 3 a 等の検出信号が入力される。

#### 【 0 0 3 1 】

主制御装置 8 0 は搭載しているプログラムに従って動作して、上述の検出信号などに基づいて遊技の進行に関わる各種のコマンドを生成して払出制御装置 8 1 及びサブ統合制御装置 8 3 に出力する。

また主制御装置 8 0 は、図柄表示装置中継端子板 9 0 を介して接続されている第 1 特別図柄表示装置 9 、第 2 特別図柄表示装置 1 0 及び普通図柄表示装置 7 の表示、第 1 特別図柄保留記憶表示装置 1 8 、第 2 特別図柄保留数表示装置 1 9 及び普通図柄保留記憶表示装置 8 の点灯を制御する。

#### 【 0 0 3 2 】

更に、主制御装置 8 0 は、大入賞口ソレノイド 1 4 b を制御することで大入賞口 1 4 の開閉を制御し、普通電動役物ソレノイド（図 4 では普電役物ソレノイドと表記） 1 2 b を制御することで第 2 始動口 1 2 の開閉を制御する。

主制御装置 8 0 からの出力信号は試験信号端子にも出力される他、図柄変動や大当たり等の管理用の信号が外部接続端子 7 8 に出力されてホールメインコンピュータに送られる。主制御装置 8 0 と払出制御装置 8 1 とは双方向通信が可能である。

#### 【 0 0 3 3 】

払出制御装置 8 1 は、主制御装置 8 0 から送られてくるコマンドに応じて払出モータ 2

10

20

30

40

50

0を稼働させて賞球を払い出させる。本実施例においては、賞球として払い出される遊技球を計数するための払出センサ21の検出信号は払出制御装置81に入力され、払出制御装置81で賞球の計数が行われる構成を用いる。この他にも主制御装置80と払出制御装置81に払出センサ21の検出信号が入力され、主制御装置80と払出制御装置81の双方で賞球の計数を行う構成を用いることも考えられる。

【0034】

なお、払出制御装置81はガラス枠開放スイッチ35、内枠開放スイッチ36、満杯スイッチ22、球切れスイッチ23からの信号が入力され、満杯スイッチ22により下皿63が満タンであることを示す信号が入力された場合及び球切れスイッチ23により球タンクに遊技球が少ないあるいは無いことを示す信号が入力されると払出モータ20を停止させ、賞球の払出動作を停止させる。なお、満杯スイッチ22、球切れスイッチ23も、その状態が解消されるまで信号を出力し続ける構成になっており、払出制御装置81は、その信号が出力されなくなることに起因して払出モータ20の駆動を再開させる。

10

【0035】

また、払出制御装置81は遊技球等貸出装置接続端子24を介してプリペイドカードユニットと交信することで払出モータ20を作動させ、貸し球を排出する。払出された貸し球は払出センサ21に検出され、検出信号は払出制御装置81に入力される。なお、遊技球等貸出装置接続端子24は精算表示基板25とも双方向通信可能に接続されており、精算表示基板25には、遊技球の貸出しを要求するための球貸ボタン、精算を要求するための返却ボタン、残高表示器が接続されている。

20

【0036】

また、払出制御装置81は、外部接続端子78を介して賞球に関する情報、枠（内枠、前枠）の開閉状態を示す情報などをホールコンピュータに送信するほか、発射制御装置84に対して発射停止信号を送信する。

なお本実施例では遊技球を払い出す構成であるが、入賞等に応じて発生した遊技球を払い出さずに記憶する封入式の構成にしても良い。

【0037】

発射制御装置84は発射モータ30を制御して、遊技球を遊技領域3に遊技球を発射させる。なお、発射制御装置84には払出制御装置81以外に発射ハンドルからの回動量信号、タッチスイッチ28からのタッチ信号、発射停止スイッチ29から発射停止信号が入力される。

30

回動量信号は、遊技者が発射ハンドルを操作することで出力され、タッチ信号は遊技者が発射ハンドルを触ることで出力され、発射停止スイッチ信号は、遊技者が発射停止スイッチ29を押すことで出力される。なお、タッチ信号が発射制御装置84に入力されなければ、遊技球は発射できないほか、発射停止スイッチ信号が入力されているときには、遊技者が発射ハンドルを触っていても遊技球は発射できないようになっている。

【0038】

サブ統合制御装置83はサブ制御装置に該当し、主制御装置80から送信されてくるデータ及びコマンドを受信し、それらを演出表示制御用、音制御用及びランプ制御用のデータに振り分けて、演出表示制御用のコマンド等は演出図柄制御装置82に送信し、音制御用及びランプ制御用は自身に含まれている各制御部位（音声制御装置及びランプ制御装置としての機能部）に分配する。そして、音声制御装置としての機能部は、音声制御用のデータに基づいて音L S Iを作動させることによってスピーカからの音声出力を制御し、ランプ制御装置としての機能部はランプ制御用のデータに基づいてランプドライバを作動させることによって各種L E D、ランプ26を制御する。また、サブ統合制御装置83には、演出ボタン67が接続されており、遊技者が演出ボタン67を操作した際には、その信号がサブ統合制御装置83に入力される。

40

【0039】

サブ統合制御装置83と演出図柄制御装置82とは双方向通信が可能である。

演出図柄制御装置82は、サブ統合制御装置83から受信したデータ及びコマンド（共

50

に主制御装置 8 0 から送信されてきたものとサブ統合制御装置 8 3 が生成したものとがある)に基づいて演出図柄表示装置 6 を制御して、擬似図柄等の演出画像を画面 6 a に表示させる。

#### 【 0 0 4 0 】

図 5 に電源基板 8 5 と、主制御装置 8 0 、払出制御装置 8 1 を含む遊技機各部との間の給電および信号系を示す。各パチンコ遊技機の電源基板 8 5 は、パチンコ店側に設けられた A C 2 4 V 電源を電源スイッチ 6 7 1 を介して電源生成回路 6 7 2 が受けており、電源生成回路 6 7 2 が、図示の主制御装置 8 1 、払出制御装置 8 1 を含む遊技機各部に給電する。電源スイッチ 6 7 1 はオンまたはオフの操作をするとその状態を保持するタイプが用いられる。

10

#### 【 0 0 4 1 】

電源生成回路 6 7 2 における全波 2 4 V 出力は電源電圧監視回路 6 7 3 に入力し、電源電圧監視回路 6 7 3 による全波 2 4 V 出力の有無の検出結果に基づいてリセット信号発生回路 6 7 4 がリセット信号を出力もしくは解除する。すなわち、電源電圧監視回路 6 7 3 は所定の基準電圧以上の非出力状態が所定の時間、維持すれば全波 2 4 V 出力停止と判断し、リセット信号発生回路 6 7 4 は全波 2 4 V 出力停止との判断に応じてリセット信号を出力する。一方、全波 2 4 V 出力が開始されるとリセット信号は解除される。ここで、リセット信号の出力とはロウレベルの信号を出力することであり、解除とはロウレベルからハイレベルに変化することをいう。なお、リセット信号の解除は、全波 2 4 V 出力の検出時点から遅延時間  $T_a$  の後なされる。

20

#### 【 0 0 4 2 】

リセット信号発生回路 6 7 4 の出力は主制御装置 8 1 、払出制御装置 8 1 それぞれの C P U 6 1 1 、 6 2 1 のリセット端子に出力される。

#### 【 0 0 4 3 】

電源電圧監視回路 6 7 3 の出力を入力として停電信号発生回路 6 7 5 が設けてあり、停電等の電源遮断時に停電信号を各制御装置 C P U 6 1 1 、 6 2 1 の N M I 端子に出力するようになっている。停電信号は電源遮断に伴ってハイレベルからロウレベルに変化する信号であり、リセット信号が出力するに先立って出力するように出力タイミングが設定されている。

#### 【 0 0 4 4 】

30

また、電源基板 8 5 は、コンデンサを含み構成されたバックアップ電源生成回路 6 7 8 により D C 5 V のバックアップ電源 ( V B B ) を生成する構成となっており、バックアップ電源 ( V B B ) 出力は各制御基板 C P U 6 1 1 、 6 2 1 のバックアップ端子 ( V B B ) に出力され、停電時には後述するように各制御装置 C P U 6 1 1 、 6 2 1 の R A M の記憶内容を保持する。

#### 【 0 0 4 5 】

電源基板 8 5 はまた、 R A M クリアスイッチ 6 7 6 を備えている。 R A M クリアスイッチ 6 7 6 は C P U 6 1 1 、 6 2 1 の各 R A M 6 1 5 , 6 2 5 に記憶されている内容をクリアするために設けられる。

#### 【 0 0 4 6 】

40

R A M クリアスイッチ 6 7 6 には押下時のみオンする押し鈕タイプのものが用いられ、上記リセット信号の解除時に R A M クリアスイッチ 6 7 6 がオンであれば、 R A M クリア信号発生回路 6 7 7 が、ハイレベルの信号である R A M クリア信号を主制御装置 8 0 、払出制御装置 8 1 それぞれの入力ポート 6 1 3 、 6 2 3 に所定時間 ( 後述 ) の間、出力する。すなわち、 R A M クリア信号はリセット信号が解除される電源投入時のみ出力される。ここで電源スイッチ 6 7 1 のオンからリセット信号解除までの遅延時間  $T_a$  は例えば 1 0 0 m s に設定され、 R A M クリア信号を発生せしめるには R A M クリアスイッチ 6 7 6 を押下しながら電源スイッチ 6 7 1 をオンすることになる。なお、各制御装置 C P U 6 1 1 、 6 2 1 は入力ポート 6 1 3 、 6 2 3 における R A M クリア信号の有無をデータバスを介して監視する。

50

## 【0047】

図6にRAMクリアスイッチ676を押下しながら電源スイッチ671をオンし電源基板85から給電を開始した時の電源基板85、および主制御装置80の各部の作動状態を示す。

## 【0048】

電源スイッチ671のオン（電源投入時）から時間Ta経過後にリセット信号が解除され、このリセット信号解除が有効になると、主制御装置CPU611がセキュリティーチェックを開始する。図示はされていないが、払出制御装置81のCPU621もリセット信号解除が有効になった時点からセキュリティーチェックを行なう。セキュリティーチェック時間T1はCPUの種類、システムクロック周波数等にもよるが、本具体例において主制御装置CPU611では185msとした。なお、セキュリティーチェックとは、周知のごとくワンチップマイコンである各CPU611、621等が遊技の進行内容を書き込んだROMの内容が正規の内容であるか否かをチェックすることである。

10

## 【0049】

パチンコ機50においては、主制御装置CPU611のセキュリティーチェック時間T1は、払出制御装置CPU621のセキュリティーチェックに要する時間より長く掛かる。このため、主制御装置CPU611のセキュリティーチェック完了時には払出制御装置CPU621はセキュリティーチェックが完了し、主制御装置CPU611がROMに書き込まれたプログラムにしたがって遊技の制御を開始する時には、払出制御装置CPU621は既に遊技の制御を実行している。この結果、電源投入後、主制御装置CPU611が直ちに払出制御装置CPU621にデータを送信しても、払出制御装置CPU621はセキュリティーチェックを終え自身の制御を実行しているので確実にデータを受信することができる。

20

## 【0050】

一方、RAMクリアスイッチ676を押しながら電源スイッチ671をオンしているので、リセット信号が解除された時点から所定時間の間、RAMクリア信号が出力されることになる。この「所定時間」は、リセット信号が解除された時点からRAMクリアスイッチ676が押されるのが停止（一般には、操作者がRAMクリアスイッチ676から手を離すことにより実現）されるまでの時間に、T3を加えた時間である。ここで、T3とは、電源投入時にRAMクリアスイッチ676が押されていた場合に、主制御装置CPU611のセキュリティーチェックが終了して、後述する電源投入時の処理を開始する（正確には同処理のS10（図8参照）を実行する）時点で、主制御装置CPU611がRAMクリア信号を確実に検知するために確保された時間である。一般に、操作者が電源スイッチ671をオンしてからRAMクリアスイッチ676から手を離すまでの時間は、主制御装置CPU611のセキュリティーチェックに要する時間よりも十分長いと考えられるが、操作者が性急にRAMクリアスイッチ676から手を離した場合を考慮して、主制御装置CPU611のセキュリティーチェックに要する185msよりも長い時間である300msをT3としている。これは、RAMクリア信号発生回路677が、RAMクリアスイッチ676が押されるのが停止されるのを検知すると、そこから更にT3の後にRAMクリア信号を停止することにより実現される。これにより、RAMクリア信号が停止される時点は、操作者がRAMクリアスイッチ676から手を離した時点に対応して変化する。

30

## 【0051】

また、電源スイッチ671、RAMクリアスイッチ676は、図7に示すように、いずれも電源基板85の一方の面に固定されており、電源基板85は、これらスイッチ671、676固定面側から樹脂を成形した箱状のカバーにより覆われている。電源スイッチ671およびRAMクリアスイッチ676はカバーから露出されて互いに近接配置されている。このため、カバーを外すことなく、片手で両スイッチ671、676を同時に操作可能となっている。

40

## 【0052】

50

電源投入時に主制御装置 80 の C P U 611 により実行される処理について図 8 を用いて説明する。電源スイッチ 671 が操作されてパチンコ機 50 が通電状態になり、リセット信号が解除され、C P U 611 自身のセキュリティーチェックが終了すると、本処理が起動され、電源投入の初期処理を実行する (S5)。そして R A M クリア信号がオンか否かを判定する (S10)。R A M クリア信号は、上述したように、リセット信号の解除時に R A M クリアスイッチ 676 がオン状態であれば H (オン) になるものなので、これは実質的に、電源投入時に R A M クリアスイッチ 676 がオン状態だったか否かを判定していることになる。

#### 【0053】

R A M クリア信号がオンではなかったとき (S10 : n o) は、主制御装置 80 を電源断時の状態に復旧する。そのためには、電源断時の発生情報が正常か否かを判定し (S15)、正常であれば (S15 : y e s)、R A M の判定値を算出し (S20)、その判定値が正常か否かを判定する (S25)。ここで R A M の判定値とは、電源断時に R A M に保存された値で、S25 では、S20 で算出された値と、R A M に保存された値が一致するか否かを判定する。判定値が正常、すなわち判定値が保存された値と一致していれば (S25 : y e s)、電源復帰時の処理 (例えば、電源断時の発生情報をクリアしたり、サブ統合制御装置 83 を電源断時の遊技状態に復帰させるためのコマンドを送信したりする) を行なう (S30)。そして割り込み設定を行い (S35)、メインルーチンに移行する。

#### 【0054】

R A M クリア信号がオンだったとき (S10 : y e s) は、主制御装置 80 を初期状態に戻す。そのためには、S40 の無限ループにて R A M クリア信号がオフになるのを待つ。オフになったら R A M の全てを 0 クリアし (S45)、初期値乱数設定処理を実行する (S50)。こうして初期値乱数設定処理が終了すると R A M の初期設定を行い (S55)、割り込み設定を行い (S60)、メインルーチンに移行する。

#### 【0055】

初期値乱数設定処理を図 10 に示す。本処理が起動すると、まずハード乱数を取得する (S200)。ハード乱数とは、主制御装置 80 の C P U 611 が備える乱数生成回路 616 (図 5 参照) により発生される乱数値である。乱数生成回路 616 は、C P U 611 の通電と略同時に起動 (図 6 も参照) し、0 ~ 65535 の値を、1 周期内では重複なく一定の規則 (例えば 0 1 2 . . . 65535 0 . . .) で更新し生成する。なお、C P U 611 の乱数生成回路 616 の周期は 50 ms となっている。電源投入から初期値乱数設定処理 (S50) を実行するまでの時間は、S40 の無限ループを何回繰り返すかによって変化する。この繰り返し回数は、R A M クリアスイッチ 676 を押しながら電源スイッチ 671 をオンにしてから、R A M クリアスイッチ 676 を押すのをやめるまでの時間 (以下、操作時間という) によって決まる事になる。これ以外の要因としては、温度変化などによる C P U 611 の動作クロックの周期変化も考えられるが、操作時間のばらつきの方が圧倒的に大きいので、操作時間が支配的となる。操作時間は上記操作の都度、変化すると考えられるので、初期値乱数設定処理でソフト乱数の初期値として設定される値は毎回異なると期待できる。

#### 【0056】

こうして取得したハード乱数を、大当たり決定用乱数の最大値 + 1 で割った余り (とすると) を算出する (S205)。パチンコ機 50 では大当たり決定用乱数の最大値は 349 となっており (後述)、S205 では 349 + 1、すなわち 350 でハード乱数の取得値を割ることになる。例えば S200 で取得したハード乱数が 65000 だった場合、350 で割ると商が 185、余りが 250 となるので、= 250 である。S210 では、このをソフト乱数の初期値として設定し、終了 (図 8 の処理にリターン) する。

#### 【0057】

メインルーチンを図 9 に従って説明する。なお、図 8 ではメインルーチンを、電源投入時の処理に引き続き実行される処理であるかのように示したが、実際にはメインルーチン

10

20

30

40

50

は、S35またはS60までの処理を実行した後、約2ms毎のハード割り込みにより繰り返し実行される。本実施形態では、当該メインルーチンが1回起動されるごとにS100～S155までの1回だけ実行される処理を「本処理」と称し、この本処理を実行して余った時間内に時間の許す限り繰り返し実行されるS160の処理を「残余処理」と称する。「本処理」は上記割り込みにより定期的に実行されることになる。

#### 【0058】

マイコンによるハード割り込みが実行されると、まず正常割り込みであるか否かが判断される(S100)。この判断処理は、メモリとしてのRAMの所定領域の値が所定値であるか否かを判断することにより行われ、マイコンにより実行される処理が本処理に移行したとき、通常の処理を実行して良いのか否かを判断するためのものである。正常割り込みでない場合としては、電源投入時又はノイズ等によるマイコンの暴走等が考えられるが、マイコンの暴走は近年の技術の向上によりほとんど無いものと考えて良いので、たいていが電源投入時である。電源投入時にはRAMの所定領域の値が所定値と異なる値となっている。

10

#### 【0059】

正常割り込みでないと判断されると(S100:n0)、初期設定(例えば前記メモリの所定領域への所定値を書き込み、特別図柄及び普通図柄を初期図柄とする等のメモリの作業領域への各初期値の書き込み等)が為され(S105)、残余処理(S160)に移行する。

#### 【0060】

20

正常割り込みとの肯定判断がなされると(S100:yess)、初期値乱数更新処理が実行される(S110)。この処理は、初期値乱数の値についてこの処理を実行する毎に+1するインクリメント処理であり、この処理実行前の初期値乱数の値に+1するが、この処理を実行する前の乱数値が最大値である「349」のときには次回の処理で初めの値である「0」に戻り、「0」～「349」までの350個の整数を繰り返し昇順に作成する。

#### 【0061】

S110に続く大当たり決定用乱数更新処理(S115)は、初期値乱数更新処理と同様に処理を実行する毎に+1するインクリメント処理であり、最大値である「349」のときは次回の処理で初めの値である「0」に戻り、「0」～「349」までの350個の整数を繰り返し昇順に作成する。なお、大当たり決定用乱数の最初の値は、初期値乱数設定処理で設定された値となる。前述の例では、=250であったから、大当たり決定用乱数は「250」「251」「252」…「349」「0」「1」…と更新されていく。

30

#### 【0062】

なお、大当たり決定用乱数が1巡(350回、更新されること)すると、そのときの前記初期値乱数の値を大当たり決定用乱数の初期値にし、大当たり決定用乱数は、その初期値から+1するインクリメント処理を行う。そして、再び大当たり決定用乱数が1巡すると、その時の初期値乱数の値を大当たり決定用乱数の初期値にする動作を行なう。つまり、この一連の動作を繰り返し続けることになる。前述の例では大当たり決定用乱数が「249」になると1巡であるから、「249」の次は前記初期値乱数の値となる。仮に初期値乱数の値が「87」だったとすると、「249」「87」「88」…「349」「0」「1」…「86」と変化していき、「86」の次は新たな前記初期値乱数の値となる。

40

大当たり図柄決定用乱数更新処理(S120)は「0」～「9」の10個の整数を繰り返し作成するカウンタとして構成され、本処理毎に+1され最大値を超えると初めの値である「0」に戻る。

#### 【0063】

S120に続く当たり決定用乱数更新処理(S125)は、「0」～「5」の6個の整数を繰り返し作成するカウンタとして構成され、本処理毎に+1され最大値を超えると初めの値である「0」に戻る。なお、当選することとなる値の数は通常確率状態時、高確率状

50

態時ともに 3 であり、値は「0」、「3」、「5」である。なお、この当り決定用乱数更新処理は普通図柄の抽選に使用し、その他の初期値乱数、大当たり決定用乱数、大当たり図柄決定用乱数、リーチ判定用乱数、変動パターン決定用乱数は特別図柄の抽選に使用する。

#### 【0064】

リーチ判定用乱数更新処理 (S130) は、「0」～「228」の 229 個の整数を繰り返し作成するカウンタとして構成され、本処理毎で +1 され最大値を超えると初めの値である「0」に戻る。なお、通常確率状態時で変動時間短縮機能未作動時に当選する値の数は 21 で、値は「0」～「20」であり、通常確率状態時で変動時間短縮機能作動時に当選する値の数は 5 で、値は「0」～「4」であり、高確率状態時に当選する値の数は 6 で、値は「0」～「5」である。 10

#### 【0065】

変動パターン決定用乱数更新処理 (S135) は、「0」～「1020」の 1021 個の整数を繰り返し作成するカウンタとして構成され、本処理毎で +1 され最大値を超えると初めの値である「0」に戻る。なお、大当たり決定用乱数、大当たり図柄決定用乱数、当たり決定用乱数、リーチ判定用乱数、変動パターン決定用乱数を、前述のハード乱数に対してソフト乱数と呼ぶ (図 6 も参照)。

#### 【0066】

続く入賞確認処理 (S140) では、第 1 始動口 11、第 2 始動口 12 の入賞の確認及びパチンコ機 50 に設けられ主制御装置 80 に接続された各スイッチ類の入力処理が実行される。 20

本実施例では、遊技球が第 1 始動口 11、第 2 始動口 12 に入賞すると大当たり決定用乱数、大当たり図柄決定用乱数、変動パターン決定用乱数、リーチ判定用乱数など複数の乱数を取得されるのだが、保留記憶できる数を第 1 始動口 11 と第 2 始動口 12 それぞれ 4 個までとしており、第 1 保留記憶が満タンである 4 個のときに遊技球が第 1 始動口 11 に入賞又は第 2 保留記憶が満タンである 4 個のときに遊技球が第 2 始動口 12 に入賞しても賞球が払出されるだけで、前記複数の乱数は保留記憶されない構成になっている。

#### 【0067】

続いて、大当たりか否かを判定する条件成立判定手段としての当否判定処理 (S145) を行う。この当否判定処理 (S145) が終了すると、続いて画像出力処理等の各出力処理 (S150) が実行される。 30

#### 【0068】

各出力処理 (S150) では、遊技の進行に応じて主制御装置 80 は演出図柄制御装置 82、払出し制御装置 81、発射制御装置 84、サブ統合制御装置 83、大入賞口ソレノイド 14b 等に対して各々出力処理を実行する。即ち、入賞確認処理 (S140) により遊技盤 1 上の各入賞口に遊技球の入賞があることが検知されたときには賞球としての遊技球を払い出すべく払出し制御装置 81 に賞球データを出力する処理を、遊技状態に対応したサウンドデータをサブ統合制御装置 83 に出力する処理を、パチンコ機 50 に異常があるときにはエラー中であることを報知すべく演出図柄制御装置 82 にエラー信号を出力する処理を各々実行する。 40

#### 【0069】

続く不正監視処理 (S155) は、普通入賞口 (第 1 左入賞口 31、第 2 左入賞口 32、第 1 右入賞口 33、第 2 右入賞口 34) に対する不正が行われていないか監視する処理であり、所定時間内における入賞口への遊技球の入球が予め決定された規定数よりも多いか否かを判断して、多かった場合には不正と判断され、その旨を報知する処理である。つまり、不正判断手段は、主制御装置 80 に設けている。

#### 【0070】

本処理に続く前述の残余処理は、初期値乱数更新処理 (S160) から構成されるが、前述した S110 と全く同じ処理である。この処理は無限ループを形成し、次の割り込みが実行されるまで時間の許される限り繰り返し実行される。前述した S100～S155 50

までの本処理を実行するのに必要とされる時間は、大当たり処理を実行するか否か、特別図柄の表示態様の相違等により割り込み毎に異なる。この結果、残余処理を実行する回数も割り込み毎に異なり、図9に示された割り込み処理が1回実行されることにより初期値乱数に更新される値も一律ではなくなる。これにより、初期値乱数が大当たり決定用乱数と同期する可能性は極めて小さくなる。大当たり決定用乱数が1巡したときの、初期値乱数の値(0~349の350通り)が、同程度に発生するとすれば、同期する確率はわずか1/350である。また、前述した当たり決定用乱数更新処理(S125)も残余処理内において実行するよう構成しても良い。

#### 【0071】

電源投入時に払出制御装置81のCPU621により実行される処理について図11を用いて説明する。電源スイッチ671が操作されてパチンコ機50が通電状態になり、リセット信号が解除され、CPU621自身のセキュリティーチェックが終了すると、本処理が起動され、電源投入の初期処理を実行する(S200)。そしてRAMクリア信号がオンか否かを判定する(S205)。上述したように、これは実質的に、電源投入時にRAMクリアスイッチ676がオン状態だったか否かを判定していることになる。

10

#### 【0072】

RAMクリア信号がオンではなかったとき(S205: no)は、払出制御装置81を電源断時の状態に復旧する。そのためにまず、停電復旧情報が設定されているか否かを判定し(S210)、設定されていれば(S210: yes)、現在のRAMに記録されているデータのチェックサムを算出し(S215)、その値が電源断時に同様に算出したチェックサムと一致している(チェックサムが正常)か否かを判定する(S220)。保存したチェックサムと一致していれば(S220: yes)、保存対象を除いた部分のRAM領域をクリアする(S225)。そしてクリアした領域に初期値を書き込み(S240)、台READY信号をオンし(S245)、CTCを設定する(S250)。ここで台READY信号とは、CRユニット56に払い出し動作が可能であることを伝達する信号である。CTCとは、払出制御装置81で行なうタイマ割込みの割込み周期を設定するもので、CTCの設定が終了すると、割込み設定を行い(S255)、払出制御装置81のメインルーチン(図示省略)に移行する。

20

#### 【0073】

RAMクリア信号がオンだったとき(S205: yes)は、払出制御装置81を初期状態に戻す。そのためにまず、RAMの全てを0クリアし(S230)、保存の対象のRAMの初期設定(S235)を行なってからS240に移行する。

30

つまり、図8に示した主制御装置80における電源投入時処理では、RAMクリア信号がオンだった場合に、再びそのRAMクリア信号がオフになるのをS40(図8)の無限ループを実行することにより待ったが、図11に示す払出制御装置81における電源投入時処理では、RAMクリア信号がオンだったときに、RAMクリア信号がオフになるのを待たずにすぐに全てのRAMをクリアする。

#### 【0074】

この結果、主制御装置80と払出制御装置81の電源投入時の処理の実行タイミングは図12のようになる。図12(a)が通常の電源投入の場合のタイムチャート、図12(b)がRAMクリアを行なう際に主制御装置および払出制御装置の双方にてRAMクリア信号がオフとなるのを待つ場合のタイムチャート、図12(c)がRAMクリアを行なう際に主制御装置のみRAMクリア信号がオフとなるのを待つ場合のタイムチャートである。

40

通常の電源オンでは、図12(a)に示すように、主制御装置80、払出制御装置81とも電源が投入されるとそれぞれセキュリティーチェックを行い、引き続き電源投入時の処理を行い、各制御装置80, 81本来の処理(メイン処理)を行なう。主制御装置80のCPU611は払出制御装置81のCPU621よりもクロック周波数が高い等の理由で高性能のものが用いられるが、主制御装置80のROM614が払出制御装置81のROM624よりも容量が大きいため、セキュリティーチェックに時間が掛かる。これによ

50

り払出制御装置 81 の投入時処理の方が主制御装置 80 の投入時処理よりも早く開始され、且つ早く終了する。この結果、主制御装置 80 がメイン処理を開始したときには、既に払出制御装置 81 は自身のメイン処理を開始した状態となっており、払出制御装置 81 は主制御装置 80 から送信されるコマンドを取りこぼすことなく処理を行なうことが可能にされている。

#### 【 0 0 7 5 】

一方、RAMクリアを行なった際には、図12(b)に示すように、主制御装置 80 は、セキュリティーチェックの後、RAMクリア信号がオンの間、無限ループ(図8のS4)を行なう分だけ処理が遅延する。そしてRAMクリア信号がオフ(RAMクリアスイッチ676から手を離す。図12では「非操作」と記載)となると、電源投入時の処理を開始し、主制御装置 80 本来の処理(メイン処理)を行なう。このとき、払出制御装置 81 も同様に、RAMクリア信号がオフとなるのを待つと、主制御装置 80 と略同時に電源投入時の処理を行なうことになるため、主制御装置 80 がメイン処理を行なう時点では、払出制御装置 81 が本来の処理(メイン処理)を開始していない可能性が生じる。これでは、払出制御装置 81 は主制御装置 80 から送信されるコマンドを取りこぼす恐れがある。

この点、本発明の払出制御装置 81 のRAMクリアを行なった際には、図8のS40に相当する処理が無いので、セキュリティーチェックが終了すると、図12(c)に示すように、直ちに電源投入時の処理を開始し、払出制御装置 81 のメイン処理を行なう。この結果、主制御装置 80 がメイン処理を行なう際には、既に払出制御装置 81 はメイン処理を開始していることとなり、払出制御装置 81 は主制御装置 80 から送信されるコマンドを取りこぼすことなく処理を行なうことができる。

#### 【 0 0 7 6 】

以上のように構成されたパチンコ機 50 によれば、たとえRAMクリアスイッチ676を押しながら電源スイッチ671をオンにしても、RAMクリアスイッチ676を押すのをやめた際(より正確には、RAMクリアスイッチ676を押すのをやめてからT3後。更に正確には、この時間T3が経過し、RAMクリア信号がオフになったことを主制御装置CPU611が検知(図8のS40参照)して、更にRAMの全てを0クリア(図8のS45参照)した後)のハード乱数の値に基づいて、大当たり決定用乱数の初期値が決定される。TaやT3の値はRAMクリアの操作ごとにほぼ一定であるが、リセット信号が解除されてからRAMクリアスイッチ676がオフになる(操作者がRAMクリアスイッチ676を押すのをやめる)までの時間は毎回異なる。このため、ハード乱数の値が、以前と同じハード乱数の値になることは殆ど無く、大当たり決定用乱数の初期値もRAMクリア操作を行なうごとに異なると期待することができる。従って、RAMクリア操作を行なうことにより大当たりを狙うという不正行為が極めて困難になる。

#### 【 0 0 7 7 】

ハード乱数は、50msで0~65535の値を一巡するという極めて高速な更新を行なうため、操作者が、電源スイッチ671のオン操作と同時にRAMクリアスイッチ676から手を離す癖を持っていたとしても、同じ値になることは殆ど無い。なお、操作者が電源スイッチ671のオン操作よりも先にRAMクリアスイッチ676から手を離してしまった場合は、S10でnoと判定されてパチンコ機50の復旧動作が始まるので、RAMクリアを利用した不正行為が行なわれる心配は無い。RAMクリアが必須ならば、そのパチンコ機50の通電を再び遮断し(例えば電源スイッチ671をオフにし)、RAMクリア操作を行なえばよい。

#### 【 0 0 7 8 】

また、払出制御装置 81 のRAMクリアについては、RAMクリアスイッチ676がオフになるのを待たずに(つまりT3の経過も待つことなく)、ROM624のセキュリティーチェックが終わるとRAM625をクリアして、電源投入時処理を行なう。従って、主制御装置 80 のメイン処理が起動した時点では、払出制御装置 81 のメイン処理は既に起動されており、払出制御装置 81 は主制御装置 80 より送信されてくる指令を着実に受信することができる。

10

20

30

40

50

## 【0079】

ここで本実施例の構成と、本発明の構成要件との対応関係を示す。S110～S115の処理が本発明の「第1乱数発生手段」に相当し、主制御装置80のCPU611が本発明の「主制御手段」に相当し、主制御装置80のRAM615が本発明の「第1RAM」に相当し、払出制御装置81のCPU621が本発明の「払出制御手段」に相当し、払出制御装置81のRAM625が本発明の「第2RAM」に相当し、RAMクリアスイッチ676が本発明の「クリアスイッチ」に相当し、S10の処理が本発明の「判定手段」に相当（S10の処理およびRAMクリア信号発生回路677が本発明の「推定手段」に相当）し、乱数生成回路616が本発明の「第2乱数発生手段」に相当し、S50の処理が本発明の「初期値設定手段」に相当し、S40の処理を経て行なうS45の処理が本発明の「第1RAMクリア手段」に相当し、S230の処理が本発明の「第2RAMクリア手段」に相当し、S30の処理が本発明の「復旧手段」に相当する。なお、RAMクリア信号発生回路677は本発明の「非操作信号出力手段」にも相当する。10

## 【0080】

## [他の実施例]

上記実施例では、ハード乱数を用いて大当たり決定用乱数の初期値を決定していたが、これに替えてハード乱数で初期値乱数の初期値を決定しても良い。こうすると、ハード乱数の値が初期値乱数に影響を与えるので、1巡目だけではなく、2巡目以降の大当たり決定乱数にも影響を与えることになる。この場合、1巡目の大当たり決定用乱数の初期値は、初期値乱数の値とするとよい。また、ハード乱数の値を大当たり乱数の初期値に設定する際の算出を、S205で行なった演算以外の方法にて行なってもよい。例えば、第2乱数の値と、これに対応する第1乱数の初期値として設定すべき数値とを対応づけたテーブルを予め用意しておき、このテーブルを参照することにより第1乱数の初期値を設定してもよい。ただしこうすると、第1乱数の初期値として設定し得る数（前記実施例では350通り）だけテーブルのデータも用意する必要があり、このテーブルを格納するためのROM等が容量を圧迫する可能性がある。この点、前記実施例では、ハード乱数の値を大当たり決定用乱数の最大値+1で割った際の余りを算出しているので、記憶容量が少なくて済む。なお、この算出を行なう際には、ハード乱数の値を大当たり決定用乱数の最大値+1で実際に除算してもよいが、ハード乱数の値から大当たり決定用乱数の最大値+1を繰り返し減算し、算出値がマイナスになったら大当たり決定用乱数の最大値+1を加えることにより算出してもよい。20

RAMクリアにより0クリアされるのは、CPU611のRAM615及びCPU621のRAM625であったが、それ以外の箇所にある不揮発性のRAM（例えば主制御装置61にあるが、CPU611の外部に設けられた不揮発性のRAMや、他の図示しない基板に設けられた不揮発性のRAM）やRAM以外の記憶媒体の記憶内容をクリアしてもよい。

## 【0081】

リセット信号は、リセット信号発生回路674から直接、主制御装置80および払出制御装置81に入力していたが、所定の遅延回路を介して双方もしくは一方に入力するよう構成してもよい。40

また、上記実施例ではいずれも信号をハイアクティブとして構成したが、一部（または全て）の信号をローアクティブとして構成し直しても構わない。例えば、RAMクリア信号をローアクティブとし、RAMクリアを行なう時点を、RAMクリア信号の立ち上がりを待って行なうように構成してもよい。

## 【0082】

また、上記実施例では、RAMクリア信号を、電源スイッチ671をオンにした際にRAMクリアスイッチ676がオンになっていたか否かの判定と、RAMクリアスイッチ676がオフになったか否かの判定との、双方に用いていたが、それぞれ別の信号を用いて判定するようにしても良い。例えば、RAMクリア信号は、上記と同様、リセット信号の解除時にRAMクリアスイッチ676がオンであれば、RAMクリア信号発生回路67750

が発生させるものとし、これとは別に、このRAMクリア信号がハイの状態において、RAMクリアスイッチ676がオフになると、T3の後に所定の信号を発生し、CPU611がこの信号を検出するとRAMの全てを0クリアしてハード乱数を取得するように構成してもよい。

また、前記実施例では、電源スイッチ671およびRAMクリアスイッチ676を、電源基板85に設けていたが、別の箇所（例えば主制御装置61や派出制御装置62など）に双方または一方を設けてもよい。

## 【符号の説明】

【 0 0 8 3 】

## 8.0 主制御装置

10

## 8.1 扱出制御装置

## 8.5 電源基板

## 671 電源スイッチ

## 6 7 4 リセット信号

## 676 RAMクリアスイッチ

【 义 1 】

【 図 2 】

【図3】

【 図 4 】

【 図 5 】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【 図 1 2 】

---

フロントページの続き

(56)参考文献 特開2008-183432(JP,A)

特開2011-245154(JP,A)

特開2011-177394(JP,A)

特開2011-143058(JP,A)

特開2010-005117(JP,A)

特開2010-240124(JP,A)

特開2010-184159(JP,A)

特開2008-200227(JP,A)

特開2003-325925(JP,A)

特開2006-612(JP,A)

(58)調査した分野(Int.Cl., DB名)

A 63 F 7 / 02