(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2010-232335

(P2010-232335A)

(43) 公開日 平成22年10月14日(2010.10.14)

(51) Int.Cl. F 1 テーマコード (参考)

|                    |                  |            |      |

|--------------------|------------------|------------|------|

| <b>H01L 29/739</b> | <b>(2006.01)</b> | H01L 29/78 | 655G |

| <b>H01L 29/78</b>  | <b>(2006.01)</b> | H01L 29/78 | 653A |

| <b>H01L 29/06</b>  | <b>(2006.01)</b> | H01L 29/78 | 652P |

|                    |                  | H01L 29/78 | 652C |

|                    |                  | H01L 29/78 | 652H |

審査請求 未請求 請求項の数 6 O L (全 11 頁) 最終頁に続く

|           |                            |          |                                              |

|-----------|----------------------------|----------|----------------------------------------------|

| (21) 出願番号 | 特願2009-77063 (P2009-77063) | (71) 出願人 | 000001889<br>三洋電機株式会社<br>大阪府守口市京阪本通2丁目5番5号   |

| (22) 出願日  | 平成21年3月26日 (2009.3.26)     | (71) 出願人 | 506227884<br>三洋半導体株式会社<br>群馬県邑楽郡大泉町坂田一丁目1番1号 |

|           |                            | (74) 代理人 | 100131071<br>弁理士 ▲角▼谷 浩                      |

|           |                            | (72) 発明者 | 米田 秀司<br>群馬県邑楽郡大泉町坂田一丁目1番1号<br>三洋半導体株式会社内    |

|           |                            | (72) 発明者 | 澤村 慶治<br>群馬県邑楽郡大泉町坂田一丁目1番1号<br>三洋半導体株式会社内    |

(54) 【発明の名称】絶縁ゲートバイポーラトランジスタ

## (57) 【要約】

## 【課題】

正孔の蓄積効果を高めつつ、電流密度の低下を抑制するIGBTを提供する。

## 【解決手段】

絶縁ゲート間ににおいて、ドリフト領域は複数に分離して形成される。そして、ドリフト領域間においては、エミッタ電極とドリフト層間に層間絶縁膜が形成される。

## 【選択図】図1

**【特許請求の範囲】****【請求項 1】**

第1導電型のドリフト層と、

前記ドリフト層の一主面側において、第1方向に延在する形状であつて前記第1方向と直行する第2方向に並行して配列されるように形成された絶縁ゲートと、

一対の前記絶縁ゲートに挟まれたゲート間領域に形成された第2導電型のベース領域と、

前記ベース領域において前記絶縁ゲートと隣接して形成された第1導電型のエミッタ領域と、

前記エミッタ領域と接続されたエミッタ電極と、

前記ドリフト層の他主面側に形成された第2導電型のコレクタ層と、

前記コレクタ層と接続されたコレクタ電極と、を含んで構成され、

前記ベース領域は、前記第1方向に沿つて前記ドリフト層により複数に分離されており、

前記ドリフト層と前記エミッタ電極とは絶縁されていること、を特徴とする絶縁ゲートバイポーラトランジスタ。

**【請求項 2】**

請求項1に記載の絶縁ゲートバイポーラトレンジスタであつて、

前記絶縁ゲートは、前記ドリフト層の一主面から前記ベース領域よりも深くなるように形成されたトレンチ内に形成されていること、を特徴とする絶縁ゲートバイポーラトレンジスタ。

**【請求項 3】**

請求項2に記載の絶縁ゲートバイポーラトレンジスタであつて、

前記ドリフト層と前記エミッタ電極とは、層間絶縁膜によって絶縁されていること、を特徴とする絶縁ゲートバイポーラトレンジスタ。

**【請求項 4】**

請求項3に記載の絶縁ゲートバイポーラトレンジスタであつて、

前記エミッタ領域と前記ドリフト層とは、前記ベース領域を介して分離されていること、を特徴とする絶縁ゲートバイポーラトレンジスタ。

**【請求項 5】**

請求項4に記載の絶縁ゲートバイポーラトレンジスタであつて、

前記ベース領域と前記ドリフト層との間には、第1導電型の不純物濃度が前記ドリフト層よりも大きい高濃度拡散領域が形成されていること、を特徴とする絶縁ゲートバイポーラトレンジスタ。

**【請求項 6】**

請求項5に記載の絶縁ゲートバイポーラトレンジスタであつて、

一の前記ゲート間領域とこれに隣接する他の前記ゲート間領域とでは、前記第2方向において前記ドリフト領域がずれるように配列されていること、を特徴とする絶縁ゲートバイポーラトレンジスタ。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、絶縁ゲートバイポーラトランジスタに関する。

**【背景技術】****【0002】**

IGBT (Insulated-Gate Bipolar Transistor) は、パワーエレクトニクス分野におけるスイッチング素子として用いられている。

**【0003】**

IGBTは、PT (Punch Through) 構造とNPT (Non Punch Through) 構造とに大別される。

10

20

30

40

50

## 【0004】

P T 構造は、コレクタ層として半導体基板が用いられ、これにバッファ層、ドリフト層が順次エピタキシャル成長されたものである。ドリフト層は、高耐圧が要求されると、それに応じた厚さが必要となる。そうすると、ドリフト層のエピタキシャル成長によるコストが増大してしまう。

## 【0005】

これに対して、N P T 構造では、ドリフト層は、F Z ( F l o a t Z o n i n g ) ウエハが研磨されて形成される。これにより、高耐圧が要求されても、製造コストの増大が抑制される。

## 【0006】

ところが、N P T 構造では、コレクタ層は、P + 型の不純物が低ドーズ量でドリフト層に注入されることにより形成される。このため、N P T 構造は、P T 構造と比較すると、コレクタ層からドリフト層に注入される正孔の量が数桁低くなる。この場合、正孔がエミッタ電極から排出される量を無視できない。

10

## 【0007】

これを解決すべく、従来においても、正孔の排出を抑制する試みがなされてきた。例えば、特許文献1では、隣接するトレンチ間の第1領域ではエミッタ領域とエミッタ電極とを接続させることで当該領域をメインセルとする一方、隣接するトレンチ間であって第1領域と異なる第2領域ではエミッタ領域とエミッタ電極との間に層間絶縁膜を形成することで当該領域をダミーセルとする構成が開示されている。正孔はIGBTがオンの状態においてコレクタ側からベース層に注入されるわけであるが、このような構成によってメインセルの面積が減少するため、正孔がメインセルを通じてエミッタ側へ排出されにくくなる。

20

## 【先行技術文献】

## 【特許文献】

## 【0008】

## 【特許文献1】特開平8-167716号公報

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0009】

30

上述のように、特許文献1に係る発明では、メインセルの面積比率を積極的に減少させることにより、正孔のエミッタ側への排出量を抑制して正孔の蓄積量を保ち、ベース層の伝導度変調を促進することができる。

## 【0010】

しかし、当該従来技術では、メインセルの面積比率が減少するため、電流密度が低下してしまう。

## 【0011】

本発明は、上記課題を解決するためになされたものであって、その目的は、IGBTにおいて、電流密度の低下を抑制しつつ、正孔の蓄積効果を高めることである。

40

## 【課題を解決するための手段】

## 【0012】

上記目的を達成するため、本発明の絶縁ゲートバイポーラトランジスタは、第1導電型のドリフト層と、前記ドリフト層の一主面側において、第1方向に延在する形状であって前記第1方向と直行する第2方向に並行して配列されるように形成された絶縁ゲートと、一対の前記絶縁ゲートに挟まれたゲート間領域に形成された第2導電型のベース領域と、前記ベース領域において前記絶縁ゲートと隣接して形成された第1導電型のエミッタ領域と、前記エミッタ領域と接続されたエミッタ電極と、前記ドリフト層の他主面側に形成された第2導電型のコレクタ層と、前記コレクタ層と接続されたコレクタ電極と、を含んで構成され、前記ベース領域は、前記第1方向に沿って前記ドリフト層により複数に分離されており、前記ドリフト層と前記エミッタ電極とは絶縁されていること、を特徴とする。

50

**【発明の効果】****【0013】**

電流密度の低下を抑制しつつ、正孔の蓄積効果を高めたIGBTを提供できる。

**【図面の簡単な説明】****【0014】**

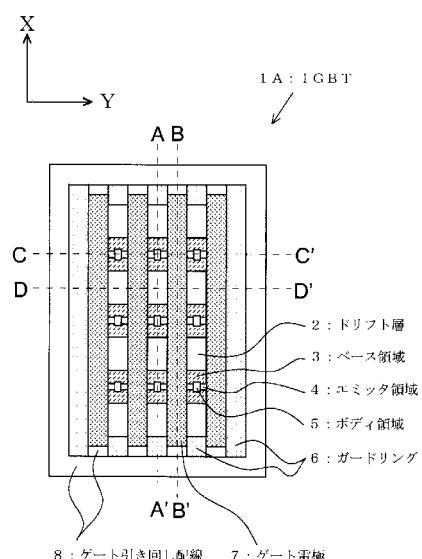

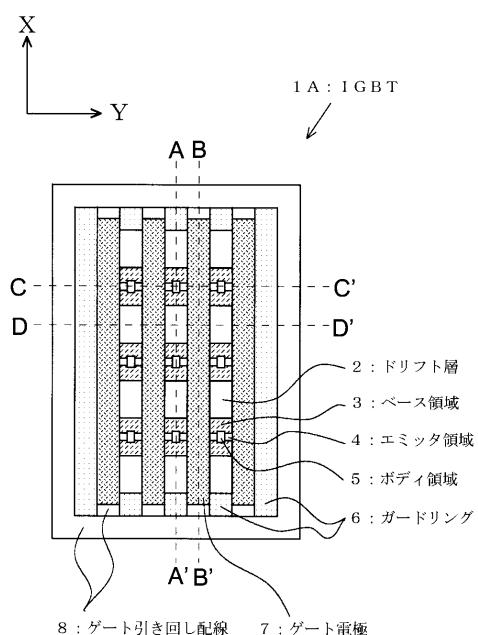

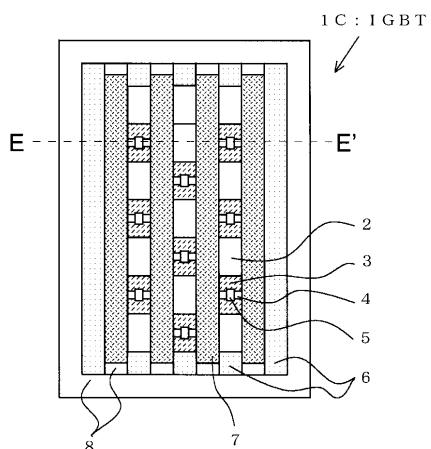

【図1】本発明の第1実施形態に係るIGBTの平面図である。

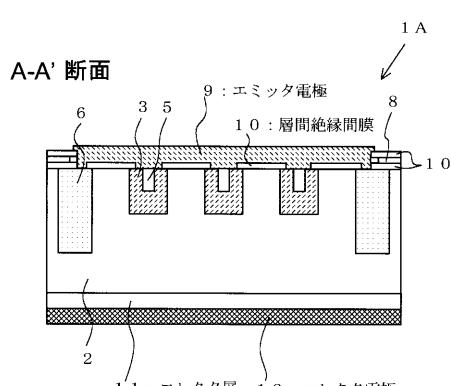

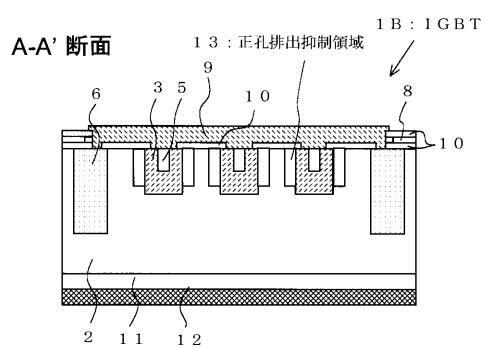

【図2】図1のIGBTのA-A'における断面図である。

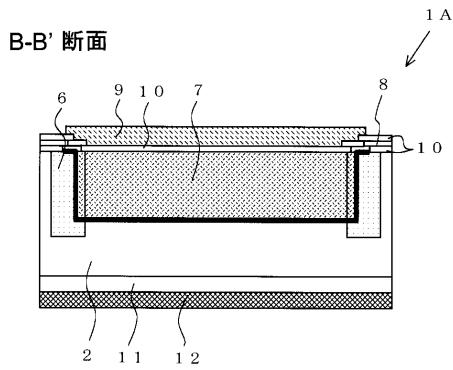

【図3】図1のIGTBのB-B'における断面図である。

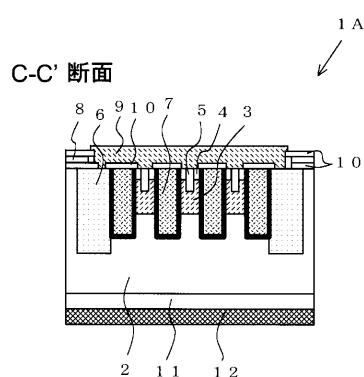

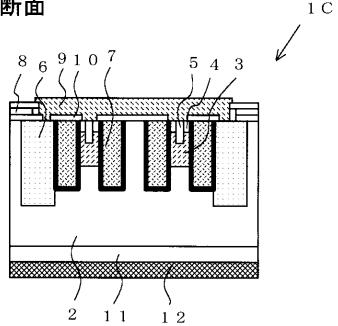

【図4】図1のIGBTのC-C'における断面図である。

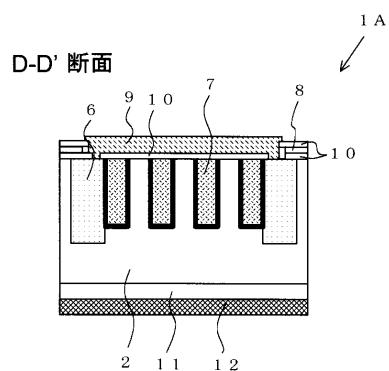

【図5】図1のIGTBのD-D'における断面図である。

【図6】本発明の第2実施形態に係るIGBTの断面図である。

【図7】本発明の第3実施形態に係るIGBTの平面図である。

【図8】図2のIGBTのE-E'における断面図である。

**【発明を実施するための形態】****【0015】**

以下、本発明の実施形態について詳述する。

**【実施例1】****【0016】**

はじめに、本発明の第1実施形態に係るIGBT1Aの構成について、図1～5を参照して具体的に説明する。図1はIGBTの平面図である。また、図2、3、4及び5は、それぞれ、図1のIGBTのA-A'、B-B'、C-C'、D-D'における断面図である。

10

**【0017】**

20

まず、図1を参照して、第1実施形態に係るIGBT1Aの平面図における構成について説明する。IGBT1Aは、ドリフト層2、ベース領域3、エミッタ領域4、ボディ領域5、ガードリング6、ゲート電極7及びゲート引き回し配線8を含んで構成される。なお、実際には、エミッタ領域4と接続されるエミッタ電極9や、このエミッタ電極9とドリフト層2又はゲート電極7とを絶縁する層間絶縁膜10が形成されているが、煩雑を避けるため、平面図においてはこれらの図示は省略した。

**【0018】**

30

各構成要素について詳述すると、ゲート電極7は、Y方向に伸びるようなストライプ形状である。そして、これらは並行してX方向に複数配列される。ゲート電極7は、IGBT1Aの周囲に形成されたゲート引き回し配線8と接続されて制御される。また、P+型導電型のガードリング6は、ゲート引き回し配線8に囲まれた領域であってゲート電極7を除く領域の周囲に形成される。

**【0019】**

N-導電型のドリフト層2は、ゲート電極7間であってガードリング6に囲まれた領域に配置するように形成される。そして、P型導電型のベース領域3は、ドリフト層2内においてそれぞれが離間して形成される。

**【0020】**

40

N+導電型のエミッタ領域4は、それぞれのベース領域3内においてゲート電極7と隣接するように形成される。そして、P+型のボディ領域5は、それぞれのベース領域3内において、エミッタ領域4間に位置するように形成される。

**【0021】**

また、ここでは図示していないが、エミッタ電極9は、全てのエミッタ領域4上を覆うように形成される。そして、層間絶縁膜10は、エミッタ電極9と、ゲート電極7及びドリフト層2と、を絶縁するように形成される。

**【0022】**

次に、図2を参照して、IGBT1AのA-A'における断面の構成について説明する。ドリフト層2の主面は、ガードリング6、ベース領域3及びボディ領域5を含んで構成

50

される。そして、当該主面上は、エミッタ電極 9、層間絶縁膜 10 及びゲート引き回し配線 8 を含んで構成される。一方、ドリフト層 2 の裏面は、コレクタ層 11 及びコレクタ電極 12 を含んで構成される。

#### 【0023】

ドリフト層 2 の正面における構成について詳述すると、ガードリング 6 は、IGBT1A の周囲に位置において、ベース領域 3 よりも深くなるように形成される。そして、ベース領域 3 は、ガードリング 6 に囲まれた領域において、それぞれが離間して複数形成される。また、ボディ領域 5 は、ベース領域 3 の表面において、中心に位置するように形成される。なお、ゲート電極 7 は、当該断面においては構成されないように配置されている。

#### 【0024】

ドリフト層 2 の正面における構成について詳述すると、エミッタ電極 9 は、全てのエミッタ領域 4 を覆うことができる程度の面積にて幅広く形成される。そして、層間絶縁膜 10 は、エミッタ電極 9 とエミッタ領域 4 とが接続され、かつ、エミッタ電極 9 とドリフト層 2 とが絶縁されるように形成される。また、ゲート引き回し配線 8 は、IGBT1A の周囲において、その上下が層間絶縁膜 10 に挟まれるように形成される。

#### 【0025】

ドリフト層 2 の裏面について詳述すると、P+導電型のコレクタ層 11 は、ドリフト層 2 の裏面の全面にイオン注入して形成される。そして、コレクタ電極 12 は、コレクタ層 11 と密接して形成される。

#### 【0026】

次に、図 3 を参照して、IGBT1A の B - B' における断面の構成について説明する。

#### 【0027】

当該断面においては、ベース領域 3、エミッタ領域 4 及びボディ領域 5 は形成されない。一方、ゲート電極 7 は、その一端及び他端がゲート引き回し配線 8 と接続されるように形成される。これにより、ゲート電極 7 は、ゲート引き回し配線 8 の信号に応じて制御される。そして、層間絶縁膜 10 は、エミッタ電極 9 とゲート電極 7 とが絶縁されるように幅広く形成される。

#### 【0028】

なお、その他の構成については、A - A' の断面の構成と大部分が共通するから、ここでは説明を省略する。

#### 【0029】

次に、図 4 を参照して、IGBT1A の C - C' における断面の構成について説明する。

#### 【0030】

当該断面においては、ガードリング 6 に囲まれたドリフト層 2 の正面において、ゲート電極 7 が離間して複数形成される。そして、それぞれのゲート電極 7 間の領域において、ベース領域 3 は、その下端がゲート電極 7 より浅い位置となるように形成される。それぞれのベース領域 3 内では、エミッタ領域 4 はゲート電極 7 に隣接するように形成され、ボディ領域 5 はエミッタ領域 4 間に位置するように形成される。

#### 【0031】

ドリフト層 2 の正面においては、エミッタ電極 9 は、全てのエミッタ領域 4 と接続される程度に幅広く形成される。そして、層間絶縁膜 10 は、エミッタ電極 9 とエミッタ領域 4 とが接続され、エミッタ電極 9 とゲート電極 7 とが絶縁されるように形成される。

#### 【0032】

その他の構成については、ここでも説明を省略する。

#### 【0033】

次に、図 5 を参照して、IGBT1A の D - D' における断面の構成について説明する。

#### 【0034】

10

20

30

40

50

ドリフト層 2 の正面における構成について詳述すると、当該断面においては C - C' における断面の構成と同様に、ガードリング 6 に囲まれたドリフト層 2 の正面において、ゲート電極 7 は離間して複数形成される。しかし、それぞれのゲート間 7 領域においては、ベース領域 3、エミッタ領域 4 及びボディ領域 5 は形成されない。

#### 【 0 0 3 5 】

ドリフト層 2 の正面ににおける構成について詳述すると、層間絶縁膜 10 は、エミッタ電極 9 と、ゲート電極 7 及びドリフト層 2 とが接続されないように全面に渡って形成される。

#### 【 0 0 3 6 】

その他の構成については、ここでも説明を省略する。

10

#### 【 0 0 3 7 】

以下に、当該構成による作用について説明する。

#### 【 0 0 3 8 】

I G B T 1 A がオン状態のとき、すなわち、エミッタ電極 9 がアースに接続され、コレクタ電極 12 に正電圧が印加されると、ドリフト層 2 とベース領域 3 とからなる P N 接合は逆バイアスとなる。この状態においてゲート電極 7 にエミッタ電極 9 との間で閾値以上の正電圧が印加されると、C - C' における断面(図4)においては、ドリフト領域 3 にはゲート電極 7 に沿って N 導電型に反転したチャネルが形成される。すると、当該チャネルを介して、電子は、エミッタ領域 4 からドリフト層 2 に電子が注入される。これにより、コレクタ層 11 からドリフト層 2 に正孔が注入され、ドリフト層 2 において伝導度変調が生じて、ドリフト層 2 の抵抗が低くなる。

20

#### 【 0 0 3 9 】

このとき、本実施形態では、この正孔がエミッタ電極 9 から排出されにくいため、伝導度変調効果が良好であるという特徴を有する。すなわち、A - A' における断面(図2)を参照すると、エミッタ電極 9 とドリフト層 2 との間には層間絶縁膜 10 が形成されているため、正孔は、ベース領域 3 間からは排出されない。これを D - D' における断面(図5)を参照して確認すると、当該断面においては、正孔が排出される経路がないことが確認できる。

#### 【 0 0 4 0 】

また、本実施形態では、電流密度の低下を抑制できるという特徴も有する。すなわち、C - C' における断面(図4)を参照すると、当該断面ではゲート電極 7 間の領域に電流経路が形成されるが、D - D' における断面(図5)を参照すると、電流経路が形成されないため、I G B T 1 A の全体としては電流密度の低下が懸念されるようにも思える。しかし、A - A' における断面(図2)を参照すると、ベース領域 3 は下面のみならず、その側面もドリフト層 2 と面している。このため、電流経路は、ベース領域 3 の下面のみならず、ベース領域 3 の側面にも形成される。そして、正孔は、ベース領域 3 の下面のみならず、ベース領域 3 の側面にも蓄積される。したがって、ベース領域 3 の側面に形成される電流経路も、抵抗値が良好に低下する。このように、本実施形態では、低抵抗の電流経路がベース領域 3 の側面にも形成されるため、電流密度の低下を抑制できる。

30

#### 【 0 0 4 1 】

なお、正孔の排出を抑制するという観点のみ考慮すると、A - A' における断面(図2)を参照したときに、層間絶縁膜 10 の形状を図示のまま形成しておけば、ベース領域 3 が左端のガードリング 6 から右端のガードリング 6 まで延在するように形成されていても良いようにも思える。しかし、そのような場合では、ベース領域 3 は全面に渡って形成されるのであるから、層間絶縁膜 10 の直下におけるベース領域 3 から正孔が入り込んでも、この正孔はベース領域 3 内を左右にも移動するのであるから、正孔は層間絶縁膜 10 が形成されていない位置からエミッタ電極 9 へと排出されてしまう。これに対して、本実施形態では、正孔は、層間絶縁膜 10 が形成されている位置においては排出される経路を有しないのであるから、正孔は良好に蓄積される。

40

#### 【 実施例 2 】

50

## 【0042】

つづいて、第2実施形態に係るIGBT1Bについて説明する。当該IGBT1Bは、第1実施形態に係るIGBT1Aよりもさらに正孔の蓄積効果を高めたものである。

## 【0043】

図6は、本実施形態に係るIGBT1Bについて、第1実施形態に係るIGBT1AのA-A'における断面(図2)に相当する断面の構成を示す。

## 【0044】

第1実施形態と対比すると、本実施形態に係るIGBT1Bでは、ベース領域3の側面にN型導電型の正孔排出抑制領域13が形成されている。他の構成については、第1実施形態と同様であるため、ここでは説明を省略する。

10

## 【0045】

当該構成による作用について説明すると、第1実施形態に係るIGBT1AのA-A'における断面(図2)を参照したときに、第1実施形態に係るIGBT1Aでは、確かに正孔はベース領域3間の層間絶縁膜下10において蓄積される。しかし、ベース領域3は、側面がドリフト層2に露出しているため、正孔が当該側面からエミッタ電極9に排出されることも考えられる。これに対して、本実施形態に係るIGBT1Bでは、ベース領域3の側面に正孔排出抑制領域13が形成されているため、正孔はベース領域3の側面から排出しにくい。これにより、本実施形態に係るIGBT1Bは、第1実施形態に係るIGBT1Aよりも正孔の蓄積効果が高くなる。

20

## 【実施例3】

## 【0046】

つづいて、第3実施形態に係るIGBT1Cについて説明する。

## 【0047】

図7は、第3実施形態に係るIGBT1Cの平面図を示す。また、図8は、IGBTのE-E'における断面の構成を示す。

30

## 【0048】

当該IGBT1Cでは、隣接するゲート電極7間の領域において、ベース領域3の形成される位置が互いにずれるように配置される。そして、ゲート電極7間の領域であってベース領域3が形成された箇所では、電流経路が形成されるとともに正孔が排出される。一方、ゲート電極7間の領域であってベース領域3が形成されない箇所においては、エミッタ電極9とドリフト層2との間に層間絶縁膜10が形成されているため、正孔の排出が抑制される。そして、当該構成によって、IGBT1Cは、第1実施形態に係るIGBT1Aと比較すると、平面視における電流密度分布を均一化することができる。

40

## 【0049】

以上、第1乃至3実施形態を通じて、本発明について具体的に説明した。本発明は、ゲート電極7間の領域において、ベース領域3は分離するように複数形成される。そして、ベース領域3間においては、エミッタ電極9とドリフト層2との間には層間絶縁膜10が形成される。これにより、正孔は、ベース領域3間から排出されなくなるため、蓄積されやくなる。さらには、ベース領域3の側面が露出しているため、電流経路がベース領域3の側面にも形成され、電流密度の低下が抑制される。

40

## 【0050】

なお、上記実施形態は本発明の理解を容易にするためのものであり、本発明を限定して解釈するためのものではない。本発明は、その趣旨を逸脱することなく、変更、改良され得ると共に、本発明にはその等価物も含まれる。

## 【0051】

例えば、上記実施形態にて提示した各導電型はこれに限定されず、それぞれが逆導電型であってもよい。

## 【0052】

また、上記実施形態では、ゲート引き回し配線8がガードリング6の外側に配置されていた。しかし、本発明はこれに限定されず、設計上、適宜変更できる。

50

## 【0053】

また、上記実施形態では、ドリフト層2の裏面は、コレクタ層1'1及びコレクタ電極1'2のみが形成されていた。しかし、本発明はこれに限定されず、例えば、ドリフト層2とコレクタ層1'1との間にN+導電型のバッファ層が形成されてもよい。

## 【符号の説明】

## 【0054】

|           |           |

|-----------|-----------|

| 1 A ~ 1 C | I G B T   |

| 2         | ドリフト層     |

| 3         | ベース領域     |

| 4         | エミッタ領域    |

| 5         | ボディ領域     |

| 6         | ガードリング    |

| 7         | ゲート電極     |

| 8         | ゲート引き回し配線 |

| 9         | エミッタ電極    |

| 10        | 層間絶縁膜     |

| 11        | コレクタ層     |

| 12        | コレクタ電極    |

| 13        | 正孔排出抑制領域  |

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図7】

【図6】

【図8】

E-E' 断面

---

フロントページの続き

(51) Int.Cl.

F I

H 01 L 29/78 6 5 2 S

テーマコード(参考)