(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6392745号

(P6392745)

(45) 発行日 平成30年9月19日(2018.9.19)

(24) 登録日 平成30年8月31日(2018.8.31)

(51) Int.Cl.

H04L 12/931 (2013.01)

G06F 15/173 (2006.01)

F 1

H04L 12/931

G06F 15/173 685 S

請求項の数 24 (全 23 頁)

(21) 出願番号 特願2015-512707 (P2015-512707)

(86) (22) 出願日 平成25年5月10日 (2013.5.10)

(65) 公表番号 特表2015-522991 (P2015-522991A)

(43) 公表日 平成27年8月6日 (2015.8.6)

(86) 國際出願番号 PCT/US2013/040508

(87) 國際公開番号 WO2013/173181

(87) 國際公開日 平成25年11月21日 (2013.11.21)

審査請求日 平成28年4月14日 (2016.4.14)

(31) 優先権主張番号 13/470,847

(32) 優先日 平成24年5月14日 (2012.5.14)

(33) 優先権主張国 米国(US)

(73) 特許権者 591016172

アドバンスト・マイクロ・ディバイシズ・

インコーポレイテッド

A D V A N C E D M I C R O D E V I

C E S I N C O R P O R A T E D

アメリカ合衆国 95054 カリフォル

ニア州、サンタクララ、オーガスティ

ン ドライブ 2485

(74) 代理人 100108833

弁理士 早川 裕司

(74) 代理人 100111615

弁理士 佐野 良太

(74) 代理人 100162156

弁理士 村雨 圭介

最終頁に続く

(54) 【発明の名称】サーバノード相互接続デバイス及びサーバノード相互接続方法

## (57) 【特許請求の範囲】

## 【請求項 1】

複数の電子デバイスと通信するスイッチファブリックと、

前記スイッチファブリックと通信するランデブーメモリと、

前記スイッチファブリックと1つ以上のネットワークインターフェースカード(N I C s)との間に接続された入出力(I/O)プロセッサと、を備え、

前記複数の電子デバイスのうち第1の電子デバイスのメモリからデータが出力可能な状態にあるとの判定に応じて、且つ、前記ランデブーメモリに前記データ用の位置が割り当てられたことに応じて、前記データが前記第1の電子デバイスから前記ランデブーメモリに転送され、

前記I/Oプロセッサは、前記N I C sに接続されたネットワーク上のリモート電子デバイスへの前記ランデブーメモリからの前記N I C sを介したデータの転送に関する動作を実行する、

集約デバイス。

## 【請求項 2】

前記第1の電子デバイスは、前記スイッチファブリックに接続したサーバノードである、請求項1に記載の集約デバイス。

## 【請求項 3】

前記第1の電子デバイスは、前記集約デバイスと通信するリモートコンピュータである、請求項1に記載の集約デバイス。

10

20

**【請求項 4】**

前記データは、前記ランデブーメモリから前記複数の電子デバイスのうち第2の電子デバイスに前記データが出力可能な状態にあるとの判定に応じて、且つ、前記第2の電子デバイスのメモリに前記データ用の位置が割り当てられたことに応じて、前記ランデブーメモリから前記第2の電子デバイスに転送される、請求項1に記載の集約デバイス。

**【請求項 5】**

前記データが第2の電子デバイスに提供可能になるまでに、前記ランデブーメモリにおいて前記データ用の位置を割り当てるランデブー管理モジュールをさらに含む、請求項1に記載の集約デバイス。

**【請求項 6】**

前記I/Oプロセッサは、出力可能な状態の前記データが受信される位置であって、前記ランデブーメモリに割り当てられた位置を識別する、請求項1に記載の集約デバイス。

**【請求項 7】**

前記複数の電子デバイスの間でデータを送信するスイッチングコントロールプレーンを管理するコントロールプレーンプロセッサをさらに含む、請求項1に記載の集約デバイス。

**【請求項 8】**

前記ランデブーメモリはTSVメモリを含む、請求項1に記載の集約デバイス。

**【請求項 9】**

前記ランデブーメモリはオンダイメモリを含む、請求項1に記載の集約デバイス。

**【請求項 10】**

複数のサーバノードと、

前記複数のサーバノードに接続した集約デバイスとを備え、

前記集約デバイスは、

前記複数のサーバノードと通信するスイッチファブリックと、

前記複数のサーバノードのうち第1のサーバノードのローカルメモリからデータが出力可能な状態にあるとの判定と、ランデブーメモリに前記データ用の位置が割り当てられたこととに応じた、前記第1のサーバノードのローカルメモリを用いたデータの転送に関するランデブーメモリと、

前記スイッチファブリックと1つ以上のネットワークインターフェースカード(NICs)との間に接続された入出力(I/O)プロセッサであって、前記NICsに接続されたネットワーク上のリモート電子デバイスへの前記ランデブーメモリからの前記NICsを介したデータの転送に関する動作を実行するI/Oプロセッサと、

を含む、サーバ集約システム。

**【請求項 11】**

前記データは、前記ランデブーメモリから宛先電子デバイスに前記データが出力可能な状態にあるとの判定と、前記データを受信するための位置が前記宛先電子デバイスに割り当てられたこととに応じて、前記ランデブーメモリから前記宛先電子デバイスに転送される、請求項10に記載のサーバ集約システム。

**【請求項 12】**

前記宛先電子デバイスは、前記複数のサーバノードのうち第2のサーバノード、又は、前記集約デバイスと通信するリモートコンピュータである、請求項11に記載のサーバ集約システム。

**【請求項 13】**

前記データが宛先電子デバイスに提供可能になるまでに、前記ランデブーメモリにおいて前記データ用の位置を割り当てるランデブー管理モジュールをさらに含む、請求項10に記載のサーバ集約システム。

**【請求項 14】**

前記I/Oプロセッサは、出力可能な状態の前記データが受信される位置であって、前記ランデブーメモリに割り当てられた位置を識別する、請求項10に記載のサーバ集約シ

10

20

30

40

50

ステム。

【請求項 1 5】

前記第 1 のサーバノードの前記ローカルメモリと前記ランデブーメモリとの間で前記データの転送を確立するコントロールプレーンプロセッサをさらに含む、請求項 1 0 に記載のサーバ集約システム。

【請求項 1 6】

複数の電子デバイスと集約システムとの間で通信する方法であって、

第 2 の電子デバイスに送信するデータを、前記複数の電子デバイスのうち第 1 の電子デバイスのローカルメモリに提供することと、

前記第 1 の電子デバイスの前記ローカルメモリから前記データを受信するための前記集約システムのランデブーメモリを提供することと、10

前記第 1 の電子デバイスの前記ローカルメモリに前記データが伝送用として存在するとの前記集約システムによる判定と、前記第 1 の電子デバイスの前記ローカルメモリから受信される前記データを記憶するための位置が前記ランデブーメモリに割り当てられているとの判定とに応じて、前記データを、前記第 1 の電子デバイスの前記ローカルメモリから前記ランデブーメモリに転送することと、

前記データを前記ランデブーメモリからリモートコンピュータである前記第 2 の電子デバイスのローカルメモリに転送することであって、前記データを、前記集約システムの I/O プロセッサと 1 つ以上のネットワークインターフェースカード (NICs) を介して、前記 NICs 及び前記第 2 の電子デバイスに接続されたネットワークを経由して前記第 2 の電子デバイスに転送することを含む、ことと、20

を含む方法。

【請求項 1 7】

前記第 1 の電子デバイスの前記ローカルメモリにおいて前記データが伝送用に使用可能であるという前記第 1 の電子デバイスからの通知を生成することと、

前記ランデブーメモリにて使用可能なバッファを識別することと、

前記第 1 の電子デバイスの前記ローカルメモリから前記データを受信するために前記使用可能なバッファを割り当てることと、

前記データを、前記第 1 の電子デバイスの前記ローカルメモリから前記ランデブーメモリの前記使用可能なバッファに出力することと、30

をさらに含む請求項 1 6 に記載の方法。

【請求項 1 8】

前記第 2 の電子デバイスのローカルメモリが前記データを受信可能であるとの判定を行うことと、

前記判定に基づいて、前記データを、前記ランデブーメモリから前記第 2 の電子デバイスの前記ローカルメモリに転送することと、

をさらに含む請求項 1 6 に記載の方法。

【請求項 1 9】

前記ランデブーメモリにおいて前記データが伝送用に使用可能であるという前記ランデブーメモリからの通知を生成することと、40

前記第 2 の電子デバイスの前記ローカルメモリにて使用可能なバッファを識別することと、

前記第 2 の電子デバイスの前記ローカルメモリにて前記使用可能なバッファを割り当てることと、

前記割り当てに基づいて、前記データを、前記ランデブーメモリから前記第 2 のデバイスの前記ローカルメモリの前記使用可能なバッファに転送することと、

をさらに含む請求項 1 8 に記載の方法。

【請求項 2 0】

前記第 1 の電子デバイスはサーバノードを含む、請求項 1 6 に記載の方法。

【請求項 2 1】

前記第2の電子デバイスはリモートコンピュータである、請求項16に記載の方法。

【請求項22】

複数の電子デバイスと集約システムとの間で通信する方法であって、

第2の電子デバイスに送信するデータを、前記複数の電子デバイスのうち第1の電子デバイスのローカルメモリに提供すること、

前記集約システムの仮想ネットワークインターフェースカード( vNIC )に対して、前記第1の電子デバイスの前記ローカルメモリにおいて前記データが伝送用として使用可能であると通知すること、

前記第1の電子デバイスの前記ローカルメモリに伝送用として前記データがあるとの判定と、前記集約システムのランデブーメモリに前記データ用の位置が割り当てられたことに応じて、前記データを、前記第1の電子デバイスの前記ローカルメモリから前記ランデブーメモリに転送すること、

前記第2の電子デバイスにおける少なくとも一つの使用可能なバッファの通知を生成すること、

前記データを受信するために前記第2の電子デバイスにおける少なくとも一つの使用可能なバッファを割り当てること、

前記データを前記ランデブーメモリからリモートコンピュータである前記第2の電子デバイスにおける少なくとも一つの使用可能なバッファに転送することであって、前記データを、前記集約システムのI/Oプロセッサと1つ以上のネットワークインターフェースカード(NICs)を介して、前記NICs及び前記第2の電子デバイスに接続されたネットワークを経由して前記第2の電子デバイスに転送することを含む、ことと、

を含む方法。

【請求項23】

前記電子デバイスの少なくとも一つはサーバノードを含む、請求項22に記載の方法。

【請求項24】

コンピュータ可読プログラムコードを記憶するコンピュータ可読記憶媒体であって、

前記コンピュータ可読プログラムコードは、

集約システムを介して第2の電子デバイスにデータを送信するために、第1の電子デバイスのローカルメモリに前記データを提供するように構成されたコンピュータ可読プログラムコードと、

前記集約システムの仮想ネットワークインターフェースカード( vNIC )に対して、前記第1の電子デバイスの前記ローカルメモリにおいて前記データが伝送用として使用可能であると通知するように構成されたコンピュータ可読プログラムコードと、

前記第1の電子デバイスの前記ローカルメモリに前記データが伝送用として存在するとの判定と、前記ランデブーメモリに前記データ用の位置が割り当てられたことに応じて、前記データを、前記第1の電子デバイスの前記ローカルメモリから前記ランデブーメモリに転送するように構成されたコンピュータ可読プログラムコードと、

前記第2の電子デバイスにおける少なくとも一つの使用可能なバッファの通知を生成するように構成されたコンピュータ可読プログラムコードと、

前記データを受信するために前記第2の電子デバイスにおける前記少なくとも一つの使用可能なバッファを割り当てるように構成されたコンピュータ可読プログラムコードと、

前記vNICが、前記データを、前記ランデブーメモリからリモートコンピュータである前記第2の電子デバイスにおける前記少なくとも一つの使用可能なバッファに転送することであって、前記データを、前記集約システムのI/Oプロセッサと1つ以上のネットワークインターフェースカード(NICs)を介して、前記NICs及び前記第2の電子デバイスに接続されたネットワークを経由して前記第2の電子デバイスに転送することを含む、ことを行うように構成されたコンピュータ可読プログラムコードと、

を含むコンピュータ可読記憶媒体。

【発明の詳細な説明】

【技術分野】

10

20

30

40

50

**【0001】**

本発明は、概して、ネットワークスイッチアーキテクチャに関し、より詳細には、スイッチファブリックを用いてサーバノードを相互接続するシステム及び方法に関する。

**【背景技術】****【0002】**

データセンタは、概して、ビジネス及び組織をサポートするインターネット及びイントラネットサービスを提供する、一元管理型の設備である。典型的なデータセンタは、様々なタイプの電子機器（例えば、コンピュータ、サーバ（例えば、電子メールサーバ、プロキシサーバ及びDNSサーバ）、ネットワークスイッチ、ルーター、データ記憶デバイス、及び、その他の関連する構成要素）を格納している。所与のデータセンタは、スイッチ及びルーターを含むスイッチングアーキテクチャを介して相互に及び外部デバイスと通信する数百又は数千の相互接続されたサーバノードを有することが可能である。また、従来のデータセンタは、仮想化のための構成をとることにより、サーバノードに対して、ネットワークインターフェイスカード（NIC）、ハードディスクドライブ又はその他のハードウェアの共有を可能にすることもできる。このようにする際には、通信データセンターアーキテクチャを介したノード間通信を容易にするために、複雑なスイッチファブリックが必要である。10

**【発明の概要】****【課題を解決するための手段】****【0003】**

一態様によれば、スイッチファブリックとランデブーメモリとを含む集約デバイスが提供される。スイッチファブリックは、複数の電子デバイスと通信する。ランデブーメモリは、スイッチファブリックと通信する。データは、複数の電子デバイスのうち第1の電子デバイスのメモリから前記データが出力可能な状態にあるという判定と、前記データ用のランデブーメモリに割り当てられた位置とに応じて、前記第1の電子デバイスから前記ランデブーメモリに転送される。20

**【0004】**

別の態様によれば、複数のサーバノードと、前記複数のサーバノードに接続した集約デバイスとを含むサーバ集約システムが提供される。集約デバイスは、前記複数のサーバノードのうち第1のサーバノードのローカルメモリを用いたデータ転送に関するランデブーメモリを含む。このデータ転送は、前記第1のサーバノードのメモリからデータが出力可能であるという判定と、前記ランデブーメモリに割り当てられた前記データ用の位置とに応じて行われる。30

**【0005】**

別の態様によれば、複数の電子デバイスと集約システムとの間で通信する方法が提供される。この方法は、複数の電子デバイスのうち第2の電子デバイスに送信するデータを、複数の電子デバイスのうち第1の電子デバイスのローカルメモリに提供することと、前記第1の電子デバイスのローカルメモリからデータを受信するために、ランデブーメモリを集約システムに設けることと、伝送用のデータが前記第1の電子デバイスのローカルメモリに存在するとの集約システムによる判定と、前記第1の電子デバイスのローカルメモリから受信したデータを記憶するための位置がランデブーメモリに割り当てられたとの判定とに応じて、第1の電子デバイスのローカルメモリからランデブーメモリにデータを転送することと、を含む。40

**【0006】**

別の態様によれば、複数の電子デバイスと集約システムとの間で通信する方法が提供される。この方法は、複数の電子デバイスのうち第2の電子デバイスに送信するデータを、複数の電子デバイスのうち第1の電子デバイスのローカルメモリに提供することと、第1の電子デバイスのローカルメモリにおいてデータが伝送用に使用可能であることを、集約システムの仮想ネットワークインターフェースカード（VNIC）に通知することと、第2の電子デバイスにおける少なくとも一つの使用可能なバッファの通知を生成することと50

、データを受信するために前記少なくとも一つの使用可能なバッファを割り当てることと、データを、第2の電子デバイスにおける前記少なくとも一つの使用可能なバッファにVNICによって出力することと、伝送用のデータが前記第1の電子デバイスのローカルメモリに存在するとの判定と、前記第2の電子デバイスにて前記少なくとも一つの使用可能なバッファを割り当てたとの判定とに応じて、第1の電子デバイスのローカルメモリからランデブーメモリにデータを転送することと、を含む。

#### 【0007】

別の態様によれば、コンピュータ可読プログラムコードを有するコンピュータ可読記憶媒体を含むコンピュータプログラム製品であって、前記記憶媒体を用いてプログラムコードが具体化されるコンピュータプログラム製品が提供される。コンピュータ可読プログラムコードは、集約システムを介して第2の電子デバイスに送信するためのデータを、第1の電子デバイスのローカルメモリに提供するように構成されたコンピュータ可読プログラムコードと、第1の電子デバイスのローカルメモリにおいてデータが伝送用に使用可能であることを、集約システムの仮想ネットワークインターフェースカード(VNIC)に通知するように構成されたコンピュータ可読プログラムコードと、第2の電子デバイスにおける少なくとも一つの使用可能なバッファの通知を生成するように構成されたコンピュータ可読プログラムコードと、データを受信するために前記少なくとも一つの使用可能なバッファを割り当てるために構成されたコンピュータ可読プログラムコードと、第2の電子デバイスにおける少なくとも一つの使用可能なバッファに対して、VNICによってデータを出力するように構成されたコンピュータ可読プログラムコードと、伝送用のデータが前記第1の電子デバイスのローカルメモリに存在するとの判定と、前記第2の電子デバイスにて前記少なくとも一つの使用可能なバッファを割り当てたとの判定とに応じて、第1の電子デバイスのローカルメモリからランデブーメモリにデータを転送するように構成されたコンピュータ可読プログラムコードと、を含む。

#### 【0008】

本発明の上記の利点及び更なる利点は、添付の図面に関連した後述の記載を参考することによって、より良く理解し得る。これらの図面において同様に表された数字は、同様の構成要素及び特徴を示している。図面は、必ずしも縮尺が揃っていないが、本発明の原理を例示することに重点が置かれている。

#### 【図面の簡単な説明】

#### 【0009】

【図1】従来のデータセンタネットワーク階層のブロック図である。

【図2】従来のインターネットファブリックスイッチに結合した複数のサーバノードを含むデータセンタのブロック図である。

【図3】一実施形態における、ランデブーメモリを有するサーバ集約システムと通信している複数のサーバノードを含む計算インフラストラクチャーのブロック図である。

#### 【図4】一実施形態における、図3のランデブー管理装置のブロック図である。

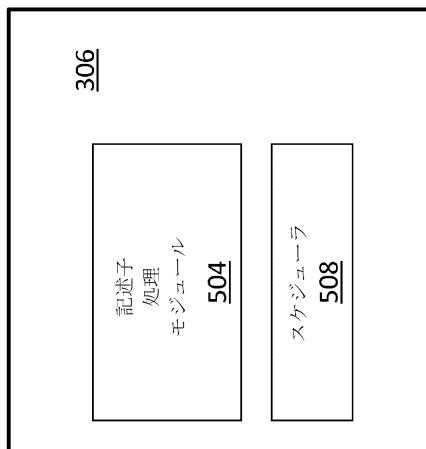

#### 【図5】一実施形態における、図3のネットワークプロセッサのブロック図である。

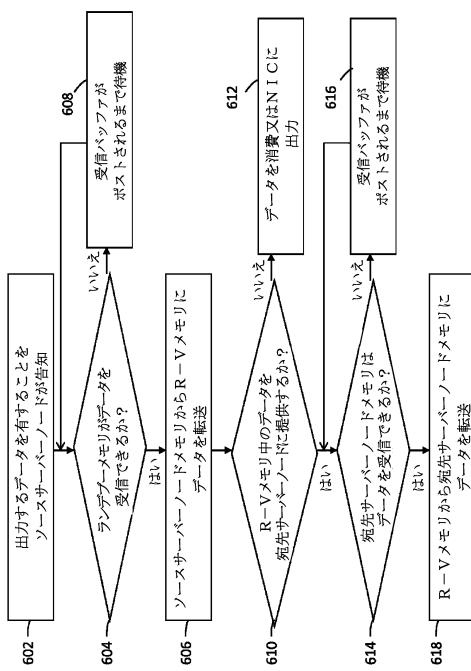

【図6】一実施形態における、サーバノードと、ランデブーメモリを有するサーバ集約システムとの間で電子通信を行う方法のフロー図である。

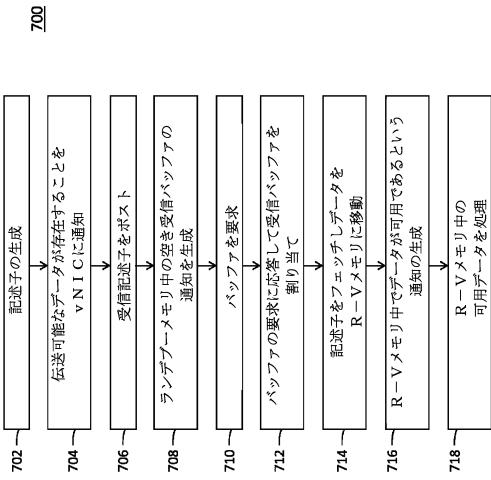

【図7】一実施形態における、ソースサーバノードと、ランデブーメモリを有するサーバ集約システムとの間で電子通信する方法のフロー図である。

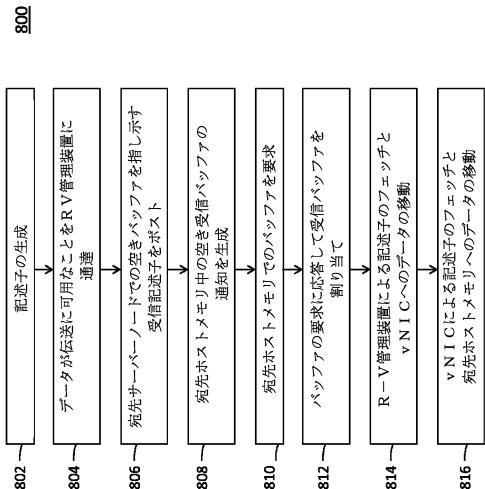

【図8】一実施形態における、サーバ集約システムと、宛先サーバノードとの間で通信を確立する方法のフロー図である。

【図9】他の実施形態における、ランデブースイッチング用に構成されたサーバ集約システムに結合した第1及び第2のサーバノード間で通信を確立する方法のフロー図である。

#### 【発明を実施するための形態】

#### 【0010】

以下の記載では具体的な詳細が記載されるが、本発明にかかるシステム及び方法が少なくともいくつかの詳細無しで実行できることは、当業者にとって認識し得るはずである。

10

20

30

40

50

場合によっては、本発明が曖昧にならないように、既知の特徴又は工程は、詳細に記載されていない。

#### 【0011】

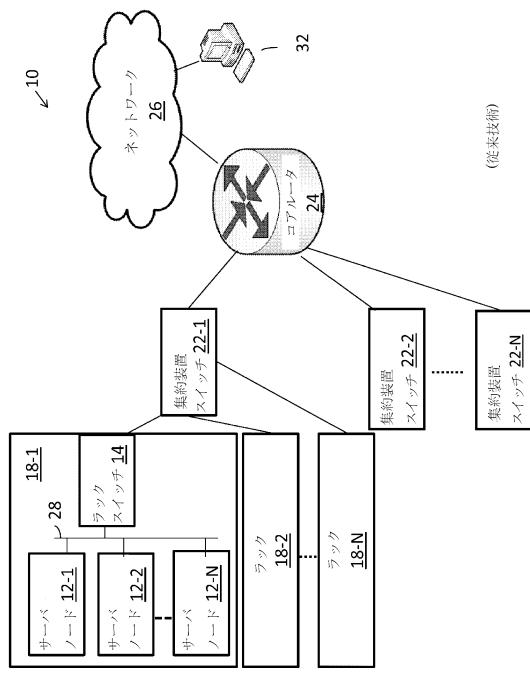

図1は、従来のデータセンタネットワーク階層10のブロック図である。図1では、複数のサーバノード12-1~12-N(Nは、1より大きい整数)は、例えば、ラック18-1のイーサネット(登録商標)ローカルエリアネットワーク(LAN)又は関連するデータネットワークなどのLANを介して、ラックスイッチ14と通信することができる。ラック18-1は、データセンタネットワーク階層10における他の一つ以上のラック18-2, 18-N(Nは、1より大きい整数)とともに、クラスタの一部として構成されてもよい。各クラスタは、集約スイッチ22-1, 22-2, 22-N(Nは、1より大きい整数)を含むことができ、これらは、イーサネット(登録商標)又は他のネットワーク接続を介して、コアルータ24に接続されている。ユーザコンピュータ32(例えば、ラップトップ、スマートフォン又はその他の電子デバイス)は、ネットワーク26(例えば、IPネットワーク、インターネットなど)を介して、サーバノード12-1~12-N(概して、12)と通信することができる。データセンタスイッチに関連する規模、経費及び電力の削減を求める一方で、データセンタの拡張性の増大を求めるという、止むことのない要求が存在する。

#### 【0012】

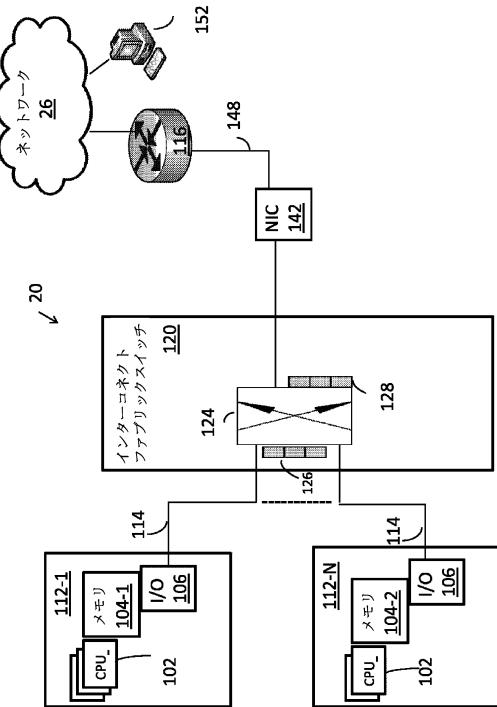

図2は、従来のインターフェクトファブリックスイッチ120に結合した複数のサーバノード112-1~112-N(Nは、1より大きい整数)を含むデータセンタ20のブロック図である。インターフェクトファブリックスイッチ120は、単一のシャーシのもとでの集約スイッチ及びラックスイッチの一元管理機能によって、スイッチの数を削減することができ、従来のサーバラックにおいて使用される従来のイーサネット(登録商標)スイッチングの要求の多くを置き換えることができる。

#### 【0013】

サーバノード112-1~112-N(概して、112)は、プロセッサクラスタとして、又は、他の周知の装置として構成することができる。サーバノード112は、単一のソケットサーバ、又は、共用インフラストラクチャーを共有する低消費電力プロセッサ102を含むことができる。サーバノードプロセッサ102は、一つ以上のマイクロプロセッサ、中央演算処理装置(CPU)、画像処理装置(GPU)、デジタルシグナルプロセッサ(DSP)、特定用途向け集積回路(ASIC)、メモリコントローラ、マルチコアプロセッサ、及び、その他のタイプのデータ処理デバイスだけでなく、これらのデバイスや他のデバイスの一部及び/又は組合せを含むことができる。

#### 【0014】

また、サーバノード112は、ローカルメモリ104と、I/Oロジック106とを含む。ローカルメモリ104は、不揮発性又は揮発性メモリ(例えば、一つ以上のチャネルのダイナミックランダムアクセスメモリ(DRAM)又は静态RAM(SRAM))を含むことができる。I/Oロジック106は、コンピュータのI/O機能(例えば、サーバノード112とインターフェクトファブリックスイッチ120との間のデータ転送)を管理するために、サウスブリッジ等を含むI/Oコントローラを有するように構成されてもよい。I/Oロジック106は、インターフェクトファブリックスイッチ120と電子通信を確立するために、イーサネット(登録商標)、PCIe又は他のネットワークコネクター114を含んでいてもよい。

#### 【0015】

インターフェクトファブリックスイッチ120は、複数の入出力ポートと、可変長又は固定長のフレーム、データパケット、セル等を入出力ポート間でルーティングし得るクロスバー124とを含み、サーバノード112、例えばNIC142又はハードドライブ144等の共有デバイス、及び/又は、例えばユーザコンピュータ152等の外部電子デバイス間での通信を容易にすることができるものである。ポートは、仮想ポート、物理ポート又はこれらの組合せを含んでいてもよい。ポートは、單方向又は双方向通信用の構成で

あってもよい。

#### 【0016】

クロスバー124は、行と列の配列に組織化され得る。データ伝送の間には、所与の行のいくつかの入力ポートは、ある列における出力ポートを奪い合う場合がある。入力ポートは、入力バッファ126と通信することができる。入力バッファは、クロスバー124が、使用可能な出力ポートにデータを送信することができるまで、サーバノード112から受信したデータを一時的に記憶するものである。出力ポートは、出力バッファ128を含む。出力バッファは、ネットワークバス140（例えば、イーサネット（登録商標）バス、PCIeバス等）を介してパケットを宛先に送信するために、所望の出力ポートが使用可能になるまで、一つ以上の入力ポートから受信したデータを一時的に記憶する。

10

#### 【0017】

しかしながら、インターフェクトファブリックスイッチ120は、輻輳に関連する問題（例えば、ヘッドライン（HOL）ブロッキング）が生じやすい。この問題は、スイッチ120の複数の入力ポートが同一の出力ポートを奪い合う場合に発生するものである。また、スケーリングに関連する課題も発生するが、これは、スイッチ120でのI/Oポートの追加によって、共有のリソースを奪い合うというリスクが増加するからである。関連する課題は、サーバノード112と、インターフェクトファブリックスイッチ120との間でバンド幅を充分に使用しないことである。例えば、HOLブロッキングは、特に、入力ポートで待機しているパケット、セル等が、ファーストイン・ファーストアウト（FIFO）のキューで記憶されている場合に、クロスバー124でかなりの量のバンド幅を消費する可能性がある。また、入力及び出力バッファ126, 128でのキューはすぐに満杯になり、その結果、望ましくない待ち時間、ジッター又はパケット喪失のみならず、オーバーラン及び/又はアンダーラン条件が生じ、これらは、バンド幅の不充分な使用及び性能の課題を生じる。

20

#### 【0018】

フロー制御技術は、容易に使用可能であり、データセンタ20でのネットワーク輻輳を緩和することができる。例えば、複雑なスケジューリング技術を適用して、クロスバー124を介したデータトラヒックを管理することができる。しかしながら、そのような技術は、概して、実現するには高価である。

30

他の周知である技術は、イーサネット（登録商標）をベースにした再送信を実現することである。しかしながら、イーサネット（登録商標）をベースにした再送信は、貴重なバンド幅を消費する。

#### 【0019】

他のフロー制御メカニズムを上流のデバイスに適用して、パケットの通過を停止せるように当該デバイスに要求することができる。そのような手法は、バッファオーバーフローを低減させるのに効果的であるものの、ネットワーク輻輳を完全に緩和しない。

#### 【0020】

他の手法は、一時記憶用の外部メモリデバイスと、パケットのキューイング（queuing）とに依るものである。しかしながら、この手法は、インターフェクトファブリックスイッチ120に対して、さらなるピン、及び、すぐにでも使用可能なメモリデバイスへの「配線」又はコネクターを必要とし、その結果として、拡張性の制限と、バンド幅に関連した問題とが、さらなる電力消費を求める関連要求とともに生じる。

#### 【0021】

本発明の概念は、従来のデータセンタ相互接続スイッチに付随する輻輳に関連した課題を、ランデブーデバイス（rendezvous device）を含むサーバ集約システムを導入することによって低減又は取り除くものである。ランデブーデバイスは、制御された方法で、高バンド幅スイッチファブリックを介して、複数のサーバノード又は関連する電子デバイスのローカルメモリと通信する。ランデブーデバイスは、出力可能なデータを有する伝送デバイスと、当該データの受信用に使用可能なメモリバッファを有する受

40

50

信デバイスとの間で通信し、伝送デバイス及び受信デバイスの間で効率的なデータ伝送経路を提供する。例えば、データが、伝送デバイスのローカルメモリから明示的に転送され得るのは、データが出力可能であるとサーバ集約システムが判定した後であって、データ記憶用のランデブーデバイスのメモリ記憶位置に特定のメモリ記憶位置が割り当てられた後である。これらの条件が真であると判定された場合、すなわち、送信するデータを伝送デバイスが有していて、使用可能なバッファ（空きバッファ）を受信デバイスが有している場合に、伝送デバイスから受信デバイスへの効率的で待ち時間の短いデータ移動が生じる。

#### 【0023】

図2に記載された従来のネットワークスイッチ環境では、データは、クロスバースイッチキュー126, 128が使用可能な空間を有しているか否かに関係なく、キュー126, 128に出力される。キュー126, 128が使用可能な空間を有していない場合には、データは通常破棄され、複雑でバンド幅を消費する再送信過程が実行される。10

#### 【0024】

一実施形態では、サーバ集約システムは、ソースサーバノード等からのデータをいつ受信するのかを判定して、「ランデブー（rendezvous）」する位置を確立することができる。この位置は、宛先サーバノード等のメモリ記憶位置と通信して、宛先サーバノードにデータをいつ送信するのかを提供することができる。事前に割り当てられた位置は、サーバ集約システムのあらゆる入力ポートからデータを着信するために、ランデブーメモリ及び／又は宛先サーバノードメモリに提供される。これを行う場合、ソースサーバノードメモリからランデブーメモリに、又は、ランデブーメモリから宛先サーバノードメモリにデータを移動させるために、解放されているデータバッファが割り当てられる。ソースサーバノードから送信されることが意図されるデータ用のランデブーメモリにおいて使用可能な位置が存在しない場合には、ランデブーメモリに記憶位置の空きができるまで、データはランデブーメモリに転送されない。また、宛先サーバノードが、データを受信する宛先サーバノードのローカルメモリに使用可能な記憶位置があることをサーバ集約システムに通知するまで、受信データをランデブーメモリに記憶することができる。20

#### 【0025】

他の実施形態では、リモートコンピュータは、外部ネットワーク上のサーバ集約システムへのデータを、外部ネットワークとサーバ集約システムとの間に結合されたNIC又は関連インターフェースに提供する。ここでは、NICは、（例えば、NICの受信リングでの記述子により識別される）ランデブーメモリの受信バッファにデータを転送する。使用可能なバッファが不十分である場合には、データは、脱落又はフィルタリングされる。そうでなければ、受信バッファは使用可能であり、データはランデブーメモリに提供され、ランデブーメモリと通信している処理複合体に通知される。次いで、メモリバッファは検査され、メモリバッファをどこにルーティングするべきか、そしてスイッチングファブリックへの処理複合体接続における記述子上のどこに置くべきかが判定される。この時点で、データは、あたかもそれがイングレスvNICにあるのと同様な方法で移動される。ここでは、ランデブーメモリ管理装置は、宛先サーバノードによって、例えばvNICを介して、宛先サーバノードメモリに空き記憶位置があるかどうか通知される。ランデブーメモリ管理装置は、受信バッファが宛先サーバノードメモリに割り当てられていない限り、宛先サーバノードメモリへの伝送用のデータをフェッチすることはしない。3040

#### 【0026】

従って、本発明の概念の特徴は、データ転送におけるランデブーメモリの入力及び／又は出力領域、すなわち、ソースサーバノードと通信するランデブーメモリの一端と、宛先サーバノードと通信するランデブーメモリのもう一端とで、フロー制御を生じさせることができるということである。また、スイッチファブリックにより実行されるバッファリング（buffering）は、ほとんど又は全く存在しないことから、スイッチファブリックのイングレスポートからエグレスポートへの処理待ち時間が低い。例えば、データトランザクションをスケジューリングすることにより、投機的データ移動が原因となる輻輳50

又はその他のトラヒックに起因するブロッキングのリスクが低減するから、待ち時間を改善することができる。

#### 【0027】

本発明の概念の他の特徴は、バンド幅を、サーバ集約システム内及びサーバノード間で効率的に分配可能であることである。これは、出力することになるデータをソースサーバノードのローカルメモリが有しているかどうか、ランデブーメモリがそのデータを受信できるかどうか、及び／又は、データのメモリ間交換を行っているサーバノードでのローカルメモリが、データを受信するのに充分な空間を有しているかどうかを、サーバ集約システムが実際のデータ転送に先立って判定することができるからである。

#### 【0028】

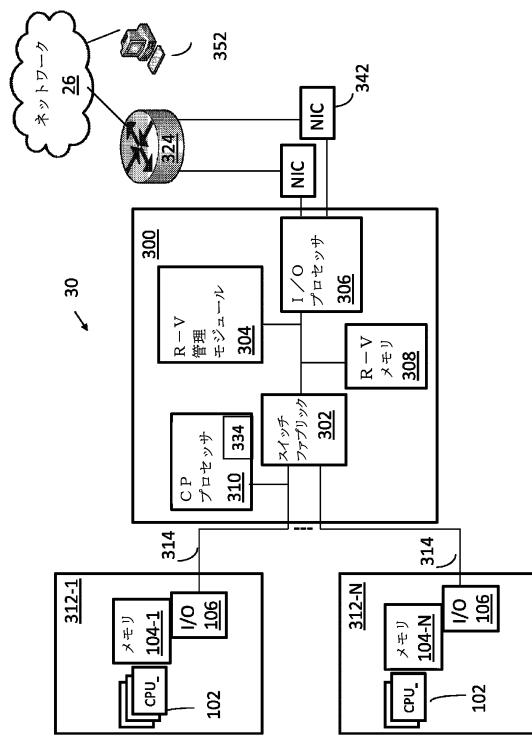

図3は、本実施形態における、ランデブーメモリ（R-Vメモリ）308を有するサーバ集約システム300と通信している複数のサーバノード312-1～312-Nを含む計算インフラストラクチャー30のブロック図である。計算インフラストラクチャー30は、大規模なデータセンタ、クラウド等を含むことができる。計算インフラストラクチャーは、図2を参照して記載されるデータセンタ20と同様の仮想化した構成をとることができる。従って、仮想化関連の構成要素に関する詳細は、簡潔にするために図3では省略される。

10

#### 【0029】

サーバ集約システム300は、スイッチファブリック302と、ランデブー管理モジュール304と、I/Oプロセッサ306と、ランデブーメモリ308と、コントロールプレーンプロセッサ310とを含む。サーバ集約システム300は、仮想化した構成とすることができる。

20

#### 【0030】

サーバノード312-1～312-N（概して、312）、又は、マイクロサーバ及び／若しくは少なくとも一つのプロセッサを有する他の電子デバイスは、コネクター314、好ましくはPCIeバス、又は、他のネットワークコネクターを介して、サーバ集約システム300と通信することができる。各コネクター314は、一つ以上のサーバノード312とサーバ集約システム300との間のデータ経路を提供することができる。サーバ集約システム300及びサーバノード312は、同一のマルチプロセッシングユニット（例えばチップ、計算デバイス又はラック）に一緒に設置されてもよい。他の実施形態では、サーバノード312は、一つ以上のユニット上に形成され、サーバ集約システム300は、独立ユニット上（例えば、チップ上）に形成される。

30

#### 【0031】

スイッチファブリック302は、複数の入力ポート及び出力ポートを含んでおり、データ又は他の電子情報を、その入力ポートと通信するサーバノード312と、そのエグレスポートと通信するランデブーメモリ308との間で移動させる構成とすることができる。スイッチファブリック302は、イングレスポートとエグレスポートとの間でデータを移動させるスイッチング構成（例えば、クロスバー）を含むことができ、このことは当業者には周知である。従来のスイッチファブリックとは異なり、スイッチファブリック302では、従来のキューイング技術が必要ないことから、バッファリングがほとんど又は全く必要ない。スイッチファブリック302及びランデブーメモリ308は、相互接続することができ、それらの間でのI/Oバンド幅通信チャネルを有しており、従って、ランデブーメモリ308にデータ用として割り当てられた充分な空間がある限り、いくつものサーバノード312からのデータも受信することができる。

40

#### 【0032】

ランデブー管理モジュール304は、コントロールプレーンプロセッサ310及びI/Oプロセッサ306とともに、サーバノード312におけるメモリ104-1～104-N（概して、104）の一つ以上とランデブーメモリ308との間のデータパケットの明示的な転送を監視する。ランデブー管理モジュール304は、ランデブーメモリ308にバッファ空間を割り当てて、宛先サーバノード又は外部計算デバイスが、ソースサーバノ

50

ードから送信されたデータをランデブーメモリ 308 から読み出すことができるまで、それを「駐車 (parking)」させておくことができる。ランデブー管理モジュール 304 は、記述子等を使用して、ランデブーメモリ 308 から宛先メモリにデータが伝送される方法を制御することができる。ランデブー管理モジュール 304 は、ランデブーメモリ 308 の受信バッファの空きを監視し、受信バッファがポスト (post) されるまで待機する。換言すれば、ランデブー管理モジュール 304 は、転送操作における一方の当事者（すなわち、ソースサーバノード又はランデブーメモリ）が伝送用データを有すること、転送操作における他方の当事者（すなわち、宛先サーバ又はランデブーメモリ）がデータを受信するのに充分な空間を有していることを保証することができる。

## 【0033】

10

ランデブーメモリ 308 は、複数のネットワークスイッチのリンクと通信する場合には、バンド幅が充分に高い（例えば、10Gb 以上）貫通ビアシリコン (TSV)、SRA M 又はオンダイ (on-die) メモリを含むことができる。ランデブーメモリ 308 は、例えば、メモリのブロックに組織化された解放された複数のデータバッファを含むように構成され得るものであって、これらのデータバッファは、データをローカルメモリ 104 からランデブーメモリ 308 に移動させる場合に、一つ以上の VNIC 334 に割り当てられ得る。

## 【0034】

20

I/O プロセッサ 306 は、ランデブーメモリ 308 と、一つ以上の電子デバイス（例えば、サーバノード 312 及び / 又はリモート計算デバイス 352）との間で転送されたデータを処理する。I/O プロセッサ 306 は、マルチブレクサ、並びに、ランデブーメモリ 308 へのデータ転送及びランデブーメモリ 308 からのデータ転送を実行するその他のロジックを含むことができるが、転送の実行は、ランデブー管理モジュール 304、コントロールプレーンプロセッサ 310 又はそれらの組合せを用いて形成された通信に従ってなされる。このように、I/O プロセッサ 306 は、サーバ集約システム 300 及びサーバ集約システム 300 から（例えば、二つ以上のサーバノード 312 の間、又はサーバノード 312 とリモート計算デバイス 352 の間）データを移動させる集結地 (staging area) としての役割を果たすことができる。

## 【0035】

30

I/O プロセッサ 306 は、使用可能なバッファを示す受信記述子をポストすることによって、ソースサーバノード 312 からの伝送可能状態にあると判定された特定のデータが一時的に（例えば、宛先サーバノード 312 がデータを読み出すまで）記憶されることになるランデブーメモリ 308 におけるバッファを識別することができる。I/O プロセッサ 306 は、ランデブーメモリ 308 からバッファ記述子を処理する VNIC 334 へのデータ移動のために、例えばランデブーメモリ 308 の一つ以上のチャネル用のバッファ記述子を保持することができる。I/O プロセッサ 306 は、受信バッファのリソースを受信記述子に追加する。

## 【0036】

40

コントロールプレーンプロセッサ 310 は、ネットワークルーティングプロトコルを処理することによって、サーバノード 312 とサーバ集約システム 300 との間のデータ送信用のスイッチングコントロールプレーン（図示省略）を管理し、サーバ集約システム 300 等で受信されるデータパケット、フレーム、セル等の転送に関与する。コントロールプレーンプロセッサ 310 の他の機能は、データレディ (data ready) 通知、受信バッファの空き通知、バッファ解放等の生成を含む。コントロールプレーンプロセッサ 310 は、サーバ集約システム 300 内のブロック、ポート及びノードの間の通信を提供することができ、ポート間のデータ移動のためにスイッチファブリック 302 と通信する。コントロールプレーンプロセッサ 310 は、ランデブーメモリ 308 及び / 又は一つ以上のサーバノードメモリ 104 への書き込み及び / 又は読み出しを行うことができる。コントロールプレーンは、使用可能な受信バッファの数を問い合わせるためのデータ可用メッセージ（例えば、送信可能メッセージ）及びバッファ解放メッセージを送信するよう

50

に構成され得る。

#### 【0037】

コントロールプレーンプロセッサ310は、ゼロ又は一つ以上のvNIC334を、好みしくはダイレクトメモリアクセス(DMA)エージェント(agent)(図示省略)、又は、スイッチファブリック302における関連するエージェントと組み合わせて実現及び管理することができる。様々なタイプの通信が、コントロールプレーンプロセッサ310の管理下で、コントロールプレーン上で行われてもよい。例えば、このような通信は、サーバノードインターフェースドライバーから書き込まれ、バッファ記述子メモリ記憶位置の状態の変化を指示する伝送/受信記述子のドアベル(door bell)通知であってもよい。他の例では、コントロールプレーンは、伝送を終えたバッファを、さらなる伝送のために又は受信バッファとして再利用させるなどのバッファ解放メッセージを管理することができる。コントロールプレーンの他の機能は、データレディ通知の提供、バッファ空き通知の受信、及び、バッファ解放等を含むことができる。10

#### 【0038】

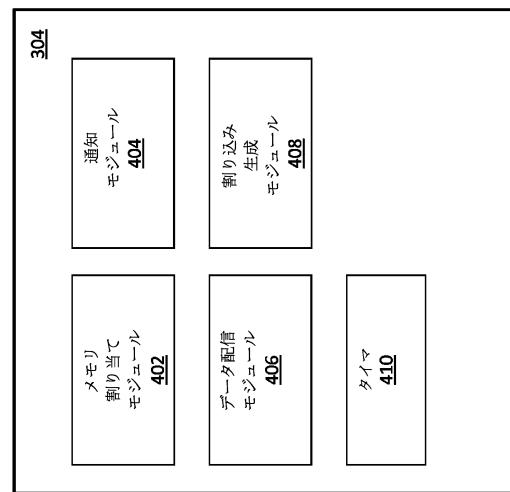

図4は、一実施形態における、図3のランデブー管理モジュール304のブロック図である。ランデブー管理モジュール304は、メモリ割り当てモジュール402、通知モジュール404、データ配信モジュール406、割り込み生成モジュール408及び/又はタイマ410を含むことができる。ランデブー管理モジュール304は、同一デバイス(例えば、チップ、ラック等)の一部として示されている。代替として、ランデブー管理モジュール304のいくつかの構成要素は、図3に示された計算インフラストラクチャー30内の別の位置に物理的に配置することができる。20

#### 【0039】

メモリ割り当てモジュール402は、ソースサーバノード312-1からデータをフェッチするときにvNIC334が使用するバッファ空間を、ランデブーメモリ308内に割り当てる。より詳細には、メモリ割り当てモジュール402は、ランデブーメモリ308のブロックを示すインデックスを提供することができる。このインデックスは、ランデブーメモリの空きデータバッファブロックを示すバッファ記述子を含む。

#### 【0040】

通知モジュール404は、ランデブーメモリ308にデータが入力された場合に、バッファ割り当てに関連した通知を生成する。例えば、通知モジュール404は、バッファを要求するvNIC334に応答して、受信バッファ割り当てをvNIC334に通知することができる。通知モジュール404は、サーバノード312からの伝送用にデータが使用可能であることを示す通知を、例えばvNIC334から受信することができる。通知モジュール404は、ランデブーメモリ308から宛先デバイス用のvNIC334への記述子及び/又はデータをフェッチした後に新規データが使用可能であることを、vNIC334に通知することができる。30

#### 【0041】

データ配信モジュール406は、割り当て用のランデブーメモリ308からvNIC334への記述子、データ等をフェッチすることができる。このvNIC334は、次いでデータを宛先ローカルメモリに提供する。40

#### 【0042】

割り込み生成モジュール408は、新規データがランデブーメモリ308にある場合に、割り込み信号をI/Oプロセッサ306に出力する。これにより、I/Oプロセッサ306は、データをランデブーメモリからブル(pull)し、当該データを提供する。また、割り込み生成モジュール408は、伝送記述子の解放後(例えば、ランデブーメモリ308から宛先ローカルメモリ104-Nにデータを移動させた後)に、割り込み信号をネットワークプロセッサに出力することができる。

#### 【0043】

タイマ410は、受信バッファが、ランデブーメモリ308にてvNIC334への割り当て用に使用可能でない(空きがない)場合に起動し得る。タイマ410は、データを

50

ランデブーメモリ 308 に転送することが不可能であることをサーバ集約システム 300 の構成要素に示し、これにより、フロー制御のレベルを提供する。

#### 【0044】

図 5 は、一実施形態における、図 3 の I/O プロセッサ 306 のブロック図である。I/O プロセッサ 306 は、プロセッサ 502、記述子処理モジュール 504 及び / 又はスケジューラ 508 を含む。I/O プロセッサは、メモリ（図示省略）を含んでもよい。I/O プロセッサ 306 は、同一のデバイス（例えばチップ、ラック等）の一部として示されているが、I/O プロセッサ 306 の構成要素のいくつか又はすべては、図 3 に示された計算インフラストラクチャー 30 の他の構成要素にあってもよい。

#### 【0045】

プロセッサ 502 は、データ出力に関連する構成要素（例えば、NIC 342）とのインターフェースをとるのに使用されるプログラムのプログラムコードを実行することが可能である。プロセッサ 502 は、ルーティングの決定を行い、受信バッファを、受信記述子リングから宛先伝送記述子リングに移動させることができる。

#### 【0046】

記述子処理モジュール 504 は、ソースサーバノード 312 - 1 からデータを受信するランデブーメモリ 308 の空き記憶位置を示す受信記述子を、生成及び / 又はポストすることができる。受信記述子は、ランデブーメモリ 308 において、バッファが常駐する位置、バッファのサイズ、複数のセグメント等を示すことができる。I/O プロセッサ 306 は、現在解放されている（データを受信するのに空いている）データバッファの記述子を、ランデブーメモリ 308 から I/O プロセッサ 306 へ受け渡すことによって、ランデブーメモリ 308 内の使用可能なデータバッファに関する情報を受信することができる。また、記述子処理モジュール 504 は、ランデブーメモリ 308 から宛先サーバノード 312 - N のローカルメモリ 104 - N にデータを転送する命令、分散収集リスト等を含む伝送記述子を生成することができる。

#### 【0047】

スケジューラ 508 は、例えば、NIC 342 若しくは PCIe コネクター 314 を介してサーバ集約システム 300 が新規データを受信するとの通知、又は、宛先デバイスへの伝送用としてランデブーメモリ 308 内で新規データが使用可能であるとの通知を受信した場合に、起動する。スケジューラ 508 は、ランデブーメモリと、一つ以上のサーバノード 312 及び / 又はリモート計算デバイス 352 との間のデータの転送を、例えばラウンドロビンの順、ファーストインファーストアウトの順又は本発明の技術分野で周知の他の順で調整することができる。スケジューラは、所定の方針に従ってデータを転送するよう調整することができる。例えば、方針は、フロー又はポートを優先度付きでタグ付けするメカニズムを含むことができる。I/O プロセッサ 306 は、あるレベルのパケット検査及び分類を実行してフローを差別化することができる。厳格な優先度スケジューラ 508 を実現することができる。代替方法として、スケジューラ 508 は、最小バンド幅割り当てを有する異なるフローを提供することができる。スケジューラ 508 は、サーバ集約システム 300 の vNIC を管理することにより、ある宛先用のデータを選択することができる。

#### 【0048】

図 6 は、一実施形態における、サーバノードと、ランデブーメモリを有するサーバ集約システムとの間で電子通信を行う方法 600 のフロー図である。方法 600 は、図 3 の一つ以上のサーバノード 312 のメモリ 104 及び / 又はサーバ集約システム 300 に記憶された命令に従うことができる。従って、図 2 ~ 5 が参照される。方法 600 のいくつか又はすべてを、ASIC、システムオンチップ（SOC）又は関連するデバイスにて、オンラインで実行することができる。

#### 【0049】

ブロック 602 では、ソースサーバノード 312 - 1 は、セル、パケット、フレーム又は他のローカルメモリ 104 - 1 内のデータのユニットが、宛先（例えば、他のサーバノ

10

20

30

40

50

ード 312-N 又はリモート計算デバイス 352)への NIC342 を介した出力に使用可能であると告知する。ソースサーバノード 312-1 は、伝送用のデータがメモリ 104-1 内にあって伝送用に使用可能であることを、vNIC334 に通知することができる。サーバノード 312 は、データを処理するためにメモリ 104-1 内で定義されているリングバッファ等を維持して、データ伝送又は受信処理を実行することができる。

#### 【0050】

ひし型の判断部 604 では、ランデブーメモリ 308 が、ソースサーバノード 312-1 のメモリ 104-1 内の伝送用データを受信することができるかどうかの判定が行われる。この判定は、ランデブー管理モジュール 304 によって行うことができる。ランデブー管理モジュール 304 は、ソースサーバノード 312-1 から直接的にデータを伝送することができるバッファ空間が、ランデブーメモリ 308 内に空いている（使用可能である）かどうかを確立することができる。ランデブーメモリ 308 がデータを受信することができない場合には、次にブロック 608 において、ランデブー管理モジュール 304 は、受信バッファがポストされるまで待機し得る。一方、ランデブーメモリ 308 がデータを受信することができる場合には、ブロック 606 にて、データ、記述子等を、ソースサーバノード 312-1 のメモリ 104-1 からランデブーメモリ 308 に転送することができる。

#### 【0051】

ひし形の判断部 610 では、I/O プロセッサ 306 は、ソースサーバノード 312-1 からランデブーメモリ 308 に転送されるデータが、宛先サーバノード（例えば、サーバノード 312-N）に転送されることになるかどうかを判定する。この判定は、宛先アドレスに基づいて行われてもよいし、伝送記述子又は宛先ポートを識別するパケットに関するメタ情報をプリpend（prepend）することによって行われてもよい。データを宛先サーバノードに転送しないという判定結果であれば、次にブロック 612 において、I/O プロセッサ 306 がデータを消費することができ、例えば、データは / プロセッサ 306 において終了する。代替方法として、I/O プロセッサ 306 は、データを、データ内容に応じて（例えば、宛先アドレスに基づいて）NIC342 に転送する。例えば、データパケットは、スイッチファブリック 302 を介してフロー管理に関連付けられることができあり、I/O プロセッサ 306 の構成要素、データのルーティングを制御する処理複合体と相互作用する。そうでなければ、ひし型の判断部 614 では、宛先サーバノード 312-N が、ランデブーメモリ 308 から伝送可能な状態のデータを受信するローカルメモリ 104-N に空き空間を有しているかどうかという判定がなされる。この判定は、コントロールプレーンプロセッサ 310 が行うことができ、この場合には、仮想 NIC334 が、宛先ローカルメモリ 104-N においてバッファ空間が空いているかどうかを確定することができる。判断部 614 にて「いいえ」の場合には、ブロック 616 において、ランデブー管理モジュール 304 は、宛先サーバノード CPU102 によって受信バッファがポストされるまで、宛先ローカルメモリ 104-N へのデータ送信を待機することができる。判断部 614 にて「はい」の場合には、ブロック 618 において、ランデブーメモリ 308 にてデータが転送用として使用可能であって、且つ、ランデブーメモリ 308 用に受信バッファが割り当てられた、との判定がなされた場合に、ランデブーメモリ 308 から宛先サーバノードメモリ 104-N にデータを転送することができる。

#### 【0052】

図 7 は、一実施形態における、サーバノードと、ランデブーメモリを有するサーバ集約システムとの間で電子通信を行う方法 700 のフロー図である。方法 700 は、図 3 の一つ以上のサーバノード 312 のメモリ 104 及び / 又はサーバ集約システム 300 に記憶された命令に従うことができる。従って、図 2 ~ 5 が参照される。方法 700 のいくつか又はすべては、ASIC、システムオンチップ（SOC）又は関連する集積回路にて、オンラインで実行することができる。

#### 【0053】

先ず、サーバノード 312-1 は、セル、パケット、フレーム又は他のデータのユニッ

10

20

30

40

50

トがローカルメモリ 104-1 にあって、宛先（例えば、他のサーバノード 312-N）又は NIC342 を介してリモート計算デバイス 352 に出力されるかどうかの判定を行う。ローカルメモリ 104-1 は、データを処理するためのキュー、リングバッファ、リンクされたリスト等を含む。

#### 【0054】

ブロック 702 では、サーバノード 312-1 の CPU102 は、サーバノード 312-1 から出力されるローカルメモリ 104-1 内のデータに関する記述子又は関連情報を生成することができる。記述子は、ランデブーメモリ 308 に転送されるデータに関連したコマンド、分散収集リスト等を含むことができる。関連する記述子情報は、データが常駐するメモリ 104-1 における記憶位置、データが伝送される宛先アドレス、移動させるデータのバイト数、及び / 又は、CPU102 と他のサーバ集約システム 300 における vNIC334 との間で通信を確立するための関連情報を識別することができる。10

#### 【0055】

ブロック 704 では、第 1 のサーバノード 312-1 の CPU102 は、新規記述子がメモリ 104-1 にあって伝送に使用可能であるということを、vNIC334 に通知する。CPU102 は、メールボックス書き込み又は関連イベントの通知を、通信経路 314 を介して vNIC334 に送信することによって、伝送用データの使用可能性を vNIC334 に通知することができる。

#### 【0056】

ブロック 706 では、I/O プロセッサ 306 は、ランデブーメモリ 308 内の使用可能なデータバッファ（空きデータバッファ）を示す受信記述子をポストする。受信記述子は、バッファのアドレス、長さ又は関連情報を含むことができる。20

#### 【0057】

ブロック 708 では、I/O プロセッサ 306 は、vNIC334 用の一つ以上のランデブーメモリバッファの使用可能性（空き状況）を、ランデブー管理モジュール 304 に通知する。

#### 【0058】

ブロック 710 では、コントロールプレーンプロセッサ 310 は、ランデブーメモリ 308 の一つ以上のバッファ記憶位置に vNIC334 用の空きを要求するように、ランデブー管理モジュール 304 にメッセージを送信する。30

#### 【0059】

ブロック 712 では、ランデブー管理モジュール 304 は、ランデブーメモリ 308 に対して、vNIC334 用の一つ以上の受信バッファを割り当てて、vNIC334 が、サーバノードメモリ 104-1 からランデブーメモリ 308 に vNIC334 がデータを転送、コピー又は移動させることができるようとする。ランデブー管理モジュール 304 は、バッファ割り当てに関する通知をコントロールプレーンプロセッサ 310 に送信する。現在空いている受信バッファがない場合には、ランデブー管理モジュール 304 は、受信バッファが空くまで待機することができる。記述子及び / 又はデータは、この待ちの期間にフェッチされない。一実施形態では、入力記述子は、待ち時間を削減するためにプリフェッチ（prefetch）され得る。これは、入力記述子が、転送待ち時間を削減するために多くのメモリ資源を消費するということがないためである。40

#### 【0060】

ブロック 714 では、vNIC334 は、データをフェッチするのに使用されるサーバノードメモリ 104-1 から伝送記述子をフェッチする。vNIC334 は、一つ以上の記述子をフェッチする、又は、フェッチするための一連の記述子に従うことができる。vNIC334 は、サーバノードメモリ 104-1 からの記述子情報（例えば、アドレス）に従ってデータをフェッチし、データを、スイッチファブリック 302 を介して、ランデブー管理モジュール 304 によって割り当てられた空き（使用可能な）ランデブーメモリ 308 に移動させる。例えば、コントロールプレーンプロセッサ 310 は、PCIe コネクター 314 を介してメモリ 104-1 に読み出しを発令し、データをフェッチしてラン50

デブーメモリ 308 に移動させることができる。

**【0061】**

ブロック 716 では、コントロールプレーンプロセッサ 310 は、ランデブー管理モジュール 304 に対して、フェッチされたデータがランデブーメモリ 308 において使用可能であるとの通知を送信することができる。ランデブー管理モジュール 304 は、I/O プロセッサ 306 に伝送される割り込みを生成することができる。これにより、I/O プロセッサ 306 は、データをランデブーメモリ 308 からプル (pull) し、当該データを提供することができる。

**【0062】**

ブロック 718 では、I/O プロセッサ 306 は、ランデブーメモリ 308 内のデータを処理して、例えば、データを消費するかどうか、NIC 342 に当該データを転送するかどうか、又は、計算インフラストラクチャー 30 の一部である他のサーバノード 312 の CPU 102 に当該データを転送するかどうかを判定することができる。

10

**【0063】**

示されてはいないが、コントロールプレーンプロセッサ 310 は、サーバノード 312 - 1 で生成された伝送記述子を解放することができる。コントロールプレーンプロセッサ 310 は、任意に、サーバノード CPU 102 に割り込むことができる。I/O プロセッサ 306 は、例えば、スケジューラ 508 に従って、ランデブーメモリ 308 内のデータの送信を制御することができる。このように、I/O プロセッサ 306 は、その宛先 (例えば、宛先サーバノード 312 - N) へのデータの送信を保証することができ、これは図 8 に記載されるとおりである。

20

**【0064】**

図 8 は、一実施形態における、ランデブースイッチングを行う構成のサーバ集約システムに結合した第 1 及び第 2 のサーバノード間で通信を確立する方法 800 のフロー図である。方法 800 は、サーバ集約システムのネットワークプロセッサによる図 7 のブロック 718 での判定に応じて実行することができる。ネットワークプロセッサは、ランデブーメモリ 308 内の使用可能なフェッチされたデータを、他のサーバノード、又は、CPU を有する関連する電子デバイス (例えば、図 3 に示されたサーバノード 312 - N) に転送する。方法 800 は、図 3 のサーバノード 312 のメモリ 104 及び / 又はサーバ集約システム 300 に記憶された命令により制御することができる。この場合には、図 2 ~ 5 及び図 7 が参照される。

30

**【0065】**

ブロック 802 では、I/O プロセッサ 306 の記述子処理モジュール 504 は、図 7 に記載される方法 700 に従ってランデブーメモリ 308 に移動されるデータに関する記述子又は関連する情報を提供することができる。記述子は、宛先サーバノード 312 - N のローカルメモリ 104 - N にデータを転送する命令、分散収集リスト等を含むことができる。関連する記述子情報は、データが常駐するメモリ 104 - 1 における記憶位置、データが伝送される宛先アドレス、移動させるデータのバイト数、及び / 又は、I/O プロセッサ 306 と、ローカルメモリ 104 - N へのデータの転送に関する VNIC 334 との間で通信を確立する他の関連情報を識別することができる。

40

**【0066】**

ブロック 804 では、I/O プロセッサ 306 は、ランデブーメモリ 308 内のデータが伝送用に使用可能であることを、ランデブー管理モジュール 304 に通知する。

**【0067】**

ブロック 806 では、宛先サーバノード 312 - N の CPU 102 は、宛先サーバノード 312 - N のメモリ 104 - N 内の使用可能なデータバッファ (空きデータバッファ) を示す受信記述子をポストする。受信記述子は、バッファのアドレス、長さ又は関連情報を含むことができる。

**【0068】**

ブロック 808 では、宛先サーバノード 312 - N の CPU 102 は、コントロールブ

50

レーンプロセッサ 310 に対して、メモリ 104-N におけるランデブー管理モジュール 304 用の一つ以上のホストメモリバッファの使用可能性（空き状況）を通知する。

#### 【0069】

ブロック 810 では、宛先サーバノード 312-N 内の CPU102 は、コントロールプレーンプロセッサ 310 に要求を送信して、宛先ノードメモリ 104-N における一つ以上のバッファ記憶位置を空きにするようにランデブー管理モジュール 304 に要求する。

#### 【0070】

ブロック 812 では、コントロールプレーンプロセッサ 310 は、ランデブー管理モジュール 304 用に宛先ノードメモリ 104-N の受信バッファを割り当てて、ランデブー管理モジュール 304 が、ランデブーメモリ 308 から宛先ノードメモリ 104-N へのデータの転送、コピー等を行えるようにする。コントロールプレーンプロセッサ 310 は、バッファ割り当てに関する通知を、ランデブー管理モジュール 304 に送信することができる。現在空いている受信バッファがない場合には、ランデブー管理モジュール 304 は、宛先サーバノードメモリ 104-N の受信バッファが空くまで待機することができる。一実施形態では、記述子及び / 又はデータは、待ち期間の間フェッチされない。

#### 【0071】

ブロック 814 では、ランデブー管理モジュール 304 は、ランデブーメモリ 308 からのデータをフェッチするのに使用される伝送記述子をフェッチする。ランデブー管理モジュール 304 は、ランデブーメモリ 308 からの記述子情報（例えば、アドレス）に従ってデータをフェッチし、データを、スイッチファブリック 302 を介して、vnic6 34 に移動させる。ランデブー管理モジュール 304 は、コントロールプレーンプロセッサ 310 に対して、宛先サーバノード 312-N 用のランデブーメモリ 308 から vNIC334 への記述子及び / 又はデータをフェッチした後に新規データが使用可能であることを、通知することができる。

#### 【0072】

ブロック 816 では、vNIC / CP は、受信バッファ用の記述子をフェッチ及び処理し、データを宛先サーバノードメモリ 104-N に移動させる。コントロールプレーンプロセッサ 310 は、メモリ 104-N に移動したデータを提供するために、宛先サーバノード 312-N の CPU102 に出力される割り込みを生成することができる。ランデブー管理モジュール 304 は、伝送記述子を解放することができ、サーバノード I/O プロセッサ 306 に任意に割り込みすることができる。

#### 【0073】

本明細書に記載の方法の実施形態により、データが宛先に送信できる状態にあるとサーバ集約システム 300 が判定した場合には、要求に応じてデータを転送することができる。ランデブーメモリ 308 がデータを受信できる状態にない場合には、データは宛先に传送されない。これは、仮に、データがソースサーバノード 312-1 において転送できる状態にあってもそうである。同様に、宛先サーバノード 312-N がデータを受信できる状態にない場合には、データは、ランデブーメモリ 308 から伝送されない。このように、従来のキューイング技術を必要とすることなく、バッファ空間がないことに起因してデータが失われるということはない。むしろ、データの移動は記述子の使用可能性と結びついている。記述子が確立される場合には、サーバ集約システム 300 は、移動させることになるデータが存在するとの判定を行うことができる。

#### 【0074】

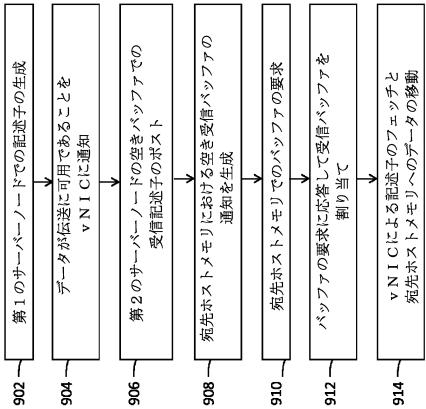

図 9 は、一実施形態における、ランデブースイッチングを行う構成のサーバ集約システムに結合した第 1 及び第 2 のサーバノード間で電子通信する方法 900 のフロー図である。方法 900 は、一つ以上のサーバノード 312 のメモリ 104 及び / 又は上記のサーバ集約システム 300 に記憶された命令により制御することができる。方法 900 の一つ以上の構成要素は、上述したものと同様であってもよい。図 2 ~ 5 が参照されるが、方法 900 は、ランデブーメモリ 308 無しに実行される。特に、ランデブー管理モジュール 3

10

20

30

40

50

04及びコントロールプレーンプロセッサ310は、方法900に関与することができ、この方法では、データ転送が、二つのサーバノード212-1, 212-Nの間で、ランデブーメモリ308の介在無しに行われる。

【0075】

ブロック902では、記述子は、第1のサーバノード312-1で生成される。

【0076】

ブロック904では、vNIC334は、データが伝送用に使用可能であることを通知される。

【0077】

ブロック906では、受信記述子は、第2のサーバノード312-Nの使用可能なバッファ(空きバッファ)でポストされる。 10

【0078】

ブロック908では、宛先サーバノード312-Nは、コントロールプレーンプロセッサ310に対して、ランデブー管理モジュール304用のメモリ104-Nの一つ以上のホストメモリバッファの使用可能性(空き状況)を通知する。

【0079】

ブロック910では、宛先メモリ104-Nのバッファの要求がなされる。

【0080】

ブロック912では、受信バッファが割り当てられる。バッファは、vNIC334用に割り当てることができ、これにより、コントロールプレーンプロセッサ310のvNIC334が、サーバノードメモリ104-1から宛先ノードメモリ104-Nにデータを転送、コピー又は移動させることができる。 20

【0081】

ブロック914では、vNIC334は、受信バッファ用の記述子をフェッチ及び処理して、データを宛先サーバノードメモリ104-Nに移動させる。

【0082】

当業者が認識し得るように、本発明の態様は、システム、方法又はコンピュータプログラム製造物として具体化されてもよい。従って、本発明の態様は、完全にハードウェアの実施形態、完全にソフトウェアの実施形態(ファームウェア、常駐ソフトウェア、マイクロコード等を含む)、又は、ソフトウェア及びハードウェアの態様を組み合わせた実施形態であって、本明細書では「回路」、「モジュール」又は「システム」と称される形態であってもよい。さらには、本発明の態様は、コンピュータプログラム製品の形態であって、一つ以上のコンピュータ可読媒体で具体化されてもよい。コンピュータ可読媒体は、コンピュータ可読プログラムコードを有していてもよい。 30

【0083】

一つ以上のコンピュータ可読媒体のあらゆる組合せが利用できる。コンピュータ可読媒体は、コンピュータ可読信号媒体、又は、コンピュータ可読記憶媒体であってもよい。コンピュータ可読記憶媒体は、例えば、電気的、磁気的、光学的、電磁気的、赤外線であってもよく、半導体システム、装置若しくはデバイスであってもよく、これらのあらゆる好適な組合せであってよいが、これらに限定されるものではない。コンピュータで可読記憶媒体のさらに特定の例(非包括的な列挙)は、以下のものを含む。すなわち、一つ以上の配線を有する電気的接続、ポータブルコンピュータディスクケット、ハードディスク、ランダムアクセスメモリ(RAM)、リードオンリーメモリ(ROM)、イレーザブルプログラマブルリードオンリーメモリ(E PROM若しくはフラッシュメモリ)、光ファイバー、ポータブルコンパクトディスククリードオンリーメモリ(CD-ROM)、光記憶デバイス、磁気記憶デバイス、又は、これらのあらゆる好適な組合せである。本文献の文脈においては、コンピュータ可読記憶媒体は、あらゆる有形の媒体であって、命令実行システム、装置若しくはデバイスにより使用されるプログラム、又は、これらに接続して使用するプログラムを含む又は記憶するものであってもよい。 40

【0084】

コンピュータ可読信号媒体は、その内部で具体化されるコンピュータ可読プログラムコード（例えば、ベースバンド又は搬送波の一部として伝搬されるデータ信号）を含んでいてもよい。このような伝搬信号は、あらゆる多様な形態（例えば、電磁的、光学的又はこれらのあらゆる好適な組合せの形態）をとってもよいが、これらには限定されない。コンピュータ可読信号媒体は、コンピュータで読み取り可能なあらゆる媒体であって、コンピュータ可読記憶媒体ではなく、命令実行システム、装置若しくはデバイスによって使用されるプログラム、又は、これらと接続して使用するプログラムを、通信、伝搬又は移動することが可能な媒体であってもよい。コンピュータ可読媒体上で具体化されるプログラムコードは、あらゆる適切な媒体、例えば、限定はされないが、無線、有線、光ファイバーケーブル、RF等又は前述のあらゆる好適な組合せを用いて伝送することができる。

10

#### 【0085】

本発明の態様の動作を実行するコンピュータプログラムコードは、Java（登録商標）、Smalltalk、C++等のオブジェクト指向プログラミング言語及び「C」プログラミング言語等の従来の手続型言語、又は、同様のプログラミング言語を含む一つ以上のプログラミング言語のあらゆる組合せで記述されていてもよい。プログラムコードは、全部がユーザのコンピュータ上で実行されてもよいし、一部がユーザのコンピュータ上で実行されてもよい。また、プログラムコードは、スタンドアロンのソフトウェアパッケージとして、一部がユーザのコンピュータ上又はリモートコンピュータ上で実行されてもよいし、全部がリモートコンピュータ上又はサーバ上で実行されてもよい。後者のシナリオでは、リモートコンピュータは、ローカルエリアネットワーク（LAN）又はワイドエリアネットワーク（WAN）を含むあらゆるタイプのネットワークを介してユーザのコンピュータに接続されてもよいし、（例えば、インターネットサービスプロバイダを用いたインターネットを介して）外部のコンピュータと接続されてもよい。

20

#### 【0086】

本発明の態様は、本発明の実施形態の方法、装置(システム)及びコンピュータプログラム製品のフローチャート並びに／又はブロック図を参照しつつ記載されている。フローチャート図及び／又はブロック図の各ブロックと、フローチャート図及び／又はブロック図におけるブロックの組合せとは、コンピュータプログラムの命令により実現可能であることは理解されるであろう。コンピュータプログラムのこれらの命令は、汎用コンピュータ、専用コンピュータ、又は、機械を製造する他のプログラマブルデータ処理装置のプロセッサに提供され、これらのコンピュータ又は他のプログラマブルデータ処理装置のプロセッサにおいて実行され、フローチャート及び／又はブロック図のブロックにおいて特定された機能／作用を実現する手段を生成するようにしてもよい。

30

#### 【0087】

また、コンピュータプログラムのこれらの命令は、コンピュータ可読媒体に記憶されてもよく、この媒体が、コンピュータ、他のプログラマブルデータ処理装置、又は、特定の方法で機能する他のデバイスに命令して、コンピュータ可読媒体に記憶された命令によって製品が製造され、その製品に、フローチャート及び／又はブロック図のブロックにおいて特定された機能／作用を実現する命令が含まれるようにしてもよい。さらに、コンピュータプログラムの命令は、コンピュータ、他のプログラマブルデータ処理装置、又は、他のデバイスにロードされて、コンピュータ、他のプログラマブル装置、又は、他のデバイス上で一連の処理ステップを実行させ、コンピュータで実現されるプロセスを生成させ、コンピュータ又は他のプログラマブル装置上で実行されるこれらの命令が、フローチャート及び／又はブロック図のブロックにおいて特定される機能／作用を実現するプロセスを提供するようにしてもよい。

40

#### 【0088】

図におけるフローチャート及びブロック図は、本発明の様々な実施形態によるシステム、方法及びコンピュータプログラム製品の実施可能なアーキテクチャ、機能性及び動作を例示する。この点で、フローチャート又はブロック図における各ブロックは、モジュール、セグメント又はコードの一部を表してもよく、これらは、特定された論理機能を実現す

50

る一つ以上の実行可能な命令を含む。いくつかの代替の実施物では、ブロックで指摘される機能は、図において指摘される順序に従うことなく生じてもよいことも留意されたい。例えば、連続して示された二つのブロックは、実際には、実質的に同時に実行されてもよいし、ブロックは、場合によっては逆順に実行されてもよく、これは関係する機能による。ブロック図及び／又はフローチャートの各ブロックと、ブロック図及び／又はフローチャートにおけるブロックの組合せとは、専用のハードウェア及びコンピュータ命令の特定された機能若しくは作用又は組合せを実行する、専用のハードウェアをベースにしたシステムによって実現されてもよいことも留意されるであろう。

## 【 0 0 8 9 】

特定の実施形態を参照して、本発明を示し記載してきたが、形態及び詳細の様々な変更が、本発明の精神及び範囲を逸脱することなく、当業者により行われてもよいことは理解されるべきである。 10

【 図 1 】

【 図 2 】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

---

フロントページの続き

(72)発明者 マーク ハメル

アメリカ合衆国 02038 マサチューセッツ州、フランクリン、スチュワート ストリート

68

(72)発明者 デイビッド メイヒュー

アメリカ合衆国 01532 マサチューセッツ州、ノースボロー、プレザント ストリート 1

59

(72)発明者 マイケル オズボーン

アメリカ合衆国 03049 ニューハンプシャー州、ホリス、ブラック オーク ドライブ 5

0

審査官 衣鳩 文彦

(56)参考文献 特開平10-229429(JP,A)

特開2005-204089(JP,A)

米国特許出願公開第2005/0041510(US,A1)

米国特許出願公開第2011/0202701(US,A1)

米国特許出願公開第2003/0208631(US,A1)

特開2009-282917(JP,A)

特開平03-082244(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04L 12/931

G06F 15/173