(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2004-538650

(P2004-538650A)

(43) 公表日 平成16年12月24日(2004.12.24)

(51) Int.C1.<sup>7</sup>

**H01L 29/78**

**H01L 21/28**

**H01L 29/417**

F 1

H01L 29/78 301S

H01L 21/28 301S

H01L 29/50 M

テーマコード(参考)

4M104

5F140

審査請求 未請求 予備審査請求 有 (全 73 頁)

(21) 出願番号 特願2003-520006 (P2003-520006)

(86) (22) 出願日 平成14年8月9日 (2002.8.9)

(85) 翻訳文提出日 平成16年2月5日 (2004.2.5)

(86) 國際出願番号 PCT/US2002/025289

(87) 國際公開番号 WO2003/015181

(87) 國際公開日 平成15年2月20日 (2003.2.20)

(31) 優先権主張番号 09/928,124

(32) 優先日 平成13年8月10日 (2001.8.10)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 09/928,163

(32) 優先日 平成13年8月10日 (2001.8.10)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 60/381,320

(32) 優先日 平成14年5月16日 (2002.5.16)

(33) 優先権主張国 米国(US)

(71) 出願人 502215177

スピネカ セミコンダクター、 インコ-

ポレイテッド

アメリカ合衆国 ミネソタ 55344,

エデン プレイリー, マーケット プ

レイス ドライブ 7550

(74) 代理人 100078282

弁理士 山本 秀策

(74) 代理人 100062409

弁理士 安村 高明

(74) 代理人 100113413

弁理士 森下 夏樹

(72) 発明者 スナイダー, ジョン ピー.

アメリカ合衆国 ミネソタ 55439,

エディナ, ロワス レーン 5705

最終頁に続く

(54) 【発明の名称】基板とのショットキーコンタクトを形成する高誘電率ゲート絶縁層、ソースおよびドレインを有するトランジスタ

## (57) 【要約】

本発明は、高基板とともにショットキーコンタクトまたはショットキー状領域を形成する誘電率ゲート絶縁層およびソースおよび/またはドレインの電流の流れをレギュレーションするデバイスおよびその製造方法に関する。1つの局面として、ゲート絶縁層は、シリコンの誘電率より大きい誘電率を有する。他の局面として、電流レギュレーションデバイスは、MOSFETデバイスになり、随意的に2次元P型またはN型MOSFETになり、いくつかの方向性を有し得る。他の局面として、ソースおよび/またはドレインは部分的または全体的にケイ素化合物から成り得る。

【選択図】図4 a

**【特許請求の範囲】****【請求項 1】**

半導体基板を供給するステップと、

半導体基板と接触する電気的絶縁層であって、4.0より大きい誘電率を有する絶縁層を供給するステップと、

少なくとも該絶縁層の一部と接触するゲート電極を供給するステップと、

該半導体基板と接触し、該ゲート電極に隣接するソース電極およびドレイン電極を供給するステップであって、該ソース電極および該ドレイン電極の少なくとも1つが該半導体経路基板とのショットキーコンタクトまたはショットキー状領域を形成する、ステップとを含む、電流をレギュレーションするデバイスの製造方法。

10

**【請求項 2】**

前記ソースおよびドレイン電極が、プラチナシリサイド、パラジウムシリサイドおよびイリジウムシリサイドで構成されるグループの1つから形成される、請求項1に記載の方法。

**【請求項 3】**

前記ソースおよびドレイン電極が、希土類シリサイドで構成されるグループの1つから形成される、請求項1に記載の方法。

**【請求項 4】**

前記絶縁層が、金属酸化物で構成されるグループの一部から形成される、請求項1に記載の方法。

20

**【請求項 5】**

前記絶縁層が、オキシニトリドスタックから形成される、請求項1に記載の方法。

**【請求項 6】**

前記ショットキーコンタクトまたはショットキー状領域が、少なくとも前記チャネルに接したエリアで形成される、請求項1に記載の方法。

**【請求項 7】**

前記ソース電極および前記ドレイン電極の少なくとも1つと前記半導体基板との間の界面全体が、該半導体基板とのショットキーコンタクトまたはショットキー状領域を形成する、請求項1に記載の方法。

30

**【請求項 8】**

前記チャネル領域にドーパントを導入する、請求項1に記載の方法。

**【請求項 9】**

前記絶縁層が、1層より多い層を含む、請求項1に記載の方法。

**【請求項 10】**

前記絶縁層が、酸化金属から構成される前記グループの1つから形成される、請求項2または3に記載の方法。

**【請求項 11】**

前記絶縁層が、オキシニトリドスタックから形成される、請求項2または3に記載の方法。

40

**【請求項 12】**

前記ショットキーコンタクトまたはショットキー状領域が、少なくとも前記チャネルに接するエリアで形成され、ドーパントが、前記チャネル領域に導入される、請求項10に記載の方法。

**【請求項 13】**

前記ショットキーコンタクトまたはショットキー状領域が、少なくとも前記チャネルに接するエリアで形成され、ドーパントが、前記チャネル領域に導入される、請求項11に記載の方法。

**【請求項 14】**

前記半導体基板に接触しているソース電極またはドレイン電極の供給が、約800より低い処理温度で実施される、請求項2または3に記載の方法。

50

**【請求項 15】**

半導体基板を供給するステップと、

該半導体基板に接触している電気的絶縁層を供給するステップであって、該絶縁層が 7 . 6 より大きい誘電率を有するステップと、

少なくとも該絶縁層の一部と接触しているゲート電極を供給するステップと、

該半導体基板と接触し、該ゲート電極に近接するソース電極およびドレイン電極を供給するステップであって、該ソース電極および該ドレイン電極の少なくとも 1 つが該半導体経路基板とのショットキーコンタクトまたはショットキー状領域を形成する、ステップとを含む、電流をレギュレーションするデバイスの製造方法。

**【請求項 16】**

前記ソースおよびドレイン電極が、プラチナシリサイド、パラジウムシリサイドおよびイリジウムシリサイドで構成されるグループの 1 つから形成される、請求項 15 に記載の方法。

**【請求項 17】**

前記ソースおよびドレイン電極が、希土類シリサイドで構成されるグループの 1 つから形成される、請求項 15 に記載の方法。

**【請求項 18】**

前記絶縁層が、金属酸化物で構成されるグループの 1 つから形成される、請求項 15 に記載の方法。

**【請求項 19】**

前記絶縁層が、オキシニトリドスタックから形成される、請求項 15 に記載の方法。

**【請求項 20】**

前記ショットキーコンタクトまたはショットキー状領域が、少なくとも前記チャネルに接したエリアから形成される、請求項 15 に記載の方法。

**【請求項 21】**

前記ソース電極および前記ドレイン電極の少なくとも 1 つと前記半導体基板との間の界面全体が、該半導体基板との、ショットキーコンタクトまたはショットキー状領域を形成する、請求項 15 に記載の方法。

**【請求項 22】**

前記絶縁層が、1 層より多い層を含む、請求項 15 に記載の方法。

**【請求項 23】**

前記チャネル領域にドーパントを導入する、請求項 15 に記載の方法。

**【請求項 24】**

半導体基板を供給するステップと、

該半導体基板に接触している電気的絶縁層であって、1 5 より大きい誘電率を有する絶縁層を供給するステップと、

少なくとも絶縁層の一部と接触しているゲート電極を供給するステップと、

該半導体基板と接触し、該ゲート電極と隣接するソース電極およびドレイン電極を供給するステップであって、該ソース電極および該ドレイン電極の少なくとも 1 つが該半導体経路基板とのショットキーコンタクトまたはショットキー状領域を形成する、ステップとを含む、電流をレギュレーションするデバイスの製造方法。

**【請求項 25】**

前記ソースおよびドレイン電極が、プラチナシリサイド、パラジウムシリサイドおよびイリジウムシリサイドで構成されるグループの 1 つから形成される、請求項 24 に記載の方法。

**【請求項 26】**

前記ソースおよびドレイン電極が、希土類シリサイドで構成されるグループの 1 つから形成される、請求項 24 に記載の方法。

**【請求項 27】**

前記絶縁層が、金属酸化物で構成されるグループの 1 つから形成される、請求項 24 に記

10

20

30

40

50

載の方法。

【請求項 2 8】

前記絶縁層が、オキシニトリドスタックから形成される、請求項 2 4 に記載の方法。

【請求項 2 9】

前記ショットキーコンタクトまたはショットキー状領域が、少なくとも前記チャネルに接したエリアから形成される、請求項 2 4 に記載の方法。

【請求項 3 0】

前記ソース電極および前記ドレイン電極の少なくとも 1 つを前記半導体基板との間の界面全体が、該半導体基板とのショットキーコンタクトまたはショットキー状領域を形成する、請求項 2 4 に記載の方法。

10

【請求項 3 1】

前記チャネル領域にドーパントを導入する、請求項 2 4 に記載の方法。

【請求項 3 2】

前記絶縁層が、1 層より多い層を含む、請求項 2 4 に記載の方法。

【請求項 3 3】

半導体基板を供給するステップと、

該半導体基板に接触している電気的絶縁層であって、4.0 より大きい誘電率を有する絶縁層を供給するステップと、

少なくとも該絶縁層の一部と接触するように配置されたゲート電極を供給するステップと、

20

該ゲート電極に接する 1 つ以上のエリアで該半導体基板を露呈するステップと、

該露呈された半導体基板の少なくとも一部で金属性薄膜を供給するステップと、

該半導体基板でショットキーまたはショットキー状ソース電極およびドレイン電極が形成されるように、該露呈された半導体基板と金属とを反応させるステップと

を含む、電流をレギュレーションするデバイスの製造方法。

【請求項 3 4】

前記ゲート電極が、

前記絶縁層に薄い導電膜の配置するステップと、

ゲート電極を形成するために、該導電膜のパターンニングおよびエッチングするステップと、

30

該ゲート電極の 1 つ以上の側壁に 1 つ以上の薄い絶縁層を形成するステップ

によって供給される

請求項 3 3 に記載の方法。

【請求項 3 5】

前記反応プロセス中に反応していない金属を除去するステップをさらに包含する、請求項 3 3 に記載の方法。

【請求項 3 6】

前記反応させるステップは、熱アニーリングを包含する、反応の請求項 3 3 に記載の方法。

40

【請求項 3 7】

前記ソースおよびドレイン電極が、プラチナシリサイド、パラジウムシリサイドおよびイリジウムシリサイドで構成されるグループの 1 つから形成される、請求項 3 3 に記載の方法。

【請求項 3 8】

前記ソースおよびドレイン電極が、希土類シリサイドで構成されるグループの 1 つから形成される、請求項 3 3 に記載の方法。

【請求項 3 9】

前記絶縁層が、金属酸化物で構成されるグループの 1 つから形成される、請求項 3 3 に記載の方法。

【請求項 4 0】

50

前記絶縁層が、オキシニトリドスタックから形成される、請求項 3 3 に記載の方法。

【請求項 4 1】

前記ショットキーコンタクトまたはショットキー状領域が、少なくとも前記チャネルに接したエリアから形成される、請求項 3 3 に記載の方法。

【請求項 4 2】

前記ソース電極および前記ドレイン電極の少なくとも 1 つと前記半導体基板との間の界面全体が、該半導体基板とのショットキーコンタクトまたはショットキー状領域を形成する、請求項 3 3 に記載の方法。

【請求項 4 3】

前記チャネル領域にドーパントを導入する、請求項 3 3 に記載の方法。

10

【請求項 4 4】

半導体基板を供給するステップと、

該半導体基板に接触している電気的絶縁層であって、7.6 より大きい誘電率を有する絶縁層を供給するステップと、

少なくとも該絶縁層の一部と接触するように配置されたゲート電極を供給するステップと、

該ゲート電極に接する 1 つ以上のエリアで該半導体基板を露呈するステップと、

該露呈された半導体基板の少なくとも一部で金属性薄膜を供給するステップと、

該半導体基板でショットキーまたはショットキー状ソース電極およびドレイン電極が形成されるように、該露呈された半導体基板と該金属とを反応させるステップと

20

を含む、電流をレギュレーションするデバイスの製造方法。

【請求項 4 5】

前記ゲート電極が、

前記絶縁層に薄い導電膜を配置するステップと、

ゲート電極を形成するために、該導電膜をパターンニングおよびエッチングするステップと、

該ゲート電極の 1 つ以上の側壁に 1 つ以上の薄い絶縁層を形成するステップ

によって供給される、

請求項 4 4 に記載の方法。

【請求項 4 6】

前記反応プロセス中の反応していない金属の除去をさらに包含する、請求項 4 4 に記載の方法。

30

【請求項 4 7】

前記反応させるステップは、熱アニーリングを包含する、反応の請求項 4 4 に記載の方法。

【請求項 4 8】

前記ソースおよびドレイン電極が、プラチナシリサイド、パラジウムシリサイドおよびイリジウムシリサイドで構成されるグループの 1 つから形成される、請求項 4 4 に記載の方法。

【請求項 4 9】

前記ソースおよびドレイン電極が、希土類シリサイドで構成されるグループの 1 つから形成される、請求項 4 4 に記載の方法。

【請求項 5 0】

前記絶縁層が、金属酸化物で構成されるグループの 1 つから形成される、請求項 4 4 に記載の方法。

【請求項 5 1】

前記絶縁層が、オキシニトリドスタックから形成される、請求項 4 4 に記載の方法。

【請求項 5 2】

前記ショットキーコンタクトまたはショットキー状領域が、少なくとも前記チャネルに接したエリアで形成される、請求項 4 4 に記載の方法。

50

**【請求項 5 3】**

前記ソース電極および前記電極の少なくとも 1 つと前記半導体基板との間の界面全体が、該半導体基板とのショットキーコンタクトまたはショットキー状領域を形成する、請求項 4 4 に記載の方法。

**【請求項 5 4】**

前記チャネル領域にドーパントを導入する、請求項 4 4 に記載の方法。

**【請求項 5 5】**

半導体基板を供給するステップと、

該半導体基板に接触している電気的絶縁層であって、15より大きい誘電率を有する絶縁層を供給するステップと、

少なくとも該絶縁層の一部と接触するように配置されたゲート電極を供給するステップと、

該ゲート電極に接する 1 つ以上のエリアで該半導体基板を露呈するステップと、該露呈された半導体基板の少なくとも一部で金属性の薄膜を供給するステップと、該半導体基板でショットキーまたはショットキー状ソース電極およびドレイン電極が形成されるように、該露呈された半導体基板と金属とを反応させるステップとを含む、電流をレギュレーションするデバイスの製造方法。

**【請求項 5 6】**

前記ゲート電極が

前記絶縁層に薄い導電膜を配置するステップと、

ゲート電極を形成するために、該導電膜をパターンニングおよびエッチングするステップと、

前記ゲート電極の 1 つ以上の側壁に 1 つ以上の薄い絶縁層を形成するステップによって供給される、

請求項 5 5 に記載の方法。

**【請求項 5 7】**

前記反応プロセス中の反応していない金属を除去するステップをさらに包含する、請求項 5 5 に記載の方法。

**【請求項 5 8】**

前記反応させるステップは、熱アニーリングを包含する、反応の請求項 5 5 に記載の方法。

**【請求項 5 9】**

前記ソースおよびドレイン電極が、プラチナシリサイド、パラジウムシリサイドおよびイリジウムシリサイドで構成されるグループの 1 つから形成される、請求項 5 5 に記載の方法。

**【請求項 6 0】**

前記ソースおよびドレイン電極が、希土類シリサイドで構成されるグループの 1 つから形成される、請求項 5 5 に記載の方法。

**【請求項 6 1】**

前記絶縁層が、金属酸化物で構成されるグループの 1 つから形成される、請求項 5 5 に記載の方法。

**【請求項 6 2】**

前記絶縁層が、オキシニトリドスタッカから形成される、請求項 5 5 に記載の方法。

**【請求項 6 3】**

前記ショットキーコンタクトまたはショットキー状領域が、少なくとも前記チャネルに接したエリアで形成される、請求項 5 5 に記載の方法。

**【請求項 6 4】**

前記ソース電極および前記ドレイン電極の少なくとも 1 つと前記半導体基板との間の界面全体が、該半導体基板とのショットキーコンタクトまたはショットキー状領域を形成する、請求項 5 5 に記載の方法。

**【請求項 6 5】**

前記チャネル領域にドーパントを導入する、請求項 5 5 に記載の方法。

**【請求項 6 6】**

半導体基板と、

ゲート電極と、

該ゲート電極と該半導体基板の間で配置される電気的絶縁層であって、4.0 より大きい誘電率を有する絶縁層と、

半導体基板と接触し、該ゲート電極に接するソース電極およびドレイン電極であって、該ソース電極および該ドレイン電極の 1 つが、該半導体基板とのショットキーコンタクトまたはショットキー状領域を形成する、ソース電極およびドレイン電極と

10 を含む、電流をレギュレーションするデバイス。

**【請求項 6 7】**

前記ソースおよびドレイン電極が、プラチナシリサイド、パラジウムシリサイドおよびイリジウムシリサイドで構成されるグループの 1 つから形成される、請求項 6 6 に記載のデバイス。

**【請求項 6 8】**

前記ソースおよびドレイン電極が、希土類シリサイドで構成されるグループの 1 つから形成される、請求項 6 6 に記載のデバイス。

**【請求項 6 9】**

前記絶縁層が、金属酸化物で構成されるグループの 1 つから形成される、請求項 6 6 に記載のデバイス。

20

**【請求項 7 0】**

前記絶縁層が、オキシニトリドスタックから形成される、請求項 6 6 に記載のデバイス。

**【請求項 7 1】**

前記ショットキーコンタクトまたはショットキー状領域が、少なくとも前記チャネルに接したエリアにある、請求項 6 6 に記載のデバイス。

**【請求項 7 2】**

前記ソース電極および前記ドレイン電極の 1 つと前記半導体基板との間の界面全体が、該半導体基板とのショットキーコンタクトまたはショットキー状領域を形成する、請求項 6 6 に記載のデバイス。

30

**【請求項 7 3】**

前記チャネル領域が、ドーピングされている、請求項 6 6 に記載のデバイス。

**【請求項 7 4】**

前記絶縁層が 1 つ以上の層を含む、請求項 6 6 に記載のデバイス。

**【請求項 7 5】**

前記絶縁層が、金属酸化物から構成されるグループの 1 つから形成される、請求項 6 7 または 6 8 に記載のデバイス。

40

**【請求項 7 6】**

前記絶縁層が、オキシニトリドスタックから形成される、請求項 6 7 または 6 8 に記載のデバイス。

**【請求項 7 7】**

前記ショットキーコンタクトまたはショットキー状領域が、少なくとも前記チャネルに接したエリアで形成され、前記チャネル領域が、ドーピングされている、請求項 7 5 に記載のデバイス。

**【請求項 7 8】**

前記ショットキーコンタクトまたはショットキー状領域が、少なくともチャネルに接したエリアで形成され、前記チャネル領域が、ドーピングされている、請求項 7 6 に記載のデバイス。

**【請求項 7 9】**

半導体基板と、

ゲート電極と、

該ゲート電極と該半導体基板との間に配置される電気的絶縁層であって、7.6より大きい誘電率を有する絶縁層と

該半導体基板と接触し、該ゲート電極に隣接しているソース電極およびドレイン電極であって、該ソース電極および該ドレイン電極の少なくとも1つが該半導体基板とのショットキーコンタクトまたはショットキー状領域を形成する、ソース電極およびドレイン電極とを含む、電流をレギュレーションするデバイス。

【請求項80】

前記ソースおよびドレイン電極が、プラチナシリサイド、パラジウムシリサイドおよびイリジウムシリサイドで構成されるグループの1つから形成される、請求項79に記載のデバイス。

【請求項81】

前記ソースおよびドレイン電極が、希土類シリサイドで構成されるグループの1つから形成される、請求項79に記載のデバイス。

【請求項82】

前記絶縁層が、金属酸化物で構成されるグループの1つから形成される、請求項79に記載のデバイス。

【請求項83】

前記絶縁層が、オキシニトリドスタックから形成される、請求項79に記載のデバイス。

【請求項84】

前記ショットキーコンタクトまたはショットキー状領域が、少なくとも前記チャネルに接したエリアにある、請求項79に記載のデバイス。

【請求項85】

前記ソース電極および前記ドレイン電極の少なくとも1つと前記半導体基板との間の界面全体が、該半導体基板とのショットキーコンタクトまたはショットキー状領域を形成する、請求項79に記載のデバイス。

【請求項86】

前記チャネル領域が、ドーピングされている、請求項79に記載のデバイス。

【請求項87】

前記絶縁層が1つ以上の層を含む、請求項79に記載のデバイス。

【請求項88】

半導体基板と、

ゲート電極と、

該ゲート電極と該半導体基板との間に配置される電気的絶縁層であって、15より大きい誘電率を有する該絶縁層と、

該半導体基板と接触し、該ゲート電極に隣接するソース電極およびドレイン電極であって、該ソース電極および該ドレイン電極の少なくとも1つが、該半導体基板とのショットキーコンタクトまたはショットキー状領域を形成する、ソース電極およびドレイン電極とを包む、電流をレギュレーションするデバイス

【請求項89】

前記ソースおよびドレイン電極が、プラチナシリサイド、パラジウムシリサイドおよびイリジウムシリサイドで構成されるグループの1つから形成される、請求項88に記載のデバイス。

【請求項90】

前記ソースおよびドレイン電極が、希土類シリサイドで構成されるグループの1つから形成される、請求項88に記載のデバイス。

【請求項91】

前記絶縁層が、金属酸化物で構成されるグループの1つから形成される、請求項88に記載のデバイス。

【請求項92】

10

20

30

40

50

前記絶縁層が、オキシニトリドスタックから形成される、請求項 8 8 に記載のデバイス。

【請求項 9 3】

前記ショットキーコンタクトまたはショットキー状領域が、少なくとも前記チャネルに接したエリアにある、請求項 8 8 に記載のデバイス。

【請求項 9 4】

前記ソース電極および前記ドレイン電極の少なくとも 1 つと前記半導体基板との間の界面全体が、該半導体基板とのショットキーコンタクトまたはショットキー状領域を形成する、請求項 8 8 に記載のデバイス。

【請求項 9 5】

前記チャネル領域が、ドーピングされている、請求項 8 8 に記載のデバイス。 10

【請求項 9 6】

前記絶縁層が 1 つ以上の層を含む、請求項 8 8 に記載のデバイス。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

(関連出願の相互参照)

本出願は、2001年8月10日出願の米国特許出願番号第 09/928,124 号、および 2001 年 8 月 10 日出願の米国特許出願番号第 09/928,163 号の一部継続出願である。本出願は、2002 年 5 月 16 日に出願の米国仮特許出願番号第 60/381,320 号の優先権をさらに主張し、全体において参照として採用される。 20

【0 0 0 2】

本発明は、電流量をレギュレーションするデバイスとこれらの製造方法とに関する。より具体的にいうと、本発明は、ショットキーバリアソースおよび / またはドレイントランジスタに関する。

【背景技術】

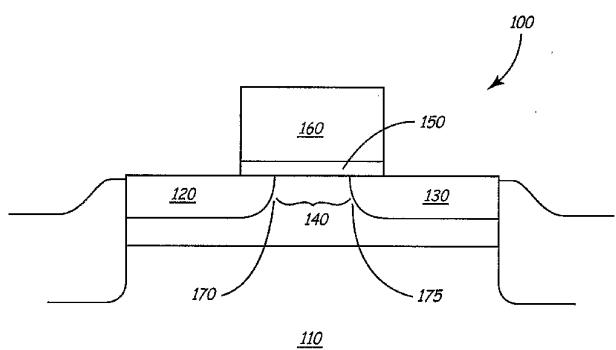

【0 0 0 3】

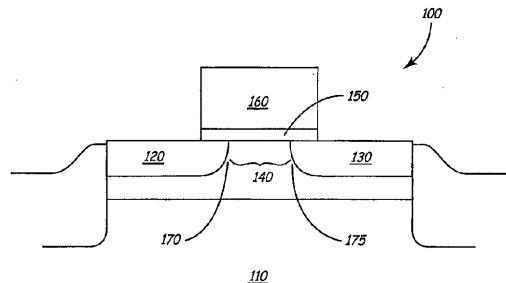

従来技術の図 1 で見られる、半導体デバイス 100 ( 例えばトランジスタ ) のような電流量レギュレーションデバイスは、不純物ドープソース 120 および不純物ドープドレイン 130 を有するシリコン基板 110 を含み得る。ソース 120 およびドレイン 130 は、チャネル領域 140 によって分離されている。チャネル領域 140 の上に絶縁層 150 がある。絶縁層 150 は、典型的に 3.9 の誘電率を有する二酸化シリコンからなる。導電性材料で作られたゲート電極 160 は、絶縁層 150 の上に配置される。 30

【0 0 0 4】

電圧  $V_G$  がゲート電極 160 に印加されたとき、チャネル領域 140 を介してソース 120 とドレイン 130 との間に電流が流れる。この電流は、駆動電流、または  $I_D$  と呼ばれる。デジタル用途で、半導体デバイス 100 を「 on 」にするために電圧  $V_G$  がゲート電極 160 に印加され得る。この状態において、半導体デバイスは、比較的大きな駆動電流を有し、この電流は、理想的にチャネル領域 140 の抵抗値によってのみ限定される。半導体デバイス 100 を「 off 」にするために、異なる電圧  $V_G$  が、ゲート電極 160 に印加され得る。この状態において、理想的な漏れ電流はゼロである。しかしながら、実際の利用では、半導体デバイス 100 の他の部分に関連する寄生インピーダンスのため、「 on 」の状態の駆動電流は理想的でない。例えば、ソースおよびドレイン領域は、有限インピーダンスを有し、結果として、チャネル領域の抵抗値に寄生インピーダンスが加えられる。また、実際の利用では、半導体デバイスが「 off 」のとき、ある程度の有限な量の漏れ電流がある。 40

【0 0 0 5】

従来技術の電流レギュレーションデバイスにおいて、駆動電流は、絶縁層 150 の誘電率  $K$  と線形的に比例し、絶縁層 150 の厚さ  $T_{ins}$  に線形的に反比例する。駆動電流  $I_D$  は、以下の関係式によって近似される。

【0 0 0 6】

$I_D \sim K / T_{ins}$

ここで  $K$  は、絶縁層の誘電率であり、 $T_{ins}$  は、絶縁層の厚さである。

【0007】

電流レギュレーションデバイスの設計においての検討事項は、所望の駆動電流を達成するために要求される電力量を低減することである。電力消費を低減する1つの方法は、本明細書中で参照として採用される「METHOD OF MANUFACTURING A SHORT-CHANNEL FET WITH SCHOTTKY BARRIER SOURCE AND DRAIN CONTACTS」と題された1999年12月16日に出願された同時係属米国特許出願の第09/465,357号および「MOSFET DEVICE AND MANUFACTURING METHOD」と題された2001年2月6日に出願された同時係属米国特許出願の第09/777,536号で記載されるような金属ソースおよびドレインと単純かつ均一に移植されたチャネルドーパントプロファイルの使用することである。

10

【0008】

電流レギュレーションデバイスの設計における他の検討事項は、生産性である。電流レギュレーションデバイスの生産性の改善の方法の1つは、本明細書中で参照として採用される「LOW TEMPERATURE SOURCE AND DRAIN FORMATION PROCESS STEPS FOR THE MANUFACTURE OF MOSFET DEVICES」と題された2002年5月16日に出願された米国仮特許出願の第60/381,320号に記載されているような、ショットキーまたはショットキー状ソースおよびドレイン電極の形成に利用されるような低温度処置を利用したソースおよびドレイン電極を形成することである。

20

【発明の開示】

【発明が解決しようとする課題】

【0009】

当該分野において、「on」状態における改善された駆動電流を示す電流量レギュレーション用のデバイスが必要である。当該分野において、低下した温度でそのようなデバイスを製造する方法がさらに必要である。

【課題を解決するための手段】

【0010】

本明細書中で開示された発明の利用によって、駆動電流特性は、改善され得、その結果として駆動電流  $I_D$  と絶縁層の誘電率 ( $K$ ) および絶縁層の厚さ  $T_{ins}$  の両方との間に非線形関係が生じる。その結果の関係は、電流レギュレーションデバイスが、従来技術と比較して  $K$  および  $T_{ins}$  の変動に対してより影響を受けやすいという結果になる。さらに、本明細書中に開示される発明の利用によって、新しいゲート絶縁体材料の生産性は、実質的に改善される。

30

【0011】

ある局面として、本発明は、電流量レギュレーション用のデバイスの製造方法を提供する。その方法は、半導体基板を提供するステップ、半導体基板に接触している電気的絶縁層であって、4.0より大きい誘電率を有する電気的絶縁層を提供するステップ、少なくとも絶縁層の一部に接触しているゲート電極を提供するステップ、および半導体基板に接触し、かつゲート電極に近接しているソース電極およびドレイン電極を提供するステップを包含し、ソース電極およびドレイン電極の少なくとも1つが、半導体基板とのショットキーコンタクトまたはショットキー状領域を形成する。ある局面としては、電流量をレギュレーションするデバイスは、金属酸化物半導体電界効果トランジスタ (MOSFET) デバイスであり得る。他の局面として、誘電率は、7.6より大きく、または15より大きくあり得る。

40

【0012】

他の局面として、ソースおよびドレイン電極が、プラチナシリサイド、パラジウムシリサイドおよびイリジウムシリサイドで構成されるグループの1つから形成され得る。他の局

50

面として、ソースおよびドレイン電極が、希土類シリサイドで構成されるグループの1つから形成され得る。他の局面として、絶縁層が、酸化金属で構成されるグループの1つから形成され得る。他の局面として、ショットキーコンタクトまたはショットキー状領域が、少なくともチャネルに接したエリアにあり得る。他の局面として、ソース電極およびドレイン電極の少なくとも一方と半導体基板との間の界面全体が、半導体基板とのショットキーコンタクトまたはショットキー状領域を形成し得る。他の局面として、チャネル領域は、ドーピングされ得る。

#### 【0013】

他の局面として、本発明は、電流をレギュレーションするデバイスの製造方法を提供する。その方法は、半導体基板を提供するステップ、半導体基板に接触している電気的絶縁層であって、4.0より大きい誘電率を有する絶縁層を提供するステップ、少なくとも絶縁層の一部と接触するように配置されたゲート電極を提供するステップ、1つ以上のゲート電極に近接したエリアで半導体基板を露呈するステップ、露呈された半導体基板の少なくとも一部に金属性薄膜を提供するステップ、ならびにショットキーまたはショットキー状ソース電極およびドレイン電極が半導体基板上で形成されるような露呈された半導体基板と金属を反応させるステップを含む。ある局面として、電流量レギュレーションデバイスは、MOSFETデバイスであり得る。他の局面として、誘電率は、7.6より大きくまたは15より大きくなり得る。

#### 【0014】

他の局面として、ゲート電極は、絶縁層上に薄い導電膜を配置するステップ、ゲート電極を形成するために導電膜をパターンニングおよびエッチングするステップ、およびゲート電極の1つ以上の側壁上に1つ以上の薄い絶縁層を形成するステップによって提供され得る。他の局面として、その方法は、反応プロセス中に反応しなかった金属を除去するステップを含み得る。他の局面として、反応するステップは、熱アーニングを含み得る。他の局面として、ソースおよびドレイン電極は、プラチナシリサイド、パラジウムシリサイドおよびイリジウムシリサイドで構成されるグループの1つから形成され得る。他の局面として、ソースおよびドレイン電極が、希土類シリサイドで構成されるグループの1つから形成され得る。他の局面として、絶縁層が、金属酸化物で構成されるグループの1つから形成され得る。他の局面として、ショットキーコンタクトまたはショットキー状領域が、少なくともチャネルに接したエリアで形成され得る。他の局面として、ソース電極およびドレイン電極の少なくとも一方と半導体基板との間の界面全体が、半導体基板とのショットキーコンタクトまたはショットキー状領域を形成し得る。他の局面として、ドーパントは、チャネル領域に導入され得る。

#### 【0015】

他の局面として、本発明は、電流をレギュレーションするデバイスを提供する。このデバイスは、半導体基板、ゲート電極、ゲート電極と半導体基板との間で配置される電気的絶縁層であって、4.0以上の誘電率を有する絶縁層、ならびに半導体基板と接触し、かつゲート電極と隣接するソース電極およびドレイン電極を含み、ソース電極およびドレイン電極の少なくとも一方は、半導体基板とのショットキーコンタクトまたはショットキー状領域を形成する。ある局面としては、電流量をレギュレーションするデバイスは、金属酸化物半導体電界効果トランジスタ(MOSFET)デバイスであり得る。他の局面として、誘電率は、7.6より大きく、または15より大きくあり得る。

#### 【0016】

他の局面として、ソースおよびドレイン電極は、プラチナシリサイド、パラジウムシリサイドおよびイリジウムシリサイドで構成されるグループの1つから形成され得る。他の局面として、ソースおよびドレイン電極が、希土類シリサイドで構成されるグループの1つから形成され得る。他の局面として、絶縁層が、金属酸化物の1つから形成され得る。他の局面として、ショットキーコンタクトまたはショットキー状領域が、少なくともチャネルに接したエリアで形成され得る。他の局面として、ソース電極およびドレイン電極の少なくとも一方と半導体基板との間の界面全体が、該半導体基板とのショットキーコンタクト

10

20

30

40

50

トまたはショットキー状領域を形成し得る。他の局面として、チャネル領域は、ドープされ得る。

【0017】

本発明の局面は、1つ以上の下記の利点を含み得る。従来の電界効果トランジスタ(FET)および他の電流レギュレーションデバイスは、ソースからドレインへ同様の駆動電流を生成するために本発明により製造されたものより高電圧を必要とする。従来のFETまたは電流レギュレーションデバイスの最大限の利用において、絶縁層の誘電率のその厚さに対する比と駆動電流は、一般的に線形的に変化する。本発明の利点の1つは、 $T_{i_{n_s}}$ より誘電率Kに対して駆動電流が影響を受け、より大きいKと $K/T_{i_{n_s}}$ との比に対してより大きい駆動電流 $I_D$ を導くという予期せぬ結果である。この結果は、ショットキーまたはショットキー状ソースおよび/またはドレインを高誘電率材料でできた絶縁層と結合することで達成される。より低電圧は、この構造を利用した超小型電子技術にとってより

低電力消費をもたらすソースからドレインへの高電流生成のために必要とされる。

【0018】

さらに、より大きいKと定数 $K/T_{i_{n_s}}$ 比の利用により、より少ないゲートの漏れ電流が達成されるという周知の利点は、本発明においても観察される。従来の構造のデバイスにとって、この特定の利点は、3.9の誘電率を有する二酸化シリコンの誘電率より大きい誘電率Kを有するゲート絶縁体の材料使用が唯一の理由である。これらの材料は、材料「ハイK」として示される。他に予想されるまたは観察される重要な利点はない。より大きいKとの組合わせるショットキーまたはショットキー状ソース/ドレインデバイスの使用によって、駆動電流 $I_D$ における予想されない、および劇的な改善が、ゲート漏れ電流の縮減に加えて達成される。

【0019】

ゲート漏れ電流の問題のために新しいハイKゲート絶縁体材料を使用することは、産業に大きな刺激を与えるにもかかわらず、ハイKゲート絶縁体の製造を困難にする技術的障害がある。最も重要な問題の1つは、不純物ドープソースおよびドレイン領域の形成のために必要とされる高温処理の間のハイKゲート絶縁体材料の劣化である。この劣化は、チャネル領域またはゲート電極におけるシリコンのような隣接する材料との反応によって引き起こされる。ショットキーまたはショットキー状ソース/ドレイン領域の形成のための処理工程は、不純物をソースおよびドレインにドーピングするために必要な1000と比較して400のようなかなり低い温度で生じる。ショットキーまたはショットキー状ソース/ドレイン領域の形成のための著しく低い温度の処理工程の結果として、ハイK材料は、実質的に隣接する材料と反応しない。このため、ハイKゲート絶縁材料と組み合わされたショットキーまたはショットキー状ソース/ドレインデバイスの使用の他の利点は、ハイKゲート絶縁体の生産性の改善である。

【0020】

多様な実施形態が、開示されるが、本発明のさらに他の実施形態は、本発明の実施形態の例を示し、かつ説明する下記の詳細な記載から当業者に明白になる。理解されるように、本発明の意図および範囲から逸脱することなく、本発明は、様々な明らかな局面において変更が可能である。したがって、図面や詳細な記載は、本質的に例であり、かつ制限されないものとして評価されるべきである。

【0021】

様々な図面において、同様の参照記号は、同様の要素を指し示す。

【発明を実施するための最良の形態】

【0022】

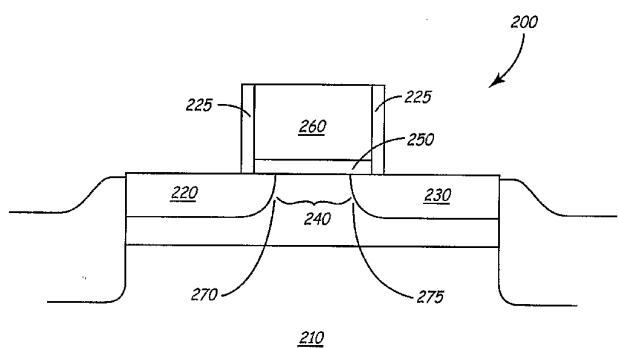

図2を参照すると、半導体デバイス200は、ソース220、およびドレイン230が形成される基板210を含む。基板210は、シリコンで構成されてもよいし、シリコンオノインシュレーター(SOI)基板であってもよい。ソース220、および/またはドレイン230は、希土類シリサイドで部分的、または全体的に構成され得る。ソース220お

10

20

30

40

50

よび／またはドレイン 230 はまた、プラチナシリサイド、パラジウムシリサイドまたはイリジウムシリサイドで部分的または、全体的に構成され得る。ソースおよびドレインは一部、金属で構成されているため、これらは、基板 210 とともにショットキーコンタクトまたはショットキー状領域 270、275 を形態とる。ここで、「ショットキーコンタクト」は、金属と半導体の間の接触によって規定され、「ショットキー状領域」は、半導体と金属とが密接することによって形成される領域である。ショットキーコンタクトまたはショットキー状領域 270、275 は、ソースおよび／またはドレインを金属シリサイドから形成することによって形成され得る。ショットキーコンタクトまたはショットキー状領域 270、275 は、ソース 220 およびドレイン 230 の間で形成されるチャネル領域 240 に隣接するエリアにある。ソース 220 およびドレイン 230 のどちらか一方または両方の全境界は、基板 210 とともにショットキーコンタクトまたはショットキー状領域 270、275 を形成し得る。チャネル領域 240 は、不純物のドーピングをされ得る。このドーピングは、従来の非均一性ドーピングであってもよく、同時係属の米国特許出願第 09/465,357 号と米国特許出願第 09/777,536 号で記載されている均一性ドーピングであってもよい。

10

20

30

40

## 【0023】

絶縁層 250 は、チャネル領域 240 の上に形成され、ソース 220 およびドレイン 230 の一部または全体の上に形成されてもよい。絶縁層 250 は、二酸化シリコンの誘電率より誘電率が大きい材料で構成される（例えば、3.9 より大きい誘電率）。例えば、絶縁層 250 は、誘電率が約 25 の  $TaO_2$ 、誘電率が約 50 ~ 60 の  $TiO_2$ 、誘電率が約 15 ~ 20 の  $HfO_2$ 、または誘電率が約 15 ~ 20 の  $ZrO_2$  のような金属酸化物によって構成されてもよい。絶縁層 250 は、ニトリド／オキシドまたはオキシナイトライドスタックのような低（modest）K 値（例えば 5 ~ 10）、単一酸化剤  $Ta_2O_3$ 、 $TiO_2$ 、 $ZrO_2$ 、 $HfO_2$ 、 $Y_2O_3$ 、 $La_2O_3$ 、 $Gd_2O_3$ 、 $Sc_2O_3$  または、珪酸塩  $ZrSiO_4$ 、 $HfSiO_4$ 、 $LaSiO_4$ 、または  $TiSiO_4$  のような中間の K 値（例えば 10 ~ 20）あるいは、アモルファス  $LaAlO_3$ 、 $ZrTiO_4$ 、 $SnTiO_4$ 、 $SrZrO_4$ 、または単結晶  $LaAl_3O_4$ 、 $BaZrO_3$ 、 $Y_2O_3$ 、 $La_2O_3$  のようなハイ K 値（例えば 20 より大きい）を有する誘導体から構成され得る。随意的に、遷移金属に関する生産性の問題を改善するために、絶縁層 250 は、1つより多い層から構成されてもよい。絶縁層 250 は、「2重層」アプローチで形成されてもよく、1種類より多い誘電体（例えば、 $Si_3N_4$  上の  $TiO_2$ ）で形成されてもよい。ゲート電極 260 は、絶縁層 250 の上に配置される。薄い絶縁層 225 は、ゲート電極 260 を取り囲んでいる。

50

## 【0024】

(1) ショットキーコンタクトまたはショットキー状領域 270、275 を基板 110 と共に形成するソース 220 またはドレイン 230 および (2) 比較的高い誘電率の絶縁層 250 を伴う半導体デバイスの形成によって、 $K/T_{ins}$  は、一定であるが、より大きな K に対してより大きい駆動電流  $I_D$  を達成することが可能である。

50

## 【0025】

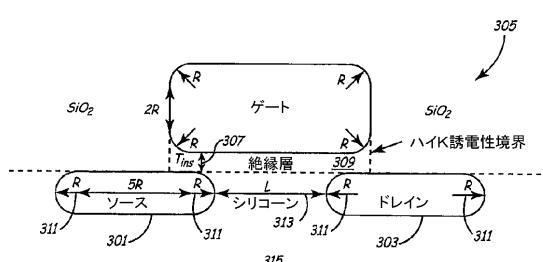

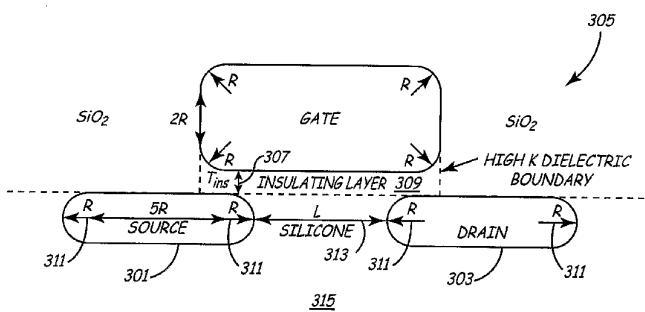

図 3 a ~ c を参照すると、完全な 2 次元静電シミュレーションは、様々な絶縁層 309 の厚さ  $T_{ins}$  307、および絶縁体誘電率 K に対して図 3 a の MOSFET デバイス 305 構造上で実施された。シミュレーションは、以下のことを仮定する。

50

## 【0026】

1) 300K の金属ソース 301 / ドレイン 303 を有する P 型 MOS 半導体デバイス 305。

50

## 【0027】

2) 10nm の曲率半径 R 311 を有する金属ソース 301 / ドレイン 303。

50

## 【0028】

3) 25nm のチャネル長 L 313、1.2V のドレイン電圧  $V_D$ 。

50

## 【0029】

4 ) シリコン基板 315において、固定か移動性かにかかわらず大きく帶電していない。

【0030】

5 ) ドレイン電流  $I_D$  は、半導体デバイス 305 のソース 301 の端部で放出プロセスによって単に制限される。

【0031】

6 ) ソース 301 での放出プロセスに対する電流密度対電界 (J 対 E) 特性は、プラチナシリサイドとシリコンとのショットキーコンタクト後に作られる。ショットキーバリアの高さは 0.187 eV、シリコン内の空孔の有効質量は 0.66 m<sub>0</sub>、フェルミ準位は 5.4 eV、そして温度は 300 K と仮定されている。ソース 301 上の特定の位置における所与の電界強度に対して、電流密度は、1 次元のシャープな三角形バリアを仮定したシユレーディング方程式の厳密解（近似解ではない）によって計算される。量子トンネル効果および反射は完全にして含まれている。総電流密度が、状態の密度でまとめられているので、電界放出、熱放出、および熱支援 (thermally assisted) 電界放出による電流が考慮されている。J 対 E の関係は、純粋な熱放出の場合 (E = 0) の実験データに対して較正されている。

【0032】

これらの仮定は、ショートチャネル (25 nm 未満) およびアンドープ (ライトドープ) 基板の実際のケースにおいて妥当である。計算されたソース 301 放出電流の絶対値は、E > 0 に対して計算されていないが、これらは、いくつかの実験結果、および第 1 原理の計算に基づいている。提案された発明の目的に対して、計算された J 対 E データは十分である。なぜなら、ソース 301 の放出電流に対する絶縁層 309 の厚さ (T<sub>ins</sub>) 307、および誘電率 (K) の効果に関するからである。T<sub>ins</sub> および K によるソース 301 の放出電流における相対的变化は、この場合、電流の絶対値のより適当である。にもかかわらず、漏れ電流、および駆動電流  $I_D$  の両方の計算値は、実際のトランジスタ計測データと一致する。

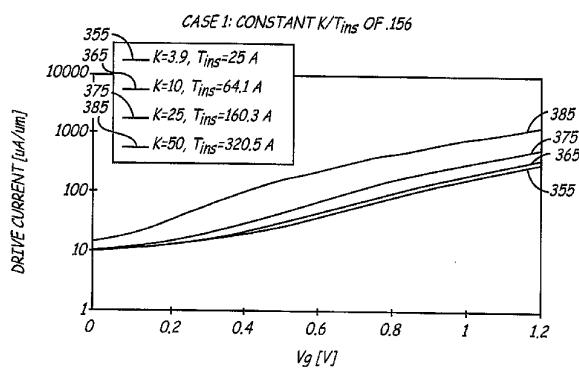

【0033】

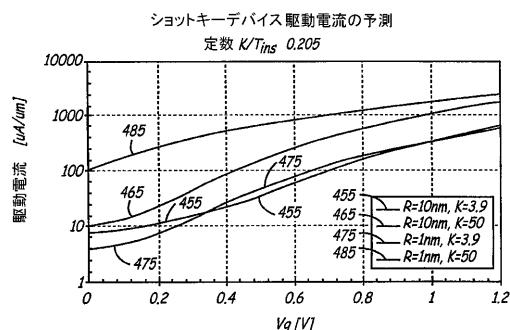

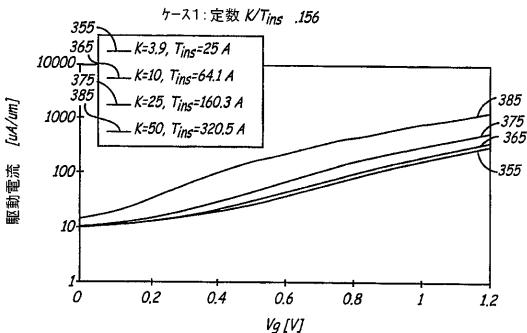

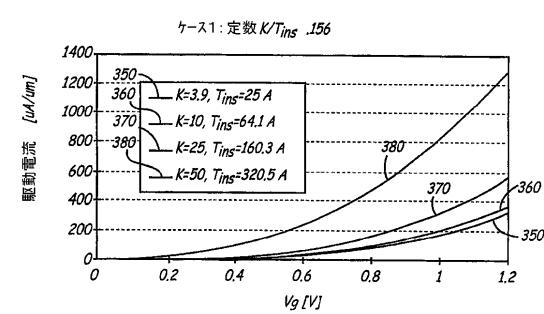

シミュレーションは、0.156 の一定の K / T<sub>ins</sub> 比で実行された。結果は、図 3b ~ c に示される。図 3c から始めて、上方へと説明する。曲線 350 は、3.9 (T<sub>ins</sub> = 25) の誘電率の絶縁層を有する半導体デバイスにおけるゲート電圧 V<sub>G</sub> と駆動電流  $I_D$  との関係を示している。曲線 360、370、および 380 は、基板とともにショットキーコンタクト、またはショットキー状領域 270、275 を形成するソース 220 およびドレイン 230 を有する半導体デバイス（それぞれ、10 (T<sub>ins</sub> = 64.1)、25 (T<sub>ins</sub> = 160.3) および 50 (T<sub>ins</sub> = 320.5) の絶縁誘電率を有する）における V<sub>G</sub> と I<sub>D</sub> の比を示している。図 3b を参照すると、曲線 355 は、3.9 (T<sub>ins</sub> = 25) の誘電率の絶縁層を有する半導体デバイスにおけるゲート電圧 V<sub>G</sub> と駆動電流  $I_D$  との対数関係を示している。曲線 365、375、および 385 は、基板とともにショットキーコンタクト、またはショットキー状領域 270、275 を形成するソース 220 およびドレイン 230 を有する半導体デバイス（それぞれ、10 (T<sub>ins</sub> = 64.1)、および 25 (T<sub>ins</sub> = 160.3)、50 (T<sub>ins</sub> = 320.5) の絶縁誘電率を有する）における V<sub>G</sub> と I<sub>D</sub> の対数比を示している。曲率半径 R 311、チャネル長 313 およびドレイン電圧 V<sub>D</sub> に関わらず同様の結果が得られると予想される。駆動電流対漏れ電流の比は、曲線 350 / 355、360 / 365、370 / 375 および 380 / 385 に対してそれぞれ 35、38、53 および 86 である。漏れ電流は、駆動電流を犠牲にすることなく、（バルクパンチスルーポートを制御するための）基板の適切なドーパントを追加することによって、または動作温度を低下させることによって少なくとも 10 分の 1 まで減少され得る。このように、基板とともにショットキーコンタクトまたはショットキー状領域を形成するソース 301 またはドレイン 303 を用いることによって、および一定の K / T<sub>ins</sub> 比を維持しながら、K を増加することによって、駆動電流  $I_D$  は、著しく増加する (V<sub>G</sub> が 1.2 V のときの 300  $\mu$ A /  $\mu$ m より若干上から約 1300  $\mu$ A /  $\mu$ m まで)。このように、所望の駆動電流に対して、デバ

10

20

30

40

50

イスは、動作のために従来技術で必要とされていた電圧より著しく低い電圧を必要とする。電力消費は、電圧の2乗で変化するため、本発明は、電力使用の著しい低下を提供する。

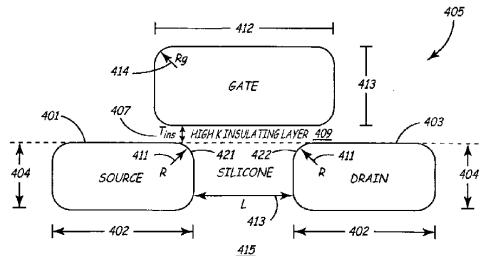

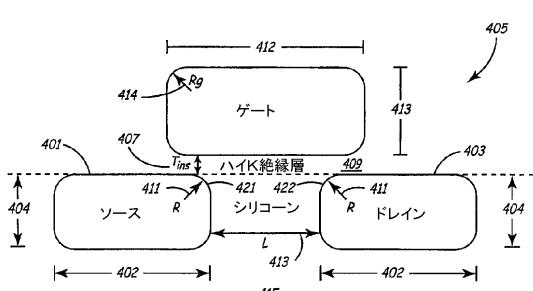

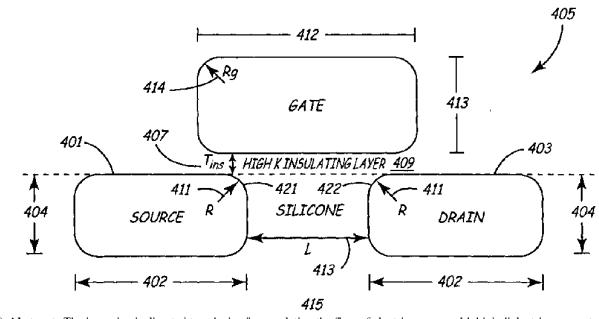

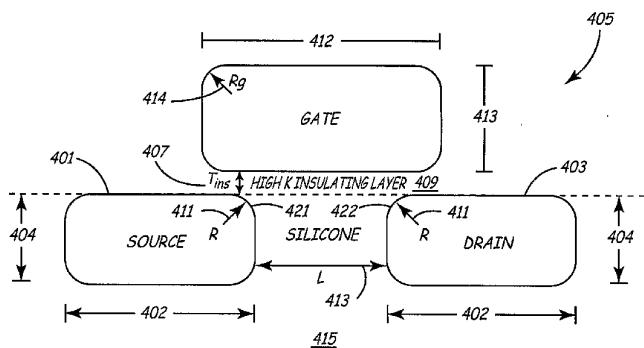

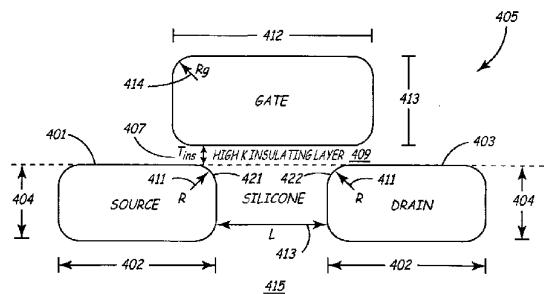

【0034】

曲率半径R311の変更が、 $I_D$ において確認されるめざましい改良を変化しないことを証明するために、完全2次元静電シミュレーションは、わずかに異なるデバイスの形状で繰り返された。図4a～cを参照すると、図4aの半導体デバイス405構造は、 $K/T_{ins}$ 比が一定であるように2つの絶縁層409の厚さ $T_{ins}407$ 、および絶縁誘電率Kに対してシミュレートされた。シミュレーションの仮定は、デバイスの形状を除けば上部に記載されたものと同じである。

10

【0035】

1) チャネル長 $L413$ は27nm。

【0036】

2) ソースおよびドレインの幅402および高さ404は、それぞれ100nmおよび30nm。

【0037】

3) ゲートの幅412および高さ413は、それぞれ67nmおよび108nm。

【0038】

4) ゲートの曲率半径 $R_g414$ は、全てのシミュレーションで10nm。

【0039】

5) ソースおよびドレイン電極の曲率半径 $R411$ は、1nmまたは10nm。

20

【0040】

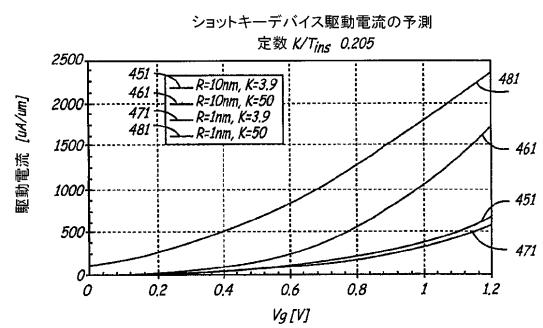

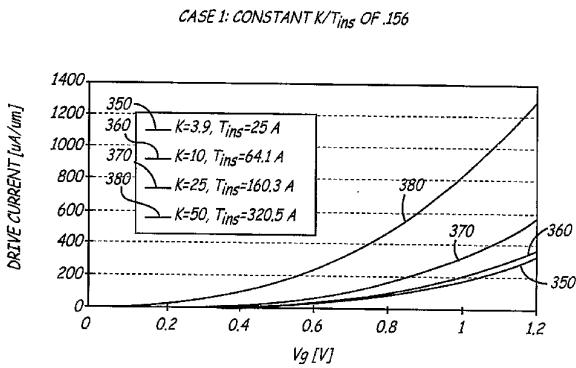

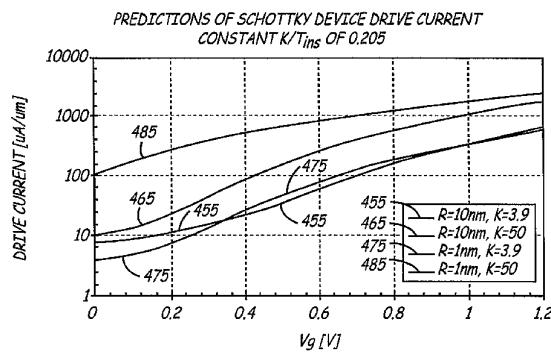

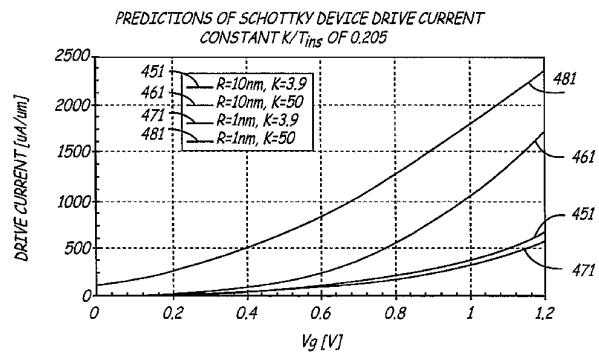

シミュレーションは、 $K/T_{ins}$ 比0.205の一定で実行された。結果は、図4b～cに示される。図4cを始めとして、曲線451および461は、それぞれ3.9( $T_{ins}=25$ )および50( $T_{ins}=244$ )の絶縁層の誘電率で10nmの曲率半径R411を有する半導体デバイスにおけるゲート電圧 $V_g$ と駆動電流 $I_D$ との間の関係を示している。図4cを続けると、曲線471および481は、それぞれ3.9( $T_{ins}=25$ )および50( $T_{ins}=244$ )の絶縁層の誘電率で1nmの曲率半径R411を有する半導体デバイスにおけるゲート電圧 $V_g$ と駆動電流 $I_D$ との間の対数関係を示している。図4bを参照すると、曲線455および465は、それぞれ3.9( $T_{ins}=25$ )および50( $T_{ins}=244$ )の絶縁層の誘電率で10nmの曲率半径R411を有する半導体デバイスにおけるゲート電圧 $V_g$ と駆動電流 $I_D$ との間の関係を示している。図4bを続けると、曲線475および485は、それぞれ3.9( $T_{ins}=25$ )および50( $T_{ins}=244$ )の絶縁層の誘電率で1nmの曲率半径R411を有する半導体デバイスにおけるゲート電圧 $V_g$ と駆動電流 $I_D$ との間の関係を示している。図4b～cは、基板とともにショットキーコンタクトまたはショットキー状領域を形成するソース401およびドレイン403を用いることによって、ならびに $K/T_{ins}$ 比を一定に維持しながら、Kを増加することによって、10nmの曲率半径R411を有するデバイスに対して駆動電流 $I_D$ は、著しく増加する( $V_g$ が1.2Vのときの約650mA/mmから約1700mA/mmまで)。 $K=50$ と $K=3.9$ の場合において、駆動電流の比は、1700/650=2.6である。同様に、1nmの曲率半径R411を有するデバイスに対して駆動電流 $I_D$ は著しく増加する( $V_g$ が1.2Vのときの約570mA/mmから約2340mA/mmまで)。この場合において、 $K=50$ と $K=3.9$ の場合において、駆動電流の比は、2340/570=4.1である。これらの結果は、より小さな曲率半径R411に対して駆動電流 $I_D$ の相対的な改良が、より大きくなることを示している。さらに、これらの結果は、 $K/T_{ins}$ 一定の場合と比較して、 $K/T_{ins}$ 比の増加が、駆動電流 $I_D$ における大きな改良を導くことを示している。従来の不純物ドーピングされたソースおよびドレインデバイスは、一定の $K/T_{ins}$ を有する $K=3.9$ と $K=50$ の両方の場合に対してほぼ同じ駆動電流 $I_D$ を有する。

30

【0041】

40

50

ソースとドレインのコーナー領域の電子顕微鏡写真の横断スキャニングは、チャネル領域に隣接するソース421電極の上部コーナー、およびドレイン422電極の上部コーナーの曲率半径R411は、10nmより1nmに近いことを示している。図4a～cのシミュレーション予想は、基板とともにショットキーコンタクトまたはショットキー状領域を形成するソース401またはドレイン403を用いることによって、およびハイK誘導性ゲート絶縁材料を用いることによって、デバイスは、所望の駆動電流に対して、従来技術が要求する動作電圧より著しく低い動作電圧を必要とすることを示している。電力消費は、電圧の2乗で変化するため、本発明は、著しく低い電力使用を供給する。

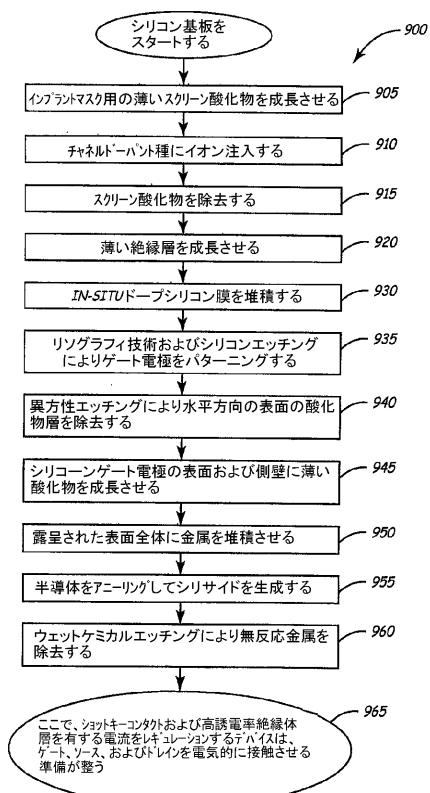

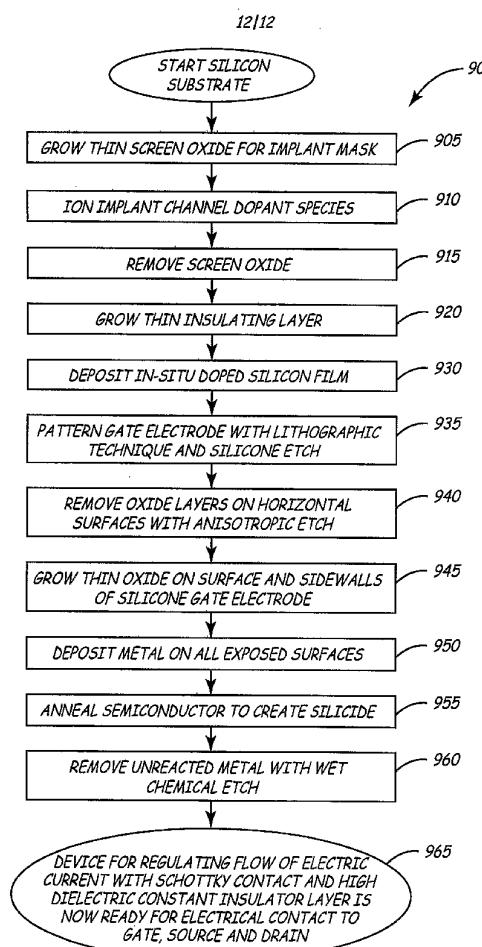

## 【0042】

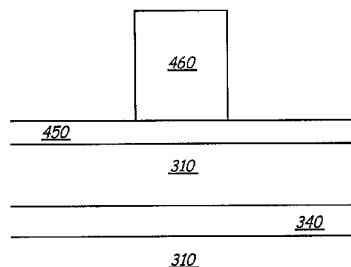

上述された電流量レギュレーションデバイス（例えば、平面のP型、またはN型MOSFET）は、図5～9に示され、図10で説明されたプロセスを用いることによって形成され得る。（平面P型、またはN型MOSFETは、水平方向に平面である必要はないが、いくつかの平面方向を仮定し得ることに留意されない）。図5および10を参照すると、薄いスクリーン酸化物323は、シリコン基板310上で成長し、基板310は、トランジスタを互いに電気的に絶縁する手段を有する（905）。選択的に厚さ200の薄いスクリーン酸化物は、チャネル領域340のドーピングのためのインプラントマスクとして機能する。適切なチャネルドーパントの種類（例えば、P型およびN型デバイスに対するそれぞれヒ素およびインジウム）は、スクリーン酸化物323を通過してシリコンの所定の深さ、例えば、（1000）にイオン注入される（910）。

## 【0043】

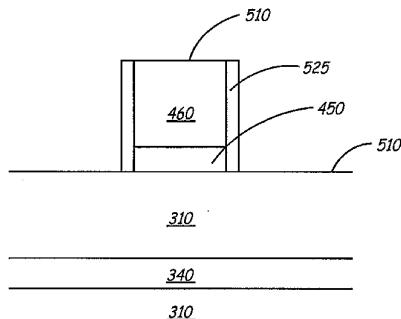

図6および10を参照すると、図5のスクリーン酸化物層323は、フッ化水素酸で取除かれ（915）、薄い絶縁層450が、少なくともチャネル領域340の一部の上に成長するか、堆積する（920）。この絶縁層は、TiO<sub>2</sub>、TaO<sub>2</sub>または、上述された高誘電率を有する他の適当な化合物で構成されてもよい。絶縁層の成長、または堆積の直後に、イン-サイチュ（in-situ）多量ドープシリコンフィルムが堆積される（930）。このシリコンフィルムは、結局ゲート電極を作り上げる。シリコンフィルムは、N型デバイス用にリンをドーピングされ、またはP型デバイス用にボロンをドーピングされ得る。ゲート電極は、その後、リソグラフィック手法、および絶縁層450を厳選するシリコンエッティングを用いてパターニングされる（935）。

## 【0044】

図7および10を参照すると、薄さが選択的に約100の薄い酸化物は、ゲート電極の上部面および側壁上に形成される（940）。その後、鉛直面の酸化物を保存する一方、酸化物層のいくつかは、異方性エッティングによって除去され、水平面510のシリコンを露呈する（945）。この工程は、ゲート側壁酸化物525を生成し、デバイスのゲート電極とチャネル領域340において、かつドーパントを電気的に活性化する。

## 【0045】

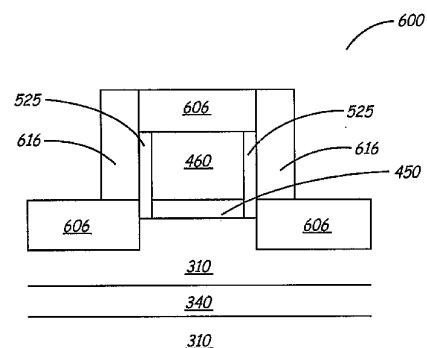

図8および10を参照すると、金属は、全ての表面上に選択的な約400の厚さの全面フィルムとして堆積される（950）。堆積された特定の金属は、デバイスがN型またはP型のどちらかによって決まる。エルビウムは、N型デバイス用に使用され得る一方、プラチナは、P型デバイス用に使用され得る。半導体デバイス600は、それから例えば400で45分の想定温度、想定時間でアニールされる（955）。この温度は、不純物のドーピングされたソースおよびドレインの形成に要する通常の温度に比べてそれほど大きくない。この温度は、800より大きい。金属がシリコンと直接的接触する場合、アニール処理は、金属を金属シリサイド606に変換する化学反応を引き起こす。シリコンに接触しない金属616は、反応しない。

## 【0046】

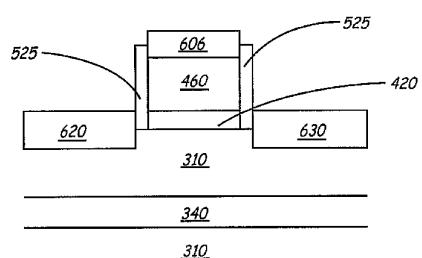

図9および10を参照すると、無反応金属616は、ウェットケミカルエッティングによって除去される（960）。例えば、堆積された金属がプラチナまたはエラジウムである場合、王水またはHNO<sub>3</sub>がその金属を除去するためにそれぞれ使用される。残ったシリサイドがソース620およびドレイン630である。高誘電率絶縁層を有する、電流をレギ

10

20

30

40

50

ュレーションするショットキーデバイスは、ここで完成し、ゲート電極 460、ソース 620 およびドレイン 630 の電気的接触の準備が整っている(965)。この処理でショットキーやショットキー状ソースおよびドレイン電極を形成するために必要な温度がソース 620、およびドレイン 630 領域に不純物をドーピングするために必要な温度よりも低いため、ゲート絶縁体 450 に用いられるハイ K 金属は、近傍の材料と反応することはそれほど多くなく、この処理は、従来技術より生産性が高い。

#### 【0047】

本発明の複数の実施形態が述べられてきた。それにもかかわらず、本発明の意図、および範囲を逸脱することなく様々な修正がなされることが理解される。例えば、特許請求の範囲に記載された半導体デバイスは、例示のためのみである。この発明のコンセプトは、様々な断面を有する半導体デバイスに適用されることが理解されるべきである。発明が、平面シリコン MOS トランジスタに関して図示されているにもかかわらず、電流をレギュレーションする他のデバイスにも同様に適用される。例えば、デバイスは、ガリウムヒ素 GaAs、リン化インジウム InP、シリコンカーバイド SiC、シリコンゲルマニウム SiGe などのような他の半導体基板上に構築される。さらに、デバイスは、ソースまたはドレインの電極コーナーに対して特定の曲率半径を有する必要がない。そして、本発明は、K/T<sub>in</sub>s の特定の比(単数または複数)を限定されない。従って、他の実施形態は、添付の特許請求の範囲内である。

#### 【0048】

本発明は、好ましい実施形態を参照して記載されているが、当業者は、本発明の意図、および範囲を逸脱することなく形式的に、かつ詳細に変更がなされることを理解している。

#### 【図面の簡単な説明】

#### 【0049】

【図 1】図 1 は、従来技術の半導体トランジスタの断面図である。

【図 2】図 2 は、ショットキーコンタクトソースおよびドレインが、ゲートとチャネル領域との間で非二酸化シリコン絶縁層と結合される、半導体基板の断面図である。

【図 3 a】図 3 a は、ショットキーコンタクトソースおよびドレインが、ゲートとチャネル領域との間で非二酸化シリコン絶縁層と結合される、半導体デバイスの断面図であり、これは、数値シミュレーションに利用されるデバイス構造である。

【図 3 b】図 3 b は、K/T<sub>in</sub>s の比が一定である、様々な K の値に対する駆動電流 I<sub>D</sub> とゲート電圧 V<sub>G</sub> との間のシミュレートされた関係を示す対数プロット図である。

【図 3 c】図 3 c は、図 3 b と同じデータの線形プロット図である。

【図 4 a】図 4 a は、ショットキーコンタクトソースおよびドレインが、ゲートとチャネル領域との間で非二酸化シリコン絶縁層と結合される、半導体基板の断面図であり、これは、数値シミュレーションの第 2 のセットに利用したデバイス構造である。

【図 4 b】図 4 b は、K/T<sub>in</sub>s の比が一定である、様々な K の値に対する駆動電流 I<sub>D</sub> とゲート電圧 V<sub>G</sub> との間のシミュレートされた関係を示す対数プロット図である。

【図 4 c】図 4 c は、図 4 b と同じデータの線形プロット図である。

【図 5】図 5 は、イオン注入後の半導体基板の断面図である。

【図 6】図 6 は、絶縁層の成長およびゲートのパターニング後の半導体基板の断面図である。

【図 7】図 7 は、側壁の酸化物層の成長後の半導体基板の断面図である。

【図 8】図 8 は、金属シリサイドソースおよびドレインの生成後の半導体基板の断面図である。

【図 9】図 9 は、図 10 に概要が示される処理工程の結果の半導体デバイスの断面図である。

【図 10】図 10 は、発明にしたがって電流量をレギュレーションするデバイスの製造の処理フローの概略のフローチャートである。

【図1】

FIG. 1

(従来技術)

【図3 a】

FIG. 3a

【図4 a】

FIG. 4a

【図4 b】

FIG. 4b

【図3 b】

FIG. 3b

【図3 c】

FIG. 3c

【図4 c】

FIG. 4c

【図10】

FIG. 10

## 【国際公開パンフレット】

(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau(43) International Publication Date

20 February 2003 (20.02.2003)

PCT

(10) International Publication Number

WO 03/015181 A1

(51) International Patent Classification: H01L 29/78, 21/336

(21) International Application Number: PCT/US02/25289

(22) International Filing Date: 9 August 2002 (09.08.2002)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

|            |                             |    |

|------------|-----------------------------|----|

| 09/928,124 | 10 August 2001 (10.08.2001) | US |

| 09/928,163 | 10 August 2001 (10.08.2001) | US |

| 60/381,320 | 16 May 2002 (16.05.2002)    | US |

(71) Applicant: SPINNAKER SEMICONDUCTOR, INC. [US/US]; 7550 Market Place Drive, Eden Prairie, MN 55344 (US).

(72) Inventors: SNYDER, John, P.; 5705 Lois Lane, Edina, MN 55439 (US); LARSON, John, M.; 419 College Street, Northfield, MN 55057 (US).

(74) Agents: KRAUS, Jason, R. et al.; Dorsey &amp; Whitney LLP, suite 1500, 50 South Sixth Street, Minneapolis, MN 55402-1498 (US).

(81) Designated States (national): AF, AG, AI, AM, AT, AU, AZ, BA, BB, BG, BR, BY, BZ, CA, CI, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, ES, H, GB, GD, GE, GI, GM, HR, HU, ID, IL, IN, IS, JP, KU, KG, KP, KR, KZ, L, I, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NO, NZ, OM, PL, PT, RO, RU, SD, SE, SG, SI, SK, SL, TJ, TM, TN, TR, TT, TZ, UA, UG, UZ, VN, YU, ZA, ZM, ZW.

(84) Designated States (regional): ARIPO patent (GH, GM, KE, L, S, MW, MZ, SD, SI, SZ, TZ, UG, ZM, ZW), Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European patent (AT, BE, BG, CL, CY, CZ, DE, DK, EE, ES, FI, FR, GR, IE, IL, LU, MC, NL, PT, SE, SK, TR), OAPI patent (BJ, BJ, CI, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NI, SN, TD, TG).

Published:

— with international search report

[Continued on next page]

(54) Title: TRANSISTOR HAVING HIGH DIELECTRIC CONSTANT GATE INSULATING LAYER AND SOURCE AND DRAIN FORMING SCHOTTKY CONTACT WITH SUBSTRATE

WO 03/015181 A1

(57) Abstract: The invention is directed to a device for regulating the flow of electric current with high dielectric constant gate insulating layer and a source and/or drain forming a Schottky contact or Schottky-like region with a substrate and its fabrication method. In one aspect, the gate insulating layer has a dielectric constant greater than the dielectric constant of silicon. In another aspect, the current regulating device may be a MOSFET device, optionally a planar P-type or N-type MOSFET, having any orientation. In another aspect, the source and/or drain may consist partially or fully of a silicide.

---

**WO 03/015181 A1**

*before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments*

*For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.*

WO 03/015181

PCT/US02/25289

**TRANSISTOR HAVING HIGH DIELECTRIC CONSTANT GATE

INSULATING LAYER AND SOURCE AND DRAIN FORMING

SCHOTTKY CONTACT WITH SUBSTRATE****CROSS-REFERENCE TO RELATED APPLICATION(S)**

5 This application is a continuation-in-part of U.S. patent application number 09/928,124, filed August 10, 2001 and of U.S. patent application number 09/928,163, filed August 10, 2001. This application claims further priority to U.S. provisional patent application number 60/381,320, filed on May 16, 2002, which is incorporated by reference in its entirety.

**10 BACKGROUND OF THE INVENTION**

The present invention is directed to devices that regulate the flow of electric current and their fabrication methods. More specifically, the present invention is directed to Schottky-barrier source and/or drain transistors.

An electric current flow regulating device such as semiconductor device 100 (for example a transistor), seen in prior art FIG. 1, may include a silicon substrate 110, with an impurity doped source 120 and impurity doped drain 130. Source 120 and drain 130 are separated by a channel region 140. Atop the channel region 140 is an insulating layer 150. Insulating layer 150 typically consists of silicon dioxide, which has a dielectric constant of 3.9. A gate electrode 160, made from electrically conductive material, is located on top of the insulating layer 150.

When a voltage  $V_G$  is applied to the gate electrode 160, current flows between the source 120 and drain 130 through the channel region 140. This current is referred to as the drive current, or  $I_D$ . For digital applications, a voltage

WO 03/015181

PCT/US02/25289

$V_G$  can be applied to the gate electrode 160, to turn the semiconductor device 100 "on." In this state, the semiconductor device will have a relatively large drive current, ideally limited only by the resistance of the channel region 140. A different voltage  $V_G$  can be applied to the gate electrode 160 to turn the 5 semiconductor device 100 "off." In this state, the ideal leakage current is zero. However, in practical applications, the drive current in the "on" state is not ideal because of parasitic impedances associated with other parts of the semiconductor device 100. For example, the source and drain regions have a finite impedance, resulting in a parasitic impedance which adds to the resistance of the channel 10 region. Also, in practical applications, there is a certain finite amount of leakage current when the semiconductor device is "off."

In prior art current regulating devices, the drive current is linearly proportional to the dielectric constant  $K$  of the insulating layer 150, and linearly inversely proportional to the thickness  $T_{ins}$  of the insulating layer 150. The drive 15 current  $I_D$  is approximated by the relationship:

$$I_D \sim K/T_{ins}$$

where  $K$  is the dielectric constant of the insulating layer and  $T_{ins}$  is the thickness of the insulating layer.

One consideration in the design of current regulating devices is reducing 20 the amount of power required to achieve a desired drive current. One way to reduce power consumption is by using a metal source and drain and a simple, uniformly implanted channel dopant profile, as described in copending U.S. Patent Applications 09/465,357, filed on December 16, 1999, entitled "METHOD

WO 03/015181

PCT/US02/25289

OF MANUFACTURING A SHORT-CHANNEL FET WITH SCHOTTKY BARRIER SOURCE AND DRAIN CONTACTS," and 09/777,536, filed on February 6, 2001, entitled "MOSFET DEVICE AND MANUFACTURING METHOD," the contents of which are hereby incorporated by reference.

5 Another consideration in the design of current regulating devices is the manufacturability. One way to improve the manufacturability of current regulating devices having gate insulators with high dielectric constant materials is to form the source and drain electrodes using a low temperature process such as that used for formation of Schottky or Schottky-like source and drain electrodes, 10 as described in U.S. Provisional Patent Application 60/381,320, filed on May 16, 2002, entitled "LOW TEMPERATURE SOURCE AND DRAIN FORMATION PROCESS STEPS FOR THE MANUFACTURE OF MOSFET DEVICES," the contents of which are hereby incorporated by reference.

15 There is a need in the art for a device for regulating the flow of electric current, which exhibits an improved drive current in the "on" state. There is a further need in the art for a method of manufacturing such a device at reduced temperatures.

#### BRIEF SUMMARY OF THE INVENTION

By using the invention disclosed herein the drive current characteristics 20 can be improved, resulting in a non-linear relationship between the drive current  $I_D$  and both the dielectric constant (K) of the insulating layer and the thickness of the insulating layer  $T_{ins}$ . The resulting relationship results in current regulating devices that are more sensitive to variations in K and  $T_{ins}$  compared to the prior

WO 03/015181

PCT/US02/25289

art. Furthermore, by using the invention disclosed herein, the manufacturability of new gate insulator materials is improved substantially.

In one aspect, the invention provides a method for manufacturing a device for regulating the flow of electrical current. The method includes the steps of 5 providing for a semiconductor substrate; providing for an electrically insulating layer in contact with the semiconductor substrate, the insulating layer having a dielectric constant greater than 4.0; providing for a gate electrode in contact with at least a portion of the insulating layer; and providing a source electrode and a drain electrode in contact with the semiconductor substrate and proximal to the 10 gate electrode wherein at least one of the source electrode and the drain electrode forms a Schottky contact or Schottky-like region with the semiconductor substrate. In one aspect, the device for regulating the flow of electrical current may be a Metal Oxide Semiconductor Field Effect Transistor (MOSFET) device.

In another aspect, the dielectric constant may be greater than 7.6 or greater than 15 15.

In another aspect, the source and drain electrodes may be formed from a member of the group consisting of: platinum silicide, palladium silicide and iridium silicide. In another aspect, the source and drain electrodes may be formed from a member of the group consisting of the rare earth silicides. In 20 another aspect, the insulating layer may be formed from a member of the group consisting of the metal oxides. In another aspect, the Schottky contact or Schottky-like region may be at least in areas adjacent to the channel. In another aspect, an entire interface between at least one of the source and the drain

WO 03/015181

PCT/US02/25289

electrodes and the semiconductor substrate may form a Schottky contact or Schottky-like region with the semiconductor substrate. In another aspect, the channel region may be doped.

In another aspect, the invention provides a method for manufacturing a device for regulating the flow of electrical current. The method includes the steps of providing for a semiconductor substrate; providing for an electrically insulating layer in contact with the semiconductor substrate, the insulating layer having a dielectric constant greater than 4.0; providing for a gate electrode located in contact with at least a portion of the insulating layer; exposing the semiconductor substrate on one or more areas proximal to the gate electrode; providing for a thin film of metal on at least a portion of the exposed semiconductor substrate; and reacting the metal with the exposed semiconductor substrate such that a Schottky or Schottky-like source electrode and a drain electrode are formed on the semiconductor substrate. In one aspect, the device for regulating the flow of electrical current may be a MOSFET device. In another aspect, the dielectric constant may be greater than 7.6 or greater than 15.

In another aspect, the gate electrode may be provided by the steps of depositing a thin conducting film on the insulating layer; patterning and etching the conducting film to form a gate electrode; and forming one or more thin insulating layers on one or more sidewalls of the gate electrode. In another aspect, the method may include the step of removing metal not reacted during the reacting process. In another aspect, the reacting may include thermal annealing. In another aspect, the source and drain electrodes may be formed from a member

WO 03/015181

PCT/US02/25289

of the group consisting of: platinum silicide, palladium silicide and iridium silicide. In another aspect, the source and drain electrodes may be formed from a member of the group consisting of the rare earth silicides. In another aspect, the insulating layer may be formed from a member of the group consisting of metal oxides. In another aspect, the Schottky contact or Schottky-like region may be formed at least in areas adjacent to the channel. In another aspect, an entire interface between at least one of the source electrode and the drain electrode and the semiconductor substrate may form a Schottky contact or Schottky-like region with the semiconductor substrate. In another aspect, dopants may be introduced 10 into the channel region.

In another aspect, the invention provides a device for regulating the flow of electrical current. The device includes a semiconductor substrate, a gate electrode, an electrically insulating layer located between the gate electrode and the semiconductor substrate, the insulating layer having a dielectric constant 15 greater than 4.0, and a source electrode and a drain electrode in contact with the semiconductor substrate and proximal to the gate electrode wherein at least one of the source electrode and the drain electrode forms a Schottky contact or Schottky-like region with the semiconductor substrate. In one aspect, the device for regulating the flow of electrical current may be a Metal Oxide Semiconductor 20 Field Effect Transistor (MOSFET) device. In another aspect, the dielectric constant may be greater than 7.6 or greater than 15.

In another aspect, the source and drain electrodes may be formed from a member of the group consisting of: platinum silicide, palladium silicide and

WO 03/015181

PCT/US02/25289

iridium silicide. In another aspect, the source and drain electrodes may be formed from a member of the group consisting of the rare earth silicides. In another aspect, the insulating layer may be formed from a member of the metal oxides. In another aspect, the Schottky contact or Schottky-like region may be at least in areas adjacent to the channel. In another aspect, an entire interface between at least one of the source and the drain electrodes and the semiconductor substrate may form a Schottky contact or Schottky-like region with the semiconductor substrate. In another aspect, the channel region may be doped.

Aspects of the invention can include one or more of the following advantages. Conventional field effect transistors (FET) and other current regulating devices require a higher voltage than those fabricated in accordance with the invention to produce a similar drive current from source to drain. In an optimized conventional FET or current regulating device, the drive current varies generally linearly with the ratio of the insulating layer's dielectric constant to its thickness. One of the advantages of the invention is the unexpected result of the drive current being more sensitive to dielectric constant  $K$  than to  $T_{ins}$ , implying larger drive current  $I_D$  for larger  $K$  and constant  $K/T_{ins}$  ratio. These results are achieved by coupling a Schottky or Schottky-like source and/or drain with an insulating layer made of a high dielectric constant material. Lower voltage is required to produce high source to drain currents which results in lower power consumption for microelectronics utilizing this architecture.

Furthermore, the well-known benefit of achieving less gate leakage current (between gate and source/drain electrodes) by using larger  $K$  and constant

WO 03/015181

PCT/US02/25289

$K/T_{ms}$  ratio, will still be observed in the present invention. For conventionally architected devices this particular benefit is the sole reason for using materials for the gate insulator having larger dielectric constants  $K$  than that of silicon dioxide, which has a dielectric constant of 3.9. These materials are denoted as "high  $K$ " materials. No other significant benefit is expected or observed. By using Schottky or Schottky-like source/drain devices in combination with a larger  $K$ , an unexpected and dramatic improvement in drive current  $I_d$  is achieved in addition to the reduction in gate leakage current.

Although there is a strong motivation for the industry to adopt new high  $K$  gate insulator materials due to the problem of gate leakage current, there are technical obstacles that make production of high  $K$  gate insulators challenging. One of the most important problems is the degradation of the high  $K$  gate insulator materials during high temperature processing required for the formation of the impurity doped source and drain regions. This degradation is caused by reactions with neighboring materials such as the silicon in the channel region or the gate electrode. The processing steps for the formation of the Schottky or Schottky-like source/drain regions occur at much lower temperatures such as 400 °C as compared to 1000 °C required for impurity doped source and drain formation. As a result of the significantly lower temperature processing steps for the formation of the Schottky or Schottky-like source/drain regions, the high  $K$  materials do not react substantially with the neighboring materials. Therefore, another benefit of using Schottky or Schottky-like source/drain devices in

WO 03/015181

PCT/US02/25289

combination with high K gate insulator materials is the improved

manufacturability of high K gate insulators.

While multiple embodiments are disclosed, still other embodiments of the

present invention will become apparent to those skilled in the art from the

5 following detailed description, which shows and describes illustrative

embodiments of the invention. As will be realized, the invention is capable of

modifications in various obvious aspects, all without departing from the spirit and

scope of the present invention. Accordingly, the drawings and detailed

description are to be regarded as illustrative in nature and not restrictive.

10 **BRIEF DESCRIPTION OF THE DRAWINGS**

FIG. 1 is a cross-section of a prior art semiconductor transistor.

FIG. 2 is a cross-section of a semiconductor substrate with Schottky

contact source and drain combined with a non-silicon dioxide insulating layer

between the gate and channel region.

15 FIG. 3a is a cross-section of a semiconductor device with Schottky

contact source and drain combined with a non-silicon dioxide insulating layer

between the gate and channel region. This is the device structure used for

numerical simulations.

FIG. 3b is a logarithmic plot showing the simulated relationship between

20 the drive current  $I_D$  and gate voltage  $V_G$  for various K values, with the ratio  $K/T_{ins}$

held constant.

FIG. 3c is a linear plot with the same data as FIG. 3b.

WO 03/015181

PCT/US02/25289

FIG. 4a is a cross-section of a semiconductor device with Schottky contact source and drain combined with a non-silicon dioxide insulating layer between the gate and channel region. This is the device structure used for a second set of numerical simulations.

5 FIG. 4b is a logarithmic plot showing the simulated relationship between the drive current  $I_D$  and gate voltage  $V_G$  for various  $K$  values, with the ratio  $K/T_{ins}$  held constant.

FIG. 4c is a linear plot with the same data as FIG. 4b.

FIG. 5 is a cross-section of semiconductor substrate after ion 10 implantation.

FIG. 6 is a cross-section of semiconductor substrate after insulating layer growth and gate patterning.

FIG. 7 is a cross-section of semiconductor substrate after growth of an oxide layer on the sidewalls.

15 FIG. 8 is a cross-section of semiconductor substrate after creation of a metal silicide source and drain.

FIG. 9 is a cross-section of the semiconductor device resulting from the process steps outlined in FIG. 10.

20 FIG. 10 is a flow chart outlining the process flow for the fabrication of a device for regulating flow of electric current in accordance with the invention.

Like reference symbols in the various drawings indicate like elements.

**DETAILED DESCRIPTION**

Referring to FIG. 2, semiconductor device 200 includes a substrate 210 in which a source 220 and drain 230 are formed. Substrate 210 may be composed of silicon or may be a silicon-on-insulator (SOI) substrate. Source 220 and/or drain 230 may be composed partially or fully of a rare earth silicide. Source 220 and/or drain 230 may also be composed partially or fully of platinum silicide, palladium silicide or iridium silicide. Because the source and drain are composed in part of a metal, they form Schottky contacts or Schottky-like regions 270, 275 with the substrate 210, where a "Schottky contact" is defined by the contact 5 between a metal and a semiconductor, and a "Schottky-like region" is a region formed by the close proximity of a semiconductor and a metal. The Schottky contacts or Schottky-like regions 270, 275 can be formed by forming the source and/or drain from a metal silicide. The Schottky contacts or Schottky-like regions 270, 275 are in an area adjacent to a channel region 240 formed between 10 the source 220 and drain 230. The entire interface between either or both of the source 220 and the drain 230 may form a Schottky contact or Schottky-like region 270, 275 with the substrate 210. The channel region 240 may be impurity doped where the doping may be conventional non-uniform doping or may be 15 uniform doping as described in copending U.S. Patent Application No. 09/465,357 and U.S. Patent Application No. 09/777,536.

An insulating layer 250 is formed on top of the channel region 240 and may be formed on part or all of the source 220 and drain 230. The insulating layer 250 is composed of a material with a dielectric constant greater than that of

silicon dioxide; e.g. a dielectric constant greater than 3.9. For example, insulating layer 250 may be composed of a metal oxide such as TaO<sub>2</sub> with a dielectric constant of approximately 25, TiO<sub>2</sub> with a dielectric constant of approximately 50-60, HfO<sub>2</sub> with a dielectric constant of approximately 15-20, or 5 ZrO<sub>2</sub> with a dielectric constant of approximately 15-20. The insulating layer 250 may consist of a dielectric with a modest K value (e.g., 5-10), such as nitride/oxide or oxy-nitride stack; a medium K value (e.g., 10-20), such as unary oxides Ta<sub>2</sub>O<sub>5</sub>, TiO<sub>2</sub>, ZrO<sub>2</sub>, HfO<sub>2</sub>, Y<sub>2</sub>O<sub>3</sub>, La<sub>2</sub>O<sub>3</sub>, Gd<sub>2</sub>O<sub>3</sub>, Sc<sub>2</sub>O<sub>3</sub> or silicates ZrSiO<sub>4</sub>, HfSiO<sub>4</sub>, LaSiO<sub>4</sub>, or TiSiO<sub>4</sub>; or a high K value (e.g., greater than 20) such as 10 amorphous LaAlO<sub>3</sub>, ZrTiO<sub>4</sub>, SnTiO<sub>4</sub>, or SrZrO<sub>4</sub>, or single crystals LaAl<sub>3</sub>O<sub>4</sub>, BaZrO<sub>3</sub>, Y<sub>2</sub>O<sub>3</sub>, La<sub>2</sub>O<sub>3</sub>. Optionally, to improve manufacturability issues 15 associated with transition metals, the insulating layer 250 may consist of more than one layer. The insulating layer 250 may be formed with a "bi-layer" approach and may consist of more than one type of dielectric, e.g., TiO<sub>2</sub> on top of Si<sub>3</sub>N<sub>4</sub>. A gate electrode 260 is positioned on top of the insulating layer 250. A thin insulating layer 225 surrounds the gate electrode 260.

By forming a semiconductor device with (1) a source 220 or drain 230 forming a Schottky contact or Schottky-like region 270, 275 with the substrate 110; and (2) an insulating layer 250 with a relatively high dielectric constant, one 15 is able to achieve a larger drive current I<sub>D</sub> for larger K, but constant K/T<sub>ins</sub>.

Referring to FIGS. 3a-c, full two dimensional electrostatic simulations were performed on the MOSFET device 305 structure of FIG. 3a, for various

WO 03/015181

PCT/US02/25289

insulating layer 309 thicknesses  $T_{ins}$  307 and insulator dielectric constants  $K$ . The simulation assumes the following:

- 1) P type MOS semiconductor device 305, metallic source 301/drain 303 at 300K.

- 5 2) Metallic source 301/drain 303 with radius of curvature R 311 of 10nm.

- 3) Channel length L 313 of 25nm, drain voltage  $V_D$  of 1.2V.

- 4) No significant charge, either fixed or mobile, in the silicon substrate 315.

- 10 5) The drain current,  $I_D$ , is limited solely by the emission process at the source 301 end of the semiconductor device 305.

- 6) The current density versus electric field ( $J$  vs.  $E$ ) characteristic for the emission process at the source 301 is modeled after a platinum silicide-to-silicon Schottky contact. The Schottky barrier height is assumed to be 0.187eV, 15 hole effective mass in the silicon is 0.66mo, fermi level is at 5.4eV, and temperature is 300K. For a given electric field strength at a particular point on the source 301, the current density is calculated via a complete, no approximations solution to the Schreedingger equation assuming a 1-D sharp triangular barrier. The effects of quantum tunneling and reflection have been 20 fully included. Because the total current density is integrated across the density of states, currents due to field emission, thermal emission, and thermally assisted field emission have been accounted for. The  $J$  vs.  $E$  relationship has been calibrated to experimental data for the pure thermal emission case ( $E=0$ ).

These assumptions are valid in the real world case of short channel (<25nm) and undoped (or lightly doped) substrates. Although the absolute values of the calculated source 301 emission currents have not been calibrated for  $E>0$ , they are based on some experimental data and first-principles calculations. For 5 the purposes of the proposed invention, the calculated  $J$  vs.  $E$  data is sufficient as the primary interest relates to the effect of the insulating layer 309 thickness ( $T_{ins}$ ) 307 and dielectric constant ( $K$ ) on source 301 emission current. Relative changes in source 301 emission current with  $T_{ins}$  and  $K$  are more relevant, in this case, 10 than the absolute value of the current. Nevertheless, calculated values of both leakage and drive currents  $I_D$  are in good agreement with the measured data of actual transistors.

Simulations were run with a constant  $K/T_{ins}$  ratio of 0.156. The results are shown in FIGs. 3b-c. Starting with FIG. 3c, working upwards, curve 350 shows the relationship between the gate voltage  $V_G$  and the drive current  $I_D$  in a 15 semiconductor device with an insulating layer dielectric constant of 3.9 ( $T_{ins} = 25$  Å). Curves 360, 370 and 380 show the ratio of  $V_G$  and  $I_D$  in semiconductor devices with sources 220 and drains 230 that form a Schottky contact or Schottky-like region 270, 275 with the substrate and insulating dielectric 20 constants of 10 ( $T_{ins} = 64.1$  Å), 25 ( $T_{ins} = 160.3$  Å), and 50 ( $T_{ins} = 320.5$  Å), respectively. Referring to FIG. 3b, curve 355 shows the logarithmic relationship between the gate voltage  $V_G$  and the drive current  $I_D$  in a semiconductor device with an insulating layer dielectric constant of 3.9 ( $T_{ins} = 25$  Å). Curves 365, 375 and 385 show the logarithmic ratio of  $V_G$  and  $I_D$  in semiconductor devices with

WO 03/015181

PCT/US02/25289

sources 220 and drains 230 that form a Schottky contact or Schottky-like region 270, 275 with the substrate and insulating dielectric constants of 10 ( $T_{ins} = 64.1 \text{ \AA}$ ), 25 ( $T_{ins} = 160.3 \text{ \AA}$ ), and 50 ( $T_{ins} = 320.5 \text{ \AA}$ ), respectively. It is expected that similar results would be achieved regardless of the radius of curvature R 311, 5 channel length 313 and drain voltage  $V_D$ . Drive current to leakage current ratios are 35, 38, 53 and 86 for the curves 350/355, 360/365, 370/375 and 380/385, respectively. Leakage currents can be lowered by at least a factor of 10, without sacrificing drive currents, by the addition of the appropriate dopants in the substrate (to control bulk-punchthrough currents) or by a reduction in operating 10 temperature. Thus, by using a source 301 or drain 303 that forms a Schottky contact or Schottky-like region with the substrate, and by increasing K while maintaining a constant  $K/T_{ins}$  ratio, the drive current  $I_D$  increases significantly (from a little over  $300 \mu\text{A}/\mu\text{m}$  for a  $V_G$  of 1.2V to approximately  $1300 \mu\text{A}/\mu\text{m}$ ). Thus, for a desired drive current, a device would need a significantly lower 15 voltage to operate than that required by the prior art. Because power consumption varies with the square of the voltage, the invention provides for significantly lower power usage.

To verify that changing the radius of curvature R 311 does not change the 20 observed dramatic improvement in  $I_D$ , full 2-D electrostatic simulations were repeated on a slightly different device geometry. Referring to FIGs. 4a-c, the semiconductor device 405 structure of figure 4a was simulated for two insulating layer 409 thicknesses  $T_{ins}$  407 and insulator dielectric constants K, such that the

WO 03/015181

PCT/US02/25289

ratio  $K/T_{ins}$  was constant. The simulation assumptions are the same as noted above, with the exception of the device geometry:

- 1) The channel length L 413 is 27 nm

- 2) The width 402 and height 404 of the source and drain are 100 nm

- 5 and 30 nm respectively.

- 3) The width 412 and height 413 of the gate are 67 nm and 108 nm respectively.

- 4) The radius of curvature  $R_g$  414 of the gate was 10 nm for all simulations.

- 10 5) The radius of curvature  $R$  411 of the source and drain electrodes was either 1 nm or 10 nm.

Simulations were run with a constant  $K/T_{ins}$  ratio of 0.205. The results are shown in FIGs. 4b-c. Starting with FIG. 4c, curves 451 and 461 show the relationship between the gate voltage  $V_g$  and the drive current  $I_D$  in a 15 semiconductor device having a radius of curvature  $R$  411 of 10 nm with an insulating layer dielectric constant of 3.9 ( $T_{ins} = 25 \text{ \AA}$ ) and 50 ( $T_{ins} = 244 \text{ \AA}$ ), respectively. Continuing with FIG. 4c, curves 471 and 481 show the relationship between the gate voltage  $V_g$  and the drive current  $I_D$  in a semiconductor device having a radius of curvature  $R$  411 of 1 nm with an insulating layer dielectric constant of 3.9 ( $T_{ins} = 25 \text{ \AA}$ ) and 50 ( $T_{ins} = 244 \text{ \AA}$ ), respectively. Referring to FIG. 4b, curves 455 and 465 show the logarithmic relationship between the gate voltage  $V_g$  and the drive current  $I_D$  in a semiconductor device having a radius of curvature  $R$  411 of 10 nm with an insulating layer dielectric constant of 3.9 ( $T_{ins}$

WO 03/015181

PCT/US02/25289

= 25 Å) and 50 ( $T_{ins} = 244$  Å), respectively. Continuing with FIG. 4b, curves 475 and 485 show the relationship between the gate voltage  $V_g$  and the drive current  $I_D$  in a semiconductor device having a radius of curvature  $R$  411 of 1 nm with an insulating layer dielectric constant of 3.9 ( $T_{ins} = 25$  Å) and 50 ( $T_{ins} = 244$  Å), respectively. FIGs. 4b-c show that by using a source 401 or drain 403 that forms a Schottky contact or Schottky-like region with the substrate, and by increasing  $K$  while maintaining a constant  $K/T_{ins}$  ratio, the drive current  $I_D$  increases significantly (from approximately 650 mA/mm for a  $V_g$  of 1.2V to approximately 1700 mA/mm) for a device having a radius of curvature  $R$  411 of 10 nm. The ratio of drive currents for the  $K=50$  to the  $K=3.9$  case is  $1700/650 = 2.6$ . Likewise, for the device having a radius of curvature  $R$  411 of 1 nm, the drive current  $I_D$  increases significantly (from approximately 570 mA/mm for a  $V_g$  of 1.2V to approximately 2340 mA/mm). In this case, the ratio of drive current for the  $K=50$  to the  $K=3.9$  case is  $2340/570 = 4.1$ . These results indicate that the relative improvement in drive current  $I_D$  grows larger for smaller radii of curvature  $R$  411. Further, these results indicate that increasing the ratio  $K/T_{ins}$  will lead to larger improvements in drive current  $I_D$  as compared to the case of constant  $K/T_{ins}$ . A conventional impurity doped source and drain device would have approximately the same drive current  $I_D$  for both  $K=3.9$  and  $K=50$  cases having constant  $K/T_{ins}$ .

Cross sectional scanning electron micrographs of the source and drain corner regions indicate that the radius of curvature  $R$  411 for the top corner of the source 421 and top corner of the drain 422 electrode adjacent to the channel

WO 03/015181

PCT/US02/25289

region are closer to 1 nm, rather than 10 nm. The simulation predictions of FIGs. 4a-c indicate that for a desired drive current, by using a source 401 or drain 403 that forms a Schottky contact or Schottky-like region with the substrate, and by using high K dielectric gate insulator materials, the device would need a significantly lower voltage to operate than that required by the prior art. Because power consumption varies with the square of the voltage, the invention provides for significantly lower power usage.

The device for regulating flow of electric current described above, for example a planar P-type or N-type MOSFET, may be formed using the process 10 shown in FIGs. 5-9 and described in FIG. 10. (Note that the planar P-type or N-type MOSFET need not be planar in the horizontal direction, but may assume any planar orientation.) Referring to FIGs. 5 and 10, a thin screen oxide 323 is grown on silicon substrate 310, the substrate 310 having a means for electrically isolating transistors from one another (905). The thin screen oxide, optionally a 15 thickness of 200 Å, acts as the implant mask for the channel region 340 doping. The appropriate channel dopant species (for example Arsenic and Indium for P-type and N-type devices respectively) is then ion-implanted through the screen oxide 323 to a pre-determined depth in the silicon (for example, 1000 Å) (910).

Referring to FIGs. 6 and 10, the screen oxide layer 323 of FIG. 5 is 20 removed with hydro-fluoric acid (915), and the thin insulating layer 450 is either grown or deposited at least on a portion of the channel region 340 (920). This insulating layer may consist of  $TiO_2$ ,  $TaO_2$ , or any other appropriate compound with a high dielectric constant as discussed above. Immediately following the

WO 03/015181

PCT/US02/25289

insulating layer growth or deposition, an in-situ heavily doped silicon film is deposited (930). This silicon film will eventually make up the gate electrode. The silicon film may be doped with phosphorus for an N-type device or boron for a P-type device. The gate electrode is then patterned with a lithographic technique and silicon etch that is highly selective to the insulating layer 450 (935).

Referring to FIGs. 7 and 10, a thin oxide, optionally approximately 100 Å in thickness, is formed on the top surface and sidewalls of the gate electrode (940). Some of the oxide layers then are removed by anisotropic etch to expose 10 the silicon on the horizontal surfaces 510, while preserving it on the vertical surfaces (945). This step serves both to create a gate sidewall oxide 525 and to electrically activate the dopants in the gate electrode and channel region 340 of the device.

Referring to FIGs. 8 and 10, a metal is deposited as a blanket film, 15 optionally approximately 400 Å thick, on all surfaces (950). The particular metal deposited will depend on whether the device is N-type or P-type. Platinum may be used for the P-type device while erbium may be used for an N-type device. The semiconductor device 600 is then annealed for a specified time at a specified temperature, for example, 45 minutes at 400 °C (955). This temperature is much 20 less the temperature typically required to form impurity doped source and drains, which is usually greater than 800 °C. Where the metal is in direct contact with the silicon, the annealing process causes a chemical reaction that converts the

WO 03/015181

PCT/US02/25289

metal to a metal silicide 606. The metal 616 not in contact with silicon does not react.

Referring to FIGs. 9 and 10, the unreacted metal 616 is removed with a wet chemical etch (960). For example, if the deposited metal was platinum or 5 erbium, aqua regia or HNO<sub>3</sub>, respectively, may be used to remove it. The silicide electrodes that remain are the source 620 and drain 630. The Schottky device for regulating flow of electric current with a high dielectric constant insulating layer is now complete and ready for electrical contacting to gate electrode 460, source 620, and drain 630 (965). Because the temperature 10 required to form the Schottky or Schottky-like source and drain electrodes in this process is much lower than that required for impurity doped source 620 and drain 630 regions, the high K material used for the gate insulator 450 is much less likely to react with neighboring materials, making this process much more manufactureable than the prior art.

15 A number of embodiments of the invention have been described. Nevertheless, it will be understood that various modifications may be made without departing from the spirit and scope of the invention. For example, the semiconductor devices illustrated in the claims are by way of example only. It should be understood that the concepts of the invention apply to semiconductor 20 devices with a variety of cross-sections. And, although the invention has been illustrated with respect to planar silicon MOS transistors, it can apply equally well to other devices for regulating the flow of electrical current. For example, devices built on other semiconductor substrates such as gallium arsenide GaAs,

WO 03/015181

PCT/US02/25289

indium phosphide InP, silicon carbide SiC, silicon germanium SiGe, etc. Further, the device is not required to have any particular radius of curvature for the source and drain electrode corners. And, the invention is not limited to any particular ratio(s) of  $K/T_{ins}$ . Accordingly, other embodiments are within the scope of the following claims.

Although the present invention has been described with reference to preferred embodiments, persons skilled in the art will recognize that changes may be made in form and detail without departing from the spirit and scope of the invention.

10

15

20

**CLAIMS**

We claim:

1. A method for manufacture of a device for regulating the flow of electrical current, the method comprising:

- 5 providing for a semiconductor substrate;

- providing for an electrically insulating layer in contact with the semiconductor substrate, the insulating layer having a dielectric constant greater than 4.0;

- providing for a gate electrode in contact with at least a portion of the insulating layer; and

- 10 providing a source electrode and a drain electrode in contact with the semiconductor substrate and proximal to the gate electrode wherein at least one of the source electrode and the drain electrode forms a Schottky contact or Schottky-like region with the semiconductor substrate.

- 15 2. The method of claim 1, wherein the source and drain electrodes are formed from a member of the group consisting of: platinum silicide, palladium silicide and iridium silicide.

3. The method of claim 1, wherein the source and drain electrodes are formed from a member of the group consisting of the rare earth silicides.

- 20 4. The method of claim 1, wherein the insulating layer is formed from a member of the group consisting of metal oxides.

5. The method of claim 1, wherein the insulating layer is formed from an oxy-nitride stack.

6. The method of claim 1, wherein the Schottky contact or Schottky-like region is formed at least in areas adjacent to the channel.

7. The method of claim 1, wherein an entire interface between at least one of the source electrode and the drain electrode and the semiconductor substrate forms a Schottky contact or Schottky-like region with the semiconductor substrate.

8. The method of claim 1, wherein dopants are introduced into the channel region.

9. The method of claim 1, wherein the insulating layer includes more than one layer.

10. The method of claim 2 or 3, wherein the insulating layer is formed from a member of the group consisting of metal oxides.

11. The method of claim 2 or 3, wherein the insulating layer is formed from an oxy-nitride stack.

- 15 12. The method of claim 10, wherein the Schottky contact or Schottky-like region is formed at least in areas adjacent to the channel, and wherein dopants are introduced into the channel region.

13. The method of claim 11, wherein the Schottky contact or Schottky-like region is formed at least in areas adjacent to the channel, and wherein dopants are introduced into the channel region.

- 20 14. The method of claim 2 or 3, wherein providing a source electrode and a drain electrode in contact with the semiconductor substrate is performed at a processing temperature of less than about 800 °C.

WO 03/015181

PCT/US02/25289

15. A method for manufacture of a device for regulating the flow of electrical current, the method comprising:

- providing for a semiconductor substrate;

- providing for an electrically insulating layer in contact with the

- 5 semiconductor substrate, the insulating layer having a dielectric constant greater than 7.6;

- providing for a gate electrode in contact with at least a portion of the insulating layer; and

- providing a source electrode and a drain electrode in contact with the

- 10 semiconductor substrate and proximal to the gate electrode wherein at least one of the source electrode and the drain electrode forms a Schottky contact or Schottky-like region with the semiconductor substrate.

16. The method of claim 15, wherein the source and drain electrodes are formed from a member of the group consisting of: platinum silicide,

- 15 palladium silicide and iridium silicide.

17. The method of claim 15, wherein the source and drain electrodes are formed from a member of the group consisting of the rare earth silicides.

18. The method of claim 15, wherein the insulating layer is formed from a member of the group consisting of metal oxides.

- 20 19. The method of claim 15, wherein the insulating layer is formed from an oxy-nitride stack.

20. The method of claim 15, wherein the Schottky contact or Schottky-like region is formed at least in areas adjacent to the channel.

WO 03/015181

PCT/US02/25289

21. The method of claim 15, wherein an entire interface between at least one of the source electrode and the drain electrode and the semiconductor substrate forms a Schottky contact or Schottky-like region with the semiconductor substrate.

- 5 22. The method of claim 15, wherein the insulating layer includes more than one layer.

23. The method of claim 15, wherein dopants are introduced into the channel region.

24. A method for manufacture of a device for regulating the flow of 10 electrical current, the method comprising:

- providing for a semiconductor substrate;

- providing for an electrically insulating layer in contact with the semiconductor substrate, the insulating layer having a dielectric constant greater than 15;

- 15 providing for a gate electrode in contact with at least a portion of the insulating layer; and

- providing a source electrode and a drain electrode in contact with the semiconductor substrate and proximal to the gate electrode wherein at least one of the source electrode and the drain electrode forms a Schottky contact or 20 Schottky-like region with the semiconductor substrate.

25. The method of claim 24, wherein the source and drain electrodes are formed from a member of the group consisting of: platinum silicide, palladium silicide and iridium silicide.

26. The method of claim 24, wherein the source and drain electrodes are formed from a member of the group consisting of the rare earth silicides.

27. The method of claim 24, wherein the insulating layer is formed from a member of the group consisting of metal oxides.

- 5 28. The method of claim 24, wherein the insulating layer is formed from an oxy-nitride stack.

29. The method of claim 24, wherein the Schottky contact or Schottky-like region is formed at least in areas adjacent to the channel.

30. The method of claim 24, wherein an entire interface between at 10 least one of the source electrode and the drain electrode and the semiconductor substrate forms a Schottky contact or Schottky-like region with the semiconductor substrate.

31. The method of claim 24, wherein dopants are introduced into the channel region.

- 15 32. The method of claim 24, wherein the insulating layer includes more than one layer.

33. A method for manufacture of a device for regulating the flow of electrical current, the method comprising:

providing for a semiconductor substrate;

20 providing for an electrically insulating layer in contact with the semiconductor substrate, the insulating layer having a dielectric constant greater than 4.0;

WO 03/015181

PCT/US02/25289

- providing for a gate electrode located in contact with at least a portion of the insulating layer;

- exposing the semiconductor substrate on one or more areas proximal to the gate electrode;

- 5 providing for a thin film of metal on at least a portion of the exposed semiconductor substrate; and

- reacting the metal with the exposed semiconductor substrate such that a Schottky or Schottky-like source electrode and drain electrode are formed on the semiconductor substrate.

- 10 34. The method of claim 33, wherein the gate electrode is provided by:

- depositing a thin conducting film on the insulating layer;

- patterning and etching the conducting film to form a gate electrode; and

- forming one or more thin insulating layers on one or more sidewalls of the

- 15 gate electrode.

35. The method of claim 33, further comprising removing metal not reacted during the reacting process.

36. The method of claim 33, wherein the reacting comprises thermal annealing.

- 20 37. The method of claim 33, wherein the source and drain electrodes are formed from a member of the group consisting of: platinum silicide, palladium silicide and iridium silicide.

WO 03/015181

PCT/US02/25289

38. The method of claim 33, wherein the source and drain electrodes are formed from a member of the group consisting of the rare earth silicides.

39. The method of claim 33, wherein the insulating layer is formed from a member of the group consisting of metal oxides.

- 5 40. The method of claim 33, wherein the insulating layer is formed from an oxy-nitride stack.

41. The method of claim 33, wherein the Schottky contact or Schottky-like region is formed at least in areas adjacent to the channel.

42. The method of claim 33, wherein an entire interface between at least one of the source electrode and the drain electrode and the semiconductor substrate forms a Schottky contact or Schottky-like region with the semiconductor substrate.

- 10 43. The method of claim 33, wherein dopants are introduced into the channel region.

- 15 44. A method for manufacture of a device for regulating the flow of electrical current, the method comprising:

providing for a semiconductor substrate;

providing for an electrically insulating layer in contact with the semiconductor substrate, the insulating layer having a dielectric constant greater

20 than 7.6;

providing for a gate electrode located in contact with at least a portion of the insulating layer;

WO 03/015181

PCT/US02/25289

exposing the semiconductor substrate on one or more areas proximal to the gate electrode;

providing for a thin film of metal on at least a portion of the exposed semiconductor substrate; and

5 reacting the metal with the exposed semiconductor substrate such that a Schottky or Schottky-like source electrode and drain electrode are formed on the semiconductor substrate.

45. The method of claim 44, wherein the gate electrode is provided by:

10 depositing a thin conducting film on the insulating layer; patterning and etching the conducting film to form a gate electrode; and forming one or more thin insulating layers on one or more sidewalls of the gate electrode.

46. The method of claim 44, further comprising removing metal not reacted during the reacting process.

15 47. The method of claim 44, wherein the reacting comprises thermal annealing.

48. The method of claim 44, wherein the source and drain electrodes are formed from a member of the group consisting of: platinum silicide, 20 palladium silicide and iridium silicide.

49. The method of claim 44, wherein the source and drain electrodes are formed from a member of the group consisting of the rare earth silicides.

WO 03/015181

PCT/US02/25289

50. The method of claim 44, wherein the insulating layer is formed from a member of the group consisting of metal oxides.

51. The method of claim 44, wherein the insulating layer is formed from an oxy-nitride stack.

52. The method of claim 44, wherein the Schottky contact or Schottky-like region is formed at least in areas adjacent to the channel.