(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6257716号

(P6257716)

(45) 発行日 平成30年1月10日(2018.1.10)

(24) 登録日 平成29年12月15日(2017.12.15)

(51) Int.Cl.

G02F 1/1339 (2006.01)

F 1

G02F 1/1339 500

請求項の数 3 (全 21 頁)

(21) 出願番号 特願2016-161172 (P2016-161172)

(22) 出願日 平成28年8月19日 (2016.8.19)

(62) 分割の表示 特願2015-3755 (P2015-3755)

分割

原出願日 平成19年9月25日 (2007.9.25)

(65) 公開番号 特開2016-191963 (P2016-191963A)

(43) 公開日 平成28年11月10日 (2016.11.10)

審査請求日 平成28年9月16日 (2016.9.16)

(31) 優先権主張番号 特願2006-266287 (P2006-266287)

(32) 優先日 平成18年9月29日 (2006.9.29)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 藤川 最史

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 細谷 邦雄

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 廣田 かおり

早期審査対象出願

最終頁に続く

(54) 【発明の名称】半導体装置

(57) 【特許請求の範囲】

【請求項 1】

第1の基板上方の第1の導電層と、

前記第1の導電層上方の絶縁膜と、

前記絶縁膜上方の半導体膜と、

前記半導体膜上方の第2の導電層と、

前記第2の導電層上方の透明導電層と、

前記透明導電層と同じ材料を有し、かつ、前記透明導電層と接触していない画素電極と

前記画素電極上方の液晶層と、

10

前記透明導電層上方の柱状スペーサと、前記液晶層上方および前記柱状スペーサ上方の第2の基板と、を有し、前記第1の導電層は、ゲート配線としての機能を有し、前記透明導電層は、前記第1の導電層と接する領域を有さず、前記第1の導電層の少なくとも一部と、前記絶縁膜の少なくとも一部と、前記半導体膜の少なくとも一部と、前記第2の導電層の少なくとも一部と、前記透明導電層の少なくとも一部と、前記柱状スペーサの少なくとも一部と、が重なっており、前記柱状スペーサは、前記透明導電層と重ならない領域を有し、前記透明導電層は、前記柱状スペーサと重ならない領域を有することを特徴とする半導体装置。

20

## 【請求項 2】

第 1 の基板上方の、第 1 の導電層及び第 2 の導電層と、

前記第 1 の導電層上方及び前記第 2 の導電層上方の絶縁膜と、

前記絶縁膜上方の半導体膜と、

前記半導体膜上方の第 3 の導電層と、

前記第 3 の導電層上方の透明導電層と、

前記透明導電層と同じ材料を有し、かつ、前記透明導電層と接触していない画素電極と

前記画素電極上方の液晶層と、

前記透明導電層上方の柱状スペーサと、

10

前記液晶層上方および前記柱状スペーサ上方の第 2 の基板と、を有し、

前記第 1 の導電層は、第 1 のゲート配線としての機能を有し、

前記第 2 の導電層は、前記第 2 のゲート配線としての機能を有し、且つ前記第 1 の導電層と隣接して配置され、

前記第 2 の導電層は、前記画素電極を挟んで、前記第 1 の導電層と対向するように配置され、

前記画素電極は、前記第 1 の導電層及び前記第 2 の導電層のいずれにも重ならないように配置され、

前記第 1 の導電層の少なくとも一部と、前記絶縁膜の少なくとも一部と、前記半導体膜の少なくとも一部と、前記第 3 の導電層の少なくとも一部と、前記透明導電層の少なくとも一部と、前記柱状スペーサの少なくとも一部と、が重なっており、

20

前記柱状スペーサは、前記透明導電層と重ならない領域を有し、

前記透明導電層は、前記柱状スペーサと重ならない領域を有することを特徴とする半導体装置。

## 【請求項 3】

第 1 の基板上方の第 1 の導電層と、

前記第 1 の導電層上方の絶縁膜と、

前記絶縁膜上方の半導体膜と、

前記半導体膜上方の第 2 の導電層と、

前記第 1 の導電層と交差する領域を有する第 3 の導電層と、

30

前記第 2 の導電層上方の透明導電層と、

前記透明導電層と同じ材料を有し、かつ、前記透明導電層と接触していない画素電極と

前記画素電極上方の液晶層と、

前記透明導電層上方の柱状スペーサと、

前記液晶層上方および前記柱状スペーサ上方の第 2 の基板と、を有し、

前記第 1 の導電層は、ゲート配線としての機能を有し、

前記第 3 の導電層は、ソース配線としての機能を有し、

前記第 1 の導電層の少なくとも一部と、前記絶縁膜の少なくとも一部と、前記半導体膜の少なくとも一部と、前記第 2 の導電層の少なくとも一部と、前記透明導電層の少なくとも一部と、前記柱状スペーサの少なくとも一部と、が重なっており、

40

前記第 3 の導電層は、前記第 1 の導電層及び前記透明導電層のいずれにも重ならない領域を有し、

前記柱状スペーサは、前記透明導電層と重ならない領域を有し、

前記透明導電層は、前記柱状スペーサと重ならない領域を有することを特徴とする半導体装置。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は薄膜トランジスタ（以下、TFTという）で構成された回路を有する半導体装

50

置およびその作製方法に関する。例えば、液晶表示パネルに代表される電気光学装置や有機発光素子を有する発光表示装置を部品として搭載した電子機器に関する。

#### 【0002】

なお、本明細書中において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指し、電気光学装置、半導体回路および電子機器は全て半導体装置である。

#### 【背景技術】

#### 【0003】

近年、絶縁表面を有する基板上に形成された半導体薄膜（厚さ数～数百nm程度）を用いて薄膜トランジスタ（TFT）を構成する技術が注目されている。薄膜トランジスタはICや電気光学装置のような電子デバイスに広く応用され、特に画像表示装置のスイッチング素子として開発が急がれている。10

#### 【0004】

画像表示装置として液晶表示装置が知られている。パッシブマトリクス型の液晶表示装置に比べ高精細な画像が得られることからアクティブマトリクス型の液晶表示装置が多く用いられるようになっている。アクティブマトリクス型の液晶表示装置においては、マトリクス状に配置された画素電極を駆動することによって、画面上に表示パターンが形成される。詳しくは選択された画素電極と該画素電極に対応する対向電極との間に電圧が印加されることによって、画素電極と対向電極との間に配置された液晶層の光学変調が行われ、この光学変調が表示パターンとして観察者に認識される。

#### 【0005】

一般的な透過型の液晶表示装置は、一対の基板の間に液晶層を配置し、第1の基板（画素電極が形成されている基板）において液晶層に近接していない外面側に、第1の偏光板を配置し、第2の偏光板を第2の基板（対向基板）において液晶層に近接していない外面側に配置する。20

#### 【0006】

また、フルカラー表示させるためにカラーフィルタを用いる場合、一般的には、偏光板が配置された基板（対向基板）の面とは異なる面にカラーフィルタを配置する。即ち、対向基板と液晶層の間にカラーフィルタを配置することが一般的である。

#### 【0007】

また、一対の基板間には、基板間隔を保持するためのスペーサが設けられており、粒子状のビーズスペーサ、或いは柱状のスペーサを配置している。対向基板に透明な樹脂からなる柱状スペーサを設ける場合、もう一方の基板と貼り合わせる際の圧力で柱状スペーサと重なるTFTを破壊する恐れがあった。従って、一対の基板の貼り合わせ精度が歩留まりに影響してしまう。30

#### 【0008】

本出願人は、画素部のスイッチング素子となるTFTを形成する基板上に柱状スペーサを形成する技術を特許文献1に開示している。また、本出願人は、TFT上に有機樹脂によるブラックマトリクスを形成する技術を特許文献2に開示している。

#### 【先行技術文献】

#### 【特許文献】

#### 【0009】

【特許文献1】特開2001-75500号公報

【特許文献2】特開平9-105953号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0010】

近年、液晶表示装置は、さらなる表示画像の高精細化が求められている。液晶表示装置の高精細化が向上するに従って高開口率が要求される。

#### 【0011】

TFTを形成する基板上に柱状スペーサを形成する場合、画素電極の面積を十分に確保し50

つつ、高開口率を実現するためには、TFTと重なる領域に柱状スペーサを配置することが好ましい。TFTと重なる領域に柱状スペーサを配置する場合、画素電極と柱状スペーサの位置を離すことができる。

#### 【0012】

しかし、TFTと重なる領域に柱状スペーサを配置すると、一対の基板の貼り合わせ時に圧力がかかり、TFTに影響を与える恐れ、クラックが発生する恐れなどがある。

#### 【0013】

本発明は、高開口率、且つ高精細化を実現できる液晶表示装置を提供する。また、工程を増やすことなく、外光下で高い表示品質を実現できる液晶表示装置を提供する。

#### 【課題を解決するための手段】

10

#### 【0014】

アクティブマトリクス型の液晶表示装置において、TFTと重なる位置に形成される柱状スペーサの下方に無機材料からなるダミー層を形成する。このダミー層をTFTと重なる位置に配置することによって、一対の基板の貼り合わせ工程時にTFTにかかる圧力を分散し、緩和する。このダミー層は、工程数を増やすことなく形成するため、画素電極と同じ材料で形成することが望ましい。

#### 【0015】

このダミー層は、一対の基板、即ち、素子基板と対向基板のいずれか一方に形成し、一対の基板の貼り合わせ工程時にTFTにかかる圧力を分散し、緩和する。

#### 【0016】

20

本明細書で開示する発明の構成は、絶縁表面を有する第1の基板上にスイッチング素子と、スイッチング素子と電気的に接続する画素電極と、第1の基板上に前記スイッチング素子と重なるダミー層と、ダミー層と重なる柱状スペーサが設けられた第2の基板と、第1の基板と第2の基板との間に液晶材料とを有し、画素電極と前記ダミー層は同じ材料の半導体装置である。

#### 【0017】

一対の基板の貼り合わせ時に圧力がかかっても、対向基板に柱状スペーサを設け、且つ、素子基板上にダミー層を設けることによってTFTにかかる圧力を分散し、緩和することができる。

#### 【0018】

30

また、素子基板上に柱状スペーサを形成してもよく、本発明の他の構成は、絶縁表面を有する基板上にスイッチング素子と、スイッチング素子と電気的に接続する画素電極と、基板上にスイッチング素子と重なるダミー層と、基板上に前記ダミー層を覆う柱状スペーサとを有し、画素電極とダミー層は同じ材料である半導体装置である。

#### 【0019】

また、ダミー層は、圧力を分散し、緩和するのであれば、特に形状や個数は限定されず、複数、または、複雑な形状、例えばS字形状、M字形状、十字形状などであってもよい。

#### 【0020】

TFTを形成する基板、即ち素子基板上に柱状スペーサを形成する場合、フォトリソグラフィ技術を用いて形成するため、マスクの合わせ精度によって所望の位置からズレが生じることがある。TFTと重なる位置に柱状スペーサの形成位置を合わせることで、所望の位置からズレてしまった場合でも、TFTと重なる位置の周辺は、隣り合う画素電極との間隔が他の箇所に比べて広い領域であるので、画素電極の一部に柱状スペーサが重なって開口率が低下することを防ぐことができる。即ち、本発明において、柱状スペーサは画素電極は重ならない位置、且つ、TFTと重なる位置とする。

40

#### 【0021】

また、素子基板上に柱状スペーサを形成する場合、圧力をさらに分散するため、柱状スペーサの断面形状を台形とすることが好ましい。望ましくは、柱状スペーサは、ダミー層の外側の位置に裾を有する断面形状とする。また、柱状スペーサを錐形台状として、対向基板側と接触する柱状スペーサの上面面積よりもTFT側の底面面積を広くすることが好ま

50

しい。また、さらに好ましくは、複数のダミー層の合計上面面積を柱状スペーサの上面面積よりも広くする。また、柱状スペーサの上端部は曲率を有している形状とする。

#### 【0022】

また、柱状スペーサの密着性を向上させるために、一つの柱状スペーサと重なるダミー層を複数設けることが好ましい。特に、液晶表示装置においては、平坦性が重要であるため、TFTで形成される凹凸を覆うための平坦化樹脂膜を設ける場合が多いが、平坦な表面、即ち平坦化樹脂膜上に柱状スペーサを形成すると接着強度が弱く、密着性が低下しやすい。平坦化樹脂膜を用いても、柱状スペーサを形成する領域に複数のダミー層を設けることで凹凸を部分的に形成し、柱状スペーサの密着性を向上させることができる。また、TFTとダミー層との間に平坦化樹脂膜を設けると、さらに圧力を分散できるため好ましい。

10

#### 【0023】

また、TFTを作製した箇所は他の箇所よりも積層数が多くトータルの膜厚が厚くなりやすいため、TFTと重なる位置に柱状スペーサを形成すると、基板間隔を調節しやすい。TFTと重なる位置に柱状スペーサを形成すると、柱状スペーサが液晶層の厚さが最も薄い領域に設けられることになるため、柱状スペーサの高さを低くすることができる。柱状スペーサの高さを低くすることができれば、基板間隔を狭めることができるので、液晶層の厚さを薄く制御したい場合に有効である。

#### 【0024】

また、液晶層の動作モードは、特に限定されず、ツイストネマティック型（TNモード）、または、垂直配向型（VAモード）、インプレーンスイッチング型（IPSモード）などとすることができます。

20

#### 【0025】

IPSモードとする場合、共通電極もダミー層と同じ材料を用いることができ、本発明の他の構成は、絶縁表面を有する第1の基板上にスイッチング素子と、スイッチング素子と電気的に接続する画素電極と、第1の基板上に共通電極と、第1の基板上にスイッチング素子と重なるダミー層と、ダミー層と重なる柱状スペーサが設けられた第2の基板と、第1の基板と第2の基板との間に液晶材料を含む液晶層とを有し、画素電極、共通電極、及びダミー層は同じ材料の半導体装置である。

30

#### 【0026】

また、ダミー層上に柱状スペーサを設けてもよく、本発明の他の構成は、絶縁表面を有する第1の基板上にスイッチング素子と、スイッチング素子と電気的に接続する画素電極と、第1の基板上に共通電極と、第1の基板上に前記スイッチング素子と重なるダミー層と、第1の基板上に前記ダミー層と重なる柱状スペーサと、第1の基板と対向する第2の基板と、第1の基板と第2の基板との間に液晶材料を含む液晶層とを有し、画素電極、共通電極、及びダミー層は同じ材料の半導体装置である。

#### 【0027】

本発明は、上述した課題の少なくとも一つを解決する。

#### 【0028】

上述したこれらの手段は単なる設計事項ではなく、柱状スペーサやダミー層を表示部に配置し、それらを用いた表示装置を作製し、画像表示させ、発明者らの深い検討の後、発明された事項である。

40

#### 【発明の効果】

#### 【0029】

工程数を増やすことなく、ダミー層をTFTと重なる位置に形成でき、柱状スペーサをTFTと重なる位置に形成できる。複数のダミー層や複雑な形状のダミー層を設けることで、柱状スペーサの密着性を向上させることもできる。

#### 【図面の簡単な説明】

#### 【0030】

【図1】画素構造を示す上面図および断面図。

50

- 【図2】画素構造を示す上面図。

【図3】画素構造を示す上面図。

【図4】着色層の配置を示す平面図。

【図5】対向電極の形状を示す平面図。

【図6】画素構造を示す上面図及び断面図。

【図7】電子機器の一例を示す図。

【図8】電子機器の一例を示す図。

【図9】電子機器の一例を示す図。

## 【発明を実施するための形態】

## 【0031】

10

本発明の実施形態について、以下に説明する。

## 【0032】

## (実施の形態1)

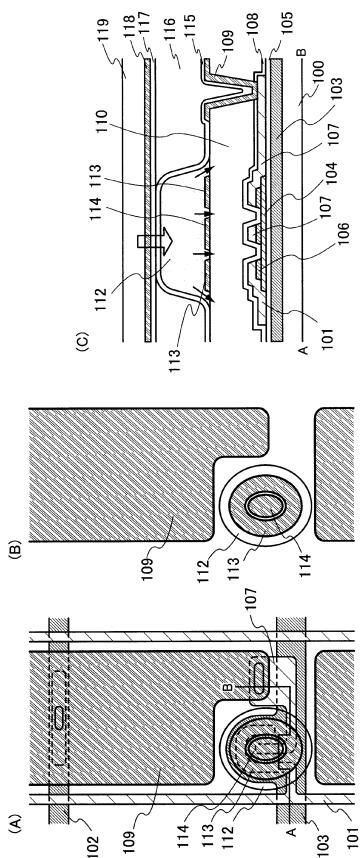

図1(A)は、アクティブマトリクス型の液晶表示装置の画素部における1画素の上面図を示している。また、図1(C)に図1(A)中の線A-Bで切断した断面図を示す。

## 【0033】

20

ソース配線101とゲート配線103の交点付近にアクティブ素子を配置する。ここではアクティブ素子としてTFTを用い、このTFTが画素電極109と電気的に接続され、スイッチング素子として機能する。TFTのオン状態或いはオフ状態をゲート配線103に印加する電圧で制御することで画素電極109近傍の液晶層の配向を変化させることにより、液晶表示装置を駆動させる。本発明は、このTFTと重なる位置に第1のダミー層113、第2のダミー層114、及び柱状スペーサ112を形成する。ここでは非晶質半導体膜を用いたボトムゲート型のTFTを形成する例を示す。

## 【0034】

また、ボトムゲート型(逆スタガ型)TFTに限定されず、TFT構造に関係なく本発明を適用することが可能であり、例えば、トップゲート型TFTや、順スタガ型TFTを用いることが可能である。また、シングルゲート構造のトランジスタに限定されず、複数のチャネル形成領域を有するマルチゲート型トランジスタ、例えばダブルゲート型トランジスタとしてもよい。TFTの作製方法は特に限定されず、公知の技術を用いて作製すればよい。

30

## 【0035】

まず、ガラス基板などの絶縁表面を有する基板100上にゲート配線103及び容量配線102を形成する。次いで、ゲート配線103及び容量配線102を覆うゲート絶縁膜105を形成する。

## 【0036】

次いで、ゲート絶縁膜105上に非晶質半導体膜、例えばアモルファスシリコン膜をPCVD法で形成し、非晶質半導体膜のエッチングを選択的に行って所望の上面形状とし、ゲート絶縁膜105を介してゲート配線103と重なる半導体層104を形成する。次いで、半導体にn型を付与する不純物元素を含む半導体膜を形成し、その半導体膜のエッチングを選択的に行って所望の上面形状とし、半導体層104上に第1のn型半導体層を形成する。次いで、第1のn型半導体層上に導電膜を形成し、導電膜のエッチングを選択的に行って所望の上面形状とし、ソース配線101と、ドレイン電極107と、容量電極を形成する。なお、容量電極は、ゲート絶縁膜105を介して容量配線102と重なり、ゲート絶縁膜105を誘電体とする補助容量を形成している。次いで、ソース配線101及びドレイン電極をマスクとして、第1のn型半導体層を自己整合的なエッチングを行って第2のn型半導体層106を形成する。さらにソース配線101及びドレイン電極をマスクとして、露呈している半導体層104の上部をエッチングして、ソース配線101及びドレイン電極と重なる領域よりも膜厚の薄い部分を形成する。こうしてチャネルエッチ型のTFTが形成される。次いで、露呈している半導体層を覆う保護膜108を形成する。以上の工程は、公知の技術を応用することで実施が可能である。

40

50

**【 0 0 3 7 】**

また、本実施の形態では、非晶質半導体膜をチャネル形成領域とするTFTの例を示したが、特に限定されず、結晶質半導体膜、例えばポリシリコン膜や微結晶シリコン膜をチャネル形成領域とするTFTとしてもよい。

**【 0 0 3 8 】**

次いで、層間絶縁膜として機能する平坦化膜110を形成する。次いで、平坦化膜110及び保護膜108のエッティングを選択的に行い、ドレイン電極に達する第1の開口と、容量電極に達する第2の開口を形成する。次いで、平坦化膜110上に透明導電膜を形成する。

**【 0 0 3 9 】**

透明導電膜の材料としては、インジウム錫酸化物(ITO)の他、例えば、Si元素を含むインジウム錫酸化物(ITSO)や酸化インジウムに酸化亜鉛(ZnO)を混合したIZO(Indium Zinc Oxide)などの透明導電材料、もしくはこれらを組み合わせた化合物を用いることができる。

**【 0 0 4 0 】**

次いで、透明導電膜のエッティングを選択的に行い、TFTと重なる第1のダミー層113及び第2のダミー層114と、ドレイン電極及び容量電極と電気的に接続する画素電極109を形成する。また、ダミー層は、TFTと重なる位置に配置され、後に行われる一対の基板の貼り合わせ工程時にTFTにかかる圧力を分散し、緩和することができる。第1のダミー層113、第2のダミー層114、及び画素電極109は同じ材料である。図1(A)では、第1のダミー層113は、少なくともTFTのチャネル形成領域の一部、ソース電極の一部、及びドレイン電極の一部と重なっている。また、第2のダミー層114は少なくともTFTのチャネル形成領域の一部、及びドレイン電極の一部と重なっている。また、ここでは図示しないが、後にFPCと接続させるための端子電極も画素電極と同一工程で同一基板上に形成する。

**【 0 0 4 1 】**

次いで、第1のダミー層113、第2のダミー層114、及び画素電極109を覆う絶縁膜を形成する。この絶縁膜の材料としては、エポキシ樹脂、アクリル樹脂、フェノール樹脂、ノボラック樹脂、メラミン樹脂、ウレタン樹脂等の樹脂材料を用いる。他にも、絶縁膜の材料としてベンゾシクロブテン、パリレン、ポリイミドなどの有機材料、シロキサン系ポリマー等の重合によってできた化合物材料、水溶性ホモポリマーと水溶性共重合体を含む組成物材料等を用いることができる。また、遮光膜としての機能を持たせるために、上述した材料にカーボンなどの顔料を含ませて黒色の樹脂としてもよい。

**【 0 0 4 2 】**

次いで、この絶縁膜のエッティングを選択的に行い、第1のダミー層113及び第2のダミー層114と重なる柱状スペーサ112を形成する。また、柱状スペーサ112はTFTと重なる。図1(A)では、柱状スペーサ112は少なくともTFTのチャネル形成領域、ソース電極の一部、及びドレイン電極の一部と重なっている。なお、図1(A)を分かりやすくするために、図1(B)の上面図には、平坦化膜110上に形成する第1のダミー層113、第2のダミー層114、画素電極109、及び柱状スペーサ112のみを示している。

**【 0 0 4 3 】**

図1(B)に示すように第1のダミー層113、及び第2のダミー層114は円状のスリットにより離間されており、第1のダミー層113を覆うように柱状スペーサ112を形成している。また、後に行われる一対の基板の貼り合わせ工程時にかかる圧力を分散するため、図1(C)に示すように柱状スペーサ112の断面形状を台形とすることが好ましい。なお、図1(C)中の白抜きの矢印が一対の基板の貼り合わせ工程時にかかる圧力を模式的に表しており、複数の黒矢印が分散された圧力を模式的に表している。また、柱状スペーサ112を錐形台状として、対向基板側と接触する柱状スペーサの上面面積よりもTFT側の底面面積を広くすることが好ましい。

10

20

30

40

50

**【 0 0 4 4 】**

第1のダミー層113及び第2のダミー層114は、柱状スペーサ112の密着性を向上させている。また、この柱状スペーサ112は、第1のダミー層113と画素電極109とが短絡するのを防ぐ効果も果たしている。また、柱状スペーサ112として黒色の樹脂を用いた場合、TFTと重なる遮光膜として機能させることもできる。

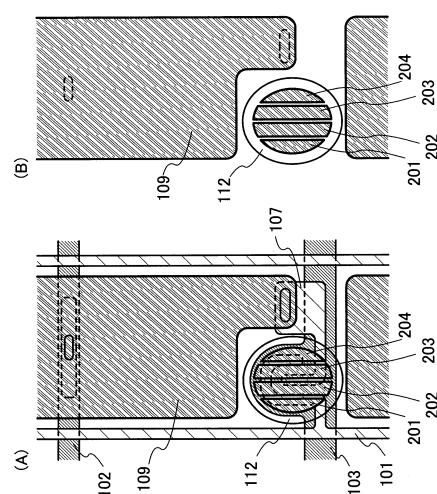

**【 0 0 4 5 】**

なお、柱状スペーサ112と重なるダミー層の個数や形状は、限定されず、例えば図2(A)で示すような上面形状としてもよい。図2(A)はダミー層の形状及び個数が異なる以外は、図1(A)と構造が同一である。また、図2(B)は、図2(A)を分かりやすくするため平坦化膜上に形成する第1のダミー層201、第2のダミー層202、第3のダミー層203、第4のダミー層204、画素電極109、及び柱状スペーサ112のみを示している。柱状スペーサの外周縁よりも内側の位置に配置するダミー層の個数が多いほうが、柱状スペーサと層間絶縁膜との密着性の向上がより一層図れる。

10

**【 0 0 4 6 】**

また、図1または図2では、ダミー層を柱状スペーサの外周縁よりも内側の位置に配置する例を示したが、特に限定されず、各画素電極と間隔を空けて網目状に連続するパターン形状としてもよい。網目状に連続するパターン形状としたダミー層と一部重なり、且つ、TFTと重なるように柱状スペーサを設ければよい。網目状に連続するパターン形状としたダミー層は、隣り合う画素電極間で発生する電界の乱れに起因する光漏れ、所謂ディスクリネーションを防止することもできる。即ち、網目状に連続するパターン形状としたダミー層は、電界遮蔽パターンとして機能する。

20

**【 0 0 4 7 】**

こうして基板100上に柱状スペーサ112を形成した後、基板100と対向基板119とを所定の間隔を保持したまま貼り合わせる。基板間隔は、ダミー層及び柱状スペーサで決定される。本実施の形態では、液晶材料の種類や特性によって異なってくるが、3~4μmとする。

**【 0 0 4 8 】**

また、一対の基板間には液晶層116を充填する。液晶滴下法を用いる場合は、一方の基板に閉ループ形状のシール材を形成し、そのシール材に囲まれた領域に液晶材料を滴下した後、減圧雰囲気とし、もう一方の基板を貼り合わせる。また、液晶注入法を用いる場合には、一対の基板を貼り合わせた後、シール材パターンの液晶注入口から毛細管現象を用いて液晶材料を注入する。シール材にフィラーを含ませることによって一対の基板間隔を維持してもよい。

30

**【 0 0 4 9 】**

また、液晶層116の液晶分子を配向させるための配向膜を両方の基板にそれぞれ形成する。図1(C)に示すように、基板100上には第1の配向膜115を形成し、対向基板119上には対向電極118及び第2の配向膜117を形成する。そして、それぞれラビング処理を行う。液晶の配向モードとしては、液晶分子の配列が光の入射から射出に向かって90°ツイスト配向したTNモードを用いる場合が多い。TNモードの液晶表示装置を作製する場合には、基板100上の配向膜に施したラビング処理のラビング方向と、対向基板119上の配向膜に施したラビング処理のラビング方向が直交するように貼り合わせる。ここでは液晶分子を配向させるために配向膜を用いる例を示したが、特に限定されず、他の配向方法、例えば光配向方法などを用いててもよい。

40

**【 0 0 5 0 】**

なお、端子電極が形成されている部分には、配向膜を形成しない。また、対向基板119と基板100とを貼り合わせた後、端子電極が形成されている部分は、対向基板とも重ならないように対向基板の一部を除去する。次いで、外部回路と接続するためのFPC(フレキシブルプリント配線板)を端子電極に貼り合わせる。FPCを実装する方法は異方導電性材料もしくはメタルバンプを用いた接続方法またはワイヤボンディング方式を採用することができる。また、外部回路と接続させるコネクターとしてはFPCに限定されず、

50

他のコネクター、TAB (Tape Automated Bonding) テープもしくはTCP (Tape Carrier Package) を用いてもよい。TCPはTABテープにICを実装したものであり、TABテープを素子形成基板上の配線に接続してICを実装する。

#### 【0051】

また、画素部の周辺には、画素部へ各信号を伝送する駆動回路が形成されたICチップを異方導電性材料により電気的に接続してもよい。また、カラー表示に対応した画素部を形成するためには、例えば、XGAクラスでデータ線の本数が3072本であり走査線が768本必要となる。このような数で形成されたデータ線及び走査線は画素部の端部で数ブロック毎に区分して引出線を形成し、ICチップの出力端子のピッチに合わせて集める。

ICチップは、公知の方法、例えばCOG (Chip On Glass) 方式により実装すればよい。

10

#### 【0052】

また、必要であれば、基板100または対向基板119に偏光板、又は円偏光板（楕円偏光板を含む）、位相差板（1/4板、1/2板）、カラーフィルタなどの光学フィルムを適宜設けてよい。

#### 【0053】

以上の工程でアクティブマトリクス型の液晶表示装置を有する表示モジュールを作製できる。

#### 【0054】

20

また、上述した液晶表示装置としては、特に限定されず、TN液晶、IPS液晶、OCB液晶、STN液晶、VA液晶、ECB型液晶、GH液晶、高分子分散型液晶、ディスコティック液晶などを用いることができるが、中でもノーマリーブラック型の液晶パネル、例えば垂直配向（VA）モードを採用した透過型の液晶表示装置とすることが好ましい。垂直配向モードとしては、いくつか挙げられるが、例えば、MVA (Multi-Domain Vertical Alignment) モード、PVA (Patterned Vertical Alignment) モード、ASVモードなどを用いることができる。具体的には、1画素を複数のサブピクセルに分割し、各サブピクセルの中央に位置する対向基板の箇所に凸部を設けることで1画素をマルチドメイン化する。1画素を複数のサブピクセルとし、各サブピクセルの中央に位置する対向基板に凸部を設けることで、1画素を配向分割（マルチドメイン化）し、広視野角を実現する駆動方法は、サブピクセル駆動と呼ばれる。なお、凸部は、対向基板または素子基板の一方または両方に設けてもよく、放射状に液晶分子を配向させ、配向規制力を向上させる。

30

#### 【0055】

また、液晶駆動用の電極、即ち画素電極の上面形状を櫛歯状やジグザグ状として、電圧のかかる方向を多様化させてよい。また、光配向を用いて1画素をマルチドメイン化してもよい。

#### 【0056】

40

また、画素電極に接続するスイッチング素子としては、非晶質構造を有する半導体膜を用いたアモルファス TFT に限定されず、有機トランジスタや、ポリシリコン TFT などの3端子型のアクティブ素子、或いは、ダイオード、MIM、ZnOバリスタなどの2端子型のアクティブ素子を用いることができる。

#### 【0057】

##### (実施の形態2)

実施の形態1では、素子基板上に柱状スペーサを形成する例を示したが、本実施の形態では、対向基板上に柱状スペーサを形成する例を示す。

#### 【0058】

まず、実施の形態1と同様にしてダミー層と画素電極を同一の素子基板上に形成する。なお、ダミー層は、スイッチング素子と重なる位置に配置される。本実施の形態では、スイッチング素子として、結晶構造を有する半導体膜、例えばポリシリコン膜を用いたトップ

50

ゲート型 TFT を用いる。トップゲート型 TFT は、n チャネル型 TFT であっても p チャネル型 TFT であってもよい。また、ここでは、電気特性のバラツキを低減させるため、ダブルゲート構造とする。また、オフ電流値を低減するため、n チャネル型 TFT を低濃度ドレイン (LDD : Lightly Doped Drain) 構造としてもよい。この LDD 構造はチャネル形成領域と、高濃度に不純物元素を添加して形成するソース領域またはドレイン領域との間に低濃度に不純物元素を添加した領域を設けたものであり、この領域を LDD 領域と呼んでいる。LDD 構造はドレイン近傍の電界を緩和してホットキャリア注入による劣化を防ぐ効果がある。また、ホットキャリアによるオン電流値の劣化を防ぐため、n チャネル型 TFT を GOLD (Gate-drain Overlap ped LDD) 構造としてもよい。ゲート絶縁膜を介して LDD 領域をゲート電極と重ねて配置させた構造である GOLD 構造は、LDD 構造よりもさらにドレイン近傍の電界を緩和してホットキャリア注入による劣化を防ぐ効果がある。このような GOLD 構造とすることで、ドレイン近傍の電界強度が緩和されてホットキャリア注入を防ぎ、劣化現象の防止に有効である。また、画素電極は、スイッチング素子と電気的に接続させる。

#### 【0059】

ダミー層も画素電極も透明導電膜、代表的にはITOで形成するため、工程を増やすことなく、緩衝材を設けることができる。また、ダミー層が透光性を有しているため、光の乱反射などがほとんど生じない。そして、ダミー層及び画素電極を接して覆う配向膜を形成する。

#### 【0060】

素子基板と貼り合わせるための対向基板を用意する。対向基板には、カラーフィルタや対向電極を形成する。これらの積層順は特に限定されないが、ここでは、カラーフィルタ上に対向電極を形成する。

#### 【0061】

そして、対向基板の対向電極上に、柱状スペーサを設ける。必要があれば、柱状スペーサを接して覆う配向膜を形成する。柱状スペーサとダミー層が重なるように、素子基板と対向基板とを貼り合わせる。従って、柱状スペーサもスイッチング素子と重なる位置に配置される。また、この柱状スペーサとして、カーボンなどの顔料を含ませた黒色樹脂を用いてスイッチング素子の遮光膜として機能させることが好ましい。

#### 【0062】

ダミー層は、素子基板と対向基板とを貼り合わせる工程時にスイッチング素子にかかる圧力を分散し、緩和することができる。また、ダミー層は、圧力を分散し、緩和するのであれば、特に形状や個数は限定されず、複数、または、複雑な形状、例えば S 字形状、M 字形状、十文字形状などであってもよい。特に柱状スペーサを対向基板に設ける場合、柱状スペーサの頂部とダミー層とが配向膜を介して重なるため、柱状スペーサの頂部の面積よりも総面積が広いダミー層とすることが好ましい。この場合、ダミー層の端部が柱状スペーサの外側に突出する形状となる。

#### 【0063】

また、柱状スペーサをスイッチング素子と重なるように配置する場合、スイッチング素子周辺は、他の場所に比べ隣合う画素電極との間隔が広くマージンが十分あるため、貼り合わせ時に位置ズレが生じてもほとんど問題ない。即ち、貼り合わせ工程によって柱状スペーサが画素電極と重なり開口率が低下してしまうことを低減することができる。また、画素電極と柱状スペーサが重ならなければ、意図的にダミー層の端部が柱状スペーサの外側に位置するように貼り合わせてもよい。

#### 【0064】

対向基板に柱状スペーサを設けても、スイッチング素子と柱状スペーサの間に緩衝材となるダミー層を画素電極と同じ材料で形成することにより、工程を増やすことなく、スイッチング素子を保護することができる。

#### 【0065】

また、本実施の形態は、実施の形態 1 と自由に組み合わせることができる。

10

20

30

40

50

**【0066】**

以上の構成でなる本発明について、以下に示す実施例でもってさらに詳細な説明を行うこととする。

**【実施例1】****【0067】**

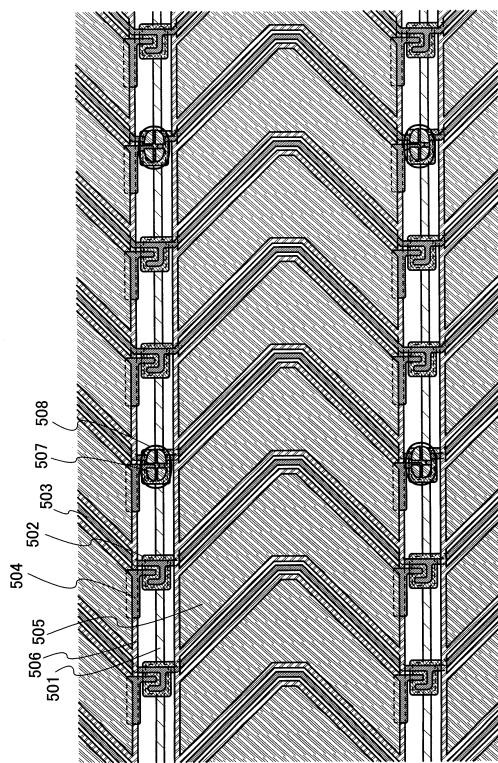

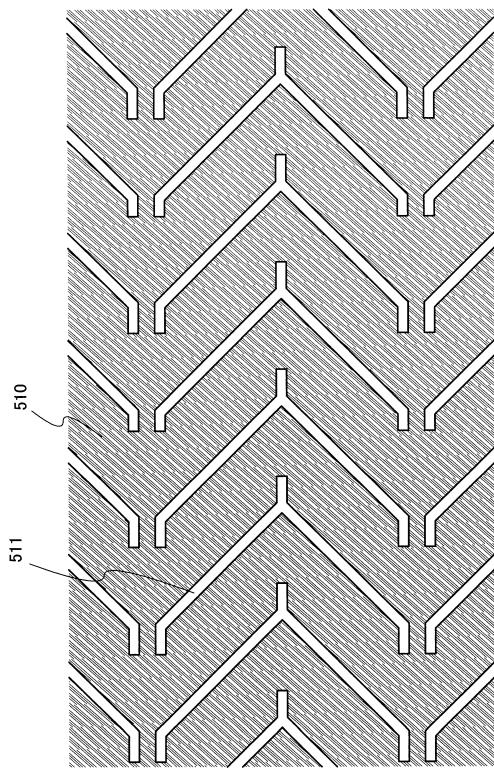

本実施例では、垂直配向（VA）モードを採用した透過型の液晶表示装置の一例を図3、図4、及び図5を用いて説明する。

**【0068】**

図3は、VA型液晶パネル（具体的にはPVAモードのパネル）の画素構造の平面図を示す図である。各画素電極505の上面形状は、図3に示すように、複雑な八角形となっている。画素部には、ゲート配線501と、ソース配線503と、容量配線506とが配置され、ゲート配線とソース配線の交点付近に半導体層502が配置されている。ここではゲート配線、ソース配線、及び半導体層を含むボトムゲート型のTFTをスイッチング素子としている。ドレイン電極は、TFTのドレイン領域と画素電極505との電気的な接続を行うための電極である。ドレイン電極504は、容量配線506と一部重なり、保持容量を形成している。

10

**【0069】**

また、画素電極と同じ材料で形成されているダミー層507がTFTと重なる位置に4つ設けられている。これらのダミー層507を覆うように柱状スペーサ508を設けている。柱状スペーサ508もTFTと重なる位置に設けられ、基板間隔を調節している。これらのダミー層507をTFTと重なる位置に配置することによって、一対の基板の貼り合わせ工程時にTFTにかかる圧力を分散し、緩和する効果がある。また、これらのダミー層507は、柱状スペーサ508の密着性を向上させるために形成している。また、柱状スペーサ508は、3つの画素電極に対して一つ設けているが、特に限定されず、例えば各画素電極にそれぞれ設けてよい。また、柱状スペーサ508として黒色樹脂を用いてブラックマトリクスの機能を持たせてもよい。また、黒色樹脂を用いた場合、TFTの遮光膜としても機能させることができる。

20

**【0070】**

図4は、カラーフィルタの一部の上面図を示す図である。図4は、第1着色層401（R）、第2着色層402（G）、及び第3着色層403（B）の3色を用いて1つの画素群を構成している。各着色層の上面形状は、画素電極505の形状と同様に、複雑な八角形となっている。

30

**【0071】**

図5に対向基板側の構造を示す。対向電極510は異なる画素間で共通化されている電極であるが、スリット511が形成されている。このスリット511と、画素電極505及び画素電極505側のスリット（隣り合う画素電極の隙間）とを交互に咬み合うように配置することで、斜め電界を効果的に発生させて液晶の配向を制御することができる。これにより、液晶が配向する方向を場所によって異ならせることができ、視野角を広げている。

40

**【0072】**

このようにダミー層507及び柱状スペーサ508を設けることで、柱状スペーサの密着性を向上させることができる。また、TFTを作製した箇所は他の箇所よりも積層数が多くトータルの膜厚が厚くなりやすいため、TFTと重なる位置に柱状スペーサを形成すると、基板間隔を調節しやすいというメリットを有する。また、本発明は、ダミー層507及び柱状スペーサ508を設けることで、高開口率、且つ高精細化を実現できる液晶表示装置を実現できる。また、工程を増やすことなく、外光下で高い表示品質を実現できる液晶表示装置を実現できる。

**【0073】**

また、本実施例は、実施の形態1、または実施の形態2と自由に組み合わせができる。

50

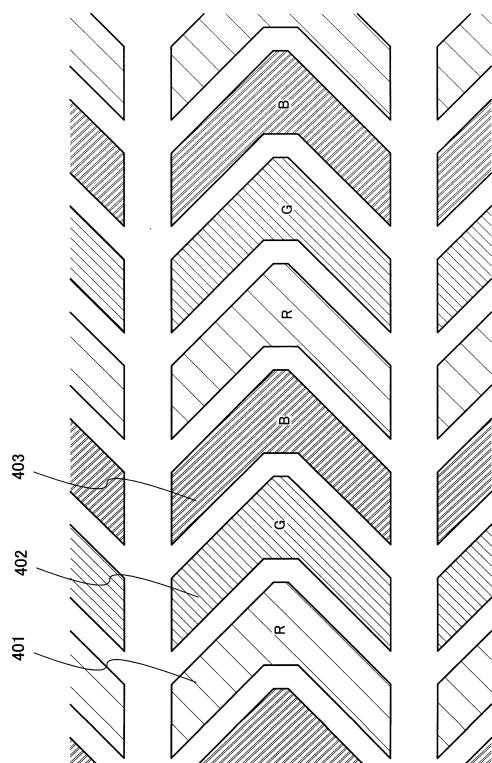

**【実施例 2】****【0074】**

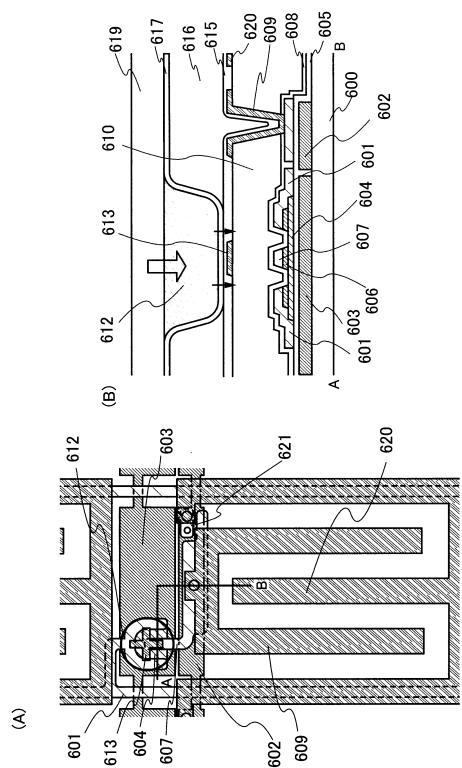

実施の形態では TN 方式の液晶表示装置の一例を示したが、本実施例では IPS ( In Plane Switching ) 方式の液晶表示装置の一例を図 6 ( A ) 及び図 6 ( B ) に示す。

**【0075】**

図 6 ( A ) は、IPS 方式の液晶表示装置の画素部における 1 画素の上面図を示している。また、図 6 ( B ) に図 6 ( A ) 中の線 A - B で切断した断面図を示す。

**【0076】**

IPS 方式の液晶表示装置は、液晶を挟持する一対の基板のうち、一方の基板 600 に画素電極 609 および共通電極 620 を形成し、これらの電極間に生じる基板面にほぼ平行な電界で液晶分子を回転させることで光のスイッチングを行い、表示を行う方式である。

10

**【0077】**

基板 600 上には、ソース配線 601 とゲート配線 603 の交点付近にアクティプ素子を配置する。ここではアクティプ素子として TFT を用い、この TFT が画素電極 609 と電気的に接続され、スイッチング素子として機能する。TFT のオン状態或いはオフ状態をゲート配線 603 に印加する電圧で制御し、画素電極 609 と共通電極 620 の間に電界（この電界を横電界とも呼ぶ）を形成して液晶層 616 に含まれる液晶分子をほぼ平行な面内で回転させることにより、液晶表示装置を駆動させる。

**【0078】**

液晶層 616 に含まれる液晶分子をほぼ平行な面内で回転させるために、視野角によって階調、色調の反転が生じることなく、TN 方式に比べて視野角を広くすることができる。なお、IPS 方式は、TN 方式とは一対の偏光板の配置が異なり、画素電極への電圧無印加時に黒表示となるように配置する。

20

**【0079】**

本発明は、この TFT と重なる位置に十文字形状のダミー層 613 形成する。ここでは非晶質半導体膜 604 を用いたボトムゲート型の TFT を形成する例を示す。

**【0080】**

まず、ガラス基板などの絶縁表面を有する基板 600 上にゲート配線 603 及び容量配線 602 を形成する。次いで、ゲート配線 603 及び容量配線 602 を覆うゲート絶縁膜 605 を形成する。次いで、ゲート絶縁膜に選択的なエッチングを行い、ゲート配線の先端部に達する開口と、容量配線に達する開口を形成する。

30

**【0081】**

次いで、ゲート絶縁膜 605 上に非晶質半導体膜、例えばアモルファスシリコン膜を P C VD 法で形成し、非晶質半導体膜のエッチングを選択的に行って所望の上面形状とし、ゲート絶縁膜 605 を介してゲート配線 603 と重なる半導体層を形成する。次いで、半導体に n 型を付与する不純物元素を含む半導体膜を形成し、その半導体膜のエッチングを選択的に行って所望の上面形状とし、半導体層上に第 1 の n 型半導体層を形成する。次いで、第 1 の n 型半導体層上に導電膜を形成し、導電膜のエッチングを選択的に行って所望の上面形状とし、ソース配線 601 と、ドレイン電極 607 と、接続電極 621 を形成する。

40 なお、ドレイン電極 607 は、ゲート絶縁膜 605 を介して容量配線 602 と重なり、ゲート絶縁膜 605 を誘電体とする補助容量を形成している。また、接続電極 621 は、ゲート絶縁膜の開口を介して容量配線 602 と電気的に接続し、さらに後に形成される共通電極 620 とを電気的に接続するために設けられる。

**【0082】**

次いで、ソース配線 601 及びドレイン電極 607 をマスクとして、第 1 の n 型半導体層を自己整合的なエッチングを行って第 2 の n 型半導体層 606 を形成する。さらにソース配線 601 及びドレイン電極 607 をマスクとして、露呈している半導体層の上部をエッチングして、ソース配線 601 及びドレイン電極 607 と重なる領域よりも膜厚の薄い部分を形成する。こうしてチャネルエッチ型の TFT が形成される。次いで、露呈している

50

半導体層を覆う保護膜 608 を形成する。以上の工程は、公知の技術を応用することで実施が可能である。

#### 【0083】

次いで、層間絶縁膜として機能する平坦化膜 610 を形成する。次いで、平坦化膜 610 及び保護膜 608 のエッティングを選択的に行い、ドレイン電極に達する第1の開口と、接続電極 621 に達する第2の開口を形成する。次いで、平坦化膜 610 上に透明導電膜を形成する。

#### 【0084】

透明導電膜の材料としては、インジウム錫酸化物 (ITO) の他、例えば、Si 元素を含むインジウム錫酸化物 (ITSO) や酸化インジウムに酸化亜鉛 (ZnO) を混合したIZO (Indium Zinc Oxide) などの透明導電材料、もしくはこれらを組み合わせた化合物を用いることができる。10

#### 【0085】

次いで、透明導電膜のエッティングを選択的に行い、TFT と重なるダミー層 613 と、ドレイン電極と電気的に接続する画素電極 609 と、接続電極 621 と電気的に接続する共通電極 620 とを形成する。また、ダミー層 613 は、TFT と重なる位置に配置され、後に行われる一対の基板の貼り合わせ工程時に TFT にかかる圧力を分散し、緩和することができる。図 6 (A) では、ダミー層 613 は少なくとも TFT のチャネル形成領域の一部、ソース電極の一部、及びドレイン電極の一部と重なっている。ダミー層 613、共通電極 620、及び画素電極 609 は同じ材料である。また、ここでは図示しないが、後に FPC と接続させるための端子電極も画素電極と同一工程で同一基板上に形成する。20

#### 【0086】

また、本実施例では、共通電極 620 及び画素電極 609 は同じ材料とし、同じ絶縁膜上に形成したが、特に限定されず、例えば、金属材料からなる共通電極を形成した後、絶縁膜を形成し、その絶縁膜の上に透明導電膜からなる画素電極を設けた構造としてもよい。

#### 【0087】

次いで、ダミー層 613、共通電極 620、及び画素電極 609 を覆う第1の配向膜 615 を形成する。次いで、第1の配向膜 615 にラビング処理を行う。

#### 【0088】

そして、対向基板 619 を用意する。対向基板には、柱状スペーサ 612 を形成する。なお、必要であれば、柱状スペーサを形成する前に、カラーフィルタなどを設けてもよい。30

#### 【0089】

柱状スペーサ 612 の材料としては、エポキシ樹脂、アクリル樹脂、フェノール樹脂、ノボラック樹脂、メラミン樹脂、ウレタン樹脂等の樹脂材料を用いる。他にも、柱状スペーサの材料としてベンゾシクロブテン、パリレン、ポリイミドなどの有機材料、シロキサン系ポリマー等の重合によってできた化合物材料、水溶性ホモポリマーと水溶性共重合体を含む組成物材料等を用いることができる。また、遮光膜としての機能を持たせるために、上述した材料にカーボンなどの顔料を含ませて黒色の樹脂としてもよい。

#### 【0090】

次いで、柱状スペーサ 612 を覆う第2の配向膜 617 を形成する。次いで、第2の配向膜 617 にラビング処理を行う。40

#### 【0091】

そして、基板 600 と対向基板 619 とを所定の間隔を保持したまま貼り合わせる。対向基板 619 に設けた柱状スペーサと、基板 600 に設けたダミー層 613 とが重なるように貼り合わせ、固定する。基板間隔は、ダミー層及び柱状スペーサで決定される。本実施の形態では、液晶材料の種類や特性によっても異なってくるが、2 ~ 6 μm とする。

#### 【0092】

図 6 (A) では十文字のダミー層を柱状スペーサの外周縁よりも内側の位置に配置する例を示したが、特に限定されず、各画素電極と間隔を空けて複雑に連続するパターン形状としてもよい。複雑に連続するパターン形状としたダミー層と一部重なり、且つ、TFT と50

重なるように、ダミー層及び TFT が設けられた基板 600 と、柱状スペーサが設けられた対向基板 619 を位置合わせすればよい。図 6 (A) では、柱状スペーサ 612 は少なくとも TFT のチャネル形成領域、ソース電極の一部、及びドレイン電極の一部と重なっている。また、柱状スペーサから突出したダミー層の一部を用いて、隣り合う画素電極間で発生する電界の乱れに起因する光漏れ、所謂ディスクリネーションを防止してもよい。

#### 【0093】

また、一対の基板間には液晶層 616 を充填する。液晶滴下法を用いる場合は、一方の基板に閉ループ形状のシール材を形成し、そのシール材に囲まれた領域に液晶材料を滴下した後、減圧雰囲気とし、もう一方の基板を貼り合わせる。また、液晶注入法を用いる場合には、一対の基板を貼り合わせた後、シール材パターンの液晶注入口から毛細管現象を用いて液晶材料を注入する。シール材にフィラーを含ませることによって一対の基板間隔を維持してもよい。10

#### 【0094】

また、必要であれば、基板 600 または対向基板 619 に偏光板、又は円偏光板（橙円偏光板を含む）、位相差板（ $\frac{1}{4}$  板、 $\frac{1}{2}$  板）などの光学フィルムを適宜設けてよい。10

#### 【0095】

以上の工程で IPS 方式の液晶表示装置を有する表示モジュールを作製できる。

#### 【0096】

本発明は、ダミー層を一方の基板に設け、もう一方の基板に柱状スペーサを設けることで、IPS 方式の液晶表示装置の高い歩留まりを実現できる。20

#### 【0097】

また、本実施例は、実施の形態 1、または実施の形態 2 と自由に組み合わせができる。

#### 【実施例 3】

#### 【0098】

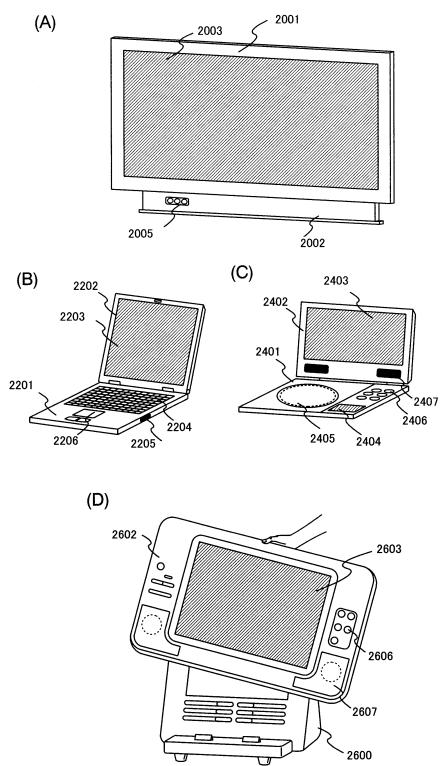

本発明の液晶表示装置、及び電子機器として、ビデオカメラ、デジタルカメラ、ゴーグル型ディスプレイ（ヘッドマウントディスプレイ）、ナビゲーションシステム、音響再生装置（カーオーディオ、オーディオコンポ等）、ノート型パソコンコンピュータ、ゲーム機器、携帯情報端末（モバイルコンピュータ、携帯電話、携帯型ゲーム機又は電子書籍等）、記録媒体を備えた画像再生装置（具体的には Digital Versatile Disc (DVD) 等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置）などが挙げられる。それら電子機器の具体例を図 7、及び図 8 に示す。30

#### 【0099】

図 7 (A) は 22 インチ～50 インチの大画面を有する大型の表示装置であり、筐体 2001、支持台 2002、表示部 2003、ビデオ入力端子 2005 等を含む。表示部 2003 が実施例 1 の液晶モジュールに相当する。なお、表示装置は、パソコンコンピュータ用、TV 放送受信用、双向 TV 用などの全ての情報表示用表示装置が含まれる。本発明により、1 辺が 1000 mm を超える第 5 世代以降のガラス基板を用いても、大型表示装置の高開口率、且つ高精細化を実現できる。40

#### 【0100】

図 7 (B) はノート型パソコンコンピュータであり、本体 2201、筐体 2202、表示部 2203、キーボード 2204、外部接続ポート 2205、ポインティングデバイス 2206 等を含む。本発明により、ノート型パソコンコンピュータの高開口率、且つ高精細化を実現できる。

#### 【0101】

図 7 (C) は記録媒体を備えた携帯型の画像再生装置（具体的には DVD 再生装置）であり、本体 2401、筐体 2402、表示部 A 2403、表示部 B 2404、記録媒体 (DVD 等) 読込部 2405、操作キー 2406、スピーカー部 2407 等を含む。表示部 A 2403 は主として画像情報を表示し、表示部 B 2404 は主として文字情報を表示する50

。なお、記録媒体を備えた画像再生装置には家庭用ゲーム機器なども含まれる。本発明により、画像再生装置の高開口率、且つ高精細化を実現できる。

#### 【0102】

図7(D)は、ワイヤレスでディスプレイのみを持ち運び可能なTVである。筐体2602にはバッテリー及び信号受信器が内蔵されており、そのバッテリーで表示部2603やスピーカ部2607を駆動させる。バッテリーは充電器2600で繰り返し充電が可能となっている。また、充電器2600は映像信号を送受信することが可能で、その映像信号をディスプレイの信号受信器に送信することができる。筐体2602は操作キー2606によって制御する。また、図7(D)に示す装置は、操作キー2606を操作することによって、筐体2602から充電器2600に信号を送ることも可能であるため映像音声双方方向通信装置とも言える。また、操作キー2606を操作することによって、筐体2602から充電器2600に信号を送り、さらに充電器2600が送信できる信号を他の電子機器に受信させることによって、他の電子機器の通信制御も可能であり、汎用遠隔制御装置とも言える。本発明により、ディスプレイの高開口率、且つ高精細化を実現できる。

10

#### 【0103】

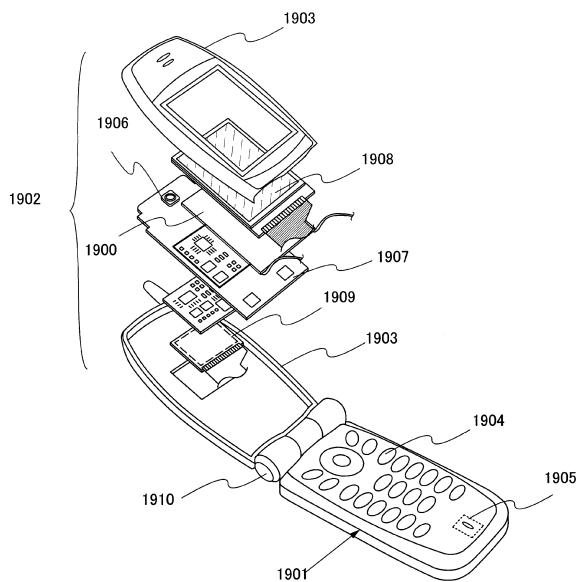

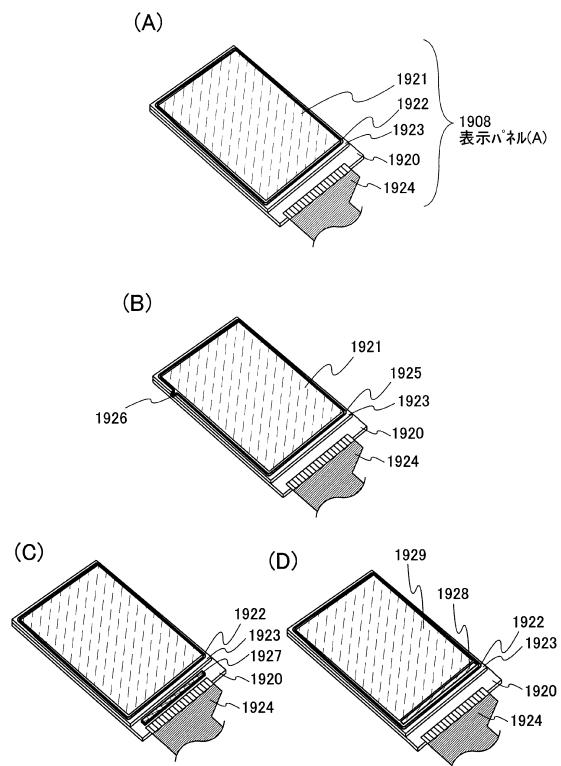

図8で示す携帯電話機は、操作スイッチ類1904、マイクロフォン1905などが備えられた本体(A)1901と、表示パネル(A)1908、バックライト部1900、表示パネル(B)1909、スピーカ1906などが備えられた本体(B)1902とが、蝶番1910で開閉可能に連結されている。表示パネル(A)1908と表示パネル(B)1909は、回路基板1907やバックライト部1900と共に本体(B)1902の筐体1903の中に収納される。表示パネル(A)1908及び表示パネル(B)1909の画素部は筐体1903に形成された開口窓から視認できるように配置される。ここでは、バックライト部1900と表示パネル(A)1908とが重なるように配置して透過型の液晶表示装置としている。バックライト部1900としては、冷陰極管を用いてもよいし、LED素子を用いてもよい。また、バックライト部として、導光板とLED素子との組み合わせを用いてもよい。

20

#### 【0104】

表示パネル(A)1908と表示パネル(B)1909は、その携帯電話機の機能に応じて画素数などの仕様を適宜設定することができる。例えば、表示パネル(A)1908を主画面とし、表示パネル(B)1909を副画面として組み合わせることができる。

30

#### 【0105】

本実施例の携帯電話機は、その機能や用途に応じてさまざまな態様に変容し得る。例えば、蝶番1910の部位に撮像素子を組み込んで、カメラ付きの携帯電話機としても良い。また、操作スイッチ類1904、表示パネル(A)1908、表示パネル(B)1909を一つの筐体内に納めさせた構成としてもよい。

#### 【0106】

また、図9(A)に表示パネル(A)1908の構成の一例を示す。表示パネル(A)1908は、画素電極が設けられた第1の基板1920と、第1の基板と対向する第2基板1923をシール材1922で貼り合わせている。また、シール材1922は表示部1921を囲むように形成されていて、第1の基板と第2基板とシール材で囲まれた領域に液晶層が設けられている。図9(A)に示す表示パネル(A)1908の液晶封止方法は、液晶滴下法を用い、減圧下での基板貼り合わせを行っている。一对の基板間隔は、隙材、具体的には、球状スペーサや柱状スペーサ、またはシール材に含ませたフィラーなどによって保持される。なお、隙材は、表示パネル(A)1908を駆動させる液晶モード(TNモード、VAモード、IPSモードなど)によって適宜選択すればよい。ただし、IPSモードは第2の基板に電極を設けなくともよいが、その他の液晶モードで第2の基板に対向電極を設ける場合が多く、その場合、一对の基板を貼り付ける際に、対向電極と、第1の基板に設けられた端子電極との導通を取るための接続も行う。

40

#### 【0107】

また、図9(B)に図9(A)とは異なる液晶封止方法を用いて作製したパネルの構成例

50

を示す。なお、図9( B )において、図9( A )と共に部分には同じ符号を用いる。図9( B )に示す表示パネルは、第1シール材1925で形成された液晶注入口から液晶を液晶注入法などを用いて注入した後、液晶注入口を第2のシール材1926で封止している。

#### 【0108】

また、図9( C )に図9( A )とは異なるパネル構成の例を示す。なお、図9( C )において、図9( A )と共に部分には同じ符号を用いる。図9( C )のパネルは、表示部を駆動させるための駆動IC1927が第1の基板1920に搭載されている。駆動IC1927を第1の基板1920に搭載することで回路の集積化を行っている。

#### 【0109】

また、図9( D )に図9( A )とは異なるパネル構成の例を示す。なお、図9( D )において、図9( A )と共に部分には同じ符号を用いる。図9( D )のパネルは、表示部1929を駆動させるための駆動回路1928が第1の基板1920に同一基板上に形成されている。駆動回路1928としては、アモルファスシリコン TFT やポリシリコン TFTなどを用いることができる。また、駆動回路だけでなく、その他の回路(光センサ回路、CPUなど)を同一基板上に形成してもよい。

#### 【0110】

図9( A )、図9( B )、図9( C )、及び図9( D )で示した表示パネルに所望の光学フィルム、例えば、偏光板、反射防止フィルム、カラーフィルタなどを重ねてもうける。本発明においては、実施の形態に示したダミー層及び柱状スペーサをTFTと重なる位置に配置することで、液晶表示装置の高開口率、且つ高精細化を実現できる。以上の様に、本発明を実施して得た液晶表示装置は、あらゆる電子機器の表示部として用いても良い。

#### 【0111】

また、本実施例は実施の形態1、実施の形態2、実施例1、または実施例2と自由に組み合わせることができる。

#### 【符号の説明】

##### 【0112】

100：基板

101：ソース配線

102：容量配線

103：ゲート配線

104：半導体層

105：ゲート絶縁膜

106：第2のn型半導体層

107：ドレイン電極

108：保護膜

109：画素電極

110：平坦化膜

112：柱状スペーサ

113：第1のダミー層

114：第2のダミー層

115：第1の配向膜

116：液晶層

117：第2の配向膜

118：対向電極

119：対向基板

201：第1のダミー層

202：第2のダミー層

203：第3のダミー層

204：第4のダミー層

10

20

30

40

50

|                       |    |  |

|-----------------------|----|--|

| 4 0 1 : 第 1 着色層       |    |  |

| 4 0 2 : 第 2 着色層       |    |  |

| 4 0 3 : 第 3 着色層       |    |  |

| 5 0 1 : ゲート配線         |    |  |

| 5 0 2 : 半導体層          |    |  |

| 5 0 3 : ソース配線         |    |  |

| 5 0 4 : ドレイン電極        |    |  |

| 5 0 5 : 画素電極          |    |  |

| 5 0 6 : 容量配線          |    |  |

| 5 0 7 : ダミー層          | 10 |  |

| 5 0 8 : 柱状スペーサ        |    |  |

| 5 1 0 : 対向電極          |    |  |

| 5 1 1 : スリット          |    |  |

| 6 0 0 : 基板            |    |  |

| 6 0 1 : ソース配線         |    |  |

| 6 0 2 : 容量配線          |    |  |

| 6 0 3 : ゲート配線         |    |  |

| 6 0 4 : 非晶質半導体膜       |    |  |

| 6 0 5 : ゲート絶縁膜        |    |  |

| 6 0 6 : 第 2 の n 型半導体層 | 20 |  |

| 6 0 7 : ドレイン電極        |    |  |

| 6 0 8 : 保護膜           |    |  |

| 6 0 9 : 画素電極          |    |  |

| 6 1 0 : 平坦化膜          |    |  |

| 6 1 2 : 柱状スペーサ        |    |  |

| 6 1 3 : ダミー層          |    |  |

| 6 1 5 : 第 1 の配向膜      |    |  |

| 6 1 6 : 液晶層           |    |  |

| 6 1 7 : 第 2 の配向膜      |    |  |

| 6 1 9 : 対向基板          | 30 |  |

| 6 2 0 : 共通電極          |    |  |

| 6 2 1 : 接続電極          |    |  |

| 1 9 0 0 : バックライト部     |    |  |

| 1 9 0 1 : 本体 ( A )    |    |  |

| 1 9 0 2 : 本体 ( B )    |    |  |

| 1 9 0 3 : 筐体          |    |  |

| 1 9 0 4 : 操作スイッチ類     |    |  |

| 1 9 0 5 : マイクロフォン     |    |  |

| 1 9 0 6 : スピーカ        |    |  |

| 1 9 0 7 : 回路基板        | 40 |  |

| 1 9 0 8 : 表示パネル ( A ) |    |  |

| 1 9 0 9 : 表示パネル ( B ) |    |  |

| 1 9 2 0 : 第 1 の基板     |    |  |

| 1 9 2 1 : 表示部         |    |  |

| 1 9 2 2 : シール材        |    |  |

| 1 9 2 5 : 第 1 シール材    |    |  |

| 1 9 2 6 : 第 2 のシール材   |    |  |

| 1 9 2 7 : 駆動 I C      |    |  |

| 1 9 2 8 : 駆動回路        |    |  |

| 2 0 0 1 : 筐体          | 50 |  |

- 2002：支持台

2003：表示部

2005：ビデオ入力端子

2201：本体

2202：筐体

2203：表示部

2204：キー ボード

2205：外部接続ポート

2206：ポインティングデバイス

2401：本体

2402：筐体

2403：表示部 A

2404：表示部 B

2405：読込部

2406：操作キー

2407：スピーカー部

2600：充電器

2602：筐体

2603：表示部

2606：操作キー

2607：スピーカ部

10

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

---

フロントページの続き

(56)参考文献 特開2000-131714(JP,A)

特開2001-93598(JP,A)

特開2001-77374(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 02 F 1 / 1339

G 02 F 1 / 1343

G 02 F 1 / 1368