(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-110366

(P2005-110366A)

(43) 公開日 平成17年4月21日(2005.4.21)

(51) Int.CI.<sup>7</sup>

**H02M 1/08**

**H02M 7/5387**

**H03K 17/28**

**H03K 17/687**

F 1

H02M 1/08

H02M 7/5387

H03K 17/28

H03K 17/687

テーマコード(参考)

A 5H007

Z 5H740

K 5J055

E

審査請求 未請求 請求項の数 2 O L (全 10 頁)

(21) 出願番号

(22) 出願日

特願2003-337695 (P2003-337695)

平成15年9月29日 (2003.9.29)

(71) 出願人 000003218

株式会社豊田自動織機

愛知県刈谷市豊田町2丁目1番地

(74) 代理人 100068755

弁理士 恩田 博宣

(74) 代理人 100105957

弁理士 恩田 誠

(72) 発明者 尾崎 公教

愛知県刈谷市豊田町2丁目1番地 株式会

社豊田自動織機内

F ターム(参考) 5H007 AA06 CA02 CB05 CC03

5H740 AA05 BA12 BB05 NN17

最終頁に続く

(54) 【発明の名称】 ドライブ回路

## (57) 【要約】

【課題】 デッドタイムのパラツキを抑制し、スイッチング素子のターンオン時のスイッチング損失を抑制する。

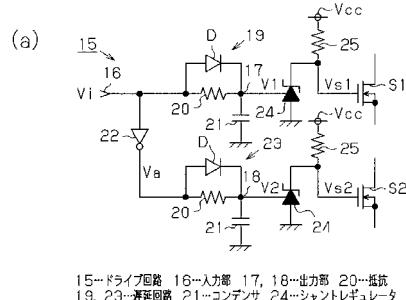

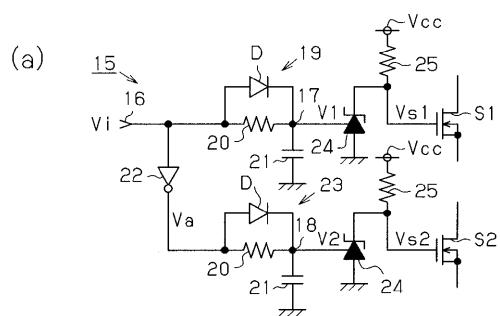

【解決手段】 ドライブ回路15は1個の入力部16と2個の出力部17, 18とを備え、出力部17, 18はそれぞれスイッチング素子S1, S2の制御端子に接続されている。入力部16と出力部17との間には遅延回路19が接続されている。遅延回路19は抵抗20及びコンデンサ21の直列回路を備え、抵抗20の一端が入力部16に接続され、コンデンサ21の他端が接地されている。抵抗20と並列にダイオードDが接続されている。即ち、ダイオードDはコンデンサ21の充電を早める方向に接続されている。入力部16と出力部18との間にはインバータ22及び遅延回路19と同じに構成の遅延回路23が接続されている。遅延回路19, 23の出力部17, 18にはシャントレギュレータ24が接続されている。シャントレギュレータ24はREF端子24aが出力部17, 18に接続されている。

【選択図】 図1

15…ドライブ回路 16…入力部 17, 18…出力部 20…抵抗

19, 23…遅延回路 21…コンデンサ 24…シャントレギュレータ

26…コンパレータ

**【特許請求の範囲】****【請求項 1】**

1個の入力部と該入力部から分岐された2個の出力部との間に設けられ、コンデンサと抵抗とからなる回路の抵抗に対してダイオードが並列に、かつ前記コンデンサの充電を早める方向に接続された2個の遅延回路を有し、前記各出力部に高精度の基準電圧を利用したコンパレータを用いてHレベル及びLレベルの出力を切り換えるデジタル回路が接続されているドライブ回路。

**【請求項 2】**

前記デジタル回路はシャントレギュレータであり、該シャントレギュレータの入力側が前記出力部に接続されている請求項1に記載のドライブ回路。 10

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、ドライブ回路に係り、詳しくはHブリッジ等を駆動する際の駆動信号にデッドタイムを設けるための回路を備えたドライブ回路に関する。 20

**【背景技術】****【0002】**

従来、Hブリッジを駆動する際の駆動信号にデッドタイムを設けるために、専用のタイマ回路を設けていた。ところが、専用のタイマ回路を設けると、回路が複雑になるという問題がある。この問題を解消するため、Hブリッジを駆動するドライブ回路におけるスイッチング素子のターンオンとターンオフに異なった定数を採用する方法が開示されている（例えば、特許文献1参照）。 20

**【0003】**

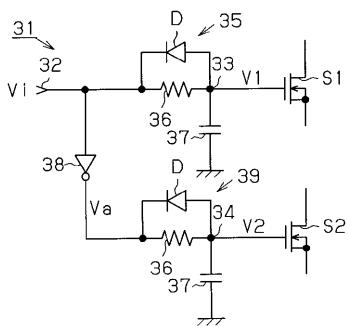

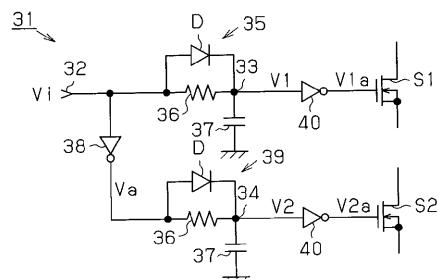

特許文献1には、図5に示すように、2個のスイッチング素子S1, S2を駆動するドライブ回路31として、1個の入力部32と2個の出力部33, 34とを備え、出力部33, 34はそれぞれスイッチング素子S1, S2の制御端子に接続されている。入力部32と第1の出力部33との間には遅延回路35が接続され、遅延回路35は抵抗36及びコンデンサ37の直列回路を備え、抵抗36とコンデンサ37との接続点に出力部33が接続されている。 30

**【0004】**

抵抗36と並列にダイオードDが、コンデンサ37の放電を早める方向、即ちスイッチング素子S1のオンが遅れる方向に接続されている。入力部32と出力部34との間にはインバータ38及び遅延回路39が接続されている。遅延回路39は遅延回路35と同じに構成され、抵抗36とコンデンサ37との接続点に出力部34が接続されている。 30

**【0005】**

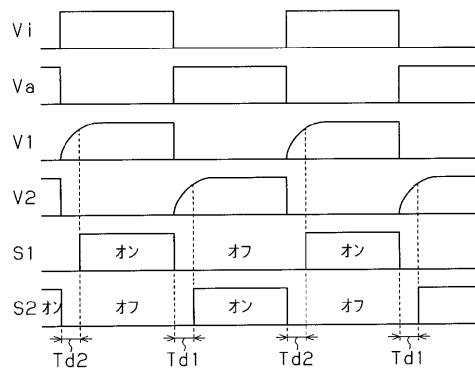

このドライブ回路31では、図6に示すように、駆動信号Viは矩形波の電圧信号として入力され、駆動信号Viが遅延回路35に入力されると、遅延回路35の出力電圧は抵抗36の抵抗値とコンデンサ37の静電容量とによって決まる時定数で上昇する。このため、遅延回路35の出力電圧がスイッチング素子S1のしきい値電圧を超えるまでに時間がかかり、スイッチング素子S1がオンするまでの時間が遅れる。また、駆動信号Viの立ち下がり時には、コンデンサ37に蓄えられた電荷は、ダイオードDを通して瞬時に放電されるため、スイッチング素子S1は駆動信号Viの立ち下がりとほぼ同時にオフする。 40

**【0006】**

一方、第2の出力部34側の遅延回路39には、駆動信号Viの立ち下がりで立ち上がりとなり、立ち上がりで立ち下がりとなる矩形波の信号Vaが入力される。遅延回路39は遅延回路35と同じに構成されているため、遅延回路39の出力電圧がスイッチング素子S2のしきい値電圧を超えるまでに時間がかかり、スイッチング素子S2がオンするまでの時間が遅れる。また、信号Vaの立ち下がり時には、コンデンサ37に蓄えられた電荷は、ダイオードDを通して瞬時に放電されるため、スイッチング素子S2は信号Vaの 50

立ち下がりとほぼ同時にオフする。従って、スイッチング素子S1のオフからスイッチング素子S2のオンまでの間にデッドタイムTd1が設けられ、スイッチング素子S2のオフからスイッチング素子S1のオンまでの間にデッドタイムTd2が設けられる。

#### 【0007】

また、特許文献1には、図7に示す回路も開示されている。この回路は、図5の構成において、遅延回路35, 39のダイオードDが抵抗36に対して逆向きに、即ちコンデンサ37の放電が抵抗36を介して行われるように接続され、各出力部33, 34とスイッチング素子S1, S2との間に反転回路としてインバータ40が接続されている。従って、駆動信号Vi及び信号Vaの立ち上がりの際は、コンデンサ37が瞬時に充電されるため、遅延回路35, 39の出力電圧が駆動信号Vi及び信号Vaの立ち上がりとほぼ同時にスイッチング素子S1, S2のしきい値電圧を超える。そして、その信号によりインバータ40からLレベルの出力V1a, V2aが出力されS1, S2はオフになる。

#### 【0008】

また、駆動信号Vi及び信号Vaの立ち下がり時には抵抗36を介してコンデンサ37が放電され、遅延回路35, 39の出力電圧がスイッチング素子S1, S2のしきい値電圧より下がるまでに時間がかかる。従って、インバータ40の出力V1a, V2aがHレベルになるまでに時間がかかり、駆動信号Vi及び信号Vaの立ち下がりからS1, S2がオンになるまでに時間がかかる。その結果、スイッチング素子S1のオフからスイッチング素子S2のオンまでの間にデッドタイムTd1が設けられ、スイッチング素子S2のオフからスイッチング素子S1のオンまでの間にデッドタイムTd2が設けられる。

【特許文献1】特開2002-335679号公報（明細書の段落[0019]～[0027]、[0036]、[0037]、図1, 2, 5, 6）

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0009】

ところが、図5の構成では、スイッチング素子S1, S2のしきい値電圧のバラツキによるデッドタイムのバラツキ、ターンオン時のスイッチング損失の増加といった問題がある。しきい値電圧のバラツキがあると、両スイッチング素子S1, S2が同時にオン状態にならないように、そのバラツキの最大を基準にしてデッドタイムを設定する必要があり、短いデッドタイムを設けることができない。また、図7の構成では、ロジック系のICである反転型のインバータ40を使用して、その出力でスイッチング素子S1, S2を駆動しているため、ターンオン時のスイッチング損失の増加の問題はないが、インバータ40のスレッシュ電圧によるデッドタイムのバラツキの問題は残る。インバータ40では入力信号がHレベルとLレベルとに切り替わるスレッシュ電圧（しきい値電圧）が保証されておらず、遅延回路でなまらせた波形を受ける場合、僅かなスレッシュ電圧の違いで大きな時間差が生じてしまうため、製品設計の際にデッドタイムを長く取らなければならないという問題がある。

#### 【0010】

本発明の目的は、スイッチング素子のしきい値電圧を利用してデッドタイムを生成する場合及び遅延回路とインバータとの組み合わせでデッドタイムを生成する場合と比較してデッドタイムのバラツキを抑制することができるとともに、スイッチング素子のターンオン時のスイッチング損失を抑制することができるドライブ回路を提供することにある。

#### 【課題を解決するための手段】

#### 【0011】

前記の目的を達成するため、請求項1に記載の発明は、1個の入力部と該入力部から分岐された2個の出力部との間に設けられ、コンデンサと抵抗とからなる回路の抵抗に対してダイオードが並列に、かつ前記コンデンサの充電を早める方向に接続された2個の遅延回路を有する。そして、前記各出力部に高精度の基準電圧を利用したコンパレータを用いてHレベルとLレベルとの出力を切り換えるディジタル回路が接続されている。ここで、「高精度の基準電圧」とは、バラツキが数%未満の基準電圧を意味する。

10

20

30

40

50

## 【0012】

この発明では、駆動信号の立ち上がり時にはコンデンサはダイオードを通して高速に充電され、出力部はデジタル回路の出力がLレベルとなる所定電圧に短時間で上昇する。そして、デジタル回路の出力電圧が短時間でLレベルとなり、スイッチング素子がオフとなる。駆動信号の立ち下がり時には抵抗を通してコンデンサが放電されるため、遅延回路の出力は抵抗の抵抗値とコンデンサの静電容量とによって決まる時定数で下降する。このため、遅延回路の出力が、デジタル回路の出力がHレベルになる電圧に達するまでに時間がかかり、スイッチング素子がオンするまでの時間が遅れる。従って、デジタル回路のスレッシュ電圧あるいは抵抗の抵抗値とコンデンサの静電容量とを変更することにより、簡単な構成で所望のデッドタイムを設けることができる。また、スイッチング素子には、デジタル信号として駆動信号が出力されるため、スイッチング素子のターンオン時のスイッチング損失を抑制することができる。10

## 【0013】

請求項2に記載の発明では、請求項1に記載の発明において、前記デジタル回路はシャントレギュレータであり、該シャントレギュレータの入力側が前記出力部に接続されている。

## 【0014】

シャントレギュレータは高精度の基準電圧を持ったコンパレータにトランジスタを組み合わせた動作を行う。従って、シャントレギュレータの入力側となるREF(リファレンス)端子に内部基準電圧を上回る電圧を入力すると、カソード端子がLレベルになり、また、REF端子に内部基準電圧を下回る電圧を入力すると、カソード端子がHレベルになる。この動作は、反転型インバータと同じような動作であるが、反転型インバータと異なり、Hレベル及びLレベルの切り換えが精度良く行われ、デッドタイムのバラツキを抑制することができる。20

## 【発明の効果】

## 【0015】

本発明によれば、スイッチング素子のしきい値電圧を利用してデッドタイムを生成する場合及び遅延回路とインバータとの組み合わせでデッドタイムを生成する場合と比較してデッドタイムのバラツキを抑制することができるとともに、スイッチング素子のターンオン時のスイッチング損失を抑制することができる。30

## 【発明を実施するための最良の形態】

## 【0016】

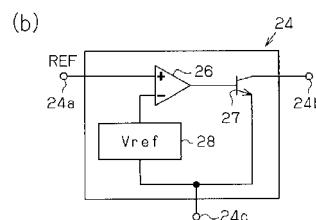

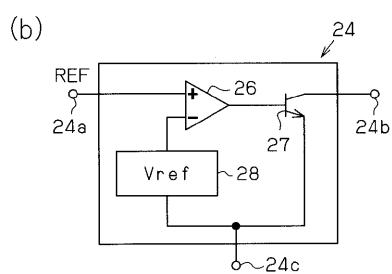

以下、本発明を直流電圧を入力して、交流電圧に変換するDC/A CインバータのHブリッジ回路のドライブ回路に具体化した一実施形態を図1～図3に従って説明する。図1(a)はドライブ回路の回路図、(b)はシャントレギュレータの等価回路、図2はDC/A Cインバータの回路図、図3は作用を説明するタイミングチャートである。

## 【0017】

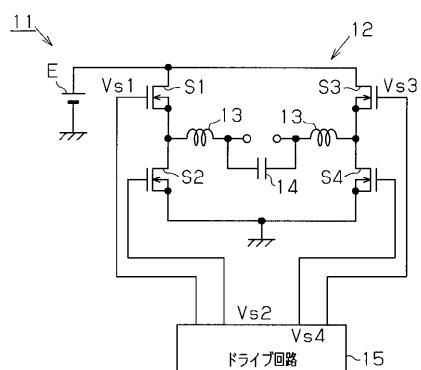

図2に示すように、DC/A Cインバータ11は4個のスイッチング素子S1～S4よりなるHブリッジ回路12を備えている。Hブリッジ回路12は、第1及び第4のスイッチング素子S1, S4の組と、第2及び第3のスイッチング素子S2, S3の組とを交互にオン・オフさせることにより、直流電源Eの直流電圧を交流に変換して、出力端子に交流電圧を出力する。各スイッチング素子S1～S4にはnチャネルのMOSFETが使用されている。出力部にはフィルタを構成するリアクトル13及びコンデンサ14が接続されている。40

## 【0018】

スイッチング素子S1, S3の制御端子(この実施の形態ではMOSFETのゲート)にはドライブ回路15から出力される駆動信号Vs1, Vs3がそれぞれ入力される。スイッチング素子S2, S4の制御端子はドライブ回路15から出力される駆動信号Vs2, Vs4がそれぞれ入力されるようになっている。

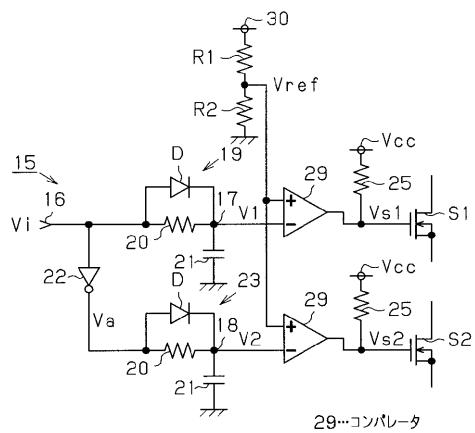

## 【0019】

次にドライブ回路 15 の構成を図 1 (a), (b) に従って詳しく説明する。なお、スイッチング素子 S1, S4 は同時にオン・オフされ、スイッチング素子 S2, S3 は同時にオン・オフされるので、図 1 (a) ではスイッチング素子 S1, S2 のみ図示している。

#### 【0020】

図 1 (a) に示すように、ドライブ回路 15 は 1 個の入力部 16 と 2 個の出力部 17, 18 を備えている。入力部 16 と第 1 の出力部 17 との間には遅延回路 19 が接続されている。遅延回路 19 は抵抗 20 及びコンデンサ 21 の直列回路を備え、抵抗 20 の一端が入力部 16 に接続され、コンデンサ 21 の他端が接地されている。抵抗 20 とコンデンサ 21 との接続点に出力部 17 が接続されている。

10

#### 【0021】

抵抗 20 と並列にダイオード D が接続されている。ダイオード D はアノードが入力部 16 側に、カソードがコンデンサ 21 側に接続されている。即ち、ダイオード D はコンデンサ 21 の充電を早める方向に接続されている。

#### 【0022】

入力部 16 と第 2 の出力部 18 との間にはインバータ（反転回路）22 及び遅延回路 23 が接続されている。遅延回路 23 は遅延回路 19 と同じに構成され、抵抗 20 とコンデンサ 21 との接続点に出力部 18 が接続されている。即ち、遅延回路 23 のダイオード D はコンデンサ 21 の充電を早める方向に接続されている。この実施の形態では、両遅延回路 19, 23 の抵抗 20 の抵抗値及びコンデンサ 21 の静電容量はそれぞれ同じ値に設定されている。

20

#### 【0023】

各遅延回路 19, 23 の出力部 17, 18 には、高精度の基準電圧を利用したコンパレータを用いて H レベル及び L レベルの出力を切り換えるデジタル回路としてのシャントレギュレータ 24 が接続されている。この実施形態ではシャントレギュレータ 24 として可変型シャントレギュレータが使用されている。シャントレギュレータ 24 は REF (リファレンス) 端子 24a、カソード端子 24b 及びアノード端子 24c の 3 端子を備え、シャントレギュレータ 24 の入力側となる REF 端子 24a が遅延回路 19, 23 の出力部 17, 18 に接続されている。また、出力側となるカソード端子 24b は抵抗 25 を介して電源 Vcc に接続され、アノード端子 24c が接地されている。

30

#### 【0024】

図 1 (b) に示すように、シャントレギュレータ 24 はコンパレータ 26、トランジスタ 27 及び基準電圧源 28 を有する。コンパレータ 26 の非反転入力端子に REF 端子 24a が接続され、反転入力端子に基準電圧源 28 が接続されている。また、コンパレータ 26 の出力端子がトランジスタ 27 の制御端子に接続されている。基準電圧源 28 は、高精度の基準電圧を出力し、そのバラツキが数 % 未満であり、市販のシャントレギュレータ 24 で基準電圧のバラツキが 1 % のものを入手できる。

#### 【0025】

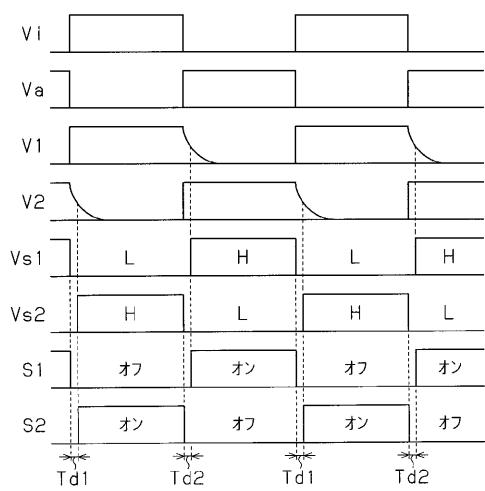

次に前記のように構成されたドライブ回路 15 の作用について説明する。

入力部 16 に図示しない制御回路から駆動信号 Vi が入力されると、第 1 の出力部 17 からは遅延回路 19 を経た出力電圧 V1 が出力され、第 2 の出力部 18 からはインバータ 22 及び遅延回路 23 を経た出力電圧 V2 が出力される。

40

#### 【0026】

図 3 に示すように、駆動信号 Vi は矩形波の電圧信号として入力され、駆動信号 Vi が遅延回路 19 に入力されると、駆動信号 Vi の立ち上がり時にダイオード D を介してコンデンサ 21 が瞬時に充電される。従って、遅延回路 19 の出力電圧 V1 は駆動信号 Vi の立ち上がりとほぼ同時にシャントレギュレータ 24 の基準電圧以上となってシャントレギュレータ 24 の出力（駆動信号 Vs1）が L レベルとなり、スイッチング素子 S1 は駆動信号 Vi の立ち上がりとほぼ同時にオフになる。また、駆動信号 Vi の立ち下がり時には、コンデンサ 21 に蓄えられた電荷は、抵抗 20 を通して放電されるため、抵抗 20 の抵

50

抗値とコンデンサ 21 の静電容量とによって決まる時定数で下がる。従って、遅延回路 19 の出力電圧 V1 は駆動信号 Vi の立ち下がりから遅れてシャントレギュレータ 24 の基準電圧より小さくなり、シャントレギュレータ 24 の出力（駆動信号 Vs1）が H レベルとなってスイッチング素子 S1 がオンとなる。

#### 【0027】

一方、第 2 の出力部 18 側の遅延回路 23 には、駆動信号 Vi の立ち下がりで立ち上がりとなり、立ち上がりで立ち下がりとなる矩形波の信号 Va が入力される。遅延回路 23 は遅延回路 19 と同じに構成されているため、信号 Va の立ち上がり時にダイオード D を介してコンデンサ 21 が瞬時に充電される。従って、遅延回路 23 の出力電圧 V2 は信号 Va の立ち上がりとほぼ同時にシャントレギュレータ 24 の基準電圧以上となってシャントレギュレータ 24 の出力（駆動信号 Vs2）が L レベルとなり、スイッチング素子 S2 は信号 Va の立ち上がりとほぼ同時にオフになる。また、信号 Va の立ち下がり時には、コンデンサ 21 に蓄えられた電荷は、抵抗 20 を通して放電されるため、遅延回路 23 の出力電圧 V2 は抵抗 20 の抵抗値とコンデンサ 21 の静電容量とによって決まる時定数で下がる。従って、遅延回路 23 の出力電圧 V2 は信号 Va の立ち下がりから遅れてシャントレギュレータ 24 の基準電圧より小さくなり、シャントレギュレータ 24 の出力（駆動信号 Vs2）が H レベルとなってスイッチング素子 S2 がオンとなる。

#### 【0028】

従って、スイッチング素子 S1 のオフからスイッチング素子 S2 のオンまでの間にデッドタイム Td1 が確実に設けられ、スイッチング素子 S2 のオフからスイッチング素子 S1 のオンまでの間にデッドタイム Td2 が確実に設けられる。

#### 【0029】

この実施の形態では両遅延回路 19, 23 の時定数が同じため、両デッドタイム Td1, Td2 は同じ値になる。デッドタイム Td1, Td2 の値は時定数を調整することにより所望の値に設定できる。スイッチング素子 S3, S4 もスイッチング素子 S1, S2 と同様に動作する。

#### 【0030】

この実施の形態では以下の効果を有する。

(1) ドライブ回路 15 が、1 個の入力部 16 と該入力部 16 から分岐された 2 個の出力部 17, 18 との間に設けられ、コンデンサ 21 と抵抗 20 からなる回路の抵抗 20 に対してダイオード D が並列に、かつコンデンサ 21 の充電を早める方向に接続された 2 個の遅延回路 19, 23 を有する。そして、各出力部 17, 18 に高精度の基準電圧を利用したコンパレータを用いて H レベル及び L レベルの出力を切り換えるデジタル回路が接続されている。従って、スイッチング素子のしきい値電圧を利用してデッドタイムを生成する場合及び遅延回路とインバータとの組み合わせでデッドタイムを生成する場合と比較して、デッドタイムのバラツキを抑制することができる。その結果、H ブリッジ回路 12 を構成するスイッチング素子 S1 ~ S4 のうち、相補的にオン・オフすべきスイッチング素子が同時にオン状態になることがなくなる。また、スイッチング素子にデジタル信号として駆動信号 Vs1, Vs2 等が出力されるため、スイッチング素子のターンオン時のスイッチング損失を抑制することができる。

#### 【0031】

(2) デジタル回路はシャントレギュレータ 24 であり、該シャントレギュレータの REF 端子 24a が出力部 17, 18 に接続されている。シャントレギュレータは高精度の基準電圧を持ったコンパレータ 26 にトランジスタ 27 を組み合わせた動作を行う。従って、反転型インバータと同じような動作を、反転型インバータと異なり精度良く行うことができ、デッドタイムのバラツキを抑制することができる。また、市販品でもコンパクトなシャントレギュレータ 24 を容易に入手でき、ドライブ回路 15 をコンパクトに形成できる。

#### 【0032】

(3) 抵抗 20 の抵抗値及びコンデンサ 21 の静電容量を変更することにより、時定

10

20

30

40

50

数を調整して所望のデッドタイムを簡単に設定できる。

実施形態は前記に限定されるものではなく、例えば、次のように具体化してもよい。

#### 【0033】

ディジタル回路として、シャントレギュレータ24に代えて、図4に示すように、コンパレータ29と高精度の基準電源30（基準電圧 $V_{ref}$ ）とにより、Hレベル及びLレベルの出力を切り換えるディジタル回路を構成してもよい。両コンパレータ29の非反転入力端子は共通の基準電源30に接続され、反転入力端子に遅延回路19, 23の出力部17, 18が接続されている。この実施形態の構成では、コンパレータ29の反転入力端子への入力電圧である遅延回路19, 23の出力電圧 $V_1$ ,  $V_2$ が基準電圧 $V_{ref}$ より高いと、コンパレータ29の出力はLレベルとなり、前記入力電圧が基準電圧 $V_{ref}$ より低いとコンパレータ29の出力はHレベルとなる。即ち、コンパレータ29は反転型インバータと同じような動作を、反転型インバータと異なり精度良く行う。この実施形態においても、前記実施形態の(1), (3)と同様な効果を有する。10

#### 【0034】

所望のデッドタイムに設定する方法として、抵抗20の抵抗値及びコンデンサ21の静電容量を変更することにより、時定数を調整して設定する方法に代えて、シャントレギュレータ24やコンパレータ29の基準電圧を変更してもよい。コンパレータ29と基準電源30を用いる構成の場合、基準電源30に接続された分圧回路の抵抗R1, R2の抵抗値を変更することで容易に対応できる。20

#### 【0035】

両遅延回路19, 23の抵抗20及びコンデンサ21の時定数が異なるように抵抗値及び静電容量を設定してもよい。

スイッチング素子S1, S2としてMOSFETに代えて、バイポーラトランジスタやIGBTを使用してもよい。

#### 【0036】

Hブリッジのドライブ回路に限らず、例えばプッシュプル形コンバータのドライブ回路に適用してもよい。

以下の技術的思想（発明）は前記実施の形態から把握できる。

#### 【0037】

(1) 請求項2に記載の発明において、前記シャントレギュレータは可変型シャントレギュレータである。30

(2) 請求項1又は請求項2に記載の発明のドライブ回路を備えたHブリッジ用のドライブ回路。

#### 【0038】

(3) 請求項1又は請求項2に記載の発明において、前記2個の遅延回路のうち一方に入力される信号は、他方に入力される信号を反転した信号である。

#### 【図面の簡単な説明】

#### 【0039】

【図1】(a)は一実施形態のドライブ回路の回路図、(b)はシャントレギュレータの等価回路。40

【図2】DC/ACインバータの回路図。

【図3】作用を説明するタイミングチャート。

【図4】別の実施形態の回路図。

【図5】従来技術の回路図。

【図6】作用を説明するタイミングチャート。

【図7】別の従来技術の回路図。

#### 【符号の説明】

#### 【0040】

D…ダイオード、 $V_{ref}$ …基準電圧、21…コンデンサ、16…入力部、17, 18…出力部、19, 23…遅延回路、20…抵抗、24…シャントレギュレータ、26, 2950

...コンパレータ。

【図1】

【図2】

26…コンパレータ

【図3】

【図4】

【図5】

【図6】

【図7】

## フロントページの続き

F ターム(参考) 5J055 AX00 AX54 AX66 BX16 BX25 CX07 CX13 CX19 DX13 DX49

DX60 EX02 EX07 EX21 EY00 EY01 EY05 EY10 EY12 EY21

EZ01 EZ07 EZ10 EZ50 EZ58 FX12 FX17 FX28 FX32 GX01

GX04 GX05