(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4876051号

(P4876051)

(45) 発行日 平成24年2月15日(2012.2.15)

(24) 登録日 平成23年12月2日(2011.12.2)

(51) Int.Cl.

G 06 T 1/60 (2006.01)

H 04 N 1/21 (2006.01)

F 1

G 06 T 1/60 450 E

H 04 N 1/21

請求項の数 7 (全 14 頁)

(21) 出願番号 特願2007-264969 (P2007-264969)

(22) 出願日 平成19年10月10日 (2007.10.10)

(65) 公開番号 特開2009-93501 (P2009-93501A)

(43) 公開日 平成21年4月30日 (2009.4.30)

審査請求日 平成22年8月19日 (2010.8.19)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

(74) 代理人 100134175

弁理士 永川 行光

最終頁に続く

(54) 【発明の名称】 画像処理装置及びその制御方法

## (57) 【特許請求の範囲】

## 【請求項 1】

レジスタ設定値または画素データからなる処理対象データを含むコマンドを処理する画像処理手段と、

前記画像処理手段で処理される処理対象データを、メモリ内のアドレスが連続する第1のアドレス空間に格納する第1格納手段と、

ダイレクトメモリアクセスにより、前記第1のアドレス空間から処理対象データを順次に読み出し、読み出した処理対象データにコマンド化のための制御情報を付加することにより前記画像処理手段が処理可能なコマンドを生成し、該コマンドを前記画像処理手段へ転送する第1転送手段と、

前記画像処理手段から出力された処理済のコマンドからレジスタ設定値または画素データを抽出し、抽出されたレジスタ設定値または画素データをダイレクトメモリアクセスにより順次に、メモリ内のアドレスが連続する第2のアドレス空間へ格納する第2転送手段とを備えることを特徴とする画像処理装置。

## 【請求項 2】

前記第1転送手段は、前記第1のアドレス空間内の先頭の所定アドレス範囲に格納されたデータに基づいて、前記コマンド化のための制御情報を生成し、前記所定アドレス範囲から読み出したデータを前記画像処理手段へ転送しないことを特徴とする請求項1に記載の画像処理装置。

## 【請求項 3】

10

20

前記第1転送手段は、

前記処理対象データがレジスタ設定値であった場合、前記所定アドレス範囲から読み出したデータに基づいてレジスタ設定値の格納先の先頭のレジスタアドレスを決定し、

前記先頭のレジスタアドレスを含む制御情報を付加して1つ目のコマンドを生成し、2つ目以降のコマンドを生成するための制御情報に含まれるレジスタアドレスを、直前に生成したコマンドの制御情報に含まれているレジスタアドレスに所定値を加算することにより決定することを特徴とする請求項2に記載の画像処理装置。

【請求項4】

前記第2転送手段は、

前記第2のアドレス空間に対するダイレクトメモリアクセスの開始の指示に応じて、前記第2のアドレス空間内の先頭の所定アドレス範囲に格納されたデータから、連続して格納されるレジスタ設定値のデータ量、或いは画素データのデータ量を取得し、

前記画像処理手段から順次に出力された処理済みのコマンドからレジスタ設定値または画素データを抽出して前記第2のアドレス空間へ順次に格納する処理を、取得した前記データ量に基づいて決定される回数だけ繰り返すことを特徴とする請求項1に記載の画像処理装置。

【請求項5】

前記第1のアドレス空間内の先頭の前記所定アドレス範囲に前記コマンド化のための制御情報の生成に用いられるデータを格納し、前記第1のアドレス空間内の前記所定アドレス範囲に続くアドレス空間に前記処理対象データを格納し、前記第1のアドレス空間の先頭アドレスをダイレクトメモリアクセスの開始アドレスとして前記第1転送手段に設定する制御手段を更に備えることを特徴とする請求項2に記載の画像処理装置。

【請求項6】

前記第2のアドレス空間内の先頭の前記所定アドレス範囲に連続して格納されるべきレジスタ設定値或いは画素データのデータ量を示すデータを格納し、前記第2のアドレス空間内の前記所定のアドレス範囲に続く、前記データ量に対応した大きさの領域を確保し、前記第2のアドレス空間の先頭アドレスをダイレクトメモリアクセスの開始アドレスとして前記第2転送手段に設定する制御手段を更に備えることを特徴とする請求項4に記載の画像処理装置。

【請求項7】

レジスタ設定値または画素データからなる処理対象データを含むコマンドを処理する画像処理手段を有する画像処理装置の制御方法であって、

第1格納手段が、前記画像処理手段で処理される処理対象データを、メモリ内のアドレスが連続する第1のアドレス空間に格納する第1格納工程と、

第1転送手段が、ダイレクトメモリアクセスにより、前記第1のアドレス空間から処理対象データを順次に読み出し、読み出した処理対象データにコマンド化のための制御情報を付加することにより前記画像処理手段が処理可能なコマンドを生成し、該コマンドを前記画像処理手段へ転送する第1転送工程と、

第2転送手段が、前記画像処理手段から出力された処理済のコマンドからレジスタ設定値または画素データを抽出し、抽出されたレジスタ設定値または画素データをダイレクトメモリアクセスにより順次に、メモリ内のアドレスが連続する第2のアドレス空間へ格納する第2転送工程とを備えることを特徴とする画像処理装置の制御方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は画像処理装置及びその制御方法に関し、特にメモリから画像処理モジュールへのデータ転送に関する。

【背景技術】

【0002】

一般に、画像処理モジュールは、レジスタ設定のためのCPUインターフェース、及び

10

20

30

40

50

、画像データ入出力のためのデータインターフェース、の2種類のインターフェースを有していた。このような画像処理モジュールは、CPUインターフェースによって制御を行うため、

- ・一連の画像処理が終了した後に割り込みによってCPUに画像処理の終了を通知し、

- ・次の処理のためのレジスタ設定を行ってから次の画像処理を開始する、

- というシーケンスが必要であった。また、CPUの変更に伴ってCPUインターフェースが替わった場合、画像処理モジュールを作り直すか、ラッパー等によりインターフェースを変換しなければならなかつた。

#### 【0003】

上記課題を解決するものとして、レジスタ設定用のデータと処理対象の画像データをコマンド化し、同一の経路で転送するという方法が提案されている。この方法による処理の流れを、図7を用いて説明する。

#### 【0004】

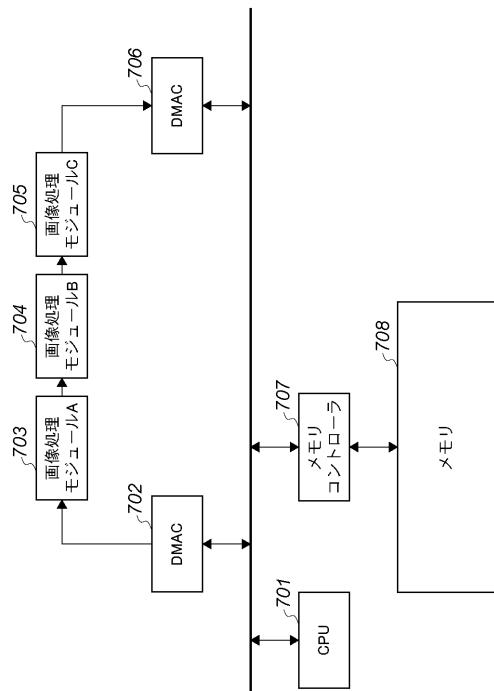

図7は一連の画像処理を実行する画像処理部のブロック図である。図7において、701はCPU、702, 706はDMA転送を制御するDMAC、703～705は画像処理モジュールA～C、707はメモリコントローラ、708はメモリである。なお、703～705に示された画像処理モジュールとしては、補正回路や色変換回路などが挙げられる。なお、DMAはダイレクトメモリアクセスの略である。

#### 【0005】

CPU701は画像処理の開始前、若しくは決められた処理単位毎に、各画像処理モジュールのレジスタに対して読み書きを行うためのレジスタコマンド、或いは画素データを格納したデータコマンドを生成する。

#### 【0006】

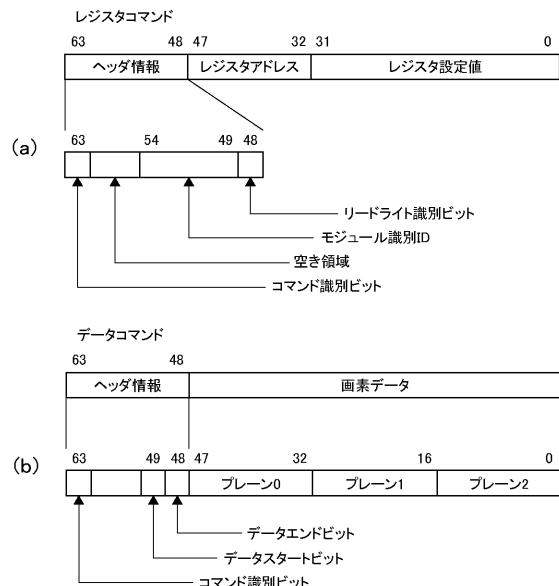

図6に各コマンドのフォーマットの具体例を示す。図6の(a)に示されるように、レジスタコマンドにはヘッダ情報、レジスタアドレス、レジスタ設定値が格納されている。また、ヘッダ情報には、コマンド識別ビット、モジュール識別ID、リードライト識別ビットが含まれる。コマンド識別ビットは、レジスタコマンドであるかデータコマンドであるかを示す。例えば、コマンド識別ビットが1であればレジスタコマンド、0であればデータコマンドであることを示す。画像処理モジュールはこのコマンド識別ビットを参照することにより、レジスタコマンド及びデータコマンドのどちらの種類のコマンドであるかを判断する。また、モジュール識別IDは、レジスタコマンドにおいてどの画像処理モジュールへの設定かを示す。画像処理モジュールは、受信したレジスタコマンドが自分への設定であるかどうかをモジュール識別IDを参照することにより判断する。また、リードライト識別ビットは、レジスタコマンドがリード、ライトのいずれのコマンドかを表す。例えば、このリードライト識別ビットが1であればレジスタライト(レジスタのライトコマンド)、0であればレジスタリード(レジスタのリードコマンド)であるとする。

#### 【0007】

一方、図6の(b)に示されるように、データコマンドのヘッダ情報は、データコマンドであることを示す0の値を有するコマンド識別ビットと、データスタートビットやデータエンドビットなどの画像制御信号が含まれている。CPU701は作成したコマンドをメモリ708へ格納する。

#### 【0008】

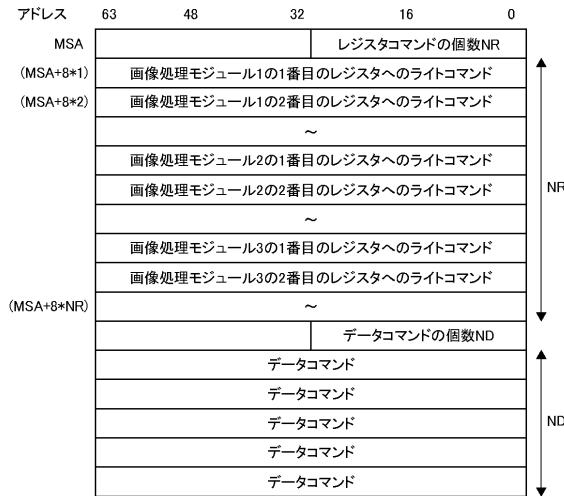

図8にメモリ708へ格納されたコマンドを示す。また、CPU701は画像データもコマンド化し、データコマンドとしてメモリ708に格納する。所定の処理単位のコマンドがメモリ708に格納されると、CPU701はDMAC702およびDMAC706のレジスタにメモリ708へのアクセスアドレスを設定し、起動する。

#### 【0009】

DMAC702はメモリ708から順次にコマンドを読み込み、画像処理モジュールAへ転送する。画像処理モジュールB704、画像処理モジュールC705は、入力されたコマンドがレジスタのライトコマンドであり、且つモジュール識別IDから自身を対象と

10

20

30

40

50

したコマンドであると判断した場合には、レジスタ設定を行う。受け取ったコマンドがレジスタのリードコマンドの時は、レジスタアドレスで示される対象レジスタから読み取った値をリードコマンドのレジスタ設定値に設定し、次の画像処理モジュールへ転送する。受け取ったコマンドがデータコマンドの時は、そのデータを用いて処理を行い、処理した結果をデータコマンドに設定し、次の画像処理モジュールへ転送する。DMA C706は画像処理モジュールC705から出力されたコマンドを受け取り、メモリ708へ書き込む。

#### 【0010】

このように、レジスタの設定、データ入力を同一のポートから設定できるようにしているので、任意のシーケンスをCPUの割込み無しに実行できる。また、CPUインターフェースが変更になっても、画像処理モジュールは一切変更する必要がないという長所を有する。

また、特許文献1には、CPUの負荷を軽減するために、転送元及び転送先のアドレスを生成する制御部を持ったDMA制御装置が記載されている。

【特許文献1】特開平10-011388号公報

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0011】

しかしながら、メモリ708にはレジスタ設定値以外のヘッダ情報やアドレスも格納するようにした場合には、大きなメモリ容量と転送帯域が必要となり、無駄なメモリ容量と転送帯域を消費することになる。また、画像データをコマンド化して格納するようにした場合には、CPU701によるコマンド化の作業が必要となり、CPUの負荷も増大してしまう。更に、特開平10-011388号のDMA制御装置を適用したとしても、コマンド化に関わる作業は解消されない。

#### 【0012】

本発明は、上記の課題に鑑みてなされたものであり、ダイレクトメモリアクセスを用いてメモリから画像処理モジュールへデータを転送するにおいて、メモリに要求される容量と転送帯域を小さくすることを可能にすることを目的とする。

#### 【課題を解決するための手段】

#### 【0013】

上記の目的を達成するための本発明の一態様による画像処理装置は以下の構成を備える。すなわち、

レジスタ設定値または画素データからなる処理対象データを含むコマンドを処理する画像処理手段と、

前記画像処理手段で処理される処理対象データを、メモリ内のアドレスが連続する第1のアドレス空間に格納する第1格納手段と、

ダイレクトメモリアクセスにより、前記第1のアドレス空間から処理対象データを順次に読み出し、読み出した処理対象データにコマンド化のための制御情報を付加することにより前記画像処理手段が処理可能なコマンドを生成し、該コマンドを前記画像処理手段へ転送する第1転送手段と、

前記画像処理手段から出力された処理済のコマンドからレジスタ設定値または画素データを抽出し、抽出されたレジスタ設定値または画素データをダイレクトメモリアクセスにより順次に、メモリ内のアドレスが連続する第2のアドレス空間へ格納する第2転送手段とを備える。

#### 【0014】

又、上記の目的を達成するための、本発明の他の態様による画像処理方法は、

レジスタ設定値または画素データからなる処理対象データを含むコマンドを処理する画像処理手段を有する画像処理装置の制御方法であって、

第1格納手段が、前記画像処理手段で処理される処理対象データを、メモリ内のアドレスが連続する第1のアドレス空間に格納する第1格納工程と、

10

20

30

40

50

第1転送手段が、ダイレクトメモリアクセスにより、前記第1のアドレス空間から処理対象データを順次に読み出し、読み出した処理対象データにコマンド化のための制御情報を附加することにより前記画像処理手段が処理可能なコマンドを生成し、該コマンドを前記画像処理手段へ転送する第1転送工程と、

第2転送手段が、前記画像処理手段から出力された処理済のコマンドからレジスタ設定値または画素データを抽出し、抽出されたレジスタ設定値または画素データをダイレクトメモリアクセスにより順次に、メモリ内のアドレスが連続する第2のアドレス空間へ格納する第2転送工程とを備える。

【発明の効果】

【0015】

10

本発明によれば、小さいメモリ容量と小さい転送帯域のメモリで画像処理モジュールを動作させることができるとなる。また、データのコマンド化という処理からCPUを解放することができる。

【発明を実施するための最良の形態】

【0016】

以下添付図面に従って本発明に係る実施形態を説明する。

【0017】

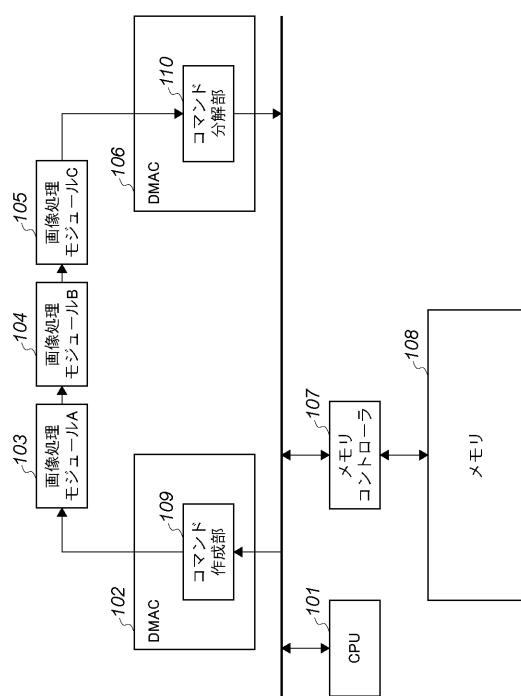

図1は、実施形態による画像処理装置の構成を示すブロック図である。図1において、101はCPU、102、106はDMAC、103～105は画像処理モジュールA～C、107はメモリコントローラ、108はメモリ、109はコマンド作成部、110はコマンド分解部である。なお、図1では画像処理モジュールが3つの場合を示したが、画像処理モジュールの数は、4つ以上であってもよいし2つ以下であってもよい。

20

【0018】

CPU101はメモリ108へレジスタ設定値や画像データの格納を行う。以下、レジスタ設定値や画像データを総称して処理対象データともいう。DMAC102はメモリ108からダイレクトメモリアクセスにより処理対象データを読み出す。コマンド作成部109は、読み出したデータを用いて、図6に示したようなコマンドを生成する。そして、DMAC102は、コマンド作成部109により作成されたコマンドを画像処理モジュールA103へ転送する。DMAC102内のコマンド作成部109は、メモリ108から読み出されたレジスタ設定値または画像データに、コマンド化のための制御情報を附加することによりコマンドを作成する。

30

【0019】

なお、図6の(a)に示すように、レジスタコマンドの制御情報は、ヘッダ情報とレジスタアドレスで構成される。又、図6の(b)に示すように、データコマンドの制御情報はヘッダ情報で構成される。画像処理モジュールA103、画像処理モジュールB104、画像処理モジュールC105は入力されたコマンドに応じて所定の処理を行う。すなわち、これらの画像処理モジュールは、レジスタ設定値または画素データに制御情報が付加された形態を有する、図6に示したコマンドを処理する。そのような画像処理モジュールの例としては、補正回路や色変換回路などが挙げられる。

【0020】

40

DMAC106はメモリコントローラ107へレジスタ設定値と画素データを転送し、それらをメモリ108へ書き込ませる。DMAC106内のコマンド分解部110は、画像処理モジュールC105から受け取ったコマンドを分解し、レジスタ設定値または画素データを作成する。すなわち、DMAC106は、画像処理モジュールC105から出力された処理済のコマンドからコマンド分解部110によって抽出されたレジスタ設定値または画素データをメモリ108へ書き込む、第2転送部として機能する。

【0021】

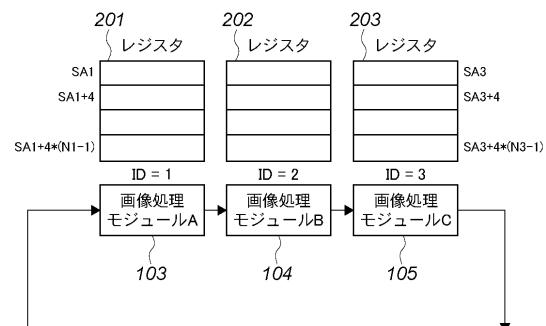

詳細な説明をする前に、レジスタコマンドにしたがったレジスタ設定の対象となる画像処理モジュールのレジスタについて説明しておく。図2は画像処理モジュールのレジスタ構成を説明する図である。画像処理モジュールA103のIDを1、レジスタのスタート

50

アドレスを S A 1 、レジスタの個数を N 1 とする。同様に、画像処理モジュール B 1 0 4 の I D を 2 、レジスタのスタートアドレスを S A 2 、レジスタの個数を N 2 とする。更に、画像処理モジュール C 1 0 5 の I D を 3 、レジスタのスタートアドレスを S A 3 、レジスタの個数を N 3 とする。また、レジスタ設定値のデータ幅は 3 2 b i t であるとする。また、本実施形態では、1つのアドレスに 8 ビットが割り当てられているものとする。

#### 【 0 0 2 2 】

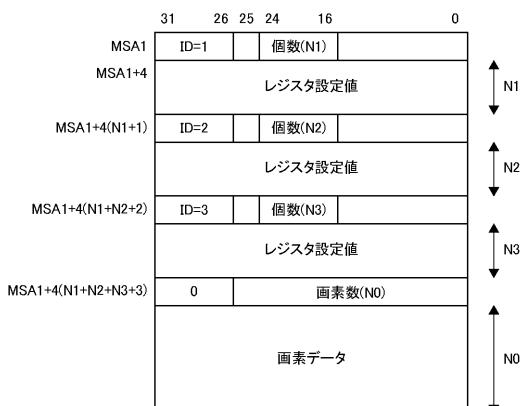

次に、 C P U 1 0 1 がメモリ 1 0 8 にコマンド作成のために必要なデータを格納する様子を、図 3 を用いて説明する。メモリ 1 0 8 へレジスタ設定値を格納する場合は、レジスタ設定値を格納する前に、まずヘッダ情報を格納する。即ち、ヘッダ情報として、図 3 の ( a ) 中のメモリアドレス M S A 0 、 M S A 0 + 4 ( N 1 + 1 ) 、 . . . に示すように、

• 3 1 b i t 目から 2 6 b i t 目までにモジュール I D 、

• 2 5 b i t 目にリードライト識別ビット ( 1 のときライトコマンド、 0 のときリードコマンドとする ) 、

• 2 4 b i t 目から 1 6 b i t 目までにレジスタの個数、

• 1 5 b i t 目から 0 b i t 目までにレジスタの先頭アドレスを格納した 3 2 ビットの制御データが格納される。そして、次のメモリアドレスからは、先のレジスタの個数分だけ、画像処理モジュールへの処理対象データとしてのレジスタ設定値が格納される。

#### 【 0 0 2 3 】

一方、画素データを格納する場合はヘッダ情報として、図 3 の ( a ) においてメモリアドレス M S A 0 + 4 ( N 1 + N 2 + N 3 + 3 ) に示すように、

• 3 1 b i t 目から 2 6 b i t 目までにはモジュール I D として 0 が、

• 2 5 b i t 目から 0 b i t 目までには入力する画素数を格納した 3 2 ビットの制御データが格納される。そして、次のメモリアドレスからは、この画素数分だけ、画像処理モジュールへの処理対象データとしての画素データが格納される。

#### 【 0 0 2 4 】

したがって、図 3 の ( a ) に示されるように、「 M S A 0 ~ M S A 0 + 4 \* ( N 1 ) 」等のメモリ 1 0 8 における連続するアドレス空間にコマンド化のための制御情報の生成に用いられるデータと転送すべき処理対象データが格納されることになる。以下、図 3 の ( a ) に示されるような、制御情報を生成するためのデータと転送対象となる処理対象データを格納するためのメモリ内の連続するアドレス空間を、第 1 のアドレス空間と称する場合もある。

#### 【 0 0 2 5 】

次に、 C P U 1 0 1 は、 D M A C 1 0 6 が画像処理モジュール C 0 1 0 5 から出力されたデータをメモリへ格納するために必要なヘッダ情報を、メモリ 1 0 8 へ格納する。即ち、レジスタ設定値を格納する場合は、図 3 の ( b ) においてメモリアドレス M S A 1 、 M S A 1 + 4 ( N 1 + 1 ) 、 . . . に示すように、

• 3 1 b i t 目から 2 6 b i t 目までにモジュール I D が、

• 2 4 b i t 目から 1 6 b i t 目までにレジスタの個数が格納される。

#### 【 0 0 2 6 】

一方、画素データを格納する場合は、図 3 の ( b ) においてメモリアドレス M S A 1 + 4 ( N 1 + N 2 + N 3 + 3 ) に示されるように、

• 3 1 b i t 目から 2 6 b i t 目までにモジュール I D として 0 が、

• 2 5 b i t 目から 0 b i t 目までに入力する画素数が格納される。

#### 【 0 0 2 7 】

又、図 3 の ( b ) に示されるように、ヘッダ情報を格納したアドレスに続けて、当該制御データによって示される個数のレジスタや画素のデータを格納するための連続するアドレス空間が確保される。

#### 【 0 0 2 8 】

こうして、メモリ 1 0 8 の連続するアドレス空間内の先頭の所定アドレス範囲に、連続して格納されるべきレジスタ設定値或いは画素データのデータ量を示すデータが格納され

10

20

30

40

50

る。そして、連続するアドレス空間内の上記所定アドレス範囲に続いて、そのデータ量に対応する大きさのメモリ領域が確保される。なお、このメモリ内の連続するアドレス空間を第2のアドレス空間と称する場合もある。

【0029】

次にCPU101は、DMAC102のレジスタにメモリアドレスMSA0を、DMA106のレジスタにメモリアドレスMSA1を設定する。こうして、CPU101は、メモリ108の第1のアドレス空間内の先頭の所定アドレス範囲に制御情報生成のためのデータを格納し、所定のアドレス範囲に続く領域に処理対象データを格納する第1格納部として機能する。そして、当該第1のアドレス空間の先頭アドレスをダイレクトメモリアクセスの開始アドレスとしてDMAC102に設定する。又、CPU101は、メモリ108の第2のアドレス空間内の先頭の所定アドレス範囲にこれから格納されるデータ量を示す制御情報を格納し、第2のアドレス空間内の所定アドレス範囲に続けて当該データ量に対応した領域を確保する第2格納部として機能する。そして、第2のアドレス空間の先頭アドレスをダイレクトメモリアクセスの開始アドレスとしてDMAC106に設定する。

【0030】

DMAC102は動作開始後、DMAC102の内部のアドレスカウンタへ、レジスタに設定されたメモリアドレスMSA0をセットする。この処理により、DMAC102はダイレクトメモリアクセスによりメモリ108の第1のアドレス空間から処理対象データを順次に読み出す。そして、コマンド作成部109は、読み出した処理対象データに制御情報を付加することにより画像処理モジュールが処理可能なコマンドを生成し、このコマンドを画像処理モジュールA103へ転送する。すなわち、DMAC102及びコマンド作成部109は、メモリ108より読み出した処理対象データをコマンド化して画像処理モジュールA103へ転送する第1転送部を構成する。

【0031】

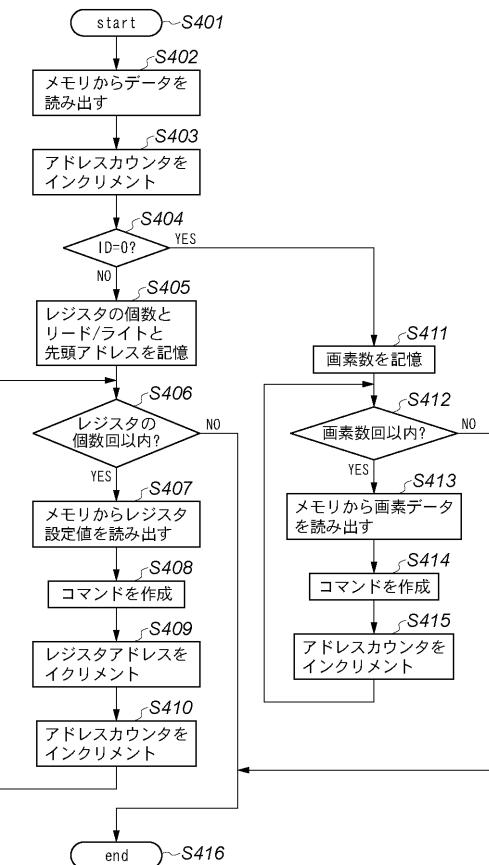

次に、DMAC102内のコマンド作成部109によるコマンド作成処理の手順を図4に示すフローチャートを用いて更に詳細に説明する。

【0032】

図4において、DMAC102はレジスタ設定処理を開始する(ステップS401)。そして、DMAC102は、アドレスカウンタが示すメモリ108のメモリアドレスからデータを読み出し、それをDMAC102が有する不図示のレジスタへ記憶する(ステップS402)。この処理により、ヘッダ情報がDMAC102のレジスタへ記憶されることになる。続いて、アドレスカウンタをインクリメントする(ステップS403)。

【0033】

次に、コマンド作成部109は、ステップS402でレジスタに記憶されたヘッダ情報のモジュールIDが0であるかどうかを判断する(ステップS404)。そして、モジュールIDが0でない場合は、コマンド作成部109は当該コマンドがレジスタコマンドであると判断する。この場合、コマンド作成部109は、モジュールIDとリードライト識別ビットの値とレジスタの個数とレジスタアドレスを自身のレジスタに記憶する(ステップS405)。

【0034】

次に、コマンド作成部109は、以降の処理(ステップS407～ステップS410)が、規定数回だけ処理が行われたか否かを判断する(ステップS406)。本実施形態では、1個のレジスタのデータが32ビットであり(図3の(a))、4つのアドレスを必要とするので、ステップS405で記憶したレジスタの個数×4が規定数となる。そして、処理回数が規定数に達した場合には、本処理を終了する(ステップS416)。一方、処理回数が規定数に達していない場合には、コマンド作成部109は、アドレスカウンタが示すメモリ108のメモリアドレスからデータ(レジスタ設定値)を読み出す(ステップS407)。そして、コマンド作成部109は、ステップS405で記憶したモジュールIDと、リードライト識別ビットの値と、レジスタアドレスとを用いて図6の(a)の

10

20

30

40

50

形式のレジスタコマンドを作成する(ステップS408)。続いて、コマンド作成部109は、レジスタアドレスをインクリメントし(ステップS409)、アドレスカウンタをインクリメントし(ステップS410)、ステップS406へ戻る。

#### 【0035】

上述したように、レジスタ設定値に付加される制御情報には、画像処理モジュールにおける当該レジスタ設定値の格納先のレジスタアドレスが含まれている。したがって、コマンド作成部109は、最初のコマンド作成時において、制御データに基づいて1つ目のレジスタアドレスを決定する(ステップS405、S408)。そして、2つ目以降のコマンドのレジスタアドレスについては、直前のコマンドの制御情報に含まれているレジスタアドレスに所定値を加算した値が用いられる(ステップS409)。

10

#### 【0036】

ステップS404においてモジュールIDが0である場合は、コマンド作成部109は、データコマンドとして当該ヘッダ情報から画素数を取得し、自身のレジスタに記憶する(ステップS411)。次に、以降の処理(ステップS413～ステップS415)が、規定数回だけ処理が行われたか否かを判断する(ステップS412)。ここで、規定回数とは、例えば、「画素数」を「1アドレスに格納される画素数」で割った値である。本実施形態では、図3の(b)に示されるように、1つの画素が48ビットを有するので、6つのアドレスを必要としており、ステップS411で記憶した画素数×6が規定数となる。そして、コマンド作成部109は、規定数に達した場合には処理を終了する(ステップS416)。

20

#### 【0037】

ステップS412で規定数に達していないと判定された場合は、コマンド作成部109は、続けてアドレスカウンタが示すメモリアドレスからデータを読み出し(ステップS413)、図6の(b)の形式のデータコマンドを作成する(ステップS414)。なお、ステップS414のコマンド作成において、コマンド作成部109は、ステップS412のループ回数を参照して、最初の画素のコマンド作成時にはデータスタートを1にセットし、他の画素に対してはデータスタートを0にセットする。また、最後の画素の時には、コマンド作成部109は、データエンドを1にし、他の画素に対してはデータエンドを0にセットする。次に、コマンド作成部109は、アドレスカウンタをインクリメントし(ステップS415)、処理をステップS412へ戻す。

30

#### 【0038】

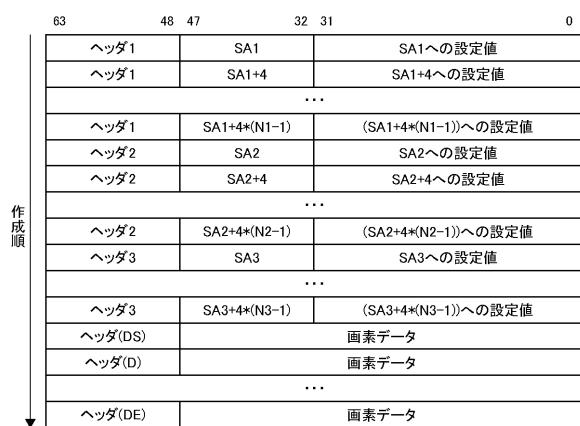

以上の手順によって作成されたコマンドの例を図5に示す。図5において、矢印で示された順にコマンドが作成転送される。ここでヘッダ1からヘッダ3は、レジスタコマンドのためのヘッダであり、コマンド識別ビットには1が、モジュール識別IDにはそれぞれ1から3の値が、リードライト識別ビットにはライトを示す1が格納されている。また、ヘッダ(DS)、ヘッダ(D)、ヘッダ(DE)はそれぞれデータコマンドのヘッダを表しており、コマンド識別ビットとして0が格納されている。また、データ制御用フラグとして、ヘッダ(DS)にはデータスタート=1とデータエンド=0が、ヘッダ(D)にはデータスタート=0とデータエンド=0が、ヘッダ(DE)にはデータスタート=0とデータエンド=1が格納されている。

40

#### 【0039】

以上のように、コマンド作成部109は、第1のアドレス空間内の先頭の所定アドレス範囲に格納されたデータに基づいて、第1のアドレス空間内のレジスタ設定値或いは画素データをコマンド化するための制御情報を生成する。そして、コマンド作成部109は、第1のアドレス空間の上記所定アドレス範囲以降から読み出した処理対象データを、上記制御情報を付加することによりコマンド化し、画像処理モジュールA103へ転送する

#### 【0040】

作成されたコマンドは画像処理モジュールA103へ転送され、全ての画像処理モジュールを通過してレジスタ設定が行われる。

#### 【0041】

50

D M A C 1 0 6 は動作の開始後、D M A C 1 0 6 の内部のアドレスカウンタに、予めレジスタに設定されたメモリアドレスM S A 1 がセットされる。

【 0 0 4 2 】

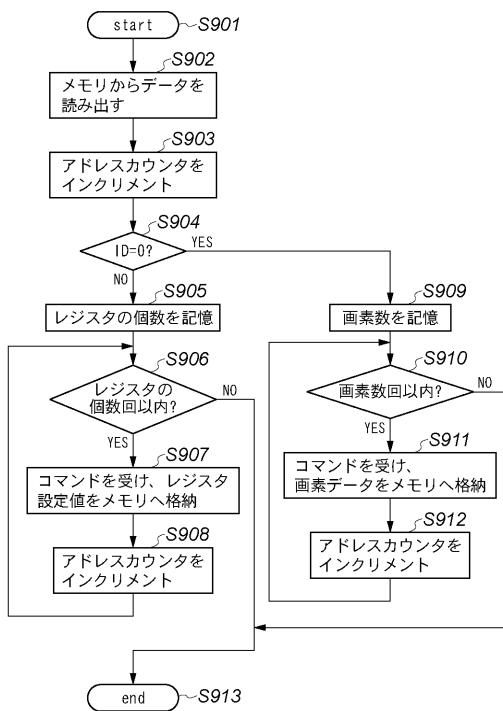

次に、D M A C 1 0 6 内のコマンド分解部 1 1 0 は、コマンドの分解処理を行う。その処理手順を図 9 に示すフローチャートを用いて説明する。

【 0 0 4 3 】

図 9 において、D M A C 1 0 6 のコマンド分解部 1 1 0 は、コマンド分解処理を開始し(ステップ S 9 0 1)、アドレスカウンタが示すメモリ 1 0 8 のメモリアドレスからデータを読み出し、自身が有する不図示のレジスタに記憶する(ステップ S 9 0 2)。ここで読み出され、記憶されるデータは、図 3 の( b )に示した、アドレス M S A 1 のヘッダ情報である。続いて、コマンド分解部 1 1 0 は、アドレスカウンタをインクリメントする(ステップ S 9 0 3)。

【 0 0 4 4 】

次に、コマンド分解部 1 1 0 は、ステップ S 9 0 2 で記憶したヘッダ情報のモジュール I D が 0 であるかを判断する(ステップ S 9 0 4)。モジュール I D が 0 でない場合は、コマンド分解部 1 1 0 は、当該ヘッダ情報がレジスタコマンドに関連するものと判断し、当該ヘッダ情報の 1 6 ~ 2 4 ビット目で表される値をレジスタの個数として D M A C 1 0 6 のレジスタに記憶する(ステップ S 9 0 5)。次に、コマンド分解部 1 1 0 は、以降の処理(ステップ S 9 0 7 ~ ステップ S 9 0 8)が、規定数回だけ行われたか否かを判断する(ステップ S 9 0 6)。この規定数は、ステップ S 4 0 6 で説明したものと同様である。処理回数が規定数に達した場合には本処理を終了する(ステップ S 9 1 3)。処理回数が規定数に達していない場合には、処理を継続する。すなわち、画像処理モジュール C 1 0 5 からコマンドを受け取り、当該コマンド内のレジスタ設定値をアドレスカウンタで示すメモリアドレスへ格納する(ステップ S 9 0 7)。続いて、コマンド分解部 1 1 0 は、アドレスカウンタをインクリメントし(ステップ S 9 0 8)、処理をステップ S 9 0 6 へ戻す。

【 0 0 4 5 】

一方、ステップ S 9 0 4 において、モジュール I D が 0 であると判定された場合、コマンド分解部 1 1 0 は、当該ヘッダ情報の 0 ~ 2 5 ビットに記録されている値を画素数として記憶する。次に、コマンド分解部 1 1 0 は、以降の処理(ステップ S 9 1 1 ~ ステップ S 9 1 2)が、規定数回だけ行われたか否かを判断する(ステップ S 9 1 0)。この規定数は、ステップ S 4 1 2 で説明したものと同様である。処理回数が規定数に達した場合には、本処理を終了する(ステップ S 4 1 6)。処理回数が規定数に達しない場合には、コマンド分解部 1 1 0 は、画像処理モジュール 3 からコマンドを受け取り、コマンド内の画素データをアドレスカウンタで示されるメモリ 1 0 8 のメモリアドレスへ格納する。続いて、コマンド分解部 1 1 0 は、アドレスカウンタをインクリメントし(ステップ S 9 1 2)、処理をステップ S 9 1 0 へ戻す。

【 0 0 4 6 】

以上のように、D M A C 1 0 6 及びコマンド分解部 1 1 0 は、画像処理モジュール C 1 0 5 から順次に出力されたコマンドからデータを抽出してメモリ 1 0 8 の第 2 のアドレス空間へ順次に格納する。このとき、抽出及び格納する処理は、ステップ S 9 0 5 またはステップ S 9 0 9 で取得されたデータ量(レジスタの個数、画素数)に基づいて決定される回数だけ繰り返される。

【 0 0 4 7 】

上記手順によってメモリ 1 0 8 に格納されたレジスタ設定値及び画像データの様子を図 1 0 に示す。すなわち、D M A C 1 0 6 は、図 3 の( b )のように用意されたメモリ 1 0 8 のアドレス空間に、画像処理モジュール C 1 0 5 から受信したコマンドのレジスタ設定値や画素データを、図 1 0 に示されるように格納する。

【 0 0 4 8 】

このように、D M A C 1 0 2 がコマンド作成を行い、D M A C 1 0 6 がコマンド分解を

10

20

30

40

50

行う構成にすることによって、従来メモリにコマンドを格納していた場合に格納されていたヘッダ情報のような冗長なデータがなくなる。そのため、メモリ容量や、D M A C とメモリ間の転送帯域の削減が可能となる。また、C P U 1 0 1 がレジスタ設定値や画素データをコマンドに変換する手間もなくなる。

#### 【 0 0 4 9 】

尚、本発明は、ソフトウェアのプログラムをシステム或いは装置に直接或いは遠隔から供給し、そのシステム或いは装置のコンピュータが該供給されたプログラムコードを読み出して実行することによって前述した実施形態の機能が達成される場合を含む。この場合、供給されるプログラムは実施形態で図に示したフロー・チャートに対応したコンピュータプログラムである。

10

#### 【 0 0 5 0 】

従って、本発明の機能処理をコンピュータで実現するために、該コンピュータにインストールされるプログラムコード自体も本発明を実現するものである。つまり、本発明は、本発明の機能処理を実現するためのコンピュータプログラム自体も含まれる。

#### 【 0 0 5 1 】

その場合、プログラムの機能を有していれば、オブジェクトコード、インタプリタにより実行されるプログラム、O S に供給するスクリプトデータ等の形態であっても良い。

#### 【 0 0 5 2 】

コンピュータプログラムを供給するためのコンピュータ読み取り可能な記憶媒体としては以下が挙げられる。例えば、フロッピー（登録商標）ディスク、ハードディスク、光ディスク、光磁気ディスク、M O 、C D - R O M 、C D - R 、C D - R W 、磁気テープ、不揮発性のメモリカード、R O M 、D V D ( D V D - R O M , D V D - R ) などである。

20

#### 【 0 0 5 3 】

その他、プログラムの供給方法としては、クライアントコンピュータのブラウザを用いてインターネットのホームページに接続し、該ホームページから本発明のコンピュータプログラムをハードディスク等の記録媒体にダウンロードすることが挙げられる。この場合、ダウンロードされるプログラムは、圧縮され自動インストール機能を含むファイルであってもよい。また、本発明のプログラムを構成するプログラムコードを複数のファイルに分割し、それぞれのファイルを異なるホームページからダウンロードすることによっても実現可能である。つまり、本発明の機能処理をコンピュータで実現するためのプログラムファイルを複数のユーザに対してダウンロードさせるW W W サーバも、本発明に含まれるものである。

30

#### 【 0 0 5 4 】

また、本発明のプログラムを暗号化してC D - R O M 等の記憶媒体に格納してユーザに配布するという形態をとることもできる。この場合、所定の条件をクリアしたユーザに、インターネットを介してホームページから暗号を解く鍵情報をダウンロードさせ、その鍵情報を使用して暗号化されたプログラムを実行し、プログラムをコンピュータにインストールするようにもできる。

#### 【 0 0 5 5 】

また、コンピュータが、読み出したプログラムを実行することによって、前述した実施形態の機能が実現される他、そのプログラムの指示に基づき、コンピュータ上で稼動しているO S などとの協働で実施形態の機能が実現されてもよい。この場合、O S などが、実際の処理の一部または全部を行ない、その処理によって前述した実施形態の機能が実現される。

40

#### 【 0 0 5 6 】

さらに、記録媒体から読み出されたプログラムが、コンピュータに挿入された機能拡張ボードやコンピュータに接続された機能拡張ユニットに備わるメモリに書き込まれて前述の実施形態の機能の一部或いは全てが実現されてもよい。この場合、機能拡張ボードや機能拡張ユニットにプログラムが書き込まれた後、そのプログラムの指示に基づき、その機能拡張ボードや機能拡張ユニットに備わるC P U などが実際の処理の一部または全部を行

50

なう。

【図面の簡単な説明】

【0057】

【図1】実施形態による画像処理装置の構成を示すブロック図である。

【図2】実施形態による画像処理モジュールのレジスタアドレスを説明する図である。

【図3】(a)は、CPUによるレジスタ設定値と画素データのメモリへの格納状態を表す図であり、(b)は、画像処理モジュールから送信されたレジスタ設定値と画素データをメモリへ格納するのに必要なヘッダ情報の格納状態を表す図である。

【図4】実施形態に係るコマンド作成部による、コマンド作成の手順を示すフローチャートである。

【図5】実施形態のコマンド作成部による、作成したコマンドの一覧と作成順序を示す図である。

【図6】実施形態によるコマンドのフォーマットを示す図である。

【図7】一般的な画像処理装置の構成を示すブロック図である。

【図8】一般的な画像処理装置において、コマンドをメモリに格納した状態を示す図である。

【図9】実施形態のコマンド分解部による、コマンドの分解の手順を示すフローチャートである。

【図10】実施形態に係る、画像処理モジュールから入力されたレジスタ設定値と画素データをメモリに格納した状態を表す図である。

10

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

---

フロントページの続き

(72)発明者 審 崎 健太

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 石川 尚

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 広 島 明芳

(56)参考文献 特開2006-326857(JP, A)

特開平04-120652(JP, A)

特開平08-096112(JP, A)

特開平07-334452(JP, A)

(58)調査した分野(Int.Cl., DB名)

G 0 6 T 1 / 6 0

H 0 4 N 1 / 2 1