(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5852431号

(P5852431)

(45) 発行日 平成28年2月3日(2016.2.3)

(24) 登録日 平成27年12月11日(2015.12.11)

|                     |                |

|---------------------|----------------|

| (51) Int.Cl.        | F 1            |

| G06F 1/26 (2006.01) | G06F 1/26 334C |

| G06F 1/30 (2006.01) | G06F 1/30 L    |

| G06F 1/32 (2006.01) | G06F 1/32 B    |

請求項の数 9 (全 16 頁)

(21) 出願番号 特願2011-270616 (P2011-270616)

(22) 出願日 平成23年12月9日 (2011.12.9)

(65) 公開番号 特開2013-122673 (P2013-122673A)

(43) 公開日 平成25年6月20日 (2013.6.20)

審査請求日 平成26年12月9日 (2014.12.9)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

(74) 代理人 100134175

弁理士 永川 行光

最終頁に続く

(54) 【発明の名称】画像処理装置、その制御方法、及びプログラム

## (57) 【特許請求の範囲】

## 【請求項 1】

画像処理装置であって、

電源スイッチと、

前記電源スイッチが操作された後に第1時間が経過した場合、前記画像処理装置への電力供給を強制的に停止する電源遮断手段と、

前記電源スイッチが操作された場合に、前記画像処理装置のCPUがワーク領域として使用する第1記憶手段の記憶内容を第2記憶手段に退避させるハイバネーション処理を実行する処理手段と、

前記第1時間が経過する前に前記ハイバネーション処理が完了するか否かを判定する判定手段と、

前記判定手段によって前記第1時間が経過する前に前記ハイバネーション処理が完了しないと判定された場合、前記処理手段による前記ハイバネーション処理を中断させて、前記画像処理装置のシャットダウン処理を実行する制御手段と、

を備えることを特徴とする画像処理装置。

## 【請求項 2】

前記シャットダウン処理が実行された前記画像処理装置が起動される場合にコールドブートを実行する起動手段、をさらに備えることを特徴とする請求項1に記載の画像処理装置。

## 【請求項 3】

10

20

前記判定手段は、前記ハイバネーション処理を開始してから現在までの経過時間と、前記経過時間で終了したハイバネーション処理の進捗と、に基づいて、前記第1時間が経過する前に前記ハイバネーション処理が完了するか否を判定する、ことを特徴とする請求項1又は2に記載の画像処理装置。

【請求項4】

前記判定手段は、前記第1時間が経過する前に、前記ハイバネーション処理が完了するか否かを判定する、ことを特徴とする請求項1乃至3の何れか1項に記載の画像処理装置。

【請求項5】

前記処理手段は、

10

前記第1記憶手段の複数のメモリブロックのうち、前記第2記憶手段へ記憶内容を退避させるメモリブロックを選択する選択手段と、

前記選択手段によって選択されたメモリブロックの情報を示す管理情報を生成する生成手段と、

前記選択手段によって選択されたメモリブロックの記憶内容と、前記生成手段によって生成された管理情報を前記第2記憶手段へ格納する退避手段と、

を備えることを特徴とする請求項1乃至4に記載の画像処理装置。

【請求項6】

前記判定手段は、前記生成手段によって生成された前記管理情報を参照して、目標時間内に、前記処理手段による前記ハイバネーション処理が完了するか否かを判定する、ことを特徴とする請求項5に記載の画像処理装置。

20

【請求項7】

前記電源スイッチが操作されてからの経過時間を計時する計時手段、をさらに備え、

前記制御手段は、前記計時手段によって前記第1時間よりも短い第2時間が計時されると、前記画像処理装置のシャットダウン処理を実行する、ことを特徴とする請求項1乃至6の何れか1項に記載の画像処理装置。

【請求項8】

電源スイッチを備える画像処理装置の制御方法であって、

電源遮断手段が、前記電源スイッチが操作された後に第1時間が経過した場合、前記画像処理装置への電力供給を強制的に停止する電源遮断ステップと、

30

処理手段が、前記電源スイッチが操作された場合に、前記画像処理装置のCPUがワーク領域として使用する第1記憶手段の記憶内容を第2記憶手段に退避させるハイバネーション処理を実行する処理ステップと、

判定手段が、前記第1時間が経過する前に前記ハイバネーション処理が完了するか否かを判定する判定ステップと、

制御手段が、前記判定ステップで前記第1時間が経過する前に前記ハイバネーション処理が完了しないと判定された場合、前記処理ステップによる前記ハイバネーション処理を中断させて、前記画像処理装置のシャットダウン処理を実行する制御ステップと、

を実行することを特徴とする画像処理装置の制御方法。

【請求項9】

40

請求項8に記載の画像処理装置の制御方法における各ステップをコンピュータに実行させるためのプログラム。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、画像処理装置、その制御方法、及びプログラムに関するものである。

【背景技術】

【0002】

現行の画像処理装置は高機能化に伴い、ユーザが電源スイッチをONしてから操作可能となるまでの起動時間が増加する傾向にある。これに対し、ユーザが電源OFF操作をし

50

た際に主記憶メモリを通電させるサスPEND方式による起動時間の高速化手法がある。しかし、サスPEND方式は、メインメモリが一般的なDRAM等である場合には通電を継続する必要があり、待機電力を増大するという問題がある。このような待機電力をゼロにする技術がハイバネーション方式であり、サスPEND方式に対して復帰時間は掛かるが、より省電力性能を向上させたい場合に採用する技術である。例えば、特許文献1には、OFF/ONの状態を有する物理的な電源スイッチ(トグル型スイッチ)をハイバネーション機能として割り当てた技術が開示されている。また、特許文献2には、バッテリ残量が少なくなった場合にハイバネーション動作を行い、その際にバッテリが切れるとハイバネーション移行中の電源断が発生することを回避する技術が開示されている。

【先行技術文献】

10

【特許文献】

【0003】

【特許文献1】特開2002-73220号公報

【特許文献2】特開平11-3151号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、上記従来技術には以下に記載する問題がある。例えば、特許文献1では、画像処理装置の電源スイッチが物理的なOFF/ONの状態を有する(トグル型)スイッチであるため、スイッチのOFF/ON状態と本体の電源のOFF/ON状態を合わせる必要がある。つまり、スイッチがOFFなのに本体電源が切れていないという状態が発生してはならない。これを回避するために、電源スイッチがOFFされた際に、ソフトウェア制御とは別に電源装置に保護タイマを設定して一定時間後に電源が必ずOFFになっていることを保証する必要がある。しかし、電源スイッチをハイバネーション機能として割り当てた場合であって、さらにハイバネーション移行処理が間に合わなかった場合に、ハイバネーション移行中に強制的に上記保護タイマにより電源がOFFされる障害が発生してしまう。

20

【0005】

本発明は、上述の問題に鑑みて成されたものであり、電源スイッチをOFFにすることにより一定時間後に必ず電源が切れる構成を有する場合であっても、安全にハイバネーション移行処理を実行するとともに、電源供給の停止までに要する時間を好適に短縮する仕組みを提供することを目的とする。

30

【課題を解決するための手段】

【0006】

本発明は、例えば、画像処理装置であって、電源スイッチと、前記電源スイッチが操作された後に第1時間が経過した場合、前記画像処理装置への電力供給を強制的に停止する電源遮断手段と、前記電源スイッチが操作された場合に、前記画像処理装置のCPUがワーク領域として使用する第1記憶手段の記憶内容を第2記憶手段に退避させるハイバネーション処理を実行する処理手段と、前記第1時間が経過する前に前記ハイバネーション処理が完了するか否かを判定する判定手段と、前記判定手段によって前記第1時間が経過する前に前記ハイバネーション処理が完了しないと判定された場合、前記処理手段による前記ハイバネーション処理を中断させて、前記画像処理装置のシャットダウン処理を実行する制御手段と、を備えることを特徴とする。

40

【発明の効果】

【0007】

本発明は、電源スイッチをOFFにすることにより一定時間後に必ず電源が切れる構成を有する場合であっても、安全にハイバネーション移行処理を実行するとともに、電源供給の停止までに要する時間を好適に短縮する仕組みを提供できる。

【図面の簡単な説明】

【0008】

50

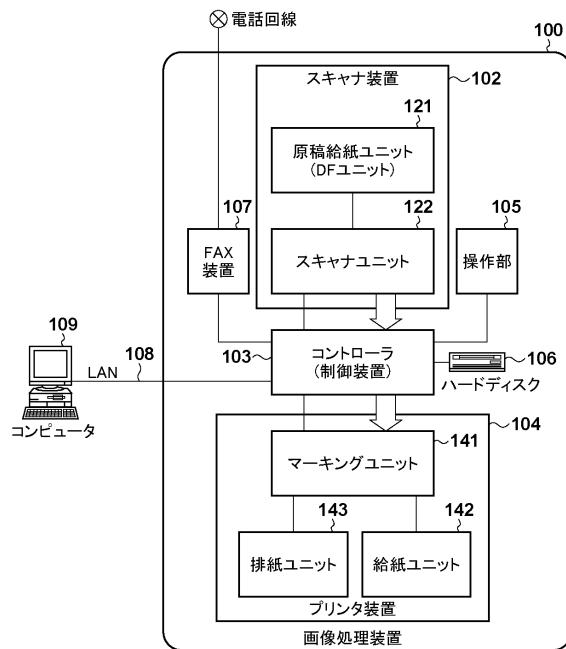

- 【図1】本実施形態に係る画像処理システムの構成例を示す図。

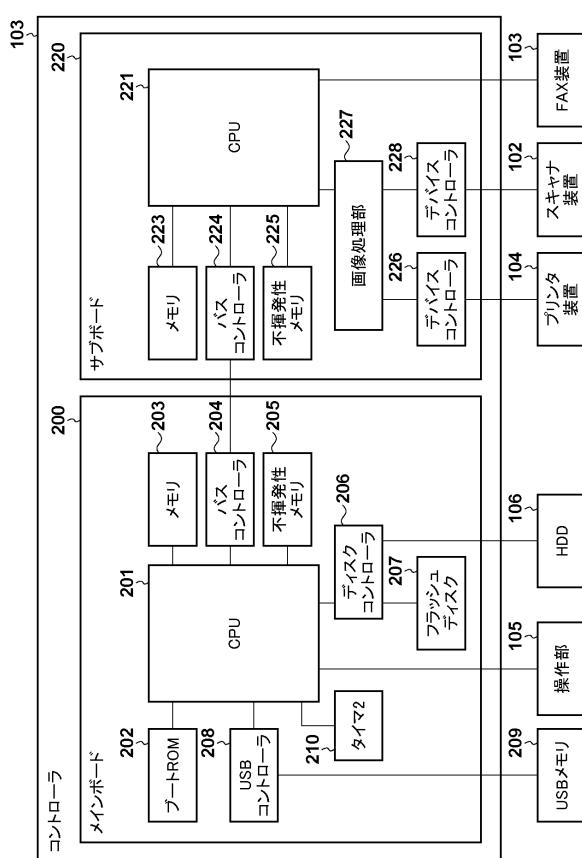

- 【図2】本実施形態に係るコントローラ部の構成例を示すブロック図。

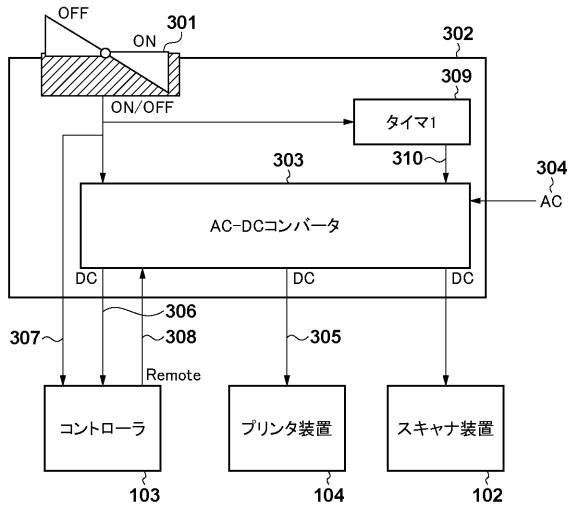

- 【図3】本実施形態に係る電源構成の一例を示す図。

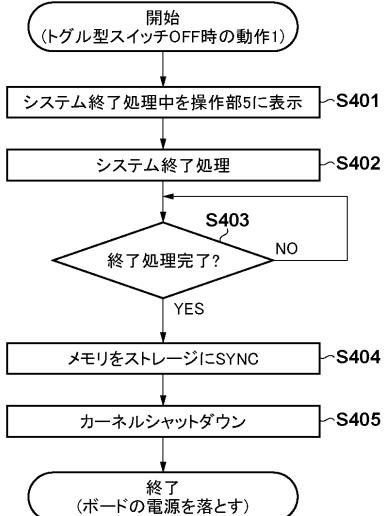

- 【図4】本実施形態に係るシャットダウン時の処理フローを示すフローチャート。

- 【図5】本実施形態に係るハイバネーションを説明する図。

- 【図6】本実施形態に係るシステム中断時の処理フローを示すフローチャート。

- 【図7】本実施形態に係る2次記憶デバイスを示す図。

- 【図8】正常な時と不具合が発生するケースを示すタイミングチャート。

- 【図9】本実施形態に係るタイミングチャート。

- 【図10】本実施形態に係るシステム保護タイマを示すタイミングチャート。 10

- 【図11】本実施形態に係る処理フローを示すフローチャート。

**【発明を実施するための形態】**

**【0009】**

以下、本発明を実施するための形態について図面を用いて説明する。尚、以下の実施形態は特許請求の範囲に係る発明を限定するものでなく、また実施形態で説明されている特徴の組み合わせの全てが発明の解決手段に必須のものとは限らない。

**【0010】**

<画像処理装置の構成>

まず、図1を参照して、本実施形態における画像処理システムの構成について説明する。図1に示すように、画像処理システムは、画像処理装置100と、当該画像処理装置100にLAN108を介して接続されたコンピュータ109を含んで構成される。なお、このシステム構成は、一例であり、本発明を限定する意図はない。例えば、他の画像処理装置や、他のコンピュータを含んで構成されてもよい。

**【0011】**

画像処理装置100は、スキャナ装置102、コントローラ103、プリンタ装置104、操作部105、ハードディスク106、及びFAX装置107を備える。スキャナ装置102は、原稿から光学的に画像を読み取りデジタル画像に変換する。プリンタ装置104は、デジタル画像を紙媒体に出力する。操作部105は、ユーザによって画像処理装置100を操作するためのインターフェースである。ハードディスク106は、デジタル画像や制御プログラム等を記憶する。FAX装置107は、電話回線等にデジタル画像を送信したり、電話回線等からデジタル画像を受信したりする。コントローラ103は、上述の各モジュールとそれぞれ接続され、各モジュールに指示を出すことで画像処理装置100上でジョブを実行する。

**【0012】**

画像処理装置100は、LAN108経由でコンピュータ109からデジタル画像の入出力、ジョブの発行や機器の指示等も行なうことが可能である。スキャナ装置102は、自動的に原稿束を自動的に逐次入れ替えることが可能な原稿給紙ユニット121、原稿を光学スキャンしデジタル画像に変換することが可能なスキャナユニット122を備える。変換された画像データは、コントローラ103に送信される。プリンタ装置104は、紙束から一枚づつ逐次給紙可能な給紙ユニット142、給紙した紙に画像データを印刷するためのマーキングユニット141、印刷後の紙を排紙するための排紙ユニット143を備える。

**【0013】**

画像処理装置100は多彩なジョブを実行可能である。一例を以下に記載する。

・複写機能

スキャナ装置102から読み込んだ画像をハードディスク106に記録し、同時にプリンタ装置104を使用して印刷を行なう。

・画像送信機能

スキャナ装置102から読み込んだ画像をLAN108を介してコンピュータ109に送信する。

・画像保存機能

スキャナ装置102から読み込んだ画像をハードディスク106に記録し、必要に応じて画像送信や画像印刷を行なう。

・画像印刷機能

コンピュータ109から送信された例えはページ記述言語を解析し、プリンタ装置104で印刷する。

【0014】

<コントローラの構成>

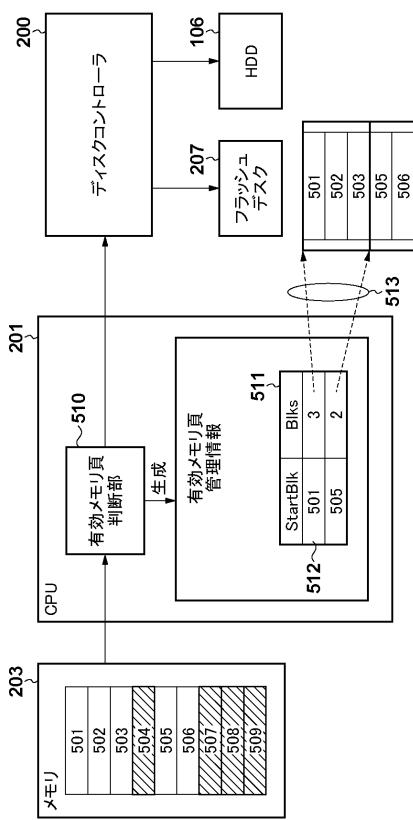

次に、図2を参照して、コントローラ103の構成例について説明する。コントローラ103はメインボード200と、サブボード220から構成される。メインボード200はいわゆる汎用的なCPUシステムであり、CPU201、ブートROM202、メモリ203、バスコントローラ204、不揮発性メモリ205、ディスクコントローラ206、フラッシュディスク207、USBコントローラ208、タイマ210を備える。CPU201は、ボード全体を統括的に制御する。ブートROM202は、初期起動時のプログラムであるブートプログラムを格納する。メモリ203は、CPU201によってワーク領域として使用される主記憶メモリである。バスコントローラ204は、外部バスとのブリッジ機能を有する。不揮発性メモリ205は、電源断された場合でも記憶内容が消えないメモリである。ディスクコントローラ206は、ストレージ装置を制御する。フラッシュディスク(SSD等)207は、半導体デバイスで構成された比較的小容量なストレージ装置である。USBコントローラ208は、USBデバイス(ここでは、USBメモリ209)を制御する。タイマ210は、計時手段として機能するシステム保護タイマである。また、メインボード200には外部に、USBメモリ209、操作部105、ハードディスク106等が接続される。

【0015】

サブボード220は、比較的小さな汎用CPUシステムと、画像処理ハードウェアから構成される。サブボード220は、CPU221、メモリ223、バスコントローラ224、不揮発性メモリ225、画像処理部227、及びデバイスコントローラ226、228を備える。CPU221は、ボード全体を統括的に制御する。メモリ223は、CPU221によってワークメモリとして使用される。バスコントローラ224は、外部バスとのブリッジ機能を有する。不揮発性メモリ225は、電源断された場合でも記憶内容が消えない。画像処理部227は、リアルタイムデジタル画像処理を行なう。デバイスコントローラ228、226は、それぞれ、外部のスキャナ装置102や、プリンタ装置104とデジタル画像データの受け渡しを行なう。なお、FAX装置107についてはCPU221が直接制御を行なう。

【0016】

なお、図2はブロック図であり簡略化している。例えばCPU201、CPU221等にはチップセット、バスブリッジ、クロックジェネレータ等のCPU周辺ハードウェアが多数含まれているが、説明を容易にするため簡略化しており、このブロック構成が本発明を制限するものではないことを理解されたい。

【0017】

ここで、コントローラ103の動作について、紙媒体による画像複写を例に説明する。ユーザが操作部105から画像複写を指示すると、CPU201は、CPU221を介してスキャナ装置102に原稿の画像読取命令を送る。スキャナ装置102は、紙原稿を光学スキャンしデジタル画像データに変換してデバイスコントローラ228を介して画像処理部227に入力する。画像処理部227はCPU221を介してメモリ223にDMA転送を行いデジタル画像データの一時保存を行なう。

【0018】

CPU201はデジタル画像データがメモリ223に一定量もしくは全て入ったことが確認できると、CPU221を介してプリンタ装置104に画像出力指示を出す。CPU221は、画像処理部227にメモリ223に格納された画像データの位置(アドレス)

10

20

30

40

50

を教える。プリンタ装置 104 からの同期信号に従ってメモリ 223 上の画像データは画像処理部 227 とデバイスコントローラ 226 を介してプリンタ装置 104 に送信され、プリンタ装置 104 において紙媒体にデジタル画像データが印刷される。複数部の印刷を行なう場合には、CPU 201 は、メモリ 223 の画像データをハードディスク 106 に保存する。したがって、2 部目以降はスキャナ装置 102 から画像をもらわざともプリンタ装置 104 に画像を送ることが可能である。

#### 【0019】

##### <電源スイッチの構成>

次に、図 3 を参照して、本実施形態に係る画像処理装置 100 における電源スイッチの構成について説明する。図 3 に示す 301 はトグル型の電源スイッチである。302 は電源ユニットである。303 は AC - DC コンバータである。304 は AC 電源入力部である。305 はプリンタ装置 104 に対して DC 電源を供給する電源ケーブルである。306 はコントローラ 103 に対して電源を供給する電源ケーブルである。307 はトグル型スイッチ 301 の状態をコントローラに通知するラインである。308 は AC - DC コンバータの出力を制御することの可能な電源リモート信号である。309 はトグル型スイッチ 301 が電源供給を停止するように操作されてから所定時間が経過するまでに確実に電源供給の停止を保障するための電源保護タイマである。310 は AC - DC コンバータの出力を制御することが可能なリモート線である。

#### 【0020】

操作者はトグル型スイッチ 301 を操作することで画像処理装置 100 を ON / OFF することが可能である。トグル型スイッチ 301 は ON 時に AC - DC コンバータに接続されており電源の通電状態を制御することができる。また、OFF 時はコントローラ 103 がシステムのシャットダウン（画像処理装置 100 の終了処理）が完了するまで 306 の電源供給を停止してはならない。つまり、307 のラインを介してトグル型スイッチ 301 の状態を通知し、シャットダウンが完了後に電源リモート信号 308 を用いて DC 電源供給 306 を OFF にするようになっている。このように、画像処理装置 100 の電源構成は、シャットダウンが必要な一般的な機器が持っている電源構成と同様である。

#### 【0021】

トグル型スイッチ 301 は ON / OFF の状態のどちらか一方の状態をメカ的に保持し続けるスイッチである。操作者は ON / OFF のいずれか側にスイッチを倒すことで電源の状態を入力することができる。タイマ 309 は、トグル型スイッチ 301 の OFF に連動して時間を計測し、一定時間後に 310 のリモート信号を変化させ、AC - DC コンバータ 303 の出力を強制的に OFF できるようになっている。つまり、トグル型スイッチ 301 が OFF された時間を計測し、一定時間後に AC - DC コンバータ 303 を OFF にすることで、一定時間後に装置電源を完全に落とす機能を備えた電源となっている。

#### 【0022】

また、コントローラ 103 は電源リモート信号 308 を用いることで自分自身の電源を落とすことが可能である。その場合トグル型スイッチ 301 の物理的な OFF / ON 状態との不一致を防止するために、コントローラ 103 は、307 による電源 OFF 通知がなされた場合は、電磁石を用いたソレノイド等を用いてトグル型スイッチ 301 を自動的に OFF することができる。

#### 【0023】

つまり、図 3 に示す電源が電力を供給する「コントローラ 103、プリンタ装置 104、スキャナ装置 102」への電源供給を止める方法は以下の 2 つの方法がある。

(1) スイッチ 301 の OFF を 307 経由でコントローラ 103 が受信、シャットダウン後に電源リモート信号 308 を用いて「コントローラ 103、プリンタ装置 104、スキャナ装置 102」の電源を落とす方法。

(2) スイッチ 301 の OFF 状態をタイマ 309 が一定時間 (120s) の時間計測する。電源リモート信号 308 において一定時間 (120s) が経過する間に OFF が発生しなかった場合、リモート制御信号 310 が変化して、「コントローラ 103、プリンタ

10

20

30

40

50

装置 104、スキャナ装置 102」の電源を落とす方法。

上記(2)はトグル型スイッチ 301 が OFF されているにも関わらず、「コントローラ 103、プリンタ装置 104、スキャナ装置 102」の電源が切れないことを防止するための電源保護回路となる。

#### 【0024】

<シャットダウン時の処理フロー>

次に、図4を参照して、トグル型スイッチ 301 が OFF された場合の処理フローについて説明する。ここでは、操作者が本体を終了させる時の動作について説明する。本体電源スイッチに相当するトグル型スイッチ 301 が OFF されたことを検知すると、CPU 201 は以下の処理を実行する。またこの時タイマ 309 は電源保護回路のための時間測定を開始する。以下で説明する処理は、CPU 201 が不揮発性メモリ 205 や HDD 106 等に格納された制御プログラムをメモリ 203 に読み出して実行することにより実現される。

10

#### 【0025】

S401において、CPU 201 は、トグル型スイッチ 301 が OFF に操作されると、操作部 105 上にシステム終了中の画面を表示する。続いて、S402において、CPU 201 は、現在行っているサービス等の中止・終了処理を行う。終了処理は複数のプロセスで平行に実行されているため、S403において、CPU 201 は終了処理が完了したか否かを判定する。終了している場合は S404 に進み、終了していない場合は S403 の判定を定期的に繰り返す。

20

#### 【0026】

S404において、CPU 201 は、メモリの値をストレージにシンク (SYNC) する。ここで「シンクする (SYNC)」とは、例えばDRAM上にキャッシュしたストレージバッファの内容をストレージへ同期させるために、当該ストレージへバッファの内容を格納する処理を示す。続いて、S405において、CPU 201 は、Kernel のシャットダウン I/F を呼び、カーネルのソフトウェア最終終了処理を行う。その後、S406において、CPU 201 は、電源リモート信号 308 経路で AC - DC コンバータ 303 を OFFさせ、装置全体の電源が落ちる。装置全体の電源が落ちることにより、タイマ 309 自体の電源も落ち、電源保護タイマは機能を停止する。

30

#### 【0027】

仮になんからの不具合により、図4に示すフローチャート内のいずれかで処理が停止した場合は、コントローラ 103 は、電源リモート信号 308 を変化させないことになる。しかしながら、その場合はタイマ 309 がリモート制御信号 310 を用いて AC - DC コンバータ 303 の出力を落とすことで強制的に電源が落とされる。

#### 【0028】

<ハイバネーション>

次に、図5を参照して、本実施形態で用いるハイバネーションの方法について説明する。ハイバネーションとは、装置の電源を切る直前の状態を保存し、次に電源を ON したときに電源を切る直前の状態から動作を再開する機能を示す。したがって、電源 OFF 時にハイバネーションを用いるためには、電源断時の所定のメモリの状態（内容）を保持しておく必要がある。CPU 201 上で動作する一般的なカーネルはメモリ 203 を一定サイズ毎に「ページ」で管理している。ページには、

40

- A . 破棄しても良い状態のメモリ（有効ではないメモリ）

- B . 破棄してはならない状態のメモリ（有効メモリ）

の 2 状態が存在する。

#### 【0029】

A は、例えば、ディスクキャッシュとして動作している状態で外部のディスクと中身が同期されていることが分かっているページ、又は、未使用のメモリ等である。B は、例えば、ユーザにより外部ディスクに対する変更要求をメモリにキャッシュしたが、まだ同期がなされていない状態のものや、カーネル自体のメモリ等である。A のメモリは破棄して

50

も構わないためハイバネーション対象として保存しなければならないメモリはBだけで良いことになる。また、有効メモリであっても全ての領域にゼロが格納されているメモリは削除しても構わないカーネルもある。有効メモリ判断部510は、選択手段として機能し、このような有効メモリを判断するが、カーネルの種類や方式により判断条件は異なる。

#### 【0030】

本実施形態では501～509のうち、501～503と505～506はBの有効メモリとし、有効メモリだけをハイバネーション方式を用いてディスクに保存し、また、復帰させることで画像処理装置100と同じ状態に戻すことができる。ハイバネーションはおおよそBIOSで行うものと、ソフトウェアが制御するものの2通りある。前者の方式は有効なメモリを限定する手段がないため全メモリ領域を保存・復帰する必要があった。近年主流となりつつあるのは後者的方式であり、カーネル内部で動作するためメモリの必要な部分だけを保存・復帰すれば、短い時間でハイバネーション処理を終了させることができる。近年、後者の（本実施形態では以降ソフトハイバネーションと称する。）ソフトハイバネーション方式がよく扱われている。本実施形態はソフトハイバネーション方式で説明するが、本発明はハイバネーションの方式を限定するものではない。

10

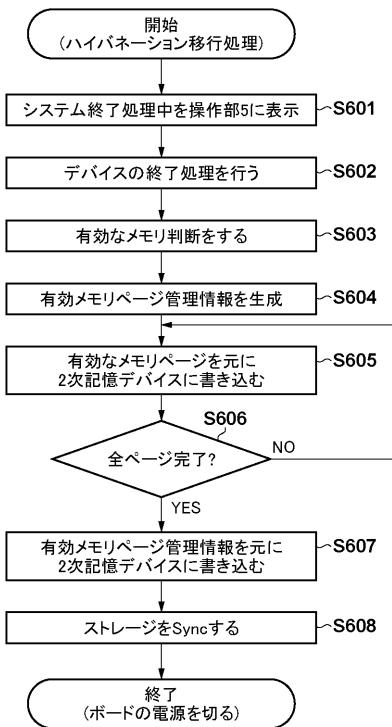

#### 【0031】

##### <ハイバネーション移行処理>

次に、図6を参照して、ハイバネーション終了する際の移行処理について説明する。ここでは、図5に示す例を用いて説明する。以下で説明する処理は、CPU201が不揮発性メモリ205やHDD106等に格納された制御プログラムをメモリ203に読み出して実行することにより実現される。

20

#### 【0032】

S601において、CPU201は、ハイバネーション移行処理を開始すると、操作部105に「システム終了処理中」を示すメッセージを出力する。続いて、S602において、CPU201は、ボードの電源を落とすため、現在動作しているハードウェアデバイスのドライバを中断させ、動作しない状態とする。

#### 【0033】

次に、S603において、CPU201は、メモリ203の501～509を遂次読み込み、有効メモリ判断部510によって必要なメモリだけを判断する。図5における有効メモリは、501～503、505～506となる。S604において、CPU201は、有効メモリページ管理情報を生成する。本実施形態では511のように、有効メモリページ管理情報は、有効なメモリが開始される先頭のブロックの情報と、有効なメモリブロックが連続するブロック数の情報を含む。この管理情報はこの2つの情報に加えて、例えば、物理メモリのアドレス、仮想メモリ上のアドレス、メモリの使用用途、ストレージ上の保存位置等、必要に応じて必要な情報を追加で含んでもよい。このように、本実施形態における有効メモリページ管理情報とは、ストレージに退避したメモリブロックを、メインメモリに復元するために参照するための管理情報を意味する。

30

#### 【0034】

S605において、CPU201は、有効メモリページ管理情報の一要素である例えば512に示す情報に従って、501から3ブロックのメモリをディスクコントローラ206を介在してフラッシュディスク207に保存する。S606において、CPU201は、有効メモリページ管理情報でリストアップされた、退避が必要な全てのメモリブロックを保存するまでループする。メモリ203から511に従って513のようなデータ転送が発生する。

40

#### 【0035】

全ての有効なメモリをフラッシュディスク207へ退避する処理が完了すると、S607において、CPU201は、有効メモリページ管理情報511自身を保存し、S608で全てのメモリ値をストレージ（フラッシュディスク207）にシンクさせる。その後、CPU201は、電源リモート信号308を用いてシステムの電源を落とす。

#### 【0036】

50

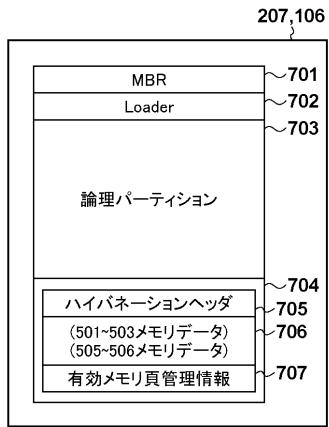

## &lt; 2 次記憶デバイス &gt;

次に、図 7 を参照して、2 次記憶デバイスとしてのフラッシュディスク 207 上のメモリマップについて説明する。701 は、MBR (Master Boot Record) である。702 がシステムのローダである。703 は論理パーティション群である。704 は、ハイバネーション用に作られた領域を示し、ハイバネーションヘッダ 705、データ領域 706、及び有効メモリページ管理情報 707 を含む。データ領域 706 には、501～503 及び 505～506 のメモリに含まれた情報が格納される。なお、このようなメモリマップは、一例であり、本発明を限定する意図はない。

## 【0037】

## &lt; タイミングチャート &gt;

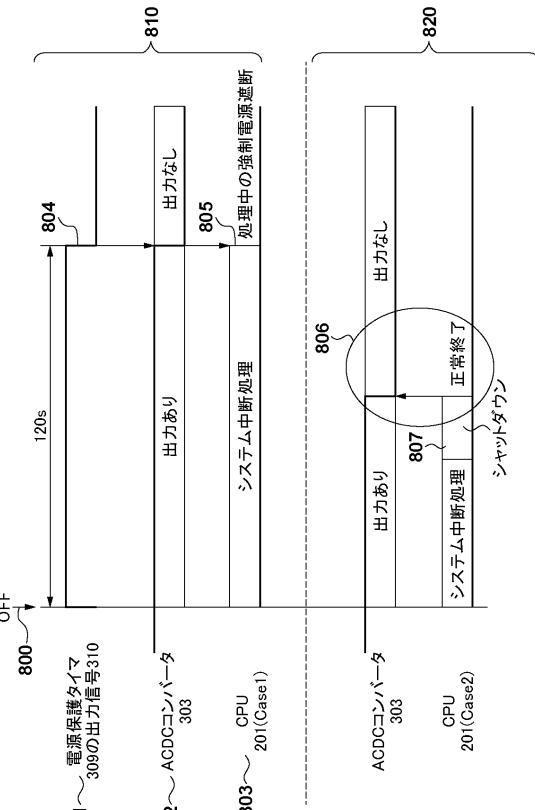

10

以下では、図 8 を参照して、ハイバネーション移行処理が正常に行われるケース 820 と、CPU201 の強制電源遮断が発生してしまうケース 810 について説明する。まず、ケース 810 について説明する。801 は図 3 の電源保護タイマ 309 のカウントアップ状態を示す。802 は AC - DC コンバータ 303 の電圧出力である。803 は図 2 の CPU201 の実行している処理内容を示す。横軸は時間であり、800 に示すトグル型スイッチ 301 が OFF されるタイミングから、801～803 の動作状況を記載したものである。

## 【0038】

操作者が 800 地点でトグル型スイッチ 301 を OFF になると、電源保護タイマ 309 は電源を保護する目的でカウントアップを開始する。本実施形態ではこの電源保護タイマ 309 の測定時間を 120 秒とする。即ち、本実施形態の場合、120 秒後に電源 OFF が保障される。

20

## 【0039】

803 に示すように、CPU201 は、図 6 を用いて説明したシステム中断処理（ハイバネーション移行処理）を実行する。電源保護タイマ 309 は電源を保護するための 120 秒を測定する。仮に 803 に示すように、CPU201 (Case 1) のシステム中断処理が 120 秒以上の時間を必要とする場合、804 のタイミングでリモート制御信号 310 が OFF となり、802 の AC - DC コンバータ 303 の電源供給が停止される。これによりコントローラ 103 の電源が OFF されることになり、CPU201 がハイバネーション処理を実行しているにもかかわらず電源が強制的に落ちることになる。ハイバネーションはメモリの値をストレージに書き込むため、ストレージアクセス中の OFF となるため、ストレージ内のデータ破損を招く可能性もある。

30

## 【0040】

ケース 820 について説明する。CPU201 (Case 2) のシステム中断処理が 120 秒以内に終了する場合はシャットダウン 807 が実行され、806 に示すようにハイバネーションの処理が完了後、AC - DC コンバータ 303 の電源を自発的に切ることができ、システムは正常に終了する。

## 【0041】

ハイバネーション移行処理にかかる時間は、変動する複数の要因が存在し、その変動幅も大きい。例えば、

40

- ・メモリ 203 が汚れてくることによりハイバネーション対象となるデータ量が大幅に増えた

- ・データ領域 706 へ書き込む際のストレージのアクセス速度の一時的な低下、等が考えられる。また、遅延が外部のデバイス要因の場合、実際にアクセスするまで所要時間は分からぬため、事前に計算することはできない。

## 【0042】

## &lt; 処理フロー &gt;

本発明は上述のような一定時間内に装置を終了させる必要がある状況下における、ハイバネーション移行処理の方法を提案するものである。以下では、図 9 乃至図 11 を参照して、本発明におけるトグル型スイッチ 301 が OFF された場合の処理フロー及びタイミン

50

グについて説明する。図9は、本実施形態におけるハイバネーション移行処理を実行した際のタイミングチャートを示し、図11は、本実施形態におけるハイバネーション移行処理の処理フローを示す。以下で説明する処理は、CPU201が不揮発性メモリ205やHDD106等に格納された制御プログラムをメモリ203に読み出して実行することにより実現される。

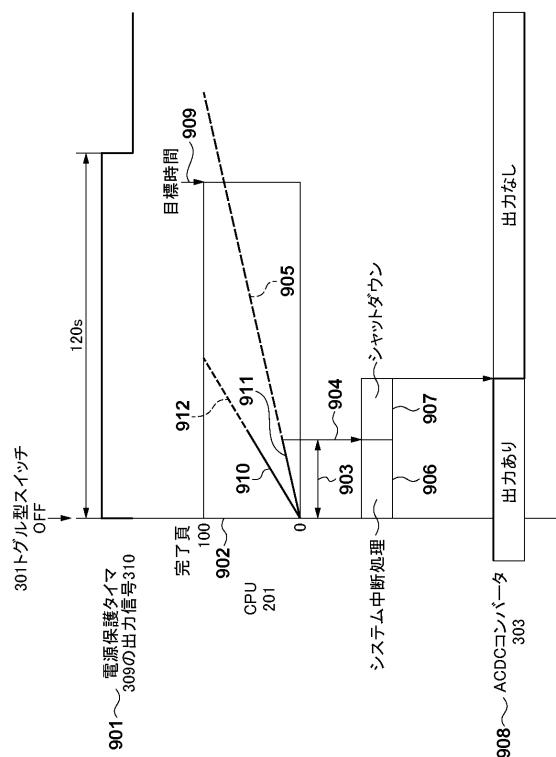

#### 【0043】

図9の901は電源保護タイマ309のカウントアップ状態を示す。902の縦軸はCPU201がS606～S607の処理を実行中に、データ領域706に書き込む必要のある全ページ数の進捗を100に正規化したものである。つまり、データ領域706に書き込むべきデータの保存処理の進捗を示すためのグラフを形成している。

10

#### 【0044】

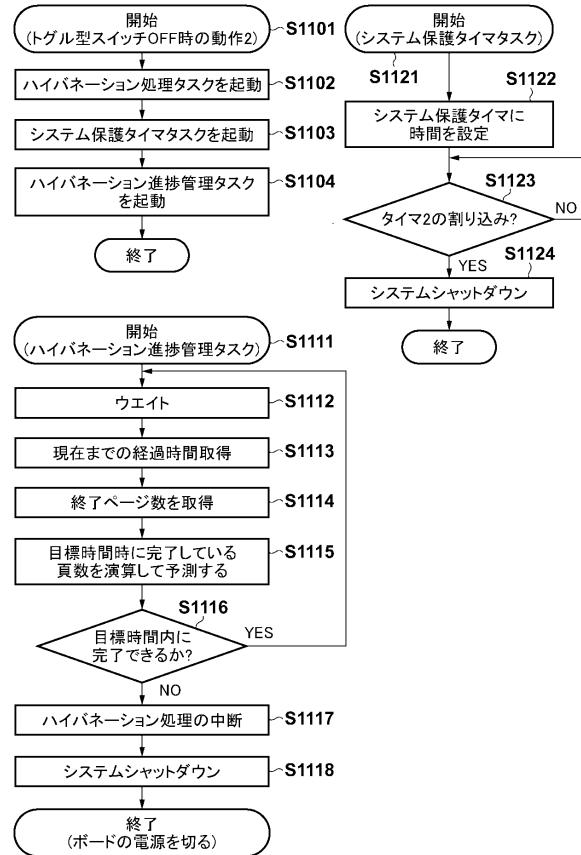

操作者がトグル型スイッチ301をOFFにした場合、本実施形態によれば、図11の1101のフローチャートが実行される。S1102において、CPU201は、ハイバネーション移行処理タスク（図6のフローチャートを実行するタスク）を起動し、S1103でシステム保護タイマタスク（図11のフローチャート1121を実行するタスク）を起動する。さらに、S1104において、CPU201は、ハイバネーション進捗管理タスク（図11のフローチャート1111を実行するタスク）を起動して、処理を終了する。これら3つのフローチャートは独立したスレッドでCPU201上で仮想的に並行して実行される。

#### 【0045】

上述したように、図6のフローチャートはハイバネーション対象となる全メモリページを算出し、データ領域706に逐次書き込んでいく。書き込みが完了すると、シャットダウンを行うハイバネーション移行処理を実行する。フローチャート1111は、ハイバネーション処理実行中においても並行で動作するハイバネーションの進捗を管理するためのタスクによって実行される。具体的には目標時間909までに図6のフローチャートが完了するか否かを監視する。

20

#### 【0046】

まず図6のフローチャートにおいて実行されるハイバネーション保存処理（ハイバネーション処理）が図9の910の実線のように動作した場合の正常終了ケースについてフローチャート1111を用いて説明する。S1112において、CPU201は、一定時間903区間の待機を実施する。続いて、S1113において、CPU201は、現在までの経過時間t（グラフ902における横軸上のポイント）を取得する。さらに、S1114において、CPU201は、メモリページにおける全ページ数と現在終了したページ数を取得する。

30

#### 【0047】

次に、S1115において、CPU201は、目標時間909までに現在のハイバネーションのメモリページ保存処理が完了するか否かを判定する。演算方法はいろいろあるが、例えば、以下の式を用いて計算することができる。

(式1) 進捗 = 書き込み完了したメモリページ数 / 書き込みが必要なメモリページ数 \* 100

40

上記式1により902の縦軸、つまり書き込み処理完了を100%とした現在の時間tにおける進捗[%]を得ることができる。

#### 【0048】

次に、S1116において、現在の進捗において目標時間909に間に合うか否かを、例えば以下の条件式を用いて判定する。

(式2) (進捗 \* 目標時間909) / t > 100

上記式2を評価することにより、目標時間内909にハイバネーションの保存処理が完了するか否かの判断を行うことができる。

#### 【0049】

実線910の場合、破線912のように進捗すると予想できるため、目標時間909ま

50

でに全ページの保存処理が完了できると判断され、S11112のウエイト処理に処理を戻す。S11112で待機した後に再び同様の評価が行われる。このようなループ処理を何度か繰り返すと、問題が無ければ破線912の進捗状態を推移し、上記S608の処理でストレージがシンクされ、AC-DCコンバータ303はOFFとなりボード電源が落ちる。これが正常ケースの処理フローとなる。

#### 【0050】

次に、図6のフローチャートのハイバネーション保存処理が実線911のように動作する、ハイバネーション中断の終了ケースについて記載する。実線910のときと同様にS11112乃至S11116が実行される。S11116の演算を行った結果、現在の進捗率では目標時間909までに処理が完了しないことが予想できる。そこでS11117に進み、CPU201は、図6のフローチャートのハイバネーション処理を中断させ、705~707のハイバネーション領域の情報のケア（中間データを破棄など）を行う。続いて、S11118において、CPU201は、電源制御手段として機能し、システムをシャットダウンさせて、電源を切る。これは図9における907のシャットダウン動作となり、908に示すようにシャットダウン完了後にボード電源が落ちることになる。

10

#### 【0051】

このように本発明を実施することにより、所定時間内にハイバネーション保存処理が完了しない場合には、目標時間909まで待つことなく、短い時間でシステムを終了することが可能である。また、目標時間909を適切に設定することにより、外部に電源を強制的にOFFする構成のタイマ装置がついている電源供給源であったとしても、ハイバネーション動作中に電源が落とされるリスクを回避することが可能となる。

20

#### 【0052】

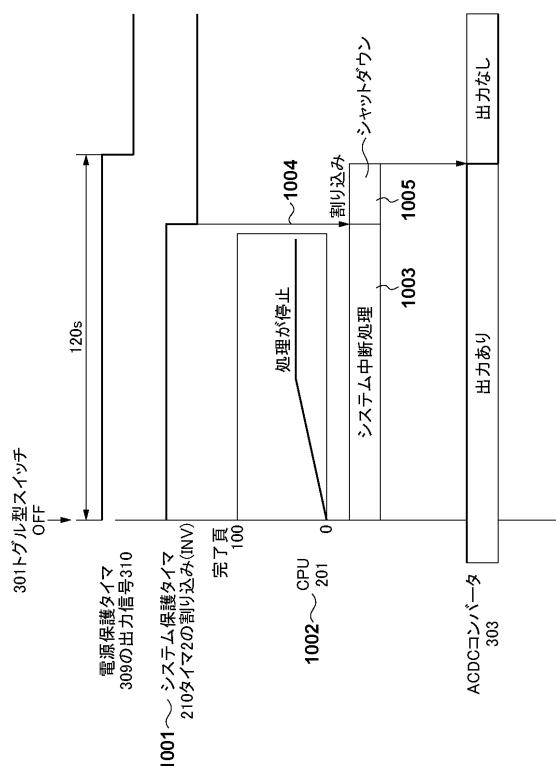

ただし、これはハイバネーションの処理を行うCPU201の処理が正常に動作している場合に有効となる方法である。一方でフローチャート1111が正常に動作しなくなった場合や、図10に示す1003のタイミングでハイバネーションを実行中のプロセスが固まって動作しなくなった場合なども考えられる。このような場合にはS11116乃至S11118までの処理を判断・実行すらできずに強制的に電源が落とされることとなる。そこで、本実施形態によれば、システム保護タイマタスクによって、これらの異常状態でも正常に終了させるための仕組みを提供する。具体的な処理について、図10のタイミングチャートと図11のフローチャート1121を参照して、説明する。

30

#### 【0053】

まず、S1122において、CPU201は、システム保護タイマ210の設定を行う。設定する時間は、

(式3) タイマ210時間 < (タイマ309時間 - シャットダウン1005時間)

かつ、タイマ210時間 > (目標時間909 + シャットダウン1005時間)とする。即ち、タイマ210に設定される時間(第2時間)は、シャットダウン処理に要する時間をタイマ309に設定する時間(第1時間)から減算した時間より短く、かつ、シャットダウン処理に要する時間を目標時間909に加算した時間よりも長くなるように設定される。このように設定することで、タイマ309の時間が経過する前にCPU201にイベントを発行し、イベント受信からシャットダウン処理1005を行ったとしても電源保護タイマ309の間に間に合うように制御することが可能となる。このように、上記式3の条件により求められるタイマ210の設定時間がS1122で設定される。

40

#### 【0054】

S1123において、CPU201は、タイマ210の割り込みが発生したか否かを判定する。発生していない場合には、定期的にS1123の判定を繰り返す。一方、割り込みが発生すると、S1124に進む。図10の1004のタイミングでタイマ210が満了するとS1124に進み、CPU201は、強制終了手段として機能し、シャットダウン処理1005を行い、その後、電源保護タイマ309の時間が満了する前にボードの電源を落とす。この制御はハイバネーションを実行しているプロセス(ソフトウェア資源)と異なるプロセスやカーネルモード等の特権モードで動作するシステムに構築することで

50

、より強い強制力を持ってシステムの正常終了処理を実行することが可能となる。

#### 【0055】

また、本実施形態によれば、ハイバネーションが行われなかった場合は、次回電源ON時にシステムのコールドブートが行われる。したがって、前回の終了前状態に復帰することはできない、また起動時間の低下が発生したりするものの、正常に装置を制御することが可能である。

#### 【0056】

以上説明したように、本実施形態によれば、トグル型スイッチ301のOFFをトリガに外部より強制的に電源供給を停止する時限タイマを有する画像処理装置において、時間変動要因の大きいハイバネーションのデータ保存処理を安全に行うことが可能となる。また、データ保存処理が間に合わない場合には、最小の時間であきらめることができあり、スイッチOFFから実際に電源が切れるまでの時間（システム終了時間）を短縮することが可能である。

#### 【0057】

<その他の実施形態>

また、本発明は、以下の処理を実行することによっても実現される。即ち、上述した実施形態の機能を実現するソフトウェア（プログラム）を、ネットワーク又は各種記憶媒体を介してシステム或いは装置に供給し、そのシステム或いは装置のコンピュータ（又はCPUやMPU等）がプログラムを読み出して実行する処理である。

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

---

フロントページの続き

(72)発明者 原 健二

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 西村 直史

(56)参考文献 特開2009-003588(JP,A)

特開2004-262065(JP,A)

特開平10-222310(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 1 / 26

G 06 F 1 / 30

G 06 F 1 / 32