(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-353626

(P2005-353626A)

(43) 公開日 平成17年12月22日(2005.12.22)

(51) Int.Cl.<sup>7</sup>

H01L 27/14

H01L 27/146

H04N 5/335

H04N 9/07

F 1

H01L 27/14

H04N 5/335

H04N 9/07

H01L 27/14

テーマコード(参考)

4M118

5C024

5C065

F

審査請求 未請求 請求項の数 8 O L (全 17 頁)

(21) 出願番号

特願2004-169458 (P2004-169458)

(22) 出願日

平成16年6月8日(2004.6.8.)

(71) 出願人 000005201

富士写真フィルム株式会社

神奈川県南足柄市中沼210番地

(74) 代理人 100105647

弁理士 小栗 昌平

(74) 代理人 100105474

弁理士 本多 弘徳

(74) 代理人 100108589

弁理士 市川 利光

(74) 代理人 100115107

弁理士 高松 猛

(74) 代理人 100090343

弁理士 濱田 百合子

最終頁に続く

(54) 【発明の名称】光電変換膜積層型固体撮像素子及びその製造方法

## (57) 【要約】

【課題】 光電変換膜積層型固体撮像素子の共通電極膜へ均一なバイアス電位を印加する配線を容易に製造可能とする。

【解決手段】 共通電極膜11r, 11g, 11bと画素対応の画素電極膜8r, 8g, 8bによって挟まれた光電変換膜10r, 10g, 10bが絶縁層12, 13を介して半導体基板1の上に複数層積層される光電変換膜積層型固体撮像素子100において、光電変換膜積層型固体撮像素子の周辺部にて共通電極膜11r, 11g, 11bを前記周辺部に沿うフラット状の配線51r, 51g, 51bにより半導体基板1に形成されている配線用高濃度不純物領域52r, 52g, 52bに接続する。

【選択図】 図2

**【特許請求の範囲】****【請求項 1】**

共通電極膜と画素対応の画素電極膜とによって挟まれた光電変換膜が絶縁層を介して半導体基板の上に複数層積層される光電変換膜積層型固体撮像素子において、該光電変換膜積層型固体撮像素子の周辺部にて前記共通電極膜を前記周辺部に沿うフラット状の配線により前記半導体基板に形成されている配線用高濃度不純物領域に接続したことを特徴とする光電変換膜積層型固体撮像素子。

**【請求項 2】**

赤色検出用、緑色検出用、青色検出用の3つ光電変換膜を検出波長の短い順に上から順に備え、3つの光電変換膜のうち2つの光電変換膜に設ける前記共通電極膜を共用したことを特徴とする請求項1に記載の光電変換膜積層型固体撮像素子。10

**【請求項 3】**

赤色検出用、緑色検出用、青色検出用、エメラルド色検出用の4つの光電変換膜を検出波長の短い順に上から備え、4つの光電変換膜のうちの隣接する2つの光電変換膜に設ける前記共通電極膜を共用したことを特徴とする請求項1に記載の光電変換膜積層型固体撮像素子。

**【請求項 4】**

前記光電変換膜の材料として無機材料を用いたことを特徴とする請求項1乃至請求項3のいずれかに記載の光電変換膜積層型固体撮像素子。

**【請求項 5】**

前記光電変換膜の材料として有機材料を用いたことを特徴とする請求項1乃至請求項3のいずれかに記載の光電変換膜積層型固体撮像素子。20

**【請求項 6】**

請求項1乃至請求項5のいずれかに記載の光電変換膜積層型固体撮像素子の製造方法において、前記画素電極膜及び前記光電変換膜を積層し前記共通電極膜を積層する前または前記共通電極膜を積層した後に、前記周辺部において前記フラット状の配線を蒸着して前記共通電極膜を前記配線用高濃度不純物領域に接続することを特徴とする光電変換膜積層型固体撮像素子の製造方法。

**【請求項 7】**

前記フラット状の配線の蒸着によって前記共通電極膜上または前記光電変換膜上に前記配線材料が盛り上がって形成された場合には、該盛り上がり部分をポリッシングして平坦化することを特徴とする請求項6に記載の光電変換膜積層型固体撮像素子の製造方法。30

**【請求項 8】**

前記共通電極膜が複数存在し各共通電極膜に接続される前記フラット状の配線を複数重ねて設ける場合には各フラット状の配線間に絶縁材を形成して電気的に分離することを特徴とする請求項6または請求項7に記載の光電変換膜積層型固体撮像素子の製造方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、信号読出回路が表面に形成された半導体基板の上に光電変換膜を積層して構成される光電変換膜積層型固体撮像素子及びその製造方法に関する。40

**【背景技術】****【0002】**

光電変換膜積層型固体撮像素子の原型的な素子として、例えば下記特許文献1記載のものがある。この固体撮像素子は、半導体基板の上に感光層を3層積層し、各感光層で検出された赤色(R)、緑色(G)、青色(B)の夫々の電気信号を、半導体基板表面に形成されているMOS回路で読み出すという構成になっている。

**【0003】**

斯かる構成の固体撮像素子が過去に提案されたが、その後、半導体基板表面部に多数の受光部(フォトダイオード)を集積すると共に各受光部上に赤色(R)、緑色(G)、青50

色（B）の各色カラーフィルタを積層したCCD型イメージセンサやCMOS型イメージセンサが著しく進歩し、現在では、数百万もの受光部（画素）を1チップ上に集積したイメージセンサがデジタルスチルカメラに搭載される様になっている。

#### 【0004】

しかしながら、CCD型イメージセンサやCMOS型イメージセンサは、その技術進歩が限界近くまで進み、1つの受光部の開口の大きさが $2\text{ }\mu\text{m}$ 程度と、入射光の波長オーダーに近づいており、製造歩留まりが悪いという問題に直面している。

#### 【0005】

また、微細化された1つの受光部に蓄積される光電荷量の上限は、電子3000個程度と少なく、これで256階調を奇麗に表現するのが困難にもなってきている。このため、画質や感度の点で今以上のイメージセンサをCCD型やCMOS型で期待するのは困難になっている。

#### 【0006】

そこで、これらの問題を解決する固体撮像素子として、特許文献1で提案された固体撮像素子の構造が見直されるようになり、特許文献2や特許文献3に記載されているイメージセンサが新たに提案される様になってきている。その他にも、特許文献4, 5に記載されたものもある。

#### 【0007】

特許文献2に記載されたイメージセンサは、シリコンの超微粒子を媒質内に分散して光電変換層とし、超微粒子の粒径を変えた複数の光電変換層を半導体基板の上に3層積層し、夫々の光電変換層で、赤色、緑色、青色の夫々の受光量に応じた電気信号を発生させる様になっている。

#### 【0008】

特許文献3に記載されたイメージセンサも同様であり、粒径の異なるナノシリコン層を半導体基板の上に3層積層し、夫々のナノシリコン層で検出された赤色、緑色、青色の各電気信号を、半導体基板の表面部に形成されている蓄積ダイオードに読み出すようになっている。

#### 【0009】

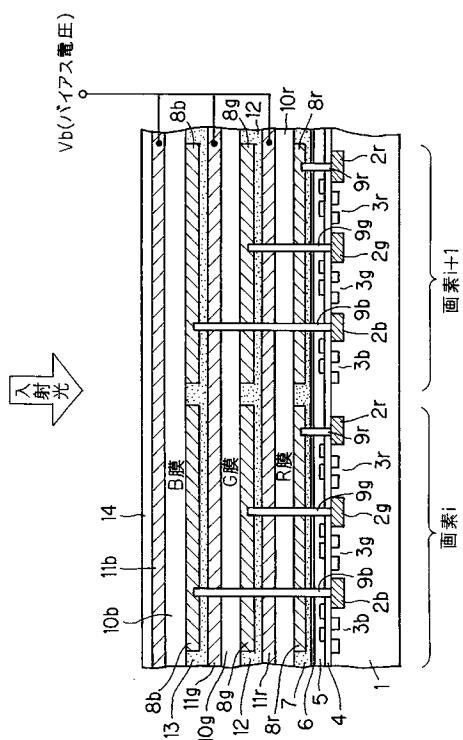

図26は、この従来の光電変換膜積層型固体撮像素子の2画素分の断面模式図である。

図26において、n型シリコン基板に形成されたPウェル層1の表面部には、赤色信号電荷蓄積用の高濃度不純物領域2rと、赤色信号読出用のMOS回路3rと、緑色信号電荷蓄積用の高濃度不純物領域2gと、緑色信号読出用のMOS回路3gと、青色信号電荷蓄積用の高濃度不純物領域2bと、青色信号読出用のMOS回路3bとが形成されている。尚、r, g, bの添え字は、以下も同様であるが、夫々、3原色の赤色(R), 緑色(G), 青色(B)に対応する。

#### 【0010】

各MOS回路3r, 3g, 3bは、半導体基板表面に形成されたソース用、ドレイン用の不純物領域と、ゲート絶縁膜4を介して形成されたゲート電極とから成る。これらのゲート絶縁膜4及びゲート電極の上部には絶縁膜5が積層されて平坦化され、その上に、遮光膜6が積層される。遮光膜6は、多くの場合、金属薄膜で形成されるため、更にその上に絶縁膜7を形成する。

#### 【0011】

上述した色信号電荷蓄積用の高濃度不純物領域2r, 2g, 2bに蓄積された信号電荷量に応じた信号は、MOS回路3r, 3g, 3bによって外部に読み出される。

#### 【0012】

図26に示す絶縁膜7の上に、画素毎に区分けされた画素電極膜8rが形成される。各画素毎の画素電極膜8rは、夫々各画素用の赤色信号電荷蓄積用高濃度不純物領域2rに柱状電極9rによって導通される。この柱状電極9rは、画素電極膜8r及び高濃度不純物領域2r以外とは電気的に絶縁される。

#### 【0013】

10

20

30

40

50

各画素電極膜 8 r の上部には、赤色検出用の光電変換膜 10 r が形成され、更にその上部に透明の共通電極膜 11 r が形成される。これらの光電変換膜 10 r 及び共通電極膜 11 r は、画素毎に区分して設ける必要はなく、半導体基板上の全面に夫々一枚構成で形成される。

#### 【0014】

同様に、共通電極膜 11 r の上部には例えば SiO<sub>2</sub> 等の透明の絶縁膜 12 が形成され、その上部に、各画素毎に区分けされた透明の画素電極膜 8 g が形成される。各画素毎の画素電極膜 8 g と対応する各画素毎の緑色信号電荷蓄積用高濃度不純物領域 2 g とは柱状電極 9 g によって導通される。この柱状電極 9 g は、画素電極膜 8 g 及び高濃度不純物領域 2 g 以外とは電気的に絶縁される。各画素電極膜 8 g の上部には緑色検出用の光電変換膜 10 g が光電変換膜 10 r と同様に一枚構成で形成され、その上部に、透明の共通電極膜 11 g が形成される。

#### 【0015】

共通電極膜 11 g の上部には透明の絶縁膜 13 が形成され、その上部に、各画素毎に区分けされた画素電極膜 8 b が形成される。各画素毎の画素電極膜 8 b は、対応する各画素毎の青色信号電荷蓄積用高濃度不純物領域 2 b に柱状電極 9 b によって導通される。この柱状電極 9 b は、画素電極膜 8 b 及び高濃度不純物領域 2 b 以外とは電気的に絶縁される。画素電極膜 8 b の上部には青色検出用の光電変換膜 10 b が形成され、その上部に、透明の共通電極膜 11 b が形成され、最上層には透明の保護膜 14 が形成される。

#### 【0016】

入射光がこの固体撮像素子に入射すると、青色光、緑色光、赤色光の各入射光量に応じた光電荷が各光電変換膜 10 b, 10 g, 10 r において励起され、共通電極膜 11 b, 11 g, 11 r と画素電極膜 8 b, 8 g, 8 r との間に電圧が印加されることで、夫々の光電荷が高濃度不純物領域 2 b, 2 g, 2 r に流れ、MOS回路 3 b, 3 g, 3 r によって外部に青色信号、緑色信号、赤色信号として読み出される。

#### 【0017】

尚、図 26 に示す光電変換膜積層型固体撮像素子は、信号読出回路を MOS 回路で構成しているが、CCD 型イメージセンサと同様に、電荷結合素子による垂直転送路、水平転送路で信号読出回路を構成する場合もある。

#### 【0018】

【特許文献 1】特開昭 58 103165 号公報

【特許文献 2】特許第 3405099 号公報

【特許文献 3】特開 2002 83946 号公報

【特許文献 4】特表 2003 502120 号公報

【特許文献 5】特表 2003 502847 号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0019】

光電変換膜積層型固体撮像素子を製造する場合、半導体基板側の信号読出回路の製造は、従来の CCD 型や CMOS 型のイメージセンサと同じであり、半導体装置の製造技術をそのまま利用することができる。また、半導体基板の上に積層する光電変換膜 10 r, 10 g, 10 b や光電変換膜を挟む電極膜 11 r, 11 g, 11 b, 8 r, 8 g, 8 b 及び絶縁膜 7, 12, 13 も、印刷技術を用いた成膜方法やスプレー法、真空蒸着法、スパッタ法、CVD 法等を利用することで容易に製造することができる。

#### 【0020】

しかし、光電変換膜積層型固体撮像素子の本体部分を製造しても、本体部分に接続する配線の製造を安価且つ確実に行う必要が生じる。光電変換膜積層型固体撮像素子は、半導体ウェハ上に集積回路技術を用いて各光電変換膜積層型固体撮像素子毎の信号読出回路を形成し、その上に、画素毎の柱状電極 9 r, 9 g, 9 b を信号読出回路に接続しながら各光電変換膜 10 r, 10 g, 10 b, 電極膜 11 r, 11 g, 11 b, 8 r, 8 g, 8 b

, 絶縁膜 7 , 12 , 13 を積層していくことになる。

【0021】

このうち、共通電極膜 11r , 11g , 11b には、画素位置にかかわらず均一なバイアス電位 Vb を印加する必要があるため、バイアス電位を共通電極膜に印加する配線の形状や設ける場所、設ける工程などを工夫する必要がある。

【0022】

本発明の目的は、共通電極膜に均一なバイアス電位を印加する配線を安価且つ確実に製造することができる光電変換膜積層型固体撮像素子及びその製造方法を提供することにある。

【課題を解決するための手段】

【0023】

本発明の光電変換膜積層型固体撮像素子は、共通電極膜と画素対応の画素電極膜とによって挟まれた光電変換膜が絶縁層を介して半導体基板の上に複数層積層される光電変換膜積層型固体撮像素子において、該光電変換膜積層型固体撮像素子の周辺部にて前記共通電極膜を前記周辺部に沿うフラット状の配線により前記半導体基板に形成されている配線用高濃度不純物領域に接続したことを特徴とする。

【0024】

この構成により、共通電極膜に印加するバイアス電位を所定電位に均一にすることが可能となる。

【0025】

本発明の光電変換膜積層型固体撮像素子は、赤色検出用、緑色検出用、青色検出用の3つ光電変換膜を検出波長の短い順に上から順に備え、3つの光電変換膜のうち2つの光電変換膜に設ける前記共通電極膜を共用したことを特徴とする。

【0026】

この構成により、3原色の色信号を検出することが可能になると共に共通電極膜数を低減でき、これにより共通電極膜への配線数も減らすことが可能となる。

【0027】

本発明の光電変換膜積層型固体撮像素子は、赤色検出用、緑色検出用、青色検出用、エメラルド色検出用の4つの光電変換膜を検出波長の短い順に上から備え、4つの光電変換膜のうちの隣接する2つの光電変換膜に設ける前記共通電極膜を共用したことを特徴とする。

【0028】

この構成により、人間の視感度に応じた色信号を検出することが可能になると共に共通電極膜数を低減でき、これにより共通電極膜への配線数も減らすことが可能となる。

【0029】

本発明の光電変換膜積層型固体撮像素子は、前記光電変換膜の材料として無機材料を用いたことを特徴とし、あるいは、前記光電変換膜の材料として有機材料を用いたことを特徴とする。

【0030】

本発明の光電変換膜積層型固体撮像素子の構造は、光電変換膜の材料に依存せず、どのような材料でも使用可能である。

【0031】

本発明の光電変換膜積層型固体撮像素子の製造方法は、上記の光電変換膜積層型固体撮像素子において、前記画素電極膜及び前記光電変換膜を積層し前記共通電極膜を積層する前または前記共通電極膜を積層した後に、前記周辺部において前記フラット状の配線を蒸着して前記共通電極膜を前記配線用高濃度不純物領域に接続することを特徴とする。

【0032】

この構成により、フラット状の配線を蒸着によって形成するため、製造が容易で安価に形成可能となる。

【0033】

10

20

30

40

50

本発明の光電変換膜積層型固体撮像素子の製造方法は、前記フラット状の配線の蒸着によって前記共通電極膜上または前記光電変換膜上に前記配線材料が盛り上がって形成された場合には、該盛り上がり部分をポリッシングして平坦化することを特徴とする。

#### 【0034】

この構成により、不要部分をポリッシングで除去するため、製造が容易且つ安価となる。

#### 【0035】

本発明の光電変換膜積層型固体撮像素子の製造方法は、前記共通電極膜が複数存在し各共通電極膜に接続される前記フラット状の配線を複数重ねて設ける場合には各フラット状の配線間に絶縁材を形成して電気的に分離することを特徴とする。

10

#### 【0036】

この構成により、個々の共通電極膜のバイアス電位を夫々制御可能となる。尚、複数の共通電極膜を同一バイアス電位にする場合には、各フラット状配線を同一の配線用高濃度不純物領域に接続する構成でもよく、各フラット状配線を電気的に絶縁する必要はない。

#### 【発明の効果】

#### 【0037】

本発明によれば、光電変換膜積層型固体撮像素子の共通電極膜に均一なバイアス電位を印加する配線を容易且つ確実に製造することが可能となる。

20

#### 【発明を実施するための最良の形態】

#### 【0038】

以下、本発明の一実施形態について、図面を参照して説明する。

#### 【0039】

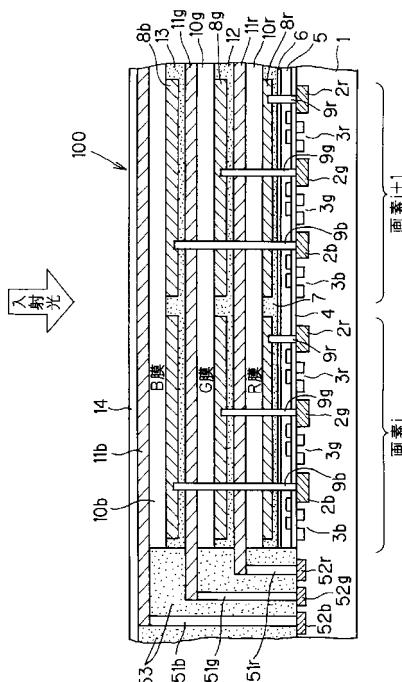

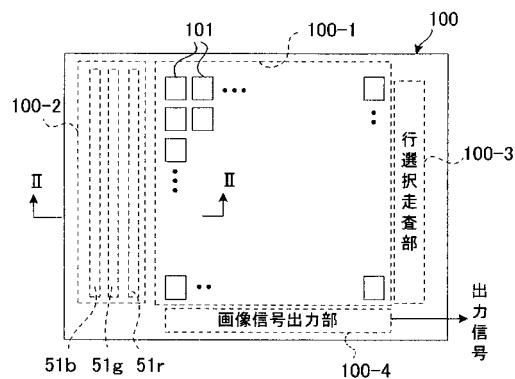

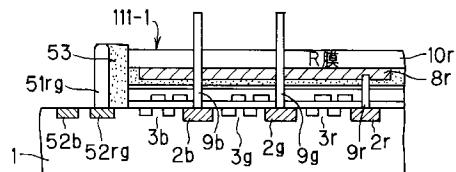

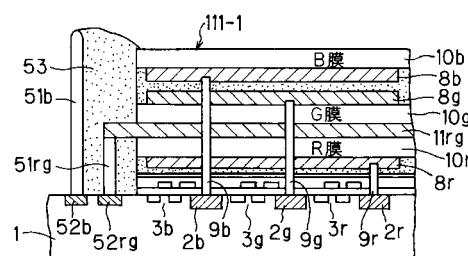

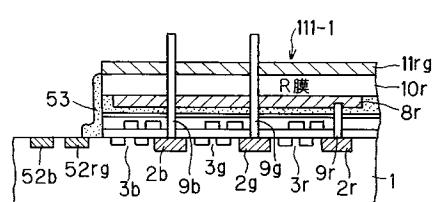

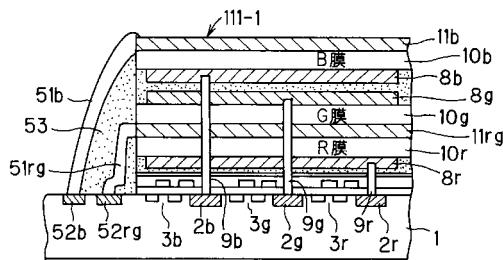

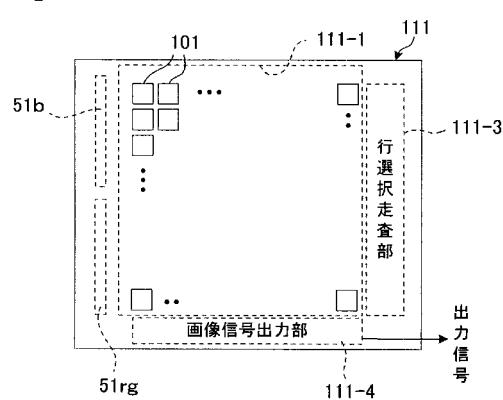

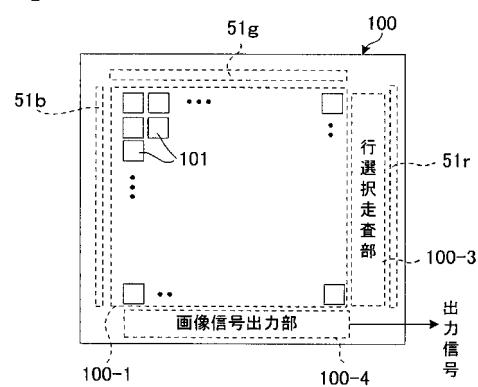

図1は、本発明の一実施形態に係る光電変換膜積層型固体撮像素子の平面模式図であり、図2は、図1のII-II線断面模式図である。光電変換膜積層型固体撮像素子100は、本体部100-1と、本体部100-1の左側に沿って設けられた共通電極膜配線部100-2と、本体部100-1の右側に沿って設けられた行選択走査部100-3と、本体部100-1の下辺側に設けられた画像信号出力部100-4とを備える。行選択走査部100-3と画像信号出力部100-4とは、CMOS型イメージセンサに設けられるものと同じである。

30

#### 【0040】

本体部100-1には多数の画素101がアレイ状に配列形成されており、その積層構造は、図26に示す構造と同一であるため、同一部材には同一符号を付してその説明は省略する。

#### 【0041】

共通電極膜配線部100-2には、本体部100-1の3枚の共通電極膜11r, 11g, 11bに夫々接続される配線51r, 51g, 51bが設けられる。各配線51r, 51g, 51bは、本体部100-1と同一幅に設けられるため、フラット状(布状)となっている。そして、半導体基板の表面部には、各配線51r, 51g, 51bとオーミックコンタクトされる配線用高濃度不純物領域52r, 52g, 52bが設けられ、各配線51r, 51g, 51bの周りはSiO<sub>2</sub>等の絶縁物53で埋められる。

40

#### 【0042】

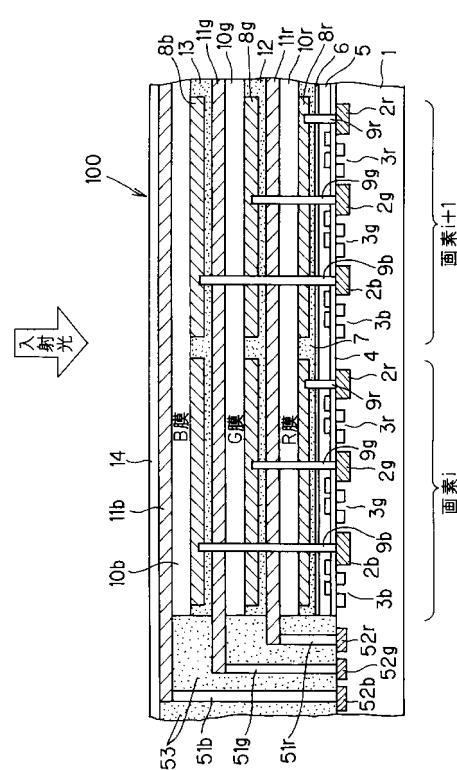

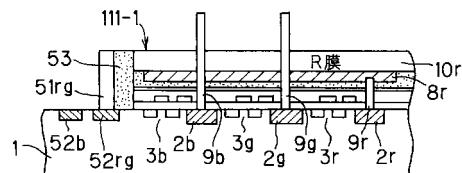

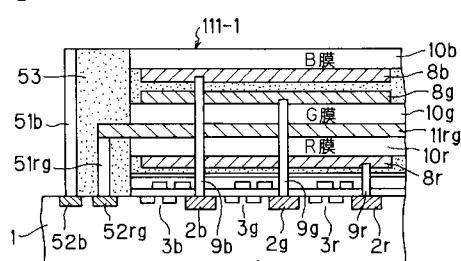

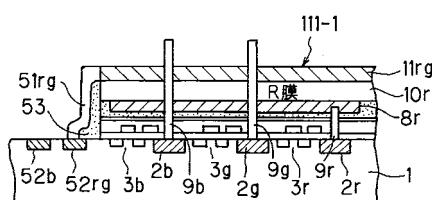

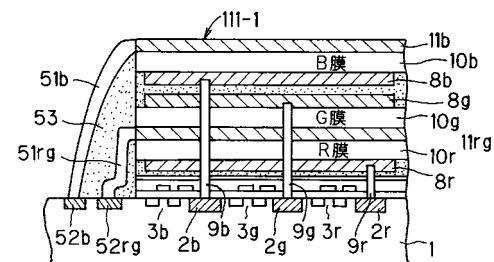

図3は、本発明の別実施形態に係る光電変換膜積層型固体撮像素子110の断面模式図である。本実施形態の構成は、図2に示す構成と殆ど同じであり、同一部材には同一符号を付してその説明は省略する。

#### 【0043】

本実施形態では、青色光電変換膜10bの下側、この例では、緑色用の共通電極膜11gの上に、イエロ(Ye)色のカラーフィルタ15を積層し、緑色光電変換膜10gの下側、この例では、赤色用の共通電極膜11rの上に、赤色(R)カラーフィルタ16を積層し、図2に示す遮光膜6の代わりにIR(赤外線)カットフィルタを積層し、最上層14の代わりに、あるいは最上層14と図示しないレンズとの間に、紫外線カットフィルタ

50

を積層した点が異なる。

【0044】

入射光中に含まれる紫外線が青色光電変換膜10bに入射すると、紫外線量に応じた光電荷が青色光電変換膜10bで発生し、青色光の光量に応じた光電荷が増量してしまう虞がある。そこで、本実施形態では、紫外線カットフィルタを設ける。

【0045】

イエロカラーフィルタ15は、3原色のうち、緑色(G)と赤色(R)を透過し、青色(B)の透過を遮断するカラーフィルタである。入射光のうち青色光の殆どは青色光電変換膜10bによって吸収され光電変換されるが、緑色に近い青色部分が透過してしまう虞がある。また、製造上、青色光電変換膜10bの膜厚を十分にとれない場合にも青色光の一部が透過してしまう虞がある。

【0046】

青色光電変換膜10bを透過した青色光は、緑色光電変換膜10gで光電変換される虞があるため、色分離を劣化させる原因となる。そこで、本実施形態では、青色光電変換膜10bの下層にイエロカラーフィルタ15を挿入することで青色光の緑色光電変換膜10gへの入射を阻止し、青色と緑色との色分離を良好にしている。イエロカラーフィルタ15に入射する青色光の光量は少ないため、カラーフィルタを使うことによる光利用効率の低下は小さい。

【0047】

赤色カラーフィルタ16は、赤色光を透過し、緑色光の透過を遮断する。この赤色カラーフィルタ16を設ける理由はイエロカラーフィルタ15を設ける理由と同じであり、緑色光電変換膜10gを透過する虞のある赤に近い緑色を遮断して緑色と赤色の色分離を良好にするためである。

【0048】

IRカットフィルタ17は、半導体基板中に赤外線が入射しない様にするために設ける。シリコン半導体に形成した信号読出回路には部分的にPN接合が形成され、ここに赤外線が入射すると光電荷が発生し、これがノイズ成分となってしまう。これを阻止するために、IRカットフィルタ17を設ける。

【0049】

図2の遮光膜6であっても、赤外線の半導体基板側への入射を阻止できるが、遮光膜6は金属膜を使用することが多く、遮光膜6で反射した赤外線が再び赤色光電変換膜10rに入射して赤色の光電荷量を増量させてしまう虞がある。そこで、本実施形態では、IRカットフィルタ17を用い、IRカットフィルタ17で赤外線を吸収してしまう構成にする。尚、IRカットフィルタを設ける場所は、この実施形態の様に半導体基板表面直近でなくても、光路中のどこでもよい。

【0050】

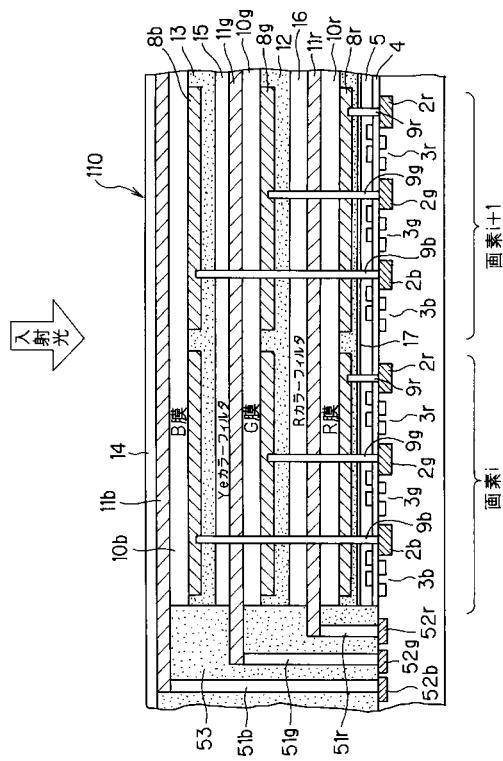

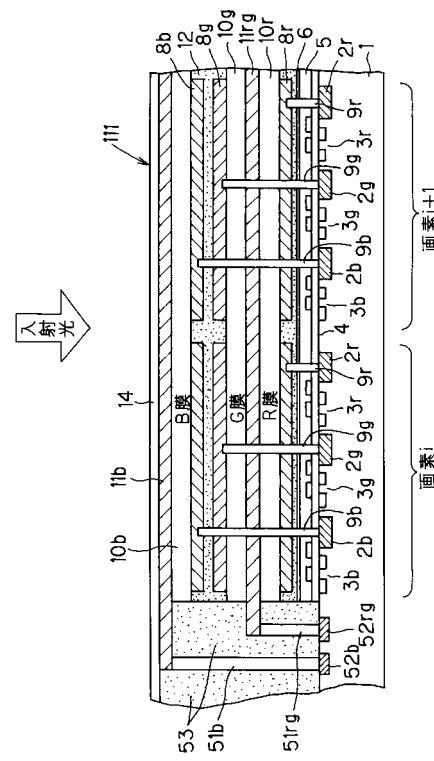

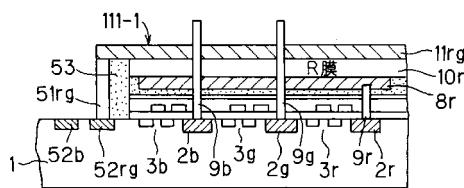

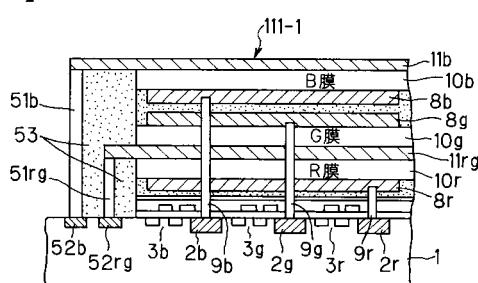

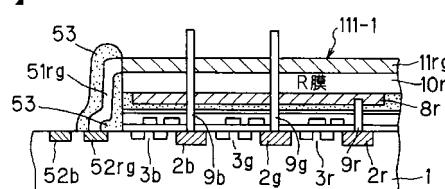

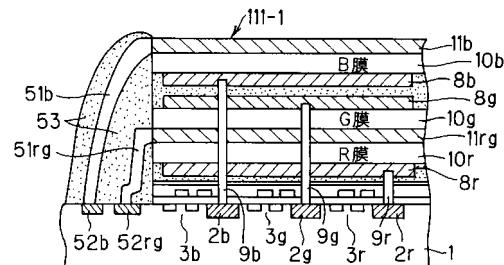

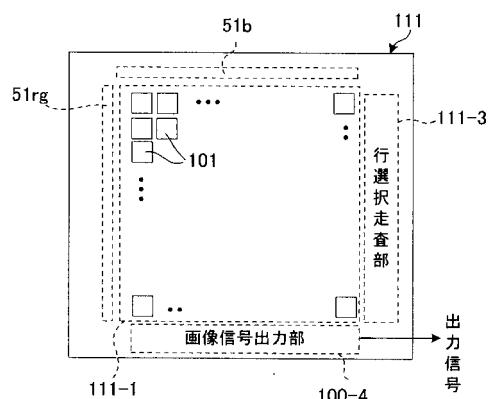

図4は、本発明の更に別実施形態に係る光電変換膜積層型固体撮像素子111の断面模式図である。基本構成は図2、図3の光電変換膜積層型固体撮像素子100、110と同じであり、同一部材に同一符号を付けてその説明は省略する。

【0051】

本実施形態は、赤色光電変換膜10rに設ける共通電極膜と、緑色光電変換膜10gに設ける共通電極膜と共に用いて共通電極膜11rgとし、更に、共通電極膜11rgを共用した関係で、緑色光電変換膜10gの上側に緑色用の画素電極膜8gを設けた点が異なる。

【0052】

これにより、共通電極膜が全体として2枚で済み、図4の左側に示す様に、共通電極膜11rに接続する配線52bと、共通電極膜11rgに接続する配線52rgの2つの配線でバイアス電位を印加できるという利点がある。

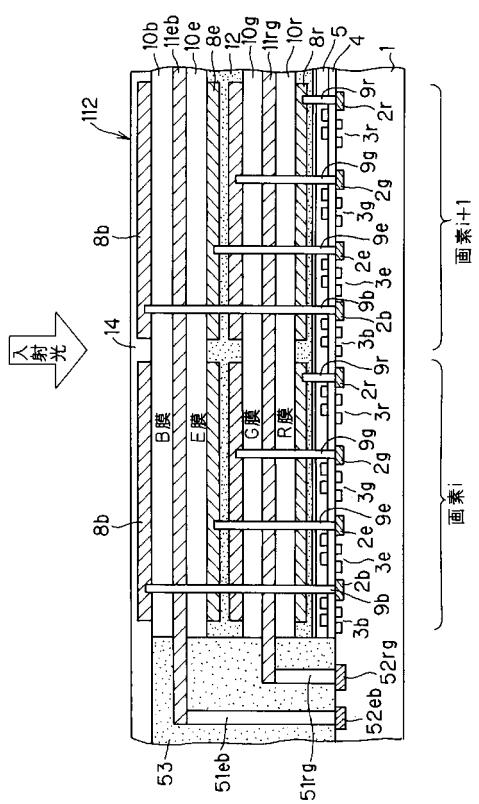

【0053】

図5は、本発明の更に別実施形態に係る光電変換膜積層型固体撮像素子112の断面模

10

20

30

40

50

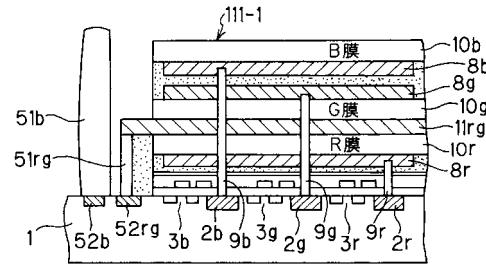

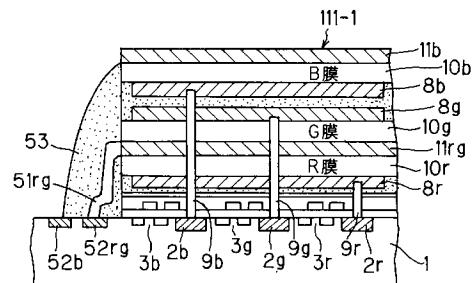

式図である。図2, 図3, 図4に示した実施形態は、赤色(R), 緑色(G), 青色(B)の3原色を検出する光電変換膜積層型固体撮像素子の例であるが、本実施形態の光電変換膜積層型固体撮像素子112では、4色を検出できる構成にしている。

#### 【0054】

即ち、本実施形態では、図4の構成に対し、緑色(G)と青色(B)の中間色(E:エメラルド色)を検出する光電変換膜10eを積層している点が異なる。また、エメラルド色光電変換膜10eと青色光電変換膜10bとで共通電極膜11ebを共用している関係で、4色を検出する構成にも関わらず、2枚の共通電極膜で済み、図5の左側に示す様に、共通電極膜11ebに接続する配線51ebと、共通電極膜rgに接続する配線51rgの2つで済むという利点がある。

#### 【0055】

本実施形態では、エメラルド色光電変換膜10eに設ける画素画素電極膜8eに、柱状電極9eを立設し、この柱状電極9eを接続する色信号電荷を蓄積する高濃度不純物領域2eと、信号読出用のMOS回路3eとを設けている。その他の構成部材は図4の光電変換膜積層型固体撮像素子111と同じであるので、同一部材には同一符号を付してその説明を省略する。

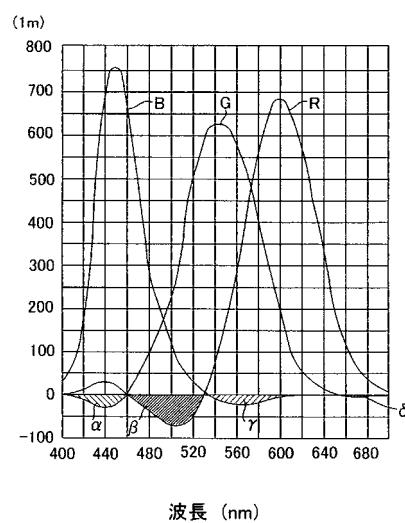

#### 【0056】

例えば、波長480~520nmのエメラルド(E)色を検出する利点は、人間の視感度に応じて赤色を補正するためである。人間の視感度は、図6に、として示す様に、緑色(G), 赤色(R), 青色(B)で負の感度を持っている。このため、固体撮像素子でR, G, Bの正の感度のみ検出して色再現を行っても、人間の見た画像を再現することはできない。そこで、負感度の一番大きいすなわち赤の負感度を光電変換膜10rによって検出し、光電変換膜10rで検出した赤の感度から、この負感度分を差し引くことで、人間の赤色に対する感度を再現することができる。

#### 【0057】

尚、上述した各実施形態において、透明な電極膜の材料としては、酸化錫(SnO<sub>2</sub>)、酸化チタン(TiO<sub>2</sub>)、酸化インジウム(Indium oxide)、酸化インジウム-錫(ITO)薄膜を用いるが、これに限るものではない。例えば、高濃度不純物を注入したポリシリコンを柱状電極や電極膜材料としてもよい。電極膜の形成方法としては、レーザアブレーション法やスパッタ法など、従来の成膜技術を使用して製造する。

#### 【0058】

また、光電変換膜10r, 10g, 10b, 10eの積層方法は特に限定するものではなく、スパッタ法やレーザアブレーション法、印刷技術、スプレー法等で積層する。材料としては、無機材料でも有機材料でよく、無機材料の場合は、例えば、GaAlAs, Si, InGaAlP, GaPAs, InAlPを用いることができる。また、有機材料の場合には、例えば、ZnPc(亜鉛フタロシアニン)/Alq3(キノリノールアルミ錯体), R6G/PMPs(rhodamine 6G(R6G)-doped polymethylphenylsilane), C6/PHPs(coumarin 6(C6)-doped poly(m-hexoxyphenyl)phenylsilane)等を用いることができる。

#### 【0059】

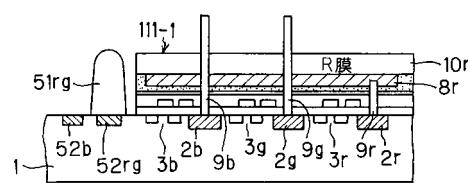

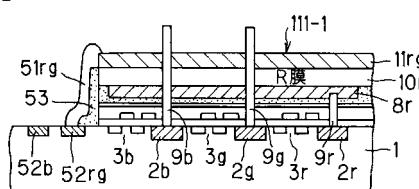

次に、図7~図14を使い、図4に示す光電変換膜積層型固体撮像素子111における共通電極膜の配線51rg及び配線51bの製造方法を説明する。尚、図2, 図3, 図5の光電変換膜積層型固体撮像素子100, 110, 112における共通電極膜の配線の製造方法も同様である。

#### 【0060】

図7に示す様に、光電変換膜積層型固体撮像素子111の画素部分が形成された本体部分111-1の赤色光電変換膜10rまでの積層を行う。この積層方法は特に限定されるものではないが、本体部分以外の、高濃度不純物領域52b, 52rgが形成された領域をマスクして行うのが良い。

#### 【0061】

10

20

30

40

50

赤色光電変換膜 10rまでの積層が終了した後は、高濃度不純物領域 52rg の表面をエッチングにより綺麗にし、その上に、図 7 に示す様に、マスク穴を通して金属たとえばアルミニウムによる配線 51rg を蒸着によって高く形成する。そして、図 8 に示す様に、配線 51rg をエッチングによって所定厚に削り、その後、低温 CVD 等によって、配線 51rg と本体部分 111 1 の側面との間の空間を SiO<sub>2</sub> 等の絶縁材 53 で埋める。

#### 【0062】

次に、図 9 に示す様に、配線 51rg 及び絶縁材 53 の頭頂部分をポリッシングしてこれらの高さを赤色光電変換膜 10r の高さに合わせ、図 10 に示す様に、共通電極膜 11rg を積層する。これにより、高濃度不純物領域 52rg と共に電極膜 11rg とがフラット状の配線 51rg によって電気的に接続される。

10

#### 【0063】

次に、本体部分 111 1 の青色光電変換膜 10b までの積層を行い、また、高濃度不純物領域 52b の表面をエッチングにより綺麗にする。そして、図 11 に示す様に、高濃度不純物領域 52b の上にマスク穴を通してアルミニウムによる配線 51b を蒸着して高く形成する。次に、図 12 に示す様に、配線 51b をエッチングによって所定厚に削った後、低温 CVD 等によって、配線 51b と本体部分 111 1 の側面との間の空間を SiO<sub>2</sub> 等の絶縁材 53 で埋める。

#### 【0064】

次に、図 13 に示す様に、配線 51b 及び絶縁材 53 の頭頂部分をポリッシングしてこれらの高さを青色光電変換膜 10b の高さに合わせ、図 14 に示す様に、共通電極膜 11b を積層する。これにより、高濃度不純物領域 52b と共に電極膜 11b とがフラット状の配線 51b によって電気的に接続される。その後、配線 51b の左側の空間を絶縁材で埋める。

20

#### 【0065】

この様に、フラット状の配線 51b, 51rg によって共通電極膜 11r, 11rg を半導体基板の配線用高濃度不純物領域 52b, 52rg に接続したため、この光電変換膜積層型固体撮像素子 111 を検査する場合に、この検査を半導体ウェハ上で行うことが可能となる。

#### 【0066】

尚、本実施形態では、配線 51b と配線 51rg とを電気的に分離して共通電極膜 11r, 11rg のバイアス電位を別々に制御する構成としたが、2枚の共通電極膜 11r, 11rg に同一バイアス電位を印加する場合には、配線用高濃度不純物領域を1つとし、これに配線 51b, 51rg を共通に接続する構成としてもよい。これは、他の光電変換膜積層型固体撮像素子 100, 110, 112 でも同様である。

30

#### 【0067】

図 15～図 22 は、図 4 に示す光電変換膜積層型固体撮像素子 111 における共通電極膜の配線 51rg 及び配線 51b の製造方法の別実施形態を説明する図である。

#### 【0068】

本実施形態では、本体部分 111 1 の共通電極膜 11rg までの積層が終了した後、図 15 に示す様に、高濃度不純物領域 52rg の端部分から赤色光電変換膜 10r の上縁まで達する例えば SiO<sub>2</sub> でなる絶縁材 53 を低温 CVD 等で形成する。次に、高濃度不純物領域 52rg 表面をエッチングして綺麗にした後、図 16 に示す様に、金属材例えはアルミニウムを蒸着し、高濃度不純物領域 52rg と共に電極膜 11rg を電気的に接続する配線 51rg を形成する。

40

#### 【0069】

次に、図 17 に示す様に、配線 51rg の頭頂部をポリッシングして共通電極膜 11rg の高さに合わせる。そして、図 18 に示す様に、絶縁材 53 を低温 CVD 等で形成して配線 51rg を覆う。このとき、本体部分 111 1 をマスクで覆い、絶縁材 53 が共通電極膜 11rg の上にかからないようにする。

50

## 【0070】

次に、本体部分 111 1 の共通電極膜 11bまでの積層を行った後、図19に示す様に、高濃度不純物領域 52b の端から青色光電変換膜 10b の上端まで達する絶縁材 53 を形成し、この絶縁材 53 の上にアルミニウムを蒸着することで、図20に示す様に、高濃度不純物領域 52b と共に電極膜 11b とを電気的に接続する配線 51b を形成する。

そして、図21に示す様に、配線 51b の頭頂部をポリッシングし、図22に示す様に、配線 51b を絶縁材 53 で覆う。

## 【0071】

上述した実施形態では、2つの配線 51b, 51rg を本体部分 111 1 の左側に並列に並べて設けたが、例えば、図23に示す様に、配線 51b と配線 51rg の幅を夫々半分にし、本体部分 111 1 の左側に一列に設けることでもよい。或いは、図24に示す様に、配線 51b, 51rg の一方を本体部分 111 1 の上辺に沿って設け、他方を本体部分 111 1 の左辺に沿って設けても良い。

## 【0072】

以上は、共通電極膜を2枚設けた光電変換膜積層型固体撮像素子 111, 112 の例であるが、共通電極膜を3枚設けた光電変換膜積層型固体撮像素子 100, 110 の場合には、共通電極膜に接続する配線 51r, 51g, 51b の3つが必要となる。この場合には、図23と図24の構成を組み合わせて3つの配線 51r, 51g, 51b を配置しても良い。

## 【0073】

また、図25に示す様に、各配線 51r, 51g, 51b を本体部分 100 1 の右辺、上辺、左辺に沿って設けることも可能である。しかし、右辺に配線 51r を設ける場合、この例では右辺に設けた行選択走査部 100 3 を本体部分 100 1 との間に挟む位置に設ける必要がある。行選択走査部 100 3 は、各画素 101 直下に設けた各画素用信号読出回路と多数のメタル配線で接続されるため、このメタル配線とフラット状配線 51r とが交差しない様にするためである。

## 【0074】

尚、図1, 図23～図25の配線 51r, 51g, 51b, 51rg の配置例は、信号読出回路がMOSトランジスタ回路の場合であり、信号読出回路がCCD型の場合には転送電極に転送パルスを印加する端子があれば良く行選択走査部 100 3 は存在しないため、各配線 51r, 51g, 51b, 51rg の配置位置の制約はなくなる。

## 【0075】

また、上述した実施形態では、例えば、配線 51b, 51g, 51r を夫々本体部の1辺にのみ設けたが、夫々の配線 51b, 51g, 51r を本体部の2辺、3辺あるいは4辺全てに設け、各配線にバイアス電位を印加する構成にしてもよい。これにより、共通電極膜のバイアス電位が画素の位置にかかわらず更に均一となり、各画素の駆動条件を同一にすることが可能となる。

## 【産業上の利用可能性】

## 【0076】

本発明による共通電極膜への配線構造によれば、製造が容易且つ確実となり、品質の高い光電変換膜積層型固体撮像素子を安価に製造可能となり、従来のCCD型イメージセンサやCMOS型イメージセンサに代わる固体撮像素子を安価に提供できる。

## 【図面の簡単な説明】

## 【0077】

【図1】本発明の一実施形態に係る光電変換膜積層型固体撮像素子の平面模式図である。

【図2】図1に示す光電変換膜積層型固体撮像素子のII-II線断面模式図である。

【図3】本発明の別実施形態に係る3層構造の光電変換膜積層型固体撮像素子の2画素分の断面模式図である。

【図4】本発明の更に別実施形態に係る3層構造の光電変換膜積層型固体撮像素子の2画素分の断面模式図である。

10

20

30

40

50

【図5】本発明の更に別実施形態に係る4層構造の光電変換膜積層型固体撮像素子の2画素分の断面模式図である。

【図6】人間の視感度を示すグラフである。

【図7】図4に示す光電変換膜積層型固体撮像素子の製造手順の説明図である。

【図8】図4に示す光電変換膜積層型固体撮像素子の製造手順のうち図7の次の手順説明図である。

【図9】図4に示す光電変換膜積層型固体撮像素子の製造手順のうち図8の次の手順説明図である。

【図10】図4に示す光電変換膜積層型固体撮像素子の製造手順のうち図9の次の手順説明図である。

【図11】図4に示す光電変換膜積層型固体撮像素子の製造手順のうち図10の次の手順説明図である。

【図12】図4に示す光電変換膜積層型固体撮像素子の製造手順のうち図11の次の手順説明図である。

【図13】図4に示す光電変換膜積層型固体撮像素子の製造手順のうち図12の次の手順説明図である。

【図14】図4に示す光電変換膜積層型固体撮像素子の製造手順のうち図13の次の手順説明図である。

【図15】図4に示す光電変換膜積層型固体撮像素子の別実施形態に係る製造手順の説明図である。

【図16】図4に示す光電変換膜積層型固体撮像素子の製造手順のうち図15の次の手順説明図である。

【図17】図4に示す光電変換膜積層型固体撮像素子の製造手順のうち図16の次の手順説明図である。

【図18】図4に示す光電変換膜積層型固体撮像素子の製造手順のうち図17の次の手順説明図である。

【図19】図4に示す光電変換膜積層型固体撮像素子の製造手順のうち図18の次の手順説明図である。

【図20】図4に示す光電変換膜積層型固体撮像素子の製造手順のうち図19の次の手順説明図である。

【図21】図4に示す光電変換膜積層型固体撮像素子の製造手順のうち図20の次の手順説明図である。

【図22】図4に示す光電変換膜積層型固体撮像素子の製造手順のうち図21の次の手順説明図である。

【図23】図4に示す光電変換膜積層型固体撮像素子の変形例の平面模式図である。

【図24】図4に示す光電変換膜積層型固体撮像素子の更に別変形例の平面模式図である。

【図25】図1に示す光電変換膜積層型固体撮像素子の変形例の平面模式図である。

【図26】従来の3層構造の光電変換膜積層型固体撮像素子の2画素分の断面模式図である。

#### 【符号の説明】

##### 【0078】

1 P ウエル層(半導体基板)

2 r , 2 g , 2 b , 2 e 高濃度不純物領域

3 r , 3 g , 3 b , 3 e MOS回路

7 , 12 , 13 絶縁膜

8 r , 8 g , 8 b , 8 e 画素電極膜

11 r , 11 g , 11 b , 11 r g , 11 e b 共通電極膜

10 r , 10 g , 10 b , 10 e 光電変換膜

51 r , 51 g , 51 b , 51 r g 共通電極膜への配線

10

20

30

40

50

5 2 r , 5 2 g , 5 2 b , 5 2 r g , 5 2 e b 高濃度不純物領域

5 3 絶縁材

100, 110, 111, 112 光電変換膜積層型固体撮像素子

1 0 0 1 , 1 1 1 1 本体部分

1 0 0    3 , 1 1 1    3 行選択走査部

1 0 0 4 , 1 1 1 4 画像信号出力部

【 図 1 】

【 四 2 】

【図3】

【 図 4 】

【図5】

【 図 6 】

【 図 7 】

【図 8】

【図 9】

【図 10】

【図 11】

【図 12】

【図 13】

【図 16】

【図 14】

【図 15】

【図 17】

【図 18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図25】

【図24】

【図26】

## フロントページの続き

(72)発明者 井上 知己

神奈川県南足柄市中沼210番地 富士写真フィルム株式会社内

Fターム(参考) 4M118 AA01 AA02 AA10 AB01 BA19 CA15 CA27 CB01 CB14 CB20

DA18 FA05 FA06 GC09 GC11

5C024 CY47 DX01 GX01

5C065 CC01 DD17 EE06