RÉPUBLIQUE FRANÇAISE

INSTITUT NATIONAL

DE LA PROPRIÉTÉ INDUSTRIELLE

PARIS

(11) N° de publication :

**2 481 461**

(A n'utiliser que pour les

commandes de reproduction).

A1

**DEMANDE

DE BREVET D'INVENTION**

(21)

**N° 80 09413**

(54) Dispositif programmable, pour tester les durées d'un signal électrique, notamment d'impulsions.

(51) Classification internationale (Int. Cl. 3). G 01 R 29/02; H 03 K 19/00.

(22) Date de dépôt..... 25 avril 1980.

(33) (32) (31) Priorité revendiquée :

(41) Date de la mise à la disposition du

public de la demande ..... B.O.P.I. — « Listes » n° 44 du 30-10-1981.

(71) Déposant : RTC LA RADIOTECHNIQUE-COMPELEC, société anonyme, résidant en France.

(72) Invention de : Alfred Kientz et Jacques Le Gars.

(73) Titulaire : *Idem* (71)

(74) Mandataire : Jean Caron, société civile SPID,

209, rue de l'Université, 75007 Paris.

"DISPOSITIF PROGRAMMABLE POUR TESTER LES DUREES

D'UN SIGNAL ELECTRIQUE, NOTAMMENT D'IMPULSIONS"

La présente invention concerne un dispositif programmable pour tester les durées d'un signal électrique, notamment d'impulsions.

Le but du dispositif selon l'invention est de reconnaître 5 une suite d'impulsions dans un signal électrique complexe, et de vérifier que les durées des impulsions ou/et des intervalles entre les impulsions sont conformes à des spécifications.

Le dispositif est utilisé, par exemple, lors de la 10 fabrication de cartes de circuits logiques, dans un appareil de test automatique desdites cartes, appareil piloté par un miniordinateur.

Un dispositif bien connu utilise une ligne à retard à prises. Cette ligne et ses prises doivent être construites 15 spécialement pour chaque circuit à tester. Une approche plus moderne consiste à enregistrer dans un registre à décalage la valeur du signal à des instants d'horloge successifs. On dispose d'un enregistrement de différentes valeurs successives du signal que l'on peut analyser par des moyens logiques connus. C'est d'ailleurs l'équivalent numérique 20 d'une ligne à retard, qui aurait autant de prises régulièrement espacées qu'il y a de positions dans le registre.

Le principal inconvénient de ce dispositif est sa lourdeur, car un découpage fin du temps exige beaucoup de positions 25 de mémorisation c'est-à-dire des registres à décalage à très grande capacité.

Une autre approche consiste à faire démarrer au début 30 de l'intervalle de temps à tester deux compteurs préchargés avec la durée maximale admissible de la durée à tester pour l'un, avec la valeur minimale pour l'autre, et à analyser à l'aide moyens logiques connus l'ordre d'apparition des

trois événements suivants :

- fin de comptage de chacun des deux compteurs et

- fin de l'intervalle de temps à tester.

Un dispositif utilisant cette approche est connu par le

5 brevet français n° 2 286 386 qui apporte une variante en ne comportant qu'un seul compteur à la place des deux compteurs ci-dessus, compteur dont on détecte deux comptes successifs prédéterminés.

Selon que l'on s'intéresse à la durée des impulsions,

10 ou à l'intervalle entre deux impulsions, ou à l'intervalle entre deux débuts d'impulsions, ou entre deux fins d'impulsions, il faut programmer un circuit de définition d'intervalle pour qu'il détecte respectivement : soit le premier front montant, puis ensuite le premier front descendant,

15 soit l'inverse, soit uniquement les fronts montants, soit uniquement les fronts descendants.

Cette méthode présente l'inconvénient qu'après le test d'un seul intervalle de temps, il faut : lire le résultat, remettre à zéro le système, recharger les compteurs et les

20 détecteurs de comptes prédéterminés et reprogrammer le circuit de définition d'intervalles, ce qui interdit de relancer la mesure suivante dans des délais très brefs.

Le but de la présente invention est de remédier aux inconvénients ci-dessus en apportant la possibilité d'analyser finement des séquences de plusieurs impulsions successives tout en utilisant une capacité de mémorisation réduite.

L'idée de base de l'invention est qu'au lieu de détecter la fin de l'intervalle de temps à tester, ce qui nécessite un circuit de définition d'intervalle, il suffit de vérifier que pour la valeur minimale de durée permise, le signal a bien la valeur souhaitée, et que lorsqu'on arrive à sa valeur maximale de durée permise un changement s'est bien produit. Ainsi, on ne sait pas à quel moment entre les deux s'est terminé l'intervalle de temps à tester, mais ceci importe peu puisqu'il ne s'agit pas de mesurer sa durée mais seulement de savoir si elle est comprise entre deux limites.

On s'affranchit aussi de la sujexion qui découle de l'idée qu'à la fin dudit intervalle de temps on doit réinitialiser tous les éléments du système pour effectuer une nouvelle mesure. Dès lors, il suffira d'utiliser une pluralité de compteurs pour tester une pluralité d'intervalles de temps successifs.

Selon l'invention, un dispositif programmable pour tester les durées d'un signal électrique, et en particulier d'impulsions, est notamment remarquable en ce qu'il comporte 10 une mémoire de valeurs numériques de programmation d'intervalles de temps, des moyens fournissant une pluralité d'impulsions séparées par une pluralité d'intervalles de temps différents définis à l'avance, et des moyens de mémorisation de plusieurs états successifs du signal à tester, la mémoire précitée étant reliée auxdits moyens fourni 15 nssant des impulsions et en ce qu'au moins une borne de sortie fournissant lesdites impulsions est connectée à au moins une borne d'entrée qui déclenche les moyens de mémorisation de l'état du signal aux instants desdites impulsions.

L'avantage de ce dispositif est qu'il permet avec des moyens légers de tester plusieurs impulsions même si elles se suivent de près, et cela avec une bonne définition des temps. En effet, la solution à registre à décalage classique exigerait  $n$  bascules pour tester un signal pendant  $n$  unités de temps, alors qu'avec le dispositif selon l'invention on peut tester une valeur au bout de  $2^n$  unités de temps avec  $n$  bascules seulement.

Avantageusement le dispositif selon l'invention est également remarquable en ce qu'il comporte un circuit de comparaison de mots numériques et une mémoire de mot de référence, les bornes de sortie des susdits moyens de mémorisation d'états sur lesquelles on trouve mémorisés les états successifs du signal à tester étant reliées aux bornes d'entrée de mot à comparer du circuit de comparaison de mots dont les autres bornes d'entrées de mots à comparer sont reliées à la mémoire de mot de référence.

Grâce à ce circuit de comparaison on peut déterminer numériquement si le signal sous test est conforme au signal souhaité ou par quoi il en diffère.

5 Selon un mode préféré de réalisation, le dispositif est remarquable en ce que les susdits moyens fournissant des impulsions sont constitués par une pluralité de compteurs montés en cascade, chacun correspondant à un desdits intervalles de temps définis, et dont le premier est déclenché en synchronisme avec le début de l'intervalle de temps pendant lequel on teste le signal électrique.

Le montage en cascade offre l'avantage de pouvoir utiliser des compteurs de moindre capacité que celle nécessaire dans le cas d'un montage en parallèle.

15 Dans une variante du mode de réalisation ci-dessus, le dispositif est remarquable en ce qu'une borne d'entrée de commande de comptage, et une borne de sortie sur laquelle apparaît une impulsion de fin de comptage de chaque compteur sont reliées à une matrice de points de connexions programmable.

20 Grâce à cette particularité, on peut prévoir des compteurs de différentes capacités et programmer l'ordre dans lequel ils sont utilisés en fonction de la longueur respective des différents intervalles de temps.

25 Avantageusement les compteurs possèdent des bornes d'entrées de préchargement qui sont reliées à la borne de sortie de la mémoire de valeurs numériques de programmation d'intervalles.

Ainsi, il est possible de précharger chacun des compteurs avec une valeur qui correspond précisément à chacun 30 des susdits intervalles de temps définis à l'avance.

Avantageusement, les moyens de mémorisation d'états sont constitués par une pluralité de registres, chacun correspondant à un des susdits compteurs, la borne d'entrée de commande d'échantillonnage de chacun des registres étant 35 reliée à une borne de sortie sur laquelle apparaît une impulsion de fin de comptage du compteur qui lui correspond, et le signal à tester étant amené à l'entrée de données de chacun

des registres.

Ce montage permet de réaliser très simplement les moyens de mémorisation d'états.

Dans une variante, les moyens de mémorisation d'états sont

5 constitués par un registre à décalage et un circuit logique, une borne de sortie sur laquelle apparaît une impulsion de fin de comptage de chacun des susdits compteurs étant reliée à une des bornes d'entrée du circuit logique qui est du type dont une sortie fournit une impulsion lorsqu'il s'en présente une sur une de ses entrées et ladite borne de sortie du circuit logique étant reliée à la borne d'entrée d'horloge du registre à décalage, tandis que le signal à tester est amené à la borne d'entrée de données dudit registre à décalage.

10

15 Il est intéressant d'utiliser cette variante si on ne dispose pas de registres multiples dont les entrées de commande d'échantillonnage sont séparées pour chaque bit.

Avantageusement, l'horloge des compteurs est à fréquence programmable, ou bien même elle est à plusieurs sorties

20 fournissant simultanément plusieurs fréquences, une matrice de points de connexions programmables permettant d'attribuer à chaque compteur une fréquence différente.

Cette solution permet d'avoir plusieurs gammes de mesure ou même plusieurs échelles de temps à l'intérieur d'une même

25 séquence d'impulsions. On peut donc obtenir des intervalles de temps très différents sans pour autant prévoir des compteurs de grande capacité.

La description qui va suivre en regard des dessins annexés, décrivant des exemples non limitatifs, fera bien comprendre comment l'invention peut être réalisée.

30

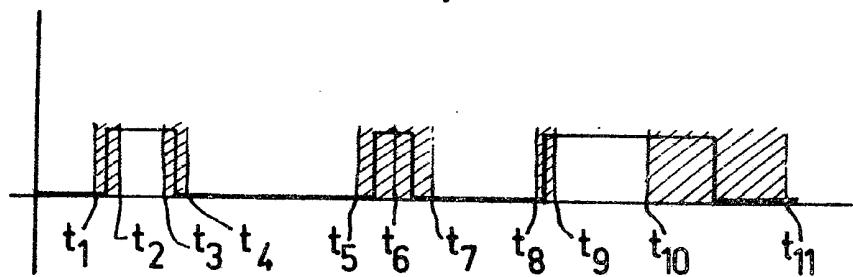

La figure 1 représente un exemple de séquence d'impulsions à tester.

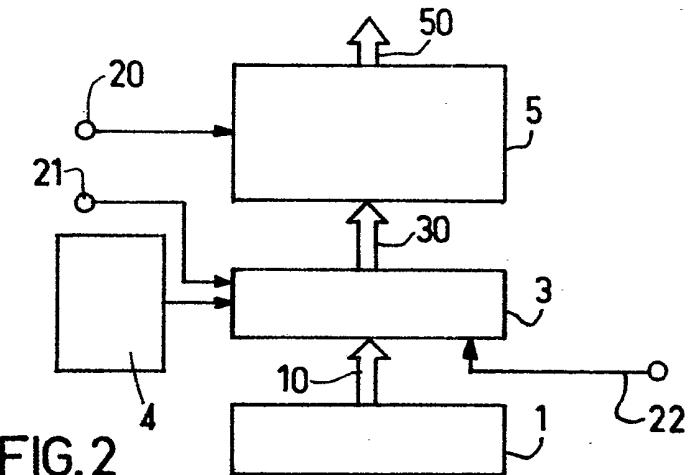

La figure 2 est un schéma synoptique simplifié du dispositif selon l'invention.

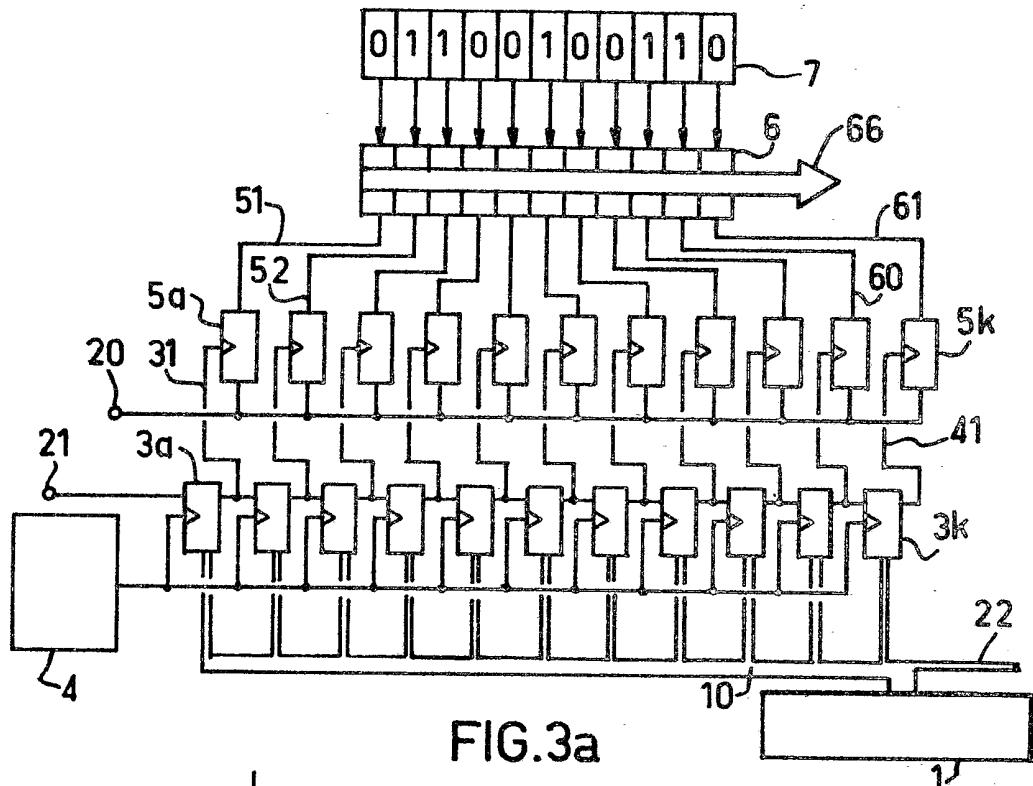

35 La figure 3 montre des schémas plus détaillés d'un exemple de réalisation de l'invention.

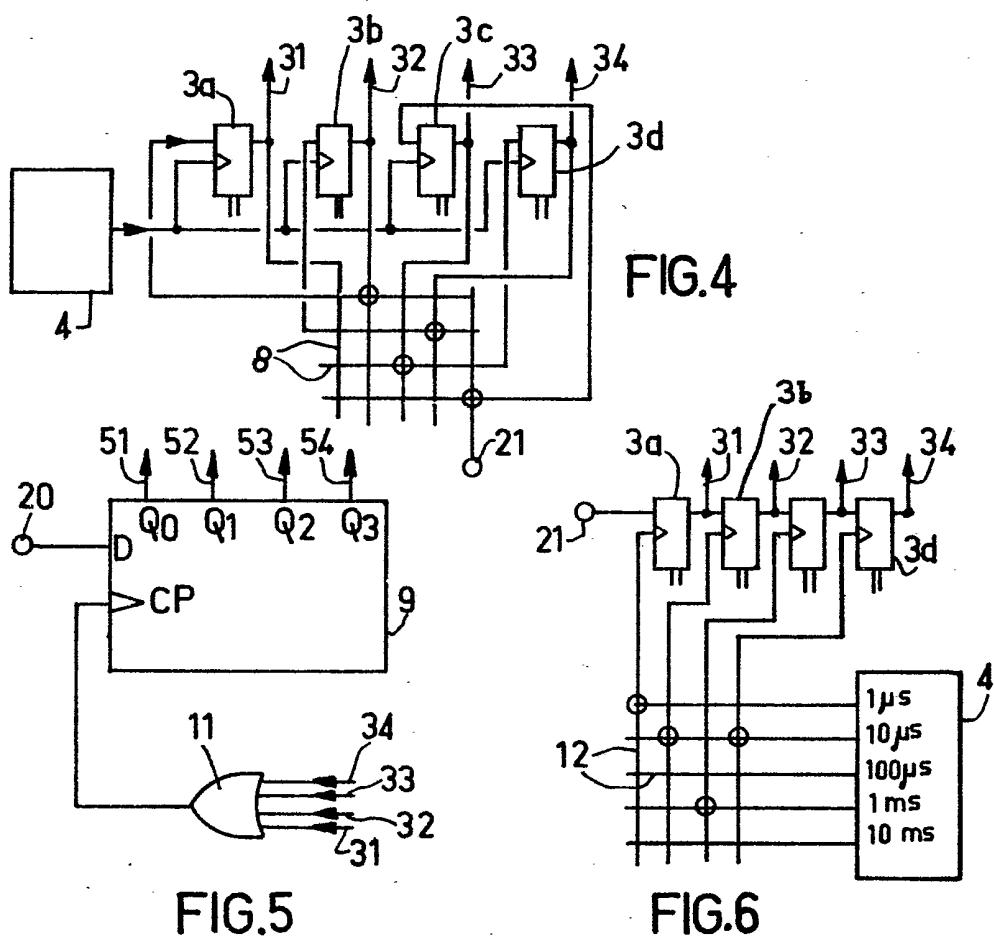

La figure 4 représente une variante de réalisation du système de compteurs en cascade.

La figure 5 représente une variante de réalisation desdits moyens de mémorisation d'états.

5 La figure 6 représente une variante de réalisation de l'ensemble horloge-compteurs.

Soit à tester une séquence d'impulsions telle que représentée par la figure 1 : on veut vérifier que les transitions bas-haut ou haut-bas se produisent dans le bon sens et 10 à l'intérieur des régions hachurées. Il suffit de vérifier qu'aux temps successifs  $t_1$  à  $t_{11}$  on a bien, respectivement les états bas-haut-haut-bas-bas-haut-bas-bas-haut-haut-bas. On remarquera que les tolérances ne sont pas également serrées et que, par exemple, on laisse beaucoup moins de marge 15 entre  $t_8$  et  $t_9$  qu'entre  $t_{10}$  et  $t_{11}$ . Également on a confondu deux temps en un seul, en  $t_6$ . Ceci illustre la souplesse offerte par le dispositif.

La figure 2 montre une mémoire de valeurs numériques de programmation (1), des moyens (3,4) fournissant des impulsions séparées par des intervalles de temps différents définis à l'avance, et des moyens de mémorisation de plusieurs états successifs du signal à tester (5). Avant le début de 20 la séquence de test, la mémoire 1 a envoyé par le bus 10 auxdits moyens fournissant des impulsions, les valeurs pré-déterminées des intervalles successifs, soit en série, soit 25 en parallèle, cependant qu'un ordre de préchargement leur est envoyé par le conducteur 22. Lesdits moyens sont ainsi programmés pour fournir des impulsions séparées par lesdits intervalles différents et prédéterminés. Ils commenceront à 30 fournir des impulsions lorsque la décision de commencer le test leur aura été notifiée par un signal sur la borne 21. L'horloge 4 fournit l'unité de temps à utiliser dans la définition des intervalles.

Une sortie fournissant les impulsions des moyens 3 35 envoie par la liaison 30 à une entrée des moyens de mémorisation d'états 5 les tops définissant les instants où lesdits moyens doivent mémoriser l'état du signal à tester,

lequel est amené sur la borne 20.

Bien entendu, dans le cas de l'exemple montré par la figure 1, les tops en question se produisent aux instants  $t_1, t_2, \dots, t_{11}$ .

5 A la fin de la durée de test, on pourra lire sur le bus 50 les états successifs du signal sous test à chacun des instants prédéterminés.

10 Sur la figure 3a sont montrées, sous la même forme que sur la figure 2, l'horloge 4 et la mémoire 1. Un mode de réalisation des fonctions 3 et 5 y est représenté, ainsi que le circuit de comparaison de mots 6,7.

15 Les moyens 3 fournissant des impulsions sont constitués par une pluralité de compteurs (3a à 3k), montés en cascade, chacun correspondant à un des intervalles de temps définis. Les compteurs pourraient aussi démarrer en même temps au lieu d'être déclenchés en cascade, mais il faudrait des compteurs de plus grande capacité, puisqu'ils devraient tous compter depuis le début de la mesure, au lieu de commencer seulement au début de l'intervalle auquel ils correspondent.

20 Il est représenté onze compteurs, pour s'accorder avec l'exemple de la figure 1, mais il est bien évident que ce n'est qu'un exemple, et que dans le cas général, le nombre de compteurs sera égal au nombre d'états successifs à tester.

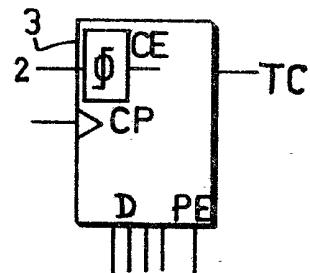

25 La figure 3c montre plus en détail les entrées et sorties des compteurs. Les entrées d'horloge CP (clock pulse) sont réunies à l'horloge 4. Les entrées de préchargement D sont réunies, par le bus 10 de la figure 3a, à la mémoire 1, qui fournit aux entrées D les valeurs numériques de programmation d'intervalles, et l'entrée de commande de préchargement PE (parallel enable) est réunie au bus 22 de la figure 3a, qui fournit aux entrées PE les ordres de préchargement provenant d'un processeur non représenté. L'entrée 2 sur laquelle arrive le signal donnant l'ordre de compter doit être munie d'un dispositif de maintien, car le dit ordre de compter est donné par un signal non permanent.

Cet ordre de compter maintenu est appliqué à la borne CE (count enable). Enfin, l'impulsion de fin de comptage sort par la sortie TC (terminal count). On doit prévoir un système qui arrête définitivement le compteur après l'apparition de l'impulsion de fin de comptage, sinon on risquerait, 5 après un décompte de toute la capacité du compteur, de trouver une nouvelle impulsion qui ferait mémo-riser à tort le signal. Ce système non représenté pour la clarté du schéma, est pour le spécialiste, facile à définir.

10 La figure 3a montre que chaque sortie de fin de comptage est réunie à l'entrée de commande du comptage du compteur suivant, ce qui provoque un fonctionnement en cascade. Le premier compteur reçoit l'ordre de démarrer au début de la période de test, par la borne 21 reliée à un processeur

15 non représenté.

Lesdits moyens de mémorisation d'états sont constitués par une pluralité de registres, référencés 5a à 5k , cha-cun correspondant à un des compteurs 3a à 3k .

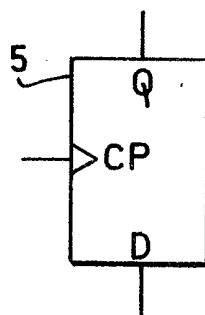

La figure 3b montre plus en détail les entrées et sor-ties de chacun de ces registres. L'entrée d'échantillonnage CP (clock pulse) reçoit l'ordre d'enregistrer à l'instant l'état du signal à tester présent sur l'entrée D de données, et ledit état, mémorisé, est disponible de façon permanente sur la sortie Q.

25 L'entrée de données D peut d'ailleurs être multiple, et on peut enregistrer alors, par exemple, la valeur, con-vertie en numérique, d'un signal analogique, ce qui offre des possibilités nouvelles d'analyse de signaux analogiques complexes. La sortie Q sera alors multiple aussi.

30 La figure 3a montre que chaque entrée de commande d'é-chantillonnage est reliée à la sortie sur laquelle apparaît une impulsion de fin de comptage du compteur qui lui corres-pond et que le signal à tester, présent sur la borne 20 , est amené à l'entrée de données de chacun des registres.

35 Les sorties sur lesquelles on trouve mémorisés les états du signal à tester sont reliées aux entrées de mot à comparer d'un circuit de comparaison 6 , (l'ensemble de

signaux logiques sur lesdites sorties constitue un mot), et les autres entrées de mot à comparer du circuit 6 sont reliées aux sorties correspondantes de la mémoire 7 sur lesquelles est présent un mot de référence. Le circuit 6 fournit par la liaison 66 une information sur la concordance de deux mots.

Les codes logiques 0 et 1 indiqué dans la mémoire 7 correspondent aux états qui doivent être relevés avec l'exemple de la figure 1.

10 Dans le cas d'un signal analogique converti en numérique, cas dans lequel les sorties des registres 5 sont multiples, chaque portion du comparateur 6 et de la mémoire 7 constitue respectivement un comparateur de mot et un mot, au lieu d'un comparateur de bit et un bit.

15 Les figures 4 et 6 représentent des dispositions correspondant à seulement quatre compteurs, afin d'être plus claires.

20 La figure 4 montre un perfectionnement au montage en cascade des compteurs. L'entrée de commande de comptage de chaque compteur est réunie à une des lignes horizontales de la matrice de points de connexion 8. La sortie sur laquelle apparaît l'impulsion de fin de comptage de chaque compteur est réunie à une des lignes verticales de la matrice 8. L'entrée 21 de commande de comptage du premier compteur est reliée aussi à une ligne verticale de la matrice. Les points de connexion sont programmables. La matrice 8 peut être réalisée aisément par le spécialiste au moyen de multiplexeurs ou de démultiplexeurs. Dans l'exemple montré ici limité à quatre compteurs, ceux-ci sont utilisés dans l'ordre 3c, 3d, 3b, 3a.

25 Ceci offre l'avantage que l'on peut gagner sur la capacité totale des compteurs dans le cas répandu où les temps successifs à vérifier sont très différents. Imaginons que l'on veuille engendrer des impulsions séparées par les intervalles suivants : 80  $\mu$ s, 3  $\mu$ s, 25  $\mu$ s, 7  $\mu$ s. Si tous les compteurs étaient identiques, ils devraient compter au moins jusqu'à 80, en supposant la fréquence de l'horloge à 1 MHz.

Si par contre, on a prévu par exemple deux compteurs de capacité 128 et deux compteurs de capacité 16 , on aura réalisé une économie, tout en ayant encore beaucoup de possibilités. Mais on ne sait pas à priori dans quel ordre se 5 présenteront les intervalles longs et courts ; c'est le rôle de la matrice 8 de câbler les entrées de déclenchement des différents compteurs en fonction de cela. Si les compteurs 3b et 3c ont une capacité de 128 , et les compteurs 3a et 3d une capacité de 16 , l'ordre choisi 10 dans l'exemple représenté par la figure 4 permettra de tester la séquence ci-dessus (80  $\mu$ s, 3  $\mu$ s, 25  $\mu$ s, 7  $\mu$ s).

La figure 5 montre un registre à décalage 9 dont l'entrée de données D est reliée par une borne 20 au signal à tester, un circuit logique 11 du type dont une sortie 15 fournit une impulsion lorsqu'il s'en présente sur une de ses entrées, ici un simple circuit OU, dont chacune des entrées 31 à 34 est reliée à la sortie sur laquelle apparaît une impulsion de fin de comptage de chaque compteur, et dont la sortie est reliée à l'entrée d'horloge CP du 20 registre à décalage 9 .

L'horloge 4 est avantageusement programmable, afin de pouvoir changer l'échelle des temps.

Une telle horloge programmable est un dispositif classique. On peut, ainsi qu'il est montré par la figure 6, utiliser une horloge (4) à plusieurs sorties, chacune d'elles 25 fournissant une fréquence différente des autres, chaque borne de sortie étant réunie à une ligne horizontale d'une matrice de points de connexions (12) programmable, les lignes verticales de cette matrice étant réunies chacune à l'entrée d'horloge de l'un des compteurs 3a à 3d . On peut ainsi faire compter les compteurs à des cadences différentes et augmenter les possibilités de mesure d'intervalles très 30 différents. Selon la figure 6, par exemple, si chacun des compteurs est capable de compter 128 impulsions d'horloge 35 on peut tester des intervalles successifs au plus égaux à 128  $\mu$ s - 1,28 ms - 128 ms - 1,28 ms respectivement. Pour avoir un compte plus fin, on peut si besoin est utiliser

deux compteurs pour jouer le rôle d'un seul. Par exemple

ici les compteurs 3a et 3b ensemble peuvent compter pen-

dant 128  $\mu$ s + 1,28 ms, soit 1,408 ms, et ceci à la micro-

seconde près. On fait seulement une mémorisation pour rien,

5 au moment de la fin de comptage du compteur 3a .

On peut aussi associer les moyens montrés par les fi-

gures 4 et 6, ayant ainsi une richesse de combinaisons

surprenante.

Il est inutile de prévoir un raccordement matriciel

10 entre les moyens de mémorisation d'états 5 et le compara-

teur de mots 6 , ou entre les sorties de fin de comptage

des compteurs et lesdits moyens de mémorisation puisque

si l'ordre d'apparition des impulsions est modifié par chan-

gement de l'ordre d'utilisation des compteurs, il suffit

15 d'en tenir compte lors de la constitution du mot de référence

contenu dans la mémoire 7 . D'ailleurs, si on utilise des

moyens de mémorisation d'états du type représenté en figure

5 , l'ordre d'utilisation des compteurs est indifférent.

A propos de tous ces dispositifs, on n'a pas décrit ni

20 représenté les bornes et connexions de remise à zéro qui

sont bien sûr nécessaires mais dont l'emploi est bien connu

des spécialistes.

- REVENDICATIONS -

1.- Dispositif programmable pour tester les durées d'au moins un signal électrique, notamment d'impulsions, caractérisé en ce qu'il comporte une mémoire (1) de valeurs numériques de programmation d'intervalles de temps, 5 des moyens (3,4) fournissant une pluralité d'impulsions séparées par une pluralité d'intervalles de temps différents définis à l'avance, et des moyens (5) de mémorisation de plusieurs états successifs du signal à tester, en ce que la mémoire précitée est reliée auxdits moyens four- 10 nissant des impulsions et en ce qu'au moins une borne de sortie fournissant lesdites impulsions, est connectée à au moins une borne d'entrée qui déclenche les moyens de mémorisation de l'état du signal aux instants desdites impulsions.

15 2.- Dispositif selon la revendication 1, caractérisé en ce qu'il comporte également un circuit de comparaison (6) de mots numériques et une mémoire de mot de référence (7), les bornes de sortie des susdits moyens de mémorisation d'états (5) sur lesquelles on trouve mémorisés les 20 états successifs du signal à tester étant reliées aux bornes d'entrées de mot à comparer du circuit de comparaison de mots (6) dont les autres bornes d'entrées de mot à comparer sont reliées à la mémoire de mot de référence (7).

3.- Dispositif selon l'une des revendications 1 ou 2, 25 caractérisé en ce que lesdits moyens fournissant des impulsions sont constitués par une pluralité de compteurs montés en cascade (3a-3k), chacun correspondant à l'un desdits intervalles de temps définis.

4.- Dispositif selon la revendication 3, caractérisé 30 en ce qu'une borne d'entrée de commande de comptage et une borne de sortie sur laquelle apparaît une impulsion de fin de comptage, de chaque compteur, sont reliées à une matrice de points de connexions programmable (8).

5.- Dispositif selon l'une des revendications 3 ou 4, 35 caractérisé en ce que les compteurs possèdent des bornes

d'entrée de préchargement qui sont reliées à la borne dé sortie de la mémoire (1) de valeurs numériques de programmation d'intervalles.

6.- Dispositif selon l'une quelconque des revendications 3 à 5, caractérisé en ce que lesdits moyens de mémorisation d'états sont constitués par une pluralité de registres (5a, 5k), chacun correspondant à un des susdits compteurs en ce que la borne d'entrée de commande d'échantillonnage de chacun des registres est reliée à une borne de sortie sur laquelle apparaît une impulsion de fin de comptage du compteur qui lui correspond, et en ce qu'au moins un conducteur portant un signal à tester (20) est relié à au moins une borne d'entrée de données de chacun des registres.

15 7.- Dispositif selon l'une quelconque des revendications 3 à 5, caractérisé en ce que lesdits moyens de mémorisation/sont constitués par un registre (9) à décalage et un circuit logique (11), en ce qu'une borne de sortie sur laquelle apparaît une impulsion de fin de comptage de chaque compteur est reliée à une des bornes d'entrées du dit circuit logique qui est du type dont une sortie fournit une impulsion lorsqu'il s'en présente une sur une de ses entrées, ladite borne de sortie du circuit logique étant reliée à la borne d'entrée d'horloge du registre à décalage (9) et en ce qu'un conducteur portant le signal à tester (20) est relié à la borne d'entrée de données du registre à décalage.

30 8.- Dispositif selon l'une quelconque des revendications 1 à 7, caractérisé en ce qu'il comporte une horloge (4) dont la borne de sortie est reliée aux bornes d'entrée d'horloge des compteurs et dont la fréquence est programmable.

35 9.- Dispositif selon l'une quelconque des revendications 1 à 7, caractérisé en ce que qu'il comporte une horloge (4) pouvant fournir simultanément plusieurs fréquences sur plusieurs sorties, dont les bornes sont réunies à une

matrice de points de connexion (12) programmable, et en ce que la borne d'entrée d'horloge de chaque compteur est réunie à la même matrice de points de connexion.

1/2

FIG. 1

FIG. 3a

FIG. 3b

FIG. 3c

2/2