(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4864810号

(P4864810)

(45) 発行日 平成24年2月1日(2012.2.1)

(24) 登録日 平成23年11月18日(2011.11.18)

|              |            |

|--------------|------------|

| (51) Int.Cl. | F 1        |

| H05K 3/36    | (2006.01)  |

| H01L 25/00   | (2006.01)  |

| H05K 3/28    | (2006.01)  |

| H05K 1/18    | (2006.01)  |

|              | HO5K 3/36  |

|              | HO1L 25/00 |

|              | HO5K 3/28  |

|              | HO5K 1/18  |

請求項の数 2 (全 9 頁)

(21) 出願番号 特願2007-133947 (P2007-133947)

(22) 出願日 平成19年5月21日 (2007.5.21)

(65) 公開番号 特開2008-288489 (P2008-288489A)

(43) 公開日 平成20年11月27日 (2008.11.27)

審査請求日 平成22年2月8日 (2010.2.8)

(73) 特許権者 000190688

新光電気工業株式会社

長野県長野市小島田町80番地

(74) 代理人 100070150

弁理士 伊東 忠彦

(72) 発明者 小林 敏男

長野県長野市小島田町80番地 新光電気

工業株式会社内

審査官 吉澤 秀明

(56) 参考文献 特開平11-55066 (JP, A)

特開2004-363566 (JP, A)

最終頁に続く

(54) 【発明の名称】チップ内蔵基板の製造方法

## (57) 【特許請求の範囲】

## 【請求項1】

複数のチップ部品が搭載されると共に隣接する前記チップ部品の間に接続用パッドが形成された第1の基板に、複数の前記チップ部品をワイヤボンディング接続により搭載する工程と、

第2の基板に基板表面から突出する電極を設ける工程と、

前記接続用パッドの配列と対応して形成された突出部と、前記チップ部品の搭載領域に対応して形成されたキャビティとを有する金型を前記第1の基板に装着し、前記突出部を前記接続用パッド表面に当接させると共に該キャビティに第1の樹脂を充填して前記チップ部品及びワイヤを樹脂封止することにより、前記第1の基板上に封止樹脂部を形成する工程と、

前記接続用パッドと前記電極とを対向させてはんだ接合し、樹脂封止された前記チップ部品が内蔵されるよう前記第1の基板と前記第2の基板を接合する工程と、

前記第1の基板と前記第2の基板との離間部分に第2の樹脂を充填する工程とを有し、前記封止樹脂部を形成する工程では、前記金型の前記突出部により前記封止樹脂部に溝部を形成し、該溝部の底部に前記接続用パッドを露出させることを特徴とするチップ内蔵基板の製造方法。

## 【請求項2】

前記電極は、銅よりなる金属コアにはんだ膜が被膜された構成であることを特徴とする請求項1記載のチップ内蔵基板の製造方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明はチップ内蔵基板の製造方法に係り、特に一対の配線基板間にチップが内蔵されたチップ内蔵基板を製造するチップ内蔵基板の製造方法に関する。

**【背景技術】****【0002】**

現在、半導体チップなどの半導体装置を用いた電子機器の高性能化が進められており、基板へ半導体チップを実装する場合の高密度化や、また半導体チップを搭載した基板の小型化、省スペース化などが求められている。

10

**【0003】**

このため、半導体チップが埋め込まれた基板、いわゆるチップ内蔵型の配線基板（以下、チップ内蔵基板という）が提案されており、半導体チップを基板に内蔵するための様々な構造が提案されている。

**【0004】**

このチップ内蔵基板の一例として、例えば特許文献1に開示されたものがある。この特許文献1に開示されたチップ内蔵基板は、第1の実装基板と第2の実装基板との間にスペーサとして機能するバンプが設けられており、このバンプにより離間された一対の基板の間にチップが実装された構成とされている。また、一対の実装基板の間に封止樹脂が配設されることにより、チップを保護する構成とされている。

20

**【0005】**

また、特許文献1に開示されたチップ内蔵基板の製造方法としては、先ず第1実装基板上に半導体チップをフリップチップ実装し、続いてスペーサとして機能するバンプを第1実装基板にはんだ付けする。次に、第1実装基板上に、少なくともバンプの頂点近傍部分が露出し、かつチップを封止するように封止樹脂を形成する。

**【0006】**

この封止樹脂が形成されると、その上部に第2の実装基板を前記バンプと電気的に接続するように積層させる。この上記の各処理を実施することにより、特許文献1に開示されたチップ内蔵基板は製造されていた。

**【特許文献1】特開2003-347722号公報**

30

**【発明の開示】****【発明が解決しようとする課題】****【0007】**

上記の特許文献1に開示されたチップ内蔵基板は、チップを第1の実装基板にフリップチップ実装する方法を用いていた。しかしながら、比較的端子数が少ないチップの場合には、ワイヤボンディング法を用いた方がフリップチップ実装法に比べて安価で組み立て性が良好となる場合がある。

**【0008】**

一方、特許文献1に開示されたチップ内蔵基板の製造方法では、チップ実装後にバンプを第1の実装基板に配設するが、そのときにはんだ付け処理を行う。この際、特許文献1には特に記載がないが、通常のはんだ付け処理では第1の実装基板のバンプのはんだ付け位置にはんだフラックスを塗布し、濡れ性の向上をはかることによりはんだ接合の信頼性の向上を図ることが行われる。

40

**【0009】**

このはんだフラックスははんだ付け後に残渣として残った場合、腐食の原因となるため洗浄処理が行われる。この洗浄処理は、フラックス除去を確実に行うため、洗浄液は比較的速い流速ではんだ接合位置に噴射される。

**【0010】**

しかしながら、前記のようにチップ内蔵基板は小型化及び省スペース化が図られており、バンプの配設位置の近傍にチップが搭載される場合がある。この際、チップが第1の実

50

装基板にワイヤボンディング法を用いて接続されると、洗浄液がワイヤにも噴射されるおそれがあり、この場合にはワイヤが破損したり、またワイヤが変形して隣接するワイヤ間で短絡が発生したりするという問題点があった。

#### 【0011】

本発明は上記の点に鑑みてなされたものであり、チップ部品を第1の基板にワイヤ接続しても高い信頼性を維持できるチップ内蔵基板の製造方法を提供することを目的とする。

#### 【課題を解決するための手段】

#### 【0012】

上記の課題は、本発明の第1の観点からは、

複数のチップ部品が搭載されると共に隣接する前記チップ部品の間に接続用パッドが形成された第1の基板に、複数の前記チップ部品をワイヤボンディング接続により搭載する工程と、

第2の基板に基板表面から突出する電極を設ける工程と、

前記接続用パッドの配列と対応して形成された突出部と、前記チップ部品の搭載領域に対応して形成されたキャビティとを有する金型を前記第1の基板に装着し、前記突出部を前記接続用パッド表面に当接させると共に該キャビティに第1の樹脂を充填して前記チップ部品及びワイヤを樹脂封止することにより、前記第1の基板上に封止樹脂部を形成する工程と、

前記接続用パッドと前記電極とを対向させてはんだ接合し、樹脂封止された前記チップ部品が内蔵されるよう前記第1の基板と前記第2の基板を接合する工程と、

前記第1の基板と前記第2の基板との離間部分に第2の樹脂を充填する工程とを有し、前記封止樹脂部を形成する工程では、前記金型の前記突出部により前記封止樹脂部に溝部を形成し、該溝部の底部に前記接続用パッドを露出させることを特徴とするチップ内蔵基板の製造方法により解決することができる。

#### 【0013】

また、上記発明において、前記電極を銅よりなる金属コアにはんだ膜が被膜された構成としてもよい。

#### 【発明の効果】

#### 【0015】

本発明によれば、接続用パッドと電極とをはんだ接合する前に、第1の基板にワイヤ接続されたチップ部品及びワイヤは金型を用いて第1の樹脂に封止されるため、接続用パッドと電極とのはんだ接合後にフラックス洗浄を行っても、フラックス洗浄時にワイヤの破損や短絡が発生することはなく、よってチップ内蔵基板の信頼性を高めることができる。

#### 【発明を実施するための最良の形態】

#### 【0016】

次に、本発明を実施するための最良の形態について図面と共に説明する。

#### 【0017】

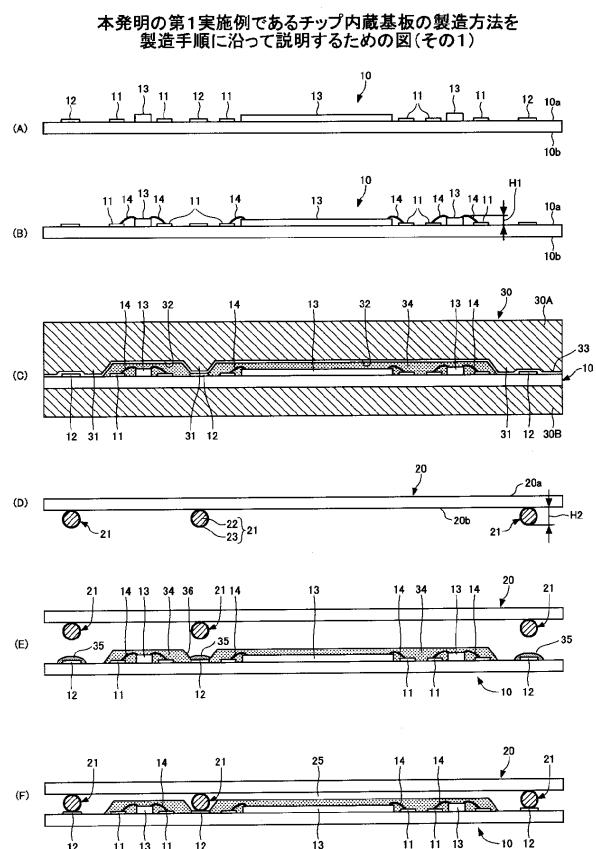

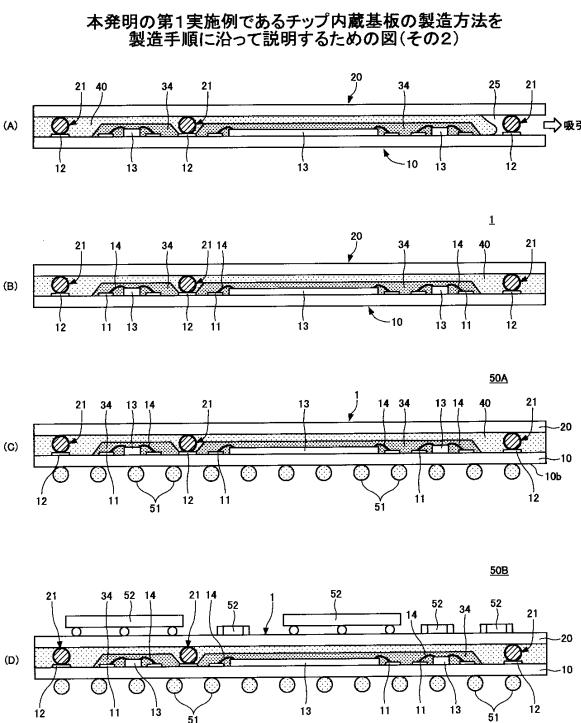

図1及び図2は、本発明の一実施例であるチップ内蔵基板の製造方法を製造手順に沿って説明するための図である。特に、図2(B)は本実施例の製造方法により製造されたチップ内蔵基板1を示しているが、説明の便宜上、チップ内蔵基板の製造方法の説明に先立ち、この図2(B)を用いてチップ内蔵基板1の構成について説明する。

#### 【0018】

チップ内蔵基板1は、大略すると第1の基板10、第2の基板20、チップ状の電子部品13(以下、チップ部品という)、第1の封止樹脂34、及び第2の封止樹脂40等により構成されている。第1の基板10は配線パターンが形成された配線基板であり、その上面10aにチップ部品13が複数個搭載されている。本実施例では、チップ部品13は、第1の基板10に形成されたワイヤ接続用パッド11にA uワイヤ等のワイヤボンディングに使用されるワイヤ14を用いて接続されている。

#### 【0019】

また、第2の基板20も配線パターンが形成された配線基板であり、この配線パターン

10

20

40

50

と接続した電極 21 を有している。この電極 21 は、第 1 の基板 10 に形成されたバンプ接続用パッド 12 とはんだ接合される。この電極 21 は第 1 の基板 10 と第 2 の基板 20 を電気的に接続すると共に、第 1 の基板 10 と第 2 の基板 20 を所定の距離だけ離間させるスペーサとして機能する。また、電極 21 の高さは、各ワイヤ 14 のワイヤループの高さよりも若干大きく設定されている。

#### 【 0 0 2 0 】

第 1 の封止樹脂 34 は、第 1 の基板 10 上にチップ部品 13 及びワイヤ 14 を封止するよう形成されている。この第 1 の封止樹脂 34 により、チップ部品 13 及びワイヤ 14 は保護される。

#### 【 0 0 2 1 】

また、第 2 の封止樹脂 40 は、第 1 の基板 10 と第 2 の基板 20 との間に充填されている。この第 2 の封止樹脂 40 は接着剤として機能し、よって第 1 の基板 10 と第 2 の基板 20 は第 2 の封止樹脂 40 により強固に接合される。

#### 【 0 0 2 2 】

上記構成のチップ内蔵基板 1 によれば、チップ部品 13 が一対の基板 10, 20 の間に配設された構成となり、また第 1 の基板 10 と第 2 の基板 20 の離間距離は電極 21 により第 2 の基板 20 がワイヤ 14 に接触しない距離に精度よく設定できるため、チップ内蔵基板 1 の小型化を図ることができる。

#### 【 0 0 2 3 】

また、上記のように第 1 の基板 10 と第 2 の基板 20 は、電極 21 による接合力と、第 2 の封止樹脂 40 による接合力（接着力）の二つの接合力により接合されるため、高い信頼性を持って接合される。

#### 【 0 0 2 4 】

続いて、上記構成とされたチップ内蔵基板 1 の製造方法について説明する。

#### 【 0 0 2 5 】

チップ内蔵基板 1 を製造するには、先ず第 1 の基板 10 を用意する。この第 1 の基板 10 は、例えば通常のプリント基板、プリブルグ材（ガラス纖維にエポキシ樹脂などを含浸させた材料）よりなるコア基板にスルーホール、有底のビアプラグ、配線パターン、及びソルダーレジスト等（図示は省略している）を配設した多層配線構成とされている。この第 1 の基板 10 の上面 10a には、配線パターンに接続されたワイヤ接続用パッド 11 及びバンプ接続用パッド 12 が形成されている。

#### 【 0 0 2 6 】

チップ部品 13 は、上記構成とされた第 1 の基板 10 の上面 10a にダイ付け様の接着剤を用いて搭載される。図 1 (A) は、第 1 の基板 10 にチップ部品 13 が搭載された状態を示している。このチップ部品 13 は例えば半導体チップであり、本実施例ではフェイスアップで搭載される。

#### 【 0 0 2 7 】

尚、第 1 の基板 10 に実装されるチップ部品 13 は、半導体チップに限定されるものではなく、他の電子部品（例えば、キャパシタ、レジスタ、インダクタ等）であってもよい。

#### 【 0 0 2 8 】

また、ワイヤ接続用パッド 11 及びバンプ接続用パッド 12 は、実際は第 1 の基板 10 に配設されたソルダーレジストに形成された開口部に露出した構成であるが、図 1 及び図 2 では、理解を容易とするために上面 10a から突出（露出）したように図示している。

#### 【 0 0 2 9 】

上記のようにしてチップ部品 13 が第 1 の基板 10 に搭載されると、続いてチップ部品 13 と第 1 の基板 10 とを電気的に接続する工程が行われる。前記のように、本実施例では各チップ部品 13 はフェイスアップで第 1 の基板 10 に搭載されており、このチップ部品 13 とワイヤ接続用パッド 11 はワイヤボンディング法を用いて接続される。

#### 【 0 0 3 0 】

10

20

30

40

50

即ち、第1の基板10はワイヤボンディング装置に装着され、チップ部品13に形成された電極とワイヤ接続用パッド11との間にワイヤ14が配設される。図1(B)は、チップ部品13とワイヤ接続用パッド11との間にワイヤ14が配設された状態を示している。

#### 【0031】

チップ部品13と第1の基板10がワイヤ14により接続されると、この第1の基板10は金型30に装着される。図1(C)は、第1の基板10が金型30に装着された状態を示している。

#### 【0032】

この金型30は、上型30Aと下型30Bとにより構成されている。また、金型30は、上型30Aの各チップ部品13及びワイヤ14との対向位置(この領域をチップ部品の搭載領域とする)にキャビティ32が形成されている。10

#### 【0033】

また、隣接するチップ部品13の間にバンプ接続用パッド12が形成されている部位においては、金型30は第1の基板10に向け突出した突出部31が形成されている。更に、第1の基板10と上型30Aとの間には離型シート33が配設されており、成型後の離型性の向上を図っている。

#### 【0034】

上記の構成とされた金型30に第1の基板10が装着されると、続いて樹脂注入装置(図示せず)からキャビティ32内に樹脂が所定の圧力を持って充填される。これにより、第1の基板10の上面10aにはチップ部品13及びワイヤ14を封止する第1の封止樹脂34が形成される。20

#### 【0035】

この樹脂が充填される際、バンプ接続用パッド12の上部(表面)には離型シート33を介して上型30Aの突出部31が当接して圧接された状態となっている。このため、バンプ接続用パッド12に第1の封止樹脂34が付着するようなことはない。

#### 【0036】

また、第1の基板10上で、隣接するチップ部品13の間にバンプ接続用パッド12が形成されている部位では、隣接する第1の封止樹脂34の間に溝部36が形成され、その底部にバンプ接続用パッド12が存在した構成となる(図1(E)参照)。30

#### 【0037】

図1(D)は、第2の基板20を示している。この第2の基板20は、前記した第1の基板10と同様な構成とされている。即ち、例えば通常のプリント基板、プリプレグ材よりなるコア基板にスルーホール、有底のビアプラグ、配線パターン、及びソルダーレジスト等(図示は省略している)を配設した多層配線構成とされている。この第2の基板20の下面20bには、配線パターンと接続された電極接続用パッド(図示せず)がソルダーレジストに形成された開口から露出した状態となっている。

#### 【0038】

上記構成とされた第2の基板20の電極接続用パッドには、電極21が接合される。図1(D)は、電極21が第2の基板20に接合された状態を示している。40

#### 【0039】

この電極21は、金属コア22にはんだ被膜23が形成(被膜)された構成とされている。本実施例では、金属コア22として銅製のボールが用いられている(以下、金属コア22を銅コア22という)。

#### 【0040】

この電極21を第2の基板20に接合するには、先ず第2の基板20の電極接続用パッドにはんだフラックスを塗布しておき、この電極接続用パッドに電極21をはんだ付けする。また、電極21を第2の基板20に接合した後、フラックスの洗浄工程を行う。このフラックス洗浄を行う際、第2の基板20は第1の基板10と接合される前の状態で行われるため、第1の基板10に影響を及ぼすようなことはない。50

**【0041】**

また第2の基板20の下面20bからの電極21の突出量(図1(D)に矢印H2で示す)は、前記したチップ部品13をワイヤ接続用パッド11に電気的に接続するワイヤ14のワイヤループの高さ(図1(B)に矢印H1で示す)よりも高くなるよう設定されている(H2>H1)。

**【0042】**

尚、図1(A), (B), (C)を用いて説明した第1の基板10にチップ部品13を搭載し、ワイヤ14を配設し、第1の封止樹脂34を形成する工程と、図1(D)を用いて説明した第2の基板20に電極21を接合する工程は、いずれを先に実施しても、また並行して実施することも可能なものである。

10

**【0043】**

上記した第1の基板10及び第2の基板20に対する各製造工程が終了すると、続いて第1の基板10と第2の基板20を接合する工程を行う。

**【0044】**

第1の基板10と第2の基板20を接合するには、先ず第1の基板10に形成されたバンプ接続用パッド12にはんだフラックス35を配設する。この際、隣接する第1の封止樹脂34の間に溝部36が形成されている部位では、この溝部36内にはんだフラックス35が配設される。

**【0045】**

はんだフラックス35がバンプ接続用パッド12に配設されると、続いて電極21とバンプ接続用パッド12とが対向するよう第1の基板10と第2の基板20との位置決めを行う。図1(E)は、第1の基板10の上部に第2の基板20が位置決めされた状態を示している。

20

**【0046】**

次に、第1の基板10と第2の基板20とを圧接し、続いてこれを例えばリフロー炉に入れて加熱することにより、電極21をバンプ接続用パッド12にはんだ付けする。これにより、電極21とバンプ接続用パッド12は接合され、電極21とバンプ接続用パッド12は電気的に接続されると共に機械的に固定される。

特に本実施例では、溝部36内にバンプ接続用パッド12が形成されることにより、全てのバンプ接続用パッド12を第1の基板10の外周位置に配置する必要がなくなる。以下、これについて説明する。

30

**【0047】**

即ち、バンプ接続用パッド12が露出した溝部36を形成することなく、第1の基板10の内側全体に第1の封止樹脂34を形成した構成を想定すると、この構成では必然的にバンプ接続用パッド12を第1の封止樹脂34の形成領域の外側(即ち、第1の基板10の外周位置)に配置する必要が生じる。しかしながら、この構成では、第1の基板10内におけるワイヤ接続用パッド11からバンプ接続用パッド12に至る配線が長くなりインピーダンスが増大してしまう。

**【0048】**

これに対し、本実施例のように隣接する第1の封止樹脂34の間にバンプ接続用パッド12が露出した溝部36を形成することにより、ワイヤ接続用パッド11からバンプ接続用パッド12に至る配線を短くすることが可能となり、配線インピーダンスの低減を図ることができる。

40

**【0049】**

ここで、チップ内蔵基板1の製造方法の説明に戻り、説明を続ける。上記のように電極21とバンプ接続用パッド12がはんだ付けされると、このはんだ付け後に残存するはんだフラックス35の洗浄工程を行う。本実施例では、電極21とバンプ接続用パッド12がはんだ付けされる前に、チップ部品13及びワイヤ14は第1の封止樹脂34により封止される。このため、バンプ接続用パッド12と電極21とのはんだ接合後にフラックス洗浄を行っても、フラックス洗浄時にワイヤ14の破損や短絡が発生することはなく、よ

50

ってチップ内蔵基板1の信頼性を高めることができる。

#### 【0050】

尚、前記したように電極21の下面20bからの高さH2は、ワイヤ14の上面20aからのワイヤループ高さH1に比べて大きく設定されている(H2>H1)ため、第1の基板10と第2の基板20とを接合した際にワイヤ14が第2の基板20と接触して短絡してしまうようなことはない。

#### 【0051】

上記のように第1の基板10と第2の基板20が接合されると、続いて図2(A)に示すように、第1の基板10と第2の基板20との離間部分(以下、空間部25という)に第2の封止樹脂40を充填する工程を行う。この際、第1の封止樹脂34と第2の封止樹脂40は、熱応力の発生を抑制する面から、同一の熱膨張率を有した材料を選定することが望ましい。10

#### 【0052】

第2の封止樹脂40の充填工程では、空間部25の一方(本実施例では図2(A)における右端部)から吸引処理を行いつつ、他方から第2の封止樹脂40を充填することにより行われる。このように、吸引処理を行いながら第2の封止樹脂40の充填を行うことにより、狭い空間部25であっても確実に空間部25内に第2の封止樹脂40を充填することができる。また、この充填工程の際、前記のようにワイヤ14は第1の封止樹脂34に封止されているため、封止樹脂40の充填によりワイヤ14が変形するようなことはない。20

#### 【0053】

第1の基板10と第2の基板20との間の空間部25に第2の封止樹脂40が充填されると、続いて第2の封止樹脂40の硬化処理(例えば、加熱処理)が行われ、以上説明した各工程を実施することにより図2(B)に示すチップ内蔵基板1が製造される。

#### 【0054】

上記のようにして製造されたチップ内蔵基板1は、内部にチップ部品13等を実装しているため、第1の基板10の下面20bに外部接続端子として機能するはんだボール51を配設した構成とすれば、図2(C)に示すような電子装置50Aとして用いることができる。更に、図2(C)に示す構成において、第2の基板20の上面20aに電子部品52を搭載することにより、更に高密度な電子装置50Bを実現することができる(図2(D)参照)。30

#### 【0055】

以上、本発明の好ましい実施例について詳述したが、本発明は上記した特定の実施形態に限定されるものではなく、特許請求の範囲に記載された本発明の要旨の範囲内において、種々の変形・変更が可能なものである。

#### 【図面の簡単な説明】

#### 【0056】

【図1】図1は、本発明の第1実施例であるチップ内蔵基板の製造方法を製造手順に沿って説明するための図である(その1)。40

【図2】図2は、本発明の第1実施例であるチップ内蔵基板の製造方法を製造手順に沿って説明するための図である(その2)。

#### 【符号の説明】

#### 【0057】

1 チップ内蔵基板

10 第1の基板

11, 12 ワイヤ接続用パッド

13 チップ部品

14 ワイヤ

20 第2の基板

- 2 1 電極

2 2 銅コア

2 3 はんだ被膜

2 5 空間部

3 0 金型

3 1 突出部

3 2 キャビティ

3 4 第1の封止樹脂

3 5 はんだフラックス

4 0 第2の封止樹脂

5 0 A, 5 0 B 電子装置

5 1 はんだボール

6 2 電子部品

- 10

【図1】

【図2】

---

フロントページの続き

(58)調査した分野(Int.Cl., DB名)

H 05K 3 / 36

H 01L 25 / 00

H 05K 1 / 18

H 05K 3 / 28