(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6957848号

(P6957848)

(45) 発行日 令和3年11月2日(2021.11.2)

(24) 登録日 令和3年10月11日(2021.10.11)

(51) Int.Cl.

G06F 12/00 (2006.01)

F 1

G06F 12/00 550A

請求項の数 4 (全 10 頁)

(21) 出願番号 特願2016-187345 (P2016-187345)

(22) 出願日 平成28年9月26日 (2016.9.26)

(65) 公開番号 特開2018-55192 (P2018-55192A)

(43) 公開日 平成30年4月5日 (2018.4.5)

審査請求日 令和1年8月30日 (2019.8.30)

(73) 特許権者 000005496

富士フィルムビジネスイノベーション株式

会社

東京都港区赤坂九丁目7番3号

(74) 代理人 100104880

弁理士 古部 次郎

(74) 代理人 100125346

弁理士 尾形 文雄

(74) 代理人 100166981

弁理士 砂田 岳彦

(72) 発明者 塙安 麻人

神奈川県横浜市西区みなとみらい六丁目1

番 富士ゼロックス株式会社内

最終頁に続く

(54) 【発明の名称】電子装置およびDRAMの初期化方法

## (57) 【特許請求の範囲】

## 【請求項 1】

リセットが可能なDRAM(ダイナミック・ランダム・アクセス・メモリ)と、

前記DRAMのリセット制御を行うリセット制御部と、

前記DRAMに対するアクセス制御を行うと共に、当該DRAMに対するリセット操作

を前記リセット制御部に依頼するDRAM制御部と、を備え、

前記リセット制御部は、予め設定された条件に基づいて前記DRAMのリセット操作

を行うと共に、前記DRAM制御部からの依頼に応じて当該DRAMのリセットおよびリセ

ット解除を行い、

前記DRAM制御部は、電源供給を開始された際の動作として、

シングルランク・モードで前記DRAMに対する初期化シーケンスを実行して当該DR

AMに対するアクセスのタイミング調整を行い、

次に、前記リセット制御部に当該DRAMのリセットを依頼し、当該シングルランク・

モードからマルチランク・モードに変更した後に、当該リセット制御部に当該DRAMの

リセット解除を依頼し、

当該マルチランク・モードで当該DRAMに対する初期化シーケンスを実行することを

特徴とする、電子装置。

## 【請求項 2】

前記リセット制御部は、前記DRAM制御部に電源供給が開始されると、前記DRAM

のリセット解除を行い、

10

20

前記DRAM制御部は、前記リセット制御部による前記DRAMのリセット解除が行われた後に、当該DRAMに対する初期化シーケンスを実行することを特徴とする、請求項1に記載の電子装置。

【請求項3】

リセットが可能なDRAM(ダイナミック・ランダム・アクセス・メモリ)に対するアクセス制御を行う装置であって、

電源供給を開始されると、シングルランク・モードで動作して、前記DRAMに対するアクセスのタイミング調整を行い、

前記DRAMのリセット制御を行う外部装置に当該DRAMをリセットさせ、リセット解除後に、マルチランク・モードで前記DRAMに対する初期化シーケンスを実行することを特徴とする、装置。

【請求項4】

リセットが可能なDRAM(ダイナミック・ランダム・アクセス・メモリ)に対してアクセス制御を行うDRAM制御部による当該DRAMの初期化方法であって、

シングルランク・モードで前記DRAMに対する初期化シーケンスを実行して当該DRAMに対するアクセスのタイミング調整を行い、

前記DRAMのリセット制御を行う外部装置に、当該DRAMのリセットを依頼し、

前記シングルランク・モードからマルチランク・モードに変更し、

前記外部装置に、前記DRAMのリセット解除を依頼し、

前記マルチランク・モードで前記DRAMに対する初期化シーケンスを実行することを特徴とする、DRAMの初期化方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電子装置およびDRAMの初期化方法に関する。

【背景技術】

【0002】

特許文献1には、省電力モードからの復帰時に、揮発性メモリに記憶されている信頼性の高い情報を利用可能なメモリ制御装置が開示されている。このメモリ制御装置において、SDRAMコントローラは、省電力モードに移行するときに、SDRAMコントローラ内に設定されている情報をSDRAMに記憶した後にSDRAMをセルフリフレッシュモードに移行させ、省エネ復帰認識回路に省電力モードを示す情報を記憶させる。そして、電力供給が開始されたときに、省エネ復帰認識回路に記憶されている情報に基づいて省電力モードからの復帰か否かを判別し、装置全体への電力供給が停止された状態から復帰を判別した場合には、SDRAMを初期化し、省電力モードからの復帰を判別した場合には、SDRAMを初期化せずにSDRAMのセルフリフレッシュモードを解除した後にSDRAMに記憶されている情報に基づいて省電力モードからの復帰処理を行う。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2006-350859号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

DDR3(Double-Data-Rate3)以降の規格によるDRAM(Dynamic Random Access Memory)では、リセット機能が設けられており、電源投入時等の初期化手順(初期化シーケンス)等の場面で必要に応じてリセット操作が行われる。一方、省電力設計においては、CPUへの電源供給を停止するモードが設定される場合がある。この場合、CPUが電源OFFの状態でもDRAMに対するリセット制御を可能とするため、DRAMのリセット制御用の外部装置が設けられる。しかし、このような構成では、DRAMのリセット制

10

20

30

40

50

御を C P U に代わって外部装置が行うため、 C P U が直接リセット操作を行う場合と異なり、操作によっては動作不良が生じる場合があった。

#### 【 0 0 0 5 】

本発明は、 C P U に代わって外部装置により D R A M のリセット制御を行う構成において、リセット操作における動作不良の発生を抑制することを目的とする。

#### 【課題を解決するための手段】

#### 【 0 0 0 6 】

本発明の請求項 1 に係る電子装置は、

リセットが可能な D R A M と、

前記 D R A M のリセット制御を行うリセット制御部と、

10

前記 D R A M に対するアクセス制御を行うと共に、当該 D R A M に対するリセット操作を前記リセット制御部に依頼する D R A M 制御部と、を備え、

前記リセット制御部は、予め設定された条件に基づいて前記 D R A M のリセット操作を行うと共に、前記 D R A M 制御部からの依頼に応じて当該 D R A M のリセットおよびリセット解除を行い、

前記 D R A M 制御部は、電源供給を開始された際の動作として、

シングルランク・モードで前記 D R A M に対する初期化シーケンスを実行して当該 D R A M に対するアクセスのタイミング調整を行い、

次に、前記リセット制御部に当該 D R A M のリセットを依頼し、当該シングルランク・モードからマルチランク・モードに変更した後に、当該リセット制御部に当該 D R A M のリセット解除を依頼し、

20

当該マルチランク・モードで当該 D R A M に対する初期化シーケンスを実行することを特徴とする、電子装置である。

請求項 2 に係る電子装置は、

前記リセット制御部は、前記 D R A M 制御部に電源供給が開始されると、前記 D R A M のリセット解除を行い、

前記 D R A M 制御部は、前記リセット制御部による前記 D R A M のリセット解除が行われた後に、当該 D R A M に対する初期化シーケンスを実行することを特徴とする、請求項 1 に記載の電子装置である。

請求項 3 に係る装置は、

30

リセットが可能な D R A M ( ダイナミック・ランダム・アクセス・メモリ ) に対するアクセス制御を行う装置であって、

電源供給を開始されると、シングルランク・モードで動作して、前記 D R A M に対するアクセスのタイミング調整を行い、

前記 D R A M のリセット制御を行う外部装置に当該 D R A M をリセットさせ、リセット解除後に、マルチランク・モードで前記 D R A M に対する初期化シーケンスを実行することを特徴とする、装置である。

請求項 4 に係る D R A M の初期化方法は、

リセットが可能な D R A M に対してアクセス制御を行う D R A M 制御部による当該 D R A M の初期化方法であって、

40

シングルランク・モードで前記 D R A M に対する初期化シーケンスを実行して当該 D R A M に対するアクセスのタイミング調整を行い、

前記 D R A M のリセット制御を行う外部装置に、当該 D R A M のリセットを依頼し、

前記シングルランク・モードからマルチランク・モードに変更し、

前記外部装置に、前記 D R A M のリセット解除を依頼し、

前記マルチランク・モードで前記 D R A M に対する初期化シーケンスを実行することを特徴とする、 D R A M の初期化方法である。

#### 【発明の効果】

#### 【 0 0 0 7 】

請求項 1 の発明によれば、 D R A M 制御部に代わって外部装置により D R A M のリセッ

50

ト制御を行う構成において、シングルランク・モードでDRAMに対するレベリングを行い、マルチランク・モードでDRAMを使用するDRAM制御部の電源供給開始時に行われる動作により、DRAM制御部がDRAMにとって不定状態となることを回避することができる。

請求項2の発明によれば、DRAMのリセットが解除されてからDRAM制御部の電源供給開始時の動作が開始されるように制御することにより、DRAM制御部によるDRAMの初期化シーケンスを確実に実行することができる。

請求項3の発明によれば、シングルランク・モードでDRAMに対するレベリングを行い、マルチランク・モードでDRAMを使用する装置の電源供給開始時に行われる動作において、装置がDRAMにとって不定状態となることを回避することができる。

請求項4の発明によれば、DRAMの初期化処理において、シングルランク・モードでDRAMに対するレベリングを行い、マルチランク・モードでDRAMを使用するDRAM制御部の電源供給開始時に行われる動作により、DRAM制御部がDRAMにとって不定状態となることを回避し、リセット操作における動作不良の発生を抑制することができる。

#### 【図面の簡単な説明】

##### 【0008】

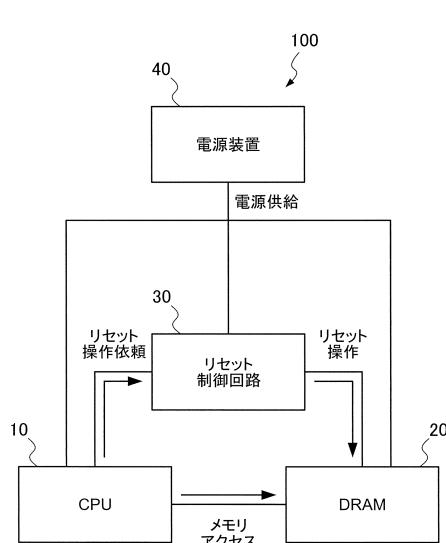

【図1】本実施形態による電子装置の構成例を概略的に示す図である。

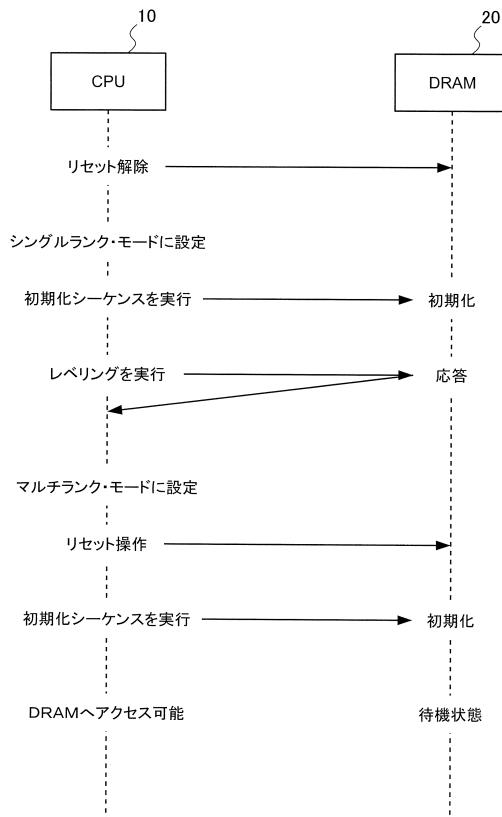

【図2】シングルランク・モードでレベリングを行った後にマルチランク・モードでDIMM(DRAM)を使用するための初期化シーケンスの例を示すシーケンス図である。

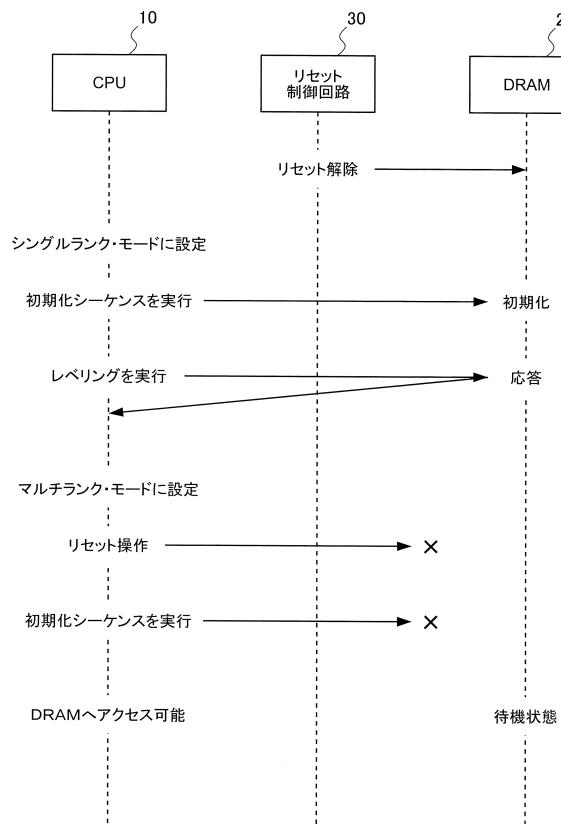

【図3】リセット制御回路を含む構成において、シングルランク・モードでレベリングを行った後にマルチランク・モードでDIMM(DRAM)を使用するための初期化シーケンスの例を示すシーケンス図である。

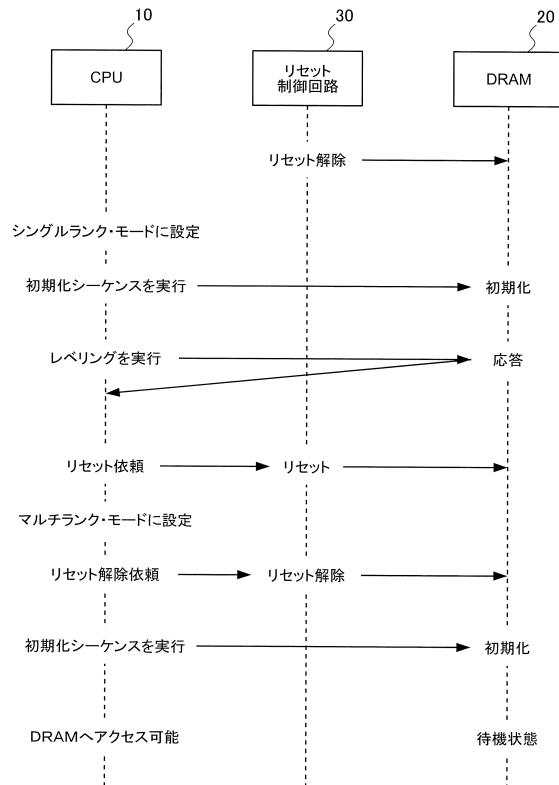

【図4】本実施形態によるDIMM(DRAM)の初期化シーケンスを示すシーケンス図である。

#### 【発明を実施するための形態】

##### 【0009】

<本実施形態が適用される電子装置の構成>

図1は、本実施形態による電子装置の構成例を概略的に示す図である。

図1に示す構成例において、本実施形態の電子装置100は、演算装置であるCPU(Central Processing Unit)10と、記憶装置であるDRAM20と、DRAM20のリセット制御を行うリセット制御回路30と、電源装置40とを備える。また、CPU10、DRAM20およびリセット制御回路30は、電源装置40から電源供給を受けている。なお、図1に示す構成例は、本実施形態における特徴的な構成のみが記載されている。実際には、外部装置とデータ交換を行うためのコントローラやインターフェイス、入力デバイス、表示制御装置などの種々の装置(モジュール、ユニット)が電子装置100に搭載される。

##### 【0010】

DRAM20は、例えば、DDR3等のリセット機能を有するRAM(Random Access Memory)であり、メモリ・コントローラ(DRAM制御部の一例)を介してデータの入出力が行われる。本実施形態では、CPU10がメモリ・コントローラの機能を兼ねる。

##### 【0011】

リセット制御回路30(リセット制御部の一例)は、DRAM20のリセット制御を行う。詳しくは後述するが、本実施形態では、DRAM20のリセット制御を、CPU10ではなく、専用の装置であるリセット制御回路30により行う。ここで、リセット制御回路30によるリセット制御は、予め設定された条件(リセット条件またはリセット解除条件)を満たすときにDRAM20へのリセット信号をLowレベルやHighレベルとし、次に別の条件(リセット解除条件またはリセット条件)を満たすまでその出力を維持するものである。一例として、電子装置100の電源投入時等、CPU10への電源供給が開始されるときには、DRAM20の初期化シーケンスを実行するために、リセット制御

10

20

30

40

50

回路30は、DRAM20のリセット解除を行う。また、本実施形態では、リセット制御回路30は、予め設定されたDRAM20のリセット制御の他に、CPU10からのリセット操作依頼を受け付けると、DRAM20のリセット操作（リセットおよびリセット解除）を行う。

【0012】

CPU10は、各種の制御動作および演算処理を実行する。また、本実施形態のCPU10は、リセット制御回路30が行う予め設定されたリセット操作の他にCPU10からの制御に基づいてDRAM20のリセットを行う必要がある場合に、リセット制御回路30に対してDRAM20のリセット操作を依頼する。

【0013】

本実施形態において、電子装置100は、いわゆる省電力モードの一つとして、CPU10の電源供給を停止するモードを有している。省電力モードでは、省電力モードに移行する際に電子装置100の動作状態についての情報がDRAM20等の記憶装置に保存され、その後に各装置への電源供給が停止される。そして、通常の動作モードに復帰する際、各装置は、記憶装置に保存されている動作状態の情報を取得して省電力モードへ移行する前の状態に復帰する。なお、DRAM20に情報を保存した場合、省電力モードにおいても、DRAM20に対しては、保存した情報を維持するために電源供給が継続される。一方、不揮発性の記憶装置に情報を保存した場合は、省電力モードにおいて、記憶装置に対する電源供給も停止することができる。

【0014】

ここで、動作状態の情報がDRAM20に保存される場合、CPU10への電源供給が停止されると、CPU10からDRAM20へのリセット信号が0(OFF)になる。すると、DRAM20もリセット状態になってしまないので、DRAM20は、記憶内容を保持することができない。そこで、本実施形態の電子装置100は、CPU10への電源供給が停止されている間もDRAM20の記憶内容を保持させるため、外部回路（外部装置）であるリセット制御回路30を設け、CPU10ではなくリセット制御回路30によりDRAM20のリセット制御を行う。

【0015】

<DRAM20の仕様とレベリング>

また、本実施形態において、DRAM20は、マルチランク構成のDIMM（Dual Inline Memory Module）とする。複数のDRAMチップをプリント基板上に搭載したメモリモジュールをDIMMと呼び、メモリモジュールの動作ブロックの単位をランクと呼ぶ。マルチランクとは、1枚のDIMMに複数のランクが設けられていることを意味し、ランク2（ランクの数が2）、ランク4（ランクの数が4）等のDIMMが存在する。また、1枚のDIMMで1ランクが設けられたメモリモジュールをシングルランク・メモリ、2ランク使用するメモリモジュールをデュアルランク・メモリ等と呼ぶ。

【0016】

ところで、DDR3以降のDIMMは、フライバイ・トポロジと呼ばれる設計が行われている。そのため、メモリ・コントローラから送信された信号がDIMM上の各DRAM20に到達するのが同時ではなく、個々のDRAM20ごとに時間差が存在する。この時間差があることを前提としてデータの読み書きを正常に行うため、DIMMに対する電源投入時の初期化シーケンスにおいて、レベリングと呼ばれるメモリ・コントローラのタイミング調整が行われる。

【0017】

上述したマルチランク構成のDIMMでは、ランクごとに個別にレベリングを行うことが好適である。しかし、このレベリングの操作を簡易に行うため、一つのランクに対してレベリングを行って得られた調整結果を他のランクに対しても流用する手法がとられる場合がある。この場合、DIMMの初期化シーケンスにおいて、まず一つのランクのみを用いるモード（シングルランク・モード）にDIMMを設定してメモリ・コントローラのレベリングを行い、その後に複数ランクを用いるモード（マルチランク・モード）にDIM

10

20

30

40

50

Mの設定を変更して動作させるようとする。ここで、シングルランク・モードからマルチランク・モードに設定を変更するために、D I M M ( D R A M 2 0 )をリセットすることが必要である。

【 0 0 1 8 】

図2は、シングルランク・モードでレベリングを行った後にマルチランク・モードでD I M M ( D R A M 2 0 )を使用するための初期化シーケンスの例を示すシーケンス図である。ここでは、レベリングを含む初期シーケンスの一般的な流れを説明するため、リセット制御回路30を用いず、C P U 1 0によりリセット制御を行う場合の動作について説明する。

【 0 0 1 9 】

図2に示す例において、C P U 1 0およびD R A M 2 0に対して電源装置40による電源供給が開始されると、まずC P U 1 0からD R A M 2 0へ送られるリセット信号がH i g h レベルとなり、D R A M 2 0のリセット解除が行われる。そして、C P U 1 0は、まずメモリ・コントローラとしての動作モードをシングルランク・モードに設定し、D R A M 2 0の初期化シーケンスを実行し、レベリングを実行する。C P U 1 0がD R A M 2 0から応答を受けてレベリングが完了する。

【 0 0 2 0 】

次に、C P U 1 0は、メモリ・コントローラとしての動作モードをマルチランク・モードに再設定し、リセット操作を行う。すなわち、C P U 1 0からD R A M 2 0へ送られるリセット信号を一度L o w レベルにし(リセット)、再びH i g h レベルにする(リセット解除)。そして、C P U 1 0は、マルチランク・モードでD R A M 2 0の初期化シーケンスを実行する。この2回目の初期化シーケンスが終了すると、D R A M 2 0は待機状態(スタンバイ)となり、C P U 1 0は、D R A M 2 0に対してマルチランク・モードでアクセス可能となる。

【 0 0 2 1 】

<本実施形態におけるD R A M 2 0の初期化シーケンス>

上述したように、本実施形態では、C P U 1 0に代わってリセット制御回路30がD R A M 2 0のリセット制御を行う。ここで、D R A M 2 0の初期化シーケンスの実行時におけるリセット制御について考える。上述したように、本実施形態では、C P U 1 0への電源供給が開始されると、リセット制御回路30がD R A M 2 0へのリセット信号をH i g h レベルにしてリセットを解除し、C P U 1 0が初期化シーケンスを開始する。

【 0 0 2 2 】

図3は、リセット制御回路30を含む構成において、シングルランク・モードでレベリングを行った後にマルチランク・モードでD I M M ( D R A M 2 0 )を使用するための初期化シーケンスの例を示すシーケンス図である。本来、マルチランク・モードでD R A M 2 0を使用する場合には、D R A M 2 0の初期化シーケンスにおけるレベリングは、マルチランク・モードで行われる。この場合、D R A M 2 0の初期化シーケンスの開始後にリセット操作が行われることはない。リセット操作を行うと、その度に再び初期化シーケンスを実行することとなるためである。そのため、図3に示す例では、リセット制御回路30は、最初にリセットを解除した後はD R A M 2 0に対するリセット操作を行わない。

【 0 0 2 3 】

図3に示すように、C P U 1 0への電源供給が開始されると、リセット制御回路30は、D R A M 2 0のリセットを解除する。そして、C P U 1 0は、メモリ・コントローラとしての動作モードをシングルランク・モードに設定し、D R A M 2 0の初期化シーケンスを実行し、レベリングを実行する。C P U 1 0がD R A M 2 0から応答を受けてレベリングが完了する。

【 0 0 2 4 】

次に、C P U 1 0は、メモリ・コントローラとしての動作モードをマルチランク・モードに再設定し、D R A M 2 0のリセット操作を行おうとする。しかし、D R A M 2 0のリセット制御はリセット制御回路30が行うように構成されている(C P U 1 0は、D R A

10

20

30

40

50

M20へのリセット信号線が接続されていない)ので、CPU10の制御によりDRAM20のリセット操作を行うことはできない。また、上述したように、リセット制御回路30は、このタイミングでDRAM20のリセット操作を行わない。そのため、この動作モードの再設定後のタイミングで、DRAM20はリセットされない。

【0025】

この後、CPU10は、DRAM20の初期化シーケンスを実行しようとするが、DRAM20は、リセットされていないために、CPU10からの再初期化コマンドに基づく初期化シーケンスが実行されない。したがって、CPU10は、この2回目の初期化シーケンスが終了した後、DRAM20に対してマルチランク・モードでアクセスしようとするが、DRAM20はシングルランク・モードのままとなり、CPU10からDRAM20へ正常にアクセスすることができなくなる。10

【0026】

上記のように、DRAM20のリセット制御を外部回路であるリセット制御回路30で行う構成では、メモリ・コントローラにおいてシングルランク・モードでレベリングを行った後にマルチランク・モードでDIMM(DRAM20)を使用する場合、正常に初期化シーケンスを実行することができない。このような事態を回避するため、本実施形態では、CPU10は、DRAM20に対してリセット操作を行う必要がある場合に、リセット制御回路30に対してリセット操作を行うように依頼する。そして、リセット制御回路30が、CPU10からの依頼を受けてDRAM20のリセット操作を行う。20

【0027】

図4は、本実施形態によるDIMM(DRAM20)の初期化シーケンスを示すシーケンス図である。図4に示す動作において、CPU10が、シングルランク・モードでレベリングを実行し、DRAM20から応答を受けてレベリングが完了するまでの動作は、図3に示した動作と同様である。20

【0028】

次に、CPU10は、リセット制御回路30に対してリセット依頼を行う。リセット制御回路30は、このCPU10からの依頼を受けて、DRAM20をリセットする(リセット信号をLowレベルにする)。そして、CPU10は、メモリ・コントローラとしての動作モードをマルチランク・モードに再設定し、リセット制御回路30に対してリセット解除依頼を行う。リセット制御回路30は、このCPU10からの依頼を受けて、DRAM20をリセット解除する(リセット信号をHighレベルにする)。30

【0029】

この後、CPU10は、マルチランク・モードでDRAM20の初期化シーケンスを実行する。この2回目の初期化シーケンスが終了すると、DRAM20は待機状態(スタンバイ)となり、CPU10は、DRAM20に対してマルチランク・モードでアクセス可能となる。

【0030】

ここで、図4に示す動作では、CPU10は、マルチランク・モードに再設定する前に、リセット制御回路30にリセット依頼を行ってDRAM20をリセット(リセット信号がLowレベル)させ、マルチランク・モードへの再設定が終了した後に、リセット制御回路30にリセット解除依頼を行ってDRAM20をリセット解除(リセット信号がHighレベル)させた。このような手順をとったのは、DRAM20にとってCPU10が不定状態となって、DRAM20が予期せぬ状態となってしまうことを抑制するためである。すなわち、DRAM20をリセットする前にCPU10のマルチランク・モードへの再設定を行うと、DRAM20にとってCPU10が不定状態となる。すると、CPU10から出力される制御信号が、DRAM20において不定出力として認識される。そのため、DRAM20において、CPU10からの初期化コマンドに基づいて初期化シーケンスの再実行が行われなかったり、保存していたデータが消失したりする等の予期せぬ事態が発生する可能性があった。そこで、本実施形態では、図4に示したように、まずDRAM20をリセットしてからCPU10のマルチランク・モードへの再設定を行い、再設定4050

が終了して CPU10 が DRAM20 にとって不定状態でなくなつてからリセット解除することにより、DRAM20 において予期せぬ事態が発生することを抑制している。

【0031】

以上説明したように、本実施形態は、CPU10 がリセット制御回路30 に対してリセット操作（リセットおよびリセット解除）を依頼し、リセット制御回路30 が CPU10 からの依頼に応じて DRAM20 に対するリセット操作を実行する。このような構成としたことにより、本実施形態によれば、リセット制御回路30 において予め設定された条件で行われるリセット操作以外にも、DRAM20 のリセット操作を行う必要がある場合に、CPU10 からリセット制御回路30 へ依頼することにより、DRAM20 のリセット操作を行うことが可能となる。

10

【符号の説明】

【0032】

10 ... CPU、20 ... DRAM、30 ... リセット制御回路、40 ... 電源装置、100 ... 電子装置

【図1】

【図2】

【図3】

【図4】

---

フロントページの続き

(72)発明者 野村 建太

神奈川県横浜市西区みなとみらい六丁目1番 富士ゼロックス株式会社内

(72)発明者 佐伯 梨佐

神奈川県横浜市西区みなとみらい六丁目1番 富士ゼロックス株式会社内

審査官 木村 貴俊

(56)参考文献 特開2009-158032(JP, A)

特開2006-252654(JP, A)

特開2012-068873(JP, A)

特開2012-059184(JP, A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 12 / 00 - 12 / 06

13 / 16 - 13 / 18