(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6577166号

(P6577166)

(45) 発行日 令和1年9月18日(2019.9.18)

(24) 登録日 令和1年8月30日(2019.8.30)

(51) Int.Cl.

G06F 13/16 (2006.01)

G06F 12/00 (2006.01)

F 1

G06F 13/16 510 F

G06F 12/00 597 U

G06F 12/00 560 A

請求項の数 6 (全 23 頁)

(21) 出願番号 特願2014-23971 (P2014-23971)

(22) 出願日 平成26年2月12日 (2014.2.12)

(65) 公開番号 特開2014-157603 (P2014-157603A)

(43) 公開日 平成26年8月28日 (2014.8.28)

審査請求日 平成29年2月8日 (2017.2.8)

(31) 優先権主張番号 13/768, 215

(32) 優先日 平成25年2月15日 (2013.2.15)

(33) 優先権主張国・地域又は機関

米国(US)

前置審査

(73) 特許権者 508243639

エルエスアイ コーポレーション

アメリカ合衆国カリフォルニア州9513

1, サンノゼ, リッダー・パーク・ドライ

ヴ 1320

(74) 代理人 110001195

特許業務法人深見特許事務所

(72) 発明者 クリストファー・ブルーアー

アメリカ合衆国 95131 カリフォル

ニア, サンホセ, リッダー パーク ド

ライヴ 1320

(72) 発明者 アール・ティ・コーエン

アメリカ合衆国 94015 カリフォル

ニア, クパチーノ, ハーモサ アベニュー

78

最終頁に続く

(54) 【発明の名称】不揮発性メモリのチャネル制御用システム及びその制御方法

## (57) 【特許請求の範囲】

## 【請求項 1】

システムであって、

コマンドインターフェースを介して、コマンドを受け取り、及びレスポンスを送出する

ように構成された高レベル制御プロセッサと、

前記システムと1以上の不揮発性メモリデバイスとを接続するように構成された不揮発

性メモリデバイスインターフェースと、

(i) 前記高レベル制御プロセッサと(ii) 前記不揮発性メモリデバイスインターフ

ェースとに接続され、コントロールストアを有する低レベルマイクロシーケンサ

を備え、

前記不揮発性メモリデバイスインターフェースは、複数のデータ入出力ピンと複数の制

御入出力ピンとを備え、

前記コントロールストアは、前記低レベルマイクロシーケンサによって読み取り可能で

あり、及び、前記高レベル制御プロセッサによって書き込み可能であり、

前記コマンドのうちの特定のコマンドを受け取ると、

前記高レベル制御プロセッサは、前記特定のコマンドに従って、前記コントロールスト

ア内の位置で前記低レベルマイクロシーケンサに実行を開始させることができ、

前記低レベルマイクロシーケンサは、前記制御入出力ピン及び前記データ入出力ピンの

状態を変更して、前記不揮発性メモリデバイスインターフェースに接続された前記1以上

の不揮発性メモリデバイスのプロトコルに従って、前記特定のコマンドを実行することが

10

20

でき、

前記コントロールストアは、前記1以上の不揮発性メモリデバイスに関連付けられている1以上のプロトコルを実行するように前記高レベル制御プロセッサによってプログラムされることからなり、

前記高レベル制御プロセッサは、さらに、

まず、前記コントロールストアが複数のタイプの不揮発性メモリデバイスと互換性のある低速プロトコルを実行するように、前記高レベル制御プロセッサが前記コントロールストアをプログラムすることができるように構成され、及び、

その後、前記コントロールストアが前記1以上の不揮発性メモリデバイスと互換性のあるより高速なプロトコルを実行するように、前記高レベル制御プロセッサが前記コントロールストアをプログラムすることができるように構成されることからなる、システム。

10

#### 【請求項2】

前記低レベルマイクロシーケンサを介して前記不揮発性メモリデバイスインターフェースに接続された出力データインターフェースであって、出力データバッファを有する出力データインターフェースと、

前記低レベルマイクロシーケンサを介して前記不揮発性メモリデバイスインターフェースに接続された入力データインターフェースであって、入力データバッファを有する入力データインターフェース

をさらに備え、

前記出力データバッファは、前記不揮発性メモリデバイスインターフェースに送られるデータを受け取ることができ、

20

前記入力データバッファは、前記不揮発性メモリデバイスインターフェースから受け取ったデータを受け取ることができることからなる、請求項1に記載のシステム。

#### 【請求項3】

前記低レベルマイクロシーケンサは、さらに、(i)前記入力データバッファの全体状態を検出し、及び、(ii)前記全体状態の検出に応じて、前記コントロールストア内の所定の位置にジャンプすることができる、請求項2に記載のシステム。

#### 【請求項4】

前記システムは、ソリッドステートドライブ(SSD)装置の一部である、請求項1～3のいずれかに記載のシステム。

30

#### 【請求項5】

前記システムは、1以上の集積回路として実施される、請求項1～3のいずれかに記載のシステム。

#### 【請求項6】

不揮発性メモリチャネルを制御する方法であって、

高レベル制御プロセッサに接続されたコマンドインターフェースを介して、コマンドを受け取り、及びレスポンスを送出するステップと、

前記高レベル制御プロセッサに接続された低レベルマイクロシーケンサを用いて、コントロールストア内の位置で命令の実行を開始するステップ

を含み、

40

前記位置は、受け取った前記コマンドのうちの特定のコマンドにしたがって、前記高レベル制御プロセッサにより決定され、

前記低レベルマイクロシーケンサは、不揮発性メモリデバイスインターフェースの制御入出力ピン及びデータ入出力ピンの状態を変更して、前記不揮発性メモリデバイスインターフェースによって前記低レベルマイクロシーケンサに接続された1以上の不揮発性メモリデバイスのプロトコルに従って、前記特定のコマンドを実行し、

前記方法はさらに、前記高レベル制御プロセッサを用いて、前記不揮発性メモリデバイスインターフェースに取付けられた前記1以上の不揮発性メモリデバイスに関連付けられている1以上のプロトコルを実行するように前記コントロールストアをプログラムするステップを含むことからなり、

50

まず、前記コントロールストアが複数のタイプの不揮発性メモリデバイスと互換性のある低速プロトコルを実行するように、前記高レベル制御プロセッサが前記コントロールストアをプログラムできるようにするステップと、

その後、前記コントロールストアが前記1以上の不揮発性メモリデバイスと互換性のあるより高速なプロトコルを実行するように、前記高レベル制御プロセッサが前記コントロールストアをプログラムできるようにするステップ

をさらに含む、方法。

【発明の詳細な説明】

【技術分野】

【0001】

10

本発明は、メモリシステムに関し、特に、低レベルプログラマブルシーケンサと共に汎用プログラマブルプロセッサを用いて不揮発性メモリのチャネル制御を実装する方法及び／又は装置に関する。

【背景技術】

【0002】

20

従来の不揮発性メモリ制御システムでは、当該システムで利用可能な種類のデバイスにフレキシブルに対応できるよう様々なプロトコルの使用を試みてきた。様々なプロトコルに対応するには、想定されるタイプのインターフェースごと、及び、必要なインターフェースコマンドタイプごとの専用制御回路が必要である。

【発明の概要】

【発明が解決しようとする課題】

【0003】

20

しかしながら、インターフェースプロトコルごとの専用制御回路に依存することはあまりフレキシブルな手法ではない。この場合、インターフェースプロトコルが新しくなったりわずかに変更したりすると、費用のかかる回路再設計が必要となる。代わりに、中央演算処理装置（CPU）を用いて、不揮発性メモリインターフェースの低レベル制御のフレキシブル性を可能にすることができる。しかしながら、これではCPUにかなりの負荷をかけるため、性能が制限されてしまう。

【0004】

30

ゆえに、低レベルプログラマブルシーケンサと共に汎用プログラマブルプロセッサを用いた不揮発性メモリのチャネル制御を実装することが望ましい。

【課題を解決するための手段】

【0005】

40

本発明は、制御プロセッサと、不揮発性メモリデバイスインターフェースと、マイクロシーケンサとを備えたシステムに関する。制御プロセッサは、コマンドインターフェースを介して、コマンドを受け取り、レスポンスを送出してもよい。不揮発性メモリデバイスインターフェースは、当該システムと1以上の不揮発性メモリデバイスとを接続してもよい。マイクロシーケンサは、通常、（i）制御プロセッサと（ii）不揮発性メモリデバイスインターフェースとに接続される。マイクロシーケンサは、マイクロシーケンサで読み取り可能、かつ、制御プロセッサで書き込み可能なコントロールストアを備える。コマンドのうち特定コマンドを受け取ると、制御プロセッサは、特定コマンドに従い、コントロールストア内の位置でマイクロシーケンサに実行開始させることができ、マイクロシーケンサは、不揮発性メモリデバイスインターフェースに接続された1以上の不揮発性メモリデバイスのプロトコルに従い、特定コマンドの少なくとも一部を実行することができる。

【0006】

50

より詳しくは、本発明の一形態は、システムであって、コマンドインターフェースを介して、コマンドを受け取り、レスポンスを送出する制御プロセッサと、前記システムと1以上の不揮発性メモリデバイスとを接続する不揮発性メモリデバイスインターフェースと、（i）前記制御プロセッサと（ii）前記不揮発性メモリデバイスインターフェースと

に接続され、コントロールストアを有するマイクロシーケンサとを備え、前記コントロールストアは、前記マイクロシーケンサで読み取り可能、かつ、前記制御プロセッサで書き込み可能であり、前記コマンドのうち特定コマンドを受け取ると、前記制御プロセッサは、前記特定コマンドに従い、前記コントロールストア内の位置で前記マイクロシーケンサに実行開始させることができ、前記マイクロシーケンサは、前記不揮発性メモリデバイスインターフェースに接続された前記1以上の不揮発性メモリデバイスのプロトコルに従い、前記特定コマンドの少なくとも一部を実行することができる。

#### 【0007】

ここで、前記不揮発性メモリデバイスインターフェースは、複数のデータ入出力ピンと、複数の制御入出力ピンとを備えてもよい。

10

#### 【0008】

また、前記マイクロシーケンサは、前記制御入出力ピンと前記データ入出力ピンとの状態を変更して、前記プロトコルに従い前記特定コマンドを実行することができてもよい。

#### 【0009】

また、前記コントロールストアは、前記不揮発性メモリデバイスインターフェースに取付けられた前記1以上の不揮発性メモリデバイスに関連付けられている1以上のプロトコルを実行するよう前記制御プロセッサによってプログラミングされてもよい。

#### 【0010】

また、前記制御プロセッサは、さらに、まず、複数のタイプの不揮発性メモリデバイスと互換性のある低速プロトコルを実行するよう前記コントロールストアを前記制御プロセッサがプログラミングすることができ、続いて、前記1以上の不揮発性メモリデバイスと互換性のあるより高速なプロトコルを実行するよう前記コントロールストアを前記制御プロセッサがプログラミングすることができてもよい。

20

#### 【0011】

また、さらに、前記マイクロシーケンサを介して前記不揮発性メモリデバイスインターフェースに接続され、出力データバッファを有する出力データインターフェースと、前記マイクロシーケンサを介して前記不揮発性メモリデバイスインターフェースに接続され、入力データバッファを有する入力データインターフェースとを備え、前記出力データバッファは、前記不揮発性メモリデバイスインターフェースに出力されるデータを受け取り可能であり、前記入力データバッファは、前記不揮発性メモリデバイスインターフェースから入力されたデータを受け取り可能であってもよい。

30

#### 【0012】

また、前記マイクロシーケンサは、さらに、(i)前記入力データバッファの全体状態を検出し、(ii)前記全体状態の検出結果に応じて、前記コントロールストア内の所定の位置にジャンプすることができてもよい。

#### 【0013】

また、前記システムは、ソリッドステートドライブ(SSD)装置の一部であってもよい。

#### 【0014】

また、前記システムは、1以上の集積回路として実装されてもよい。

40

#### 【0015】

また、本発明の別の形態は、不揮発性メモリチャネルの制御方法であって、制御プロセッサに接続されたコマンドインターフェースを介して、コマンドを受け取り、レスポンスを送出するステップと、前記制御プロセッサに接続されたマイクロシーケンサを用いて、コントロールストア内の位置で命令実行を開始するステップとを含み、前記位置は、受け取った前記コマンドのうち特定コマンドに従い、前記制御プロセッサにより決定され、前記マイクロシーケンサは、不揮発性メモリデバイスインターフェースにより前記マイクロシーケンサに接続された1以上の不揮発性メモリデバイスのプロトコルに従い、前記特定コマンドの少なくとも一部を実行する。

#### 【0016】

50

ここで、さらに、前記制御プロセッサを用いて、前記不揮発性メモリデバイスインターフェースに取付けられた前記1以上の不揮発性メモリデバイスに関連付けられている1以上のプロトコルを実行するよう前記コントロールストアをプログラミングするステップを含んでもよい。

【0017】

また、さらに、まず、複数のタイプの不揮発性メモリデバイスと互換性のある低速プロトコルを実行するよう前記コントロールストアを前記制御プロセッサにプログラミングさせるステップと、続いて、前記1以上の不揮発性メモリデバイスと互換性のあるより高速なプロトコルを実行するよう前記コントロールストアを前記制御プロセッサにプログラミングさせるステップとを含んでもよい。

10

【発明の効果】

【0018】

本発明により、低レベルプログラマブルシーケンサと共に汎用プログラマブルプロセッサを用いた不揮発性メモリのチャネル制御が実現される。つまり、専用回路で実現した場合の長所と汎用プロセッサで実現した場合の長所の両方を併せ持つ不揮発性メモリのチャネル制御が実現される。

【図面の簡単な説明】

【0019】

本発明の実施形態は、後述の詳細な説明、並びに、添付された特許請求の範囲及び図面から明らかになる。

20

【図1】図1は、本発明の実施形態に係る不揮発性メモリ制御システムを示す図である。

【図2】図2は、本発明の実施形態に係るインターフェース管理プロセッサを示す図である。

【図3】図3は、図2の出力データバッファの実装例を示す図である。

【図4】図4は、図2の入力データバッファの実装例を示す図である。

【図5】図5は、図2の制御部の実装例を示す図である。

【図6】図6は、図2の低レベル不揮発性メモリインターフェースの実装例を示す図である。

【図7】図7は、図6の低レベル不揮発性メモリインターフェースシーケンサ部の実装例を示す図である。

30

【図8】図8は、図6のDQ取り込みブロックの実装例を示す図である。

【図9】図9は、図8のDQ取り込みニアパッド論理回路(NPL)ブロックの実装例を示す図である。

【図10】図10は、図8のDLLブロックの実装例を示す図である。

【図11】図11は、出力インターフェースニアパッド論理回路ブロックの実装例を示す図である。

【図12】図12は、本発明の実施形態に係るマルチチャネル型不揮発性メモリ制御システムを示す図である。

【発明を実施するための形態】

【0020】

本発明の実施形態は、低レベルプログラマブルシーケンサと共に汎用プログラマブルプロセッサを用いて不揮発性メモリ(例えば、フラッシュなど)のチャネル制御を実装する方法及び/又は装置を含む。本発明の実施形態では、(i)高レベル制御用汎用中央演算処理装置(CPU)と、不揮発性メモリインターフェースの低レベル制御用プログラマブルマイクロシーケンサとを組み合わせ、(ii)マイクロシーケンサを用いて、シーケンスプログラミングで定義されたような不揮発性メモリインターフェースのクロックサイクル制御によりクロックサイクルを供給し、(iii)どのような不揮発性メモリインターフェースも扱えるようにマイクロシーケンサをプログラミングでき、(iv)まだ想定されていない今後の不揮発性メモリインターフェースのプログラミングを可能にし、(v)マイクロシーケンサを用いて、不揮発性メモリのピン出力を制御、データ出力及びデータ

40

50

取込を制御、インターフェース動作モードを設定、かつ／又は、（パイプライン遅延を生じることなく）定義されたシーケンスで設定回数ループするよう命令し、（*v i*）マイクロシーケンサを用いて、コンフィギュラブルな方法でデータ欠乏状態及びデータバックプレッシャー状態に対処できる性能を与え、（*v i i*）C P Uとマイクロシーケンサとの間で共有メモリを実装することにより、シーケンスパラメータを引き渡し可能、かつ、マイクロシーケンス制御コードを容易に変更可能にし、（*v i i i*）シーケンスを実行するための要求をマイクロシーケンサに渡し、シーケンスが完了、又は、エラー状態のときにのみマイクロシーケンサからのレスポンスを生成し、かつ／又は、（*i x*）より高レベルなスケジューリング、管理、及び、決定を行えるようにC P Uの負荷を削減してもよい。

## 【0021】

10

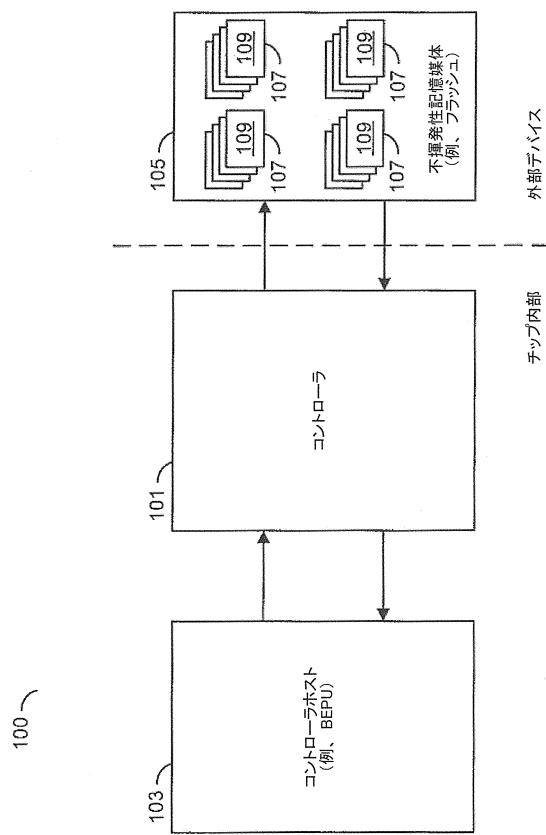

図1は、本発明の実施形態に係る不揮発性メモリ制御システム100を示す図である。ある実施形態では、不揮発性メモリ制御システム100は、ブロック101とブロック103とを備える。ブロック101は、インターフェース管理プロセッサ（I M P）とも呼ばれるメモリチャネルコントローラを実装してもよい。ブロック103は、コントローラホストを実装してもよい。コントローラ101は、本発明に係るシステムの一例であり、1以上の個別不揮発性メモリチャネルを制御してもよい。ある実施形態では、複数の不揮発性メモリチャネルを制御するようにコントローラ101のマルチインスタンスを実装してもよい。コントローラ101は、コマンドを受け取ってホスト103にレスポンスを送出するコマンドインターフェースを有する。ホスト103は、例えば、バックエンド処理部（B E P U）を備えててもよい。複数の不揮発性メモリチャネルを実装する実施形態では、ホスト103は、また、コントローラ101のマルチインスタンスとB E P Uとを接続する多重化回路を備えててもよい。ある実施形態では、ホスト103は、ソリッドステートディスク（S S D）コントローラなどのI / Oデバイスコントローラであり、B E P Uは、N A N Dフラッシュ不揮発性メモリチップなどの複数の不揮発性メモリデバイスをスケジューリング及び／又はデータ管理するコントローラの一部である。別の実施形態では、B E P Uは、データ又はその他の情報を格納し、かつ、当該データ又は他の情報をホスト103とコントローラ101との間で移動させるためのデータバッファリング及びダイレクトメモリアクセス（D M A）エンジンを備える。

## 【0022】

20

また、コントローラ101は、システム100と不揮発性記憶媒体105とを接続する不揮発性メモリインターフェースを有してもよい。不揮発性記憶媒体105は、1以上の不揮発性メモリデバイス107を備えててもよい。不揮発性メモリデバイス107は、ある実施形態において、1以上の不揮発性メモリダイ109を有する。不揮発性メモリデバイス107のうち特定タイプのものによれば、この特定の不揮発性メモリデバイス107内の複数の不揮発性メモリダイ109は、オプション及び／又は選択的に、並列アクセス可能である。不揮発性メモリデバイス107は、通常、通信的にコントローラ101と接続できるあるタイプのストレージデバイスの代表的なものである。しかしながら、様々な実施形態では、S L C（シングルレベルセル）N A N Dフラッシュメモリ、M L C（マルチレベルセル）N A N Dフラッシュメモリ、T L C（トリプルレベルセル）N A N Dフラッシュメモリ、N O Rフラッシュメモリ、読み取り専用メモリ（R O M）、スタティックランダムアクセスメモリ（S R A M）、ダイナミックランダムアクセスメモリ（D R A M）、磁気抵抗ランダムアクセスメモリ（M R A M）、強誘電体メモリ（例えば、F e R A M、F - R A M、F R A M（登録商標）など）、相変化メモリ（例えば、P R A M、P C R A Mなど）、レーストラックメモリ（又は、ドメイン壁メモリ（D W M））、抵抗変化型メモリ（R R A M（登録商標）又はR e R A M）、又は、他のタイプのメモリデバイス若しくはストレージメディアなど、どんなタイプのストレージデバイスも利用可能である。

## 【0023】

40

ある実施形態では、コントローラ101及び不揮発性記憶媒体105は別々の集積回路に実装される。コントローラ101と不揮発性記憶媒体105とを別々の集積回路（又は装置）として実装した場合、コントローラ101の不揮発性メモリインターフェースは、

50

通常、複数のデータ入力／出力（I/O）ピンと複数の制御I/Oピンとを管理できる。データI/Oピン及び制御I/Oピンは、コントローラ101を含む装置と不揮発性記憶媒体105を形成する外部デバイスとを接続するように構成されてもよい。

#### 【0024】

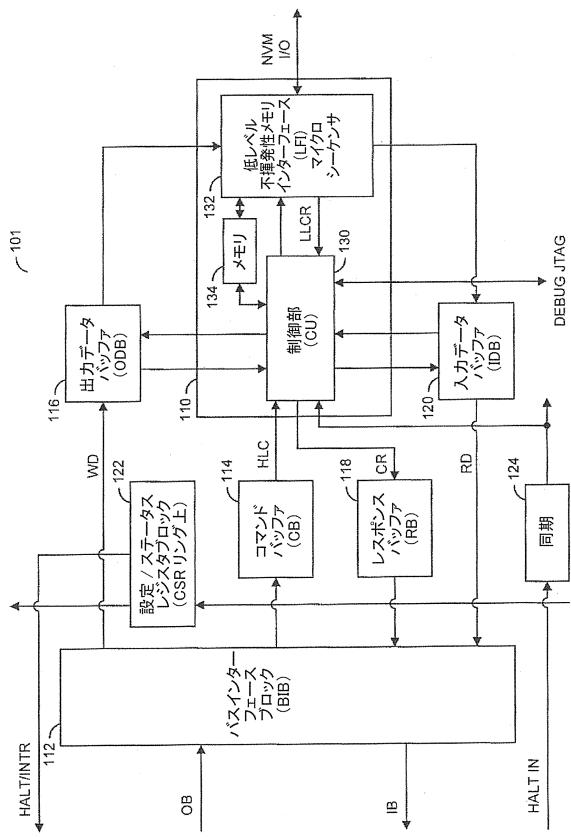

図2は、本発明の実施形態に係るコントローラ101の実装例を示す図である。ある実施形態では、コントローラ101は、インターフェース管理プロセッサ（IMP）を実装する。ある実施形態では、コントローラ101は、ブロック（又は回路）110と、ブロック（又は回路）112と、ブロック（又は回路）114と、ブロック（又は回路）116と、ブロック（又は回路）118と、ブロック（又は回路）120と、ブロック（又は回路）122と、ブロック（又は回路）124とを備える。通常、ブロック110は、コンフィギュラブルで、フレキシブル、かつ、拡張可能な方法で複数の不揮発性メモリデバイスを制御するシリコン論理回路及びファームウェアを実装する。ブロック112は、バスインターフェースブロック（BIB）を実装する。ブロック114は、コマンドバッファ（CB）を実装する。ブロック116は、マイクロシーケンサを介して不揮発性メモリデバイスインターフェースに接続され、出力データバッファを有する出力データインターフェースの一例であり、出力データバッファ（ODB）を実装する。ブロック118は、レスポンスバッファ（RB）を実装する。ブロック120は、マイクロシーケンサを介して不揮発性メモリデバイスインターフェースに接続され、入力データバッファを有する入力データインターフェースの一例であり、入力データバッファ（IDB）を実装する。ブロック122は、設定／ステータスレジスタ（CSR）ブロックを実装する。ブロック124は、同期ブロックを実装する。

10

20

#### 【0025】

バスインターフェースブロック（BIB）112は、バックエンド処理部（例えば、ホスト103）との情報伝達を処理する。BIB112は、出力バス（例えば、OB）を介してBEPUから受け取った低レベルのデータリンクコマンドを処理し、コマンドバッファ114と出力データバッファ116とにコマンドとデータとを渡す。また、BIB112は、入力バス（例えば、IB）を介して、レスポンスバッファ（RB）118からのコマンドレスポンスと入力データバッファ（IDB）120からの入力データとをバックエンド処理部に送出する。コマンドバッファ（CB）114は、出力バスワードをハードウェア制御ポート（HCP）のダブルワードに蓄積し、このHCPダブルワードをCU（制御部）130に出力する。ダブルワードという用語は、1サイクルにおけるデータ転送単位を表す（例えば、8バイト）。レスポンスバッファ（RB）118は、CU130からHCPダブルワードを取得し、このHCPダブルワードを複数の入力バスワードに分解し、そして、この複数の入力バスワードをBIB112に送出する。ある実施形態では、HCPダブルワードは、BEPUとCU130との間でやりとりされたメッセージを含む。例えば、BEPUは、CU130にメッセージを送って、CU130が管理するワークのキューに不揮発性メモリデバイスへのアクセス動作命令を追加し、CU130は、当該動作命令の完了及び／又はステータスを示すメッセージをBEPUに送り返す。別の実施形態では、BEPUからのメッセージには、動作命令のデータ転送にそれぞれ関連付けられたタグが含まれており、CU130は、これらのタグを用いて、不揮発性メモリデバイスに書き込まれるデータのフェッチを開始すること、又は、不揮発性メモリデバイスから読み込んだデータの動作命令別移動先を示すことができる。このように、BIB112、CB114及びRB118により、コマンドインターフェースが構成される。

30

40

#### 【0026】

CSRブロック122は、システム100のCSRリング上に位置する。CSRブロック122は、インターフェース管理プロセッサ（IMP）情報へのアクセス権を与え、CSRブロック122のレジスタを介してIMP動作を設定する。例えば、CSRブロック122のレジスタは、CU130の起動を有効にし、CU130動作のステータスを示し、コントローラ101のデバッグ及び／又は診断上の機能、並びに、その他の管理アクセス機能を有効にする。CSRリングは、複数のバス規格（例えば、PalmBus、AM

50

B A、A H Bなど)のうちいずれの規格を用いて実装してもかまわない。様々な実施形態では、複数(例えば、2つ)の優先割り込み信号と停止信号(例えば、HALT / INT R)とをバックエンド処理部に送出してもよい。バックエンド処理部は、コア領域への停止信号と優先割り込み信号とを同期させる。ブロック124は、コントローラ101のクロック領域へのグローバル停止入力(例えば、HALT IN)を同期させてもよい。その後、同期化されたグローバル停止入力は、CSR制御下で、コントローラ101を停止することができる。

#### 【0027】

ブロック110は、通常、制御部(CU)130と、低レベル不揮発性メモリインターフェース(LFI)132とを備える。CU130は、コマンドインターフェースを介して、コマンドを受け取り、レスポンスを送出する制御プロセッサの一例であり、通常、汎用中央演算処理装置(CPU)を備える。LFI132は、システムと1以上の不揮発性メモリデバイスとを接続する不揮発性メモリデバイスインターフェースと、制御プロセッサ及び不揮発性メモリデバイスインターフェースに接続され、コントロールストアを有するマイクロシーケンサである低レベルプログラマブルマイクロシーケンサとを備える。CU130とLFI132の低レベルプログラマブルマイクロシーケンサとは、共有メモリ(例えば、ブロック134)によって密に結合されている。CU130とLFI132の低レベルプログラマブルマイクロシーケンサとは、1以上の不揮発性メモリデバイス(例えば、図1の不揮発性記憶媒体105)に接続するシステム出力及び入力(例えば、NVM I/O)を制御することができる。CU130は、総合システムコントローラからコマンドを受け取ることができ、(i)LFI132の低レベルプログラマブルマイクロシーケンサにどのコマンドを発行するかの決定、(ii)中央システムデータレポジトリへのデータフローの制御、(iii)起こり得るエラー状態の処理、及び、(iv)コマンドの完了を示すための総合システムコントローラへのレスポンス送出を担う。

#### 【0028】

このように、制御プロセッサは、コマンドのうち特定コマンドを受け取ると、特定コマンドに従い、コントロールストア内の位置でマイクロシーケンサに実行開始させることができる。マイクロシーケンサは、不揮発性メモリデバイスインターフェースに接続された1以上の不揮発性メモリデバイスのプロトコルに従い、特定コマンドの少なくとも一部を実行することができる。そのために、マイクロシーケンサは、入力データバッファの全体状態を検出し、全体状態の検出結果に応じて、コントロールストア内の所定の位置にジャンプすることができる。ここで、制御プロセッサは、まず、複数のタイプの不揮発性メモリデバイスと互換性のある低速プロトコルを実行するようコントロールストアを制御プロセッサがプログラミングし、続いて、1以上の不揮発性メモリデバイスと互換性のあるより高速なプロトコルを実行するようコントロールストアを制御プロセッサがプログラミングすることができる。

#### 【0029】

LFI132の低レベルプログラマブルマイクロシーケンサは、取付けられた特定タイプの不揮発性メモリデバイスに対応し、かつ、制御するためのプログラムで構成されてもよい。このため、LFI132の低レベルプログラマブルマイクロシーケンサは、特定の不揮発性メモリインターフェースプロトコルに関する内容をCU130から抜き出し、より高レベルなシーケンス呼び出しをCU130に出力してもよい。CU130、LFI132の低レベルプログラマブルマイクロシーケンサ、及び、それぞれのプログラムによって、通常、総合システムコントローラは、高レベルの不揮発性メモリコントローラ101にコマンドを発行できるようになる。CU130のプログラムは、(例えば、1以上の不揮発性メモリデバイス用の)より高レベルなコマンドのスケジューリングを処理し、この高レベルコマンドをより低レベルなコマンドに分解し、この低レベルコマンドをLFI132の低レベルプログラマブルマイクロシーケンサに発行する。コマンドが完了すると、プログラムは、BEPUコントローラにレスポンスを発行する。これにより、BEPU及び/又はホスト103のその他のプロセッサは、不揮発性メモリインターフェースの内容

10

20

30

40

50

を処理する必要がない。新たな不揮発性メモリデバイスを導入しても、C U 1 3 0用とL F I 1 3 2の低レベルプログラマブルマイクロシーケンサ用の新たなプログラムを単に展開するだけで、上述したフレキシブルな手法により、新たなデバイスを使用することができる。

#### 【 0 0 3 0 】

L F I 1 3 2は、不揮発性記憶媒体からデータを受け取る際のバックプレッシャー、又は、不揮発性記憶媒体にデータを送出する際のデータ欠乏などによるデータ障害を検出することができる。また、L F I 1 3 2の低レベルプログラマブルマイクロシーケンサは、プログラムループから「抜け出し」て、例外状況に入ることができる。例外状況では、L F I 1 3 2の低レベルプログラマブルマイクロシーケンサは、第1モードとして、データの回復を検出して動作を継続する、又は、第2モードとして、C U 1 3 0への割り込みによってより高レベルの動作を再開させることができる。第2モードでは、C U 1 3 0は、L F I 1 3 2の低レベルプログラマブルマイクロシーケンサにより転送されたデータにアクセスでき、例えば、アドレス及び／又は長さを整えて、データ転送が中断されたポイントからデータ転送を再開することができる。10

#### 【 0 0 3 1 】

C U 1 3 0は、インターフェース管理プロセッサコマンドに割り込み、レスポンスを出力する。また、C U 1 3 0は、入力データバッファと出力データバッファとにアクセスでき、L F I 1 3 2を制御する。L F I 1 3 2は、不揮発性メモリI/Oにアクセスして制御し、コマンド順序を決定し、データ出力順序を決定し、そして、返信データを取り込む。C U 1 3 0の機能性のうち大部分をファームウェアに実装することにより、フレキシブル性及びこれからの不揮発性メモリタイプに対するサポートが可能となる。20

#### 【 0 0 3 2 】

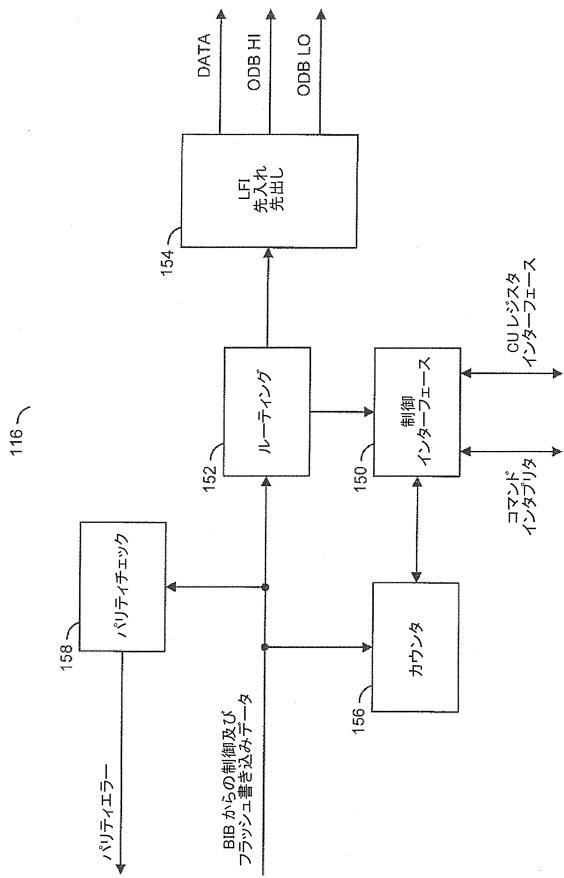

図3は、図2の出力データバッファ(ODB)116の実装例を示す図である。ある実施形態では、ODB116は、ブロック(又は回路)150と、ブロック(又は回路)152と、ブロック(又は回路)154と、ブロック(又は回路)156と、ブロック(又は回路)158とを備える。ブロック150は、通常、制御インターフェースを実装する。ブロック152は、通常、ルーティング動作を行うことができる。ブロック154は、不揮発性メモリデバイスインターフェースに出力されるデータを受け取り可能な出力データバッファの一例であり、先入れ先出し(FIFO)バッファを実装する。ブロック156は、カウンタを実装する。ブロック158は、通常、パリティチェックを行うことができる。30

#### 【 0 0 3 3 】

動作の第1モード(例えば、通常モード)では、L F I 1 3 2に受信データを直接入力するよう、制御及びルーティングをセットアップすることができる。デバッグ又はその他の高度機能のために、C Uレジスタインターフェースに受信データを直接入力するよう、制御及びルーティングをセットアップすることができる。C Uファームウェアをダウンロードするために、C U 1 3 0のコマンドインタプリタに受信データを直接入力するよう、制御及びルーティングをセットアップすることができる。例えば、ブロック154を、8ビット幅、4エントリー深度のFIFOバッファとして実装してもよい。ただし、他の深度及び幅を実装して特定の実装の設計基準を満たしてもかまわない。ブロック154は、シーケンス制御の一部として用いられる、コンフィギュラブルなH<sub>i</sub>及びL<sub>o</sub>レベル(例えば、FIFO閾値)を有している。典型的に、4深度のダブルデータレート(DDR)システムの場合は、H<sub>i</sub>は2に設定され、L<sub>o</sub>は1に設定される。4深度のシングルデータレートシステムの場合は、H<sub>i</sub>は1に設定され、L<sub>o</sub>は0に設定される。ブロック156は、ODB116に入力されたバイト数をカウントする、C UのCSRアクセス可能カウンタとして実装してもよい。また、ブロック156は、C U 1 3 0によって書き込み可能であり、正確なバイト数が書き込みデータバスから入力されたことの確認としてのデバッグの際に有用かもしれない。ブロック158は、データインターフェースのパリティチェックを行い、パリティエラーなどの例外時に割り込みをBEPUSHINGナーリングできる4050

CSR ブロック 122 にパリティエラーを報告することができる。

#### 【0034】

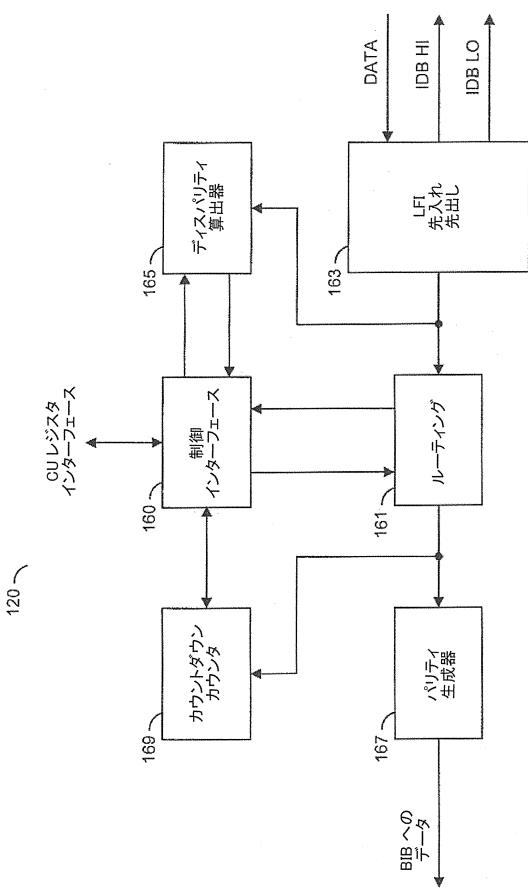

図4は、図2の入力データバッファ(IDB)120の実装例を示す図である。ある実施形態では、IDB120は、ブロック(又は回路)160と、ブロック(又は回路)161と、ブロック(又は回路)163と、ブロック(又は回路)165と、ブロック(又は回路)167と、ブロック(又は回路)169とを備える。ブロック160は、通常、制御インターフェースを実装する。ブロック161は、通常、ルーティング動作を行うことができる。ブロック163は、不揮発性メモリデバイスインターフェースから入力されたデータを受け取り可能な入力データバッファの一例であり、先入れ先出し(FIFO)バッファを実装する。ブロック165は、ディスパリティ算出器を実装する。ブロック167は、パリティ生成器を実装する。ブロック169は、カウントダウンカウンタを実装する。

#### 【0035】

IDB120は、通常、ブロック163を介して、LFIから受信データを受け取る。ある実施形態では、ブロック163を、8ビット幅、40エントリーのFIFOバッファとして実装してもよい。ただし、他の深度及び幅を適宜実装して特定の実装設計基準を満たしてもかまわない。ブロック163は、LFI132でのフロー制御において用いられる、コンフィギュラブルなHi及びLoレベル(例えば、FIFO閾値)を有している。ブロック163は、早い転送レートで重要なシステム100の往復レイテンシ(例えば、30ns)を許容し、また、FIFOバッファに受信データをバッファリングしている間に、転送開始時の時刻をメッセージのヘッダにCU130から挿入することができる。ダブルデータレートシステムに対するHi及びLoレベル(例えば、FIFO閾値)の設定例として、Hiレベルは22、Loレベルは21である。

#### 【0036】

LFI132からのデータは、通常、IDB120とBIB112とを接続する送信FIFOバッファ(図示せず)に直接入力される。また、LFI132からのデータは、制御インターフェース160のCUレジスタインターフェースを用いてCU130により読み出すことができる(例えば、この機能は、データがCU130で使用される、不揮発性メモリデバイスのレジスタ読み出し、ステータス読み出しなどに用いることができる)。また、CUレジスタインターフェースを用いて、データをCU130からBIB112へ送出することもできる(例えば、この機能は、データヘッダ/トレーラに用いることができる)。

#### 【0037】

ブロック165は、通常、ランニングディスパリティ算出器を実装する。ある実施形態では、ランニングディスパリティ算出器は、読み込みデータストリーム内の0のビット数よりも1のビット数が多い分の累積数を示す符号付き20ビットを保持する。ディスパリティ計算の例は、以下の(式1)で示される。

#### 【0038】

$$\text{ディスパリティ} = 1 \text{ に設定されたビット総数} - (\text{ビット総数} / 2) \quad (\text{式1})$$

#### 【0039】

ディスパリティ値が20ビットの正又は負の最大値に達すれば、ディスパリティ値は飽和して一定値になる。不揮発性メモリデバイスからの読み込みデータが既知の予測ディスパリティを有する場合は、ディスパリティ算出器を用いて、少なくとも部分的に、読み込みデータが有効かどうかを判断する。1つ目の例として、不揮発性メモリデバイスからの読み込みデータが暗号化されていて「0」と「1」の分布が統計的に半々ならば、ディスパリティは0に近いと予測される。2つ目の例として、NANDフラッシュなどの不揮発性メモリデバイスが、全て「1」の消去状態にあるとする。ディスパリティ計算により、読み込んだデータビットの実質全てが1の値であると示されれば、おそらく、消去ページが読み込まれたものと考えられる。

#### 【0040】

10

20

30

40

50

データ読み込みが完了すると、ディスパリティ値は C U 1 3 0 によって読み出されて、データトレーラに含められるか、又は、レスポンスとして B E P U に返される。C U 1 3 0 は、通例、データ転送開始前にディスパリティ値をクリアするはずである。送信データストリームは、ブロック 1 6 7 で保護されたパリティである。

#### 【 0 0 4 1 】

ブロック 1 6 9 は、通常、C S R アクセス可能カウントダウンカウンタを実装する。ブロック 1 6 9 は、I D B 1 2 0 から送出されるバイト数をカウントダウンする。これは転送の長さに設定することができ、転送終了時に 0 になるようカウントダウンされる。また、ブロック 1 6 9 は、C U 1 3 0 のC S R レジスタによりプログラミングされ、転送開始 / 終了時に第 1 / 最終の表示（例えば、フレーミング情報を与えるサイドバンド信号）を生成することができる。カウンタが 0 になった後、第 2 C S R レジスタを用いてブロック 1 6 9 を初期設定する。10

#### 【 0 0 4 2 】

B I B 1 1 2 への送信データが C U 1 3 0 によって生成される場合（例えば、データヘッダ及びトレーラ用）、B I B 1 1 2 への第 1 出力と最終出力も C U 1 3 0 によって制御される。典型的な読み込みでは、C U 1 3 0 は、まず、I D B 1 2 0 を「C U から」モードにして、L F I 1 3 2 で読み込みコマンドを開始し、そして、ヘッダを B I B 1 1 2 へ転送する。そして、L F I 1 3 2 からのデータとブロック 1 6 3 内のデータとを B E P U に転送するよう、I D B 1 2 0 を「通常」モードにする。最後に、C U 1 3 0 は、必要であればトレーラを生成する。20

#### 【 0 0 4 3 】

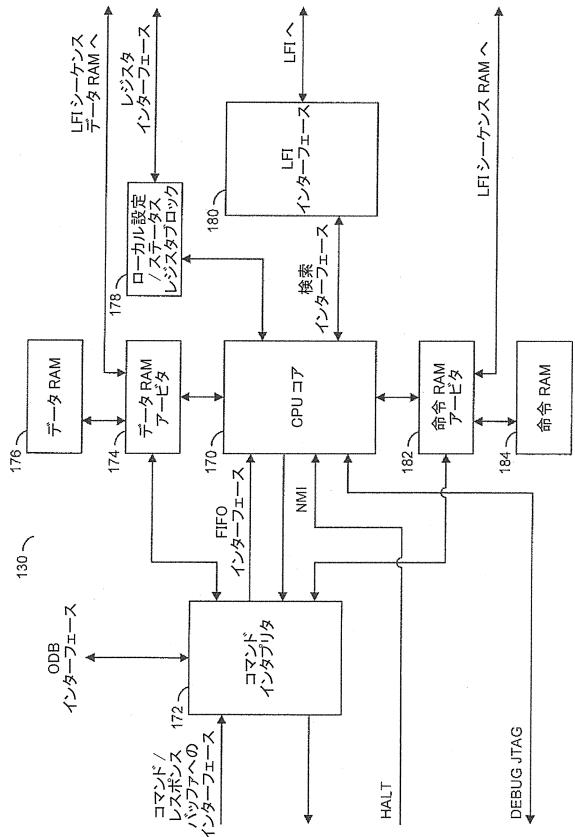

図 5 は、図 2 の制御部（C U ）1 3 0 の実装例を示す図である。C U 1 3 0 は、通常、コントローラ 1 0 1 のマイクロプロセッサベース監視制御部を実装する。C U 1 3 0 は、出力バス（O B ）からコマンドを受け取り、コマンドスケジューリングと優先順位付けとを行う。ある実施形態では、C U 1 3 0 は、ブロック（又は回路）1 7 0 と、ブロック（又は回路）1 7 2 と、ブロック（又は回路）1 7 4 と、ブロック（又は回路）1 7 6 と、ブロック（又は回路）1 7 8 と、ブロック（又は回路）1 8 0 と、ブロック（又は回路）1 8 2 と、ブロック（又は回路）1 8 4 とを備える。ブロック 1 7 0 は、通常、C P U （中央演算処理装置）コアを備える。ブロック 1 7 2 は、通常、コマンドインターフェースを実装する。ブロック 1 7 4 は、アービタを実装する。ブロック 1 7 6 は、データを格納するランダムアクセスメモリ（R A M ）を実装する。ブロック 1 7 8 は、ローカル設定 / ステータスレジスタ（C S R ）ブロックを実装する。ブロック 1 8 0 は、L F I 1 3 2 とのインターフェースを実装する。ブロック 1 8 2 は、アービタを実装する。ブロック 1 8 4 は、命令を格納するランダムアクセスメモリ（R A M ）を実装する。30

#### 【 0 0 4 4 】

スタートアップ時、C P U 1 7 0 は、ブロック 1 7 8 のC S R レジスタによりリセット状態に保たれる。命令 R A M 1 8 4 と L F I 1 3 2 のシーケンス R A M とデータ R A M 1 7 6 との初期状態をプログラミングするよう、I M P コマンドが B E P U によって発行される。初期状態は、通常、システム R O M （図示せず）から入手する。初期プログラミングの後、リセット状態が解除され、C P U 1 7 0 はその初期ファームウェアを実行開始する。ファームウェアにより、C P U 1 7 0 は、B E P U から発行されたコマンドに応答することができる。初期動作状態の間、B E P U は、不揮発性メモリデバイスからバックエンドバッファ（図示せず）に最終動作コードをもってきてもよい。最終動作コードは、C P U 1 7 0 だけでなくシステム 1 0 0 上の他のC P U も設定するために用いられる。一例として、この段階で、不揮発性メモリに格納されたファームウェアの性能を最適化したものが C U コードをリロードする可能性がある。これは、通常、データ転送として発生し、I M P コマンドを用いて、命令 R A M 1 8 4 、データ R A M 1 7 6 、及び / 又は、L F I 1 3 2 のシーケンス R A M に受信 I D B データを直接入力する。一般に、C U 1 3 0 は、主な動作コードのロード中はリセット状態である。40

#### 【 0 0 4 5 】

データRAM176、命令RAM184、及び、LFI132のシーケンスRAMにIMPコマンドがアクセスできるよう、アービタ182とアービタ174とをCPU170のRAMインターフェース上で用いてもよい。一例として、CPU170のストールメカニズムを利用しててもよい。これにより、IMPコマンドインタプリタ172に優先権が与えられる。ただし、CPU170によるアクセス以外の、データRAM176、命令RAM184、及び、LFI132のシーケンスRAMへのアクセスは、初期設定時にしか発生しないと考えられる。

#### 【0046】

また、CPU170は、BEPUからのメッセージを渡し、かつ、BEPUにレスポンスを返すための入力IFOインターフェース及び出力IFOインターフェースを備えてもよい。また、出力IFOインターフェースは、（例えば、ホスト103の）ダイレクトメモリアクセス(DMA)エンジンにメッセージを渡してデータ転送動作を開始するためにも用いられる。10

#### 【0047】

CPU170のインターフェースは、ローカルCSRにアクセスし、LFI132にコマンドを発行するために用いられる。テンシリカCPUを用いた実施形態では、インターフェースはTIE(Tensilica Instruction Extension)検索インターフェースである。グローバル停止信号（例えば、電源障害又はその他の異常事態が生じた場合にホスト103から送出される信号）を用いて、CPUコア170のノンマスカブル割り込み(NMI)を発生させてもよい。20

#### 【0048】

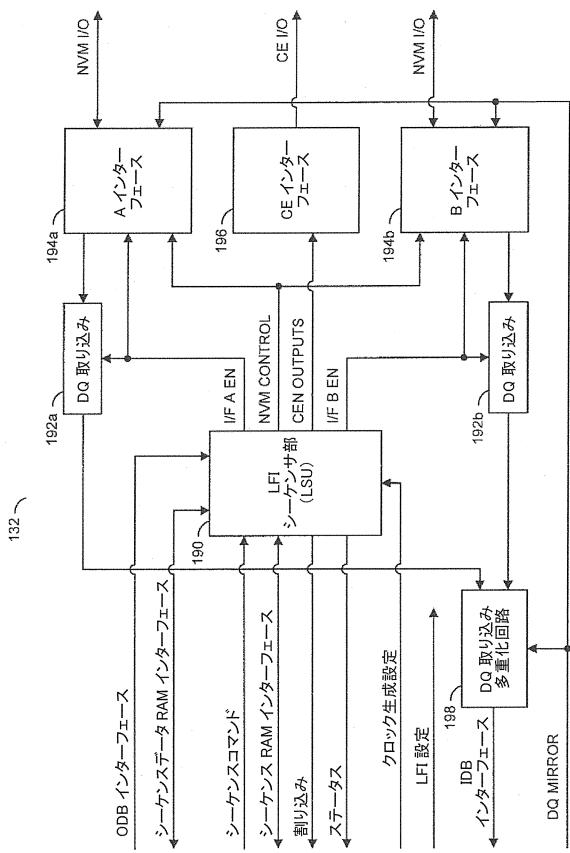

図6は、図2の低レベル不揮発性メモリインターフェース(LFI)132の実装例を示す図である。LFI132は、不揮発性メモリインターフェースを低レベル制御する。LFI132は、いかなる不揮発性メモリインターフェースプロトコルにもコンフィギュラブルに設計されたプログラマブルシーケンスエンジンを備える。使用されるシーケンスは、CU130によって設定され、CU130により与えられたコマンドで実行される。また、CU130によるプログラミング及びシーケンスによるアクセスが可能なシーケンスデータ領域が存在するため、ジェネリックシーケンスをセットアップでき、シーケンス自体を変更することなくデータをシーケンスに関連付けることができる。

#### 【0049】

ある実施形態では、1つの物理インターフェースだけではなく2以上の物理インターフェースに対応している。例えば、2つの物理インターフェース（例えば、A及びB）と共に、LFI132は、ブロック（又は回路）190と、ブロック（又は回路）192aと、ブロック（又は回路）192bと、ブロック（又は回路）194aと、ブロック（又は回路）194bと、ブロック（又は回路）196と、ブロック（又は回路）198とを備えてもよい。ブロック190は、通常、低レベル不揮発性メモリインターフェース(LFI)シーケンサ部(LSU)を備える。ブロック192a及び192bは、通常、DQ取り込みブロックを実装する。ブロック194a及びブロック194bは、それぞれ、A不揮発性メモリインターフェース及びB不揮発性メモリインターフェースを実装する。ブロック196は、チップイネーブル(CE)インターフェースを実装する。ブロック198は、2つのDQ取り込みブロック192a及び192bから選択する多重化回路を実装する。ブロック192a及び192bと、ブロック196とは、複数のデータ入出力ピンと複数の制御入出力ピンとを備える不揮発性メモリデバイスインターフェースの一例である。

#### 【0050】

LFIシーケンサ部(LSU)190は、制御プロセッサと不揮発性メモリデバイスインターフェースとに接続され、コントロールストアを有するマイクロシーケンサの一例であり、シーケンスを実行して、不揮発性メモリコマンドの出力、つまり、書き込みデータ転送及び読み出しデータ転送を指示する。マイクロシーケンサは、不揮発性メモリデバイスインターフェースの制御入出力ピンとデータ入出力ピンとの状態を変更して、プロトコ4050

ルに従い特定コマンドを実行することができる。シーケンスRAMインターフェースにより、LSU190の内部シーケシングメモリをシーケシング開始前にセットアップすることができ、また、CU130により動的にプログラミングされたシーケンスを内部シーケシングメモリで保持することもできる。そして、LSU190のシーケンスコマンドインターフェース上でシーケンスコマンドを発行することができる。コマンドがどのインターフェース向けなのでインターフェース選択（例えば、信号I/F A EN及び信号I/F B EN）はプログラミングされ、この選択によってコマンドは適切なインターフェースに入力される。ある実施形態及び／又は利用状況では、各コマンドは1つのインターフェースに入力される。別の実施形態及び／又は利用状況では、少なくともいくつかのコマンド（例えば、リセットコマンド）が複数のインターフェースに入力される。チップイネーブル（CE）インターフェース（例えば、信号CEN OUTPUTS）により、不揮発性メモリインターフェースのうち1つに取付けられたダイを選択するためのCE出力をフル制御することができる。ある実施形態では、最大8CEまでの設定に対応している。ダイは、どの不揮発性メモリインターフェースでも取付けることができる。

10

#### 【0051】

DQ取り込みブロック192a及び192bは、DQSを用いた高速データ取り込みを行い、非同期モードに対するシーケンス遅延もとらえる。DQ\_Mirror信号は、DQ出力と取込データとのミラーリングを制御する。ミラーリングでは、ビット0を7と、1を6と、2を5と、3を4と入れ替える。これは、基板レイアウトの問題を軽減するいくつかの構造で行われるものであり、コントローラによって処理される必要がある。ミラーモードは、コマンドがLFI132に発行される前にCU130によって選択される。送信ミラーリングは、送信インターフェースで行われ、受信ミラーリングは、DQ取り込み多重化回路198のDQ取り込みに続いて行われる。

20

#### 【0052】

LFI132は、通常、プログラマブルシーケンスエンジンと、I/Oピン出力ブロック群と、データ取り込みブロック群とを備える。シーケンスエンジンは、通常、I/Oピンに取付けられた特定の不揮発性メモリデバイスの不揮発性メモリプロトコルを実行可能なシーケンス群でプログラミングされる。シーケンスは、シーケンスマモリ内の複数の位置で開始する命令群から構成されている。例えば、LFI132をプログラミングして実行する動作ごとにそれぞれの開始位置が存在する。ある実施形態では、シーケンスマモリは、512の32ビット位置として実装される。シーケンスの実行は、コマンドインターフェース上でコマンドを発行することにより開始される。コマンドは、通常、ジャンプするためのシーケンスマモリのアドレスと、シーケンス内の命令のうちいくつかが利用できる1バイトのコマンドデータとを含む。ただし、このコマンドデータは利用されない場合もある。

30

#### 【0053】

また、インデックスレジスタを用いて間接アドレス指定されるシーケンステータRAMも設けられる。インデックスは、MODE命令を用いて設定され、通常、コマンドデータから得られる値に設定される。このように、コマンドシーケンスに関連付けられたデータはいずれもシーケンステータRAMに設定できるため、シーケンス自体を変更する必要はない。一例として、5バイトのアドレスを有する読み込みコマンドを挙げる。アドレスのバイトはシーケンステータRAMの連続した位置に置かれ、シーケンスマモリ内の読み込みコマンドシーケンスのアドレスと、シーケンステータRAM内のアドレスの1番目のバイトのアドレスとを含んだコマンドが発行される。シーケンスは、インデックスレジスタを設定してから、必要なシーケンスを実行してアドレスを送出し、このアドレスシーケンスをアドレスのバイトごとに繰り返す。命令により、インデックスレジスタはインクリメントされる（メモリの最後の次は先頭に戻る）。ただし、WIG命令（不揮発性メモリデバイスに接続されたI/Oピンをワイグルするのに用いられる）の場合は、インクリメントはオプションである。

40

#### 【0054】

停止を引き起こす命令を受けるまで、シーケンスは実行される。停止命令はシーケンス実行を終了させ、LFIは、次のコマンドが届くのを待つて何もアクションを起こさない状態になる。不揮発性メモリデバイスに対するアクションの実行は、複数のシーケンス呼び出しで構成してもよい。例えば、1シーケンスを呼び出してデバイスを選択し、別のシーケンス呼び出しで読み込みを発行し、最終シーケンスでデバイス選択の解除を行うことができるであろう。

#### 【0055】

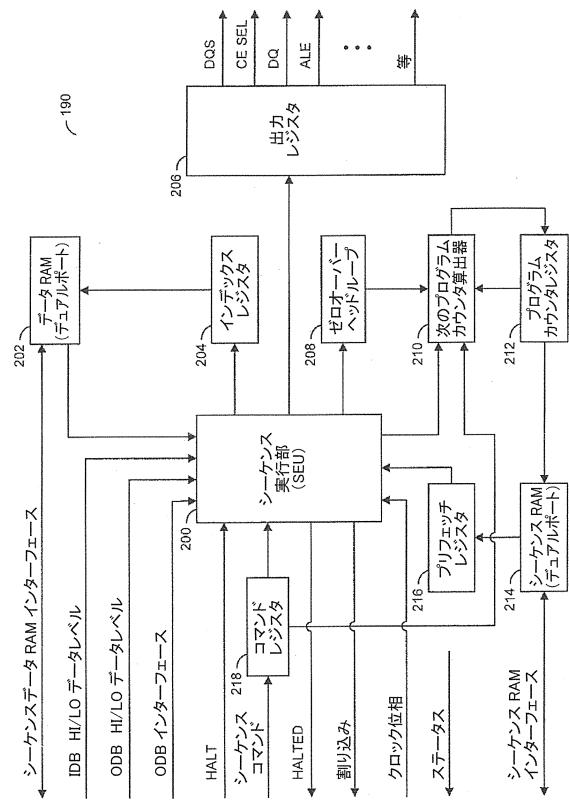

図7は、図6の低レベル不揮発性メモリインターフェース(LFI)マイクロシーケンサ部(LSU)190の実装例を示す図である。ある実施形態では、LSU190は、ブロック(又は回路)200と、ブロック(又は回路)202と、ブロック(又は回路)204と、ブロック(又は回路)206と、ブロック(又は回路)208と、ブロック(又は回路)210と、ブロック(又は回路)212と、ブロック(又は回路)214と、ブロック(又は回路)216と、ブロック(又は回路)218とを備える。ブロック200は、通常、シーケンス実行部(SEU)を備える。ブロック202は、通常、シーケンスデータを格納するランダムアクセスメモリ(RAM)(例えば、シーケンスデータRAM)を実装する。一例として、シーケンスデータRAM202をデュアルポートメモリとして実装してもよい。ブロック204は、インデックスレジスタを実装する。ブロック206は、多数の出力レジスタを実装する。ブロック208は、ゼロオーバーヘッドラープ(ZOL)レジスタを実装する。ブロック210は、通常、次のプログラムカウンタ(PC)の算出を行う。ブロック212は、プログラムカウンタ(PC)レジスタを実装する。ブロック214は、マイクロシーケンサで読み取り可能、かつ、制御プロセッサで書き込み可能なコントロールストアの一例であり、通常、シーケンスを格納するランダムアクセスメモリ(RAM)(例えば、シーケンスRAM)を実装する。一例として、シーケンスRAM214をデュアルポートメモリとして実装してもよい。ブロック216は、プリフェッチャレジスタを実装する。ブロック218は、コマンドレジスタを実装する。

10

20

30

#### 【0056】

シーケンスRAM214を初期化してから、いずれのコマンドも実行する必要がある。シーケンスRAM214の初期化は、通常、最初の不揮発性メモリ読み込みを行うためにスタートアップ時に一度行われ、二度目は、不揮発性メモリデバイスから主な実行コードをロードしたときに行われる。ある実施形態では、シーケンスRAM214を32ビット幅(+ECCビット)で512ワード深度のデュアルポートRAMとして実装して、シーケンスの実行中にCU130からアクセスできようにもよい。ある実施形態では、シーケンスアドレスは9ビットである。ただし、他のメモリ仕様を適宜実装して特定の実装の設計基準を満たしてもかまわない。このように、コントロールストアは、不揮発性メモリデバイスインターフェースに取付けられた1以上の不揮発性メモリデバイスに関連付けられている1以上のプロトコルを実行するよう制御プロセッサによってプログラミングされる。

#### 【0057】

シーケンスデータRAM202により、CU130は、インデックスレジスタ204を用いたコマンドでアクセスできる様々なコマンド値を設定できる。様々なコマンド値の設定は、コマンド/アドレスシーケンスをセットアップするような動作に用いることができる。ある実施形態では、シーケンスデータRAM202は、CU130から32ビットワード単位としてではなく、インデックスレジスタ204により1バイト単位としてアドレス指定される。ある実施形態では、シーケンスデータRAM202は、64バイト(16ワード)として実装される。ただし、他のメモリ仕様を適宜実装して特定の実装の設計基準を満たしてもかまわない。シーケンスデータRAM202からデータはプリフェッチされるので、偽ECCエラーの可能性をなくすため、シーケンスデータRAM202全体を使用前に初期化すべきである。

40

#### 【0058】

PCレジスタ212には、カレントシーケンスポインタが保持されている。カレントシ

50

ーケンスポインタは、通常、次のシーケンス命令をフェッチするためにインクリメント器 210を通る。ZOLレジスタ208は、シングルレベルのゼロオーバーヘッドルーピングに対応している。出力レジスタ206は、不揮発性メモリインターフェースに接続し、その動作を制御する。

#### 【0059】

シーケンスRAM214とシーケンスデータRAM202とは共にECC保護されており、CU130のメモリマップ内に存在する。ECCエラーはCU130への割り込みを発生させるため、レジスタを読み取って、エラー訂正が可能かどうか、また、どのRAMがエラー状態だったのかを判断することができる。訂正可能なエラーはいずれも、通常、メモリのリードスクラップとなる。シーケンスRAMの読み込み中に訂正不能なエラーが生じた場合は、シーケンスも直ちに停止される。10

#### 【0060】

外部信号（例えば、HALT）は、CU130によりアサートされて、シーケンス実行部200の動作をいつでも停止することができる。通常、シーケンス実行部200の停止実行により、カレントシーケンスはカレント位置で直ちに終了する。新たなシーケンスを開始するためには、新たなコマンドを発行する必要がある。シーケンス実行部200の内部ステータスは、CU130で利用できる。

#### 【0061】

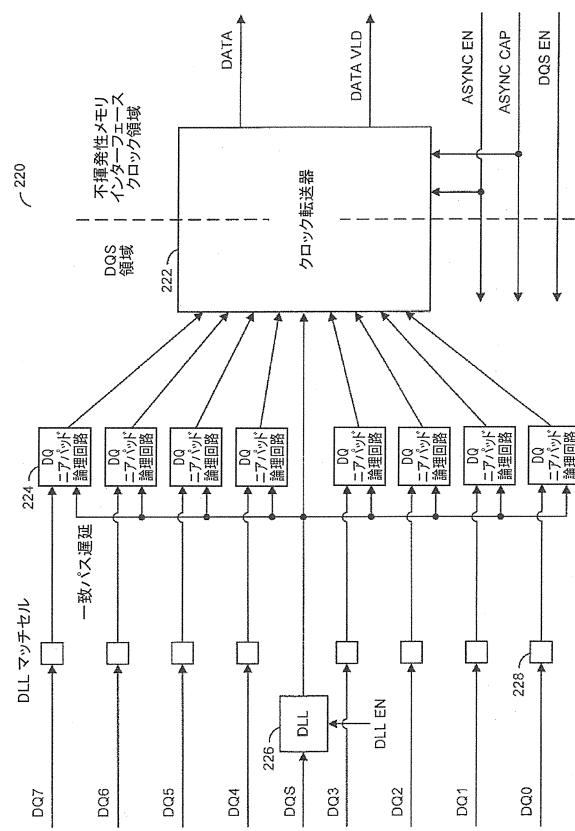

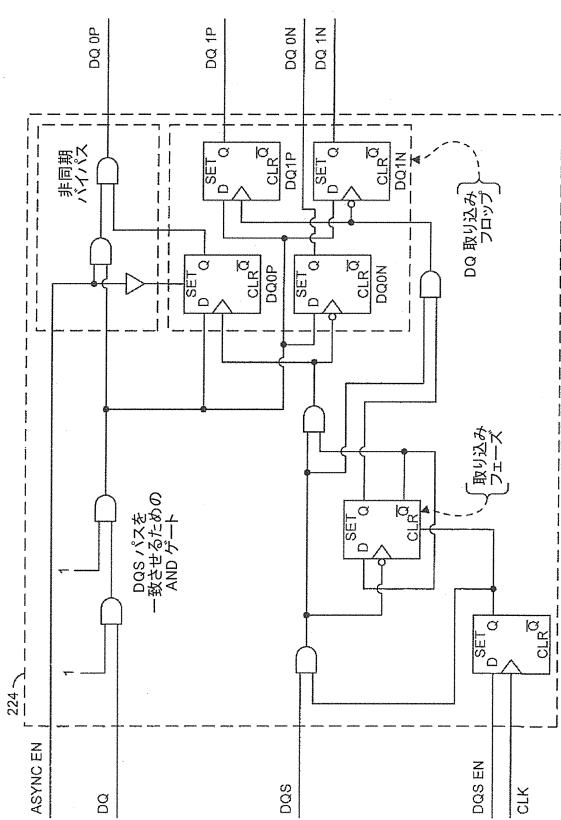

図8は、DQ取り込みブロック220の実装例を示す図である。DQ取り込みブロック220を用いて、図6のDQ取り込みブロック192aと192bとを実装してもよい。20

ある実施形態では、DQ取り込みブロック220は、クロック転送ブロック222と、複数のDQニアパッド論理回路ブロック224と、DLLブロック226と、複数のマッチセル228とを備える。ニアパッド論理回路（NPL）は、パッド付近に配置されたシリコンマクロブロックを備える。NPLブロックは、インターフェース論理回路上でタイミングを厳密に制御することを可能にする。各NPLブロックは、対応するパッドから一定の距離離して配置される。DQS入力は、DLLブロック226のスレーブモジュールを介して入力される。DLLブロック226のスレーブモジュールは、DQSサイクルの4分の1の遅延をDQS信号に挿入する。各DQNPLブロック224に対するDQSバス遅延は、同じNPLブロックに対するDQ遅延と一致するはずである。DQNPLブロック224は、後のDQSエッジ上でDQ値を4つ取り込む。4つのDQ値は、不揮発性メモリインターフェースのクロック領域に値を転送するクロック転送ブロック222に出力される。30

#### 【0062】

図9は、図8のDQ取り込みニアパッド論理回路（DQ\_NPL）ブロック224の実装例を示す図である。ある実施形態では、DQ\_NPLブロック224は、取り込みフェーズフロップと、複数のDQ取り込みフロップ（例えば、DQ0P、DQ0N、DQ1P、DQ1N）とを備えている。読み込み転送の開始前は、信号（例えば、DQS\_EN）はLOWである。これにより、いかなるDQSグリッヂもゲートオフされ、取り込みフェーズフロップはフェーズ0で保持される。1つ目の立ち上がりDQSエッジはDQ0Pフロップに取り込まれ、1つ目の立ち下がりエッジはDQ0Nフロップに取り込まれる。また、1つ目の立ち下がりエッジは取り込みフェーズを切り替え、次の2つのDQSエッジはDQ1PとDQ1Nとにそれぞれ取り込まれる。データ転送中、サイクルは4DQSエッジごとに繰り返される。40

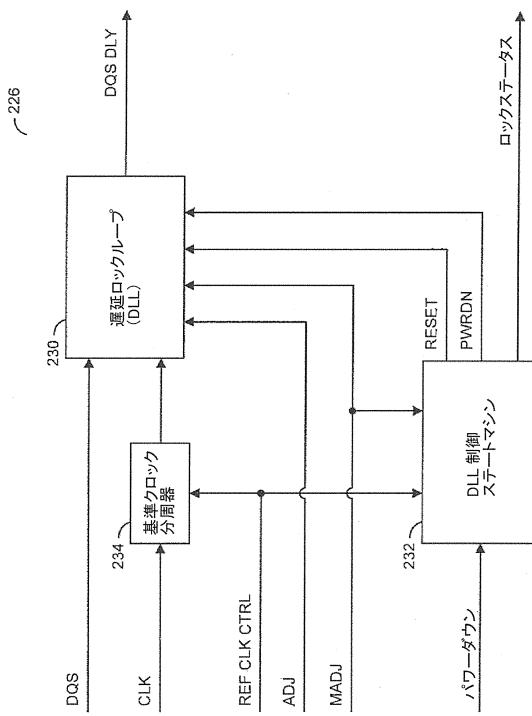

#### 【0063】

図10は、図8のDLLブロック226の実装例を示す図である。ある実施形態では、DLLブロック226は、遅延ロックループ（DLL）230と、制御ステートマシン（FSM）232とを備える。DLL230は、マスター部とスレーブ部とを備える。DLL230のマスター部は、入力基準クロックにロックする。DLL230のスレーブ部は、マスター基準クロックのプログラマブル分割により、任意の信号（例えば、DQS）を遅延させる。ある実施形態では、エッジアラインされたDQデータを取り込むために、受50

信号 DQS を DQS 周期の 4 分の 1 遅延させる必要がある。 DLL ブロック 226 は、入力基準サイクルにロックする。入力基準サイクルは、コントローラ 101 のクロック（例えば、CLK）、又は、コントローラクロックを分周したもの（例えば、基準クロック分周器 234 で生成）でもよい。一般に、基準クロックは、送信 DQS と同じ周波数、又は、2 倍の周波数に設定されるものである。挿入される遅延は、一般的に、DQS 周波数の約 4 分の 1 になるようプログラミングされる。DLL 230 のスレーブ部の遅延は、以下の（式 2）に基づき算出してもよい。

## 【0064】

$$\text{Delay} = T_f + \text{Trref} * ((\text{ADJ} + \text{ADJoff}) / \text{MADJ}) \quad (\text{式 } 2)$$

## 【0065】

ここで、 $T_f$  は固定オフセット遅延、 $\text{Trref}$  は基準クロック周期、 $\text{ADJ}$  はプログラム調整オフセット、 $\text{ADJoff}$  は、固定コードオフセット（例えば 34）、 $\text{MADJ}$  は通常 160 に設定されるマスター調整オフセット（ただし、76、・・・、255 の範囲の値に変更可能）である。通常、固定オフセット遅延  $T_f$  は、DQ ライン上で用いられるマッチセル 228 で合わせられるため、無視することができる。したがって、（例えば、マッチセルを用いることにより） $T_f$  を消去し、 $\text{ADJ}$  について解を求める（式 3）が得られる。

## 【0066】

$$\text{ADJ} = \text{MADJ} * (\text{Delay} / \text{Trref} - \text{ADJoff}) \quad (\text{式 } 3)$$

## 【0067】

例えば 400MT/s の動作条件の場合、DQS 周波数は 200MHz、コントローラクロックは 400MHz である。ある実施形態では、400MHz クロックを DLL に直接入力することができ、信号 DQS を基準クロックの 2 分の 1 周期（DQS 周期の 4 分の 1 に相当）遅延させることができる。別の実施形態では、コントローラクロックを 200MHz に分周することができ、信号 DQS を基準クロック周期の 4 分の 1 遅延させる。

## 【0068】

また、ソフトウェアにトレーニング方式を実装することも可能である。このようなトレーニング方式を有する実施形態では、既知のパターンを不揮発性メモリデバイスから読み込む間に、 $\text{ADJ}$  値はロー設定からハイ設定にスイープされる。最終的に $\text{ADJ}$  は、読み込み中の正しいデータとなる中央値に設定される。基準クロック分周器若しくは $\text{MADJ}$  の何らかの変更、又は、パワーダウンが、最小 1us 間 DLL をリセットするのに必要となる。制御 FSM 232 は、プログラミングされた回数のクロックサイクルの間（例えば、400MHz の 1us 周期の場合、デフォルトは 400）、DLL 230 をリセット状態に保持する。DLL 230 が実行可能になった後、ロックステータスは 500 基準クロック分にアサートされ、読み込み動作が開始される前に、この状態をファームウェアで確認することができる。

## 【0069】

DLL ブロック 226 の制御レジスタは、（例えば、BEPU から）CSR リングを介して、又は、CU 130 から局所的にアクセス及び設定可能である。ローカルアクセスは、トレーニング型機能（必要であれば）、又は、微粒子パワーダウン制御に用いられる。一般に、 $\text{DLL}$  値は、コンフィグレーションレコードから設定されるので、通常の動作中に調整する必要はない。節電のために、 $\text{DLL}$  制御 FSM 232 に関連付けられたパワーダウン要求レジスタを設定することができる。 $\text{DLL}$  230 は、DQS 入力を使用する不揮発性メモリ読み込みモード（例えば、ONFI 2/3 の DDR モード及びトグルモード）に対する読み込み動作中にのみ用いられる。パワーダウンから抜けると続いてリセット及びロックシーケンスが起動されるため、動的パワーダウンは読み込み性能に影響を及ぼす可能性がある。チップをリセットするとすぐに、 $\text{DLL}$  230 は、通常、パワーダウンモードになる。

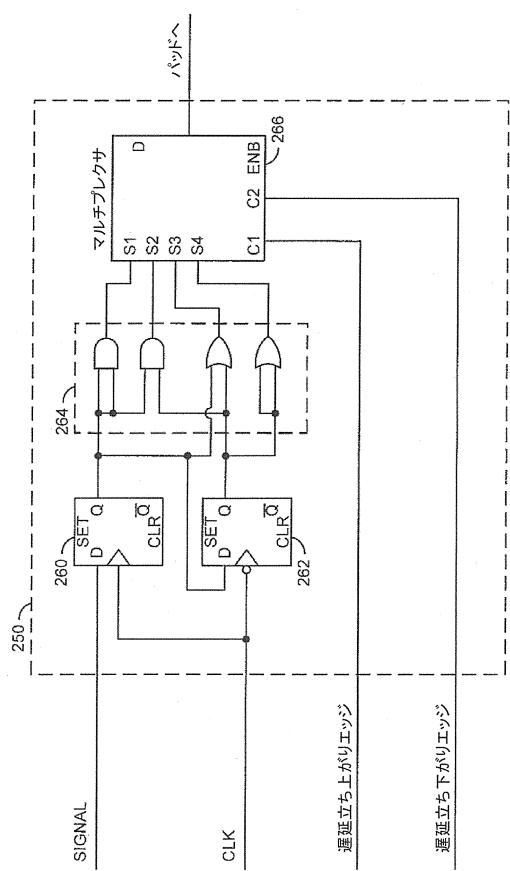

## 【0070】

図 11 は、出力インターフェースニアパッド論理回路（NPL）ブロック 250 の実装

10

20

30

40

50

例を示す図である。各送信信号は、出力インターフェースNPLブロック250を介して出力される。MPLブロック250は、送信信号をクロック（例えば、CLK）にタイミングを合わせさせ、オプションで2分の1サイクルの遅延を送信信号の立ち上がり／立ち下がりエッジに加える。各送信信号に対する遅延は、CSRで設定可能である。各NPLブロック250は、各コントローラ101インスタンスからの全出力にわたりNPLブロック250からパッドへの遅延が一致する対応パッド近くに配置されるべきである。ある実施形態では、MPL250は、フリップフロップ260と、フリップフロップ262と、組み合わせ論理回路264と、マルチプレクサ266とを備える。ある実施形態では、フリップフロップ260及び262はD型フロップとして実装される。ある実施形態では、組み合わせ論理回路264は、ANDゲート、ORゲート、及び／又は、NOTゲートを備えてもよい。NPL250内において、マルチプレクサ266への可能な各パスは、できるだけ厳密に合わせるべきである。

#### 【0071】

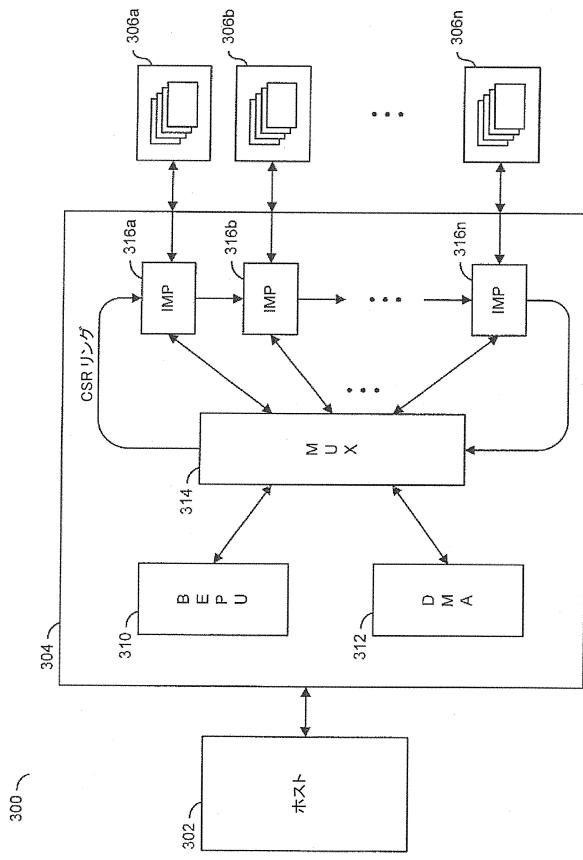

図12は、本発明の実施形態に係るマルチチャネル型不揮発性メモリ制御システムを示す図である。ある実施形態では、不揮発性メモリシステム300は、ホスト302と、不揮発性メモリコントローラサブシステム304と、複数の不揮発性記憶媒体306a～306nとを備えてもよい。ホスト302は、コマンドインターフェースを介して不揮発性メモリコントローラサブシステム304と情報のやりとりを行う。このコマンドインターフェースは、ホスト302と不揮発性メモリコントローラサブシステム304との間でコマンドとレスポンスとを転送する。不揮発性記憶媒体306a～306nはそれぞれ、不揮発性メモリコントローラサブシステム304のチャネルに接続されてもよい。

#### 【0072】

ある実施形態では、不揮発性メモリコントローラサブシステム304は、ブロック310と、ブロック312と、ブロック314と、複数のブロック316a～316nとを備えてもよい。ブロック310は、バックエンド処理部(BEPU)、及び／又は、不揮発性メモリコントローラサブシステム304の他のプロセッサとを備えてもよい。ブロック312は、ダイレクトメモリアクセス(DMA)エンジン、又は、不揮発性メモリコントローラサブシステム304のエンジンを備えてもよい。ブロック314は、不揮発性メモリコントローラサブシステム304の多重化サブシステムを実装してもよい。ブロック314は、ブロック316a～316nと、ブロック310及びブロック312とを接続させてもよい。ブロック316a～316nは、上述のコントローラ101と同様に実装されたインターフェース管理プロセッサを備えてもよい。ブロック316a～316nは、CSRリングとそれぞれのコマンドインターフェースとによってブロック314に接続されてもよい。また、ブロック316a～316nは、各ブロック316a～316nをそれぞれの不揮発性記憶媒体306a～306nに接続する不揮発性メモリインターフェースを有する。

#### 【0073】

動詞と組み合わせてここで用いられる「してもよい」及び「通常」という用語は、説明は例示であり、開示に記載された具体例だけでなくこの開示に基づいて導き出される別の例も包含するよう十分に広義であるという意図を伝えるためのものである。ここで用いられたような「してもよい」及び「通常」という用語は、必ずしも、対応要素の省略の望ましさ又は可能性を暗に意味すると受け取られるべきではない。

#### 【0074】

図1～12に示された機能は、当業者に明らかなように、明細書の教示に従ってプログラミングされた1以上の、従来の汎用プロセッサ、デジタルコンピュータ、マイクロプロセッサ、マイクロコントローラ、RISC(reduced instruction set computer)プロセッサ、CISC(complex instruction set computer)プロセッサ、SIMD(single instruction multiple data)プロセッサ、シグナルプロセッサ、中央演算処理装置(CPU)、算術論理装置(ALU)、ビデオデジタル信号プロセッサ(VD

10

20

30

40

50

S P )、及び／又は、類似の計算器を用いて実装（例えば、モデル化）されてもよい。また、適切なソフトウェア、ファームウェア、コーディング、ルーチン、命令、オペコード、マイクロコード、及び／又は、プログラムモジュールは、当業者に明らかのように、開示の教示に基づいて当業者であるプログラマにより容易に作成されてもよい。通常、ソフトウェアは、マシン実装の1以上のプロセッサにより、1つ又はいくつかの媒体から実行される。

#### 【0075】

また、本発明の実施形態は、ASIC(application specific integrated circuit)、プラットフォームASIC、FPGA(field programmable gate array)、PLD(programmable logic device)、CPLD(complex programmable logic device)、SOG型(sea-of-gate)、RFIC(radio frequency integrated circuit)、ASSP(application specific standard product)、1以上のモノリシック集積回路、フリップチップモジュール及び／又はマルチチップモジュールとして構成された1以上のチップ又はダイを準備することによって、又は、ここで記載したように従来の素子回路の適切なネットワークを相互接続することによって実装されてもよい。これらの変形例も、当業者には容易に明らかであろう。

#### 【0076】

また、本発明の実施形態は、マシンをプログラミングして本発明に係る1以上のプロセス又は方法を実行するために用いられる命令を含む記憶媒体及び／又は伝送媒体でもよいコンピュータ製品を含んでもよい。マシンによりコンピュータ製品に含められた命令を周辺回路の動作とともに実行すると、入力データは、音声及び／又は視覚表現などの代表的な物体又は物質である記録媒体及び／又は1以上の出力信号上の1以上のファイルに変換されてもよい。記憶媒体は、フロッピー(登録商標)ディスク、ハードドライブ、磁気ディスク、光ディスク、CD-ROM、DVD、光磁気ディスクなどのディスク、及び、ROM(read-only memory)、RAM(random access memory)、EPROM(erasable programmable ROM)、EEPROM(electrically erasable programmable ROM)、UVPROM(ultra-violet erasable programmable ROM)、フラッシュメモリ、磁気カード、光カード、及び／又は、電子命令を格納するのに適した媒体などの回路を備えるが、これらに限定されるものではない。

#### 【0077】

本発明の構成要素は、1以上の、デバイス、ユニット、コンポーネント、システム、マシン、及び／又は、装置の一部又は全てを形成してもよい。デバイスは、サーバ、ワークステーション、ストレージアレイコントローラ、ストレージシステム、パーソナルコンピュータ、ラップトップコンピュータ、ノートブックコンピュータ、手のひらサイズコンピュータ、個人用デジタル情報端末、携帯用電子デバイス、バッテリー駆動デバイス、セットトップボックス、エンコーダ、エコーダ、トランスコーダ、コンプレッサ、デコンプレッサ、プリプロセッサ、ポストプロセッサ、トランスマッタ、レシーバ、トランシーバ、暗号回路、携帯電話、デジタルカメラ、位置及び／又はナビゲーションシステム、医用機器、ヘッドアップディスプレイ、ワイヤレスデバイス、音声記録、音声記憶及び／又は音声再生装置、映像記録、映像記憶及び／又は映像再生装置、ゲーム機、周辺機器、及び／又は、マルチチップモジュールなどでもよいが、これらに限定されるものではない。本発明の構成要素は、特定の適用基準を満たす別のタイプのデバイスにおいて実装されてもよいと当業者に理解されよう。

#### 【0078】

本発明の内容は、その実施形態を参照しながら具体的に示して説明してきたが、本発明の範囲から逸脱することなく形態及び詳細の様々な変更を行ってもよいと当業者に理解さ

10

20

30

40

50

れよう。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【 図 7 】

【 図 8 】

【 四 9 】

【 図 1 0 】

【図 1 1】

【図12】

---

フロントページの続き

審査官 酒井 恭信

(56)参考文献 米国特許出願公開第2007/0271423(US, A1)

台湾特許出願公開第200743957(TW, A)

国際公開第2011/106049(WO, A1)

米国特許出願公開第2012/0311371(US, A1)

特表2013-520721(JP, A)

特開2004-110785(JP, A)

特開2003-131940(JP, A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 13/16 - 13/18

G 06 F 12/00 - 12/06