(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6759578号

(P6759578)

(45) 発行日 令和2年9月23日(2020.9.23)

(24) 登録日 令和2年9月7日(2020.9.7)

(51) Int.Cl.

H01R 11/01 (2006.01)

F 1

H01R 11/01 501C

請求項の数 21 (全 24 頁)

(21) 出願番号 特願2015-249132 (P2015-249132)

(22) 出願日 平成27年12月21日 (2015.12.21)

(65) 公開番号 特開2016-119306 (P2016-119306A)

(43) 公開日 平成28年6月30日 (2016.6.30)

審査請求日 平成30年11月19日 (2018.11.19)

(31) 優先権主張番号 特願2014-259509 (P2014-259509)

(32) 優先日 平成26年12月22日 (2014.12.22)

(33) 優先権主張国・地域又は機関

日本国 (JP)

前置審査

(73) 特許権者 000108410

デクセリアルズ株式会社

東京都品川区大崎一丁目11番2号 ゲートシティ大崎イーストタワー8階

(74) 代理人 110000224

特許業務法人田治米国際特許事務所

(72) 発明者 林 慎一

東京都品川区大崎一丁目11番2号 ゲートシティ大崎イーストタワー8階 デクセリアルズ株式会社内

(72) 発明者 斎藤 雅男

東京都品川区大崎一丁目11番2号 ゲートシティ大崎イーストタワー8階 デクセリアルズ株式会社内

最終頁に続く

(54) 【発明の名称】異方導電性フィルム及び接続構造体

## (57) 【特許請求の範囲】

## 【請求項 1】

絶縁接着剤層と、該絶縁接着剤層に配置された導電粒子を含む異方導電性フィルムであつて、

異方導電性フィルムで接続する電子部品の端子の配列領域の外形に対応して形成された接続用導電粒子配置領域を有し、該接続用導電粒子配置領域が、異方導電性フィルムの長手方向に周期的に形成されている異方導電性フィルム。

## 【請求項 2】

隣り合う接続用導電粒子配置領域の間に、導電粒子が配置されていないバッファー領域を有する請求項1記載の異方導電性フィルム。

10

## 【請求項 3】

異方導電性接続する端子と異方導電性フィルムとの位置合わせのためのアライメントマークとなる位置合わせ用導電粒子配置領域を有する請求項1又は2記載の異方導電性フィルム。

## 【請求項 4】

位置合わせ用導電粒子配置領域が接続用導電粒子配置領域と別個に形成されている請求項3記載の異方導電性フィルム。

## 【請求項 5】

位置合わせ用導電粒子配置領域が、接続用導電粒子配置領域と重複して形成されている請求項3記載の異方導電性フィルム。

20

**【請求項 6】**

接続用導電粒子配置領域に、複数の導電粒子で形成された粒子配列群が配列している請求項 1 ~ 5 のいずれかに記載の異方導電性フィルム。

**【請求項 7】**

接続用導電粒子配置領域において、異方導電性フィルムで接続する電子部品の一つのバンプあたり 3 個以上の導電粒子が配置されている請求項 1 ~ 6 のいずれかに記載の異方導電性フィルム。

**【請求項 8】**

複数の接続用導電粒子配置領域がそれぞれ異方導電性フィルムの長手方向に周期的に形成されている請求項 1 ~ 7 のいずれかに記載の異方導電性フィルム。 10

**【請求項 9】**

異方導電性フィルムの長手方向に沿って接続用導電粒子配置領域が並列して形成されている請求項 1 ~ 8 のいずれかに記載の異方導電性フィルム。

**【請求項 10】**

絶縁接着剤層と、該絶縁接着剤層に配置された導電粒子を含む異方導電性フィルムであつて、

複数の導電粒子が配置されている第 1 の導電粒子配置領域、及び第 1 の導電粒子配置領域に対して導電粒子の配列態様、配列位置又は密度が異なる第 2 の導電粒子配置領域を有し、第 1 の導電粒子配置領域及び第 2 の導電粒子配置領域が单一の絶縁接着剤層に配置され且つ異方導電性フィルムの長手方向に周期的に形成されている異方導電性フィルム。 20

**【請求項 11】**

異方導電性フィルムの長手方向に隣り合う第 2 の導電粒子配置領域の間に、導電粒子が配置されていないバッファー領域を有する請求項 10 記載の異方導電性フィルム。

**【請求項 12】**

第 1 の導電粒子配置領域が、異方導電性接続する端子と異方導電性フィルムとの位置合わせのためのアライメントマークとなる位置合わせ用導電粒子配置領域である請求項 10 又は 11 記載の異方導電性フィルム。

**【請求項 13】**

第 2 の導電粒子配置領域が、異方導電性フィルムで接続する電子部品の端子の配列領域の外形に対応して形成された接続用導電粒子配置領域である請求項 10 ~ 12 のいずれかに記載の異方導電性フィルム。 30

**【請求項 14】**

位置合わせ用導電粒子配置領域が、位置合わせ用導電粒子から形成されている請求項 12 記載の異方導電性フィルム。

**【請求項 15】**

絶縁接着剤層と、該絶縁接着剤層に配置された導電粒子を含む異方導電性フィルムであつて、

複数の導電粒子が配置されている第 1 の導電粒子配置領域、及び第 1 の導電粒子配置領域に対して導電粒子の配列態様、配列位置又は密度が異なる第 2 の導電粒子配置領域を有し、各導電粒子配置領域が導電粒子の集合からなり且つ導電粒子が各導電粒子配置領域の輪郭を形成しており、第 1 の導電粒子配置領域及び第 2 の導電粒子配置領域が異方導電性フィルムの長手方向に周期的に形成されている異方導電性フィルム。 40

**【請求項 16】**

異方導電性フィルムの長手方向に隣り合う第 2 の導電粒子配置領域の間に、導電粒子が配置されていないバッファー領域を有する請求項 15 記載の異方導電性フィルム。

**【請求項 17】**

第 1 の導電粒子配置領域が、異方導電性接続する端子と異方導電性フィルムとの位置合わせのためのアライメントマークとなる位置合わせ用導電粒子配置領域である請求項 15 又は 16 記載の異方導電性フィルム。

**【請求項 18】**

50

第2の導電粒子配置領域が、異方導電性フィルムで接続する電子部品の端子の配列領域の外形に対応して形成された接続用導電粒子配置領域である請求項15～17のいずれかに記載の異方導電性フィルム。

【請求項19】

位置合わせ用導電粒子配置領域が、位置合わせ用導電粒子から形成されている請求項17記載の異方導電性フィルム。

【請求項20】

請求項1～19のいずれかに記載の異方導電性フィルムで第1電子部品と第2電子部品が異方導電性接続されている接続構造体。

【請求項21】

10

請求項1～19のいずれかに記載の異方導電性フィルムで第1電子部品と第2電子部品とを異方導電性接続する接続構造体の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、異方導電性フィルム、異方導電性フィルムを用いる接続方法、及び異方導電性フィルムで接続された接続構造体に関する。

【背景技術】

【0002】

異方導電性フィルムは、ICチップ等の電子部品を基板に実装する際に広く使用されている。近年では、携帯電話、ノートパソコン等の小型電子機器において配線の高密度化が求められており、この高密度化に異方導電性フィルムを対応させる手法として、異方導電性フィルムの絶縁接着剤層に導電粒子を格子状に均等配置する技術が知られている。

20

【0003】

しかしながら、導電粒子を均等配置しても、異方導電性フィルムを用いて上下の端子を異方導電性接続するときに、端子の縁边上に位置した導電粒子が絶縁性接着剤の溶融によりスペースに流れ出て端子で挟まれず、接続抵抗がばらつくという問題がある。この問題に対しても、導電粒子の第1の配列方向を異方導電性フィルムの長手方向とし、第1の配列方向に交差する第2の配列方向を、異方導電性フィルムの長手方向に直交する方向に対して5°以上15°以下で傾斜させることが提案されている（特許文献1）。

30

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特許4887700号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、異方導電性フィルムで接続する電子部品のバンプサイズがさらに小さくなると、バンプで捕捉できる導電粒子の数もさらに少くなり、特許文献1に記載の異方導電性フィルムでは導通信頼性を十分に得られない場合があった。特に、液晶画面等の制御用ICをガラス基板上の透明電極に接続する、所謂COG（Chip on Glass）接続では、液晶画面の高精細化に伴う多端子化とICチップの小型化によりバンプサイズが小さくなっている、また、テレビのディスプレイ用のガラス基板とフレキシブルプリント配線板（FPC：Flexible Printed Circuits）とを接合するFOG（Film on Glass）接合を行う場合でも接続端子がファインピッチとなり、接続端子で捕捉できる導電粒子数を増加させることが課題となつた。

40

【0006】

接続端子で捕捉できる導電粒子を増加させるためには、異方導電性フィルムにおける導電粒子の密度をさらに高めることが考えられる。しかしながら、異方導電性フィルムにおいて導電粒子の密度を高めると、異方導電性フィルムの製造コストが高くなる。

50

**【 0 0 0 7 】**

これに対し、本発明は、ファインピッチのFOG接続やCOG接続に使用することができ、かつ導電粒子の密度増加に伴う製造コストの上昇を抑制することのできる異方導電性フィルムの提供を課題とする。

**【課題を解決するための手段】****【 0 0 0 8 】**

本発明者は、(i)異方導電性フィルムにおける導電粒子の配置領域として、導電粒子の配列様式、配列位置又は密度が異なる複数の配列領域を設ける場合には、異方導電性フィルムで接続する対象物に応じた導電粒子の配置領域を形成できること、即ち、導電粒子の配置領域を、該異方導電性フィルムで接続する電子部品の端子の配列領域の外形に対応させられること（例えば、異方導電性フィルムでCOG接続する場合に、バンプ列が存在するICチップの周辺部に対応する領域には導電粒子を配置するが、バンプが存在しない中央部に対応する領域には導電粒子を配置しない等）、(ii)これにより接続に関与しない導電粒子の数を低減でき、異方導電性フィルムの製造コストを抑えられること、また、(iii)電子部品の端子の配列領域と異方導電性フィルムにおける導電粒子の配置領域とを位置合わせする場合、異方導電性フィルムにアライメントマークとなるものが必要となるが、これを導電粒子の配置により形成すると、従前の異方導電性フィルムの製造工程に対してアライメントマーク形成のための追加工程が不要となることを見出し、本発明を想到した。

**【 0 0 0 9 】**

即ち、本発明は、絶縁接着剤層と、該絶縁接着剤層に配置された導電粒子を含む異方導電性フィルムであって、複数の導電粒子が配置されている第1の導電粒子配置領域、及び第2の導電粒子配置領域に対して導電粒子の配列様式、配列位置又は密度が異なる第2の導電粒子配置領域を有し、第1の導電粒子配置領域及び第2の導電粒子配置領域が異方導電性フィルムの長手方向に周期的に形成されている異方導電性フィルムを提供する。

**【 0 0 1 0 】**

また、本発明は、絶縁接着剤層と、該絶縁接着剤層に配置された導電粒子を含む異方導電性フィルムであって、異方導電性フィルムで接続する電子部品の端子の配列領域の外形に対応して形成された導電粒子配置領域（以下、接続用導電粒子配置領域ともいう）を有し、該導電粒子配置領域が、異方導電性フィルムの長手方向に周期的に形成されている異方導電性フィルムを提供する。

**【 0 0 1 1 】**

加えて、本発明は、上述の異方導電性フィルムで第1電子部品と第2電子部品が異方導電性接続されている接続構造体を提供する。

**【発明の効果】****【 0 0 1 2 】**

本発明の異方導電性フィルムによれば、接続用導電粒子配置領域を端子の配列領域の外形に応じて形成することにより、接続に関与しない導電粒子を低減させることができるの40で、異方導電性フィルムの製造コストを抑制することができる。

**【 0 0 1 3 】**

特に、本発明の異方導電性フィルムにおいて、アライメントマークとなる導電粒子配置領域（以下、位置合わせ用導電粒子配置領域ともいう）を形成した場合には、接続用すべき電子部品の端子の配列領域と、異方導電性フィルムの接続用導電粒子配置領域とを位置合わせすることができるので、確実に端子に導電粒子を捕捉させ、導通を確保することができる。

**【 0 0 1 4 】**

さらに、このアライメントマークとなる導電粒子配置領域の形成は、従前の異方導電性フィルムの製造工程において追加工程を要することなく形成することができる。

10

20

30

40

50

## 【図面の簡単な説明】

## 【0015】

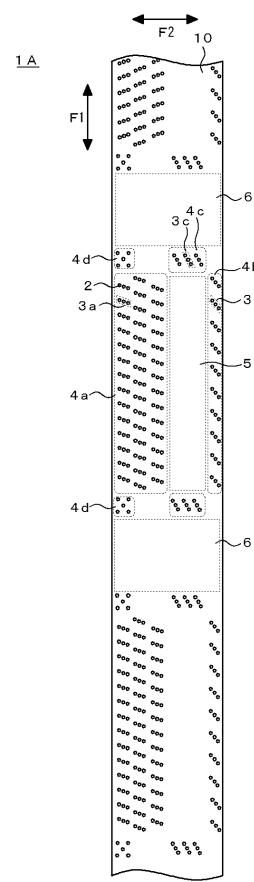

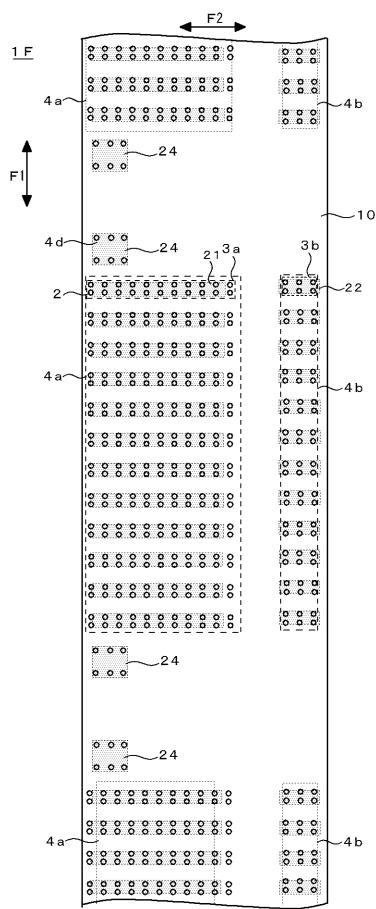

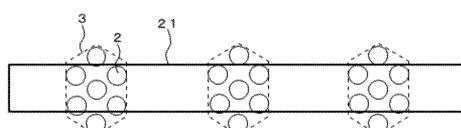

【図1A】図1Aは、異方導電性フィルム1Aにおける導電粒子の配置図である。

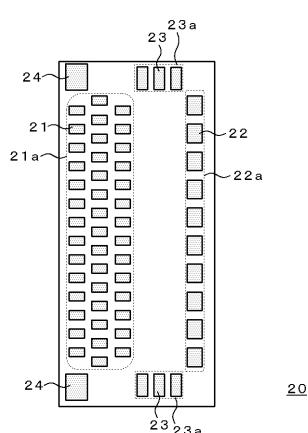

【図1B】図1Bは、異方導電性フィルム1Aで接続するICチップの端子面の平面図である。

【図1C】図1Cは、異方導電性フィルム1AをICチップに熱圧着することによりICチップの端子に導電粒子を捕捉させた状態の平面図である。

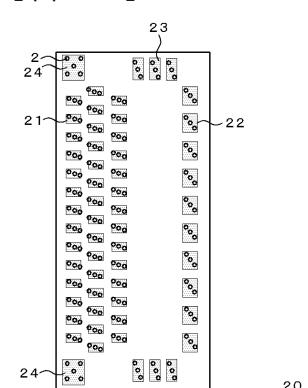

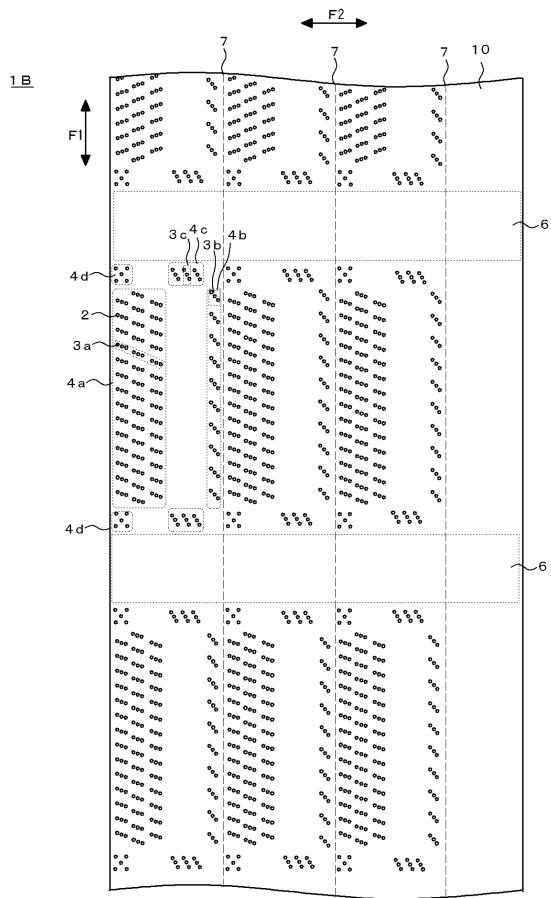

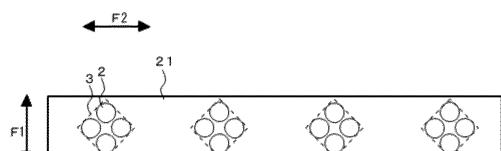

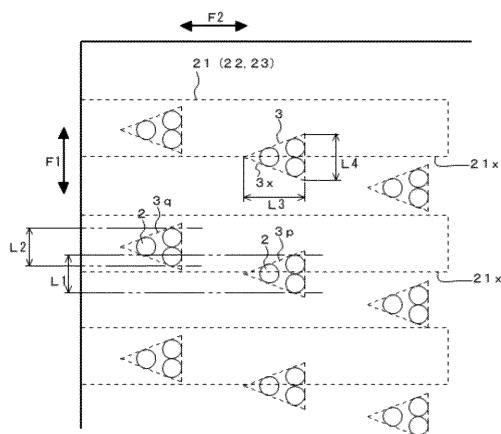

## 【図2】図2は、異方導電性フィルム1Bにおける導電粒子の配置図である。

## 【図3】図3は、異方導電性フィルム1Cにおける導電粒子の配置図である。

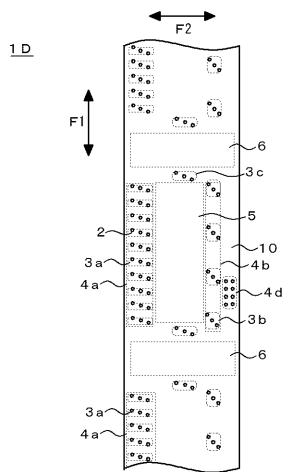

## 【図4】図4は、異方導電性フィルム1Dにおける導電粒子の配置図である。

10

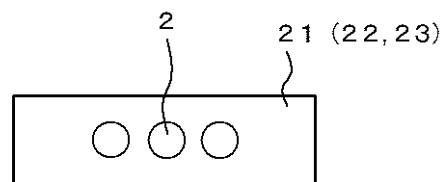

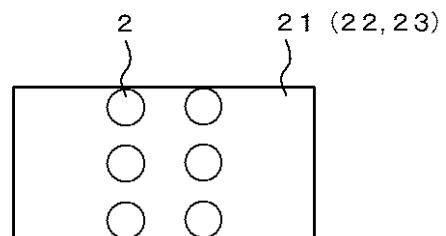

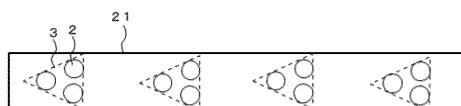

## 【図5A】図5Aは、粒子配列群における導電粒子の配置図である。

## 【図5B】図5Bは、粒子配列群における導電粒子の配置図である。

## 【図5C】図5Cは、粒子配列群における導電粒子の配置図である。

## 【図5D】図5Dは、粒子配列群における導電粒子の配置図である。

## 【図5E】図5Eは、粒子配列群における導電粒子の配置図である。

## 【図6】図6は、異方導電性フィルム1Eにおける導電粒子の配置図である。

## 【図7】図7は、異方導電性フィルム1Fにおける導電粒子の配置図である。

## 【図8A】図8Aは、粒子配列群を形成する導電粒子の配置図である。

## 【図8B】図8Bは、粒子配列群を形成する導電粒子の配置図である。

## 【図8C】図8Cは、粒子配列群を形成する導電粒子の配置図である。

20

## 【図8D】図8Dは、粒子配列群を形成する導電粒子の配置図である。

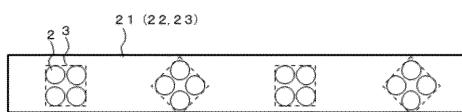

## 【図9】図9は、粒子配列群を形成する導電粒子の配置図である。

## 【図10】図10は、粒子配列群を形成する導電粒子の配置図である。

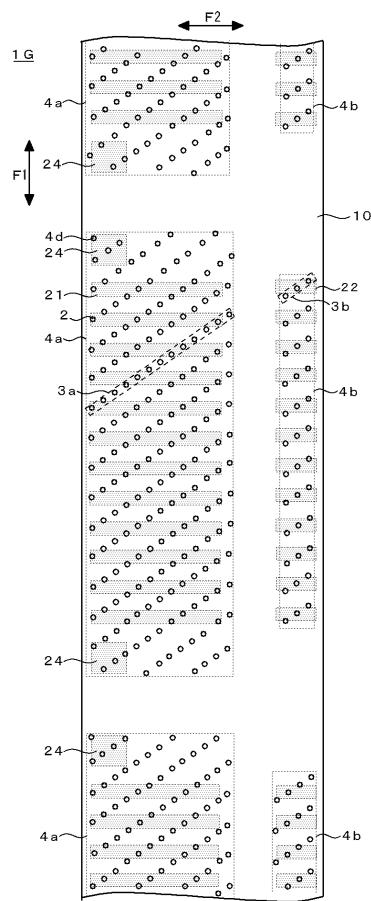

## 【図11】図11は、異方導電性フィルム1Gにおける導電粒子の配置図である。

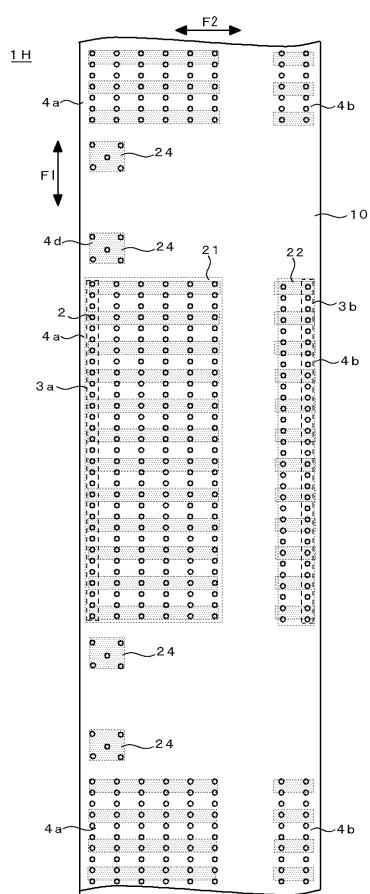

## 【図12】図12は、異方導電性フィルム1Hにおける導電粒子の配置図である。

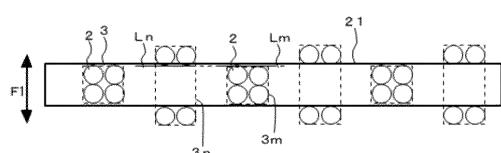

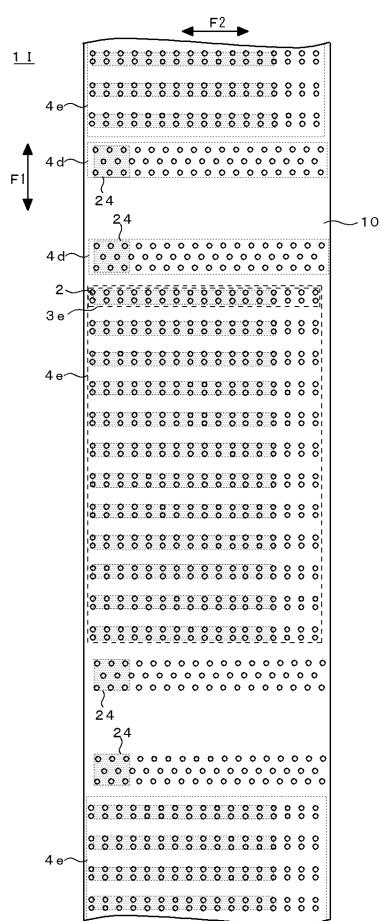

## 【図13】図13は、異方導電性フィルム1Iにおける導電粒子の配置図である。

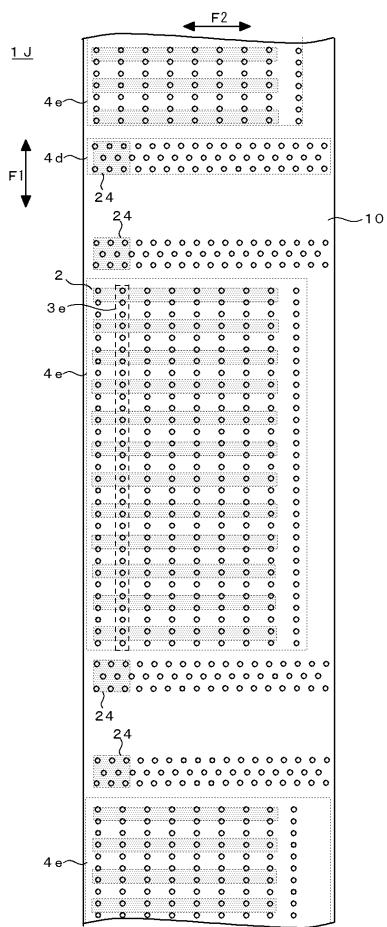

## 【図14】図14は、異方導電性フィルム1Jにおける導電粒子の配置図である。

## 【発明を実施するための形態】

## 【0016】

以下、図面を参照しつつ本発明を詳細に説明する。なお、各図中、同一符号は同一又は同等の構成要素を表している。

30

## 【0017】

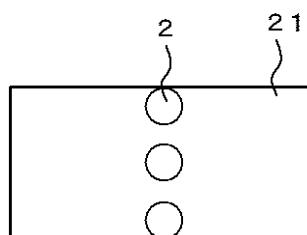

図1Aは、COG接続に使用される本発明の一実施例の異方導電性フィルム1Aにおける導電粒子2の配置図であり、図1Bは異方導電性フィルム1Aで接続するICチップ20の端子面の平面図であり、図1Cは、異方導電性フィルム1AをICチップ20に熱圧着することによりICチップ20の端子に導電粒子を捕捉させた状態の平面図である。

## 【0018】

この異方導電性フィルム1Aは、絶縁接着剤層10と、絶縁接着剤層10に配置された導電粒子2を有する。図1A、図1B及び図1Cからわかるように、異方導電性フィルム1Aにおいて導電粒子2は、ICチップ20の端子の配列に対応して配置されている。

40

## 【0019】

より具体的には、ICチップ20の出力側バンプ21に対応する部位では、3個の導電粒子2が一列に配列して粒子配列群3aを形成しており、粒子配列群3aが千鳥格子状に配列して接続用導電粒子配置領域4aを形成している。各粒子配列群3aは、異方導電性フィルム1AとICチップ20とを重ね合わせた場合に、大凡、ICチップ20の個々の出力側バンプ21内に配置されるように形成されており、各粒子配列群3aにおける導電粒子2の配列は異方導電性フィルム1Aの長手方向F1に対して傾き、出力側バンプ21による粒子捕捉性を向上させている。

## 【0020】

また、接続用導電粒子配置領域4aの外形と出力側バンプ21の配列領域21aの外形

50

が対応している。即ち、双方の外形は略同一形状であるが、異方導電性フィルム 1 A と I C チップ 2 0 とを重ね合わせた場合に接続用導電粒子配置領域 4 a が output 側バンプ 2 1 の配列領域 2 1 a をカバーするように、接続用導電粒子配置領域 4 a が output 側バンプ 2 1 の配列領域 2 1 a よりも若干大きく形成されている。このため接続用導電粒子配置領域 4 a も、output 側バンプ 2 1 の配列領域 2 1 a も異方導電性フィルム 1 A の長手方向に沿って延びている。

#### 【 0 0 2 1 】

I C チップ 2 0 の input 側バンプ 2 2 に対応する部位やサイドバンプ 2 3 に対応する部位にも上述の output 側バンプ 2 1 に対応する部位と同様に、3 個の導電粒子 2 が一列に配列した粒子配列群 3 b、3 c が個々のバンプ 2 2、2 3 に対応して形成されている。 10

#### 【 0 0 2 2 】

そして、input 側バンプ 2 2 に対応する粒子配列群 3 b が異方導電性フィルム 1 A の長手方向 F 1 に沿って一列に配列することにより接続用導電粒子配置領域 4 b が形成されている。この接続用導電粒子配置領域 4 b の外形は、input 側バンプ 2 2 の配列領域 2 2 a の外形に対応し、接続用導電粒子配置領域 4 b が input 側バンプ 2 2 の配列領域 2 2 a をカバーするように形成されている。

#### 【 0 0 2 3 】

また、サイドバンプ 2 3 に対応する粒子配列群 3 c が異方導電性フィルム 1 A の短手方向 F 2 に配列して接続用導電粒子配置領域 4 c が形成されている。接続用導電粒子配置領域 4 c の外形もサイドバンプ 2 3 の配列領域 2 3 a の外形に対応し、接続用導電粒子配置領域 4 c がサイドバンプ 2 3 の配列領域 2 3 a をカバーするように形成されている。 20

#### 【 0 0 2 4 】

このように、この異方導電性フィルム 1 A では、導電粒子の配列態様又は配列位置が異なる導電粒子配置領域（第 2 の導電粒子配置領域）4 a、4 b、4 c が形成され、これら導電粒子配置領域 4 a、4 b、4 c の外形は、I C チップ 2 0 のバンプの配列領域 2 1 a、2 2 a、2 3 a の外形に対応して形成されているので、接続に関与しない導電粒子に数を低減することができ、それにより異方導電性フィルムの製造コストを抑制することができる。

#### 【 0 0 2 5 】

さらに、この異方導電性フィルム 1 A では、各導電粒子配置領域 4 a、4 b、4 c は、個々のバンプ 2 1、2 2、2 3 に対応して配置された粒子配列群 3 a、3 b、3 c から形成されているので、バンプ 2 1、2 2、2 3 に捕捉される導電粒子の数を接続が確保される限りで低減させることができる。よって、異方導電性フィルム 1 A に必要とされるトータルでの導電粒子の数を低減し、これによっても異方導電性フィルムの製造コストを抑制することができる。 30

#### 【 0 0 2 6 】

また、I C チップのバンプ 2 1、2 2、2 3 に捕捉される導電粒子数を、接続が確保される限りで低減させることは、接続時に加圧ツールで I C チップにかける押圧力の低減を可能とする。このため、接続時の押圧力に対する I C チップの許容限界で規定されるバンプの個数密度を増やし、それにより I C チップ 1 個あたりのバンプの接続総面積を大きくすることができる。例えば、一般的な I C チップでは、I C チップ 1 個あたりのバンプの接続総面積が  $5 \times 10^6 \mu m^2$  程度であるが、それを 1.5 ~ 3 倍にすることができる。これにより I C チップのさらなる高集積化を図ることが可能となる。 40

#### 【 0 0 2 7 】

一方、この異方導電性フィルム 1 A において、I C チップ 2 0 のアライメントマーク 2 4 に対応する部位には、矩形の四隅と中央部に配置された導電粒子 2 により位置合わせ用導電粒子配置領域（第 1 の導電粒子配置領域）4 d が形成されている。このアライメントマーク 2 4 に対応した位置合わせ用導電粒子配置領域 4 d は、I C チップ 2 0 の端子の配列領域 2 1 a、2 2 a、2 3 a に対応した接続用導電粒子配置領域 4 a、4 b、4 c とは別個の位置に形成されており、接続に関与しないが、異方導電性フィルム 1 A と I C チップ 50

プ 2 0との位置合わせに使用することができる。なお、位置合わせ用導電粒子配置領域 4 d 内にさらに導電粒子を配置し、該領域 4 d 内の導電粒子の個数密度を接続用導電粒子配置領域 4 a、4 b、4 c より高めてもよい。

【 0 0 2 8 】

従来、 I C チップ 2 0 のアライメントマーク 2 4 は数十  $\mu\text{m}$  ~ 数百  $\mu\text{m}$  の大きさに形成されており、 C C D 又はレーザーを用いて I C チップと基板とのアライメントが行われているが、異方導電性フィルムには I C チップ 2 0 のアライメントマーク 2 4 に対応するマークは形成されていない。これは、従来の異方導電性フィルムでは、その全面に導電粒子が単分散ないし格子状に配置されているため、異方導電性フィルムと基板又は I C チップとをバンプサイズの精度で貼り合せをする必要がなく、異方導電性フィルムに（アライメントの位置検出に用いる）レーザー光などを透過させて I C チップと基板とのアライメントを行うからである。10

【 0 0 2 9 】

一方、本実施例の異方導電性フィルム 1 A のようにバンプ 2 1、2 2、2 3 に捕捉される導電粒子 2 の数を接続が確保される限りで低減させる場合には、バンプサイズに対応した精度で異方導電性フィルム 1 A をバンプと貼り合わせる必要があり、異方導電性フィルム 1 A にアライメントマークを設けることが必要となる場合がある。

【 0 0 3 0 】

また、異方導電性フィルム 1 A にアライメントマークを形成する方法として、 I C チップ 2 0 のアライメントマーク 2 4 に対応する大きさのものを絶縁接着剤層に配置することも考えられるが、異方導電性フィルムの製造工程上の制約から難しい。また、絶縁接着剤層に直接的に印刷等によりマーキングすることも考えられるが、アライメントマークが小さすぎて実際上のマーキングの加工が困難である。20

【 0 0 3 1 】

これに対し、導電粒子の配列をアライメントマークとして使用すると、異方導電性フィルムの製造工程に新たな工程を追加することが不要であり、また、製造された異方導電性フィルムを異方導電性接続に使用する場合に格別の制限も生じず、異方導電性フィルムにおける導電粒子の配置と I C チップのバンプに対応した基板側の電極との位置を合わせることが可能となる。そこで、本実施例の本発明の異方導電性フィルム 1 A においては、アライメントマークとして位置合わせ用導電粒子配置領域 4 d を形成している。また、このように導電粒子 2 によって異方導電性フィルム 1 A にアライメントマークを形成する場合に、異方導電性フィルム 1 A では、バンプ 2 1、2 2、2 3 に捕捉される導電粒子 2 の数を接続が確保される限りで低減させており、異方導電性フィルム 1 A の透過性が高い。したがって、基板側から透視してアライメント作業を行うことも可能になる。このため、 I C チップ側のアライメントマークの設計自由度を高くすることができ、 I C チップ側のアライメントマークをバンプの形成領域の近傍に設け、アライメント精度を向上させることが可能となる。30

【 0 0 3 2 】

位置合わせ用導電粒子配置領域 4 d の大きさとしては、特に制限はないが、検出精度を保つため、 C O G 用の本実施例の異方導電性フィルム 1 A では  $100 \mu\text{m}^2$  以上  $1 \text{mm}^2$  以下が好ましい。なお、 F O G および F O B 用の異方導電性フィルムでは、検出精度を保つために  $0.01 \text{mm}^2$  以上  $9 \text{mm}^2$  以下とすることが好ましい。40

【 0 0 3 3 】

一方、この異方導電性フィルム 1 A には、 I C チップ 2 0 の出力側バンプ 2 1 の配列領域 2 1 a に対応した導電粒子配置領域 4 a と、入力側バンプ 2 2 の配列領域 2 2 a に対応した導電粒子配置領域 4 b との間には、導電粒子が配置されていない中央部領域 5 が形成されている。また、異方導電性フィルム 1 A の長手方向 F 1 には、 I C チップ 2 0 のバンプの配列領域 2 1 a、2 2 a、2 3 a に対応した上述の導電粒子配置領域 4 a、4 b、4 c が周期的に繰り返し形成されており、異方導電性フィルム 1 A の長手方向 F 1 で隣り合う導電粒子配置領域 4 c 同士の間には導電粒子が配置されていないバッファー領域 6 が形50

成されている。

【0034】

一般に、異方導電性フィルム1Aはロール状に巻き回して保管され、引き出して使用されるところ、バッファー領域6は、異方導電性フィルム1Aの使用時に、ロール状に巻き回した異方導電性フィルム1Aを引き出し、カッティング作業をするために使用される。

【0035】

バッファー領域6の異方導電性フィルム1Aの長手方向F1の長さは、特に制限はないが、一例として、異方導電性フィルム1Aの引き出しやカッティング等の作業性を向上させる点から、0.1mm以上が好ましく、0.2mm以上がより好ましい。一方、異方導電性フィルム1Aの一つのロール体において、接続に寄与できる領域を多く確保する点から、10mm以下が好ましく、3mm以下がより好ましく、1mm以下が更により好ましい。

【0036】

このように、この異方導電性フィルム1Aによれば、ICチップ20のバンプの配列領域21a、22a、23aに対応して導電粒子配置領域4a、4b、4cが形成されているので、導電粒子配置領域4a、4b、4cでは導電粒子2の密度を適切にしてバンプにおける導電粒子2の捕捉性を高めることができ、また、バンプの無い領域に対応する中央部領域5やバッファー領域6では導電粒子が存在しないので接続に寄与しない導電粒子を低減させることができる。さらに、導電粒子配置領域4a、4b、4cでは、導電粒子2が個々のバンプに対応して配列した粒子配列群3a、3b、3cが形成されているので、バンプ21、22、23における粒子捕捉性を向上させ、隣り合うバンプ間でショートが発生することを抑制することができる。

【0037】

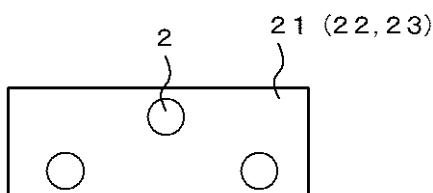

本発明の異方導電性フィルムは、種々の態様をとることができる。例えば、図2に示す異方導電性フィルム1Bのように、その長手方向F1に、上述の異方導電性フィルム1Aと同様の、ICチップ20のバンプの配列領域に対応した接続用導電粒子配置領域4a、4b、4cが周期的に繰り返し形成され、異方導電性フィルム1Bの短手方向F2には、かかる接続用導電粒子配置領域4a、4b、4cの繰り返し列が複数列形成されていてもよい。この異方導電性フィルム1Bは、スリット線7の位置でスリットされて使用される。

【0038】

また、図3に示す異方導電性フィルム1Cのように、入力側バンプ22に対応する粒子配列群3bを異方導電性フィルム1Cの短手方向F2に延長し、異方導電性フィルム1Cのスリットが、スリット線7aで行われてもよく、延長した導電粒子の列分だけ外側のスリット線7bで行われてもよいとすることができる。これにより、実際のスリット加工でスリット位置がずれてもスリット後の異方導電性フィルムを使用することが可能となる。

【0039】

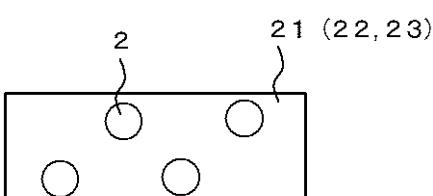

図4に示す異方導電性フィルム1Dのように、アライメントマークとして使用する位置合わせ用導電粒子配置領域4dを、異方導電性フィルム1Dの長手方向F1の縁部に沿った位置に形成してもよい。アライメントマークとして使用する位置合わせ用導電粒子配置領域4dの形成配置は、ICチップに形成されているアライメントマークに応じて適宜変更することができる。

【0040】

なお、本発明において、導電粒子配置領域内における導電粒子の配置には特に制限はない。前述の異方導電性フィルム1A～1Dのように、導電粒子2が粒子配列群3a、3b、3cを形成し、粒子配列群3a、3b、3cが配列して導電粒子配置領域4a、4b、4cを形成してもよく、導電粒子がランダムに集合して粒子群を形成し、その粒子群が導電粒子配置領域内で配列していてもよく、導電粒子配置領域内で単独の導電粒子が格子状に配列してもよく、導電粒子配置領域内で導電粒子がランダムに配置されていてもよい。導電粒子配置領域内における導電粒子の配置は、アライメントを正確に行う点から、導

10

20

30

40

50

電粒子配置領域の輪郭が認識できる程度に導電粒子の集合を形成していることが好ましい。

【0041】

導電粒子配置領域内で導電粒子が粒子配列群を形成する場合、粒子配列群内において隣接する導電粒子の間隔は導電粒子の粒子径の1/4未満とすることができ、接触していてもよい。一方、隣接する粒子配列群同士の間隔は導電粒子の粒子径の0.5倍以上とすることが好ましい。ここで、導電粒子の粒子径は、異方導電性フィルム1Aを形成する導電粒子の平均径である。導電粒子の平均径は、ショート防止と、接続する端子間接合の安定性の点から好ましくは1~30μm、より好ましくは1~10μmである。

【0042】

粒子配列群を構成する導電粒子の数は2個以上、好ましくは3個以上とすることができる。また、各粒子配列群は、前述の異方導電性フィルム1Aの粒子配列群3a、3b、3cのように、バンプの長手方向に対して傾斜した一列の直線状としても良く、また、導電粒子2の配列を、一つのバンプ21(22、23)を横断する直線状としても良く(図5A)、一つのバンプ21(22、23)を縦断する直線状としても良く(図5B)一つのバンプ21(22、23)に対して複数列の直線状の配列としても良く(図5C)、一つのバンプ21(22、23)に対して導電粒子を三角形の頂点に配置した形状としてもよく(図5D)、四角形などの頂点に配置した形状としても良い(図5E)。このように個々の粒子配列群の外形を多角形とする場合に、その多角形状は、正三角形、正方形、長方形等であってもよく、一つ以上の頂点が突出するなどにより歪んだ多角形状ないし非シンメトリーな形状であってもよい。一般的にバンプは矩形もしくは円形であるため、これと相似性や類似性を持たない方が、異方導電性接続の押圧時にイレギュラーな粒子ズレが起きても、端子における導電粒子の捕捉性の低下を抑制することができる。

【0043】

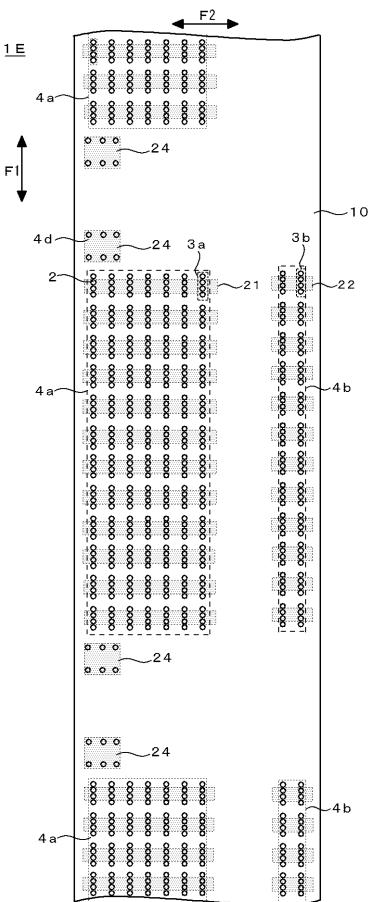

また、粒子配列群を構成する導電粒子は、一つのバンプに対応する領域内にあってもよく、図6に示す異方導電性フィルム1Eの粒子配列群3a、3bのように、一つのバンプ21、22内に収まることなく該バンプを横切るように形成されていてもよい。なお、図6において、ドットによる塗りつぶし領域は、異方導電性フィルム1Eで接続するICチップのバンプ21、22やアライメントマーク24を示している。

【0044】

また、粒子配列群における導電粒子の配列方向は、図6に示すように異方導電性フィルム1Eの長手方向としてもよく、図7に示すように異方導電性フィルム1Fの短手方向F2(即ち、各バンプ21、22の長手方向)としてもよい。さらに、バンプの長辺が導電粒子径に対して十分に長い場合に、図7に示す異方導電性フィルム1Fの粒子配列群3aのように、3個より多くの導電粒子2を異方導電性フィルムの短手方向F2(即ち、各バンプ21、22の長手方向)に配列してもよい。粒子配列群を構成する導電粒子の配置は、バンプ自体の形状や、ICチップにおけるバンプの配置状況に応じて適宜定めることができる。

【0045】

また、粒子配列群の配列態様に関し、バンプの長辺が導電粒子径に対して十分に長い場合に、図8A~図8Dに示すように、粒子配列群3を構成する導電粒子2の外接形状を3角形以上の多角形とし、その粒子配列群3をバンプ21の長手方向に配列してもよい。この多角形の形状は正多角形であっても、歪んだ多角形であってもよい。

【0046】

この場合、図8Bに示すように、粒子配列群3の導電粒子2が外接する多角形の各辺の向きが異方導電性フィルムの長手方向F1又は短手方向F2と交わる向きとすることができる。一般的な矩形のバンプ21に対し、導電粒子2が外接する多角形の各辺の向きをこのように定めることにより、異方導電性フィルムのアライメントズレに対する許容量を大きくすることができる。

【0047】

10

20

30

40

50

図 8 C に示すように、バンプ 2 1 を跨ぐように離間した一対の粒子配列群からなる導電粒子ユニット（導電粒子 4 個）3 n と、バンプ 2 1 上で導電粒子が近接している粒子配列群（導電粒子 4 個）3 m とを配列してもよい。同図の態様では、粒子配列群 3 m のバンプ長手方向の外接線 L m と、一対の粒子配列群からなるユニット 3 n のバンプ長手方向の内接線 L n とが重なる。これにより、異方導電性接続時に異方導電性フィルムの長手方向 F 1 に位置ズレが生じても、バンプ 2 1 では一定数の導電粒子 2 を捕捉することが可能となる。

#### 【 0 0 4 8 】

図 8 D に示すように、粒子配列群 3 のバンプ短手方向の長さをバンプ 2 1 の短手方向の長さよりも大きくしてもよい。図 8 C 及び図 8 D に示すように、粒子配列群 3 として、そのバンプ短手方向の長さがバンプ 2 1 の短手方向の長さよりも大きいものが存在すると、フィルムの撓みなどによりバンプ 2 1 に対する粒子配列群 3 の位置が所期の位置からずれても導電粒子 2 がバンプ 2 1 で捕捉されやすくなる。

#### 【 0 0 4 9 】

導電粒子 2 の捕捉性の向上のために、図 9 に示すように、粒子配列群 3 p を構成する導電粒子の、異方導電性フィルムの長手方向 F 1 に伸びる辺への投影幅 L 1 と、その粒子配列群 3 p に対して異方導電性フィルムの短手方向 F 2 で隣接する粒子配列群 3 q の同様の投影幅 L 2 を重複させることが好ましい。

#### 【 0 0 5 0 】

また、図 9 に示したように、粒子配列群 3 を構成する導電粒子 2 の外接形状を 3 角形とする場合に、この 3 角形の頂点が異方導電性フィルムの長辺側又は短辺側に突き出すようにすることが好ましい。3 角形の頂点が異方導電性フィルムの長辺側に突き出すようにすることで、異方導電性フィルムの短手方向 F 2 の 3 角形の長さ L 3 が、異方導電性フィルムの長手方向 F 1 の三角形の長さ L 4 よりも長くなると、バンプ 2 1 の縁辺 2 1 x に対して三角形の辺 3 x が鋭角に交わるため、特に、ファインピッチの場合に導電粒子の捕捉性が向上する。

#### 【 0 0 5 1 】

また、粒子配列群 3 内における導電粒子 2 の配列は、各粒子配列群 3 において同じでもよく、異なっていてもよい。異ならせる場合に、規則的に変更することができる。例えば、図 1 0 に示すように、粒子配列群 3 を構成する導電粒子 2 が同一個数、外接形状が同一であるが、外接形状の向き異なるものを混在させてもよい。粒子配列群 3 として、それを構成する導電粒子数の異なるものを規則的に繰り返し配列してもよい。

#### 【 0 0 5 2 】

図 1 1 に示す異方導電性フィルム 1 G は、複数のバンプ 2 1 にわたる粒子配列群 3 a において導電粒子 2 を異方導電性フィルムの長手方向 F 1 に対して斜めに配列したものである。バンプにおける粒子捕捉性を向上させる点から、粒子配列群における導電粒子の配列は、異方導電性フィルム 1 G の長手方向に対して斜めであることが好ましい。

#### 【 0 0 5 3 】

また、図 1 1 に示す異方導電性フィルム 1 G では、粒子配列群 3 a が異方導電性フィルムの長手方向 F 1 に配列することにより形成された導電粒子配置領域 4 a が I C チップの出力側バンプの形成領域を覆うように形成されており、この導電粒子配置領域 4 a の外形の端部が半導体チップのアライメントマーク 2 4 に対応する。そのため、この異方導電性フィルム 1 G では、I C チップのバンプに対応した導電粒子の配列とは別個の、I C チップのアライメントマーク 2 4 に対応した導電粒子の配列は形成されていない。

#### 【 0 0 5 4 】

図 1 2 に示す異方導電性フィルム 1 H のように、複数のバンプ 2 1、2 2 にわたる粒子配列群 3 a、3 b が、導電粒子 2 を異方導電性フィルム 1 H の長手方向 F 1 に配列したものでもよい。この粒子配列群 3 a、3 b を異方導電性フィルム 1 H の短手方向 F 2 に配列することにより導電粒子配置領域 4 a、4 b が形成される。

#### 【 0 0 5 5 】

10

20

30

40

50

なお、いずれの態様においても、一つのバンプで捕捉される導電粒子の数が3個以上となるように導電粒子を配置することが好ましく、10個以上とすることがさらに好ましい。

【0056】

また、一つのバンプを横切るように粒子配列群を形成する場合、粒子配列群における隣接する導電粒子の間隔が導電粒子の粒子径の1/4未満のときには、異方導電性接続後のショートの発生を低減する点から、粒子配列群の、異方導電性フィルムの長手方向の長さ（バンプの短手方向の長さ）は、バンプ間距離の0.8倍未満が好ましく、0.5倍未満がより好ましい。

【0057】

一方、異方導電性フィルムをFOG接続に使用する場合も、複数の導電粒子が配置されている第1の導電粒子配置領域、及び第1の導電粒子配置領域に対して導電粒子の配列様、配列位置又は密度が異なる第2の導電粒子配置領域が、異方導電性フィルムの長手方向に周期的に形成されているようにする。即ち、位置合わせ用導電粒子配置領域と、基板の端子配列領域の外形に対応して形成された接続用導電粒子配置領域を異方導電性フィルムの長手方向F1に周期的に形成する。例えば、図13に示す異方導電性フィルム1Iのように、導電粒子2が、基板の各端子に対応する粒子配列群として、異方導電性フィルム1Iの短手方向F2に配列した粒子配列群3eを形成し、その粒子配列群3eを異方導電性フィルム1Iの長手方向F1に配列して接続用導電粒子配置領域4eを形成し、この接続用導電粒子配置領域4eを異方導電性フィルム1Iの長手方向F1に周期的に形成する。この接続用導電粒子配置領域4eの外形は、基板における端子の配列領域の外形に対応する。また、基板のアライメントマーク24に対応する異方導電性フィルム1Iのアライメントマークとして、位置合わせ用導電粒子配置領域4dが異方導電性フィルム1Iの長手方向に周期的に形成されている。

【0058】

図14に示す異方導電性フィルム1Jのように、導電粒子2が、異方導電性フィルム1Hの長手方向F1に配列した粒子配列群3eを異方導電性フィルム1Jの短手方向F2に配列して導電粒子配置領域4eを形成し、この導電粒子配置領域4eを異方導電性フィルム1Hの長手方向F1に周期的に形成してもよい。この導電粒子配置領域4eの外形も、基板における端子の配列領域の外形に対応している。

【0059】

これらの異方導電性フィルム1I、1Jには、ガラス基板又はフレキシブルプリント配線板に形成されているアライメントマーク24と位置合わせするための導電粒子配置領域4dが形成されているが、異方導電性フィルム1I、1Jと、ガラス基板又はフレキシブルプリント配線板とを位置合わせして重ね合わせた場合に、導電粒子配置領域4eの端部がアライメントマーク24と重なるように形成することで位置合わせ用導電粒子配置領域4dの形成を省略し、導電粒子配置領域4eの端部を異方導電性フィルム側のアライメントマークとして使用してもよい。

【0060】

また、電子部品のバンプ配列内には、電子部品同士の接続には関与しないが、異方導電性接続時の熱圧着条件を圧痕から検査できるようにするダミーバンプが設けられる場合があり、また、ファインピッチのバンプ配列と共に比較的大きいサイズの入出力用のバンプが設けられる場合がある。そこで、ダミーバンプや比較的大きいサイズのバンプに対応する導電粒子配置領域を異方導電性フィルムに設け、これをアライメントマークに代替させることも可能である。

【0061】

上述のように粒子配列群を構成する導電粒子は種々の配置をとることができ、各バンプが捕捉する導電粒子数を接続が確保できる限りで減らす場合に、異方導電性接続時の異方導電性フィルムの絶縁接着剤層を構成する樹脂の流れ、フィルム、基板、又はICチップの撓みなども踏まえて導電粒子を各バンプに対して適切に配置することが好ましい。

10

20

30

40

50

## 【0062】

本発明において導電粒子配置領域における導電粒子2の密度は、特に制限はなく、対象物によって適宜設定できるが、好ましくは10個/mm<sup>2</sup>以上、より好ましくは1000個/mm<sup>2</sup>以上、さらに好ましくは10000個/mm<sup>2</sup>以上、特に20000個/mm<sup>2</sup>以上とすることができます。一方、上限は接続対象物の条件により変更されるため、特にないが、例えば粒子配列群において導電粒子を連結させて配置する場合や、アライメントマークやダミーバンプ等に対応させて導電粒子を高密度に配置する場合等においては、導電粒子2の密度は250000個/mm<sup>2</sup>以下とすることができます。通常は、100000個/mm<sup>2</sup>以下が好ましく、50000個/mm<sup>2</sup>以下がより好ましい。この粒子密度は、導電粒子2の粒子径と配列様式によって適宜調整される。

10

## 【0063】

本発明において、導電粒子2自体の構成や絶縁接着剤層10の層構成又は構成樹脂については種々の態様をとることができます。

## 【0064】

即ち、導電粒子2としては、公知の異方導電性フィルムに用いられているものの中から適宜選択して使用することができる。例えば、ニッケル、コバルト、銀、銅、金、パラジウムなどの金属粒子、金属被覆樹脂粒子などが挙げられる。2種以上を併用することもできる。

## 【0065】

絶縁接着剤層10としては、公知の異方導電性フィルムで使用される絶縁性樹脂層を適宜採用することができる。例えば、アクリレート化合物と光ラジカル重合開始剤とを含む光ラジカル重合型樹脂層、アクリレート化合物と熱ラジカル重合開始剤とを含む熱ラジカル重合型樹脂層、エポキシ化合物と熱カチオン重合開始剤とを含む熱カチオン重合型樹脂層、エポキシ化合物と熱アニオン重合開始剤とを含む熱アニオン重合型樹脂層等を使用することができる。これらの樹脂層は、必要に応じて、それぞれ重合したものとすることができる。また、絶縁接着剤層10を、複数の樹脂層から形成してもよい。

20

## 【0066】

絶縁接着剤層10には、必要に応じてシリカ微粒子、アルミナ、水酸化アルミ等の絶縁性フィラーを加えても良い。絶縁性フィラーの配合量は、絶縁接着剤層を形成する樹脂100質量部に対して3~40質量部とすることが好ましい。これにより、異方導電性接続時に絶縁接着剤層10が溶融しても、溶融した樹脂で導電粒子2が不用に移動することを抑制することができる。

30

## 【0067】

絶縁接着剤層全体の最低溶融粘度としては、100~10000Pa·sが好ましく、500~5000Pa·sがより好ましく、特に好ましくは1000~3000Pa·sである。この範囲であれば、絶縁接着剤層10に導電粒子を精密に配置することができ、且つ異方導電性接続時の押し込みにより樹脂流動が導電粒子の捕捉性に支障を来たすことを防止できる。最低溶融粘度の測定は、レオメータ( TA 社製 ARES )を用いて、昇温速度5 / min、測定温度範囲50~200、振動周波数1 Hzの条件で求めることができる。

40

## 【0068】

絶縁接着剤層10に導電粒子2を上述の配置で固定する方法としては、導電粒子2の配置に対応した凹みを有する型を機械加工やレーザー加工、フォトリソグラフィなど公知の方法で作製し、その型に導電粒子を入れ、その上に絶縁接着剤層形成用組成物を充填し、硬化させ、型から取り出せばよい。このような型から、更に剛性の低い材質で型を作成しても良い。

## 【0069】

また、絶縁接着剤層10に導電粒子2を上述の配置におくために、絶縁接着剤層形成組成物層の上に、貫通孔が所定の配置で形成されている部材を設け、その上から導電粒子2を供給し、貫通孔を通過させるなどの方法でもよい。

50

## 【0070】

本発明の異方導電性フィルムを用いて、FPC、リジッド基板、セラミック基板、プラスチック基板、ガラス基板などの第1電子部品の接続端子と、ICチップ、ICモジュール、FPCなどの第2電子部品の接続端子を異方導電性接続する場合、例えば、異方導電性フィルム1Aの長手方向F1と、第1電子部品又は第2電子部品の接続端子の短手方向を合わせ、さらにCCD等を用いた画像検出などにより双方のアライメントマークを合わせ、加熱加圧する。また、光硬化を利用して接続することもできる。また、ICチップやICモジュールをスタックして第2電子部品同士を異方導電性接続することもできる。このようにして得られる接続構造体も本発明の一部である。

## 【0071】

10

本発明は、こうして異方導電性接続した第1電子部品と第2電子部品の接続構造体も包含する。

## 【実施例】

## 【0072】

以下、実施例に基づき、本発明を具体的に説明する。

## 実施例1～4、比較例1

## (1) FOG接続用の異方導電性フィルムの製造

フェノキシ樹脂（熱可塑性樹脂）（新日鐵住金（株）、YP-50）60部、エポキシ樹脂（熱硬化性樹脂）（三菱化学（株）、jER828）40部、カチオン系硬化剤（三新化学工業（株）、SI-60L）2部を含む絶縁性樹脂の混合溶液を調製し、それを、フィルム厚さ50μmのPETフィルム上に塗布し、80℃のオーブンにて5分間乾燥させ、PETフィルム上に厚み20μmの粘着層を形成した。

20

## 【0073】

一方、FOG接続する基板の電極端子の配置に対応させて、凸部が所定の配置密度の配列パターンを周期的に有する金型（実施例1～4）又は凸部が所定の配置密度でランダムな配置の金型（比較例1）を作成し、公知の透明性樹脂のペレットを溶融させた状態で該金型に流し込み、冷やして固めることで、凹部が格子状のパターンの樹脂型を形成した。この樹脂型の凹部に導電粒子（積水化学工業（株）、AUL704、粒径4μm）を充填し、その上に上述の絶縁性樹脂の粘着層を被せ、紫外線硬化により該絶縁性樹脂に含まれる硬化性樹脂を硬化させた。そして、型から絶縁性樹脂を剥離し、表1に示す実施例及び比較例の異方導電性フィルムを製造した。

30

## 【0074】

ここで、FOG接続するフレキシブルプリント基板は、電極の端子幅20μm、端子長さ1mm、端子間スペース20μm、ICチップのバンプ密度に相当する端子の密度が1mm<sup>2</sup>あたり25本のものとした。

ガラス基板はITOベタガラスを使用した。

## 【0075】

また、実施例1では、1つの電極端子（20μm×1mm）あたり10個の導電粒子が該電極端子内に収まるように配置され、電極端子間には導電粒子が存在しないように粒子配列群を周期的に形成した。

40

## 【0076】

実施例2では、1つの電極端子（20μm×1mm）あたり14個の導電粒子が配置され、電極端子間には導電粒子が存在しないように粒子配列群を周期的に形成した。この場合、各電極端子において該端子幅方向に導電粒子が導電粒子径1個分はみ出るようにした。

## 【0077】

実施例3では、導電粒子が粒子間距離4μmの4方格子で、端子短手方向に2列、端子長手方向に40～42列に配列した粒子配列群が、電極端子上に配置されるように粒子配列群を周期的に形成した。それにより、25本の電極端子に対応する導電粒子配置領域（端子間領域含む）（1mm<sup>2</sup>）にある導電粒子の合計は2080個となった。

50

## 【0078】

実施例4では、実施例3と略同様の4方格子の粒子配列群であって、端子短手方向に4列、端子長手方向に20～24列に配列した粒子配列群を各電極端子に対して形成した。この場合、粒子配列群の端子短手方向の長さは、端子幅（端子の短手方向の長さ）を上回っている。それにより、25本の電極端子に対応する導電粒子配置領域（端子間含む）（1mm<sup>2</sup>）にある導電粒子の合計は2130個となった。

## 【0079】

比較例1では、導電粒子個数密度が5000個/mm<sup>2</sup>となるように導電粒子をランダムに配置した。

## 【0080】

## (2)導通評価

10

実施例1～4及び比較例1の異方導電性フィルムの(a)初期導通抵抗、(b)導通信頼性、(c)ショート発生率を、それぞれ次のように評価した。結果を表1に示す。

## 【0081】

## (a)初期導通抵抗

実施例1～4及び比較例1の異方導電性フィルムを、上述のフレキシブルプリント基板とガラス基板との間に挟み、加熱加圧（180、5MPa、5秒）して各評価用接続物を得、その評価用接続物の導通抵抗を測定した。

## 【0082】

この場合、フレキシブルプリント基板、異方導電性フィルム及びガラス基板の位置合わせは、実体顕微鏡を用いながら手作業で行った。

20

## 【0083】

## (b)導通信頼性

(a)初期導通抵抗の評価用接続物を温度85、湿度85%RHの恒温槽に500時間おき、その導通抵抗を、(a)と同様に測定した。なお、この導通抵抗が5以上であると、接続した電子部品の実用的な導通安定性の点から好ましくない。

## 【0084】

## (c)ショート発生率

ショート発生率の評価用ICとして次のIC（7.5μmスペースの櫛歯TEG（test element group））を用意した。

30

## 【0085】

外径 1.5 × 13mm

厚み 0.5mm

バンプ仕様 金メッキ、高さ15μm、サイズ25 × 140μm、バンプ間距離7.5μm

## 【0086】

各実施例及び比較例の異方導電性フィルムを、ショート発生率の評価用ICと、該評価用ICに対応したパターンのガラス基板との間に挟み、(a)と同様の接続条件で加熱加圧して接続物を得、その接続物のショート発生率を求めた。ショート発生率は、「ショートの発生数 / 7.5μmスペース総数」で算出される。ショート発生率が50ppm以上であると実用上の接続構造体を製造する点から好ましくない。

40

## 【0087】

【表1】

|                                   | 比較例1    | 実施例1 | 実施例2 | 実施例3 | 実施例4 |

|-----------------------------------|---------|------|------|------|------|

| 粒子高密度領域                           | ランダム    | 周期的  | 周期的  | 周期的  | 周期的  |

| 導電粒子個数密度<br>(個数/mm <sup>2</sup> ) | 5000    | 250  | 350  | 2080 | 2130 |

| 初期導通抵抗                            | 2Ω 以下   | ←    | ←    | ←    | ←    |

| 導通信頼性                             | 10Ω 以下  | ←    | ←    | ←    | ←    |

| ショート発生率                           | 50ppm未満 | ←    | ←    | ←    | ←    |

10

## 【0088】

表1から、実施例1～4の異方導電性フィルムは比較例1よりも導電粒子配置領域における導電粒子の個数密度が低いが、比較例1と同様の導通特性を有し、好ましい導通特性の異方導電性フィルムを安価に製造できることがわかる。尚、実施例3では8μm、実施例4では16μmほどフィルムの長手方向に意図的にずらして貼り合せを行って同様に接続しても、略同様の結果が得られた。

## 【0089】

実施例1～4において、絶縁性樹脂100部にシリカフィラー（シリカ微粒子、アエロジルRY200、日本アエロジル(株)）20部を追加し、同様に異方導電性フィルムを製造し、導通評価を行ったところ、いずれも良好であった。

20

## 【0090】

## 実施例5～9、比較例2

## (1) COG接続用の異方導電性フィルムの製造

実施例1と同様にして、フェノキシ樹脂（熱可塑性樹脂）（新日鐵住金(株)、YP-50）60部、エポキシ樹脂（熱硬化性樹脂）（三菱化学(株)、jER828）40部、カチオン系硬化剤（三新化学工業(株)、S1-60L）2部を用いてPETフィルム上に厚み20μmの粘着層を形成した。

## 【0091】

30

一方、COG接続するICチップのバンプ配置に対応させて、凸部が所定の配置密度の配列パターンを周期的に有する金型（実施例5～9）又は凸部が4方格子（格子ピッチ8μm）の金型（比較例2）を作成し、公知の透明性樹脂のペレットを溶融させた状態で該金型に流し込み、冷やして固めることで、凹部が格子状のパターンの樹脂型を形成した。この樹脂型の凹部に導電粒子（積水化学工業(株)、AUL704、粒径4μm）を充填し、その上に上述の絶縁性樹脂の粘着層を被せ、紫外線硬化により該絶縁性樹脂に含まれる硬化性樹脂を硬化させた。そして、型から絶縁性樹脂を剥離し、表2に示す実施例及び比較例の異方導電性フィルムを製造した。

## 【0092】

ここで、COG接続するICチップとガラス基板はそれらの端子パターンが対応しており、サイズは以下に示す通りである。

40

## 【0093】

## ICチップ

外形 0.7×20mm

厚み 0.2mm

バンプ仕様 金メッキ、高さ12μm、サイズ15×100μm、バンプ間スペース13μm、バンプ個数 1300個（ICチップの長手の対向する辺にそれぞれ650個）

## 【0094】

実施例5～9では、ICチップのバンプに対応する領域にのみ、表2に示す導電粒子の配置パターンで粒子配列群を形成し、この粒子配列群をバンプの短手方向に配列させるこ

50

とにより、ICチップのバンプ形成領域に対応する領域に、表2に示した粒子配列群からなる導電粒子配置領域を形成した。比較例2では、導電粒子を粒子間距離4μmの4方向格子配列で、ICチップのバンプ形成面の全面に配置した。また、実施例5～9では、アライメントマークとして100μm×100μmの外形にあわせて、4方格子で一辺12個で12列（合計144個）で導電粒子配置領域を形成した。

【0095】

なお、表2における導電粒子個数は、ICチップのバンプ形成領域（ $(14\mu\text{m} + 13\mu\text{m}) \times 100\mu\text{m} \times 650 \times 2 = 3.64\text{mm}^2$ ）に存在する導電粒子数である。

【0096】

ガラス基板

10

ガラス材質 コーニング社製

外径 30×50mm

厚み 0.5mm

電極 ITO配線

【0097】

(2)導通評価

実施例5～9及び比較例2の異方導電性フィルムの(a)初期導通抵抗、(b)導通信頼性、(c)ショート発生率を、それぞれ次のように評価した。結果を表2に示す。

【0098】

(a)初期導通抵抗

20

実施例5～9及び比較例2の異方導電性フィルムを、上述のICチップとそれに対応するガラス基板との間に挟み、加熱加圧（180、80MPa、5秒）して各評価用接続物を得、その評価用接続物の導通抵抗を測定した。

【0099】

この場合、ガラス基板及び異方導電性フィルムの位置合わせは、まず、ICチップのアライメントマークに対応したマーク（100μm×100μm）をガラス基板に設けた。次に、このガラス基板に設けたマークを実体顕微鏡で確認しながら、ガラス基板と異方導電性フィルムとの位置合わせを手作業で行い、仮貼りした。この仮貼りは60、2Mpa、1秒で行った。そして、ガラス基板に仮貼りした異方導電性フィルムとICチップとを位置合わせし加熱加圧してICチップを接続した。このICチップの接続にはフリップチップボンダーFC1000（東レエンジニアリング（株））を用いた。

30

【0100】

(b)導通信頼性

実施例1と同様にしてショート導通信頼性を測定した。この導通抵抗が5以上であると、接続した電子部品の実用的な導通安定性の点から好ましくない。

【0101】

(c)ショート発生率

実施例1と同様にしてショート発生率を評価した。ショート発生率が50ppm以上であると実用上の接続構造体を製造する点から好ましくない。

【0102】

40

【表2】

| 粒子配列群における導電粒子のパターン      | 比較例2<br>均等配列 | 実施例5 | 実施例6 | 実施例7  | 実施例8  | 実施例9  |

|-------------------------|--------------|------|------|-------|-------|-------|

|                         |              |      |      |       |       |       |

| ICチップのバンプ形成領域における導電粒子個数 | 58000        | 6500 | 5200 | 10400 | 11700 | 11700 |

| 初期導通抵抗                  | 1Ω以下         | ↓    | ↓    | ↓     | ↓     | ↓     |

| 導通信頼性                   | 5Ω以下         | ↓    | ↓    | ↓     | ↓     | ↓     |

| ショート発生率                 | 50ppm未満      | ↓    | ↓    | ↓     | ↓     | ↓     |

10

20

30

40

## 【0103】

表2から、実施例5～9の異方導電性フィルムは、比較例2よりもICチップのバンプ形成領域（バンプ間スペース含む）にある導電粒子の個数が少ないが、比較例2と同様の導通特性を有し、好ましい導通特性の異方導電性フィルムを安価に製造できることがわかる。

## 【0104】

実施例10～14

50

実施例5～9において、絶縁性樹脂100部にシリカフィラー（シリカ微粒子、アエロジルRY200、日本アエロジル（株））20部を追加し、実施例5～9と同様に異方導電性フィルムを製造し、導通評価を行った。その結果、いずれも良好であった。

【0105】

実施例15～19

実施例5～9において、アライメントマークの形成を省略する以外は、実施例5～9と同様に異方導電性フィルムを製造し、導通評価を行った。その結果、実施例5～9に比してアライメントに時間を要したが、導通評価は良好であった。

【0106】

実施例20～24

実施例5～9において、初期導通抵抗の評価時に、異方導電性フィルムの導電粒子配置領域とICチップのバンプ形成領域とが僅かに重ね合わさったものを加熱加圧することにより評価用接続物を得た。この評価用接続物の導通抵抗の評価から次のことを確認できた。即ち、実施例20（実施例5の導電粒子配置）において、導電粒子群が矩形のバンプの幅方向に粒子径1個分ずれても接続できることがわかった。

【0107】

実施例21（実施例6の導電粒子配置）において、導電粒子群の中心がバンプ幅の中心からバンプ幅方向にバンプ幅の30%（4.5μm）ずれても接続できることがわかった。

【0108】

実施例22（実施例7の導電粒子配置）において、矩形に配置した導電粒子群の長辺のいずれか一辺がバンプ幅に収まれば、導電粒子群がバンプ幅方向に、導電粒子径の2個分ずれても接続できることがわかった。

【0109】

実施例23（実施例8の導電粒子配置）において、矩形に配置した導電粒子群の中心がバンプ幅の中心に対してバンプ幅方向に導電粒子径の3個分ずれても接続できることがわかった。

【0110】

実施例24（実施例9の導電粒子配置）において、矩形に配置した導電粒子群の中心がバンプ幅の中心に対してバンプ幅方向に導電粒子径の3個分ずれても接続できることができた。なお、実施例8よりも押圧された導電粒子の状態が良好であった。

【0111】

実施例25～29

実施例15において、1つのバンプに対応する導電粒子の配置を図8A～図8D及び図10に示した粒子配列群3の配列とし、実施例15と同様に導通評価を行った。この場合、バンプの大きさは実施例15と同様に15μm×100μm、バンプ間スペースは13μmであり、バンプ1個あたりの導電粒子の捕捉数は、図8Aの態様では12個、図8Bの態様では16個、図8Cの態様では12個、図8Dの態様では15個、図10の態様では16個である。これらのいずれにおいても良好な接続状態を得られた。

【符号の説明】

【0112】

1A、1B、1C、1D、1E、1F、1G、1H、1I、1J 異方導電性フィルム

2 導電粒子

3、3a、3b、3c、3e、3m、3p、3q 粒子配列群

4a、4b、4c、4e 接続用導電粒子配置領域

4d 位置合わせ用導電粒子配置領域

5 導電粒子が配置されていない中央部領域

6 導電粒子が配置されていないバッファー領域

7、7a、7b スリット線

10 絶縁接着剤層

10

20

30

40

50

|       |                |    |

|-------|----------------|----|

| 2 0   | I C チップ        |    |

| 2 1   | 出力側バンプ         |    |

| 2 1 a | 出力側バンプの配列領域    |    |

| 2 2   | 入力側バンプ         |    |

| 2 2 a | 入力側バンプの配列領域    |    |

| 2 3   | サイドバンプ         |    |

| 2 3 a | サイドバンプの配列領域    |    |

| 2 4   | アライメントマーク      |    |

| 3 0   | 基板の電極端子        |    |

| 3 1   | 基板のアライメントマーク   | 10 |

| F 1   | 異方導電性フィルムの長手方向 |    |

| F 2   | 異方導電性フィルムの短手方向 |    |

【図 1 A】

【図 1 B】

【図 1 C】

【図2】

【図3】

【図4】

【図5 B】

【図5 C】

【図5 A】

【図5D】

【図5E】

【図6】

【図7】

【図8A】

【図8B】

【図8C】

【図8D】

【 四 9 】

【図10】

【 図 1 1 】

【図 1 2】

【 図 1 3 】

【図14】

---

フロントページの続き

(72)発明者 塚尾 怜司

東京都品川区大崎一丁目11番2号 ゲートシティ大崎イーストタワー8階 デクセリアルズ株式

会社内

(72)発明者 阿久津 恭志

東京都品川区大崎一丁目11番2号 ゲートシティ大崎イーストタワー8階 デクセリアルズ株式

会社内

審査官 小野 孝朗

(56)参考文献 国際公開第2008/143358 (WO, A1)

国際公開第2008/029580 (WO, A1)

国際公開第2014/021424 (WO, A1)

(58)調査した分野(Int.Cl., DB名)

H01R 11/01