(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-30635

(P2006-30635A)

(43) 公開日 平成18年2月2日(2006.2.2)

(51) Int.C1.

G09F 9/30 (2006.01)

HO1L 51/50 (2006.01)

F 1

G09F 9/30 338

HO5B 33/14 A

テーマコード(参考)

3K007

5C094

審査請求 未請求 請求項の数 6 O L (全 10 頁)

(21) 出願番号

(22) 出願日特願2004-209889 (P2004-209889)

平成16年7月16日 (2004.7.16)

(71) 出願人 000002185

ソニー株式会社

東京都品川区北品川6丁目7番35号

(74) 代理人 100086298

弁理士 舟橋 國則

(72) 発明者 猪野 益充

東京都品川区北品川6丁目7番35号 ソニー株式会社内

(72) 発明者 藤村 寛

東京都品川区北品川6丁目7番35号 ソニー株式会社内

F ターム(参考) 3K007 AB17 BA06 DB03 GA00

5C094 AA09 BA03 BA27 CA19 DA13

FB12

(54) 【発明の名称】表示装置

## (57) 【要約】

【課題】信号線や走査線からの寄生容量を介しての容量素子への飛び込み電位の進入を防止することができ、これによりクロストーク等の表示不良を防止することができるアクティブマトリックス型の表示装置を提供する。

【解決手段】基板101上に複数行の走査線1と複数列の信号線2とがマトリックス状に配線され、これらの各交差部に画素電極と当該画素電極を駆動するための画素回路とを備えた画素部が設けられた表示装置において、画素回路を構成する容量素子(保持容量Cs、オフセット容量Coff)を覆う状態で、走査線1および信号線2に対して電界シールドとなる金属パターン106を配置した。この金属パターン106は、定電位の直流電源に接続されている。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

基板上に複数行の走査線と複数列の信号線とがマトリックス状に配線され、これらの各交差部に画素電極と当該画素電極を駆動するための画素回路とを備えた画素部が設けられた表示装置において、

前記画素回路を構成する容量素子の周辺に、前記走査線および信号線に対して電界シールドとなる金属パターンが配置されている

ことを特徴とする表示装置。

**【請求項 2】**

請求項 1 記載の表示装置において、

前記金属パターンは、絶縁膜を介して前記容量素子の上部を覆う状態で設けられていることを特徴とする表示装置。

**【請求項 3】**

請求項 2 記の表示装置において、

前記金属パターンは、前記容量素子を構成する上部電極および下部電極の上方を完全に覆う状態で設けられている

ことを特徴とする表示装置。

**【請求項 4】**

請求項 1 記載の表示装置において、

前記金属パターンは、前記画素回路を構成する配線と同一層で構成されていることを特徴とする表示装置。

**【請求項 5】**

請求項 1 記載の表示装置において、

前記金属パターンは、定電位の直流電源に接続されている

ことを特徴とする表示装置。

**【請求項 6】**

請求項 1 記載の表示装置において、

前記各画素部には、前記画素電極を用いた有機電界発光素子が設けられていることを特徴とする表示装置。

10

20

30

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、絶縁基板上に形成した薄膜トランジスタにより画素駆動を行うアクティブマトリックス型の表示装置に関し、特に薄膜トランジスタを備えた画素回路内に寄生容量効果を介しての飛び込み電位が進入することを防止するための発明である。

**【背景技術】****【0002】**

有機 E L 表示装置や液晶表示装置等の表示装置のうち、アクティブマトリックス型の表示装置においては、画素毎に薄膜トランジスタや容量素子を備えた画素回路が設けられ、この画素回路によって画素電極の駆動が行われる。

40

**【0003】**

このようなアクティブマトリックス型の表示装置では、基板上に複数行分の走査線と電源線とが交互に配線され、これらに直交する状態で複数列分の信号線が配線されている。そして、各走査線と信号線との交差部にはそれぞれ画素部が配置されており、各画素部には、走査線および信号線に隣接する位置に画素回路を構成する薄膜トランジスタや容量素子が設けられている。また、各画素部において画素回路に接続される画素電極は、走査線、信号線、さらには画素回路を覆う層間絶縁膜上に設けられており、層間絶縁膜に形成された接続孔を介して画素回路に接続されている。

**【0004】**

50

尚、画素回路を構成する薄膜トランジスタや容量素子は、同一の半導体層をパターンングすることによって形成され、これによって製造工程の簡略化を図っている（以上下記特許文献参照）。

#### 【0005】

以上のような構成のアクティブマトリックス型の表示装置のうち、有機電界発光素子（有機EL素子）を用いた有機EL表示装置においては、上記各画素電極をアノード電極（またはカソード電極）とし、この上部に有機層を介してカソード電極（またはアノード電極）を積層してなる有機EL素子が、層間絶縁膜上の各画素部に設けられている。

#### 【0006】

【特許文献1】特開平7-333651号公報

10

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0007】

しかしながら、上述した構成のアクティブマトリックス型の表示装置においては、信号線や走査線に近接して薄膜トランジスタや容量素子が配置されている。このため、信号線や走査線と、薄膜トランジスタや容量素子を構成する導電層との間には、寄生容量が発生する。そして、走査線や信号線にパルス信号が印加されることにより、寄生容量に周期的な電位変動が生じ、この寄生容量の電位変動によって容量素子に飛び込み電位が侵入する。このような容量素子への飛び込み電位により、この画素回路に接続された画素電極に対する入力電位が変動し、この入力電位の変動がクロストークと呼ばれる表示不良を引き起こす要因になっている。

#### 【0008】

特に、薄膜トランジスタを構成する半導体層がアモルファスシリコンからなる場合、容量素子を構成する上部電極または下部電極の一方もアモルファスシリコンで構成されることになるが、アモルファスシリコンは抵抗値が高いため、外部からの高周波で変動する電位に由来する速い飛び込み電位を放電する時間を確保することができない。従って、この飛び込み電位が、容量素子における周期的な電位変動となって出現し、上記クロストークが発生し易くなる。尚、半導体層がポリシリコンからなる場合であっても、金属材料と比較して抵抗値が高いため、同様の問題が生じる。

#### 【0009】

そこで本発明は、アクティブマトリックス型の表示装置において、信号線や走査線からの寄生容量を介しての容量素子への飛び込み電位の進入を防止することができ、これによりクロストーク等の表示不良が発生することがなく、優れた表示品位を達成することができる構成を提供することを目的としている。

#### 【課題を解決するための手段】

#### 【0010】

このような目的を達成するための本発明の表示装置は、基板上に複数行の走査線と複数列の信号線とがマトリックス状に配線され、これらの各交差部に画素電極と当該画素電極に接続された画素回路とを備えた画素部が設けられた表示装置において、画素回路を構成する容量素子の周辺に、走査線および信号線に対して電界シールドとなる金属パターンが配置されていることを特徴としている。

#### 【0011】

このような構成の表示装置では、走査線や信号線にパルス信号が印加されることによって急激に変動する電界が画素内に生じた場合であっても、金属パターンが電界シールドとなり容量素子に対しての電界の影響が小さく抑えられる。これにより、容量素子に対する飛び込み電位の侵入が防止される。

#### 【発明の効果】

#### 【0012】

したがって、本発明の表示装置によれば、画素回路を構成する容量素子が安定した電位に保たれ、この画素回路に接続された画素電極に安定した画像電位を供給することが可能

20

30

40

50

になる。この結果、クロストークの発生が防止され表示品位の向上を図ることが可能になる。

**【発明を実施するための最良の形態】**

**【0013】**

次に、本発明の表示装置の実施形態を図面に基づいて詳細に説明する。ここでは、本発明をアクティブマトリックス型の有機EL表示装置に適用した実施の形態を説明する。

**【0014】**

本実施形態の表示装置は、従来の技術で説明した液晶表示装置と同様に、複数行の走査線と複数列の信号線とがマトリックス状に配線され、これらの各交差部に画素部が設けられたものである。まず、図1に基づいて実施形態の表示装置の要部構成を説明するのに先立ち、本実施形態が適用される画素回路の回路構成とこの画素回路を用いた表示駆動を図3および図4に基づいて説明する。尚、以下の実施形態においては、薄膜トランジスタがpチャンネル型である場合を例示するが、薄膜トランジスタはnチャンネル型であっても良い。

**【0015】**

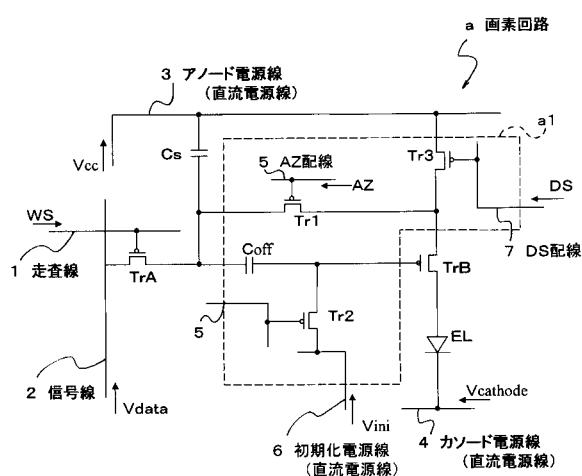

**<画素回路>**

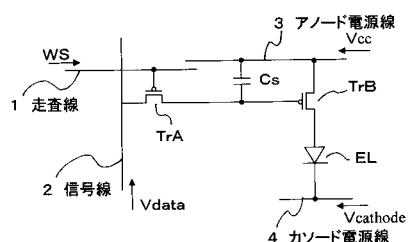

図3は、本発明が適用される表示装置（有機EL表示装置）の画素回路の一例を示す回路図である。この図に示す画素回路aにおいては、走査線1にゲートを接続させ、信号線2にソースを接続させた状態で、書き込み走査用の薄膜トランジスタ（書込トランジスタ）TrAが設けられている。この書込トランジスタTrAのドレインとアノード電源線3との間には、保持容量Csが設けられている。また、アノード電源線3と有機EL素子ELとの間には、書込トランジスタTrAと保持容量Csとの間にゲートを接続させた状態で、有機EL素子駆動用の薄膜トランジスタ（画素トランジスタ）TrBが設けられている。そして、有機電界発光素子（以下、有機EL素子）ELは、画素トランジスタTrBのドレインにアノード電極を接続させ、定電位電源であるカソード電源線4にカソード電極を接続させた状態で配置されている。

**【0016】**

またこの画素回路aには、画素トランジスタTrBの閾値Vthをキャンセルするためのオフセット回路a1が設けられている。すなわち、書込トランジスタTrAのドレインと画素トランジスタTrBのゲートの間には、閾値Vthをオフセットするためのオフセット容量Coffが設けられている。また、書込トランジスタTrAのドレインと画素トランジスタTrBのソースとの間には、AZ（Auto Zero Scan Gate Line）配線5にゲートを接続させた第1トランジスタTr1が設けられている。そして、オフセット容量Coffと画素トランジスタTrBのゲートとの間には、ソースを初期化電源線6に接続させゲートをAZ配線5に接続させた第2トランジスタTr2が設けられている。さらに、画素トランジスタTrBとアノード電源線3との間には、ゲートをDS（Drive Scan Gate Line）配線7に接続させた第3トランジスタTr3が設けられている。

**【0017】**

以上のような構成の画素回路aにおいては、信号線2から入力されたVdata信号が、走査線1からのWS信号によって制御された書込トランジスタTrAの動作により、保持容量Csに蓄積される。そして、保持容量Csに蓄積された電荷量に依存して画素トランジスタTrBが動作し、有機EL素子ELに所定流量の電流が流れ発光が生じる。

**【0018】**

また、以上のようなWS信号による書き込み動作に先立ち、第3トランジスタTr3をOFFにした状態で、DS配線7AZ配線5からAZ（Auto Zero）信号を入力すると、第1トランジスタTr1と第2トランジスタTr2とが同時にONとなり、画素トランジスタTrBのソースとゲートとが短絡し、画素トランジスタTrBのVth分のオフセット電荷がオフセット容量Coffに初期注入される。これにより、薄膜トランジスタが、低温ポリシリコンやアモルファスシリコンで構成されている場合、画素トランジスタTrBの閾値Vthにバラツキが生じた場合であっても、次の書き込み動作の際に、画素トランジスタ

10

20

30

40

50

$T_{rB}$  の閾値  $V_{th}$  がキャンセルされ、信号線 2 から入力された  $V_{data}$  信号に忠実な電流変換を可能としている。

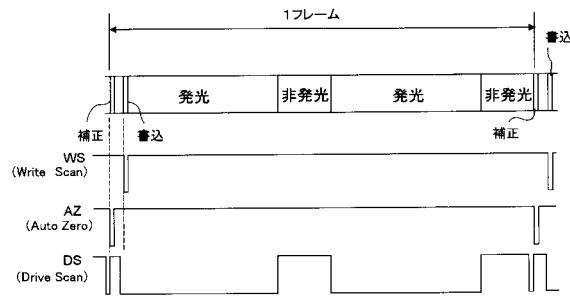

#### 【0019】

図 4 には、このような画素回路を有する 1 つの画素分の駆動を示す 1 フレーム期間分のタイミングチャート図を示した。この図に示すように、1 フレーム期間のはじめに、DS 信号を OFF にした状態で、AZ 信号の入力により画素トランジスタ  $T_{rB}$  の  $V_{th}$  分のオフセット電荷をオフセット容量  $C_{off}$  に初期注入しておく。その後、DS 信号によって第 3 トランジスタ  $T_{r3}$  を ON 状態にし、WS 信号による書き込み動作を行う。尚、このような第 3 トランジスタ  $T_{r3}$  を設けた画素回路  $a_1$  においては、第 3 トランジスタ  $T_{r3}$  を OFF 状態とすることによりに、1 フレーム期間中に非発光時間を設けてフリッカを防止することもできる。

#### 【0020】

##### <要部レイアウト>

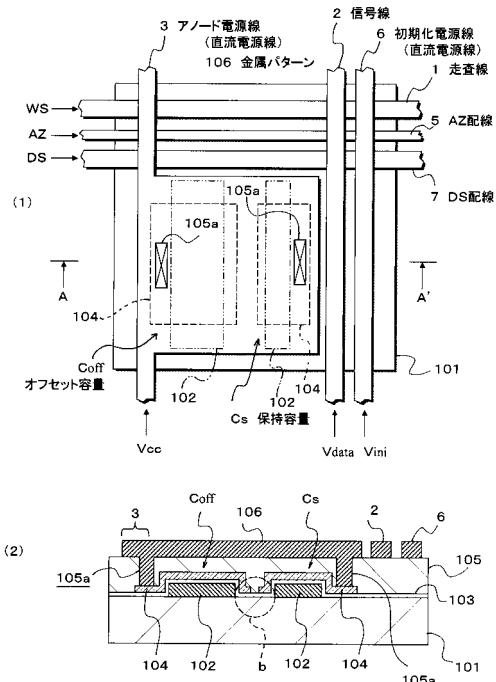

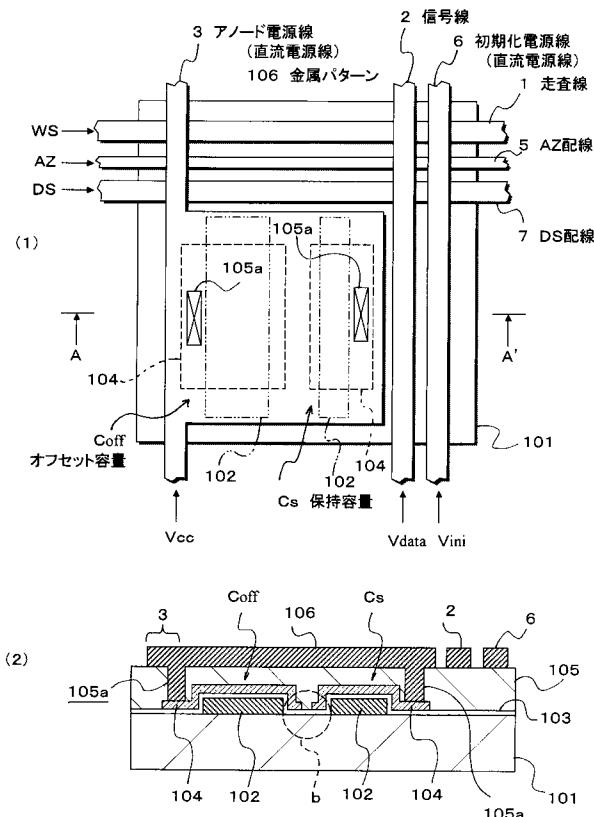

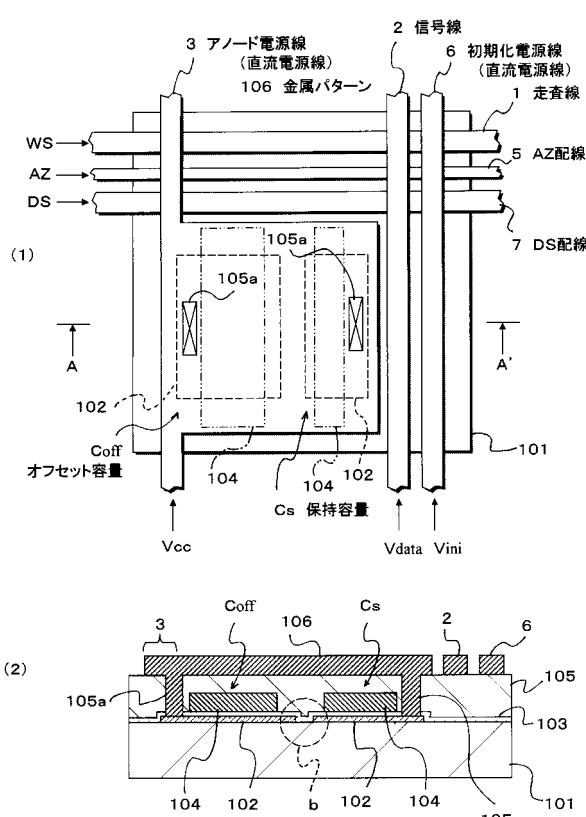

図 1(1) は、上記構成の画素回路  $a$  における要部、すなわち走査線 1 と信号線 2 とが交差する付近のレイアウトを示す平面図である。また、図 1(2) は、図 1(1) の平面図における A-A' 断面図を示す。

#### 【0021】

これらの図（主に平面図）に示すように、上述した画素回路においては、絶縁性の基板 101 上に、走査線 1 と平行に AZ 配線 5 と DS 配線 7 とが配線され、信号線 2 と平行にアノード電源配線 3 と初期化電源線 6 とが配線されている。そして、ここでの図示を省略したが、走査線 1、AZ 配線 5、および DS 配線 7 に対して一部を積層させた状態で、薄膜トランジスタ ( $T_{rA}$ 、 $T_{rB}$ 、...) が配置されている。そして、走査線 1、AZ 配線 5、および DS 配線 7 の脇で、かつアノード電源線 3 と、信号線 2 および初期化電源線 6 とに挟まれた位置に、これらの配線に隣接して保持容量  $C_s$  とオフセット容量  $C_{off}$  とが配置されている。保持容量  $C_s$  とオフセット容量  $C_{off}$  とは、10fF ~ 1000fF と非常に微少な容量で設計されている。

#### 【0022】

上記保持容量  $C_s$  とオフセット容量  $C_{off}$  は、基板 101 上に設けられた下部電極 102 と、この下部電極 102 を覆う誘電体膜 103（断面図のみに図示）と、誘電体膜 103 を介して下部電極 102 上に設けられた上部電極 104 とで構成されている。このような構成の保持容量  $C_s$  およびオフセット容量  $C_{off}$  は、この基板 101 上に設けられる薄膜トランジスタ ( $T_{rA}$ 、 $T_{rB}$ 、...) と同一層を用いて構成されている。

#### 【0023】

このため、薄膜トランジスタ ( $T_{rA}$ 、 $T_{rB}$ 、...) が、ボトムゲート型である場合（図 1 に示した例）においては、下部電極 102 は、薄膜トランジスタのゲート電極を構成する金属層をパターニングしてなり、例えばモリブデン (Mo) からなる。また、上述した走査線 1、AZ 配線 5、DS 配線 7 も、これと同一層で構成されることになる。そして、誘電体膜 103 はゲート絶縁膜と同一層で構成される。さらに上部電極 104 は、n 型または p 型の不純物を含有する半導体層をパターニングしてなる。尚、薄膜トランジスタ ( $T_{rA}$ 、 $T_{rB}$ 、...) が、トップゲート型である場合には、図 2 の平面図および断面図に示すように、下部電極 102 が半導体層からなり、上部電極 104 が金属層からなる。

#### 【0024】

このような保持容量  $C_s$  およびオフセット容量  $C_{off}$  が設けられた基板 101 の上方は、層間絶縁膜 105（断面図のみに図示）で覆われており、この層間絶縁膜 105 上に、信号線 2、アノード電源線 3、および初期化電源線 6 が配線されて、これらの配線と共に本実施形態に特有の構成である金属パターン 106 が配置されている。

#### 【0025】

この金属パターン 106 は、走査線 1 や信号線 2、さらには AZ 配線 5 や DS 配線 7 のように、信号がパルス送信する配線に対して、保持容量  $C_s$  およびオフセット容量  $C_{off}$  を保護するための電界シールドとなるものである。このため、金属パターン 106 は、保

持容量  $C_s$  やオフセット容量  $C_{off}$  の上方を十分に覆っている必要がある。特に、保持容量  $C_s$  およびオフセット容量  $C_{off}$  を構成する半導体層の上部を完全に覆うことが好ましい。したがって、図 1 に示したボトムゲート型の例においては、半導体層からなる上部電極 104 の上方を、下部電極 102 の下方に配置されているフリンジ部分 b まで、完全に覆う状態で金属パターン 106 が配置されることが好ましく、最も好ましくは金属材料からなる下部電極 102 も含めて容量素子  $C_s$ ,  $C_{off}$  を構成する下部電極 102 および上部電極 104 の上方を完全に覆うことが好ましい。これは、図 2 に示したトップゲート型の例、すなわち下部電極 102 が半導体層からなる場合も同様である。ただし、レイアウト上の問題から半導体層からなる電極の上部を完全に覆うことができない場合であっても、できるだけ広い面積で半導体層からなる電極の上部を覆うことが好ましい。

10

## 【0026】

また、この金属パターン 106 は、定電位の直流電源に接続されていることとする。このためここでは、この金属パターン 106 をアノード電源線 3 から延設させた構成とした。そして、容量素子  $C_s$ ,  $C_{off}$  を覆う層間絶縁膜 105 に設けられた接続孔 105a を介して、金属パターン 106 と一体形成されたアノード電源線 3 が容量素子  $C_s$ ,  $C_{off}$  に接続されている。この接続状態は、図 1 に示したボトムゲート型の例においては、半導体層からなる上部電極 104 にアノード電源線 3 を接続させる一方、図 2 に示したトップゲート型の例においては、半導体層からなる下部電極 102 にアノード配線 3 を接続させる。尚、金属パターン 106 は、定電位の直流電源に接続されなければ良いため、アノード電源線 3 に接続されている構成に限定されることではなく、初期化電源線 6 や、ここでは図示されないさらに上層に設けられたカソード電源線、さらにはその他の定電位の直流電源に接続されていても良い。

20

## 【0027】

さらに、この金属パターン 106 は、導電性の良好な金属材料で構成されることが好ましく、アノード電源線 3 から延設させた構成としたことにより、信号線 2、アノード電源線 3、および初期化電源線 6 と同一層で構成されている。尚、このような金属パターン 106 の構成材料としては、例えばアルミニウム (Al) を主成分とし、シリコン (Si)、チタン (Ti)、モリブデン (Mo)、マグネシウム (Mg)、銀 (Ag)、銅 (Cu)、クロム (Cr)、鉄 (Fe)、サマリウム (Sm) 等を適宜比率で混ぜた合金が好ましく用いられる。

30

## 【0028】

## &lt;画素表示部分の構成&gt;

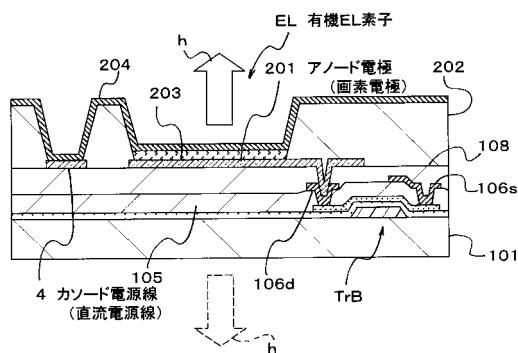

図 5 は、上記構成の画素回路を備えた各画素部における画素表示部の断面図である。

## 【0029】

この図に示すように、上記構成の画素回路が形成された基板 101 の上方には、先に説明した保持容量やオフセット容量を覆う層間絶縁膜 105 のさらに上部に、各薄膜トランジスタ（ここでは画素トランジスタ TrB を図示）に接続されたソース電極線 106s およびドレイン電極線 106d が設けられている。これらのソース電極線 106s およびドレイン電極線 106d は、上述した保持容量やオフセット容量の上部を覆う金属パターンや、信号線、さらにはアノード電源線と同一層で構成されている（図 1 参照）。

40

## 【0030】

これらのソース電極線 106s およびドレイン電極線 106d は、各薄膜トランジスタ（画素トランジスタ TrB）に接続され、層間絶縁膜 105 上において配線されている。そして、これらのソース電極線 106s およびドレイン電極線 106d の層を覆う状態で、さらに上層の層間絶縁膜 107 が設けられ、この層間絶縁膜 107 上に有機 EL 素子 EL が設けられている。

## 【0031】

この有機 EL 素子 EL は、層間絶縁膜 108 に設けた接続孔 108a を介して画素トランジスタ TrB のドレイン電極線 106d に接続されたアノード電極 201 を備えている。このアノード電極 201 は、画素電極としてパターニングされており、その周囲が絶縁

50

膜パターン202で覆われて中央部のみが広く露出した状態となっている。また、各アノード電極201の露出部上には、それぞれバーニングされた状態で、少なくとも発光層を備えた有機層203が積層されている。この有機層203に設けられる発光層は、当該発光層に注入された正孔と電子との再結合によって発光を生じる有機材料からなることとする。そして、このようにバーニングされた各有機層203と絶縁膜パターン202の上方に、アノード電極201との間に絶縁性が保たれた状態でカソード電極204が配置形成されている。このカソード電極204は、各有機EL素子ELに共通の電極として形成されている。

#### 【0032】

また、層間絶縁膜108上には、アノード電極201と同一層で、カソード電源線4が10

パターン形成されており、このカソード電源線4上に接してカソード電極204が設けら

れている。

#### 【0033】

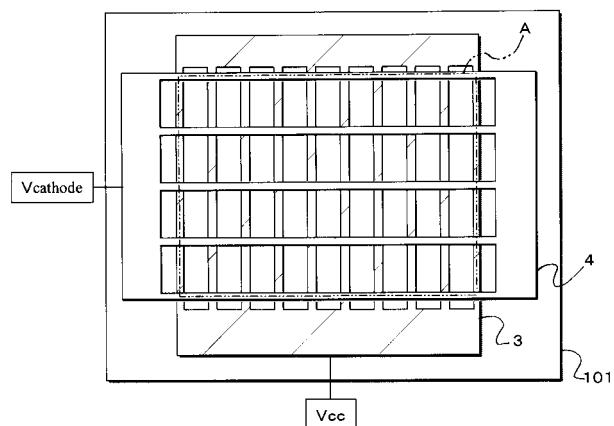

図6は、基板101の上方におけるカソード電源線4のレイアウトを示す平面図である。

この図に示すように、基板101の上方において画素部が並列配置される表示領域Aには、下層に配置されるアノード電源線3に対して交差する状態でカソード電源線4が配置される。これらのアノード電源線3およびカソード電源線4は、それぞれ共通のバスラインとして配線されており、アノード電源線3とカソード電源線4とが交差する部分に各画素部が設けられている。尚、この表示装置がフルカラー表示されるものであれば、青(B)色の画素部と、緑(G)色の画素部と、R(赤)色の画素部とが、所定状態で交互に配列されていることとする。

#### 【0034】

この様に配線された有機EL素子ELは、アノード電極201とカソード電極204との間に狭持された有機層203に正孔と電子とを注入することにより、有機層203の発光層部分において発光が生じる構成となっている。尚、この表示装置が、カソード電極204側から発光光hを取り出す上面発光型(いわゆるトップエミッション型)である場合、カソード電極204は光透過性の高い材料を用いて構成されることとする。一方、この表示装置が、基板101側から発光光hを取り出す透過型(いわゆるボトムエミッション型)である場合、基板103およびアノード電極201は光透過性の高い材料を用いて構成されることとする。

#### 【0035】

以上説明した構成の表示装置では、図1を用いて説明したように、画素回路を構成する保持容量Csおよびオフセット容量Coffを、直流電源線であるアノード電源線3に接続させた構成としている。このため、これらの容量素子Cs、Coffの近接する走査線1、信号線2、AZ配線5、およびDS配線7から、図4を用いて説明したように各信号がパルス的に印加された場合であっても、この金属パターン106が電界シールドとなり、上記パルス信号に起因する電界が容量素子Cs、Coffに大きな影響を及ぼすことを防止できる。

#### 【0036】

特に、容量素子Cs、Coffを構成する半導体層102と、これらの容量素子Cs、Coffに近接して配置される各配線との間には寄生容量が発生するが、半導体層102の上方が十分に金属パターン106で覆われているため、この寄生容量に対して上記パルス信号に起因する電界が影響を及ぼすことが防止され、この寄生容量を介しての容量素子Cs、Coffに対する飛び込み電位の侵入が防止される。

#### 【0037】

したがって、本発明の表示装置によれば、10fF～1000fFと非常に微少な容量で設計された容量素子Cs、Coffが、周辺の配線にパルス的(交流的)に印加される信号に影響されることなく安定した電位に保たれ、この画素回路に接続された有機EL素子のアノード電極(画素電極)に安定した画像電位を供給することが可能になる。この結果、走査線1、信号線2、AZ配線5、およびDS配線7等に沿って、階調不良が生じるク

10

20

30

40

50

クロストークの発生が防止され、表示品位の向上を図ることが可能になる。

#### 【0038】

また本実施形態においては、図3に示したように、もともと保持容量  $C_s$  およびオフセット容量  $C_{off}$  が接続されたアノード電源線3から金属パターン106を延設し、図1に示したように、この金属パターン106で保持容量  $C_s$  とオフセット容量  $C_{off}$  の上部を覆った。このため、この金属パターン106が積層されている部分も容量素子の一部とすることができる。したがって、保持容量  $C_s$  およびオフセット容量  $C_{off}$  における単位面積あたりの容量を増加させることができるのである。これにより、保持容量  $C_s$  およびオフセット容量  $C_{off}$  の専有面積を縮小し、画素部における開口面積を広くすることができる。そして、有機EL素子に印加する電流を増加させずに高輝度化が可能となる。さらに、輝度を一定とした場合には、有機EL素子に流す電流を下げることが可能となるため、有機EL素子の長寿命化を図ることが可能になる。10

#### 【0039】

以上説明した実施形態においては、図1を用いて説明したように、保持容量  $C_s$  とオフセット容量  $C_{off}$  の上部を覆う金属パターン106を、アノード電源線3に接続させた構成を説明した。しかしながら、先にも述べたように、金属パターン106は、定電位の直流電源に接続されれば良いため、初期化電源線6や、図5を用いて説明したカソード電源線4に接続させた構成でも良い。20

#### 【0040】

ただし、金属パターン106を初期化電源線6に接続させる場合には（図1参照）、アノード電源線3と保持容量  $C_s$  およびオフセット容量  $C_{off}$  との接続を維持した状態で、保持容量  $C_s$  およびオフセット容量  $C_{off}$  を覆う金属パターン106と、アノード配線3とを分離する。そして、金属パターン106を初期化電源線6から延設された状態にパターン形成する。20

#### 【0041】

また、図5を用いて説明したカソード電源線4に対して、図1を用いて説明した金属パターン106を接続させる場合には、アノード電源線3と保持容量  $C_s$  およびオフセット容量  $C_{off}$  との接続を維持した状態で、保持容量  $C_s$  およびオフセット容量  $C_{off}$  を覆う金属パターン106と、アノード配線3とを分離する。そして、これらを覆う層間絶縁膜、すなわち図5に示した層間絶縁膜108に接続孔を形成し、この接続孔を介して金属パターン106とカソード電源線4とを接続させる。30

#### 【0042】

さらに上述した実施形態においては、有機EL素子ELの構成として、基板101側から順にアノード電極201、有機層203、カソード電極204を配置した構成を説明した。しかしながら、有機EL素子ELは、この積層順を逆にした構成であっても良い。この場合、有機EL素子ELのカソード電極が画素トランジスタTrBに接続された構成となり、上述したアノード電源線とカソード電源線とを逆に読み替えることとする。

#### 【0043】

また、上述した実施形態においては、図3を用いて説明した画素回路aを有する表示装置に本発明を適用した構成を説明した。しかしながら本発明は、例えば図3の画素回路aからオフセット回路a1を除き、図7に示す様な画素回路を有する表示装置にも適用可能であり、上述した実施形態の表示装置と同様にクロストークを防止する効果を得ることができる。40

#### 【0044】

さらに、上述した実施形態においては、有機EL素子を用いた有機EL表示装置に本発明を適用した場合を例示したが、本発明はアクティブマトリックス駆動の表示装置において、画素回路が容量素子を有する構成に広く適用可能であり、同様の効果を得ることが可能である。

#### 【図面の簡単な説明】

#### 【0045】

【図1】本実施形態の表示装置における要部構成（ボトムゲート型）を説明するための図である。

【図2】本実施形態の表示装置における要部構成（トップゲート型）を説明するための図である。

【図3】実施形態の表示装置における画素回路を示す回路図である。

【図4】1画素分の表示を示すタイミングチャートである。

【図5】本実施形態の表示装置の各画素部における画素表示部の断面図である。

【図6】アノード電源線およびカソード電源線のレイアウトを示す平面図である。

【図7】本発明が適用される表示装置の他の画素回路例である。

#### 【符号の説明】

#### 【0046】

101...基板、1...走査線、2...信号線、3...アノード電源線（直流電源線）、4...カソード電源線（直流電源線）、5...AZ配線、6...初期化電源線（直流電源線）、7...DS配線、105...層間絶縁膜（絶縁膜）、106...金属パターン、201...アノード電極（画素電極）、a...画素回路、Cs...保持容量（容量素子）、Coff...オフセット容量（容量素子）、EL...有機EL素子（有機電界発光素子）

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】